Analog turbo-networks in VLSI The next step in turbo decoding and equalization

Esoteric N-03T网络音频传输系统说明书

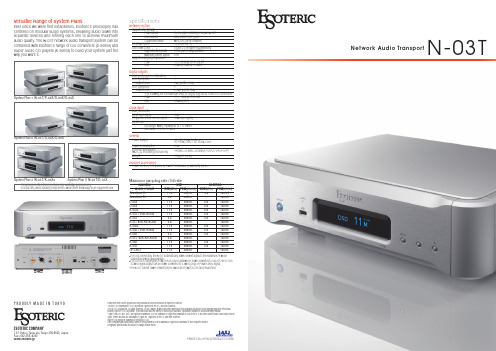

Network Audio Transpor tN-03TVersatile Range of System PlansEver since we were first established, Esoteric’s philosophy has centered on modular audio systems, breaking audio down into separate devices and refining each one to achieve maximum audio quality. The N-03T network audio transport system can be combined with Esoteric’s range of D/A converters (D series) and Super Audio CD players (K series) to build your system just the way you want it.USB XLR/RCAGrandioso K111.2 384/32 2.8 192/24Grandioso D1 5.6 384/32 - 192/24D-02X 11.2 384/32 2.8 192/24D-05X 11.2 384/32 2.8 192/24K-01Xs 11.2 384/32 2.8 192/24K-01X + VUK-K01Xs 11.2384/322.8192/24K-01X 5.6 384/32 2.8 192/24K-01+ V UK-K01XUSB 2.8 384/32 - 192/24K-03Xs 11.2 384/32 2.8 192/24K-03X + VUK-K03Xs 11.2 384/32 2.8 192/24K-03X 5.6 384/32 2.8 192/24K-03 + VUK-K01XUSB 2.8384/32-192/24K-05X 11.2 384/32 2.8 192/24K-07X 11.2 384/32 2.8 192/24OP-DAC111.2 384/32 - 192/24Maximum sampling rate / bit rateConnection Models / FormatDSD (MHz) PCM (kHz/bit) DSD (MHz) PCM (kHz/bit ) System Plan 1 N-03T/P-02X/D-02X/G-02XSystem Plan 2 N-03T/D-02X/G-02XSystem Plan 3 N-03T/K-03Xs System Plan 4 N-03T/D-05X* The arrangements in these photos are for illustrative purposes only.In actual use, avoid stacking components. Mount them individually in an equipment rack.PRINTED IN JAPAN 0218O05•TECD-0266ESOTERIC COMPANY1-47 Ochiai, Tama-shi, Tokyo 206-8530, Japan Fax: (042)356-9240www.esoteric.jpPlease note that Esoteric products are only available at select distributors in respective countries.“Esoteric” is a trademark of TEAC Corporation, registered in the U.S. and other countries.©2018 TEAC Corporation. All Rights Reserved. All text, images, graphics and other materials in this catalogue are subject to the copyright and other intellectual property rights of TEAC Corporation. These materials shall not directly or indirectly be published, reproduced, modified or distributed in any medium.“Super Audio CD” and “DSD” are registered trademarks. IOS is a trademark or registered trademark of Cisco in the U.S. and other countries and is used under license.Apple, iPhone and iPad are trademarks of Apple Inc., registered in the U.S. and other countries. Bulk Pet is a registered trademark of Interface Co.,Ltd.Other company names and product names in this document are the trademarks or registered trademarks of their respective owners.Design and specifications are subject to change without notice.P R O U D L Y M A D E I N T O K Y O•For USB connection, the N-03T automatically down-convert signal to the maximum Fs whichconnected device can playback.•For XLR/RCA connection, PCM 384/352.8kHz data will be down-converted to 192/176.4kHz. DSD 5.6MHz signal output can be down-converted to 2.8MHz (Dop) or PCM88.2kHz signal.*The N-03T cannot down-convert DSD11.2MHz and PCM768/705.6kHz music files.SpecificationsNetwork sectionSupported file formats PCM lossless FLAC , Apple Lossles s (ALAC), WAV, AIFFDSD lossless DSF , DSDIFF (DFF ), DoP Compressed audio MP3, AAC (m4a container ) ETHERNET port1(1000BASE-T)USB DRIVE ports 2 (USB 2.0 or higher recommended) Supported file formats FAT32, NTFS Single partition Maximum current supply 0.5ASupported sampling frequencies PCM 44.1–384kHz, 16/24/32 bitDSD 2.8MHz, 5.6MHz, 11.2MHzDigital outputsUSB port (USB 2.0 standard) 1 X LR connector 1Output level 3Vp-p (into 110Ω) RCA connector 1Output level0.5Vp-p (into 75Ω)*The following are the maximum limits for output from the XLR and RCA connectors. PCM 44.1–192kHz, 16/24 bitDSD2.8MHz (Do P )Clock inputBNC connector 1 Input impedance50ΩFrequencies that can be input 10MHz(±10ppm)Input level Rectangle wave: equivalent to TTL levels Sine wave: 0.5 to 1.0 VrmsGeneralPower supply AC 220-240V, 50/60HzAC 120V, 60Hz / AC 220V, 60Hz Power consumption31WExternal dimensions(W×H×D, including protrusions) 445m m ×131m m ×360mm(17 5/8"×5 1/4"×14 1/4") Weight17kg (37 1/2 lb)Included accessoriesPower cor d ×1, Felt pad s ×3, Owner’s manual ×1, Warranty car d ×1High-Sampling Digital OutputThe N-03T has a USB port enabling digital output up to DSD 11.2MHz and PCM 384kHz/32-bit. This allows the N-03T to be connected to a USB DAC or a disc player with a USB port.Two other digital output systems (XLRx1 and RCAx1) are also included, supporting PCM up to 192kHz/24-bit and DSD2.8MHz (DoP).Music Server FunctionThe N-03T can also be used as a simplified music server in which a player and a librar y can be integrated by connecting large-capacity storage devices to two USB ports on the front and rear of the unit.Compatible with a Wide Range of Streaming Services and Audio CodecsEsoteric has partnerships with a wide range of streaming service and audio codec providers, and preparations are underway for compatibility with new services.**Information on newly supported services will be released on the ESOTERIC website. However, regional restrictions may be implemented on some services.Compatible with a Wide Range of Audio SourcesCare has been taken with every detail to achieve audio quality suitable for high-end network playback. The N-03T is compatible with a vast range of formats (DSF, DSDIFF, FLAC, Apple Lossless, WAV, AIFF, MP3 and AAC) and supports playback up to DSD 11.2MHz and PCM 384kHz/32-bit by USB output. Gapless playback is also suppor ted for all lossless formats for uninterrupted playback of live or opera recordings.Esoteric Sound StreamEsoteric Sound Stream is an Apple iOS network playback app for tablets and smartphones designed with an emphasis on intuitive operability. Simply select music tracks by using your tablet or smartphone to create a customized playlist and then play the playlist. All screens are intuitively designed for easy operation and access to playlists and libraries, making it easy for anyone to use. It also has a wide range of advanced features that meet the demands of even the most experienced users.A key feature is the excellent search and retrieval function that fully utilizes tag information. Images are also stored in the app, enabling you to instantly scroll through album artwork and libraries according to categories such as artist, year of recording, composer or category.Equipped with Two Powerful Independent Power SuppliesThe N-03T is equipped with two large independent toroidal transformers, one for the internal network module and one for the other digital circuits, enabling the ideal supply of power to each circuit block. Unlike a standard switching power supply, these large linear power supplies are made with high qualit y components such as large filter capacitors and Schottky barrier diodes. The dedicated power supply for the network module also has an EDLC (Electric Double-layer Capacitor), a super-capacitor that has 1F (1,000,000μF) capacitance. These provide a dramatic improvement in audio quality.High-Rigidity Chassis ConstructionThe bottom chassis used to secure the circuit components has a dual layer structure with two steel plates (5mm and 2mm). Th e power supply transformer and oth er components are arranged th ree-dimensionally on th e two layers to prevent interference between components, and laser-cut slits are applied to each layer for effective controlling of vibration. And a th ick, h eavyweigh t aluminum panel enclosure and Esoteric’s unique pinpoint feet (patents no. JP4075477 and JP3778108) provide t oroug mechanical grounding against vibration.P R O U D L Y M A D E I N T O K Y ONetwork AudioThe N-03T fulfills every music lover’s dream: to access music freely from your living room chair and enjoy the very best audio quality. The DSD master audio source provides a crystal-clear audio experience, your CD collection is arranged in a library for easy access, and streaming services put new music at your fingertips. The N-03T is a network audio transport system specially designed to connect with an external DAC or a Super Audio CD player’s built-in DAC via USB connection. Other than your audio system, all you need is a home LAN (Wi-Fi router, etc.), a tablet or smartphone and a NAS (music server) to store your music library. That’s all you need for an easy, comfortable musicexperience where you don’t have to compromise on quality.N-03TNetwork Audio TransportMassive, super high quality modular systems are the key philosophy that Esoteric has followed since we were first established.We are now bringing this same philosophy to network playback systems with the N-03T network digital audio transport system.Your favorite D/A converter or Super Audio CD player can be digitally connected by USB, enabling you to build just the right system to enjoy playing files or streaming content your way.Esoteric takes digital transport to a new level with endless options and even more possibilities for audio playback.N-03TTablet / SmartphoneD/A converterSuper Audio CD player,etc.USB / XLR / RCA Digital connection Internet。

思博伦CyberFlood添加全新的虚拟和可扩展测试能力

界

要

闻

七七七七七七七七七七七七七

七七七七七七七七七七七七七

《信息通信技术与政策》2018 年 7 月第 7 期

业界要闻

思博伦荣获东京 Interop 2018 展多项大奖,

400G 以及安全测试方案均上榜

的合作伙伴,

思博伦满足客户快速发展需求的能力。

思博伦 CyberFlood 添加全新的虚拟和

在 6 月 13—15 日举办的东京 Interop 展上,思博伦通信荣

更强的测试选择,这不仅符合当前的需要,同时也为将来做

实的 TCP/UDP 流量,可扩展至数以百万计的用户和连接,对

好了准备。”

要求高性能、高密度的客户来说,

是理想的选择。

在此次 Interop Tokyo 展会上,思博伦 400G 方案被多家合

用户可以使用 CF20 在数分钟内完成测试的部署和启

动,单台 1U 设备即可提供 1G/10G/40G 和 100G 连接速率。

解决方案。本次展会上,思博伦有数个解决方案入围 Best of

云和 SDN/NFV 领域的多样化的测试选项。CF20 是一种多

Interop Show 决赛,其中包括最终获奖的 PX3-400G 测试模

合一、尺寸小巧且高度便携的多速率测试设备,具备 Cyber-

块,以及小巧且高度便携的多速率安全测试设备 CF20。

水平。

一种理想的测试解决方案。

CF20 是 2018 年推出的一种多合一、尺寸小巧且高度便

思博伦在日本的经销商伙伴 Toyo 公司总经理 Masahiko

携的多速率测试设备,可用来验证用户的网络性能和安全,

Kawauchi 指出:

“ 在先进的安全和性能测试中,CF20 是一个

RBK40 全家型 AC2200 三带 WiFi 系统说明书

Data SheetRBK40Whole Home AC2200 Tri-band WiFi SystemOverviewThis Orbi WiFi System comes with an Orbi WiFi Router and Satellite that deliver unparalleled WiFi coverage. It covers homes up to 4,000 square feet with strong WiFi signals. Innovative Tri-band WiFi helps maximize the Internet speeds available in your home.Enjoy better WiFi. Everywhere.FeaturesSingle Network Name.One WiFi name and seamless roaming for your whole home to enjoy.Max Internet Speeds.Innovative Tri-band WiFi helps deliver fast Internet speeds even as more devices connect.Your Home. Covered.This kit of two covers up to a 4,000 sq ft † home with high-performance AC2200 WiFi.Simple & Secure.Use the Orbi app or a web browser to create secure whole home WiFi in minutes. With no accounts to set up.Data SheetRBK40Whole Home AC2200 Tri-band WiFi SystemHouse DiagramD E D I CA T E DT R I-B AN DC O N N EC T I ONINTERNETOrbi SatelliteOrbi Router4,000 Square Feet of Orbi WiFi CoverageDedicated Tri-band Connection ensures devices connect directly to maximum Internet speeds1Internet plan and devices that support these speeds are required.Simple setup from your smartphone or tablet.Use the Orbi app to set up and manage your network. To find the app, scan one of the following QR codes or search for NETGEAR Orbi in the Apple App Store or Google Play Store.Data SheetRBK40 Whole Home AC2200 Tri-band WiFi SystemOrbi Router (RBR40)Sync buttonPower buttonPlugs intoexisting modemPlugs into Ethernet-enabled devicesSync buttonPower buttonPlugs into Ethernet-enabled devicesOrbi Satellite (RBS40)Data SheetRBK40Whole Home AC2200 Tri-band WiFi SystemTechnical Specifications• O rbi AC2200 Router & AC2200 Satellite (866+866+400Mbps)†• Simultaneous Tri-band WiFi- R adio 1: IEEE ® 802.11b/g/n 2.4GHz–256QAM support - R adio 2: IEEE ® 802.11a/n/ac 5GHz–256QAM support - R adio 3: IEEE ® 802.11a/n/ac 5GHz–256QAM support • Dedicated Backhaul Technology• F our (4) high-performance antennas with high-power amplifiers • I mplicit/Explicit Beamforming for 2.4 & 5GHz bands (866+866+400Mbps)†• M U-MIMO capable for simultaneous data streaming on multiple devices • F our (4) 10/100/1000Mbps Gigabit Ethernet ports - O rbi Router (RBR40): 1 WAN & 3 LAN - O rbi Satellite (RBS40): 4 LAN • S ecurity- W PA/WPA2-PSK support- G uest WiFi Network is easy to setup separate& secure Internet access for guestsThis product comes with a limited warranty that is valid only if purchased from a NETGEAR authorized reseller.* 90-day complimentary technical support following purchase from a NETGEAR authorized reseller.† M aximum wireless signal range derived from IEEE standard 802.11 specifications. Actual data throughput and data over distance will vary. Network conditions and environmental factors, including volume of network traffic, building material and construction, and network overhead, result in lower actual data throughput rate and wireless coverage.1Internet plan and devices that support these speeds are required.For indoor use only.For regulatory compliance information, visit /about/regulatoryNETGEAR, the NETGEAR Logo, and Orbi are trademarks and/or registered trademarks of NETGEAR, Inc. Any other trademarks mentioned herein are for reference purposes only. ©2017 NETGEAR, Inc.NETGEAR, Inc. 350 E. Plumeria Drive, San Jose, CA 95134-1911 USA, /supportD-RBK40-2Physical Specifications• Orbi Router (RBR40)- D imensions: 6.4 x 3.1 x 8.0 in - W eight: 1.65 lb • Orbi Satellite (RBS40)- D imensions: 6.4 x 3.1 x 8.0 in - W eight: 1.65 lbWhat’s In the Box?• One (1) Orbi Router (RBR40)• One (1) Orbi Satellite (RBS40)• One (1) 2m Ethernet cable • Two (2) 12V/2.5A power adapters • Quick start guideWhat Do I Need for Orbi to Work?• High-speed Internet connection • Connect to existing modem or gateway。

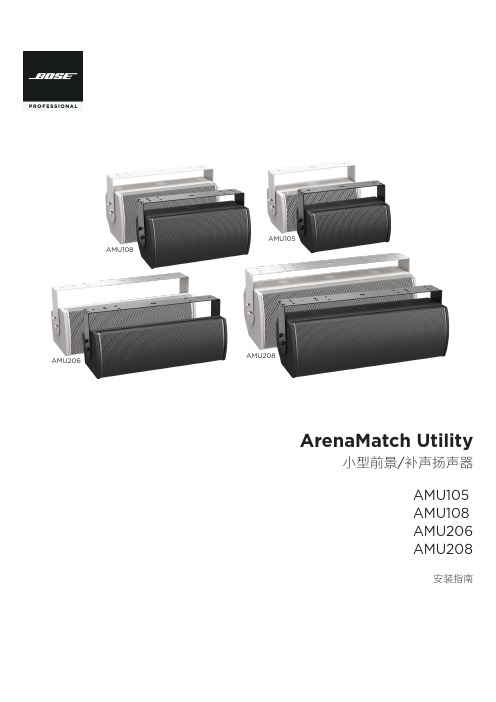

ArenaMatch Utility 小前景 补声扬声器 AMU105 AMU108 AMU206

规范信息

本产品符合所有适用的欧盟指令要求。您可以从网站 /compliance 找到完整的符合性声明。

此符号表示不得将此产品作为生活垃圾丢弃,应将其送到合适的 回收站点进行回收。正确处理和回收有助于保护自然资源、人类 健康和环境。想要获得更多关于此产品的处理和回收的信息,请 联系当地市政当局、垃圾处理服务部门或您购买此产品的商店。

中国危险物质限用表

有毒或有害物质或元素名称及成分

有毒或有害物质和元素

零件名称

铅

汞

(Pb) (Hg)

镉 ()

六价铬 (CR(VI))

多溴化 联苯 (PBB)

印刷电路板 X

O

O

O

O

金属零件

X

O

O

O

O

塑料零件

O

O

O

O

O

扬声器

X

O

O

O

O

线缆

X

O

O

O

O

此表格依据 SJ/T 11364 的要求制定。

O:表示此零件中所有均质材料所包含的此类有毒或有害物质均低于 GB/T 26572 中的限定要求。

6. 只能使用制造商指定的附件/配件。

7.

只能使用制造商指定或随本设备一起销售的推车、支架、

三角架、托架或工作台。如果使用推车,则在移动推车/设

备时应格外小心,以免因倾倒而造成伤害。

警告/小心:

包含可能导致窒息危险的小部件。不适合 3 岁以下的儿童使用。

本产品含有磁性材料。有关这是否会影响到您的植入式医疗器 械,请咨询您的医生。

包装清单................................................................................................................................................................................................... 5 可选配件................................................................................................................................................................................................... 5 检查和维护....................................................................................................................................................................................................... 6 保持防风雨性........................................................................................................................................................................................... 6 推荐使用的工具.............................................................................................................................................................................................. 6 产品尺寸........................................................................................................................................................................................................... 7 ArenaMatch Utility AMU105........................................................................................................................................................... 7 ArenaMatch Utility AMU108........................................................................................................................................................... 8 ArenaMatch Utility AMU206.......................................................................................................................................................... 9 ArenaMatch Utility AMU208........................................................................................................................................................ 10

一种高吞吐低延迟片上互连网络路由器

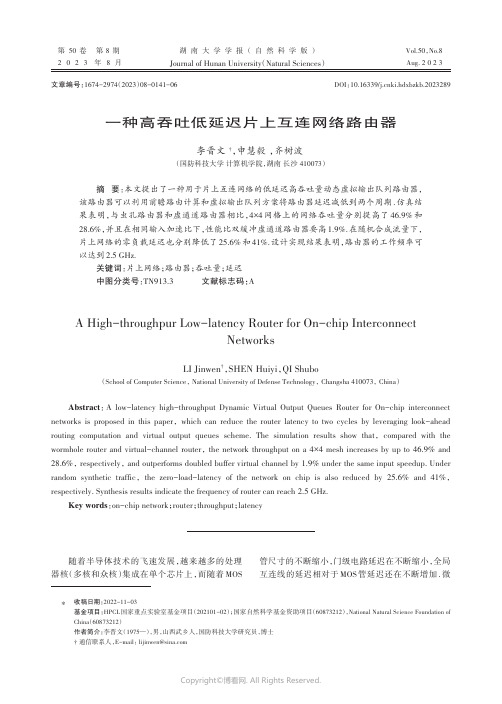

第50 卷第 8 期2023年8 月Vol.50,No.8Aug. 2023湖南大学学报(自然科学版)Journal of Hunan University(Natural Sciences)一种高吞吐低延迟片上互连网络路由器李晋文†,申慧毅,齐树波(国防科技大学计算机学院,湖南长沙 410073)摘要:本文提出了一种用于片上互连网络的低延迟高吞吐量动态虚拟输出队列路由器,该路由器可以利用前瞻路由计算和虚拟输出队列方案将路由器延迟减低到两个周期.仿真结果表明,与虫孔路由器和虚通道路由器相比,4×4网格上的网络吞吐量分别提高了46.9%和28.6%,并且在相同输入加速比下,性能比双缓冲虚通道路由器要高1.9%.在随机合成流量下,片上网络的零负载延迟也分别降低了25.6%和41%.设计实现结果表明,路由器的工作频率可以达到2.5 GHz.关键词:片上网络;路由器;吞吐量;延迟中图分类号:TN913.3 文献标志码:AA High-throughpur Low-latency Router for On-chip InterconnectNetworksLI Jinwen†,SHEN Huiyi,QI Shubo(School of Computer Science, National University of Defense Technology, Changsha 410073, China)Abstract:A low-latency high-throughput Dynamic Virtual Output Queues Router for On-chip interconnect networks is proposed in this paper,which can reduce the router latency to two cycles by leveraging look-ahead routing computation and virtual output queues scheme. The simulation results show that,compared with the wormhole router and virtual-channel router, the network throughput on a 4×4 mesh increases by up to 46.9% and 28.6%, respectively, and outperforms doubled buffer virtual channel by 1.9% under the same input speedup. Under random synthetic traffic,the zero-load-latency of the network on chip is also reduced by 25.6% and 41%,respectively. Synthesis results indicate the frequency of router can reach 2.5 GHz.Key words:on-chip network;router;throughput;latency随着半导体技术的飞速发展,越来越多的处理器核(多核和众核)集成在单个芯片上,而随着MOS 管尺寸的不断缩小,门级电路延迟在不断缩小,全局互连线的延迟相对于MOS管延迟还在不断增加.微∗收稿日期:2022-11-03基金项目:HPCL国家重点实验室基金项目(202101-02);国家自然科学基金资助项目(60873212),National Natural Science Foundation of China(60873212)作者简介:李晋文(1975—),男,山西武乡人,国防科技大学研究员,博士† 通信联系人,E-mail:*****************文章编号:1674-2974(2023)08-0141-06DOI:10.16339/ki.hdxbzkb.2023289湖南大学学报(自然科学版)2023 年处理器体系结构设计的重点正在从以提高计算为中心的单核能力设计转向以互连通信为中心的多核设计.由于互连延迟可预测、设计复杂度比较低、易扩展性和结构规整,片上网络已成为CMP和MPSoC中片上众核互连最有前途的选择[1].其中2D mesh互连网络已广泛应用于许多原型芯片,如Intel 80核Tera⁃flop、Tilera 64核和TRIPS[2-4].片上网络的概念来源于多处理器间互连网络,但实际与多芯片间互连网络有着许多不同的特点.最重要的一点,芯片内互连线和引脚比芯片间网络中的互连线和引脚资源更丰富[1].然而,片上网络中缓冲buffer容量不足.网络的延迟对实际多核的计算性能有很大影响.当路由器的每跳延迟从一个周期增加到五个周期时,全系统的性能将下降10%[5].基准的虚通道路由器的流水线级数为4.近年来,业界提出了几种新型架构的低延迟路由器,包括推测虚通道路由器[6]、采用虫孔交换的两虚通道结构路由器[7]、混合电路交换路由器[5]、带bundle的两周期路由器[8]、组合型两周期路由器[9]、无缓存片上路由器[10]、基于时间序列开关分配路由器[11]以及关键路径延迟只有35个FO4[12]的单周期路由器(FO4是指一个反相器驱动四个相同尺寸反相器产生的延迟,高性能微处理器的周期一般约为20个FO4).缓冲buffer的实现对互连网络的性能至关重要.缓冲buffer可以用寄存器或SRAM来实现.在芯片中,通常缓冲buffer的容量相对较小,因此使用低延迟的寄存器实现更为有利,而使用SRAM会存在较大的地址译码延迟以及存储阵列访问延迟,这些延迟与全局位线相关;此外还能节省位线预充电功耗[13].在标准的虚通道路由器中,每个虚通道都需要自带缓冲buffer,一个虚通道无法使用其他虚通道的缓冲buffer[14].DAMQ路由器设立了5个缓冲buffer队列,每个队列对应一个虚通道,多出的一个队列作为共享缓冲buffer,一个报文flit从到达到离开路由器需要3个时钟周期[15].VichaR路由器能够根据数据流量(traffic)来调节和分配每个物理通道的虚通道和缓冲buffer数量,并使用复杂的VC控制表来管理报文flit,能够有效提高缓冲buffer的使用效率,其缺点是路由器延迟会达到四个时钟周期.当路由器中发生拥塞时,无论是采用基于信用还是基于开关的流控策略,通道流水线中的缓冲buffer都不能用于缓冲flit.iDEAL路由器提出用中继器(repeater)电路来缓冲flit报文[16],然而中继器存在较大漏流问题,会导致不可靠.本文提出了一种新型的两周期路由器——动态虚通道输出队列路由器(DVOQR),采用多端口缓冲buffer和虚拟输出队列来消除虚通道路由器中的分配站(allocation stage).采用Ready/Valid握手机制来控制路由器之间的flit流,在这种策略下,流水线通道中的存储器可以用于缓冲flit报文.本文其余部分组织如下,第1节介绍了路由器的微架构.第2节给出了路由器的具体设计实现.第3节分析了模拟结果.最后,第4节对本文工作进行了简要总结.1 路由器微架构1.1 DVOQR路由器微架构本文提出了一种新型动态虚通道输出队列路由器(DVOQR),其微架构如图1所示.路由器包括P个输入端口和P个输出端口.对于二维mesh网络,P= 5;一个端口连接到本地处理器(核),其他端口连接到相邻路由器.输入单元由三个主要模块组成:集中动态缓冲器(Unified Dynamic Buffer,UDB)、集中动态缓冲分配器(Unified Dynamic Buffer Allocation,UDBA)、P个虚拟输出地址队列(Virtual Ouput Address Queue,以下简称VOAQ).输出端口包括一个P选1的仲裁器和一个P输入的多路复用器.由多个flit组成1个数据报文,存储在同一FIFO队列中,路由到同一输出端口.每个输入端口有P个FIFO队列,它们共享一个UDB并各自带一个私有的VOAQ.每个FIFO中flit的地址存储在虚拟输出地址队列(VOAQ)中.这样一来,就可以有效消除队列头阻塞(HOL)延迟问题[17].芯片间网络路由器中的缓冲buffer一般使用SRAM来实现.大容量的多端口SRAM存储器由于需要较大的面积开销、较高的功耗和访问延迟而难以实现,而使用小容量的寄存器来实现多端口缓冲器buffer要容易得多.受片上资源的限制,UDB用低延迟的多端口寄存器实现,具有1个写端口和P个读端口.每个读端口对应1个FIFO队列.尽管使用多个端口会导致面积开销增加,但可以消除虚通道路由器流水线的分配站.连接到输出端口的CDB,由CDB控制器和两项142第 8 期李晋文等:一种高吞吐低延迟片上互连网络路由器寄存器组成,如图2(a )所示.其中一个寄存器负责接收来自路由器的flit ,而另一个寄存器负责将flit 发送到下一个路由器,一收一发.在下一个周期中,两个寄存器交换收发功能.因此CDB 可以同时接收和发送flit ,可以避免流水线产生气泡.图2(b )给出了CDB 控制器的实现电路.state [1:0]表征两个寄存器的状态.读指针rd_ptr 对应发送寄存器,写指针wr_ptr 对应接收寄存器.当路由器之间的线延迟超过一个时钟周期时,可以插入多个CDB.UDBA 用于为队列分配时隙或释放空时隙.使用状态向量来跟踪所有时隙的状态,1表示时隙可用.当时隙分配给flit 时,相应的位将被清掉.采用固定优先级仲裁器以简化分配逻辑,最低可用时隙将被分配最高的优先级.设计了四个物理VOAQ 来缓存同一队列中的flit.当某一个flit 注入UDB 时,UDBA 负责将分配给它的时隙号写入对应的VOAQ ,该VOAQ 还会保存该报文的路由信息以及flit 类型.在UDB 读操作之前,需要首先从VOAQ 中读出UDB 中flit 的地址,这将增加UDB 的访问延迟.本文设计了一种新颖的移位FIFO ,可以有效减少UDB 的读延迟.图3给出了VOAQ 的微架构,使用one-hot 向量来指向FIFO 的尾部,而第一项指向FIFO 的头部.尾向量的宽度比UDB 的深度D 要大1.当tail_vector [0]为1时,FIFO 为空;而tail_vector [D ]等于1时,FIFO 为满.当头数图1 DVOQR 路由器微架构Fig.1 Microarchitecture of DVOQR(a )Architecture of channel double buffer(b ) Channel double buffer controller图2 通道的双缓存控制器Fig.2 Channel double buffer controller143湖南大学学报(自然科学版)2023 年据离开队列时,VOAQ 中的其他数据将向前移一位,而tail_vector 将进行右移.当新数据到达时,数据将被添加到VOAQ 的尾部,并且tail_vector 左移1位.当新数据在同一时钟周期内到达和离开时,tail_vector 将不发生移位.DVOQR 中的交换分配单元使用P 个round-robin 仲裁器实现.交换分配单元只需要一级仲裁,即可实现最大匹配,从而提高路由器吞吐量并降低分配延迟.1.2 DVOQR 流水线设计DVOQR 路由器的流水线由两站组成:flit 交换站(Flit Switch ,FS )和链路传输站(Link Traversal ,LT ).FS 站:完成交叉开关分配、前瞻路由计算、UDB读操作和Crossbar 传输.其中交叉开关分配、前瞻路由计算和UDB 读操作能够并行.当VOAQ 的第一项是head flit 报文片时,会为目的仲裁器产生一个请求信号.同时,发送VOAQ 中的flit 地址到UDB ,启动读操作,根据报文的路由信息,采用维序路由算法进行路由的前瞻计算.如果请求未被批准,将在下一个周期中重试,而不需要再次读取flit 报文.LT 站:在这一站中,flit 通过物理链路发送并写入UDB ,并根据FS 站的前瞻路由计算结果,将分配给flit 的地址写入VOAQ 中.1.3 流控机制DVOQR 使用了一种新的流控机制,称为ready-valid 握手机制(handshake ).ready 输出表示UDB/CDB 有可用的存储来接收flit 报文.valid 信号标识当前的flit 报文是有效的.当ready 和valid 信号在同一个周期内有效时,说明flit 报文已经提交.当下一级路由器发生拥塞时,链路上流水线中的CDB 可以缓冲flit 报文,这等效于增加了缓冲buffer 容量.基于维序路由算法,这种流控机制可以有效避免死锁.2 设计实现基于RTL 设计实现了用于片上2D mesh 网络的DVOQR 路由器,数据位宽128位,带有16项UDB ,评估了路由器的性能和功耗,综合生成门级网表,并对时序进行了详细的分析.FS 站和LT 站的关键路径延迟分别为400 ps (11.4 FO4)和252 ps (7.2 FO4),该工艺下的FO4为35 ps.表1给出了路由器中各功能部件的面积和功耗.3 模拟结果3.1 模拟方法本文采用随机人工合成流量模型评估互连网络的性能.表2给出了模拟实验的参数设置.采用周期精确模拟器Booksim [14]来评估虫孔路由器(Worm⁃hole Router ,WH )和虚通道路由器(Virtual-channel Router ,VC ).本文使用Verilog HDL 设计实现了DVOQR 的RTL 模型.测试程序采用随机通讯的合成程序,进行了仿真模拟,预热时间为1万个时钟周期,测量时间为10万个时钟周期.3.2 模拟结果分析3.2.1 不同缓冲容量的影响图4为带16项UDB 的DVOQR 路由器在随机流量负载下的平均延迟曲线.虫孔路由器和虚信道路由器中的输入缓冲buffer 数量为16~64 flit.与其他两种路由器相比,DVOQR 的吞吐量分别增加了33.2%和12%,而其他路由器缓冲buffer 的容量是DVOQR 的3倍.因此,DVOQR 可以更有效地使用输入缓冲器.其中,三种路由器的零负载延迟分别为10.4、14.0和17.7.表1 路由器中各功能部件的面积和功耗Tab.1 Area and power consumption of each functionalcomponent模块UDBVOAQinput portoutput port CDBrouter 组合逻辑面积/(μm )218 9452 49629 7311 5102 236167,385时序逻辑面积/(μm )231 47531 6844 0931133 065221,595总面积/(μm )250 4205 66473 8241 6235 301403,740功耗/mW58.87.589.30.60312.1507.5数量/个5205551图3 VOAQ 的微架构Fig.3 Microarchitecture of virtual ouput address queue144第 8 期李晋文等:一种高吞吐低延迟片上互连网络路由器3.2.2 相同输入加速比UDB 有四个读端口,因此DVOQR 的输入加速比是4.图5给出了在随机流量负载相同输入加速比时的平均延迟曲线.与VC_4×4和VC_4×8相比,VOQ_16的吞吐率分别增加17.6% 和1.9%,而VC_8×8 和VC_8×16的吞吐率分别比VOQ_16要高2.9%和7.5%.DVOQR 吞吐率比双缓冲虚通道路由器要高1.9%.在相同的输入加速比下,采用动态缓冲buffer分配只需要一半的buffer 容量就能达到相同的吞吐率.3.2.3 UDB 深度的影响图6给出了随机流量下DVOQR 网络性能与UDB 深度的相关性.2项UDB 的网络饱和点约为50%,16项UDB 的饱和点可达到82.4%.当UDB 的深度大于8时,吞吐率的增加随着UDB 深度的增加速度放缓.当注入流量小于0.4时,采用不同深度UDB 的平均延迟几乎是相同的.可以根据网络流量打开或关闭一部分UDB ,这样可以有效减少缓冲buffer 的漏流功耗.事实上,缓冲buffer 产生的漏流功耗是整个NoC 路由器漏流功耗的最主要来源.3.2.4 报文长度的影响图7给出了随机流量下带16项UDB 的DVOQR平均延迟与数据报文长度的关系,报文长度为2~32个flit.吞吐率随着报文长度的增加而降低.报文长度为32 flit 和2 flit 网络的饱和点分别为57.5%和87.5%.报文长度进一步增加将导致阻塞,因此需要占用更多的物理通道,而且竞争增加将导致更大的延迟.图7 对应不同报文长度下DVOQR 平均延迟Fig.7 Average latency of DVOQR under differentmessage lengths表2 模拟参数设置Tab.2 Simulation parameter settingsnetwork路由算法报文长度流量注入DVOQR 路由器虫孔路由器(WH )虚通道路由器(VC )4×4 meshdimension-order routing four flitsBernoulli processtwo-stage pipeline ,the depth of UDB is 16 for VOQ_16three-stage pipeline ,the depth of buffer is 16 for WH_16.four-stage pipeline ,the channel number is 4 and the depth of buffer in channel is 8for VC_4×8.图4 不同buffer 容量的DVOQR 路由器平均延迟Fig.4 Average latency of DVOQR with different buffer capacities图5 相同输入加速比下DVOQR 平均延迟Fig.5 Average latency of DVOQR under the sameinput acceleration ratio图6 不同深度UDB 的DVOQR 的平均延迟Fig.6 Average latency of DVOQR with different UDB145湖南大学学报(自然科学版)2023 年4 结论本文提出了一种基于ready-valid握手流控策略的两级流水线片上互连网络路由器,该路由器采用维序路由可以避免死锁.与虫孔路由器和虚通道路由器相比,4×4 mesh网络中的网络吞吐量分别提高了46.9%和28.6%,并且在相同的输入加速比下,DVOQR路由器比双缓冲虚通道路由器性能提高了1.9%.综合结果表明,路由器的时钟频率可达2.5 GHz.参考文献[1]DALLY W J,TOWLES B.Route packets,not wires:on-chip interconnection networks[C]//Proceedings of the 38th DesignAutomation Conference .Las Vegas,NV,USA:IEEE,2005:684-689.[2]VANGAL S,HOWARD J,RUHL G,et al.An 80-tile 1.28TFLOPS network-on-chip in 65nm CMOS[C]//2007 IEEE InternationalSolid-State Circuits Conference. San Francisco,CA,USA:IEEE,2007:98-589.[3]GRATZ P,KIM C,SANKARALINGAM K,et al.On-chip interconnection networks of the TRIPS chip[J].IEEE Micro,2007,27(5):41-50.[4]WENTZLAFF D,GRIFFIN P,HOFFMANN H,et al.On-chip interconnection architecture of the tile processor[J].IEEE Micro,2007,27(5):15-31.[5]JERGER N E,LIPASTI M,PEH L S.Circuit-switched coherence [J].IEEE Computer Architecture Letters,2007,6(1):5-8.[6]PEH L S,DALLY W J.A delay model and speculative architecture for pipelined routers[C]//Proceedings HPCA SeventhInternational Symposium on High-Performance ComputerArchitecture. Monterrey,Mexico:IEEE,2002:255-266.[7]胡哲琨,陈杰.消息传递型片上多核系统的设计[J].湖南大学学报(自然科学版),2013,40(8):102-109.HU Z K,CHEN J.Design of a message-passing multi-core system[J].Journal of Hunan University (Natural Sciences),2013,40(8):102-109.(in Chinese)[8]KUMARY A,KUNDUZ P,SINGHX A P,et al.A 4.6Tbits/s3.6GHz single-cycle NoC router with a novel switch allocator in65nm CMOS[C]//2007 25th International Conference onComputer Design. Lake Tahoe,CA,USA:IEEE,2008:63-70.[9]TIWARI V , KHARE K , SHANDILYA S . An efficient 4×4 mesh structure with a combination of two NoC router architecture[J].International Journal of Sensors,Wireless Communication andControl, 2021,11(2):169-180.[10]CHIOU S Y . Bufferless routing algorithms:a survey[J].Advances in Computational Sciences and Technology,2018,11(5):381-386.[11]李存禄,董德尊,吴际,等.低延迟路由器中高效开关分配机制的实现与评测[J].湖南大学学报(自然科学版),2015,42(4):78-84.LI C L,DONG D Z,WU J,et al.Design and implementation ofefficient switching in low-latency router[J].Journal of HunanUniversity (Natural Sciences),2015,42(4):78-84.(in Chinese)[12]MULLINS R,WEST A,MOORE S.The design and implementation of a low-latency on-chip network[C]//Proceedings of the 2006Asia and South Pacific Design Automation Conference.New York:ACM,2006:164-169.[13]HU J C,MARCULESCU R.Energy- and performance-aware mapping for regular NoC architectures[J].IEEE Transactions onComputer-Aided Design of Integrated Circuits and Systems,2005,24(4):551-562.[14]MULLINS R,WEST A,MOORE S.The design and implementation of a low-latency on-chip network[C]//Proceedings of the 2006Asia and South Pacific Design Automation Conference.New York:ACM,2006:164-169.[15]TAMIR Y,FRAZIER G L.High-performance multiqueue buffers for VLSI communication switches[C]//[1988]The 15th AnnualInternational Symposium on Computer Architecture.Honolulu,HI,USA: IEEE,2002:343-354.[16]KODI A,SARATHY A,LOURI A.Design of adaptive communication channel buffers for low-power area-efficientnetwork-on-chip architecture[C]//Proceedings of the 3rd ACM/IEEE Symposium on Architecture for Networking andCommunications Systems.New York:ACM,2007:47-56.[17]KAROL M,HLUCHYJ M,MORGAN S.Input versus output queueing on a space-division packet switch[J].IEEE Transactionson Communications,1987,35(12):1347-1356.146。

通信信号处理中的概率计算及其应用

概率计算原理小结

概率计算最基本的运算为概率乘法和加法。基于 这种概率加法和乘法,可以衍生出一些基本概率 逻辑,即概率“与”、概率“非”、概率“或” 和概率“异或”; 基于接收符号或序列计算发送符号和序列的概率 运算可以转换成基本的概率运算,即概率乘法、 概率加法和包括概率与、概率非、概率或和概率 异或等概率逻辑; 采用模拟集成电路构建基本的概率运算单元,算 法任务用这些基本计算单元完成; 概率计算适合于低功耗、快速的密集概率运算任 务。

内容提要

概率计算的基本原理

概通 率信 计信 算号 及处 其理 应中 用的

国内外发展情况

基于概率计算的帧同步

基于概率计算的置信传播译码

小结

20

概率计算的研究状况(1)

1970年James N. Cronholm给出了概率门的定义 [James 1970] Probability gates statistics 概率门表示一个固定但可控的转移概率P,P具有数字电路的随时 钟变化特性 由于数字技术的迅猛发展,直到近几年基于概率门的信号处理方 法才又被人们重视起来 1998年~1999年瑞士研究人员在瑞士国家科学基金的支持下完成 了turbo/LDPC码中的BP算法在模拟VLSI上的实现工作 [Hans-Andrea Loeliger] Probability Propagation and Decoding in Analog VLSI (IEEE TRANS. ON I.T., 47(2), FEB. 2001; 会议版本ISIT 1998) [Hans-Andrea Loeliger] Decoding in Analog VLSI (IEEE Communications Magazine , April 1999)

turbo编译码资料

© Copyright 2012–2015 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.IntroductionThe LogiCORE™ IP 3GPP Mixed Mode Turbo Decoder provides a flexible turbo convolutional decode function for both LTE and WCDMA air interfaces. The implementation is compliant with the requirements set out in both [Ref 1] and [Ref 2]. The core provides an optimized turbo decode function for base stations at all form factors, from femto to macrocells. The decoder, when used with a TCC encoder,provides an effective way of transmitting data reliably over noisy data channels.Additional DocumentationA full product guide is available for this core. Access to this material can be requested by clicking on this registration link:/member/mm_tcc_dec_eval/index.htmFeatures•Three versions of this core can be generated, each supporting different standard options:°LTE only °UMTS only °LTE and UMTS•When UMTS and LTE are both supported the core can switch between different standards on a block by block basis.•Each core is completely self contained, requiring nothing else to decode data.•All 3GPP LTE block sizes supported: 188 different block sizes in the range 40–6144•All 3GPP UMTS block sizes supported, that is block sizes in the range 40-5114.See Feature Summary for additional features.LogiCORE IP 3GPP Mixed ModeTurbo Decoder v2.0PB009 (v2.0) November 18, 2015Product BriefLogiCORE IP Facts TableCore SpecificsSupportedDevice Family (1)UltraScale+™ Families UltraScale ™ ArchitectureZynq®-7000 All Programmable SoC7 SeriesSupported User InterfacesAXI4-StreamProvided with CoreDesign Files Encypted RTLExample Design VHDL Test Bench VHDLConstraints File Not ProvidedSimulation Model Encrypted VHDLC Model and MATLAB® ModelSupported S/W DriverN/ATested Design Flows (2)Design Entry Vivado® Design SuiteSimulation For supported simulators, see theXilinx Design Tools: Release Notes Guide .SynthesisVivado SynthesisSupportProvided by Xilinx at the Xilinx Support web pageNotes:1.For a complete listing of supported devices, see the Vivado IPcatalog.2.For the supported versions of the tools, see theXilinx Design Tools: Release Notes Guide .Feature Summary•Configurable with either 1, 2, 4 or 8 decode units, allowing resource utilization to be optimized while meeting system performance requirements at all base station form factors.•Dynamically selectable number of iterations 1-15.•Support for MAX, MAX_SCALE and MAX_STAR algorithms.•AXI4-Stream interfaces used for control and data input/output.• C model and MATLAB MEX function available for bit accurate modelling of error correcting performance.•Number representation: Twos complement fractional.•Data Input: 7 or 8 bits (4 or 5 integer bits with 3 fractional bits)•Hardware DSP units can be used instead of logic resources to tailor the core resource usage to specific user applications.•Demonstration test bench to show an example of core usage.•Integrated scheduler ensures that decode latency remains virtually constant with variable block sizes.OverviewThe TCC decoder is used in conjunction with a TCC encoder to provide an effective way of transmitting data reliably over noisy data channels. The turbo decoder operates very well under low signal-to-noise conditions and provides a performance close to the theoretical optimal performance defined by the Shannon limit [Ref3].References1.3GPP TS 25.212 "Multiplexing and channel coding (FDD)", v10.1.02.3GPP TS 36.212 "Multiplexing and channel coding", v10.3.03. C. Berrou, A. Glavieux, and P. Thitimajshima, Near Shannon Limit Error-correcting Coding andDecoding Turbo Codes, IEEE Proc 1993 Int Conf. Comm., pp1064-1070Technical SupportXilinx provides technical support at the Xilinx Support web page for this LogiCORE™ IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support if you do any of the following:•Implement the solution in devices that are not defined in the documentation.•Customize the solution beyond that allowed in the product documentation.•Change any section of the design labeled DO NOT MODIFY.To contact Xilinx Technical Support, navigate to the Xilinx Support web page. Licensing and Ordering InformationThis Xilinx LogiCORE™ IP module is provided under the terms of the Xilinx Turbo Code LogiCORE IP License Terms.The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.For more information, visit the 3GPP Mixed Mode Turbo Decoder product page.Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.Disclaimer: France Telecom, for itself and certain other parties, claims certain intellectual property rights covering Turbo Codes technology, and has decided to license these rights under a licensing program called the Turbo Codes Licensing Program. Supply of this IP core does not convey a license nor imply any right to use any Turbo Codes patents owned by France Telecom, TDF or GET. Contact France Telecom for information about its Turbo Codes Licensing Program at the following address:France Telecom R&D,VAT/TURBOCODES,38, rue du Général Leclerc,92794 Issy Moulineaux,Cedex 9,France.Evaluation LicenseAn evaluation license is available for this core. The evaluation version of the core operates in the same way as the full version for several hours, depending on clock frequency. Operation is then disabled and the data output does not change. If you notice this behavior in hardware, it means that you are using an evaluation version of the core. The Xilinx tools warn that an evaluation license is being used during netlist implementation. If a full license is installed in order for the core to run on hardware, delete the old configuration file and re-create the core from new.Revision HistoryThe following table shows the revision history for this document:Please Read: Important Legal NoticesThe information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available “AS IS” and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY,NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at /legal.htm#tos ; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at /legal.htm#tos .DateVersionDescription of Revisions11/18/2015 2.0UltraScale+ device support added.04/02/2014 2.0Characterization data added to PG030.12/18/2013 2.0Added UltraScale architecture support.03/20/2013 2.0Updated for Vivado design tools.01/18/20121.0Xilinx initial release.。

NORMA 4000 5000 Power Analyzer 用户说明手册说明书

Since some countries or states do not allow limitation of the term of an implied warranty, or exclusion or limitation of incidental or consequential damages, the limitations and exclusions of this warranty may not apply to every buyer. If any provision of this Warranty is held invalid or unenforceable by a court or other decision-maker of competent jurisdiction, such holding will not affect the validity or enforceability of any other provision.

BEGRENZTE GEWÄHRLEISTUNG UND HAFTUNGSBESCHRÄNKUNG

Fluke gewährleistet, daß jedes Fluke-Produkt unter normalem Gebrauch und Service frei von Material- und Fertigungsdefekten ist. Die Garantiedauer beträgt 2 Jahre ab Versanddatum. Die Garantiedauer für Teile, Produktreparaturen und Service beträgt 90 Tage. Diese Garantie wird ausschließlich dem Erster

Analog Devices视频解码器连接MIPI CSI-2接收器的设计考虑说明书

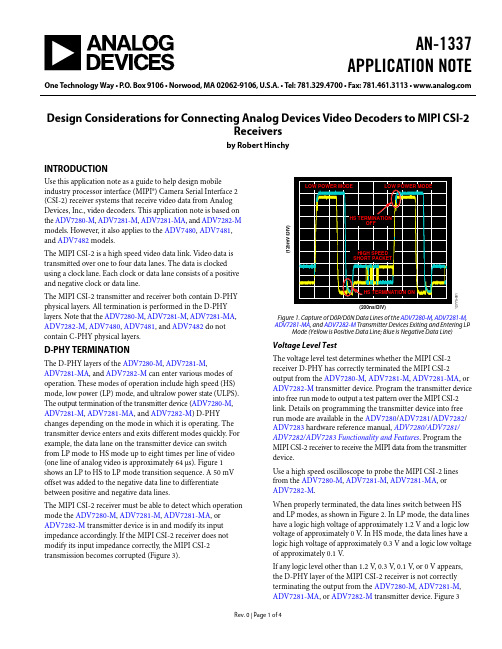

AN-1337APPLICATION NOTE One Technology Way•P.O.Box9106•Norwood,MA02062-9106,U.S.A.•Tel:781.329.4700•Fax:781.461.3113•Design Considerations for Connecting Analog Devices Video Decoders to MIPI CSI-2Receiversby Robert HinchyINTRODUCTIONUse this application note as a guide to help design mobileindustry processor interface (MIPI®) Camera Serial Interface 2(CSI-2) receiver systems that receive video data from AnalogDevices, Inc., video decoders. This application note is based onthe ADV7280-M, ADV7281-M, ADV7281-MA, and ADV7282-Mmodels. However, it also applies to the ADV7480, ADV7481,and ADV7482 models.The MIPI CSI-2 is a high speed video data link. Video data istransmitted over one to four data lanes. The data is clockedusing a clock lane. Each clock or data lane consists of a positiveand negative clock or data line.The MIPI CSI-2 transmitter and receiver both contain D-PHYphysical layers. All termination is performed in the D-PHY layers. Note that the ADV7280-M, ADV7281-M, ADV7281-MA, ADV7282-M, ADV7480, ADV7481, and ADV7482 do not contain C-PHY physical layers.D-PHY TERMINATIONThe D-PHY layers of the ADV7280-M, ADV7281-M,ADV7281-MA, and ADV7282-M can enter various modes of operation. These modes of operation include high speed (HS) mode, low power (LP) mode, and ultralow power state (ULPS). The output termination of the transmitter device (ADV7280-M, ADV7281-M, ADV7281-MA, and ADV7282-M) D-PHY changes depending on the mode in which it is operating. The transmitter device enters and exits different modes quickly. For example, the data lane on the transmitter device can switch from LP mode to HS mode up to eight times per line of video (one line of analog video is approximately 64 μs). Figure 1 shows an LP to HS to LP mode transition sequence. A 50 mV offset was added to the negative data line to differentiate between positive and negative data lines.The MIPI CSI-2 receiver must be able to detect which operation mode the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device is in and modify its input impedance accordingly. If the MIPI CSI-2 receiver does not modify its input impedance correctly, the MIPI CSI-2 transmission becomes corrupted (Figure 3).12775-1(125mV/DIV)Figure 1. Capture of D0P/D0N Data Lines of the ADV7280-M, ADV7281-M, ADV7281-MA, and ADV7282-M Transmitter Devices Exiting and Entering LP Mode (Yellow is Positive Data Line; Blue is Negative Data Line) Voltage Level TestThe voltage level test determines whether the MIPI CSI-2 receiver D-PHY has correctly terminated the MIPI CSI-2 output from the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device. Program the transmitter device into free run mode to output a test pattern over the MIPI CSI-2 link. Details on programming the transmitter device into free run mode are available in the ADV7280/ADV7281/ADV7282/ ADV7283 hardware reference manual, ADV7280/ADV7281/ ADV7282/ADV7283Functionality and Features. Program the MIPI CSI-2 receiver to receive the MIPI data from the transmitter device.Use a high speed oscilloscope to probe the MIPI CSI-2 lines from the ADV7280-M, ADV7281-M, ADV7281-MA, orADV7282-M.When properly terminated, the data lines switch between HS and LP modes, as shown in Figure 2. In LP mode, the data lines have a logic high voltage of approximately 1.2 V and a logic low voltage of approximately 0 V. In HS mode, the data lines have a logic high voltage of approximately 0.3 V and a logic low voltage of approximately 0.1 V.If any logic level other than 1.2 V, 0.3 V, 0.1 V, or 0 V appears, the D-PHY layer of the MIPI CSI-2 receiver is not correctly terminating the output from the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device. Figure 3AN-1337Application Noteshows an example of the MIPI CSI-2 positive data line output from the transmitter device for a poorly terminated receiver. When the transmitter device (ADV7280-M , ADV7281-M ,ADV7281-MA , or ADV7282-M ) is programmed, the MIPI CSI-2 clock lane exits LP mode and enters HS mode. Unless the transmitter device is manually programmed to enter LP mode or is reset, the clock lane remains in HS mode. If any logic level other than 0.3 V or 0.1 V appears on the MIPI CSI-2 clock lines, the D-PHY layer of the MIPI CSI-2 receiver does not correctly terminate the output from the transmitter device.Capture of Positive Data Line in High Speed and Low Power ModesFigure 2 and Figure 3 show the difference between a correct and an incorrect termination of the MIPI CSI-2 signal by the D-PHY layer in the MIPI CSI-2 receiver.12775-002(200m V /D I V )Figure 2. Positive Data Line (D0P) Output from the ADV7280-M , ADV7281-M , ADV7281-MA , and ADV7282-M Transmitter Devices; Correct MIPI CSI-2Receiver Termination12775-003(200m V /D I V )Figure 3. Positive Data Line (D0P) Output from the ADV7280-M , ADV7281-M , ADV7281-MA , and ADV7282-M Transmitter Devices; Incorrect MIPI CSI-2Receiver TerminationD-PHY Mode Detection TestTo test that the MIPI CSI-2 receiver can detect each operation mode, manually program the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M transmitter device to enter HS mode, LP mode, and ULPS. Then, test the MIPI CSI-2 receiverto verify that it can correctly detect the operation mode of the transmitter device.Refer to the ADV7280/ADV7281/ADV7282/ADV7283hardware reference manual, ADV7280/ADV7281/ADV7282/ ADV7283 Functionality and Features , for details on manually programming the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M to enter HS mode, LP mode, and ULPS.Clock Lane Low Power to High Speed Transition Some MIPI CSI-2 receivers wait for an LP to HS modetransition on the MIPI CSI-2 clock lane before starting video capture. However, the LP to HS mode transition on the MIPI CSI-2 clock lane occurs only once on the ADV7280-M , ADV7281-M , ADV7281-MA , and ADV7282-M immediately after they are initially programmed.If the MIPI CSI-2 receiver is initialized after the transmitter device is initialized, the MIPI CSI-2 may never detect the LP to HS mode transition on the clock lane from the transmitter device. If the MIPI CSI-2 receiver does not detect the LP to HS mode transition, it may never start video capture.To overcome this issue, manually program the clock lane of the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M to enter and then exit LP mode. The easiest way to do this is by toggling the CSITX_PWRDN bit (Address 0x00, Bit 7).The MIPI CSI-2 receiver then recognizes an LP to HS mode transition and begins video capture.DESIGN OF MIPI CSI-2 RECEIVER SYSTEMThe following sections provide tips on debugging issues with the MIPI CSI-2 receiver system that is receiving video data from the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M .Lock StatusWhen an analog video source is connected to the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M video decoder, it can take the video decoder a period of time before it locks to the incoming analog video. This period of time can take up to 250 ms in fast switch mode and more than 500 ms in autodetect mode. The ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M outputs spurious data over the MIPI CSI-2 link until the device locks to the incoming analog video. It is recommended that the MIPI CSI-2 receiver system be set to ignore the output from the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M until the ADV7280-M ,ADV7281-M , ADV7281-MA , or ADV7282-M has locked to the analog video.The FSC_LOCK, LOST_LOCK, and IN_LOCK bits (Register 0x10, Bits[2:0]) indicate whether the ADV7280-M , ADV7281-M , ADV7281-MA , or ADV7282-M transmitter device has locked to the analog video source.Use the INTRQ hardware interrupt pin in conjunction with the FSC_LOCK, LOST_LOCK, and IN_LOCK bits to verify when a lock event has occurred. Using the INTRQ hardware interruptApplication Note AN-1337pin saves the MIPI CSI-2 receiver from constantly polling the FSC_LOCK, LOST_LOCK, and IN_LOCK bits.Use the CSITX_PWRDN bit to stop the MIPI CSI-2 output from the ADV7280-M, ADV7281-M, ADV7281-MA, orADV7282-M. Stop the MIPI CSI-2 output until the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M has locked to the analog video source, as indicated by the INTRQ hardware interrupt pin.For more information on the CSITX_PWRDN, FSC_LOCK, LOST_LOCK, and IN_LOCK bits and on the INTRQ hardware interrupt pin, see the ADV7280/ADV7281/ADV7282/ADV7283 hardware reference manual, ADV7280/ADV7281/ ADV7282/ADV7283Functionality and Features. DeinterlacerBy default, the ADV7280-M, ADV7281-M, ADV7281-MA, and ADV7282-M transmitter devices output video data in an interlaced format in the YCbCr 4:2:2 color space. In most applications, the MIPI CSI-2 receiver system requires a deinterlacing function. The most common way of performing this function is by using a frame buffer. For example, an odd field and an even field of video are transmitted into a memory buffer in the MIPI CSI-2 receiver system. The data stored in the memory buffer is then analyzed as a complete progressive frame of video by the MIPI CSI-2 receiver system.Alternatively, the ADV7280-M and ADV7282-M transmitter devices have an integrated deinterlacer. This is referred to as the interlaced to progressive (I2P) core in the ADV7280-M and ADV7282-M data sheets and in the hardware reference manual, ADV7280/ADV7281/ADV7282/ADV7283Functionality andFeatures. Using the I2P cores on the ADV7280-M and the ADV7282-M transmitter devices and programming them to output in progressive mode eliminates the need for deinterlacing in the MIPI CSI-2 receiver system.The I2P core of the ADV7280-M and ADV7282-M interpolates between two lines of video. An algorithm is used to smooth the resulting image to minimize low angle artifacts.Odd and Even Fields of Different LengthsThe ADV7280-M, ADV7281-M, ADV7281-MA, andADV7282-M video decoders output video over the MIPI CSI-2 stream. However, the video timing is based on the ITU-R BT.656-3 or ITU-R BT.656-4 standard.In interlaced mode, an NTSC video source results in theADV7280-M, ADV7281-M, ADV7281-MA, and ADV7282-M transmitter devices outputting video where the odd fields are one line longer than the even fields. This difference occurs with NTSC sources only. PAL sources result in even and odd fields of the same length.When designing video frame buffers in the MIPI CSI-2 receiver system, the even and odd fields can be of different length. However, the ADV7280-M and ADV7282-M models with I2P cores can be programmed to output progressive video. In progressive mode, all fields output by the transmitter devices are the same length.For more information on the video output timing or the I2P core, see the ADV7280/ADV7281/ADV7282/ADV7283 hardware reference manual, ADV7280/ADV7281/ADV7282/ ADV7283Functionality and Features.Video Frame Buffer OverflowsMost MIPI CSI-2 receivers contain a video frame buffer. Each video frame from the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device is stored in a memory buffer before being analyzed by the MIPI CSI-2 receiver.Under certain circumstances (if the analog video source is disconnected, for example), the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device can output video frames with a nonstandard number of lines because the transmitter device is designed to be effective at processing poor video sources.When the CVBS source is not present, the ADV7280-M,ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device continues to output MIPI CSI-2 video data and enters a search mode. When the device is in search mode, any noise on the CVBS input is tested to determine whether it is an analog video signal. When in search mode, the transmitter device outputs frames that are much longer than standard.The ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device remains in search mode for approximately 1 sec in autodetect mode. In fast switch mode, the transmitter device remains in search mode for approximately six fields of video.If a valid analog video source is not detected after the period where the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M is in search mode, the device determines that no video source is present. The device then exits search mode and enters free run mode. In free run mode, the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device outputs test pattern video frames with standard timing. These nonstandard video frames output during search mode can cause a buffer overflow event in the MIPI CSI-2 receiver. One of the best solutions to prevent a buffer overflow is to use a line counter.The line counter is a control loop in the MIPI CSI-2 receiver that counts the number of lines being output per frame by the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device. If the number of lines output per frame exceeds a limit, the MIPI CSI-2 receiver ignores the output from the transmitter device until the next frame start packet. Choose the line number limit so that the video buffer memory of the MIPI CSI-2 receiver does not overflow and so that standard video sources are not attenuated.AN-1337 Application NoteBy default, the MIPI CSI-2 frame start/end packets and the MIPI line start/end packets are output by the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device.Free Run ModeWhen the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device is programmed into free run mode, the device ignores the analog video input and outputs a fixed test pattern. Free run mode can help customers debug issues with their MIPI CSI-2 receiver systems. A number of test patterns are available. For more information, see the ADV7280/ ADV7281/ADV7282/ADV7283 hardware reference manual, ADV7280/ADV7281/ADV7282/ADV7283Functionality and Features.LAYOUT OF MIPI CSI-2 TRACESMIPI CSI-2 is designed as a chip to chip interface; therefore, it does not transmit over long distances. The D-PHY specification defines the maximum lane flight time to 2 ns. Using standard printed circuit board (PCB) materials and design rules (for example, transmitting MIPI CSI-2 through a microstripline on a standard FR4 PCB), results in a maximum trace length of 25 cm to 30 cm. Therefore, keep the MIPI CSI-2 traces from the ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device to the MIPI CSI-2 receiver under 30 cm in length.MIPI CSI-2 line traces must have a characteristic impedance of 50 Ω single-ended and 100 Ω differential.Loosely couple the positive and negative lines of each lane (for example, Data Line 0 positive; Data Line 0 negative) because the positive and negative lines are differential in HS mode but are single-ended in LP mode. As a general rule, space apart the line traces by a distance equal to twice the thickness of the PCB dielectric.Connect MIPI CSI-2 traces from one ADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter device to one MIPI CSI-2 receiver. It is not possible to daisy-chain multipleADV7280-M, ADV7281-M, ADV7281-MA, or ADV7282-M transmitter devices to one MIPI CSI-2 receiver.All filtering and termination is performed in the D-PHY layer of the ADV7280-M, ADV7281-M, ADV7281-MA, andADV7282-M transmitter devices and in the D-PHY layer of the MIPI CSI-2 receiver. Do not place additional components, such as resistors, electrostatic discharge (ESD) diodes, capacitors, or common-mode chokes on the MIPI CSI-2 traces. REFERENCESMIPI® Alliance Specification for D-PHY, Version 1.00.00, Mobile Industry Processor Industry Alliance, 2009.MIPI® Alliance Specification for Camera Serial Interface 2 (CSI-2), Version 1.01.00, Mobile Industry Processor Industry Alliance, 2010.©2014 Analog Devices, Inc. All rights reserved. Trademarks andregistered trademarks are the property of their respective owners.AN12775-0-12/14(0)。

WBOX-516X产品手册说明书

产品手册WBOX-516X,无风扇工业计算机版本:V1.01 / 41认可声明AMI 为Award Software International, Inc. 的商标。

Intel 和Atom 为Intel Corporation 的商标。

IBM、PC/AT、PS/2 和VGA 为International Business Machines Corporation的标。

Intel 和Atom 为Intel Corporation 的商标。

Microsoft Windows 为Microsoft Corp. 的注册商标。

RTL 为Realtek Semiconductor Co., Ltd. 的商标。

所有其它产品名称和商标均为其所有者的财产。

本手册适用于WBOX-516x系列.符合性声明这些限制旨在为商业环境下的系统操作提供合理保护,使其免受有害干扰。

本设备会产生、使用和发射无线电频率能量。

如果没有按照手册说明正确安装和使用,可能对无线电通讯造成有害干扰。

但即使按照手册说明进行安装和使用,也并不能保证不会产生干扰。

若本设备会对无线电或电视信号接收产生有害干扰,用户可通过开、关设备进行确认。

当本设备产生有害干扰时,用户可采取下面的措施来解决干扰问题:●1、调整接收天线的方向或位置●2、增大本设备与接收器之间的距离●3、将本设备的电源接头插在与接收器使用不同电路的电源插座●4、若需技术支持,请咨询经销商或经验丰富的无线电/电视技术人员警告!权利可能会被取消。

包装清单在您打开包装时,请确认包装中附有以下各项:●–WBOX-516x 1pcs附件盒,装有以下各项:●- 电源端子1pcs●- 国标电源线1.8米(可选)1pcs●- 电源适配器(可选)1pcs如果其中任何一项缺失或者破损,请立即联系您的销售商或销售代表。

2 / 41选购信息技术支持与服务用户若需技术支持,请与当地分销商、销售代表客服中心联系。

进行技术咨询前,用户须将下面各项产品信息收集完整:–产品名称及序列号–外围附加设备的描述–用户软件的描述(操作系统、版本、应用软件等)–产品所出现问题的完整描述–每条错误信息的完整内容警告! 1. 输入电压为DC 12-24V电源(电源功率90W或以上)2. 包装:需谨慎,请以双手托住设备。

电子通信领域经典书籍推荐

电子通信领域经典书籍推荐【书名】:光同步数字传输网/viewthread.php?tid=71513&extra=page%3D2【语言】:中文【作者】:韦乐平【推荐理由】:SDH传输的必备资料,凡有志于传输领域的同志应该人手一本【相关信息】:无【书名】:数字通信【语言】:英文、中文【作者】:John G. Proakis【推荐理由】:一本万中选一的书,按信道做分析,虽然公式多,不是通俗易懂,但整体论述严谨,做数字通信必看的【相关信息】:无【书名】:数字通信——基础与应用【语言】:英文、中文【作者】:BERNARD SKLAR【推荐理由】:本书作者工程出身,做过通信的实际项目,讲解理论贴合通信工程师需求,特别是信道编解码部分,引经据典,比较详细【相关信息】:无【书名】:WCDMA技术与系统设计:第三代移动通信系统的无线接入(原书第三版)【语言】:有英文和中文【作者】:(芬)Harri Holma,Antti Toskala【推荐理由】:正在看,看了一半,觉得很好,内容较全,讲解较好,第三版加入了新的内容。

【相关信息】:无Elements of Information Theory(1991,2006)【书名】:Elements of Information Theory(1991,2006)【语言】:English【作者】:THOMAS M. COVER and JOY A. THOMAS【推荐理由】:信息论的经典著作,看了以后你会深入理解信息理论的精髓,看一些外文论文时不会再一头雾水。

第一版1991年,第二版2006年。

multiuser detection(1998)【书名】:multiuser detection(1998)【语言】:English【作者】:Sergio Verdu【推荐理由】:多用户检测的经典著作,大牛Verdu是普利斯顿大学的教授,是多用户检测最重要的开创人。

这本书介绍了CDMA系统里的多用户检测。

PMM L2-16B 人工模拟网络说明书

L2-16BTwo Lines Single Phase V-Network9 kHz - 30 MHz, 16 A for AC and DC powered EUTThe AMN - Artificial Mains Network, also known as LISN - Line Impedance Stabilization Network - is the ancilliary device intended for repeatable and accurate measurement ofthe disturbance voltage that an EUT (Equipment Under T est) may inject into the power line or mains.This is obtained by providing well known impedance value and phase response across the frequency range of the test.PMM L2-16B is suitable for measurement on AC single phase and DC power circuits from DC to 60 Hz. The equivalent V-Network circuit of 50 Ω // (5 Ω + 50 μH) with 250μH choke is fully compliant with the reference standards .PMM Artificial Mains Networks provide robust and stable mechanical construction, high quality electric components, easy and perfect grounding, solid input-output power con-nections. They can be used in conjunction with any EMI receiver or spectrum analyzer and offer features required for safe, repeatable and accurate measurements.Provided Features•Powering the EUT•EUT termination to a standardizedimpedance respect to the reference ground •Coupling of the measuring receiver to the disturbance generated by the EUT•Decoupling of the measuring receiver from unwanted RF signals from the power lineMain Features•9 kHz to 30 MHz frequency range•Up to 16A continuous rated output current •Suitable for DC to 60 Hz power lines•Built-in, selectable 150 kHz high pass filter •Artificial Hand circuit•Local and remote control from PMM EMI receivers•Meets the requirements of several standards including CISPR 16-1-2, VDE 0876, FCC part 15, MIL-STD 461FAdvanced Test Equipment Corp. 800-404-ATEC (2832)L2-16B equivalent circuitL2-16BTwo Lines Single Phase V-Network 9 kHz - 30 MHz, 16 A for AC and DC powered EUTNarda Safety Test Solutions Srl Via Leonardo da Vinci, 21/2320090 Segrate (Milano) - ITALY Phone: +39 02 2699871Fax: +39 02 26998700E-Mail:********************Internet: www.narda-sts.itL 216B -F E N -30400 - S p e c i fi c a t i o n s s u b j e c t t o c h a n g e s w i t h o u t p r i o r n o t i c e•Electrical safety and presence of ground protection relays do require the installation of properly rated insulating transformer(s) between mains power line and AMN line inputs.•High mains noise may require the installation of properly rated mains filters to reduce the level of unwanted signals.9 kHz - 30 MHz 16 A 250 VAC 350 VDC DC - 60 Hz50 Ω // [5 Ω + 50 µH]with 250µH choke BNC female SCHUKO connector -10 °C to +45 °C -25 °C to +75 °C 230 x 105 x 285 mm 5,5 kgSPECIFICATIONSFrequency rangeContinuous rated output current Maximum permissible operating voltage (L/N) L/PE) AC supply frequency range Equivalent circuit RF output Test itemRated temperature Storage temperatureOverall Dimensions mm (W x H x D) WeightReceiversLISNRFI Filters• 7010: EMI receiver 150 kHz -1 GHz • 9010: EMI receiver 10 Hz - 30 MHz • 9010F: EMI receiver 10 Hz - 30 MHz• 9010/03P: EMI receiver 10 Hz - 300 MHz • 9010/30P: EMI receiver 10 Hz - 3 GHz •9010/60P: EMI receiver 10 Hz - 6 GHz• L3-32: 4 lines, 3-phase AMN, 32 A • L3-64: 4 lines, 3-phase AMN, 64 A• L3-64/690 4 lines, 3-phase AMN, 64A/690V • L3-100: 4 lines, 3-phase AMN, 100 A • L3-500: 4 lines, 3-phase AMN, 350 A• L1-150M: single-path, 50 Ohm etc AMN 150 A • L1-500 Single phase AMN, 500A•L2-D: Delta LISN for telecom, 2 A, 150 Ω• FIL-L2-16F: single phase RFI filter, 16 A • FIL-L2-24M: single phase RFI filter, 24 A • FIL-L3-32M: 3-phase+neutral RFI filter, 32 A •FIL-L3-70M: 3-phase+neutral RFI filter, 70 AOrdering Information:L2-16B single phase Artificial Mains Network Includes: power supply cable, RF cable, LISN remote control cable, user’s manual, calibration certificate.Optional accessories:LISN service kit(AC-BNC adapter for LISN verification and calibration)Related Products。

ADI电路笔记 CN-0359说明书

电路笔记CN-0359Circuits from the Lab® reference designs are engineered and tested for quick and easy system integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit /CN0359.连接/参考器件AD825310 MHz、20 V/μs、G = 1、10、100、1000、i CMOS可编程增益仪表放大器ADuCM360集成双通道Σ-Δ型ADC和ARM Cortex-M3的低功耗精密模拟微控制器ADA4627-1 30 V、高速、低噪声、低偏置电流JFET运算放大器AD8542CMOS轨到轨通用放大器ADA4000-1 低成本、精密JFET输入运算放大器ADP2300 1.2 A、20 V、700 kHz/1.4 MHz异步降压型稳压器ADA4638-1 30 V、零漂移、轨到轨输出精密放大器ADP1613 650 kHz/1.3 MHz升压PWM DC-DC开关转换器ADA4528-2 精密、超低噪声、RRIO、双通道、零漂移运算放大器ADG1211低电容、低电荷注入、±15 V/+12 V iCMOS四通道单刀单掷开关ADA4077-2 4 MHz、7 nV/√Hz、低失调和漂移、高精度放大器ADG1419 2.1 Ω导通电阻、±15 V/+12 V/±5 V、iCMOS单刀双掷开关AD8592 CMOS、单电源、轨到轨输入/输出运算放大器,具有关断功能ADM3483 3.3 V限摆率、半双工、RS-485/RS-422收发器全自动高性能电导率测量系统Rev. 0Circuits from the Lab® reference designs from Analog Devices have been designed and built by AnalogDevices engineers. Standard engineering practices have been employed in the design andconstruction of each circuit, and their function and performance have been tested and veri ed in a labenvironment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2015 Analog Devices, Inc. All rights reserved.评估和设计支持电路评估板CN-0359电路评估板(EVAL-CN0359-EB1Z)设计和集成文件原理图、源代码、布局文件、物料清单电路功能与优势图1中的电路是一个完全独立自足、微处理器控制的高精度电导率测量系统,适用于测量液体的离子含量、水质分析、工业质量控制以及化学分析。

微微创新AG-加利欧功能概述 M000204-08说明书

Description M000204-08 Galileo Function OverviewMicro Innovation AGSpinnereistrasse 8-14CH-9008 St.GallenTel. +41 71 243 24 24Fax +41 71 243 24 90Table of contents1General (5)1.1System Requirements (5)1.2MICRO PANEL GF-x / XV (5)2Possibilities and Limits (6)2.1Project (6)2.2Mask (7)2.3Printing Functions (7)2.4Windows CE (7)3Project Handling (8)3.1Project Handling (8)3.2Project Documentation (8)3.3Project Settings (8)3.4Project Conversion (8)4Mask Handling (9)4.1Mask Handling (9)4.2Sub Mask (9)4.3Mask Documentation (9)4.4Mask Settings (9)4.5Object Handling (10)5Static Objects (11)5.1Drawing Objects (11)5.2Background and Images (11)5.3Dynamic Properties (11)5.4General Functions of Static Objects (11)6Dynamic Objects (12)6.1Basic Objects (12)6.2Graphical Presentation of Objects (12)6.3Keyboards (13)6.4Function Objects (13)6.5Special Function Objects (13)6.6Dynamic Properties (14)6.7General Functions of Dynamic Objects (14)7Script (15)7.1Loop-Script (15)7.2Event-Script (15)8PLC, panel type selection and data definition (16)8.1PLC Selection (16)8.2Definition of Tags (16)8.3Assign Tags (16)8.4Handling (16)8.5MICRO Panel Configuration (17)8.6Text Editing (17)8.7Further Settings and Handling (17)9Testing and Operating (18)9.1Simulation of Objects (18)9.2Optimizing (18)9.3Compiling (18)9.4Download and Upload (18)9.5Online Testing and Operating from PC (18)10PLC Protocols (19)10.1M PB-TP (19)10.2M PB1-TP / MPB2-TP (20)10.3P DP-TP (20)10.4E IB-TP (20)10.5I BS-TP (20)10.6B CB-TP (21)10.7P anel System Port (without a communication card) (21)10.8E thernet (depending on the panel type) (21)Proper useHardware, software, operating systems and drivers must only be used for the applica-tions specified in this description and only in conjunction with the components recom-mended by Micro Innovation AG.Warning!No warranty claims will be recognized for faults arising from the improper handling of any device.Devices and communication should not be used for the implementation of any safety functions relating to the protection of personnel and machinery.No liability is accepted for claims for damages arising from a failure or functional defect. All data specified in this document do not represent guaranteed specifications in the legal sense.Legend* The file size of recipe management depends on the number of data records, the number of variables and used variable types. Within Galileo the exact file size is displayed.Note: The specification of the 'Maximum Data' relate to the limiting values which are managed by the software. The number of available amounts used in the different panels depends on the free memory (depending upon type of device of the internal flash memory or of the PCMCIA card).M000204-08.doc / PD 21 / 21 19.04.2010。

跳频滤波器上电控制时序的研究与设计

现代电子技术Modern Electronics TechniqueAug.2023Vol.46No.162023年8月15日第46卷第16期0引言无线电通信技术发展快速,在航空航天等多个领域发挥着不可替代的作用。

在军用无线电通信中,因为通话和数据传输需要具备保密和抗干扰能力,故跳频技术成为军用通信系统设计最常采用的有效手段之一。

其中跳频滤波器是跳频技术的典型元器件应用,正确的地址码对应相匹配的输出频率是跳频滤波器正常工作的关键指标之一。

本文从跳频滤波器供电和地址码两者控制时序对输出频率影响方面进行了分析和研究,发现正确的上电时序是跳频滤波器频率正常输出极易被忽略的设计要素,并基于此提出了同类别跳频滤波器上电控制时序的设计思路,解决了跳频滤波器因上电控制时序设计差错而导致无法正常工作的潜在隐患。

1跳频滤波器工作原理跳频滤波器要实现滤波器中心频率的快速变换,核心是通过连续快速改变或用开关改变带通滤波器的全部或部分地址码参数。

因通信中使用的频率随地址码状态变换而产生不同的输出频率,故本文采用数字调谐式方案进行跳频滤波器的设计,其主要由数字控制部分和模拟部分组成,作用包括以下两点:1)数字控制部分作用:输入控制信号的逻辑转换,将外部输入的调谐频率控制码转换为可以驱动射频电DOI :10.16652/j.issn.1004⁃373x.2023.16.010引用格式:陈新.跳频滤波器上电控制时序的研究与设计[J].现代电子技术,2023,46(16):61⁃64.跳频滤波器上电控制时序的研究与设计陈新(中国电子科技集团公司第十研究所,四川成都610036)摘要:电磁信号日益密集、复杂,对通信对抗设备的反干扰能力要求越来越高,而跳频技术作为新一代通信对抗技术被广泛应用,在现代电子战中显现出巨大的优越性。

文中分析一种跳频滤波器上电控制时序对其频率输出的影响,通过对上电和频率地址码达到稳态状态的时间差异进行ADS 仿真分析,并结合实物信号测试,指出跳频滤波器存储器处于不稳定状态时,发送指定频点地址码指令,数据口输出状态会出错,从而导致输出频率异常。

创新声卡KX驱动插件中英文对照表

创新声卡KX驱动插件中英文对照表硬件设备菜单1 FXBus 路由器2 FXBus2 路由器3 FXBus32 路由器4 epiloglt_k1终解程序5 epiloglt_k2终解程序6 p16v 2496解码器7 prolog 初构程序8 prologlt9 xrouting基本处理器菜单1 FXMix 多路路由器2 FXMix2 多路路由器3 Mono Mix 单声混合器4 Pan 声道控制5 Pan x2 声道控制6 Peak 相位7 Phase8 St Vol 音量控制9 Stereo Mix 立体声混音器10 Stereo Mix +Gain 立体声加强混音器11 Summ 萨姆12 Vol 音量13 Vol+DC 麦克增益14 crossfade 淡出器15 div416 gain 放大器17 gainHQ 音量控制18 x4x4 放大4倍19 xSumm_x萨姆20 xor 异或E-MU APS菜单(电子亩接入点)1 APS AutoWah 自动哇音2 APS Compressor 压限器3 APS Compressor+ 压限增益4 APS Everb5 APS Expander 扩展器(扩张器、膨胀器)6 APS Expander+ 扩展增益7 APS Flanger 凸缘器(镶边)8 APS Fuzz 微噪音9 APS Pitch 音调器(变声插件)Creative LiveWare菜单(创新器件)1 CL Reverb 混音器2 CLEAX3Reverb3 CLEAX4Reverb环绕声处理器菜单1 3D Sound Gen 3D环绕2 HPhSp 重低音3 Pos3DFX 3D环绕路由4 Prologica 音效连接器5 Surrounder+ 环绕混音加强6 cnv51to207 downmix 低音混合8 encode4 解码器9 surrounderlt 环绕混音均衡器和滤波器菜单1 EQ Bandpass 滤波转换器(均衡带通)2 EQ G10 图示均衡器(十段均衡器)3 EQ Highpass 低切(高通)4 EQ Highshelf 高架5 EQ Lowpass 高切(低通)6 EQ Lowshelf 低架7 EQ Notch 断口器8 EQ P1 波段器(小一均衡器)9 EQ P1 (Mono) 单声道波段器(单声道小一均衡器)10 EQ P5 五段均衡器11 EQ P5 (Mono) 单声道五段12 EQ peaking 波段调峰13 Freq Splitter 频率分离器14 phat EQ Mono 单声均衡15 Phat EQ Stereo 混合均衡(单声道立体声)16 Timbre 音色调节直通菜单1 ac3passthrough 交流穿透器2 b2b 优质ProFX菜单1 proFx:ADC 麦克风输入插件2 proFx:ASIO 低延时器(音频流输入输出接口)3 proFx:MX6 六路调音台4 proFx:Src 系统音源输入插件5 proFx:kXLt 总音频输出插件旧版本插件菜单1 16to322 Delay Old3 Dynamics Processor 动态压缩器4 FXBusX 路由器5 Overdrive6 Overdrive27 RingMod8 Wave Generator9 Wave Generator 2.010 ac3passthru_old11 ac3passthru_x12 b2b_old13 xrouting_old 调音台EF-X菜单(英法X的)1 EFX Oscilloscope 示波器2 EFX ReverbStation 混响器3 EFX TubeDrive 吉他效果器2nd order crossover 第二路交叉4nd order crossover 第四路交叉Booble Gum 气泡Chorus 和声(合唱)Crossover-2 二路交叉Crossover-4 四路交叉Delay A 延迟Delay B 延迟Dynamics Processor 动态效果器(闪避效果器) FxRouter 外汇路由器GainX 放大器HarmonicsGen 谐频Info 域名(信息)Loudness Comensator 响度补偿Mixy 4x2 四路混合台Mixy 8x2 八路混合台Mono Vocoder 单声码器Noise Gate 2T 噪声门Noise Gate 2Ts 噪声门PeakX 限制器Phaser 相位器ProFx:MX8 八路调音台ProFx:NoiseGate 噪音门ProFx:NoiseGateST 噪音门ProFxeak4 四路限制器ProFx:Peak6 六路限制器ProFx:Peak8 八路限制器Reverb Lite 精简效果器Reverb R 效果器Stereo Chorus 混合和声器Stereo Decimator 混响抽取器(立体声降频)Streo Vocoder 单声道混合器Surrounder 镶边TheDelay 替换延迟TheSmallDelay 小延迟TimeBalanceV2 时间平衡TubeSound 声音传导Wave Generator 3.0 波形震荡器epilogepilog_oldprolog_oldroutingvibrato 颤音roPhaser 相位器putnik 普特呢克真人发音器ibrato 震动器remolo 颤音调和器。

通信领域经典书籍推荐

电子通信领域经典书籍推荐评论:上面的东西是往其它地方转载的,主要侧重在通信,做点自己的补充数字通信总体的书籍首推Prokais的书,讲得比较全,也不算很深,入门不错,但本科生看起来还是有些难度,因为随机过程不一定理解得有多好,学过的话就好办多了。

其次可以看Gallager的新书,大牛对通信的看法很特别,看完以后通信的基本框架就掌握了,也不一定要看得很深入,如果时间不允许的话。

通信系统,网络方面的书没有专门看过,最好结合电信网和计算机网一起来看,在两者的比较之中可以对网络认识更清楚一些,毕竟电信的人和计算机的人思维方式,处理问题的方法都很不相同,两者也会互相借鉴一些方法。

计算机界的人冲到通信界来抢饭碗就是一个证明,不说引起矛盾的话了,电信网和因特网的书以及各种参考资料实在太多,对理解通信系统来说,Simon.Haykin的Communication.Systems不错,这些年网络很火,通信网包括的东西很多,传输技术,交换技术,复用技术等纷繁复杂。

各层协议一个接一个的提。

有的协议虽然不难,但很烦,看起来都头大(比如ATM ?),要理解的话,还是从分层结构结合实际网络来,这方面绝对不能停留在理论上,搞排队论之类的也是这样,实际情况很重要。

信源编码的书不多,看过David Salomon的<数据压缩>,07年的新书,写得不错,国内东南吴乐南也有一本,不过比较小,具体涉及到语音和图像视频编码可以参考专门的书籍,需要语音和图像处理的基础。

语音方面推荐语音信号数字处理那本书,谁写的忘记了,图像处理就参考Gonzalez冈萨雷斯的书吧,也是经典。

信道编码的书不少,Lin Shu(林舒)的最为推荐,第二版,大而全而新,王新梅的做代数码的可以参考,概率解码的就算了,还有一些据说也是好书,但没看过,弄好一本已足够。

如果要具体到编解码算法的时候,T odd K. Moon的书Error.Correction.Coding.Mathematical.Methods.and.Algorithms不错,比较具体。

南星S9接收机【OPENBOX,KD,PVR,3612(S9),接收机的录像功能与DIY】

南星S9接收机OPENBOX,KD,PVR,3612(S9),接收机的录像功能与DIY】如今讲到OPENBOX KD PVR 3612接收机,大家并不生疏了,该机如今已改名为OPENBOX KD PVR s9接收机,软件也在不断更新,如今接受了的F1旗舰版本的软件,比老版本改良很多,例如解决了硬盘NTFS与FT32格式化两种可选,可任意删除录像存贮的某个节目的文件夹,可写入9个CCCm等;本刊在20XX年第19期中,笔者介绍了该机的常规技术性能与使用方法,时隔3月,在实际使用中对该机的有用性与廉价的性价比还是情有独钟,该机工作稳定,功能有用,接口齐全,打开面板小门,可看到有2个卡槽,下面个为模块,上面一个为智能卡,也就是讲该机支持多种加密方式的收看,只需配上相对应的模块与智能卡,参见图。

尤其是该机的录,放像功能与节目编辑功能,设计特别到位,在卫星设置方面支持16切1,这在接收机中也不多见,切换速度也很快,接收门限较低,再认真看看其生产工艺与用料,在低价位的接收机中,该机的用料还是不错的,如最易发生故障的电源板中,选用了优质的电解电容,沟通整流滤波电解电容选用了33uf450V,通常为22uf400V,几路直流输出滤波电解电容选用了金字电解电容,开关变压器质量也很好,电源板设计功率余量较大,这给提供移动硬盘用作电源制造了条件,主板上元器性的焊接工艺糈良,在发热较高的CPU及13/18V电源稳压集成块317上均加装了散热片,加上机壳合理的散热孔使机内温升不大;与主板连接的每个插件均打有翔胶,且很牢固,从而保证了运输中的防震与紧偶合,如需拔下插头跗,应先用刀将封胶割除才能拔下;该机机壳与面板均贴有爱护膜,将面板上爱护膜撕去,可看到其面板是单独贴上去的,面板经过镀膜处理,光滑度特别高,如镜面般可照出人影,参见图二。

该机录像功能还是很强的,该机除了可预设八个不同时段的节目定时录像外,可以对己录像保存的节目进行加锁与删除,也可以对己录像保存的节目进行重命名,目前该机只支持用英文命名,使用遥控器上的数字键就可轻松完成,也可退格等;该机也支持用“U〞盘或移动硬盘来播放音乐与图片,还可设定图片用幻灯片模式播放,可设定图片间隔时间,可选择设定从1秒到9秒与关闭,还可设定图片大小,可选择“全屏〞或者“原始〞。

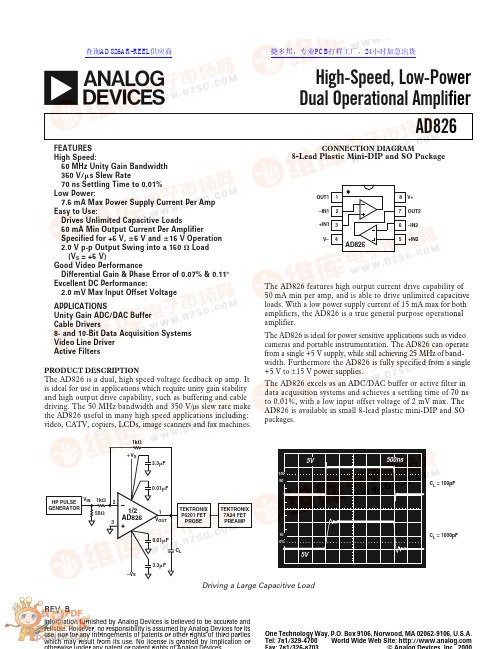

高精度、高驱动电流、双运算放大器AD826说明书