实验三 层次电路原理图与多层电路板的设计

层次电路原理图的绘制和PCB设计流程

层次电路原理图的绘制和PCB设计流程摘要:Protel99SE软件因其功能强大、界面友好、简单易学使其成为一款使用非常普遍的电路绘图软件,在很多高校的《电气识图及CAD》和《医用电子线路设计与制作》等课程中使用,因为与后续的版本完全兼容,所以学习之后再升级为高版本的软件,不存在障碍,过渡到其他版本也很容易,且该版本软件占用内存小,运行快也稳定性非常好,所以深受师生的广泛爱戴,同时因为拥有的用户多,所以网上的相关学习资源也丰富,自学起来也是非常容易的。

关键词:原理图绘制;PCB板;设计脉搏计是一款用来自动测量在某个单位时间点内任何一个人心脏平均跳动的次数多少的中小型医用智能电子仪器。

技术参数用来直接测量脉动频率的较电压低很多的一个小的信号(传感器输出电压一般为几个毫安),它具有的一种基本工作功能主要是通过用传感器直接将有关脉搏的跳动变化的一种电生理信号直接转换输出为一种电压信号,因为这些信号一般非常较弱,所以一定要再加以滤波放大后并能进行二次整形运算和滤波,再进行计数,最后通过数码管显示出来。

接下来我们就以"数显脉搏计"为例讲解层次电路图的绘制和PCB的设计流程。

如果一张电路图比较简单,我们可以直接用单张原理图进行绘制就可以,但是如果电路结构比较复杂,并且可以根据原理和功能分为几块电路图,我们就可以选用层次电路图来绘制原理图。

数显式脉搏计电路由脉冲信号采集子电路、时基子电路、计数子电路组成,我们就可以将每个子电路绘制在一张电路图纸上,然后建立一张总的块状电路图将几张子电路图联系在一起,从而实现整张电路图纸的功能,同时也可以实现PCB板的自动生成。

一、层次原理图设计首先新建项目设计数据库,命名为“数显脉搏计”并且在数据库中的Documents文件夹下新建电路图、封装库、PCB板等文件。

1.新建原理图设计文件,命名为:“数显脉搏计.Sch”(1)在原理图编辑页面,点击连线工具栏最右侧出现的一个数字"方块图图标"按钮后,放置一个尺寸大小都比较合适的方块,代表是一个脉冲信号采集子电路,双击此方块图后即可直接弹出一个属性对话框,在其中的Filename栏框内和Name栏框内就可以直接分别点击填入带有其相应的属性信息的文件名称,其中NAme代表了这个方块图文件的一个原始文件名字,没有其它别的一些特殊的格式要求,将Name修改为PulseSignal Collection,而Filename通常是这个方块图代表的原理图文件,后缀名通常为.sch,将方块图对应的电路原理图文件名修改为Pulse Signal Collection.Sch,为了防止两个名字书写过程中出现错误和书写麻烦可以使用复制粘贴命令;用同样的方法可以放置代表时基子电路的方块图,将Filename 和Name 框中分别填入相应的名称Reference Time.Sch和Reference Time;再用同样的方法放置代表计数子电路的方块图;将方块图属性对话官中的Filename 和Name 框中分别填入相应的名称Counter.Sch和Counter。

电路板设计与制作第7-8讲 有源功率放大器层次电路图设计及实训

11

四、设置图纸信息

主图和子图绘制完毕,一般要添加图纸信息,设置 好原理图的编号和原理图总数。下面以设置主图的图纸 信息为例进行说明,主图原理图编号为1,项目原理图总 数为6。

标题栏位于工作区的右下角,主图标题栏信息如图 2-84所示。

12

图2-84所示标题栏中设置的主 要参数有:Title(标题)、 SheetNumber(原理图编号)、 SheetTotal(原理图总数)及DrawnBy (绘图者)。

(1)放置标题栏参数字符串 执行菜单“放置”→“文本字符 串”,光标上粘着一个字符串,按键 盘上的<Tab>键,屏幕弹出字符串属性 对话框,如图2-85所示,单击“文本” 后的下拉列表框,在其中选择所需的 参数,移动到指定位置后单击鼠标左 键放置参数字符串。

3

二、功放层次电路主图设计

下面以图2-78所示的单片机主图为例,介绍层次 电路主图设计。

4

设计前建立“有源功放”项目文件,创建“有源功放” 主图原理图文件并保存。

1.电路方块图设计 电路方块图,也称为子图符号(图纸符号),它对 应着一个具体的内层电路,即子图。图2-78所示的有源 功放主图文件,它是由5个电路方块图组成。

13

本例中在Title后设置参数“=Title”,在Sheet后 设 置 参 数 “ =SheetNumber” , 在 of 后 设 置 参 数 “ =SheetTotal” , 在 Drawn By 后 设 置 参 数 “=DrawnBy”,如图2-86所示。图中由于SheetNumber 和SheetTotal参数字符较长,出现重叠,但不影响功能。 图中的Data和Files是由系统根据当前情况自动定义的。

电路原理第3章层次电路图的设计

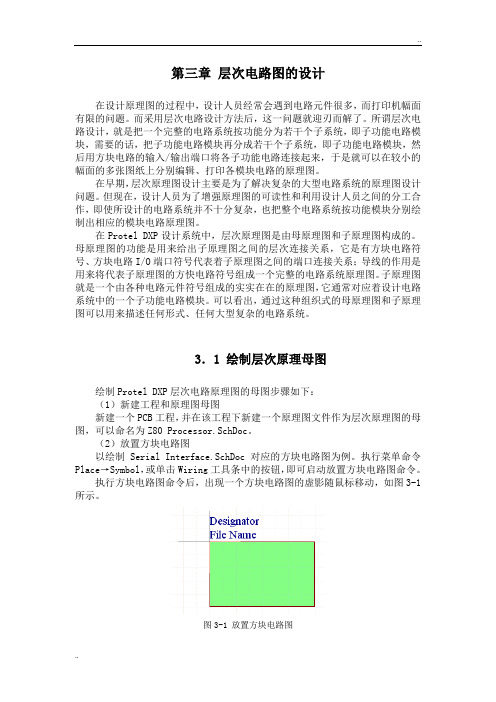

第三章层次电路图的设计在设计原理图的过程中,设计人员经常会遇到电路元件很多,而打印机幅面有限的问题。

而采用层次电路设计方法后,这一问题就迎刃而解了。

所谓层次电路设计,就是把一个完整的电路系统按功能分为若干个子系统,即子功能电路模块,需要的话,把子功能电路模块再分成若干个子系统,即子功能电路模块,然后用方块电路的输入/输出端口将各子功能电路连接起来,于是就可以在较小的幅面的多张图纸上分别编辑、打印各模块电路的原理图。

在早期,层次原理图设计主要是为了解决复杂的大型电路系统的原理图设计问题。

但现在,设计人员为了增强原理图的可读性和利用设计人员之间的分工合作,即使所设计的电路系统并不十分复杂,也把整个电路系统按功能模块分别绘制出相应的模块电路原理图。

在Protel DXP设计系统中,层次原理图是由母原理图和子原理图构成的。

母原理图的功能是用来给出子原理图之间的层次连接关系,它是有方块电路符号、方块电路I/O端口符号代表着子原理图之间的端口连接关系;导线的作用是用来将代表子原理图的方快电路符号组成一个完整的电路系统原理图。

子原理图就是一个由各种电路元件符号组成的实实在在的原理图,它通常对应着设计电路系统中的一个子功能电路模块。

可以看出,通过这种组织式的母原理图和子原理图可以用来描述任何形式、任何大型复杂的电路系统。

3.1 绘制层次原理母图绘制Protel DXP层次电路原理图的母图步骤如下:(1)新建工程和原理图母图新建一个PCB工程,并在该工程下新建一个原理图文件作为层次原理图的母图,可以命名为Z80 Processor.SchDoc。

(2)放置方块电路图以绘制Serial Interface.SchDoc对应的方块电路图为例。

执行菜单命令Place→Symbol,或单击Wiring工具条中的按钮,即可启动放置方块电路图命令。

执行方块电路图命令后,出现一个方块电路图的虚影随鼠标移动,如图3-1所示。

图3-1 放置方块电路图此时,按[Tab]键,即可进入方块电路图属性设置,如图3-2所示。

层次电路原理图设计

2. 绘制方块电路

移动光标到合 适位置单击鼠 标左键,作为 方块电路的左 上角端点,此 时移动光标, 可带出方块电 路,当方块电 路大小合适时 再次单击鼠标 左键完成方块 电路FK1的绘

层次电路原理图设计

3. 绘制其它方块电路

层次电路原理图设计

5.2.3 放置方块电路端口

方块电路绘制完成后,为了建立方 块电路之间的电气连接,必须为方 块电路添加方块电路端口,下面以 放置显示模块方块电路中的端口 “P1[0..7]”为例讲解具体放置方法。

方块电路端口

层次电路原理图设计

2. 方块电路端口

为了表示各子原理图之间的电气连 接关系,各方块电路之间需要有相 互连接的电气端口,即方块电路端 口,如上页图所示,通过方块电路 端口,可以清楚的表达和实现各子 原理图之间的电气连接关系。

层次电路原理图设计

3. 方块电路之间的连接

方块电路代表的是子原理图,各子 原理图必须根据系统的要求相互连 接,才能构成实用的电路系统。为 了实现子原理图之间的电气连接, 用户只需将方块电路端口通过导线 或总线连接起来即可。如下页图所 示。

层次电路原理图设计

方块电路属性

按键盘上的【Tap】键,弹出如图所 示的方块电路属性对话框。

层次电路原理图设计

方块电路属性

方块电路属性对话框中主要的属性有: 【Designator】:方块电路序号,和元件序 号作用相同,不能重复。 【】:文件名,即方块电路代表的子原理 图文件名称,最好不要采用中文命名。 因为此处绘制显示模块的方块电路,而 且是第一个方块电路,所以在 【Designator】栏输入“FK1”,表示第一 个方块电路,在【】输入 “display.SchDoc”,表示显示模块。

实验三 层次化设计电路

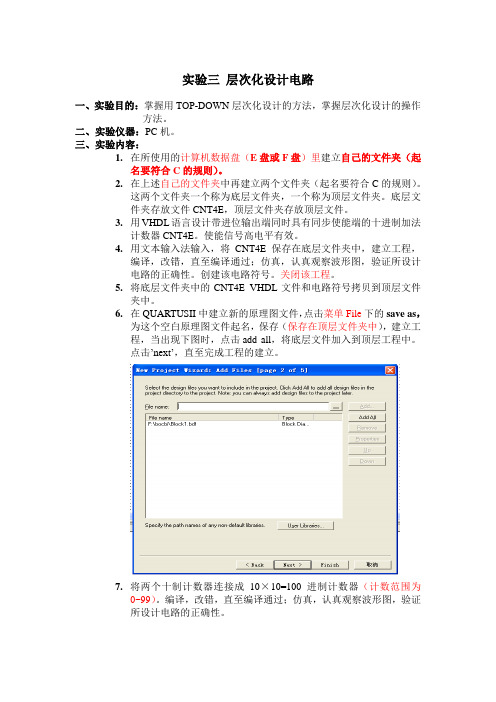

实验三层次化设计电路

一、实验目的:掌握用TOP-DOWN层次化设计的方法,掌握层次化设计的操作

方法。

二、实验仪器:PC机。

三、实验内容:

1.在所使用的计算机数据盘(E盘或F盘)里建立自己的文件夹(起

名要符合C的规则)。

2.在上述自己的文件夹中再建立两个文件夹(起名要符合C的规则)。

这两个文件夹一个称为底层文件夹,一个称为顶层文件夹。

底层文

件夹存放文件CNT4E,顶层文件夹存放顶层文件。

3.用VHDL语言设计带进位输出端同时具有同步使能端的十进制加法

计数器CNT4E。

使能信号高电平有效。

4.用文本输入法输入,将CNT4E保存在底层文件夹中,建立工程,

编译,改错,直至编译通过;仿真,认真观察波形图,验证所设计

电路的正确性。

创建该电路符号。

关闭该工程。

5.将底层文件夹中的CNT4E VHDL文件和电路符号拷贝到顶层文件

夹中。

6.在QUARTUSII中建立新的原理图文件,点击菜单File下的save as,

为这个空白原理图文件起名,保存(保存在顶层文件夹中),建立工

程,当出现下图时,点击add all,将底层文件加入到顶层工程中。

点击’next’,直至完成工程的建立。

7.将两个十制计数器连接成10×10=100进制计数器(计数范围为

0~99)。

编译,改错,直至编译通过;仿真,认真观察波形图,验证

所设计电路的正确性。

写出正确的操作方法,并简要说明实验中遇到的问题及解决方法。

层次原理图实验报告

实验报告数字学院(院、系)数码嵌入专业3-4班Protel99se 电路设计课学号姓名:实验日期:2012.10.3 教师评定一、实验名称:层次原理图设计二、实验目的:1.掌握层次原理图的建立方法2.掌握由方块电路符号产生新原理图的方法3.掌握电气规则检查和网络报表的生成三、实验内容:层次化原理图设计的流程四、实验步骤:步骤1:绘制总原理图(1)执行菜单命令“File”→“New”数据库命名为我的文件(2)对电路进行合理的功能分块,并画出层次原理图总图1、在文件对话框中,右击“New”,从框中选择原理设计服务图标。

2、双击图标或单击【OK】按钮,就会建立原理图设计文档3、双击原理图文档图标,进入原理图设计服务器的界面。

4、执行菜单命令“放置”→“图纸符号”。

5、执行完该命令后,光标变为十字形状,并带着方块电路,在此命令下,按下<Tab>键,在对话框中,将文件名选项设置为l.sch,将名称选项设置为Sheet 1。

6、将光标移动到适当的位置后,单击鼠标左键,确定方块电路的左上角位置。

然后拖动鼠标,移动到适当的位置后,单击鼠标左键,确定方块电路的右下角。

这样就定义了方块电路的大小和位置,绘制出了一个名为Sheet l的模块。

7、用步骤(5)(6)的方法,也绘制一个名为2.sch 的模块。

8、执行菜单命令“放置”→“放置图纸符号”。

9、在(8)的命令下,光标变为十字形状,并带着方块电路的端口符号,在此命令下,按下<Tab>键,在对话框中,将名称选项设置为1,I/O类型选项设置为输出,边和样式选项设置为向右。

将光标移动到模块边界后,单击鼠标左键,将其定位;同样,根据实际电路,在Sheet l模块上放置一个 1. 2的端口。

10、重复(9)的操作,设置模块的端口备注:也可以先绘制原理子图添加符号后,在“设计”中,“由符号生成图纸”出现十字光标点击将会生成模块步骤2:绘制子原理图1 利用由方块电路符号产生新原理图的方法,画出个功能模块的详细电路原理图。

实验三 protel DXP中绘制层次电路原理图

实验三绘制层次电路原理图一、实验目的1.熟练掌握ProtelDXP的操作。

2.掌握层次电路原理图的绘制方法,能够绘制较复杂的层次电路。

3.进一步熟悉ERC校验和网络表的生成。

二、实验内容1.新建电路原理图,图纸大小设置为A4,参照图5所示,完成层次电路原理图主图的绘制。

图中,VSIN选用仿真库(Simulation Sources.IntLib)中的VSIN元件;各子图符号I/O端口中,子图Modulator中的端口Vcarrier和Vsingal为输入,Vmod为输出,子图Amplifier中的端口Vmod为输入,OUT为输出。

将电路原理图以文件名“AMPMOD.prj’’存盘。

图5 主图“AMPMOD.prj”执行菜单Design—Document Options—Parameters填写图样信息,在Sheet Number栏中设置图纸编号(NO)为1;在Sheet Total栏中设置图纸总数(Total)为3。

2.执行菜单命令Design—Create Sheet From Symbol,将光标移到子图符号Modulator 上,单击鼠标左键,在产生的新电路原理图上按照图6绘制第一张子图,设置图样编号为2,并保存该电路。

3·采用同样的方法,分别参照图7绘制第二张子图,设置图样编号为3。

图6 子图modulator.sch 图7 子图amplifier.sch4.对整个层次电路原理图进行ERC校验(执行菜单:Project—Compile PCB Project1.PrjPCB),若有错误,加以修改。

5.生成此层次电路的网络表,检查网络表各项内容,是否与原理图相符合。

三、思考题1.简述设计层次电路原理图的步骤。

2.设计层次电路原理图时应注意哪些问题?3.画出下图的洗衣机控制电路的层次电路图顶层图CPU电路晶震、复位电路控制电路1K显示电路。

电子电路CAD 实验三 层次电路图的设计

实验三、层次电路图的设计课程名称:电子电路CAD专业班级:电子1412___学生学号: 14200106214 学生姓名:孙玮_____所属院部:电子与信息工程学院指导教师:顾敏明__ _2015 —— 2016 学年第 2 学期实验三层次电路图的设计一、实验目的1、掌握层次图的绘制方法和技巧。

层次式设计的方式2、加深原理图的理解。

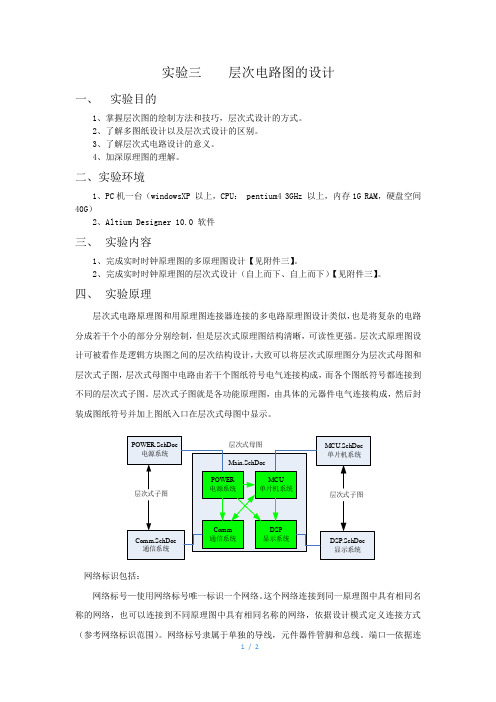

二、实验环境1、PC机一台(windowsXP 以上,CPU:pentium4 3GHz 以上,内存1G RAM,硬盘空间40G)2、Altium Designer 10.0 软件三、实验内容1、完成实时时钟原理图的多原理图设计的。

2、完成实时时钟原理图的层次式设计(自上而下、自下而上)四、实验步骤1、多电路原理图的绘制建立一个空的工程并添加电源电路原理图、单片机系统原理图、通信系统原理图和显示电路原理图,然后在各原理图中添加原理图连接器。

2、自上而下的层次式设计1.创建新的工程并添加一个原理图文件用来绘制母图;2.在母图中添加单片机系统功能模块、电源系统功能模块、显示系统功能模块和通信功能模块,然后添加相应的模块接口;3.绘制导线连接各图纸符号相对应的端口;4.执行【CreateSheet From Sheet Symbol】命令,由图纸符号生成原理图;5.绘制各个层次式电路子图;6.编译层次式电路原理图。

3、自下而上的层次式设计1.新建一个工程文件并将自上而下所绘制的层次式原理图各子图复制到与工程相同的文件夹,然后添加到工程中;2.新建一个层次式电路图母图并命名,且不添加其他元件和图纸符号;3.在母图中执行【Create Sheet from Symbol or HDL】命令,在弹出的对面选中其中一个电路原理图并确认;4.放置原理图对应的图形符号,并修改图纸入口的位置和图纸符号的大小;5.为其他子原理图在母图中创建图纸符号,并进行电气连接。

五、实验结果(截图)1、多原理图设计截图2、自上而下层次式设计截图3、自下而上层次式设计截图六、实验总结与心得在本次实验中,我深入地学习了AD10的多电路原理图的编辑、自上而下的电路原理图设计和自下而上的电路原理图设计等,并学会了模板的应用、图纸连接器的使用、图纸符号及其入口及端口的操作和层次式原理图之间的切换。

层次原理图的设计概述

选择电路面讲层次电路图的设计方法有两种,现在 就利用自上而下的方法设计一个4串行接口的 原理图。它们分别由串行接口和线驱动模块 (4 Port UART and Line Drivers.sch)和ISA总 线与地址解码(ISA Bus and Address Decoding.sch)两部分组成。 • 下图 是该原理图的层次电路图。

6

选择对话框 •

7

• 这个对话框询问在产生与电路方块图相对应的原理 图时,相对的输入输出点是否将信号方向反向,此 处应选择No。

2.自下而上的层次电路设计方法

此方法指首先画出原理图,再由原理图来产生方 块电路图的方法。和刚才的步骤相反,先绘制原理 图,再执行菜单“Desgin”下的 “Design\Create Symbol From Sheet ”。点击之后会 出现如下所示的对话框。从中选中要创建层次电路 图的方块图。(前提是要先建好子图。从总图操作 Design\Create Symbol From Sheet )

17

18

• 3.放置出入端口 • 点击画电路图工具栏里的图标 ,或者执行菜 单Place -> Add Sheet Entry。 • 光标变成十字状,将光标移动到方块电路中, 点击鼠标,光标上面出现一个小圆点,且光标将被 限制在方块电路的左右边界内,确定合适的位置后 点击鼠标,即可在该处放置一个方块图的进出点, 点击右键结束放置方块图进出点状态。 • 按Tab键,即可出现方块电路进出点编辑对话 框。

10

11

图 层次电路图

12

• 绘制的具体步骤: • 1.建立如下图 所示的文档,并且命名。

图3-2 文档

• 2.建立层次原理的文件(.prj)。

13

实验电路结构图介绍(doc 7页)

实验电路结构图介绍(doc 7页)第三节:实验电路结构图CLOCK0CLOCK2CLOCK5CLOCK9目标芯片F PG A /C P L D HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8NO.0S P E A K E R扬声器实验电路结构图译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16CLOCK9CLOCK5CLOCK2CLOCK0SPEAKER扬声器NO.1PIO11-PIO8PIO15-PIO12PIO48PIO49D15D16HEX HEXPIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39D1D2D3D4D5D6D7D8实验电路结构图译码器译码器译码器译码器FPGA/CPLD 目标芯片12345678PIO3-PIO0PIO7-PIO4HEX HEX 键1键2键3键4键5键6键7键8PIO39-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2 实验电路结构图NO.0 附图3 实验电路结构图NO.1附图13 GW48-CK系统的VGA和RS232引脚连接图(此两个接口与PK系列引脚不同)附图14 新GW48-PK3/CP+系统的VGA和RS232引脚连接图(此VGA接口与老式PK系列引脚不同)附图7 实验电路结构图NO.5(VGA引脚为老式PK系列和新式PK2S/4引脚)CLOCK9CLOCK5CLOCK2CLOCK0PIO8D11D12PIO9D13PIO10D14PIO11D15PIO12PIO13D16D6D5D4D3D2D1D7D8)(12345678实验电路结构图NO.6目标芯片FPGA/CPLD 扬声器S P E A K E RPIO3-PIO0PIO7-PIO4HEX HEXPIO16PIO13-PIO8PIO23PIO22PIO21PIO20PIO19PIO18PIO17直接与7段显示器相接PIO46-PIO40PIO38-PIO32PIO30-PIO24PIO22-PIO16PIO46-PIO40 接 g, f, e, d, c, b, aPIO38-PIO32 接 g, f, e, d, c, b, aPIO30-PIO24 接 g, f, e, d, c, b, a 七段PIO22-PIO16 接 g,f,e,d,c,b,a键1键2键3键4键5键6键7键8附图8 实验电路结构图NO.6 附图12 GW48-PK2上扫描显示模式时的连接方式: 8数码管扫描式显示,输入信号高电平有效D+(PIO65)D-(PIO64)GNDVCCSLAVEUSB PIO65PIO64OO O O选择开关T O F P G A T O M C U键复位接PC 机串行通讯接口接口电路235RS-232B4P27P26P25P24P23P22P21P20PSEN ALE EA P07P06P05P04P03P02P01P00VCC A T 89C 5140393837363534333231302928272625242223212019181716151413121110987654321GND X1X2PIO66PIO67PIO77PIO76PIO79PIO78P31P30RESET PIO75PIO74PIO73PIO72PIO71PIO70PIO69PIO68LCD 液晶显示屏VCC GND P22P21P20P00P01P02P03P04P05P06P07P23P241234567891011121314151617181920附图11 实验电路结构图COM (GW48-PK3上液晶与单片机以及FPGA 的I/O 口的连接方式)P82P62EP1C3目标板插座EP1C6/12目标板插座P94P91P79PIO26PIO28PIO30PIO32PIO34目标板插座22423PIO27PIO29PIO31PIO33PIO35+12V -12V 2423GND VCC VCCIO o o o o o oo o o o o o o o o o o o o o PIO26PIO28PIO30PIO32PIO342423PIO27PIO29PIO31PIO33PIO35+12V -12V P177P144P1432423GND VCC VCCIO P5P23o o o o o oo o o o o o o o o o o o o o第七节 GW48CK/PK2/PK3/PK4 系统万能接插口与结构图信号/与芯片引脚对照表结构图上的信号名GWAC6 EP1C6/12Q240Cyclone GWAC3 EP1C3TC144Cyclone GWA2C5 EP2C5TC144 CycloneIIGWA2C8 EP2C8QC208 CycloneIIGW2C35 EP2C35FBGA484C8 CycloneII WAK30/50 EP1K30/50TQ C144 ACEXGWXS200 XC3S200 SPARTANGWXS200 XC3S200 SPARTAN引脚号引脚号引脚号引脚号引脚号引脚号 引脚号引脚号PIO 0 233 1 1438 AB15 8 5 21PIO 1 234 2 144 10 AB14 9 6 22 PIO 2 235 3 3 11 AB13 10 7 24 PIO 3 236 4 4 12 AB12 12 8 26 PIO 237 5 7 13 AA20 13 10 27PIO239 7 9 15 AA18 18 12 29 6240 10 24 30 L19 19 13 31 PIO71 11 25 31 J14 20 14 33 PIO8PIO2 32 26 33 H15 21 15 34 93 33 27 34 H14 22 17 15 PIO104 34 28 35 G16 23 18 16 PIO116 35 30 37 F15 26 20 35 PIO127 36 31 39 F14 27 21 36 PIO138 37 32 40 F13 28 23 37 PIO1412 38 40 41 L18 29 24 39 PIO15PIO13 39 41 43 L17 30 25 40PIO1714 40 42 44 K22 31 26 42PIO1815 41 43 45 K21 32 27 43PIO1916 42 44 46 K18 33 28 44PIO2017 47 45 47 K17 36 30 45结构图上的信号名GWAC6EP1C6/12Q240CycloneGWAC3EP1C3TC144CycloneGWA2C5EP2C5TC144CycloneIIGWA2C8EP2C8QC208CycloneIIGW2C35EP2C35FBGA484C8CycloneIIWAK30/50EP1K30/50TQC144 ACEXGWXS200XC3S200SPARTANGWXS200XC3S200SPARTAN 引脚号引脚号引脚号引脚号引脚号引脚号引脚号引脚号PIO2118 48 47 48 J22 37 31 46PIO2219 49 48 56 J21 38 32 48PIO2320 50 51 57 J20 39 33 50PIO2421 51 52 58 J19 41 35 51PIO2541 52 53 59 J18 42 36 52PIO128 67 67 92 E11 65 76 113 26132 68 69 94 E9 67 77 114 PIO27133 69 70 95 E8 68 78 115 PIO28134 70 71 96 E7 69 79 116 PIO29PIO135 71 72 97 D11 70 80 117 30136 72 73 99 D9 72 82 119 PIO31PIO137 73 74 101 D8 73 83 120 32138 74 75 102 D7 78 84 122 PIO33139 75 76 103 C9 79 85 123 PIO34PIO140 76 79 104 H7 80 86 123 35141 77 80 105 Y7 81 87 125 PIO36PIO158 78 81 106 Y13 82 89 126 37159 83 86 107 U20 83 90 128 PIO38160 84 87 108 K20 86 92 130 PIO39161 85 92 110 C13 87 93 131 PIO40PIO162 96 93 112 C7 88 95 132 41163 97 94 113 H3 89 96 133 PIO42PIO164 98 96 114 U3 90 97 135 43165 99 97 115 P3 91 98 137 PIO44166 103 99 116 F4 92 99 138 PIO45PIO167 105 100 117 C10 95 100 139 46168 106 101 118 C16 96 102 140 PIO47PIO169 107 103 127 G20 97 103 141 48173 108 104 128 R20 98 104 143 PIO49226 131 129 201 AB16 137 130 2 PIO60225 132 132 203 AB17 138 131 3 PIO61PIO224 133 133 205 AB18 140 132 4 62223 134 134 206 AB19 141 135 5 PIO63PIO222 139 135 207 AB20 142 137 7 64219 140 136 208 AB7 143 140 9 PIO65218 141 137 3 AB8 144 141 10 PIO66PIO217 142 139 4 AB11 7 1 11 67180 122 126 145 A10 119 129 161 PIO68PIO69181 121 125 144 A9 118 123 156结构图上的信号名GWAC6EP1C6/12Q240CycloneGWAC3EP1C3TC144CycloneGWA2C5EP2C5TC144CycloneIIGWA2C8EP2C8QC208CycloneIIGW2C35EP2C35FBGA484C8CycloneIIWAK30/50EP1K30/50TQC144 ACEXGWXS200XC3S200SPARTANGWXS200XC3S200SPARTAN 引脚号引脚号引脚号引脚号引脚号引脚号引脚号引脚号PIO70182 120 122 143 A8 117 122 155PIO71183 119 121 142 A7 116 119 154PIO72184 114 120 141 A6 114 118 152PIO73185 113 119 139 A5 113 116 150PIO74186 112 118 138 A4 112 113 149PIO75187 111 115 137 A3 111 112 148PIO76216 143 141 5 AB9 11 2 12PIO77215 144 142 6 AB10 14 4 13PIO78188 110 114 135 B5 110 108 147PIO79195 109 113 134 Y10 109 107 146SPEAKER174 129 112 133 Y16 99 105 144CLO CK0 28 93 91(CLK4)23 L1 126 124 184CLO CK2 153 17 89(CLK6)132 M1 54 125 203CLO CK5 152 16 17(CLK0)131 M22 56 127 204CLO CK9 29 92 90(CLK5)130 B12 124 128 205。

第3讲 层次电路原理图设计

12

PCB辅助设计 PCB辅助设计

六、层次电路的切换

在层次电路中,经常要在各层电路图之间相互切换, 在层次电路中,经常要在各层电路图之间相互切换, 切换的方法主要有2 切换的方法主要有2种。 利用设计管理器,鼠标左键单击所需文档, ⑴利用设计管理器,鼠标左键单击所需文档,便可在 右边工作区中显示该电路图。 右边工作区中显示该电路图。 执行菜单Tools→Up/Down Hierarchy或单击主工具 ⑵执行菜单Tools→Up/Down Hierarchy或单击主工具 将光标移至需要切换的子图符号上, 栏上按钮 ,将光标移至需要切换的子图符号上,单击 鼠标左键,即可将上层电路切换至下一层的子图; 鼠标左键,即可将上层电路切换至下一层的子图;若是从 下层电路切换至上层电路, 下层电路切换至上层电路,则是将光标移至下层电路的 I/O端口上 单击鼠标左键进行切换。 端口上, I/O端口上,单击鼠标左键进行切换。

PCB辅助设计 PCB辅助设计

PCB辅助设计 PCB辅助设计

1

PCB辅助设计 PCB辅助设计

第3讲

层次电路原理图设计

主 要 内 容

一、层次设计基本结构 二、主图电路方块图设计 放置子图符号的I/O I/O端口 三、放置子图符号的I/O端口 四、设置图纸信息 五、由子图符号生成子图文件 六、层次电路的切换

10

PCB辅助设计 PCB辅助设计

五、由子图符号生成子图文件

执行菜单Design→Create Symbol, 执行菜单Design→Create Sheet From Symbol, 将光标移到子图符号上,单击鼠标左键, 将光标移到子图符号上,单击鼠标左键,屏幕弹出是否 颠倒I/O端口的电气特性的对话框,如图2 40所示 I/O端口的电气特性的对话框 所示。 颠倒I/O端口的电气特性的对话框,如图2-40所示。若 选择“ 则生成的电路图中的I/O I/O端口的输入输出 选择“是”,则生成的电路图中的I/O端口的输入输出 特性将与子图符号I/O端口的输入输出特性相反; I/O端口的输入输出特性相反 特性将与子图符号I/O端口的输入输出特性相反;若选 则生成的电路图中的I/O I/O端口的输入输出特 择“否”,则生成的电路图中的I/O端口的输入输出特 性将与子图符号I/O端口的输入输出特性相同, I/O端口的输入输出特性相同 性将与子图符号I/O端口的输入输出特性相同,一般选 择“否”。

层次电路图的设计

实验三层次电路图的设计一、实验目的1、掌握层次图的绘制方法和技巧,层次式设计的方式。

2、了解多图纸设计以及层次式设计的区别。

3、了解层次式电路设计的意义。

4、加深原理图的理解。

二、实验环境1、PC机一台(windowsXP 以上,CPU: pentium4 3GHz 以上,内存1G RAM,硬盘空间40G)2、Altium Designer 10.0 软件三、实验内容1、完成实时时钟原理图的多原理图设计【见附件三】。

2、完成实时时钟原理图的层次式设计(自上而下、自上而下)【见附件三】。

四、实验原理层次式电路原理图和用原理图连接器连接的多电路原理图设计类似,也是将复杂的电路分成若干个小的部分分别绘制,但是层次式原理图结构清晰,可读性更强。

层次式原理图设计可被看作是逻辑方块图之间的层次结构设计,大致可以将层次式原理图分为层次式母图和层次式子图,层次式母图中电路由若干个图纸符号电气连接构成,而各个图纸符号都连接到不同的层次式子图。

层次式子图就是各功能原理图,由具体的元器件电气连接构成,然后封装成图纸符号并加上图纸入口在层次式母图中显示。

网络标识包括:网络标号—使用网络标号唯一标识一个网络。

这个网络连接到同一原理图中具有相同名称的网络,也可以连接到不同原理图中具有相同名称的网络,依据设计模式定义连接方式(参考网络标识范围)。

网络标号隶属于单独的导线,元件器件管脚和总线。

端口—依据连接方式,一个端口可以横向连接具有相同名字的其它端口,或纵向的连接到具有相同名字的图纸入口。

图纸入口—当连接是纵向的,你可以用图纸入口连接到下层原理图中有相同名字的端口。

添加一个图纸入口执行“Place » Add Sheet Entry”命令。

电源端口—整个设计中所有相同名称的电源端口是相互连接的。

隐藏管脚—隐藏管脚类似电源端口,在整个设计中,连接所有具有相同名称的网络。

五、实验步骤(书本P136-152)1.打开上次所用的CAD图,重新建一个工程和四个文件,并且改一下文件名以便区分,将各个部分复制到各个对应的文件中。

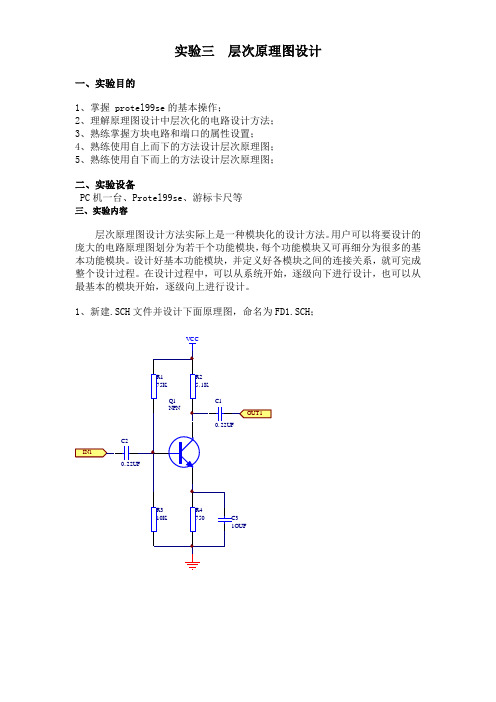

实验三 层次原理图设计

实验三层次原理图设计一、实验目的1、掌握 protel99se的基本操作;2、理解原理图设计中层次化的电路设计方法;3、熟练掌握方块电路和端口的属性设置;4、熟练使用自上而下的方法设计层次原理图;5、熟练使用自下而上的方法设计层次原理图;二、实验设备PC机一台、Protel99se、游标卡尺等三、实验内容层次原理图设计方法实际上是一种模块化的设计方法。

用户可以将要设计的庞大的电路原理图划分为若干个功能模块,每个功能模块又可再细分为很多的基本功能模块。

设计好基本功能模块,并定义好各模块之间的连接关系,就可完成整个设计过程。

在设计过程中,可以从系统开始,逐级向下进行设计,也可以从最基本的模块开始,逐级向上进行设计。

1、新建.SCH文件并设计下面原理图,命名为FD1.SCH;R1 75K R2 5.1KR3 10K R4 750C20.22UFC10.22UFC31OUF Q1NPNIN1OUT1 VCC2、新建.SCH 文件设计下面原理图,命名为FD2.SCH ; R168KR25.1K R310K R4680C20.22UFC31OUFQ1NPN IN2OUT2VCC3、新建.SCH 文件,命名为FD.SCH ;进入FD.SCH 文件,在总图窗口,执行[Design ]/[Creat Sheet From Symbol ]菜单命令,生成FD1.SCH 、FD2.SCH 模块,连线绘制如下总图。

FD 1FD 1.SchIN1O UT1FD 2FD 2.Sch IN2O UT2O UTIN四、实验步骤实验步骤自己根据绘图过程写,写出关键步骤即可五、思考题1、什么是层次原理图?2、什么是自顶向下设计?。

多层电路板及其制作方法

多层电路板及其制作方法多层电路板(Multilayer Printed Circuit Board,简称MLBP)是指通过多层电路板的设计与制造技术,将两个或两个以上的单层、双层或多层电路板互相连接而成的一种电路板。

多层电路板具有高密度、高性能、稳定性好等优点,广泛应用于电子产品中。

1.设计:根据电路需求,通过电路设计软件进行电路图的设计。

在多层电路板的设计中,需要注意不同层之间的连线与连接孔设计,以及厚铜层的设置等。

2.材料准备:根据设计要求,选择合适的玻璃纤维布基材和铜箔,并进行切割成所需的大小和形状。

3.板层处理:将切割好的玻璃纤维布基材浸入树脂溶液中,使其充分浸湿。

然后将涂覆了铜箔的电路板塞入树脂浸润剂中,使其表面与铜箔之间有良好的粘附性。

4.激光孔凿:将经过处理的玻璃纤维布基材覆盖在钢板上,使用激光孔凿机对电路板进行钻孔操作。

通过激光束的照射和打孔,形成多层电路板内部的连线孔。

5.排胶:将凿完孔的电路板取出,进行排胶处理。

排胶是为了去除在激光孔凿过程中产生的残渣和生成的乳液。

6.层压:将钻孔后的电路板铺放在钢板上,然后叠加多层的玻璃纤维布基材和铜箔,形成叠压结构。

再将层压结构的上下表面用铝箔层包裹,并放入预先加热的层压机中,进行高温和高压的压制。

7.成型:经过层压处理的多层电路板,采用CNC机器或模具切割成所需的尺寸和形状。

8.焊接与覆膜:将电路板上的元器件进行焊接,并进行控制阻焊、喷锡和覆膜等后续处理。

以上就是多层电路板的制作方法的基本流程。

在实际制作中还需要注意多层电路板的层与层之间的连线设计,以及焊接工艺、质量控制等方面的要求。

随着电子产品的不断发展和需求的变化,多层电路板的制作技术也在不断创新和改进,为电子产品的发展提供了坚实的基础。

初中物理三级电路实验设计

初中物理三级电路实验设计实验目的本实验旨在通过设计和构建三级电路,加深学生对电路中电流和电压的理解,并应用欧姆定律和串联电路、并联电路的知识解决相关问题。

实验原理1. 欧姆定律:电流与电压成正比,与电阻成反比。

可表示为 `I = V / R`,其中 `I` 为电流,`V` 为电压,`R` 为电阻。

2. 串联电路:电流在串联电路中保持恒定,总电压为各个电阻之和。

3. 并联电路:电压在并联电路中保持恒定,总电流为各个电阻之和。

实验材料1. 电池组2. 电阻3. 开关4. 电线5.电流表6. 电压表7. 电池盒8. 铁丝实验步骤1. 将电池组、电阻和开关依次连接,构建串联电路。

2. 测量并记录各个电阻的电压和电流。

3. 分别改变电阻的数值,观察电流和电压的变化,并进行记录。

4. 将电阻改为并联连接,构建并联电路。

5. 测量并记录并联电路中各个电阻的电压和电流。

6. 分别改变电阻的数值,观察电流和电压的变化,并进行记录。

实验结果分析1. 串联电路:根据欧姆定律,串联电路中电流保持恒定,总电压为各个电阻之和。

通过实验可以观察到,随着电阻值的增加,电流逐渐减小,而电压逐渐增加。

2. 并联电路:根据欧姆定律,并联电路中电压保持恒定,总电流为各个电阻之和。

实验结果表明,随着电阻值的增加,电流逐渐增大,而电压保持不变。

实验注意事项1. 在连接电路前,确保电源关闭。

2. 操作电线时要小心,避免触及金属部分。

3. 测量电流和电压时,要注意接线的正确性,并将万用表设置到相应的测量模式。

实验拓展学生可以进一步探究以下问题:1. 如何计算串联电路中的总电压和总电流?2. 如何计算并联电路中的总电流和总电压?3. 为什么串联电路中电流保持恒定,而并联电路中电压保持恒定?4. 通过改变电阻值,如何调节电流和电压的大小?实验结论通过本实验的设计与实施,学生能够更好地理解欧姆定律和串联电路、并联电路的原理与特点,并且掌握相关的实验操作技巧。

多层电路板原理

多层电路板原理多层电路板是指在一张电路板上同时堆叠多层电路层,通过相互之间的电气连线进行信号传输和电源供应。

它广泛应用于各种电子设备中,例如手机、电脑、通信设备等。

多层电路板的设计和制造需要一系列的原理和技术,下面将详细介绍多层电路板的原理。

首先,多层电路板的设计原理是为了满足电子设备对于高集成度和小体积的要求。

传统的单层电路板由于受限于空间和层数的限制,无法满足复杂电路的布线和连接需求。

而多层电路板的设计将电路层进行堆叠,通过垂直连接信号和电源层,在相同的面积上实现了更多的电路布线和连接。

这不仅提高了电路的集成度,还有效地减小了电子设备的尺寸和重量。

其次,多层电路板的信号传输原理是通过垂直连接信号和电源层来实现。

每一层都有自己的信号和电源层,并通过通过铜壳以及插针等电气接头连接在一起。

信号层主要用于传输电子设备之间的信号。

电源层主要用于提供供电电源。

通过合理的设计层间连线,可以在不同层之间传输信号和供电,从而满足电路的需求。

最后,多层电路板的制造原理包括多种工艺和技术。

首先是层间电气连线的制造技术。

常见的制造技术有盲孔和埋孔技术,它们可以在不同层之间打孔,使电气连线和连接器连接在一起。

其次是制造层内电路的技术。

常见的制造技术有沉金、镀铜等,它们可以在不同层之间制造电路。

另外,为了提高电路板的抗干扰能力和信号传输速度,还需要在电路板上布置电路板封装和电磁屏蔽等附加结构。

总之,多层电路板是一种用于满足电子设备高集成度和小体积要求的电路板。

它通过堆叠多个电路层,并通过垂直连接信号和电源层来实现信号传输和电源供应。

多层电路板的设计、制造和原理都是非常复杂的,需要结合多种工艺和技术来实现。

随着电子设备的发展,多层电路板在各个领域中的应用将会更加广泛。

层次原理图及其PCB设计PPT26页

36、“不可能”这个字(法语是一个字 ),只 在愚人 的字典 中找得 到。--拿 破仑。 37、不要生气要争气,不要看破要突 破,不 要嫉妒 要欣赏 ,不要 托延要 积极, 不要心 动要行 动。 38、勤奋,机会,乐观是成功的三要 素。(注 意:传 统观念 认为勤 奋和机 会是成 功的要 素,但 是经过 统计学 和成功 人士的 分析得 出,乐 观是成 功的第 三要素 。

39、没有不老的誓言,没有不变的承 诺,踏 上旅途 ,义无 反顾。 40、对时间的价值没有没有深切认识 的人—卡耐基 47、书到用时方恨少、事非经过不知难。——陆游 48、书籍把我们引入最美好的社会,使我们认识各个时代的伟大智者。——史美尔斯 49、熟读唐诗三百首,不会作诗也会吟。——孙洙 50、谁和我一样用功,谁就会和我一样成功。——莫扎特

实验三、AD层次原理图设计

实验三、AD层次原理图设计【实验目的】进一步掌握原理图设计的技巧,熟练原理图绘制过程掌握AD层次原理图的基本设计方法。

掌握自顶向下的层次设计思想,学习由母图生成子图的方法掌握子图、母图的相互切换【实验要求】上机操作,根据题目要求保存文件。

下课时自己设法将文件带走保存好。

在实验报告本写上实验日期、周次和本次实验的标题、实验目的、实验内容和实验总结。

实验内容只抄题目,不需要抄操作提示,也不需要写操作步骤。

如果某个题目的操作步骤是你以前没接触过的,也可在实验报告上顺便记录一下。

遇到不会的题目,通过与同学或老师讨论、参阅参考书、上网检索等方式解决。

【实验内容】1.进入ftp://10.81.40.222/张利民/电子线路CAD/PDF READER/, 下载安装PDF阅读器。

2.进入实验三,打开实验三-声控变频器.pdf,按照要求绘制原理图3.本实验需新建项目,项目存储在EXM-3-学号文件夹,本项练习要求将原理图加入所建立的项目中,做ERC测试,输出BOM表,输出网络表4.ERC测试后,如出现错误提示,请修改并记录错误信息并修改,直至测试通过为止5.层次图说明:a)母图:声控变频器.SchDocb)子图一:Power Sheet.SchDocc)子图二:FC Sheet.SchDoc6.相关提示:a)所需库名称:i.Miscellaneous Devices.IntLibii.Miscellaneous Connector.IntLibiii.ST Analog Timer CircuitaIntLibiv.ST Power Mgt V oltage RegulatoraIntLibb)器件库搜索提示:i.LF365N 搜索时使用OP AMP 关键字【实验总结】请写下你在完成上述题目时的主要收获和遇到的主要困难。

写下ERC测试遇到的问题和解决方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三层次电路原理图与多层电路板

的设计

班级:电子121 姓名:王少男学号:1262211124

一、实验目的:

1、掌握层次电路设计方法掌握层次原理的浏览方法,和主电

路与子电路图之间切换

2、掌握多通道电路图设计方法

3、掌握多层电路板设计方法

二、实验内容:

绘制如图所示的主电路图,和该主电路图下面的三个子电路图如图所示。

分别用自上而下和自下而上的方法。

三、 实验小结

通过本次试验,发现在进行由子图生成母图时什么情况下点YES 什么情况下点NO,经过同学的知道已经解决,以后课下需要多加练习。