MegaWizard应用

如何使用logisim

Logisim的简单入门一,准备工作参考:罗老板的计算机结构与组成课程/rjgcx/lzw/COD/Machine Structures. Spring 2010, UC Berkeley/~cs61c/sp10/软件环境:Logisim仿真软件(需要JAVA虚拟机)/~burch/logisim/QuartusII 8.1/硬件环境:PC机with Windows XPDE2开发板(DE2 Development and Education Board User Manual)参考书:anization.and.Design关于QuartusII的使用教程先来以一个与门电路的实验,来看一下基本的操作,在Logisim中一个与门电路生成过程如下:1.按与门的选择按钮,添加一个与门到电路中。

2.使用按钮添加一个输入引脚,用于设置输入电平。

3.添加一个引脚,通过属性中设置Pin的属性为输出:这样得到一个输出引脚。

4.移动以上添加的元素,得到原理图:注意选中按钮,此时可以拖拽连线,那么我们把电路各部分连接如下:5. 接下来通过选中按钮就可以鼠标点击设定输入管脚上的电平为1或0了,输出引脚也会相应改变,输出结果。

当然通过左下方的属性设定,还可以设定当前选择元件的朝向,数据位数,输入端口数等参数。

6.另外推荐大家后面设计的时候使用一下tunnel这个工具,代替复杂的连线,在后面复杂设计的地方,让你从蜘蛛网一样的连线中解脱出来,例如上面的电路可以这样表示:图中输入,与门模块,输出三部分结构分的很清晰,tunnel的使用使我们的电路设计更加规,类似logisim中的tunnel工具在其他原理图工具中类似的工具是经常见到的,虽然名字会有不同,用途是一样的。

7.最后是子电路添加方法,选择Project--->Add Circuit…,如下图“:子电路的绘制与上面基本相同,注意的是输入输出引脚要连接Pin引脚,并设定好输入输出属性。

EDA技术3-QUARTUS使用方法

厦门理工学院通信系 刘虹

26

3.4 LPM_ROM宏模块应用

使用Quartus II 的MegeWizard Plug-In Manager中的宏功能模块可以帮助用户完成一些复 杂系统的设计,并可以方便地对现有的设计文件 进行修改。这些宏功能模块包括LPM(Library Parameterized Megafunction)、MegaCore(例 如FFT、FIR等)和AMMP(Altera Megafunction Partners Program,例如PCI、DDS等)。下面以 波形发生器的设计为例,介绍Quartus II宏功能 模块的使用方法。

厦门理工学院通信系 刘虹 2

为了方便电路设计,设计者首先应当在计 算机中建立自己的工程目录(如d:\myeda)。 将自己的全部EDA设计文件放在文件夹中。

注意:工程文件夹的名称不要使用汉字,最好 也不要使用数字。

厦门理工学院通信系 刘虹

3

Quartus II原理图输入的基本操作

编辑原理图

引脚锁定

厦门理工学院通信系 刘虹

24

在设计中嵌入SignalTap Ⅱ逻辑分析

仪有两种方法:第一种方法是建立一个

SignalTap Ⅱ文件(.stp),然后定义STP文

件的详细内容;第二种方法是用

MegaWizard Plug-InManager建立并配臵

STP文件,然后用MegaWizard实例化一个

HDL输出模块。

厦门理工学院通信系 刘虹

29

1. 加入计数器元件 用鼠标双击原理图编辑窗, 在弹出的元件选择窗的 “Libraries”栏目中选择 “arithmetic”的 “lpm_counter”(计数器) LPM元件。LPM是参数化的多功 能库元件,每一种LPM元件都 具有许多端口和参数,通过对 端口的选择与参数的设臵得到 设计需要的元件。

Mega软件的使用1

MEGA软件的使用Mega软件输入数据的格式Mega软件输入数据的格式比较简单,在众多遗传学分析软件中是比较容易制作的一种。

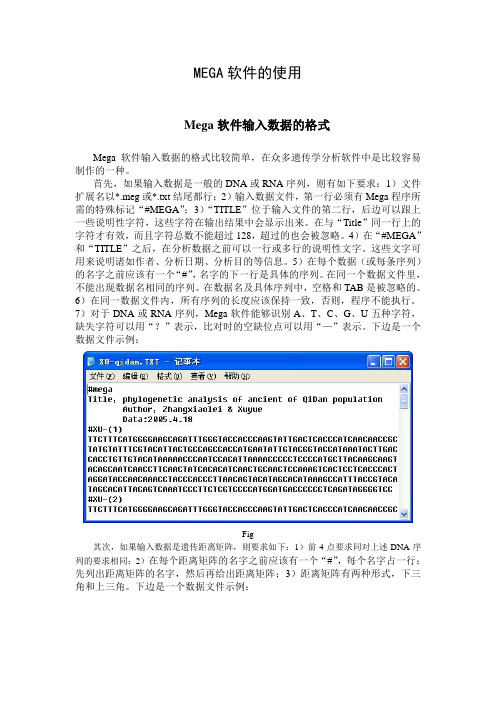

首先,如果输入数据是一般的DNA或RNA序列,则有如下要求:1)文件扩展名以*.meg或*.txt结尾都行;2)输入数据文件,第一行必须有Mega程序所需的特殊标记“#MEGA”;3)“TITLE”位于输入文件的第二行,后边可以跟上一些说明性字符,这些字符在输出结果中会显示出来。

在与“Title”同一行上的字符才有效,而且字符总数不能超过128,超过的也会被忽略。

4)在“#MEGA”和“TITLE”之后,在分析数据之前可以一行或多行的说明性文字。

这些文字可用来说明诸如作者、分析日期、分析目的等信息。

5)在每个数据(或每条序列)的名字之前应该有一个“#”,名字的下一行是具体的序列。

在同一个数据文件里,不能出现数据名相同的序列。

在数据名及具体序列中,空格和TAB是被忽略的。

6)在同一数据文件内,所有序列的长度应该保持一致,否则,程序不能执行。

7)对于DNA或RNA序列,Mega软件能够识别A、T、C、G、U五种字符,缺失字符可以用“?”表示,比对时的空缺位点可以用“—”表示。

下边是一个数据文件示例:Fig其次,如果输入数据是遗传距离矩阵,则要求如下:1)前4点要求同对上述DNA序列的要求相同;2)在每个距离矩阵的名字之前应该有一个“#”,每个名字占一行;先列出距离矩阵的名字,然后再给出距离矩阵;3)距离矩阵有两种形式,下三角和上三角。

下边是一个数据文件示例:下图是距离矩阵的示意图,左边是下三角矩阵,右边是上三角矩阵。

再次,如果数据是测序图谱的形式,直接导入即可。

下图是测序图谱示例:FigMEGA界面及操作Mega是一款操作十分简便的遗传学分析软件,其界面十分友好,即使初学者也很易上手。

1、数据的录入及编辑Mega软件能够接受多种数据格式,如FASTA格式、Phylip格式、PAUP数据格式等等。

EDA第七章_宏功能模块与IP应用

下面以确定64点正弦波在ROM内的波形数据文件 为例分别说明。

1.建立.mif格式文件

使用工具:Quartus II 的ROM数据文件编辑窗口或其他编辑器

【例7-1】用Quartus II 的ROM数据文件编辑窗口产生.mif格式文件 方法:File菜单NewOther files页Memory Initialization File项 选择ROM字数和字长,再填写好下列表格并保存即得。

7.2 LPM模块应用实例

正弦信号发生器

一、定制LPM_ROM初始化数据文件

Quartus II 能接受的LPM_ROM中的初始化数据 文件的格式有2种:

Memory Initialization File(.mif)格式 Hexadecimal(Intel-Format) File(.hex)格式

使用Megafunction将大大的减少设计风险及缩短开发周期。

Megafunction可以使设计师将更多时间和精力放在改善及提高系统级 的产品上,而不要重新开发现成的Megafunction。

IP(知识产权)

一个好的IP Core要具备可靠、可重用、 可配置、可测试的特性,还应有详细 准确的说明文档 最成功的IP提供商之一: 虽然只有LPM、部分器件专有的 Megafunction是免费的,但是这些免 费的模块也足够满足大多数设计的需 要(LPM库只有25个基本模块就号称 可以完成所有的设计)。 评估付费Megafunction: 使用开放式内核(OpenCore)技术 , 其设计流程如右图所示。 如何用好Altera的Megafunction:认真 阅读文档并执行必要的配置工作

硬件评估

购买

当您对 IP 内核完全满意,并准备将设计投产时,可以购买许可,生成产品 器件编程文件。Altera MegaCore®许可能够永久使用,支持多种工程,包括 一年更新和支持。 对 Altera 所有 IP 提供浮动和节点锁定的许可。可提供多种不同许可期限、 条件和价格模型的第三方 IP 内核。请直接联系 IP 合作伙伴,了解详细信息。

MegaWizardPlug-InManager的简单使用图解

MegaWizard Plug-In Manager的简单使用图解

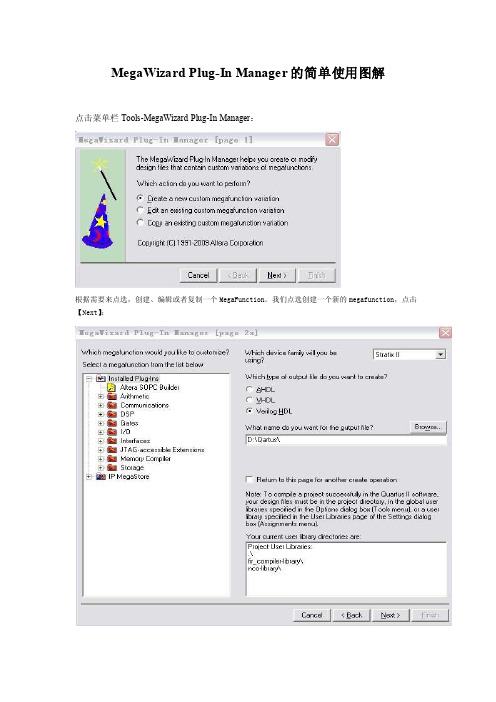

点击菜单栏Tools-MegaWizard Plug-In Manager:

根据需要来点选,创建、编辑或者复制一个MegaFunction。

我们点选创建一个新的megafunction,点击【Next】:

根据需要来选择一个MegaFunction,左侧列表为Altera公司提供的MegaFunction资源,这些资源划分为算术(Arithmetic)、逻辑门(Gates)、输入输出(I/O)、存储器(Memory Compiler)、寄存器(Storage)等等。

出现灰色的模块是因为CPLD器件族或者软件授权所致。

我们选择Arithmetic列表下的LPM_MULT模块(这是一个参数化的定点数乘法模块,而ALTFP_MULT是参数化的浮点数乘法模块),右侧选择芯片类型、描述语言类型、设置文件名(注意该模块名,不能与顶层原理图同名)。

点击【Next】:

然后在Parameters中根据需要(位数、有无符号、)来进行定制Megafunction,点击【Next】。

接着是EDA 窗口,该窗口指定用于仿真LPM模块功能的库文件,初学者不必做任何修改,直接点击【Next】。

最后是Summary窗口,这个窗口主要列出了宏功能模块实例化向导所生成的文件的详细描述。

最后点击【Finish】完成MagaFunction的设计。

最后在工程目录下,找到此模块的.v文件。

就可以把模块copy出来,在文本文件的mudule中调用。

quartus中fft模块使用

注释:(1) 描述数据和旋转因子精度。

(2) 使用Stratix II器件设计,Quartus II软件报告的设计使用的自适应查找表(ALUT)数。

逻辑单元(LE)数ALUT数相关。

(3) 在允许使用M-RAM资源的情况下,前面的数字表明在FFT设计向导中取消使用M-RAM时.M4K-RAM 的模块数。

注释:(1) 同表8.1(1)。

(2) 当使用缓冲突发结构时,在FFT。

向导中可以指定四输出(Quad.output)FFT擎数。

(3) 同表8.1(2)。

(4) 同表8.1(3)。

注释:(1) 同表8.1(1)。

(2) 当使用缓冲突发结构时,在FFI、向导中可以指定四输出(Quad—output)FFT引擎数。

用户可以并行选择1、2或4个四输出引擎。

(3) 在缓冲突发结构中,转换时间(Transform Time)定义为从已经加载N点输入数据块到第一个转换输出样点准备输出之间的时间。

转换时间不包括输出所有转换输出数据块所用的额外N一1个时注释:(1) 同表8.1(1)。

(2) 当使用突发数据流结构时,在FFT向导中可以指定引擎数。

可以并行选择l到2个单输出引擎或1、2或4个四输出引擎。

(3) 同表8.1(2)。

表8.5在stratix Ⅱ器件中使用突发(BurSt)数据流结构的性能注释:(1) 同表8.1(1)。

(2) 在突发I/O数据流结构中,可以在FFT向导中指定引擎数。

可以并行选择1到2个单输出引擎,或1、2或4个四输出引擎。

(3) 转换时间定义为从已经加载输入数据块到第一个转换结果样点(对应于输入数据块)输出之间的时帧(Time )。

转换时间不包括输出所有转换输出数据块的时间。

(4) 同表8.3(4)。

二.FFT兆核函数的应用1 系统要求本节讲述的应用需要下列硬件和软件配置:?装有Windows NT/2000/XP,Red Hat Linux 7.3/8.0或Red Hat企业版,Linux 3.0操作系统的PC机;或装有Solaris 7或8操作系统的Sun工作站。

进化树分析软件MEGA的用法

进化树分析软件MEGA的用法MEGA(Molecular Evolutionary Genetics Analysis)是一款功能强大的分子进化遗传学分析软件,用于构建进化树、进行序列比对、计算基因组变异等。

它提供了丰富的功能和易于使用的界面,使用户能够对生物序列进行详细的进化分析。

下面是MEGA软件的用法详解。

1.安装和启动MEGA软件2.导入序列数据在MEGA软件中,可以导入多种类型的序列数据,如DNA序列、蛋白质序列等。

您可以通过"File"菜单下的"Open"选项来导入已有的序列文件,或通过粘贴操作将文本格式的序列数据直接粘贴到MEGA软件中。

3.序列比对MEGA提供了多种序列比对方法,如ClustalW、MUSCLE等。

您可以通过"Align"菜单下的"Multiple Sequence Alignment"选项选择适当的方法进行序列比对。

在比对完成后,软件将显示每个位置的序列相似性信息。

4.进化树构建MEGA支持多种进化树构建方法,如NJ法(Neighbor-Joining)、ML法(Maximum Likelihood)等。

您可以通过"Phylogeny"菜单下的"Construct/Inference Phylogenetic Trees"选项选择适当的方法进行进化树构建。

MEGA还支持Bootstrap分析,用于评估构建的进化树的可靠性。

6.进化分析MEGA提供了多个工具用于进一步研究和分析进化树上的数据。

通过"Phylogeny"菜单下的"Tree Explorer"选项,您可以对进化树进行多种分析,如比较进化树的拓扑结构、计算进化树的分支长度、分析基因组变异等。

7.分支针对性分析MEGA还提供了一些工具用于对进化树上的特定分支进行分析。

利用高级Cyclone_III_FPGA_PLL,提高灵活性,增加集成度

利用高级Cyclone III FPGA PLL,提高灵活性,增加集成度-技术白皮书来源:EDACN摘要:在使用FPGA时,经常忽略了它的一个优点——能够集成时钟解决方案。

这种集成能力不但降低了系统成本,而且最新的65-nm Altera®Cyclone®III FPGA支持高级时钟管理和锁相环(PLL)技术,因此,还极大地提高了设计灵活性。

设计人员利用Cyclone III时钟管理功能,管理整个FPGA和电路板的时钟系统。

而且,由于Cyclone III PLL集成在FPGA中,可以利用Altera 的Quartus®II设计环境,轻松进行设置和配置。

关键词:FPGA,Cyclone III FPGA PLL,集成度引言在使用FPGA时,经常忽略了它的一个优点——能够集成时钟解决方案。

这种集成能力不但降低了系统成本,而且最新的65-nm Altera®Cyclone®III FPGA支持高级时钟管理和锁相环(PLL)技术,因此,还极大地提高了设计灵活性。

设计人员利用Cyclone III时钟管理功能,管理整个FPGA 和电路板的时钟系统。

而且,由于Cyclone III PLL集成在FPGA中,可以利用Altera的Quartus®II 设计环境,轻松进行设置和配置。

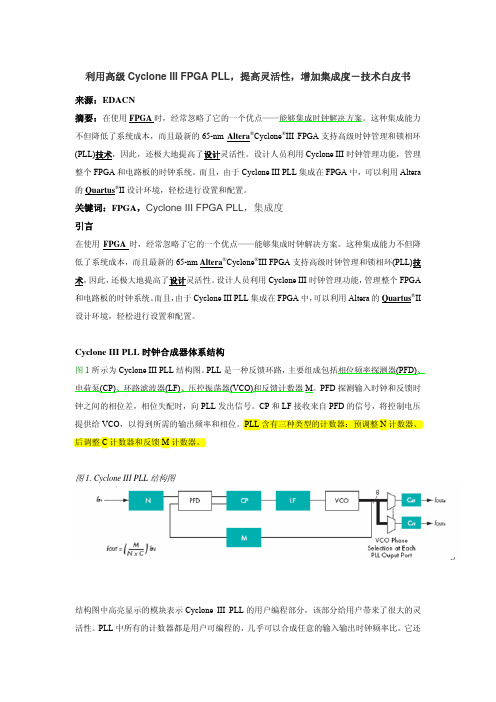

Cyclone III PLL时钟合成器体系结构图1所示为Cyclone III PLL结构图。

PLL是一种反馈环路,主要组成包括相位频率探测器(PFD)、电荷泵(CP)、环路滤波器(LF)、压控振荡器(VCO)和反馈计数器M。

PFD探测输入时钟和反馈时钟之间的相位差,相位失配时,向PLL发出信号。

CP和LF接收来自PFD的信号,将控制电压提供给VCO,以得到所需的输出频率和相位。

PLL含有三种类型的计数器:预调整N计数器、后调整C计数器和反馈M计数器。

图1. Cyclone III PLL结构图结构图中高亮显示的模块表示Cyclone III PLL的用户编程部分,该部分给用户带来了很大的灵活性。

通过MegaWizard Plug-In Manager 配置PLL

通过MegaWizard Plug-In Manager 配置PLL

2014年4月23日 10:14

1.什么是PLL?

PLL(Phase-locked loops)中文翻译为锁相环,是一种通过反馈控制原理实现频率和香 味的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时 钟的频率和相位发生变化时,锁相环会检测到这种变化,并且通过其内部的反馈系统 来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

pll_ctrl exp_pll_inst ( //PLL模块例化 .areset ( !RST_n ), .inclk0 ( clk ), .c0 ( c0 ), .c1 ( c1 ), .locked ( locked ) ); endmodule /********************************/ 通过ModelSim进行仿真,通过运行仿真文件编写模板进行仿真文件编写,然后调用ModelSim进行 仿真,具体方法参见

• 源同步模式(In source-synchronous compensation Mode): 如果数据和时钟同时到达输入管脚, 那么在I/O单元输入寄存器的数据域时钟端口,数据和时钟之间的相位关系保持不变,下图为 源同步模式中数据域时钟之间的相位关系。

分区 FPGA 的第 4 页

• 零延时缓冲模式(In zero delay buffer mode):PLL外部时钟输出管脚的时钟信号和PLL输入时钟时 相位对齐的,没有延迟,内部时钟相对于输入时钟管脚有相位偏移,该模式下需要在输入时 钟和输出时钟上使用同一I/O标准,下图是零延迟缓冲模式下PLL时钟相位关系的范例波形。

分区 FPGA 的第 8 页

MEGA软件地使用

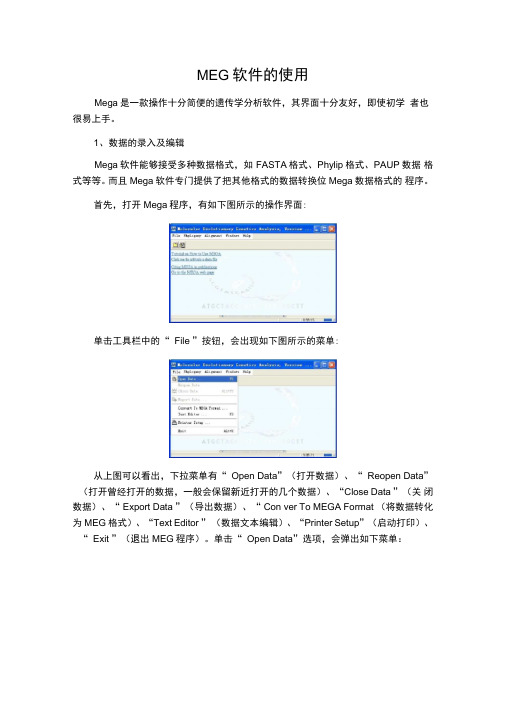

MEG软件的使用Mega是一款操作十分简便的遗传学分析软件,其界面十分友好,即使初学者也很易上手。

1、数据的录入及编辑Mega软件能够接受多种数据格式,如FASTA格式、Phylip格式、PAUP数据格式等等。

而且Mega软件专门提供了把其他格式的数据转换位Mega数据格式的程序。

首先,打开Mega程序,有如下图所示的操作界面:单击工具栏中的“ File ”按钮,会出现如下图所示的菜单:从上图可以看出,下拉菜单有“ Open Data”(打开数据)、“ Reopen Data”(打开曾经打开的数据,一般会保留新近打开的几个数据)、“Close Data ”(关闭数据)、“ Export Data ”(导出数据)、“ Con ver To MEGA Format (将数据转化为MEG格式)、“Text Editor ” (数据文本编辑)、“Printer Setup”(启动打印)、“ Exit ”(退出MEG程序)。

单击“ Open Data”选项,会弹出如下菜单:浏览文件,选择要分析的数据打开,单击“打开”按钮,会弹出如下操作界面:此程序操作界面,提供了三种选择数据选择:Nucleotide Sequences (核苷酸序列)、Protein Sequences (蛋白质序列)、Pairwise Distanee (遗传距离矩阵)。

根据输入数据的类型,选择一种,点击“ 0K”即可。

如果选择“ Pairwise Distanee ”,则操作界面有所不同;如下图所示:根据遗传距离矩阵的类型,如果是下三角矩阵,选择“ Lower Left Matrix ' 即可;如果是上三角矩阵,选择“ Upper Right Matrix ”即可。

点击“ OK按钮, 即可导入数据。

如果是核苷酸数据,则读完之后,会弹出如下对话框:如上图,如果是编码蛋白质的核苷酸序列,则选择“Yes”按钮;如果是不编码蛋白质的核苷酸序列,则点击“ No”按钮。

MegaWizard应用

MegaWizard Plug-In Manager工具提供了丰富的库函数,这些库函数专门针对Altera公司的器件进行优化,电路结构简单,并大大减少了设计者的工作量。

通过MegaWizard Plug-In Manager工具的向导,设计者可以利用Quartus II提供的库函数自定义功能宏块,并设置模块参数和可选端口数值。

1.运行工具向导在运行MegaWizard Plug-In Manager工具向导之前,应该先在磁盘建立一个工程目录。

1.1 选择Tools菜单中的“Mega Wizard Plug-In Manager”命令,打开工具向导。

在弹出的页面中选择“Create a new custom megafunction variation”选项。

1.2 单击【next】按钮,在弹出的向导页面中指定工程目录的位置以及文件名,并选择所需的宏功能模块。

1.3 单击【next】按钮,进入下一个向导页面,按页面提示指定输入数据和输出数据的位宽。

1.4 单击【next】按钮,在弹出的向导页面中按提示对输入数据和输出数据做进一步设置。

1.5 单击【next】按钮,进入下一个向导页面,按提示确定是否使用流水线方式工作。

1.6 单击【next】按钮,进入最后一个向导页面,该页面总结了前面步骤所生成的详细参数设置。

单击【finish】完成工具向导。

2.编译与测试和编译自己创建的普通工程一样对其进行编译,同样,完成之后可以测试是否正确。

以设计双端口RAM为例说明。

Step1:打开QuartusII,选择File—New Project Wizard,创建新工程,出现图示对话框,点击Next;Step2:创建工程存放目录、工程名和顶层文件名,工程名和顶层文件名保持一致topram2;Step3:选择器件类型;Step4:选择是否使用第三方工具,此处不使用;Step5:选择Tools—MegaWizard Plug-In Manager,创建新的MegaCore;Step6:选择memory compiler—RAM:2-PORT,输出文件类型,输出文件名称myram2;Step7:定义读写端口,RAM大小;Step8:定义输入数据宽度(此处为4),RAM深度(此处为16);Step9:选择读写时钟;Step10:定义输出锁存;Step11:选择是否进行初始化;Step12:显示创建的输出文件类型;Q2的Megawizard输出文件默认分类 2009-04-03 21:12:43 阅读53 评论0字号:大中小订阅文件描述说明*.bsf Q2原理图编辑器中使用的块符号文件*.cmp VHDL设计中使用的单元声明文件*.inc AHDL设计中使用的包含文件*.tdf 在 AHDL设计中实例化的封装文件只有语言选择AHDL 时才输出*.vhd 在VHDL设计中实例化的封装文件,或白盒网表文件只有语言选择VHDL 时才输出*.v 在Verilog设计中实例化的封装文件,或白盒网表文件只有语言选择Verilog时才输出*_bb.v 在Verilog设计中使用的只包含端口的黑盒文件用于第3方综合工具*_inst.vhd 在VHDL设计中实例化的摸板*_inst.tdf 在 AHDL设计中实例化的摸板*_inst.v 在Verilog设计中实例化的摸板有一些基本宏功能模块有一个可选的"白盒(clearbox)模式"(在Megawizard的page2).一般来说我们生成的宏功能模块都是以黑盒(blackbox)方式产生的,这样放到第三方综合工具综合时候,只需要把生成的封装文件声明为黑盒即可,第三方综合工具综合的时候也不会对模块内部的网表做优化,以白盒生成的宏模块,它生成的文件就不仅仅是一个封装文件,而是内部包含了许多详细的实现信息和特定的器件信息,这样的模块放到第三方综合工具综合,使综合工具对模块内部进行优化.。

MegaWizard应用

MegaWizard Plug-In Manager工具提供了丰富的库函数,这些库函数专门针对Altera公司的器件进行优化,电路结构简单,并大大减少了设计者的工作量。

通过MegaWizard Plug-In Manager工具的向导,设计者可以利用Quartus II提供的库函数自定义功能宏块,并设置模块参数和可选端口数值。

1.运行工具向导在运行MegaWizard Plug-In Manager工具向导之前,应该先在磁盘建立一个工程目录。

1.1 选择Tools菜单中的“M egaWizard Plug-In Manager”命令,打开工具向导。

在弹出的页面中选择“Create a new custom megafunction variation”选项。

1.2 单击【next】按钮,在弹出的向导页面中指定工程目录的位置以及文件名,并选择所需的宏功能模块。

1.3 单击【next】按钮,进入下一个向导页面,按页面提示指定输入数据和输出数据的位宽。

1.4 单击【next】按钮,在弹出的向导页面中按提示对输入数据和输出数据做进一步设置。

1.5 单击【next】按钮,进入下一个向导页面,按提示确定是否使用流水线方式工作。

1.6 单击【next】按钮,进入最后一个向导页面,该页面总结了前面步骤所生成的详细参数设置。

单击【finish】完成工具向导。

2.编译与测试和编译自己创建的普通工程一样对其进行编译,同样,完成之后可以测试是否正确。

以设计双端口RAM为例说明。

Step1:打开QuartusII,选择File—New Project Wizard,创建新工程,出现图示对话框,点击Next;Step2:创建工程存放目录、工程名和顶层文件名,工程名和顶层文件名保持一致topram2;Step3:选择器件类型;Step4:选择是否使用第三方工具,此处不使用;Step5:选择Tools—MegaWizard Plug-In Manager,创建新的MegaCore;Step6:选择memory compiler—RAM:2-PORT,输出文件类型,输出文件名称myram2;Step7:定义读写端口,RAM大小;Step8:定义输入数据宽度(此处为4),RAM深度(此处为16);Step9:选择读写时钟;Step10:定义输出锁存;Step11:选择是否进行初始化;Step12:显示创建的输出文件类型;Q2的Megawizard输出文件默认分类 2009-04-03 21:12:43 阅读53 评论0字号:大中小订阅文件描述说明*.bsf Q2原理图编辑器中使用的块符号文件*.cmp VHDL设计中使用的单元声明文件*.inc AHDL设计中使用的包含文件*.tdf 在AHDL设计中实例化的封装文件只有语言选择AHDL 时才输出*.vhd 在VHDL设计中实例化的封装文件,或白盒网表文件只有语言选择VHDL 时才输出*.v 在Verilog设计中实例化的封装文件,或白盒网表文件只有语言选择Verilog时才输出*_bb.v 在Verilog设计中使用的只包含端口的黑盒文件用于第3方综合工具*_inst.vhd 在VHDL设计中实例化的摸板*_inst.tdf 在AHDL设计中实例化的摸板*_inst.v 在Verilog设计中实例化的摸板有一些基本宏功能模块有一个可选的"白盒(clearbox)模式"(在Megawizard的page2).一般来说我们生成的宏功能模块都是以黑盒(blackbox)方式产生的,这样放到第三方综合工具综合时候,只需要把生成的封装文件声明为黑盒即可,第三方综合工具综合的时候也不会对模块内部的网表做优化,以白盒生成的宏模块,它生成的文件就不仅仅是一个封装文件,而是内部包含了许多详细的实现信息和特定的器件信息,这样的模块放到第三方综合工具综合,使综合工具对模块内部进行优化.。

MEGA软件的使用

MEGA软件的使用Mega是一款操作十分简便的遗传学分析软件,其界面十分友好,即使初学者也很易上手。

1、数据的录入及编辑Mega软件能够接受多种数据格式,如FASTA格式、Phylip格式、PAUP数据格式等等。

而且Mega软件专门提供了把其他格式的数据转换位Mega数据格式的程序。

首先,打开Mega程序,有如以下图所示的操作界面:单击工具栏中的“File”按钮,会出现如以下图所示的菜单:从上图可以看出,下拉菜单有“Open Data”〔打开数据〕、“Reopen Data”〔打开曾经打开的数据,一般会保留新近打开的几个数据〕、“Close Data”〔关闭数据〕、“Export Data”〔导出数据〕、“Conver To MEGA Format”〔将数据转化为MEGA格式〕、“Text Editor”〔数据文本编辑〕、“Printer Setup”〔启动打印〕、“Exit”〔退出MEGA程序〕。

单击“Open Data”选项,会弹出如下菜单:浏览文件,选择要分析的数据打开,单击“打开”按钮,会弹出如下操作界面:此程序操作界面,提供了三种选择数据选择:Nucleotide Sequences〔核苷酸序列〕、Protein Sequences〔蛋白质序列〕、Pairwise Distance〔遗传距离矩阵〕。

根据输入数据的类型,选择一种,点击“OK”即可。

如果选择“Pairwise Distance”,则操作界面有所不同;如以下图所示:根据遗传距离矩阵的类型,如果是下三角矩阵,选择“Lower Left Matrix”即可;如果是上三角矩阵,选择“Upper Right Matrix”即可。

点击“OK”按钮,即可导入数据。

如果是核苷酸数据,则读完之后,会弹出如下对话框:如上图,如果是编码蛋白质的核苷酸序列,则选择“Yes”按钮;如果是不编码蛋白质的核苷酸序列,则点击“No”按钮。

之后,会弹出如下操作窗口:此作界面的名称是“Sequence Data Explorer”,在其最上方是工具栏“Data”、“Display”、“Highlight”等,然后是一些数据处理方式的快捷按钮,在操作界面的左下方是每个序列的名称。

Quartus中宏功能模块的使用

图 10

2020/1/28

西安邮电学院计算机系

10

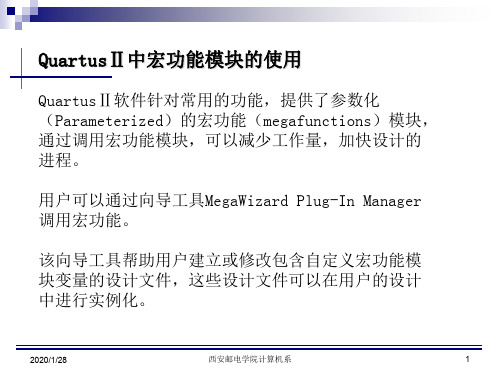

QuartusⅡ中宏功能模块的使用

2020/1/28

图 11 西安邮电学院计算机系

仿真与综合相关信息 11

QuartusⅡ中宏功能模块的使用

2020/1/28

图 12 西安邮电学院计算机系

选取输出的文件 .bsf 文件: 图形编辑器中使用的宏 功能模块符号 .v文件: Verilog HDL实例化的 宏功能模块包装文件

2020/1/28

西安邮电学院计算机系

15

完

2020/1/28

西安邮电学院计算机系

16

选择新建一个宏功能实例,进入下一步(图4)。

图3

2020/1/28

西安邮电学院计算机系

3

QuartusⅡ中宏功能模块的使用

这里列举了可供调用的宏功能模块

数学运算功能类,包括代码纠正、 浮点加/减/乘法器、计数器、平方根 等功能模块。

逻辑门类功能类,包括与/或/非门 常数发生器、反相器模块等。

I/O接口功能类,包括数据收发器 锁相环、I/O缓冲模块等。

该向导工具帮助用户建立或修改包含自定义宏功能模 块变量的设计文件,这些设计文件可以在用户的设计 中进行实例化。

2020/1/28

西安邮电学院计算机系

1

QuartusⅡ中宏功能模块的使用

在QuartusⅡ软件中使用MegaWizard Plug-In Manager对宏功能模块进行实例 化的步骤如下:

特别是针对一些与Altera器件底层结构相关的特性,必须通过Megafunction实现,例 如一些存储器模块(DPRAM、SPRAM、FIFO、CAM等),DSP模块,LVDS驱动器,PLL,高 速串行收发器(SERDERS),DDR输入/输出(DDIO)等。另外一些诸如乘法器、计数器、 加法器、滤波器等电路虽然也可以直接用代码描述,然后用通用逻辑资源实现,但是 这种描述方法不但费时费力,在速度和面积上与Megafunction的实现结果仍然有较大 的差距。

如何使用logisim

Logisim的简单入门一,准备工作参考:罗老板的计算机结构与组成课程/rjgcx/lzw/COD/Machine Structures. Spring 2010, UC Berkeley/~cs61c/sp10/软件环境:Logisim仿真软件(需要JAVA虚拟机)/~burch/logisim/QuartusII 8.1/硬件环境:PC机with Windows XPDE2开发板(DE2 Development and Education Board User Manual)参考书:anization.and.Design关于QuartusII的使用教程先来以一个与门电路的实验,来看一下基本的操作,在Logisim中一个与门电路生成过程如下:1.按与门的选择按钮,添加一个与门到电路中。

2.使用按钮添加一个输入引脚,用于设置输入电平。

3.添加一个引脚,通过属性中设置Pin的属性为输出:这样得到一个输出引脚。

4.移动以上添加的元素,得到原理图:注意选中按钮,此时可以拖拽连线,那么我们把电路各部分连接如下:5. 接下来通过选中按钮就可以鼠标点击设定输入管脚上的电平为1或0了,输出引脚也会相应改变,输出结果。

当然通过左下方的属性设定,还可以设定当前选择元件的朝向,数据位数,输入端口数等参数。

6.另外推荐大家后面设计的时候使用一下tunnel这个工具,代替复杂的连线,在后面复杂设计的地方,让你从蜘蛛网一样的连线中解脱出来,例如上面的电路可以这样表示:图中输入,与门模块,输出三部分结构分的很清晰,tunnel的使用使我们的电路设计更加规范,类似logisim中的tunnel工具在其他原理图工具中类似的工具是经常见到的,虽然名字会有不同,用途是一样的。

7.最后是子电路添加方法,选择Project--->Add Circuit…,如下图“:子电路的绘制与上面基本相同,注意的是输入输出引脚要连接Pin引脚,并设定好输入输出属性。

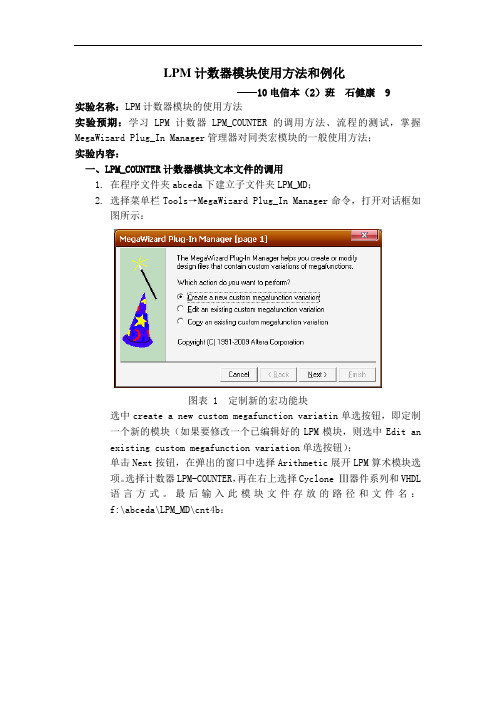

LPM计数器模块使用方法

LPM计数器模块使用方法和例化——10电信本(2)班石健康 9实验名称:LPM计数器模块的使用方法实验预期:学习LPM计数器LPM_COUNTER的调用方法、流程的测试,掌握MegaWizard Plug_In Manager管理器对同类宏模块的一般使用方法;实验内容:一、LPM_COUNTER计数器模块文本文件的调用1.在程序文件夹abceda下建立子文件夹LPM_MD;2.选择菜单栏Tools→MegaWizard Plug_In Manager命令,打开对话框如图所示:图表 1 定制新的宏功能块选中create a new custom megafunction variatin单选按钮,即定制一个新的模块(如果要修改一个已编辑好的LPM模块,则选中Edit an existing custom megafunction variation单选按钮);单击Next按钮,在弹出的窗口中选择Arithmetic展开LPM算术模块选项。

选择计数器LPM-COUNTER,再在右上选择Cyclone Ⅲ器件系列和VHDL语言方式。

最后输入此模块文件存放的路径和文件名:f:\abceda\LPM_MD\cnt4b:单击next按钮,弹出对话框。

选择4位计数器,选择“Creat an updown input…”使计数器有加减控制功能。

单击next按钮,打开对话框,选择Modulus…12,则表示模12计数器,从0记到11(若选择Plain binary则表示是普通的二进制计数器)。

然后选择时钟使能控制Clock Enable和进位输出Carry-out,如图:7.再单击next按钮,打开对话框,选择4位数据同步加载控制Load和异步清零控制Clear,如图:8.再按next按钮结束设置。

二、例化1)生成的LPM计数器模块VHDL源程序cnt4b如下:LIBRARY ieee;USE lpm;USE ;ENTITY cnt4b ISPORT(aclr : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);sload : IN STD_LOGIC ;updown : IN STD_LOGIC ;cout : OUT STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );END cnt4b;ARCHITECTURE SYN OF cnt4b ISSIGNAL sub_wire0 : STD_LOGIC ;SIGNAL sub_wire1 : STD_LOGIC_VECTOR (3 DOWNTO 0);COMPONENT lpm_counterGENERIC (lpm_direction : STRING;lpm_modulus : NATURAL;lpm_port_updown : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT (sload : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;aclr : IN STD_LOGIC ;clock : IN STD_LOGIC ;cout : OUT STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);updown : IN STD_LOGIC);END COMPONENT;BEGINcout <= sub_wire0;q <= sub_wire1(3 DOWNTO 0);lpm_counter_component : lpm_counterGENERIC MAP (lpm_direction => "UNUSED",lpm_modulus => 12,lpm_port_updown => "PORT_USED",lpm_type => "LPM_COUNTER",lpm_width => 4)PORT MAP (sload => sload,clk_en => clk_en,aclr => aclr,clock => clock,data => data,updown => updown,cout => sub_wire0,q => sub_wire1);END SYN;它调用了更底层的文件lpm_counter,同时可以作为一个底层元件被上一层设计调用或例化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

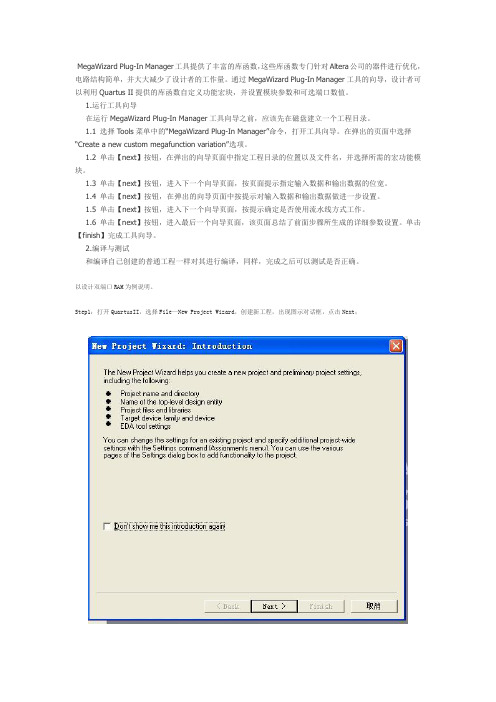

MegaWizard Plug-In Manager工具提供了丰富的库函数,这些库函数专门针对Altera公司的器件进行优化,电路结构简单,并大大减少了设计者的工作量。

通过MegaWizard Plug-In Manager工具的向导,设计者可以利用Quartus II提供的库函数自定义功能宏块,并设置模块参数和可选端口数值。

1.运行工具向导

在运行MegaWizard Plug-In Manager工具向导之前,应该先在磁盘建立一个工程目录。

1.1 选择Tools菜单中的“M egaWizard Plug-In Manager”命令,打开工具向导。

在弹出的页面中选择“Create a new custom megafunction variation”选项。

1.2 单击【next】按钮,在弹出的向导页面中指定工程目录的位置以及文件名,并选择所需的宏功能模块。

1.3 单击【next】按钮,进入下一个向导页面,按页面提示指定输入数据和输出数据的位宽。

1.4 单击【next】按钮,在弹出的向导页面中按提示对输入数据和输出数据做进一步设置。

1.5 单击【next】按钮,进入下一个向导页面,按提示确定是否使用流水线方式工作。

1.6 单击【next】按钮,进入最后一个向导页面,该页面总结了前面步骤所生成的详细参数设置。

单击【finish】完成工具向导。

2.编译与测试

和编译自己创建的普通工程一样对其进行编译,同样,完成之后可以测试是否正确。

以设计双端口RAM为例说明。

Step1:打开QuartusII,选择File—New Project Wizard,创建新工程,出现图示对话框,点击Next;

Step2:创建工程存放目录、工程名和顶层文件名,工程名和顶层文件名保持一致topram2;

Step3:选择器件类型;

Step4:选择是否使用第三方工具,此处不使用;

Step5:选择Tools—MegaWizard Plug-In Manager,创建新的MegaCore;

Step6:选择memory compiler—RAM:2-PORT,输出文件类型,输出文件名称myram2;

Step7:定义读写端口,RAM大小;

Step8:定义输入数据宽度(此处为4),RAM深度(此处为16);

Step9:选择读写时钟;

Step10:定义输出锁存;

Step11:选择是否进行初始化;

Step12:显示创建的输出文件类型;

Q2的Megawizard输出文件

默认分类 2009-04-03 21:12:43 阅读53 评论0字号:大中小订阅

文件描述说明

*.bsf Q2原理图编辑器中使用的块符号文件

*.cmp VHDL设计中使用的单元声明文件

*.inc AHDL设计中使用的包含文件

*.tdf 在AHDL设计中实例化的封装文件只有语言选择AHDL 时才输出*.vhd 在VHDL设计中实例化的封装文件,或白盒网表文件只有语言选择VHDL 时才输出*.v 在Verilog设计中实例化的封装文件,或白盒网表文件只有语言选择Verilog时才输出

*_bb.v 在Verilog设计中使用的只包含端口的黑盒文件用于第3方综合工具

*_inst.vhd 在VHDL设计中实例化的摸板

*_inst.tdf 在AHDL设计中实例化的摸板

*_inst.v 在Verilog设计中实例化的摸板

有一些基本宏功能模块有一个可选的"白盒(clearbox)模式"(在Megawizard的page2).一般来说我们生成的宏功能模块都是以黑盒(blackbox)方式产生的,这样放到第三方综合工具综合时候,只需要把生成的封装文件声明为黑盒即可,第三方综合工具综合的时候也不会对模块内部的网表做优化,以白盒生成的宏模块,它生成的文件就不仅仅是一个封装文件,而是内部包含了许多详细的实现信息和特定的器件信息,这样的模块放到第三方综合工具综合,使综合工具对模块内部进行优化.。