基于McBSP实现DSPs与串行AD_DA的接口设计

基于DSP的McBSP串口操作(汇编语言)

McBSP串口操作一、实验目的1.学习C54x的McBSP串口的控制和使用;2.利用VC5402的McBSP串口实现数据的收发;二、实验原理所有的 TMS320C54x 都提供了串口,大多数都支持缓冲串口。

BSP 串行接口能与串行设备,如编/译码器,串行A/D 和D/A 转换器等直接通信。

BSP 支持8,10,12 或16-bit数据单元的发送,同时允许程控串口通讯的时钟频率。

从VC5402 开始,TMS32054x 提供了统一的多通道缓冲串口McBSP。

McBSP 串口是基于TMS320C2X、C20X、C5X、C54X 的标准串口上扩展的,McBSP 提供:·全速双工通信·双缓存发送和三缓存接收数据寄存器,以支持连续传送·收和发使用独立的帧和时钟·直接与多媒体数字信号编解码器的工业标准接口,以及有模拟接口和与串行ADC/DAC 的接口·外部变速时钟发生器,内部可编程时钟发生器此外,McBSP 还有下列功能:·直接与下列格式接口_ T1/E1 framers_ MVIP switching compatible and ST-BUS compliant devices including:_ MVIP framers_ H.100 framers_ SCSA framers_ IOM-2 compliant devices_ AC97 compliant devices_ IIS compliant devices_ SPI_ devices·多通道收发,通道数达 128·字宽可选: 8, 12, 16, 20, 24, and 32 bits· U-Law and A-Law 压缩与扩展· 8 位传输时可选先传: LSB or MSB·帧信号与时钟信号极性可编程1. McBSP 概述McBSP 原理图如图9.1所示。

TMS320VC5402与串行ADDA转换器的接口设计

TMS320VC5402与串行AD/DA转换器的接口设计ΞDesign of the Interface B et w een TMS320VC5402and Serial AD/DA Converter张秀丽,李 萍,陆光华(浙江万里学院DSP重点实验室 浙江宁波315100)【摘 要】 从软件和硬件两个方面设计了一种简单、实用的DSP与串行AD/DA转换器的接口电路。

该方法中AD/DA转换器与McBSP串行口直接相连,不需要占用并行数据总线,避免了总线冲突。

此方法已成功应用于各种速率的数据采集与处理系统中。

关键词:DSP,AD/DA转换器,多通道串行口【Abstract】 This paper designs a simple and practical interface between serial AD/DA converter and DSP.In this design,the AD/DA converter is directly connected to the serial port McBSP,not occupying DSP’s parallel data bus and will avoid from bus interference.The technology derived in this paper has been successfully applied in data acquisition and processing systems with several rates.K eyw ords:DSP,AD/DA converter,multi2channel serial port1 引 言TLC320AD50C是TI公司生产的高性能16bit串行AD/DA转换器,具有16种可编程的采样频率,最低采样频率为250Hz,最高采样频率可达80kHz。

TMS320VC5402(以下简称VC5402)是TI公司生产的一种性能优越的16bit定点DSP,它具有运算速度快、通用性强、接口连接方便等特点,重要的是它具有两个可以采用外部时钟信号的McBSP口(多通道缓冲串行口),完全可以与TLC320AD50C连接完成各种速率数据采集。

基于McBSP实现DSPs与串行AD_DA的接口设计

第30卷第5期2009年5月微 计 算 机 应 用M I CROCOMP UTER APP L I CATI O NSVol130No15M ay12009基于M c BSP实现D SPs与串行AD/DA的接口设计杨 雪 牟燕妮(北京强度环境研究所 北京 100076)摘要:重点介绍了利用DSPs的多通道缓冲串口Mc BSP实现与A/D、D/A串行接口的设计。

TI公司T MS320C67x系列DSPs的Mc BSP有两种配置方式,一种是配置成串口的模式,一种是配置成通用I/O的模式,本文分别用这两种模式进行了A/D和D/ A接口的设计,其硬件及软件的实现方法简单、方便,可节省程序代码空间和CP U运行时间。

关键词:M cBSP T M S320C67x A/D D/AI n terface D esi gn between the D S PCh i Pand Ser i a l AD/DA Ba sed on M c BSPY ANG Xue,MU Yanni(Beijing I nstitute of Strength and Envir on ment Engineering,Beijing,100076,China)Abstract:This paper p resents the interface design bet w een M c BS Pand A/D、D/A.There are t w o M c BS Pconfigurati on:one is con2 figured as serial model;The other is configured as common I/O model.I n this paper,these t w o models were used t o carry out the A/D and D/A interface design.Its hard ware circuit and s oft w are p r ogra mm ing are si m p le,s o it can econom ize p r ogra m code s pace and CP U running ti m e.Keyword:Mc BSP,T M S320C67x,A/D,D/A随着数字化的飞速发展,数字信号处理已经成为一个核心的概念。

基于DSP的McBSP串口操作源程序(汇编语言)

McBSP串口操作源程序;----------------------------------------------------------------; This program use McBSP1 sent SINE table.The table is in VC5402'; ROM.So, the program move the talbe to xbuffer first, then send; them from McBSP1.The rbuffer use to save recived data !;----------------------------------------------------------------.title "for test BSP program (Transmit) ".mmregs.global _c_int00,int_send,int_rev;----------define serial control registers' address--------DRR10 .set 0x0021 ; McBSP0 data receive register 1 DRR11 .set 0x0041 ; McBSP1 data receive register 1 DRR12 .set 0x0031 ; McBSP2 data receive register 1 DXR10 .set 0x0023 ; McBSP0 data transmit register 1 DXR11 .set 0x0043 ; McBSP1 data transmit register 1 DXR12 .set 0x0033 ; McBSP2 data transmit register 1 MCBSP0_SPSA .set 0x0038MCBSP0_SPSD .set 0x0039MCBSP1_SPSA .set 0x0048 ; serial 1MCBSP1_SPSD .set 0x0049 ; serial 1MCBSP2_SPSA .set 0x0034MCBSP2_SPSD .set 0x0035MCBSP_SPCR1_SUB_ADDR .set 0x0000MCBSP_SPCR2_SUB_ADDR .set 0x0001MCBSP_RCR1_SUB_ADDR .set 0x0002MCBSP_RCR2_SUB_ADDR .set 0x0003MCBSP_XCR1_SUB_ADDR .set 0x0004MCBSP_XCR2_SUB_ADDR .set 0x0005MCBSP_SRGR1_SUB_ADDR .set 0x0006MCBSP_SRGR2_SUB_ADDR .set 0x0007MCBSP_MCR1_SUB_ADDR .set 0x0008MCBSP_MCR2_SUB_ADDR .set 0x0009MCBSP_RCERA_SUB_ADDR .set 0x000aMCBSP_RCERB_SUB_ADDR .set 0x000bMCBSP_XCERA1_SUB_ADDR .set 0x000cMCBSP_XCERA2_SUB_ADDR .set 0x000dMCBSP_PCR_SUB_ADDR .set 0x000estack_size .set 100htemp .usect ".var",1 ; temp is in 60h-7fh, dp=0;send_ptr .usect ".var",1 ; save sent buf ptrrev_ptr .usect ".var",1 ; save rev buf ptrisnew .usect ".var",1 ;xbuffer .usect ".xbuf",256rbuffer .usect ".rbuf",256.bss addr_stack,stack_size.text_c_int00:ssbx intm ; disable all interrupt !stm #2028h,PMST ; vector in 2000hstm #addr_stack+stack_size,sp ; init SPstm #0c00h,IMR ; enable serial_1 sendstm #xbuffer,ar0rpt #255mvpd #0fe00h,*ar0+ ; move sine tabel to xbuffer !stm #rbuffer,ar0rpt #255st #0,*ar0+ ; clear rev_buffer to 0stm #xbuffer,send_ptrstm #rbuffer,rev_ptrstm #256,bk ; circular buffer size=256;******************************************************************; The following codes are used to initalize McBSP1 !; When Transmit, this DES5402PP makes CLK,FS ! the other; DES5402PP receives the CLK,FS !;****************************************************************** stm #0,MCBSP1_SPSA ; choose SPCR11stm #2000h,MCBSP1_SPSD ; receive sign_extend in DRRstm #1,MCBSP1_SPSA ; choose SPCR20stm #100h,MCBSP1_SPSD ;stm #2,MCBSP1_SPSA ; choose RCR10stm #40h,MCBSP1_SPSD ; 16 bits each wordstm #3,MCBSP1_SPSA ; choose RCR20stm #40h,MCBSP1_SPSDstm #4,MCBSP1_SPSA ; choose XCR10stm #40h,MCBSP1_SPSD ; 16 bits each wordstm #5,MCBSP1_SPSA ; choose XCR20stm #0,MCBSP1_SPSDstm #6,MCBSP1_SPSA ; choose SRGR1stm #1C8h,MCBSP1_SPSD ; CLKG=100M /200=500Kstm #7,MCBSP1_SPSA ; choose SRGR2stm #2000h,MCBSP1_SPSD ; Sample rate generator clock derived from CPU clock; 0x8,0x9,0xa,0xb,0xc,0xd all = 0x0stm #0eh,MCBSP1_SPSA ; choose PCR0stm #0a0eh,MCBSP1_SPSDrpt #0ffhnopstm #0h,MCBSP1_SPSAstm #2001h,MCBSP1_SPSD ; enable recive !stm #1,MCBSP1_SPSAstm #1c1h,MCBSP1_SPSD ; enable transmit !stm #0,DXR11;------ init serial port 1 end -----------------------------rsbx intm ; enable all int,again:nopnopb againnop;-------------------------------------------------------------; interrupt for INT_BXINT !;-------------------------------------------------------------int_send:pshm st0pshm st1pshm ar2ld #0,dpmvdk send_ptr,ar2 ; restore send ptr !mvdk *ar2+%, DXR11 ; send data to serial portnopnopmvmd ar2,#send_ptr ; save send ptr !popm ar2popm st1popm st0rete;-------------------------------------------------------------; interrupt for INT_BRINT !;-------------------------------------------------------------int_rev:pshm st0pshm st1pshm ar2ld #0,dpmvdk rev_ptr,ar2 ; restore rev ptr !ld DRR11,astl a,-1,*ar2+% ; save data to rev_buf; nop; nopmvmd ar2,#rev_ptr ; save rev ptr !cmpm ar2,#0400hbc con,ntcnop ; set breakpoint here !nop ; show wave in 0x200 and 0x400con:popm ar2popm st1popm st0rete.end中断向量文件vectors.asm:.sect ".vectors".ref _c_int00 ; C entry point.global int_send,int_rev.align 0x80 ; must be aligned on page boundary RESET: ; reset vectorB _c_int00 ; branch toC entry pointnopnopnmi: RETE ; enable interrupts and return from oneNOPNOPNOP ; software interruptssint17 .space 4*16sint18 .space 4*16sint19 .space 4*16sint20 .space 4*16sint21 .space 4*16sint22 .space 4*16sint23 .space 4*16sint24 .space 4*16sint25 .space 4*16sint26 .space 4*16sint27 .space 4*16sint28 .space 4*16sint29 .space 4*16sint30 .space 4*16int0: RETENOPNOPNOPint1: RETENOPNOPNOPint2: RETENOPNOPNOPtint0: RETENOPNOPNOPrint0: RETENOPNOPNOPxint0: RETENOPNOPNOPdmac0: RETENOPNOPNOPtint1: RETENOPNOPNOPint3: RETENOPNOPNOPhpint: RETENOPNOPNOPrint1: b int_revNOPNOPxint1: b int_sendNOPNOP.end链接命令文件:MEMORY{PAGE 0: EPROG: origin = 0x2080, len = 0x1f80 VECT: origin = 0x2000, len = 0x80 PAGE 1: USERREGS: origin = 0x60, len = 0x1c BIOSREGS: origin = 0x7c, len = 0x4IDA TA: origin = 0x80, len = 0x1f80EDATA: origin = 0x2000, len = 0x8000 }SECTIONS{.vectors: {} > VECT PAGE 0.sysregs: {} > BIOSREGS PAGE 1.trcinit: {} > EPROG PAGE 0.gblinit: {} > EPROG PAGE 0.bios: {} > EPROG PAGE 0frt: {} > EPROG PAGE 0.text: {} > EPROG PAGE 0.cinit: {} > EPROG PAGE 0.pinit: {} > EPROG PAGE 0.sysinit: {} > EPROG PAGE 0.bss: {} > IDA TA PAGE 1.far: {} > IDA TA PAGE 1.const: {} > IDATA PAGE 1.switch: {} > IDATA PAGE 1.sysmem: {} > IDATA PAGE 1.cio: {} > IDA TA PAGE 1.MEM$obj: {} > IDA TA PAGE 1.sysheap: {} > IDATA PAGE 1.xbuf align(512): {} > IDATA PAGE 1 .rbuf align(512): {} > IDA TA PAGE 1 .var {} > USERREGS PAGE。

DSP与串行AD73360AD转换器接口设计(精)

DSP与串行AD73360A/D转换器接口设计DSP与串行AD73360A/D转换器接口设计类别:单片机/DSP来源:电子技术应用作者:何学辉苏涛摘要:讨论了TI公司的数字信号处理器TMS320VC5402的多通道缓冲串口与串行A/D变换器AD73360的接口设计,详细阐述了两者的硬件接口和软件实现。

关键词:多通道缓冲串口TMS320VC5402DSPAD73360A/D转换器随着对信号处理要求的不断提高以及DSP技术的不断发展,越来越多的工程技术人员开始采用DSP进行系统设计。

美国TI公司的TMS320VC5402(以下简称VC5402)DSP具有运算速度快、功耗小和性价比高的特点,已在个人移动通信、信号与信息处理以及自动控制等领域得到了广泛的应用。

该芯片提供了两个多通道缓冲串行接口(McBSP)与外部设备进行通信。

它与串行A/D变换器构成的信号采集与处理系统具有硬件设计简单、可靠性好的特点。

本文将详细阐述VC5402与AD73360的接口设计。

1VC5402的McBSPVC5402的McBSP是一种同步串行接口,支持多种通信方式和SPI协议,该串口可以根据设计者的不同需求进行配置,使用非常灵活。

它的主要特点如下:全双工的串行通信;连续的发送和接收数据流功能;具有外部时钟输入或内部可编程时钟两种时钟控制方式;可独立编程的发送和接收帧同步;多通道数据传输(最多可达128个通道);可选的数据宽度:8、12、16、20、24或32位;用于数据压缩的μ律和A律压缩扩展;可编程的时钟和帧同步极性。

McBSP包括6个引脚,分别是串行数据发送信号DX、串行数据接收信号DR、发送时钟信号CLKX、接收时钟信号CLKR、发送帧同步信号FSX和接收帧同步信号FSR。

由于McBSP内带有一个可编程的采样和帧同步时钟产生器,所以串口接收、发送时钟和帧同步等信号既可由内部产生,也可以由外部输入。

VC5402的McBSP由23个寄存器进行控制,除了少数几个不能由程序访问之外,一般在串口进行数据通信之前都要对它们进行初始化,部分寄存器是存储器映射寄存器,必须通过子地址的方式进行访问。

基于McBSP实现DSP与串行Flash之间的接口通讯

基于McBSP实现DSP与串行Flash之间的接口通讯

孟勃;朱明

【期刊名称】《电子器件》

【年(卷),期】2006(029)003

【摘要】利用多通道缓冲串口McBSP0实现了TMS320VC5509 DSP与外部串行Flash之间的SPI通讯.完成了用DSP控制Flash进行在线系统编程.有效地降低了系统设计的复杂性,节省了空间.重点介绍了McBSP与Flash之间串行接口的设计,并介绍了TMS320VC5509串行8位引导装载的实现方法.同时给出用CSL库函数实现McBSP配置的程序.

【总页数】5页(P920-924)

【作者】孟勃;朱明

【作者单位】中国科学院,研究生院,北京,100039;中国科学院,长春光学精密机械与物理研究所,长春,130033;中国科学院,长春光学精密机械与物理研究所,长

春,130033

【正文语种】中文

【中图分类】TN91

【相关文献】

1.基于McBSPs实现TMS320C6000系列DSPs异步串行通信 [J], 商丹;高永清;陈义平

2.DSP同步串行口和PC机之间异步通讯的实现方法 [J], 徐彦峰;徐睿

3.C6000与C2000系列DSP之间串行数据通讯的研究与实现 [J], 韩开亮;张涛

4.TMS320C54XX系列DSP的McBSP串行接口技术及应用 [J], 马庆春;迟宝全

5.基于McBSP实现DSPs与串行AD/DA的接口设计 [J], 杨雪;牟燕妮

因版权原因,仅展示原文概要,查看原文内容请购买。

基于McBSPs实现TMS320C6000系列DSPs异步串行通信

文章编号:1009-671X (2004)05-0031-03基于McBSPs 实现T MS320C6000系列DSPs 异步串行通信商 丹1,高永清1,2,陈义平1(1.黑龙江科技学院自动化工程系,黑龙江哈尔滨 150027;2.中国矿业大学机电与信息学院,北京 100083)摘 要:为解决T MS320C6000系列DSPs 的异步串行通信能力,提出一种新的解决方案,即利用多通道缓冲串行接口(McBSPs )与专用串行异步收发器来扩展异步串行接口.其硬件电路及软件编程简单、方便,可节省程序代码空间和CPU 运行时间,是一种使用广泛的串行总线接口标准.通过对应用系统的配置,可支持多种速率和多种方式的SPI ,可以方便地用于各种不同的SPI 设备.关 键 词:McBSPs ;T MS320C6000;异步串行通信;串行外围接口中图分类号:TP911.3 文献标识码:A收稿日期:2003-08-12.作者简介:商 丹(1974-),女,讲师,主要研究方向:DSP 与单片机应用技术.R ealization of TMS 320C 6000’s UART communication based on McBSPsSHANG Dan 1,G AO Y ong 2qing 1,2,CHE N Y i 2ping 1(1.Dept.of Auto 2engineering ,Heilongjiang Institute of Science and T echnology ,Harbin 150027,China ;2.C ollege of Engine and E lec 2tronic C ommunication ,China University of M ining and T echnology ,Beijing 100083,China )Abstract :In order to s olve the capacity for T MS320C6000’s UART communication ,a new scheme was presented for expanding UART interface by using multi channel bu ffered serial ports and dedicated chip of asynchronous communi 2cations transceiver .And its hardware circuit and s oftware programming are sim ple and convenient ,s o it can econo 2mize program code space and CPU running time.It is a s ort of standard of serial bus interface used widely.Throughconfiguration of the application system ,it can support serial peripheral interface (SPI ),which com prises various kinds of speeds and m odes ,and can be used for all kinds of SPI equipment conveniently.K ey w ords :McBSPs ;T MS320C6000;UART communication ;SPI 随着数字信号处理(DSP )技术的快速发展,数字信号处理器(DSPs )由于具有很强的数据处理能力而使其在视频信号处理方面得到广泛的应用.在DSP 应用系统设计中,包括硬件电路和软件编程的设计.在硬件电路设计中,通信接口的好坏直接影响着应用系统的性能.美国德州仪器(TI )公司生产的T MS320C6000系列DSPs 芯片提供了一个或多个串行接口,然而这一系列芯片没有提供通用异步串行接口(UART ),只提供同步串行接口.在实际的应用系统中,也需要DSPs 能够与外设进行异步串行通信.因此,实现T MS320C6000系列DSPs 芯片异步串行接口的通信能力就显得至关重要.1 方案提出综合分析DSP 应用系统中扩展异步串行接口的方法,大体上有3种:一是利用软件编程来实现,此时要借用DSPs 的McBSP 和DMA ,而不扩展任何硬件,这种方法的特点是硬件电路简单,但软件复杂,增大了CPU 的负担,影响数据处理及传送的速率,所以不适合应用通信数据量大的场合.二是利用专用的异步串口芯片,在DSPs 的并行总第31卷第5期 应 用 科 技 V ol.31,№.52004年5月 Applied Science and T echnology May 2004线上进行扩展,是一种用硬件实现异步数据的传输,其特点是软件实现简单,但是在总线上扩展了异步串口芯片,使目标系统复杂化[1].三是利用数字信号处理器(DSPs )的多通道缓冲串行接口(McBSPs ),在扩展适当硬件的情况下,将同步数据转换为异步数据进行传输,这样就充分利用DSPs 的片上资源,使硬件电路尽量简单化.虽然它能够支持SPI 接口,但是它没有通用异步串行接口(UART ).综合考虑以上3种方法的特点,为实现硬件连接简单方便,软件编程容易,笔者采用第三种方法,并且利用MAXI M 公司的专用串行异步收发器(MAX3110E ),与DSPs 的McBSPs 直接连接.由于异步数据的发送和接收由MAX3110E 以硬件实现,所以软件编程只需要考虑的是DSPs 与MAX3110E 之间的同步数据通信.这样,用最简单的硬件连接和软件编程就能实现同步到异步的串行数据格式转换.2 串行异步通信芯片MAX3110E2.1 MAX3110E 的主要引脚MAX3110E 的引脚图如图1所示.图1 M AX 3110E 的引脚图2.2 MAX3110E 的工作配置MAX3110E 包括一个简单的UART 、SPI 接口、波特率发生器和一个中断发生器,能通过“写配置寄存器”完成波特率、字长、校验、8字节接收FIFO的设定并选择通用UART 方式或IrDA 方式,控制节电状态和4个中断服务.其写配置寄存器时序如图2所示.MAX3110E 有4个中断源:校验(Pr )、接收数据(R )、接收开始/帧错误(RA/FE )和发送缓存空(T ),每个中断源可以被屏蔽.图2 写配置寄存器时序3 T MS320C6000系列DSP 芯片的McBSPs 的功能与特点[2,3]3.1 McBSPs 的功能McBSPs 是在标准串行接口的基础上对功能进行扩展的,除具有标准串口的功能特点外,其灵活性体现在如下几个方面:1)两级缓冲区发送,三级缓冲区接收,允许连续数据流传输;2)可与SPI 、ST -BUS 、T 1/E1、AC97、MVIP 等兼容设备直接接口;3)可编程帧同步、数据时钟极性,支持外部移位时钟或内部频率可编程移位时钟;4)拥有相互独立的数据发送和接收帧同步脉冲和时钟信号;5)多通道发送和接收,最多可达256个通道,速度可高达200Mbit/s.3.2 McBSPs 的SPI 方式T MS320C6000系列DSP 芯片的McBSPs 串口工作于时钟停止模式时与SPI 协议兼容.当将McBSPs 配置为时钟停止模式时,发送器和接收器在内部得到同步,这时McBSPs 可作为SPI 的主设备或从设备.发送时钟信号(C LK X )对应于SPI 协议中的串行时钟信号(SCK ),发送帧同步信号对应于从设备使能信号(/CS ).在这种方式下对接・23・应 用 科 技 第31卷收时钟信号(C LK R )和接收帧同步信号(FSR )将不进行连接,因为它们在内部与C LK X 和FSX 相连接.4 SP 芯片的McBSPs 与MAX3110E的接口电路设计T MS320C6000系列DSP 芯片的McBSPs 工作于SPI 模式时可直接与MAX3110E 进行连接,从而实现与RS -232设备进行异步数据传输.此时DSP 作为SPI 协议中的主设备,其接口电路如图3所示.DSP 芯片的发送时钟信号(C LK X )作为MAX3110E 的串行时钟输入,发送帧同步脉冲信号(FSX )作为MAX3110E 的片选信号(/CS ).DX与DI N 连接作为发送数据线,DR 与DOUT 连接作为接收数据线.MAX3110E 的TX 与T 1I N 连接,RX 与R1OUT 连接,以便利用其片内的转换器实现UART 到RS 2232电平的转换.MAX3110E的中断信号(/IRQ )与DSP 芯片的外部中断相连.图3 McBSPs 与M AX 3110E 的接口电路 在SPI 串行协议中,主设备提供时钟信号并控制数据传输过程.MAX3110E 接口电路数据传输时序图如图4所示,由图4可知,必须设置DSP 的McBSPs 于适当的方式才能保证与MAX3110E 的时序相配合.图4 M AX 3100E 数据传输时序 MAX3110E 要求在数据传输过程中/CS 信号必须为低电平,在传输完毕后必须为高电平.此信号由McBSPs 的FSX 引脚提供,因此必须正确设置DSP 的帧脉冲发生器,使之在每个数据包传输期间产生帧同步脉冲,即在数据包传输的第一位变为有效状态,然后保持此状态直到数据包传输结束.McBSPs 的采样率发生器产生适当频率的时钟信号,由C LK X 引脚输出,保证主从设备间的同步数据传输.因此必须正确设置DSP 的采样率发生器时钟源C LK S M 和时钟分频因子C LKG DV.根据SPI 传输协议,必须正确设置数据发送延迟时间(X DAT D LY ).由图4可知MAX3110E 要求在SC LK 变高之前的半个时钟周期开始传输数据.所以必须为McBSPs 选择合适的时钟方案,即设置McBSPs 的时钟停止模式.在本应用中采用McB 2SPs 的时钟停止模式2:C LK STP =11b ,C LK XP =0,表示为时钟高有效,有延时,McBSPs 在C LK X 上升沿的半个时钟周期之前发送数据,在C LK R 的上升沿读取数据.这样即可保证与MAX3110E 的时序相配合.5 通信电路的软件设计通信电路的软件主要包括McBSPs 作为SPI 的初始化、McBSPs 寄存器的配置、MAX3110E 工作模式及波特率的配置[5].5.1 McBSPs 作为SPI 的初始化1)设置SPCR2的XRST 和SPCR1的RRST 为0,进行McBSPs 的复位;2)设置McBSPs 的主从模式有其他相关参数;3)设置SPCR2的G RST ,对采样率发生器进行复位;(下转第50页)・33・第5期 商 丹,等:基于McBSPs 实现T MS320C6000系列DSPs 异步串行通信点,同时通过在局部公式中设置σ0×Δ来计算刷新链路(u,v)上新的信息素强度(此时信息素处于挥发操作),并且转到第5)步.否则,进行下一步.7)如果链路(u,v)上带宽满足,则蚂蚁分组被发送到节点v,同时刷新ant.con,并记录蚂蚁经过链路(u,v)所用的时间t k(u,v),进行下一步.否则,蚂蚁返回到前一个节点,并利用局部公式刷新链路上的信息素强度,转到第5)步.8)如果ant.time+t k(u,v)≤D w,则利用局部公式刷新链路上的信息素强度,同时刷新蚂蚁分组中的每个域;否则,蚂蚁死亡(丢弃蚂蚁分组),并利用局部公式刷新链路(u,v)上的信息素强度,转到下一步.9)节点v作为当前节点转到第5)步,重复以上过程.10)如果k≥m,算法结束.表明网络不能满足连接请求,拒绝连接请求.否则,选择在源节点释放第k+1只蚂蚁,重复以上步骤.3 结 论本文根据蚂蚁算法提出了一个解决多限制Q oS路由的DQRAM M算法,针对网络中的延时、抖动、带宽、包丢失和最小费用等约束条件设计.该算法也容易扩展到组播路由的情况.参考文献:[1]DORIG O M,G AM BARDE LLA L M.Ant colony system:acooperative learning approach to the traveling salesman prob2 lem[J].IEEE T rans on Ev olutionary C om putation,2001(2): 53-56.[2]W ANG Z,CROWCROFT J.Quality of service routing forsupporting multimedia applications[J].JS AC,2000(7): 1228-1234.[责任编辑:李雪莲](上接第33页) 4)等待2个采样率发生器的时钟周期,使McBSPs处于稳定状态;5)选择配置由CPU或DMA控制McBSPs,然后将XRST和RRST设置为1;6)等待两个采样率发生器的时钟周期,使McBSPs处于稳定状态.5.2 McBSPs寄存器的配置C LK X M=1(PCR),BC LK X为输出.C LK S M=1(SRG R2),采样率发生器时钟来源于CPU.C LKG DV=29(SRG R1),采样率发生器分频数为30,串行时钟周期为300ns.FSX M=1(PCR),FSX为输出.FSG M=0(SRG R2),FSX在每次包传输时被激活.FSXP=1(PCR),FSX低有效.X DAT D LY=01b(XCR2),发送时钟延时为1.RDAT D LY=01b(RCR2),接收帧延时为1.C LK STP=11(SPCR1),时钟停止模式2,有延时,数据接收在上升沿.C LK XP=0(PCR),发送数据在时钟上升沿.RW D LE N1=010b(RCR1),发送包长为16位数据.XW D LE N1=010b(XCR1),接收包长为16位数据.5.3 MAX3110E工作模式及寄存器的配置在对整个系统进行初始化时,DSP必须根据命令序列格式向MAX3110E写入配置命令字,才能进行正确的数据通信.如波特率为19200、8位数据位、无奇偶校验位、一位停止位、使能接收和发送中断的异步数据传输.需要向MAX3110E写入配置命令字为:0xCC0A.6 结束语本文扩展的T MS320C6000系列DSPs异步串行接口,充分利用了DSPs的片上硬件资源,通过简单的硬件电路将同步串行接口转换为异步串行接口,很好在解决了DSPs的异步串行通信问题.此种方法经过实践证明,在多种速率下(300-230K bps),可以实现数字信号处理器与外设快速、可靠、远距离通信.参考文献:[1]利用T L16C750实现DSP与PC机的高速串行通信[J].国外电子元器件,2000(9):28-31.[2]李方慧,王 飞.T MS320C6000系列DSPs原理与应用(第2版)[M].北京:电子工业出版社,2003.[责任编辑:李雪莲]・5・应 用 科 技 第31卷。

DSP实验 AD与DA转换

DSP实验 AD与DA转换§5.7 [实验5.7] 高精度音频A/D与D/A转换实验一、实验目的1.悉DSP中多功能缓冲串口(McBSP);2.熟悉数字D/A,A/D芯片的功能和结构;3.掌握MCBSP及AIC23的设置和使用方法;4.了解AIC23与MCBSP的硬件结构与连接方式。

二、实验设备1.一台装有CCS软件的计算机;2.DSP实验箱;3.DSP硬件仿真器;三、实验原理为了方便实验,我们首先介绍一下AIC23与MCBSP的原理与使用方法。

1.AIC23基本性能AIC23是德州仪器公司(TI)生产的高性能音频A/D、D/A放大电路。

外围接口工作电压为3.3V,内核工作电压是1.5V,在48kHz采样率条件下,A/D变换信噪比可达100dB,其控制口可由硬件设置为同步置口(SP2)模式或两线制(2-wire),音频数据接口可采用I2S格式、DSP格式、USB格式及最高位或最低位数据调整格式。

音频数据字长可设置为16、24、20、32位,输出可直接驱动耳机,在32Ω条件下输出可达30mW。

内置前置放大器及偏置电路可直接连接麦克风。

该芯片功耗很低,在休眠(power-down)状态下,功耗小于15uW。

2.AIC23内部结构及功能简介AIC23的内部结构框图如下(1)AIC23有两个数字接口,其一是由CS、SDIN、SCLK和MODE构成的数字控制接口,通过它将芯片的控制字写入AIC23,从而控制AIC23功能;另一组是由LRCIN、DIN、LROUT、DOUT和BLCK组成的数字音频接口,AIC23的数字音频信号从这个接口接收或发出。

(2)在模拟信号接口方面,AIC23有四组,一是由RLINEIN和LLINEIN组成的线路输入接口,其内部带可控增益放大器及静音电路,其最大输入模拟信号为1VRMS;第二组是由MICIN构成的MIC接口,内部包含1个5倍固定增益放大器及0~20dB可变增益放大器,该信号与线路输入信号(LINEIN)通过内部模拟开关选择送往A/D变换电路;第三组是由RHPOUT和LHPOUT组成的耳机驱动电路,在电源电压3.3V、负载32Ω的条件下输出功率为30mW,音量从+6dB~-73dB可控,其输入信号来自内部的D/A变换电路同时混合MIC信号,也可放大线路输入信号(即Bypass功能);第四组是模拟接口ROUT和LOUT,其信号来源于AIC23内部D/A变换电路,标称输出信号为1V有效值(1Vrms)。

利用DSP的McBSP实现与PC机串行通信

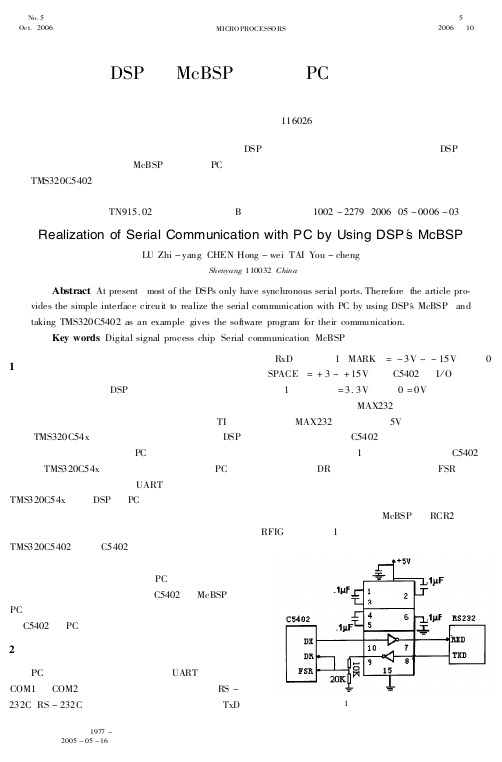

0 ! 硬件接口电路设计

’$ 机 通 常 有 两 个 可 编 程 的 ;G%1, 分别是 $&"- 和 $&"0 。它们的接口通信标准通常是 %) 8 020$ , %) 8 020$ 对逻辑电平作了如下规定: 在 1X*

作者简介: 陆志洋 ( -699 8 ) , 男, 安徽贵池人, 硕士研究生, 主研 收稿日期: 0//3 8 /3 8 -.

/ ! 引! 言

数字信号处理器 ( *)’) 因其强大的数据处理能 力已在通信和信号处理、 信号与信息处理、 自动控制 等领域得到越来越广泛的应用。尤其象美国 1# 公 司的 1")20/$34X 系列, 更 具有通用性。经过 *)’ 处理后的 数据通常 要送到 ’$ 机进行 显示或 监控 等。但 1")20/$34X 只具有同步串口, 而通常 ’$ 机 都是 通 用 异 步 串 行 接 口 ( ;G%1 ) 。目前常用的 1")20/$34X 系列 *)’ 与 ’$ 机进行串行通信的方 式要么在软件编程上过于烦琐, 使通信速率慢; 要么 在硬件设计上过于复杂, 增大系统的体积。在利用 1")20/$34/0 ( 简称 $34/0 ) 进行抗噪声对消系统的 设计时, 为了在软件和硬件不过于复杂化的情况下 实现该系统与上位机 ( 这里即为 ’$ 机) 进行数据信 息的交换, 我们设计了一种利用 $34/0 的 "+,)’ 与 ’$ 机进行异步串行通信的方案。这种方案能够实 现 $34/0 与 ’$ 机之间的高速全双工通信。

和 %X* 上, 逻辑 ( "G%Y)Z 8 2[ \ 8 -3[, 逻辑 / ( )’G$()Z ] 2 \ ] -3[。而 $34/0 的 # ^ & 电平是: 逻辑 - 或无信号 Z 27 2[, 逻辑 / Z /[。为了使它们 相互通信, 必须通过 "G_020 芯片进行 电平转换。 但由于 "G_020 供给电平为 3[ , 故采用两串联电阻 进行分压以达到与 $34/0 的接收电 平匹配。具 体 的硬件接口电路如图 - 所示。另外这里把 $34/0 的 数据接收线 *% 和接收帧同步 信号线 ‘)% 接在 一 起, 是利用一帧的起始位始终为低电平进行接收帧 同步触发的。但为了接收帧同步信号不受起始位后 面其他位 的干 扰, 必须将 "+,)’ 的 %$%0 寄存 器 %‘#a 位设置 为 - , 即 忽略第 一字以 后的 帧同步 信 号。

基于McBSP的高速串行数据采集系统设计

基于McBSP的高速串行数据采集系统设计1. 序言本文介绍了基于TI 公司的新一代DSP 芯片TMS320C6711 和AD 公司的串行模数转换芯片AD974 的嵌入式数据采集系统的设计方法。

TMS320C6711 是32bit 浮点信号处理器,核心电压1.8V,工作频率100-150MHz,2 级Cache,运算速度900MFLOPS。

其多通道缓冲串口(Multi- channel Buffered Serial Port,McBSP)可直接与AD974 进行串口连接,为系统提供高性能的A/D 转换和数据处理能力。

AD974 是美国模拟器件公司生产的一个200kSPS、4 通道、16 位数据采集系统。

具有高通过率、低功耗、高精度等特性,此外,该器件还集成了外围器件,并采用串行通讯方式,因而可极大地简化数据采集电路的设计,非常适合于体积小、信号复杂的应用系统,如工业控制、医疗仪器等。

2. AD974 芯片的特点及工作原理2.1 AD974 芯片的特点AD974 是一个四通道、16 位串行通讯数据采集模数转换器。

该器件内含模拟输入多路转换器、高速16 位采样模数转换器和+2.5V 参考电压。

从应用角度看,AD974 具有如下特点:(1)支持复杂的信号采集系统。

具有四个单端的模拟输入通道,能提供多种可设置的模拟输入范围,包括0V~4V、0V~5V 或-10V~+10V;(2)采用串行接口。

与大多数微处理器的串行接口兼容,具有数据传送效率高、数据连线少的特点;(3)可简化电路的设计,AD974 由单电源+5V 供电,并且只需较少的外围电路。

为了达到简化电路设计的目的,AD974 内部还集成了模拟输入多路转换器、高速逐次逼近开关电容ADC、时钟电路和内部2.5V 参考电。

最新DSP与PC机串口通信设计报告

1 序言:本次设计题目主要是进一步掌握同步串口McBSP的结构及工作原理,学习DSP实现RS232串口通讯的程序设计,学习MAX3111与DSP 的接口设计。

近年来,DSP在电子、通信和控制领域得到了非常广泛的应用,在DSP应用系统设计中与上位机和下位机的通信必不可少。

串口通信作为重要的通信方式之一,优点就是接口需要的引脚少,结构简单易于实现。

本文介绍了TMS320C5416多通道缓冲口,并通过具体的实例介绍说明利用串口进行DSP通信的具体实现。

2 McBSP的接口信号及工作过程McBSP由一个数据通道和一个控制通道组成,如图1所示。

不同的接受和发送引脚实现和外部器件之间的通信。

McBSP的接收操作采用三级缓冲方式,发送操作采用两级缓冲方式。

数据发送引脚(DX)负责数据的发送,数据接受引脚负责数据的接受,另外五个引脚(CLKS, CLKX, CLKR, FSX和FSR)提供了控制信号(时钟和帧同步)接口。

C5416CPU通过片内的外设总线访问串口的32位控制寄存器,从而实现与McBSP间的通信与控制。

接受的数据到达DR引脚后移位到RSR,一旦整个数据单元接受完毕,如果RBR寄存器未满,则RSR被复制到RBR中。

如果DRR中的数据已经被CPU/DMA控制器读取,则RSR被将被复制到DRR中。

发送数据首先由CPU或DMA控制器写入DXR中。

如果XSR寄存器为空,则DXR中的值被复制到XSR并准备移位输出,否则,DXR会等待XSR中旧数据的最后一位被移位输出到DX引脚后,才将数据复制到XSR中。

3 McBSP与 SPI设备的接口SPI(Series Protocol Interface)是一个利用4根信号线的串行接口协议,包括主从两种模式。

4个接口信号分别是:串行数据输入(MISO,设备输入,从设备输出)、串行数据输出(MOSI,主设备输出,从设备输出),移位时钟(SCK)、低电平有效的从设备使能信号(SS)。

基于McBSP通信接口的DSP外设扩展设计

基于McBSP通信接口的DSP外设扩展设计王振,朱磊(西安工程大学电子信息学院,陕西西安710048)摘要:TMS320VC5416型DSP是一种较为先进的高速数字信号处理器,然而由于缺少A/D、D/A、FLASH等常用片上外设,造成在部分场所的应用不便,为此,文章提出利用功能强大的McBSP通信接口来扩展DSP的上述外设。

利用DSP 片上McBSP0与C8051F340处理器的SPI接口互连,实现了具有DSP程序代码存储与自举功能的FLASH外设扩展,利用DSP片上McBSP1与A/D转换器TLV2541及D/A转换器TLV5636的SPI接口互连,通过McBSP1接口分时控制实现A/D与D/A转换外设扩展。

实验表明,利用McBSP接口扩展DSP的外设,占用DSP硬件资源少,可有效实现DSP 程序代码的存储与自举以及A/D与D/A转换功能。

关键词:DSP外设扩展;McBSP;FLASH;A/D;D/A中图分类号:TP332文献标识码:A文章编号:1673-1131(2016)10-0186-030引言TMS320VC5416是一种采用改进哈佛结构的16位定点型先进高速数字信号处理器,由于其具有多条总线、流水线指令处理结构,40位逻辑运算单元(ALU),单周期的乘累加操作(MAC),选择、比较、存储单元(CSSU)等特殊结构及丰富的特殊运算指令,使得该DSP具有最高可到160MIPS 的高速指令运算处理能力,被广泛应用于通信、医疗电子、消费电子等众多数字信号处理领域。

TMS320VC5416型DSP片上具有McBSP、HPI、并口等通信接口,然而片上却没有不少应用中常常用到的A/D与D/A转换器,同时也没有可用于存储程序代码的FLASH存储器,从而给基于该款DSP处理器的不少应用带来了不便[1-2]。

为此,本文利用TMS320VC5416型DSP多个功能强大的片上McBSP通信接口,扩展了A/D转换器、D/A转换器及程序代码存储的FLASH存储器,从而给基于TMS320VC5416型DSP的应用开发提供了一种基于McBSP接口扩展外设的有益参考。

基于McBSPs实现TMS320C6000系列DSPs异步串行通信

基于McBSPs实现TMS320C6000系列DSPs异步串行通

信

商丹;高永清;陈义平

【期刊名称】《应用科技》

【年(卷),期】2004(031)005

【摘要】为解决TMS320C6000系列DSPs的异步串行通信能力,提出一种新的解决方案,即利用多通道缓冲串行接口(McBSPs)与专用串行异步收发器来扩展异步串行接口.其硬件电路及软件编程简单、方便,可节省程序代码空间和CPU运行时间,是一种使用广泛的串行总线接口标准.通过对应用系统的配置,可支持多种速率和多种方式的SPI,可以方便地用于各种不同的SPI设备.

【总页数】4页(P31-33,50)

【作者】商丹;高永清;陈义平

【作者单位】黑龙江科技学院,自动化工程系,黑龙江,哈尔滨,150027;黑龙江科技学院,自动化工程系,黑龙江,哈尔滨,150027;中国矿业大学,机电与信息学院,北

京,100083;黑龙江科技学院,自动化工程系,黑龙江,哈尔滨,150027

【正文语种】中文

【中图分类】TP911.3

【相关文献】

1.基于McBSP的TMS320C6713异步串行通信的实现 [J], 张云昌;张令弥;赵建洋

2.TMS320C6000系列DSPs外接FLASH引导方式的实现 [J], 李鹏;郑喜凤;丁铁

夫

3.基于McBSP实现TMS320C6000系列DSPs的帧传输处理 [J], 阚颖

4.基于McBSP实现TMS320C6000系列DSPs的音频编解码 [J], 赖焰根;郭继昌;王书娟

5.TMS320C6000系列DSP的McBSP功能扩展 [J], 方波;陈柘

因版权原因,仅展示原文概要,查看原文内容请购买。

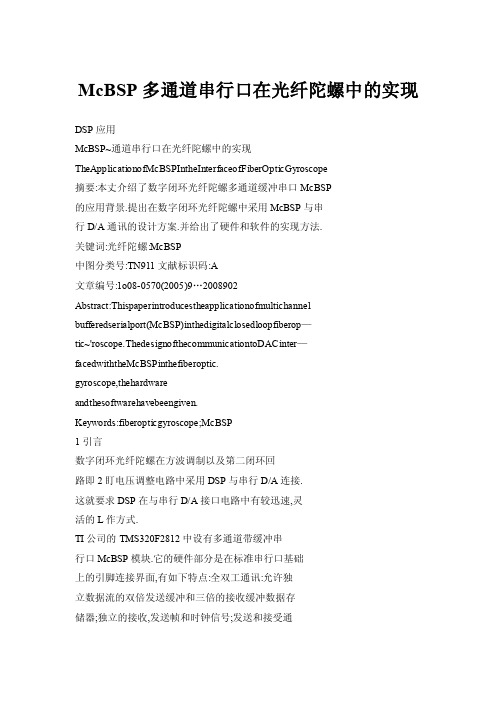

McBSP多通道串行口在光纤陀螺中的实现

McBSP多通道串行口在光纤陀螺中的实现DSP应用McBSP~通道串行口在光纤陀螺中的实现TheApplicationofMcBSPIntheInterfaceofFiberOpticGyroscope摘要:本丈介绍了数字闭环光纤陀螺多通道缓冲串口McBSP的应用背景.提出在数字闭环光纤陀螺中采用McBSP与串行D/A通讯的设计方案.并给出了硬件和软件的实现方法.关键词:光纤陀螺:McBSP中图分类号:TN911文献标识码:A文章编号:1o08-0570(2005)9 (2008902)Abstract:Thispaperintroducestheapplicationofmultichannelbufferedserialport(McBSP)inthedigitalclosedloopfiberop—tic~'roscope.ThedesignofthecommunicationtoDACinter—facedwiththeMcBSPinthefiberoptic.gyroscope,thehardwareandthesoftwarehavebeengiven.Keywords:fiberopticgyroscope;McBSP1引言数字闭环光纤陀螺在方波调制以及第二闭环回路即2盯电压调整电路中采用DSP与串行D/A连接.这就要求DSP在与串行D/A接口电路中有较迅速,灵活的L作方式.TI公司的TMS320F2812中设有多通道带缓冲串行口McBSP模块.它的硬件部分是在标准串行口基础上的引脚连接界面,有如下特点:全双工通讯:允许独立数据流的双倍发送缓冲和三倍的接收缓冲数据存储器;独立的接收,发送帧和时钟信号;发送和接受通道数最多可达128路;两个16级.32位的FIFO代替DMA;可直接与工业标准的编码器,模拟界面芯片(AICS),其他串行A/D,D/A器件连接;宽范围的数据格式选择,包括8,12,16,24,32位字长.TMS320F2812 的多通道带缓冲串行口McBSP模块符合光纤陀螺的要求:集成光学调制器图l数字闭环光纤陀螺结构框图李琛:硕士生基金资助:国防预研计划项目,国家十五规划项目编号不公开京航空航天大学)李琛张春熹Li,ChenZhang,Chunxi2McBSP在光纤陀螺中的工作方式数字闭环光纤陀螺的结构如图1所示.闭环的检测电路方案以高速DSP芯片为中心,对数字信号进行滤波和计算,控制串行D/A的输出从而实现闭环控制.F2812在FIFO模式下McBSP发送数据部分结构如图2所示.包括数据通路和控制通路两部分,控制通路由多通道选择器,时钟和帧同步信号发生器及其控制部分和中断与事件控制模块组成.时钟和帧同步发生器及其控制部分决定时钟和帧信号的模式,频率,极性.中断信号有FIFO和非FIFO两种模式选择. 两个中断信号MRINT,MXINT触发CPU的中断. REVT,XEVT分别为触发FIFO的接收和发送同步信号,REVTA,XEVTA分别为A率模式下的接收和发送同步信号.McBSP由引脚DX,FSX,CLKX与外部器件相连.需要送出的数字信号经引脚DX送人外部器件.引脚CLKX和FSX分别输出时钟和帧同步信号.图2McBSP发送部分结构图McBSP发送数据时,先将数据写入数据发送寄存器DXR[1,2】,在发送时钟CLKX和帧同步发送信号电话:010—62132436,62192616(T/F)l'现场总线技术应用200例I/,中国自控网:http:I/www.aLltocontro1.Crl'三多国自控嗣邮局订阅号:82.946360元/年一89—睡丽爻再蓊丽院士关注}中文核心期刊<微计算机信息)(嵌入式与SOC)2005年第21卷第9-2期Fsx的控制下.数据由发送引脚DX移送出.图3为单FRX和MFFCT将不会起作用.随后给MFFCT,相位模式下McBSP的各引脚输出信号图:cLK(WX1FS(R/X1D(R/X图3单相位模式McBSP输出信号McBSP与串行D/AAD5317连接时,引脚FSX与AD5317的引脚_N相连.CLKX与D/A的引脚SCLK相连.DX与D/A的引脚DIN相连.另外,在TMS2812上还需再定义一个I/O口为串行D/A更新输出.即与丽相连.3McBSP软件设计由于McBSP工作在FIFO模式下能在一个帧同步信号后连续发送数据,而且当FIFO中保存数据的级数与已定义FIFO触发中断的级数相等时,将产生中断请求.这样可以在McBSP中断服务子程序中将丽引脚拉低.从而更新D/A输出.所以程序中McBSP采用FIFO模式.设置DSP为C28I作模式设置C28地址模式中断向量表Ox3FFFC一从0x3FFFFF0关闭看门狗l设置系统时钟频率I设置高速外设时钟频率l设置低速外设时钟频率f复位看门狗关闭可屏蔽中断中断标志寄存器IFR清零中断使能寄存器IER清零中断应答寄存器清零清除所有中断请求将ENPIE置1从外设中断扩展控制器中读取中断向量使能INT6使~/ee,MXINT使能可屏蔽中断图4系统初始化流程图图5外设中断初始化流程图在对系统和外设中断初始化结束后.使能外设McBSP模块时钟,将引脚22(DX),28(CLKG)定义为McBSP引脚,定义通用I/O引脚GPIOB15为输出引脚,即用它输出串行D/A所需的更新信号(低有效). 然后复位FIFO,同时将McBSPFIFO接收寄存器的RXFFIL设为OxlF,这样在可以避免复位后因接收部分的FIFO缓冲器在大多数时间内为空而产生的频繁中断请求.在复位过程中,FIFO寄存器MFFTX,MF—MFFINT及MFFST赋值.分别定义FIFO中的数发送到DXR1的延迟时间,McBSP中断类型和以及对相应的标志位清零.FIFO寄存器定义结束后,使能FIFO. 再将SPCR2设为0,复位发送器.在初始化McBSP寄存器中.定义数据,帧同步信号和输出时钟的格式:发送一帧数据中所包含的相位数,字长和一帧数据的长度.如何处理额外的帧信号,中断模式,帧信号和输出时钟的极性.帧信号的周期及脉宽等.最后使能SRG, 发送器和FSX.使能外设McBSP时钟将通用引脚GPFMUF8,10,12定义为McBSP~I脚DX,FSX,CLKX11k厶儿,口TDnl"I上拉高弓脚LDAC1r复位FIF01r设置发送数据间的延迟设置FIF0中断模式使能FIFOIlJ_nn_L=:::I,r复位McBSP选择相位模式,数据是否压缩,一个字节所含的位数何时送出帧同步信号,CLKG由SRG决定,它的频率,上升或下降沿送数使能SRG1r使发送部分不处于复位状态1r使能Fsx向DX写入数据图6McBSP初始化流程图McBSP中断服务子程序中,触发面_C信号.即将其电平拉低,至少保持20ns低电平后将其拉高.随后清中断标志位.软件采用汇编语言编写,程序流程图如下:(见1O页)中国自控网:一90—360元/年邮局订阅号:82.946中文核心期刊《微计算机信息》(嵌入式与$0C)2005年第21卷第9-2期"O1"发送启动码来初始化IIC总线.然后总线控制器发送7位从设备地址(ZLG7290的地址是70H)写数据时,先设置状态寄存器的BF位;然后写人数据到移位缓冲寄存器,此时BF位会自动清零.连续读/写时.必须设置ACK位.读数据时.在$3C4510接收到ZLG7290传来的低电平中断后,先设置BF位,然后读出移位缓冲寄存器中的内容.读/写完最后一个字节后,复位ACK位.而后通过设置[5:4】="10"来生成结束码,结束此次操作.$3C4510的IIC发送子程序流程图如图2所示,实现如下:图2IIC发送数据程序框图voidIICWrite(U8SlaveAddr,U8WriteAddr,U8 data,U8DataSize){charj;iic—txmit.SLAVE—ADDR=SlaveAddr;for(j=0;j<DataSize;j++)iic—txmit.PAGE—BUFFER[j]=data++;iic—txmit.WriteDataSize=DataSize;IicSetup0;iic—txmit.FLAG=OxO;iic—txmit.BuffByteCnt:OxO;iic—txmit.BYTE—ADDR—LSB=WriteAddr;while(IICCON&BUSY);IICCON=STARTIACK;IICBUF=iic—txmit.SLAVE—ADDRIS—WRITE;while(!(iic—txmit.FLAG&iic—page—tx_done))fwhile(!(IICCON&BF));i!(iic—txmit.FLAG&(U32)iic_byte—addr—lsb)){IICBUF=iic—txmit.BYTE—ADDR—LSB;iic—txmit.FLAGI=(U32)iic—byte—addr—lsb;}elseif(iic—txmit.BuffByteCnt<iic—txmit.Write—DataSme)IICBUF=iic—txmit.PAGE—BUFFER[iic—txmit.BuffByteClat++];elsefIICCON=STOP;iic—txmit.FLAGI=(U32)iic—page—tx—done;}}4结束语利用IIC接口及ZLG7290芯片扩展键盘与LED显示电路,极大地补充了ARM芯片自身在普通IO上的不足.使之可以适应更多的场合.参考文献[1】李驹光,等ARM应用系统开发详解,清华大学出版社,2003.12(1); 作者简介:俞泓(1981一),男,汉族,研究方向:嵌入式系统.上海交通大学在读硕士研究生,专业:电工理论与新技术.Email:****************.cn;张士文(1976一),男,汉族,研究方向:嵌入式系统,上海交通大学在读博士,专业:自动化.(200240上海交通大学电工与电子技术中心)俞泓张士文(ElectricalandElectronicsTechnologyCenter, ShanghaiJiaoTongUniversity,Shanghai,200240)Yu,HongZhang,Shiwen(投稿日期:2005.3.12)(修稿日期:2005.3.21)f接第9O页)1)系统初始化流程图4所示:2)外设中断初始化流程图5所示:3)McBSP初始化流程图6所示:4结束语本文提出并介绍在数字闭环光纤陀螺中采用McBSP(多通道缓冲串行口)与串行D/A相接.实现光纤陀螺数字闭环的方法.该方法经实验测试稳定可靠,光纤陀螺的动态范围可达一200./s一200./s,标度因数线性度小于50ppm.参考文献[1】TMs32OF28xmultiehannelbufferedserialport(McBSP)peripheral referenceguid,TEXASINSTRUMENTS,2003[2]TMS320F2810,TMS320F2812digitalsignalprocessorsdatamanua, TEXASINSTRUMENTS,2003作者简介:李琛(1980一),女,湖南人,硕士生,lichen——*************(100083北京航空航天大学仪器与光电工程学院)李琛张春熹(SchoolofApparatusandPhotoelectricityEngineering,Bei- jingUniversityofAeronauticsandAstronautics,Beijing100083,China)Li,ChenZhang,Chunxi(投稿日期:2005.2.25)(修稿日期:2005.3.1O) 中国自控网:.crl 一1O一360元,年邮局订阅号:82.946。

第十二课-ADSP处理器和AD-DA的接口设计

ADSP-BF533处理器内部不带有CAN控制器,所以在进行CAN总线连 接时需要外接一个CAN控制芯片,这里以微芯技术公司(Microchip Technology)的CAN控制芯片MCP2515为例,同时使用CAN总线收发 器SN65HVD230,介绍基本的CAN控制系统设计。系统连接框图如图

MOSI MISO BF533 PF2 PF6 SCLK

MISO MOSI CS ADS7843

X+ XY+ Y-

触摸屏

PENIRQ DCLK

触摸屏接口设计系统框图

键盘接口设计

概述

键盘接口分为独立式键盘接口和矩阵式键盘接口。独立式按键就是各按 键相互独立。每个按键各接一根输入线,一根输入线上的按键工作状态 不会影响其他输入线上的工作状态。因此通过检测输入线的电平状态可 以很容易判断哪个按键按下。 独立式按键电路配置灵活,软件结构简单。但是每个按键需要占用一根 输入先,在按键数量较多时,输入口浪费大,电路结构显得很复杂,故 此种键盘适用于按键较少或操作速度较高的场合。 矩阵式键盘适用于按键数适用于按键较多的场合,它由行线和列线组成, 按键位于行、列的交叉点上,例如一个3*3的行、列结构可以构成一个 有9个按键的键盘。

停止位

IrDA1.0数据帧格式

硬件电路设计

Blackfin®系列处理器支持IrDA1.0,最高速率能够达到115200bps。通 过设置UART_GCTL寄存器中的IREN位,可以把UART使能为IrDA1.0 模式。再通过外接的红外发射管与接收管,就可以很方便的实现红外无 线通信。红外发射和接收管使用英飞凌公司的红外收发器IRM5000。 IRM5000是一个3.3V供电,具有节能模式,并且符合IrDA标准的红外收 发器。具体的电路连连关系如下:

DSP与串行AD73360AD转换器接口设计(精)

DSP与串行AD73360A/D转换器接口设计DSP与串行AD73360A/D转换器接口设计类别:单片机/DSP来源:电子技术应用作者:何学辉苏涛摘要:讨论了TI公司的数字信号处理器TMS320VC5402的多通道缓冲串口与串行A/D变换器AD73360的接口设计,详细阐述了两者的硬件接口和软件实现。

关键词:多通道缓冲串口TMS320VC5402DSPAD73360A/D转换器随着对信号处理要求的不断提高以及DSP技术的不断发展,越来越多的工程技术人员开始采用DSP进行系统设计。

美国TI公司的TMS320VC5402(以下简称VC5402)DSP具有运算速度快、功耗小和性价比高的特点,已在个人移动通信、信号与信息处理以及自动控制等领域得到了广泛的应用。

该芯片提供了两个多通道缓冲串行接口(McBSP)与外部设备进行通信。

它与串行A/D变换器构成的信号采集与处理系统具有硬件设计简单、可靠性好的特点。

本文将详细阐述VC5402与AD73360的接口设计。

1VC5402的McBSPVC5402的McBSP是一种同步串行接口,支持多种通信方式和SPI协议,该串口可以根据设计者的不同需求进行配置,使用非常灵活。

它的主要特点如下:全双工的串行通信;连续的发送和接收数据流功能;具有外部时钟输入或内部可编程时钟两种时钟控制方式;可独立编程的发送和接收帧同步;多通道数据传输(最多可达128个通道);可选的数据宽度:8、12、16、20、24或32位;用于数据压缩的μ律和A律压缩扩展;可编程的时钟和帧同步极性。

McBSP包括6个引脚,分别是串行数据发送信号DX、串行数据接收信号DR、发送时钟信号CLKX、接收时钟信号CLKR、发送帧同步信号FSX和接收帧同步信号FSR。

由于McBSP内带有一个可编程的采样和帧同步时钟产生器,所以串口接收、发送时钟和帧同步等信号既可由内部产生,也可以由外部输入。

VC5402的McBSP由23个寄存器进行控制,除了少数几个不能由程序访问之外,一般在串口进行数据通信之前都要对它们进行初始化,部分寄存器是存储器映射寄存器,必须通过子地址的方式进行访问。

TMS320VC54x处理器McBSP接口的设计和实现.

TMS320VC54x处理器McBSP接口的设计和实现以低速语音编解码系统为例,介绍了TMS320VC54x数字信号处理器的多通道缓冲串口的软硬件设计,给出了具体的设计思想和实现方法。

关键词:数字信号处理;语音编解码;接口;TMS320VC54x模数接口是数字信号处理(DSP)系统中一个重要的组成部分,其设计和实现直接影响到信号处理的质量,许多A/D、D/A转换芯片都采用并行的数字接口,与DSP接口时需要设计相应的译码电路。

TMS320VC54x系列芯片配备了多通道带缓冲能力的串行口(MultichannelBuffered SerialPort,McBSP),为设计模数接口提供了极大的便利。

McBSP具有双向的自动缓冲单元,缓冲单元有自己的循环寻址寄存器组,用来将串行口和C54x内部存储器之间数据传输的缓存。

同时McBSP的功能非常强大,除具有一般DSP串口功能之外,还可以支持T1/E1,ST-BUS,IOM2,SPI,HS等不同标准;为便于进行多通道的数字信号处理,McBSP最多支持128个通道;支持多种数据格式(8/12/16/20/24/32 b)的传输;可自动进行语音的μ律、A律压扩;其工作速率可达到1/2 CPU时钟速率。

这些特性为设计A/D,D/A接口电路提供了很大的灵活性。

下面具体以语音编解码器为例来说明McBSP的设计和实现。

1 语音编解码系统及McBSP接口的硬件设计低速率语音编解码器是一种能够将传统的模拟语音信号(带宽为0.3~3.4 kHz)实时压缩编码成1.2~9.6 kb/s数据比特流,而保持相当语音质量的语音编解码系统。

由于他大大压缩了传输数字语音所需的带宽,便于实现高保密度的语音通信,因此在语音的保密通信、多媒体通信和移动通信系统中应用十分广泛。

如图1所示,语音采样芯片TP3067和数字信号处理器TMS320VC5409组成了一个语音编解码系统。

在模拟端口一侧,模拟语音输入采用同相输入,经过话筒前置放大器(microphone preamplifier)放大后,从VFxI+管脚输入;模拟语音的输出也采用同相输出,经过两级放大后由VPO+输出,输出端可以驱动阻抗为600Ω的扬声器。

DSP串行接口实验设计报告

DSP实验设计报告名称:RS232串行接口实验教师: 李遥姓名: 朱清亮班级: 08电子信息工程(2) 学号: 0805070161日期: 2011-11-28一、实验目的1. 进一步掌握同步缓冲口M出BSP的结构及工作原理;2. 学习DSP实现RS232串口通信的程序设计;3. 学习MAX3111与DSP的接口设计。

二、实验设备计算机;DSP硬件仿真器;SZ-DSPF教学开发平台;串行线一根三、实验硬件设置做实验之前,需要接通该实验所需的硬件电路,本实验为:现将实验箱上的电源开关“MS2”、“MS3”和“MS4”按下,将串口线一端连接到计算机的串口,另一头连接到SZ-5416D 开发教学平台的主控模块中的“RS232”端口,在将机箱右侧的船型开关往“I”方向打开电源;SZ-541D主控模块上的J7,J9、J4、J16短接;在“设置模块”中将“A”和“C”设置为“1”。

然后开始做实验,注意在做DSP实验时开始按了SZ-5416D主控模块上的K1硬件复位后,程序运行中不要再按复位键,以免实验由于DSP复位而失败。

四、实验原理1.MAX3111功能特点MAX3111通用同步收发器是MAXIM公司专门为小型微处理系统进行最优化设计的UART,它包括一个振荡器和一个可编程波特率发生器;具有一个可屏蔽的中断源;另具有一个8字节的接受FIFO(先入先出)缓冲器。

它应用SPI/MICROWIRE接口技术直接与主控制器进行通信,线路简单、体积小,通信率可达230kbit/s。

另外其内部除具有UART之外,还包括两个RS-232电平转换器,这样无需再接入普通的MAX232进行电平转换,即可应用一个芯片实现微控制器(具有SPI/MICROWIRE接口)与PC机或其它设备之间的异步数据传输。

2.MAX3111的操作MAX3111通过SPI接口与主设备进行16位数据的全双工同步通信,即主设备传送16位数据给MAX3111的同时,也可接收到MAX3111发送的16位数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第30卷第5期2009年5月微 计 算 机 应 用M I C R O C O M P U T E RA P P L I C A T I O N SV o l.30N o.5M a y.2009基于Mc B S P实现D S P s与串行A D/D A的接口设计杨 雪 牟燕妮(北京强度环境研究所 北京 100076)摘要:重点介绍了利用D S P s的多通道缓冲串口M c B S P实现与A/D、D/A串行接口的设计。

T I公司T M S320C67x系列D S P s的M c B S P有两种配置方式,一种是配置成串口的模式,一种是配置成通用I/O的模式,本文分别用这两种模式进行了A/D和D/ A接口的设计,其硬件及软件的实现方法简单、方便,可节省程序代码空间和C P U运行时间。

关键词:Mc B S P T MS320C67x A/D D/AI n t e r f a c e D e s i g nb e t w e e n t h e D SP C h i P a n d S e r i a l A D/D AB a s e do nMc B S PY A N GX u e,M UY a n n i(B e i j i n gI n s t i t u t e o f S t r e n g t ha n dE n v i r o n m e n t E n g i n e e r i n g,B e i j i n g,100076,C h i n a)A b s t r a c t:T h i s p a p e r p r e s e n t s t h e i n t e r f a c ed e s i g nb e t w e e nM cB SP a n dA/D、D/A.T h e r ea r et w o M c B SP c o n f i g u r a t i o n:o n e i s c o n-f i g u r e da s s e r i a l m o d e l;T h e o t h e r i s c o n f i g u r e da s c o m m o n I/Om o d e l.I n t h i s p a p e r,t h e s e t w o m o d e l s w e r e u s e d t o c a r r y o u t t h e A/D a n d D/Ai n t e r f a c e d e s i g n.I t s h a r d w a r e c i r c u i t a n ds o f t w a r e p r o g r a m m i n g a r e s i m p l e,s o i t c a n e c o n o m i z e p r o g r a mc o d e s p a c e a n dC P U r u n n i n g t i m e.K e y w o r d:M c B S P,T M S320C67x,A/D,D/A随着数字化的飞速发展,数字信号处理已经成为一个核心的概念。

数字信号处理器(D S P s)以其在数字信号处理方面强大的数据处理能力得到了迅速的发展。

T M S320C67x系列D S P芯片是T I公司在T M S320C6000平台上推出的浮点D S P芯片,最高时钟可达300M H z,已经在图像处理、数字信号处理以及自动控制等领域得到了广泛的应用。

实现D S P s与外围设备之间的接口设计是D S P s系统设计的重要组成部分。

本文从硬件和软件两个方面深入探讨了如何利用多通道缓冲串口实现D S P s与A/D、D/A之间的通信。

1 Mc B S P的介绍多通道缓冲串口(M c B S P,M u t l t i c h a n n e l B u f f e r e d S e r i a l P o r t)是在T D M(时分复用串口)、B S P(缓冲串口)的基础上发展起来的。

它既可以实现时分多路通信的功能,又可以通过D S P s提供的E D M A功能实现不用C P U参与的自动缓存功能,从而把C P U从串口通信中解放出来,提高了C P U的运行效率。

M c B S P支持多种通信方式,可以根据设计者的不同需求进行配置。

T M S320C67x系列D S P s的M c B S P在结构上分为数据通道和控制通道两部分。

数据通道完成数据的发送和接收:C P U或E D M A控制器向数据发送寄存器(D X R)中写入待发送的数据,从数据接收寄存器(D R R)读取接收到的数据。

写入D X R的数据通过发送移位寄存器(X S R)移位输出至D X管脚。

同样,D R管脚上接 本文于2008-12-29收到。

5期 杨 雪等:基于M c B S P 实现D S P s 与串行A D /D A 的接口设计收到的数据先移位进入接收转移寄存器(R S R )中,然后被复制到接收缓冲寄存器(R B R )中,R B R 再将数据复制到D R R ,后者等待C P U 或E D M A 控制器将数据读走。

这就允许片内的数据搬移和外部的数据通信可以同时进行;控制通道包括内部时钟产生,帧同步信号产生和对这些信号的控制以及多通道选择,控制模块利用表1列出的4个信号向C P U 发送重要中断通知,向E D M A 控制器发送事件通知[1]。

表1 Mc B SP C P U 中断和E D MA 同步事件中断名说明R I N T到C P U 的接收中断X I N T到C P U 的发送中断R E V T 到E D M A 控制器的接收同步事件X E V T到E D M A 控制器的发送同步事件图1 M c B S P 的结构框图 T M S 320C 67x 系列D S P s 一般有2个多通道缓冲串口(M c B S P ),每个M c B S P 包括7个管脚,如图1所示。

D X 与D R 负责串行数据的发送和接收,帧同步信号F S X /F S R 负责提供发送/接收帧同步信号,3个引脚提供时钟信号:发送时钟信号C L K X 、接收时钟信号C L K R 、外时钟输入C L K S 。

2 系统的硬件设计T M S 320C 67x 系列D S P s 的M c B S P 有两种模式可以配置:1、串口模式;2、通用I /O 模式。

在本设计中,A /D 与D S P s 的接口设计成模式1,D S P s 与D /A 的接口设计成模式2。

2.1 A /D 与D S P s 的接口设计数据采集的A /D 芯片选用A D 公司的A D 7323,它是一个四通道12位的A D 芯片,拥有2.5V 的内部基准。

功耗低。

有四个软件可编程的输入范围,每一个模拟输入通道都可以进行独立的编程。

最大的采样速率可以高达500k S P S [2]。

A D 7323作为一种串行的A /D 转换芯片,提供了与S P I 兼容的接口,支持与处理器串行口或S P I 接口器件进行连接。

在S P I 模式下,系统通常有一个主设备和一个或多个从设备组成。

S P I 协议是由串行数据输入(主模式端输入从模式端输出-M I S O )、串行数据输出(主模式端输出从模式端输入-M O S I )、移位时钟(S C K )和一个低电平有效的从模式端使能信号(S S )组成的4线接口。

主模式端和从模式端之间的通信由主模式端时钟的存在与否决定:检测到主模式端时钟时数据传输开始,主模式端时钟结束时数据传输结束。

M c B S P 的时钟停止模式与S P I 协议兼容,M c B S P 与A D 7323通信的时序如图2所示。

图2 M c B S P 与A D 7323通信时序图57 微 计 算 机 应 用 2009年在本设计中,A D 7323与T M S 320C 67x 的M c B S P 0相连,M c B S P 0作为主设备,其中将发送数据帧时钟(F S X )用作从模式端使能信号(S S ),而将发送数据位时钟(C L K X )用作S P I 协议中的S C K 。

A D 7323与M cB S P 0连接方式如图3所示。

2.2 D S P s 与D /A 的接口设计D /A 芯片选用A D 公司的A D 5554,该芯片是一个四通道14位的D /A 芯片,输出的最大电压由外部基准提供的电压决定[3]。

A D 5554支持三线S P I 协议,但由于A D 5554需要同步转换信号,所以把T M S 320C 67x的M c B S P 1配置成通用I /O 口的模式。

M c B S P 1与D /A 的连接如图4所示:图3 M c B S P 0作为主设备S P I接口框图图4 M c B S P 1作为通用I /O 口与D /A 连接框图 M c B S P 1与A D 5554通信的时序图如图5所示:图5 M c B S P 1与D /A 通信时序图3 系统的软件设计3.1 A /D 与D S P s 接口的程序设计D S P s 通过M c B S P 接收A /D 采集的数据,D S P s 的C P U 或E D M A 控制器从M c B S P 的数据接收寄存器(D R R )读取接收到的数据,其中C P U 与M c B S P 之间数据传送方式一共有2种:查询方式和中断方式[4]。

在本设计中,C P U 每隔4m s 对采集的数据进行一次处理,所以采用定时器来定时,而在定时器的中断服务程序中C P U 采用查询的方式把数据从M c B S P 的接收寄存器(D R R )中读入相应缓存。

在A /D 与M c B S P 的接口程序设计中,D S P s 首先要根据接口通信的需要初始化M c B S P 0和定时器,然后对A D 7323进行初始化设置,初始化结束后D S P s 的C P U 使用定时器中断服务程序接收数据。

3.1.1 M c B S P 0的初始化(1)设置S P C R 寄存器,使帧同步和采样率发生器复位,使能时钟停止模式(时钟开始自下降沿)。

(2)设置接收控制寄存器R C R 和发送控制寄存器X C R ,使接收帧和发送帧的相位为单相帧(R P H A S E =0),并且每一帧的长度为16位。

(3)设置采样率发送器寄存器(S R G R ),使采样率发生器时钟来自内部时钟源,发送帧同步信号(F S X )由采样率发生器的帧信号F S G 驱动。

采样率发生器时钟分频器C L K G D V 的计算公式如公式(1)所示:C L K G =C L K I ×1C L K GD V+1(1)58 5期 杨 雪等:基于M c B S P 实现D S P s 与串行A D /D A 的接口设计程序中设的时钟主频为90M H z ,内部时钟源的频率为C P U 主频的1/2,是45M H z (C L K I )。