5 SCI 异步串行通讯l

串行通信接口SCI

串行通信分为同步通信和异步通信。

串行通信接口都具有发送引脚TXD和接收引脚RXD,它们是TTL平电。

如果要利用这两个引脚与外界实行异步通信,必须将TTL电平转化为RS-232电平。

SCI是一种全双工异步串行通信接口,主要用于MCU与其他计算机或设备之间的通信,几个独立的MCU也能通过SCI实现串行通信,形成网络。

从编程角度看,先设定好波特率,通信格式,是否校验,是否允许中断等。

接着发送数据时,先检查相应的标志位是否允许发送数据,如果可以,则把数据放入SCI数据寄存器即可,剩下的工作芯片自动完成:将数据从SCI数据寄存器送到发送移位寄存器,硬件驱动将发送移位寄存器里的数据按规定发送到发送引脚TXD,供对方接收。

接收时,数据逐位从接收引脚RXD进入到接收移位寄存器,当收到一个完整字节时,芯片会自动将数据送到SCI数据寄存器,并置相应的标志位,我们就可以根据标志位的情况来读取数据了。

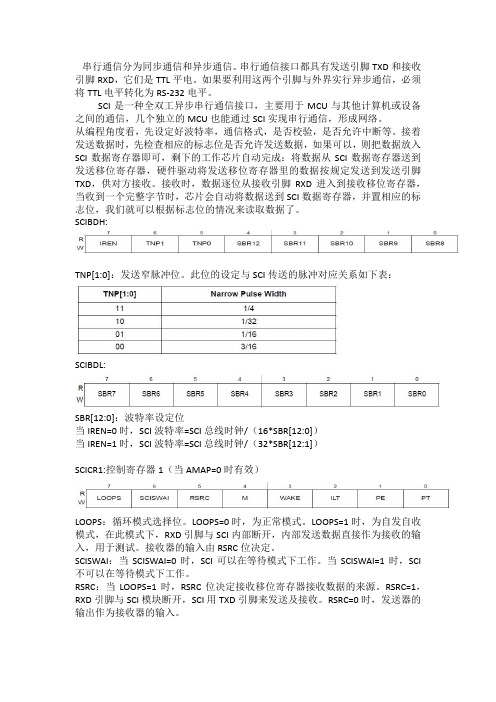

SCIBDH:TNP[1:0]:发送窄脉冲位。

此位的设定与SCI传送的脉冲对应关系如下表:SCIBDL:SBR[12:0]:波特率设定位当IREN=0时,SCI波特率=SCI总线时钟/(16*SBR[12:0])当IREN=1时,SCI波特率=SCI总线时钟/(32*SBR[12:1])SCICR1:控制寄存器1(当AMAP=0时有效)LOOPS:循环模式选择位。

LOOPS=0时,为正常模式。

LOOPS=1时,为自发自收模式,在此模式下,RXD引脚与SCI内部断开,内部发送数据直接作为接收的输入,用于测试。

接收器的输入由RSRC位决定。

SCISWAI:当SCISWAI=0时,SCI可以在等待模式下工作。

当SCISWAI=1时,SCI 不可以在等待模式下工作。

RSRC:当LOOPS=1时,RSRC位决定接收移位寄存器接收数据的来源。

RSRC=1,RXD引脚与SCI模块断开,SCI用TXD引脚来发送及接收。

RSRC=0时,发送器的输出作为接收器的输入。

sci串口通信原理

sci串口通信原理SCI(Serial Communication Interface,串行通信接口)是一种广泛应用于嵌入式系统和电子设备中的串行通信协议。

SCI通常指的是UART(Universal Asynchronous Receiver/Transmitter,通用异步收发传输器)的一种实现方式。

在SCI通信原理中,数据以串行的方式通过一根或多根信号线进行发送和接收。

基本的通信参数包括波特率(bits per second, bps)、数据位数、停止位数和校验类型等。

1. 波特率:指每秒钟传输的比特数,是通信双方必须同步的一个重要参数。

2. 数据格式:1)数据位数(Data Bits):通常为5、6、7或8位。

2)停止位(Stop Bits):通常为1或2位,用于表示一个字符数据包的结束。

3)校验位(Parity Bit):奇偶校验,可选无校验、奇校验或偶校验,用于检测数据传输过程中可能出现的错误。

3. 通信过程:1)发送端将并行数据转换为串行数据,并按照设定的波特率和格式输出。

2)接收端则按照相同的参数设置解码接收到的串行数据,还原成并行数据。

4. 控制信号:1)RTS (Request to Send) 和CTS (Clear to Send) 用于硬件握手,确保双方都准备好进行通信。

2)DTR (Data Terminal Ready) 和DSR (Data Set Ready) 另一对硬件握手信号,用于设备之间表明就绪状态。

3)TXD (Transmit Data) 是发送数据的信号线,RXD (Receive Data) 是接收数据的信号线。

4)其他可能还包括中断请求线(如IRQ)等。

在嵌入式系统中,例如使用TMS320F28xx系列DSP芯片时,SCI模块负责处理这些串行通信任务,通过配置相应的寄存器来设定上述参数,然后利用中断机制实现在数据发送和接收过程中的实时响应与处理。

数字信号处理 串行通信接口(SCI)

12

SCI的增强特性

SCIFIFO描述 发送器与接收器各有16级FIFO,有3个专门的寄存器控制; 复位时,SCI工作于标准模式,禁止FIFO功能。

自动波特率检测 自动检测SCI通信的波特率,并刷新BRR寄存器。

(BRR+1)×8

注意:如果BRR=0,则波特率=LSPCLK/16.

SCICLK×8

1≤BRR≤65535,如果BRR=0,等同于BRR=1

BRR

SYSCLKOUT/4

6

SCI多处理器通信

在同一条串行连线上,多处理器通信模式允许一个处理器 (主机)向串行线上其它处理器(从机)发送数据。

一条串行线上每刻只能有一个节点发送数据(发送使能控 制),但可以多个节点同时接收数据。 1、地址字节

13

第7章 DSP片上串行通信外设

7.3 串行通信接口(SCI)

串行通信概述

串行通信:通信线上既传输数据信息,也传输联络信息,因 此收发双方就必须要有通信协议。特点是串行传输成本低, 适用于远距离通信,但传输速度低。 串行通信分类:1)同步通信;2)异步通信。

同步通信:发送器和接收器通常使用同一时钟源来同步。方法是在发送器 发送数据时同时包含了时钟信号,接收器利用该时钟信号进行接收。 异步通信:收发双方的时钟不是同一个时钟,是由双方各自的时钟实现数 据的发送和接收。但要求双方使用同一标称频率,允许有一定偏差。 同步方法:要正确传输字符,准确读取每一位是必须用各自的时钟同步的, 为克服不同时钟的偏差,每个字符都有一个起始位进行同步。

方法二: 利用TXWAKE位产生11位的空闲时间 1)首先置位TXWAKE(SCICTL1.3),控制数据发送特征; 2)写一个数据字节(内容不重要)到SCITXBUF,发送一个

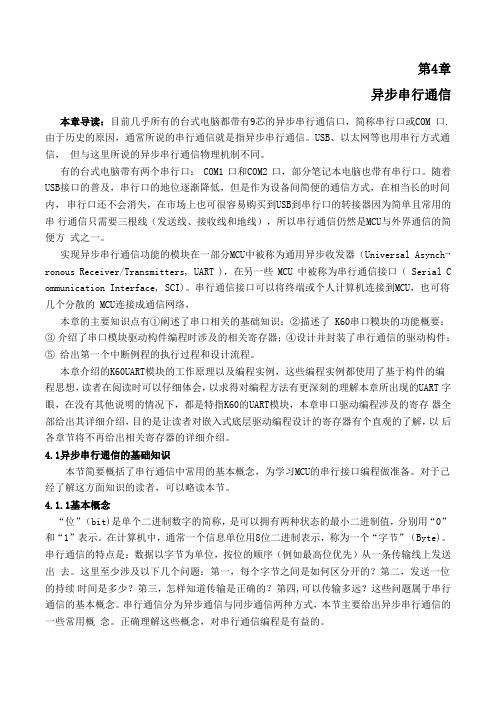

第4章 异步串行通信

第4章异步串行通信本章导读:目前几乎所有的台式电脑都带有9芯的异步串行通信口,简称串行口或COM 口.由于历史的原因,通常所说的串行通信就是指异步串行通信。

USB、以太网等也用串行方式通信,但与这里所说的异步串行通信物理机制不同。

有的台式电脑带有两个串行口: COM1 口和COM2 口,部分笔记本电脑也带有串行口。

随着 USB接口的普及,串行口的地位逐渐降低,但是作为设备间简便的通信方式,在相当长的时间内,串行口还不会消失,在市场上也可很容易购买到USB到串行口的转接器因为简单且常用的串行通信只需要三根线(发送线、接收线和地线),所以串行通信仍然是MCU与外界通信的简便方式之一。

实现异步串行通信功能的模块在一部分MCU中被称为通用异步收发器(Universal Asynch¬ronous Receiver/Transmitters, UART ),在另一些 MCU 中被称为串行通信接口( Serial Communication Interface, SCI)。

串行通信接口可以将终端或个人计算机连接到MCU,也可将几个分散的 MCU连接成通信网络,本章的主要知识点有①阐述了串口相关的基础知识;②描述了K60串口糢块的功能概要;③介绍了串口模块驱动构件编程时涉及的相关寄存器;④设计并封装了串行通信的驱动构件;⑤给出第一个中断例程的执行过程和设计流程。

本章介绍的K60UART模块的工作原理以及编程实例,这些编程实例都使用了基于构件的编程思想,读者在阅读时可以仔细体会,以求得对编程方法有更深刻的理解本章所出现的UART 字眼,在没有其他说明的情况下,都是特指K60的UART模块,本章串口驱动编程涉及的寄存器全部给出其详细介绍,目的是让读者对嵌入式底层驱动编程设计的寄存器有个直观的了解,以后各章节将不再给出相关寄存器的详细介绍。

4.1异步串行通信的基础知识本节简要概括了串行通信中常用的基本概念,为学习MCU的串行接口编程做准备。

串行通信接口SCI与SPI

8.3 SCI模块的编程结构

(1)SCI波特率寄存器 ) 波特率寄存器(SCI Baud Rate Register,SCBR) , 波特率寄存器

具有串行通信功能的 MC68HC908G932最小系统电路原理图 最小系统电路原理图

40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

MC68HC908GP32

1 0.1μ +5V PLL滤波 L 10K 0.47µ 0.01µ 2 3 4 5 6 9 10 11 12 13 14 15 16 17 18 19 20 0.1μ 复位电路 +5V RST 7 8 10K 0.1µ +5V 51 +5V

SCC2的地址是:$0014 ,定义为: 的地址是: 定义为: 的地址是 定义为

数据位 定义 复位 D7 SCTIE 0 D6 TCIE 0 D5 0 D4 0 D3 TE 0 D2 RE 0 D1 RWU 0 D0 SBK 0

SCRIE ILIE

发送完成中 断允许位 发送中断 允许位

空闲线中 断允许位

开始位 第0 位 第1 位 第2 位 第3 位 第 4 位 第5 位 第6 位 第7 位 停止位

SCI数据格式

8.1 串行通信基本知识概要

(2)串行通信的波特率 ) 波特率( ):每秒内传送的位数 波特率(baud rate):每秒内传送的位数。 ):每秒内传送的位数。

波特率单位是位/秒 记为 波特率单位是位 秒,记为bps。通常情况下,波特率的单位可以 。通常情况下, 省略。通常使用的波特率有 省略。通常使用的波特率有300、600、900、1200、1800、2400、 、 、 、 、 、 、 4800、9600、19200、38400。 、 、 、 。

简述并行、串行、异步、同步通信原理

标题:并行、串行、异步、同步通信原理解析一、介绍并行、串行、异步、同步通信的概念1. 并行通信:指多个数据信号在同一时刻通过不同的传输路径传输,在数据传输过程中,多个信号可以同时进行传输,从而提高数据传输效率。

2. 串行通信:指数据信号按照顺序一个接一个地通过同一传输路径传输,在数据传输过程中,数据信号只能依次进行传输,适用于长距离传输和节约传输线路资源。

3. 异步通信:指数据传输时没有固定的时钟信号,数据在发送方和接收方之间按照不规则的时间间隔传输,需要通过起始位和停止位来标识数据的起始和结束。

4. 同步通信:指数据传输时需要有固定的时钟信号,数据在发送方和接收方之间按照固定的时间间隔传输,需要通过时钟信号进行同步。

二、并行通信的原理及特点1. 原理:多个数据信号同时通过不同的传输路径传输。

2. 特点:1) 传输速度快:由于多个数据信号同时进行传输,因此传输速度相对较快。

2) 传输距离有限:由于多条传输路径之间的信号相互干扰,因此传输距离相对较短。

3) 成本较高:需要多条传输路径和大量的接口,成本相对较高。

三、串行通信的原理及特点1. 原理:数据信号按照顺序一个接一个地通过同一传输路径传输。

2. 特点:1) 传输速度慢:由于数据信号只能依次进行传输,因此传输速度相对较慢。

2) 传输距离远:适用于长距离传输,可以节约传输线路资源。

3) 成本较低:只需要一条传输路径和少量的接口,成本相对较低。

四、异步通信的原理及特点1. 原理:数据传输时没有固定的时钟信号,数据在发送方和接收方之间按照不规则的时间间隔传输。

2. 特点:1) 灵活性高:数据传输时间不固定,可以根据实际需要进行调整。

2) 精度较低:由于没有固定的时钟信号,数据传输的精度相对较低。

3) 适用于短距离传输:由于数据传输精度较低,适用于短距离传输和数据量较小的情况。

五、同步通信的原理及特点1. 原理:数据传输时需要有固定的时钟信号,数据在发送方和接收方之间按照固定的时间间隔传输。

sci串行通信接口工作原理

sci串行通信接口工作原理

SCI(Serial Communication Interface)是一种串行通信接口,用于在数字系统中进行串行数据传输。

SCI通常包括发送和接收端,通过串行方式传递数据,它在嵌入式系统和通信领域中被广泛使用。

以下是SCI串行通信接口的基本工作原理:

1.帧结构:SCI通信以帧为单位,每一帧包含了一定数量的比特,通常包括起始位、数据位、奇偶校验位(可选)、停止位等。

这种帧结构有助于接收端正确解析和识别数据。

2.波特率设置:波特率是SCI通信的速率,表示每秒传输的比特数。

在SCI通信中,发送端和接收端必须配置相同的波特率,以确保数据的正确传输。

3.起始位和停止位:为了使接收端能够准确识别帧的起始和结束,通常在每帧的开始设置一个起始位,结束时设置一个或多个停止位。

4.数据传输:数据以二进制形式传输,由发送端按照事先定义好的帧结构进行发送。

接收端在正确配置的情况下,能够识别并解析这些帧,将二进制数据还原为原始数据。

5.同步机制:为确保数据的同步传输,通常在帧的开始设置一个起始位,作为同步信号,帮助接收端正确解析后续的数据。

6.协议选择:在SCI通信中,数据的传输可以使用不同的协议,例如异步传输和同步传输。

异步通信不需要与时钟同步,而同步通信则需要与外部时钟同步。

总体而言,SCI串行通信接口通过在帧中使用起始位、数据位、停止位等结构,按照事先定义好的协议传输数据。

这种方式具有灵活性和可靠性,适用于许多嵌入式系统和通信场景。

sci与spi的区别与联系

SPI与S CI--[360doc]1. SPI串行外围设备接口(se rialperip heral inte rface)总线技术是Moto rola公司推出的一种同步串行接口。

Mo torol a公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

SPI总线是一种三线同步总线,因其硬件功能很强,所以,与S PI有关的软件就相当简单,使C PU有更多的时间处理其他事务。

2.SCI串行通信接口(seria l com munic ation inte rface)也是由M otoro la公司推出的。

它是一种通用异步通信接口UART,与MCS-51的异步通信功能基本相同。

说白一点一个是同步串行、一个是异步串行再白一点——同步的需要多出一条时钟线、异步的只需要接收、发送两条线SCI模块用于串行通讯,如RS422、RS485、RS232;S PI模块用于扩展外设,如AD、DA、FR AM、DS P等。

SCI模块和SPI模块是两个外设的扩展模块!SC I是异步通信SPI是同步通信sc i是异步串行通信接口,spi是同步,sp i分主从机,通信速率上spi高于sci------------------------------------------------------------------------------[百度知道]通常,大部分人把SCI、UART与RS232混为一谈,其实他们有本质上的差别:SC I(Ser ial C ommun icati on In terfa ce)意为“串行通信接口”,是相对于并行通信的,是串行通信技术的一种总称,最早由Motol ora公司提出的。

sci基本通讯过程

sci基本通讯过程

SCI(串行通信接口)是一种用于串行数据传输的通信协议,常用于嵌入式系统和通信设备中。

下面是SCI的基本通讯过程:

初始化:首先,发送方和接收方需要初始化SCI通信参数,包括波特率、数据位数、校验位和停止位等。

帧起始位:发送方发送一个起始位,通常为低电平,用于标识数据帧的开始。

数据传输:发送方依次发送数据位,从最高位到最低位。

每个数据位的传输时间根据所设置的波特率确定。

校验位:可选的校验位用于验证数据的正确性。

常见的校验位包括奇偶校验和循环冗余校验(CRC)等。

停止位:发送方发送一个或多个停止位,通常为高电平,用于标识数据帧的结束。

确认和响应:接收方接收到数据后,可以发送确认信号给发送方,表示数据接收成功。

发送方可以根据接收方的确认信号采取相应的控制动作。

重复以上步骤:发送方可以继续发送下一个数据帧,重复以上的通讯过程。

需要注意的是,SCI通信过程中的数据传输是单向的,即发送方发送数据,接收方接收数据。

如果需要双向通信,需要使用两条SCI通信线路,一条用于发送,一条用于接收。

SCI通信协议可以根据具体的应用需求进行定制和扩展,可以加入流控制、错误检测和纠错等功能。

以上是SCI的基本通讯过程,具体的实现和应用还需要根据具体的硬件和软件平台进行配置和开发。

常见总线简介CAN、USART、SPI、SCI等

任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线将会错综复杂,甚至难以实现。

为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线。

采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备间实现互连。

微机中总线一般有内部总线、系统总线和外部总线。

内部总线是微机内部各外围芯片与处理器之间的总线,用于芯片一级的互连;而系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连;外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连。

另外,从广义上说,计算机通信方式可以分为并行通信和串行通信,相应的通信总线被称为并行总线和串行总线。

并行通信速度快、实时性好,但由于占用的口线多,不适于小型化产品;而串行通信速率虽低,但在数据通信吞吐量不是很大的微处理电路中则显得更加简易、方便、灵活。

串行通信一般可分为异步模式和同步模式。

随着微电子技术和计算机技术的发展,总线技术也在不断地发展和完善,而使计算机总线技术种类繁多,各具特色。

下面仅对微机各类总线中目前比较流行的总线技术分别加以介绍。

一、内部总线1.I2C总线I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

2.SPI总线串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口。

Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

异步串行通讯

异步串行通信不论8位、16位还是32 位,单片机的基本系统都是通过异步串行口与人沟通的。

使用串行通信接口SCI(Serial Communication Interface)通信是计算机与人对话最传统、最基本的方法,异步通信接口也称为通用异步接收器/发送器UART(Universal Asynchronous Receiver/Transmitter),在介绍SCI口的驱动设计之前,有必要先了解一些异步串行通信的基本知识。

串行通信协议RS-232标准多年来,人与计算机通信主要采用异步串行通信方式,人通过计算机数据终端设备与计算机通信。

EIA RS-232-C是美国电子工业协会正式公布的异步串行通信标准,也是目前最常用的异步串行通信标准,用来实现计算机与计算机之间、计算机与外设之间的数据通信,与国际电报电话咨询委员会CCITT指定的串行接口标准V.24“数据终端设备(DTE)和数据通信设备(DCE)之间的接口电路定义表”基本相同。

RS-232-C电平采用负逻辑,即,逻辑1:-3~-15V,逻辑0:+3~+15V。

注意,单片机使用的CMOS电平中,高于电源电压70%为高电平,例如,若单片机以+5V供电,则高于3.5V为逻辑1,低电平0~0.8V为逻辑0。

单片机的SCI口要外接电平转换电路芯片把与TTL兼容的CMOS高电平表示的1转换成RS-232的负电压信号,把地电平转换成RS-232的正电压信号。

典型的转换电路给出-9V和+9V。

在RS-232端口,如PC机的COM1,用万用表测量到+9V或-9V 电位则说明这一端为输出端,量到不确定电平的是输入端。

量到负电压信号说明信号有效,有效的含义是1,和定义一致,如DTR(Data Terminal Ready),为负电压时为“Ready”,正电压表示“Not Ready”。

RS-232-C适用于设备之间的通信距离不大于15m(50英尺),传输速率最大为20KB/s的数据传输领域,后来随着CPU运行速度的提高,对于较短的通信距离,例如2m (约6英尺),单片机与PC之间,异步串行通信的速率可使用115200B/s。

通用异步串行通信标准-概述说明以及解释

通用异步串行通信标准-概述说明以及解释1.引言1.1 概述通用异步串行通信标准是一种在不同设备之间进行异步通信的通用标准,通过该标准,不同设备之间可以实现数据交换和通信。

在现代社会中,越来越多的设备需要进行通信,而这些设备通常具有不同的硬件和软件平台。

因此,为了实现设备之间的互联互通,需要一种通用的异步串行通信标准。

本文将详细介绍通用异步串行通信标准的重要性、基本原则以及应用范围。

通过对该标准的深入探讨,可以帮助读者更好地了解设备之间异步通信的重要性,以及如何通过通用标准实现不同设备之间的有效通信。

1.2文章结构文章结构部分的内容如下:文章结构包括以下几个部分:1. 引言: 在这部分中,我们将介绍通用异步串行通信标准的概述,以及文章整体结构和目的。

2. 正文: 在这一部分,我们将详细探讨通用异步串行通信标准的重要性、基本原则以及应用范围。

3. 结论: 最后,我们将对文章进行总结,展望未来通用异步串行通信标准的发展,并通过结束语来为整个文章画上一个完美的句号。

通过这样的结构,读者将清晰地了解到文章的整体框架和内容安排,有助于他们更好地理解和消化文章中的信息。

1.3 目的本文旨在探讨通用异步串行通信标准的重要性、基本原则和应用范围,以便为广大读者提供清晰的指导和参考。

通过深入分析该标准,我们希望能够帮助读者更好地理解和应用通用异步串行通信,提高通信效率和准确性,促进各种应用领域的发展和创新。

同时,我们也希望通过本文的研究和讨论,为未来进一步完善通用异步串行通信标准提供有益的参考和启发。

我们相信,通过本文的阐述和探讨,读者将能够更深入地了解和掌握通用异步串行通信标准,从而推动相关技术和行业的持续进步和发展。

2.正文2.1 通用异步串行通信标准的重要性通用异步串行通信标准的重要性在于它可以提高系统之间的通信效率,并且简化系统设计和开发过程。

通过定义一套统一的通信协议和接口,不同系统之间可以更加方便地进行通信,无需重复开发和定制通信协议,从而节省时间和资源。

SCI,SPI,UART三种串行总线协议的区别

SCI,SPI,UART三种串行总线协议的区别SCI (串行通讯接口)模块对其进行控制。

(注:SCI 首先由Motorola 微串口微控制器而得名,SCI 另一种说法是UART 控制器)常用的许多芯片中都包含了SCI ,例如ARM 的S3C2410X 芯片内嵌了3 个串行接口控制器,而Nios等软核芯片则可以用选用UART(RS232) 的IP 对UART 进行控制。

PC 机则常用16650 UART,16750 UART 等控制串口。

--这样说来SCI 只不过属于UART里面比较特殊的一种串行通讯方式了。

确实也只是在飞思卡尔芯片上遇见过。

第一个区别当然是名字:SCI(Serial Communicate Interface:串行通信接口)SPI(Serial Peripheral Interface:串行外设接口)另外曾在一官方datasheet 里面看见这种说法:Serial Parallel Interface:串并行接口UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)第二,区别在电气信号线上:SPI 总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。

SPI 总线可以实现多个SPI 设备互相连接。

提供SPI 串行时钟的SPI 设备为SPI 主机或主设备(Master),其他设备为SPI 从机或从设备(Slave)。

主从设备间可以实现全双工通信,当有多个从设备时,还可以增加一条从设备选择线。

如果用通用IO 口模拟SPI 总线,必须要有一个输出口(SDO),一个输入口(SDI),另一个口则视实现的设备类型而定,如果要实现主从设备,则需输入输出口,若只实现主设备,则需输出口即可,若只实现从设备,则只需输入口即可。

UART 总线是异步串口,因此一般比前两种同步串口的结构要复杂很多,一般由波特率产生器(产生的波特率等于传输波特率的16 倍)、UART 接收器、UART 发送器组成,硬件上由两根线,一根用于发送,一根用于接收。

嵌入式技术基础与实践复习题参考答案

嵌入式技术基础与实践(第二版)习题参考答案目录嵌入式技术基础与实践(第二版) (1)习题参考答案 (1)第 1 章概述习题参考答案. (2)第 2 章 FreescaleS08微控制器习题参考答案 (3)第 3 章第一个样例程序及工程组织习题参考答案. (4)第 5 章串行通信接口SCI 习题参考答案 (6)第 6 章 GPIO的应用实例—键盘、LED与 LCD习题参考答案 (9)第 7 章定时器模块习题参考答案 (10)第 8 章串行外设接口SPI 习题参考答案 (11)第 9 章 Flash 存储器在线编程习题参考答案 (13)第 1章概述习题参考答案1.嵌入式系统的基本含义是什么?为什么说单片机是典型的嵌入式系统?答:即 MCU的含义是:在一块芯片上集成了中央处理单元( CPU)、存储器( RAM/ROM等)、定时器 / 计数器及多种输入输出( I/O )接口的比较完整的数字处理系统。

大部分嵌入式系统以 MCU为核心进行设计。

MCU从体系结构到指令系统都是按照嵌入式系统的应用特点专门设计的,它能很好地满足应用系统的嵌入、面向测控对象、现场可靠运行等方面的要求。

因此以MCU为核心的系统是应用最广的嵌入式系统。

2.简述嵌入式系统的特点以及应用领域。

答:嵌入式系统属于计算机系统,但不单独以通用计算机的面目出现 ; 嵌入式系统开发需要专用工具和特殊方法 ; 使用 MCU设计嵌入式系统,数据与程序空间采用不同存储介质 ; 开发嵌入式系统涉及软件、硬件及应用领域的知识 ; 嵌入式系统的其他特点 , 比如紧的资源,较高稳定性要求,低功耗,低成本等。

一般用于工业控制,智能家电,日常电子等领域。

4.比较 MCU与 CPU的区别与联系。

答: CPU是一个单独的PC处理器。

而MCU,则有微处理器,存储器(RAM/ROM等)、定时器 / 计数器及多种输入输出(I/O )接口的比较完整的数字处理系统。

所以可以这么说,MCU是一个包含微处理器的嵌入式系统,而CPU紧紧是一个处理器而已。

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线(USB)等,这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文详细介绍了嵌入式系统设计的串行总线、驱动器和物理接口的特性,并为总线最优选择提供性能比较和选择建议。

由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。

目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。

微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C)和通用串行总线,以及车用串行总线,包括控制器区域网(CAN)和本地互连网(LIN)。

这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。

为了说明方便起见,本文的阐述是基于微处理器的设计。

串行与并行相比串行相比于并行的主要优点是要求的线数较少。

例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。

较少的线意味着所需要的控制器引脚较少。

集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。

相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。

另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB 板面积更大、更复杂,从而增加了硬件成本。

SCI串行通信

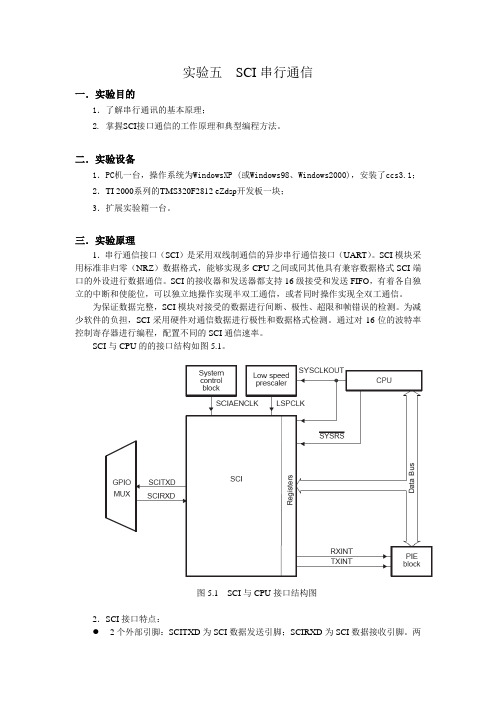

实验五SCI串行通信一.实验目的1.了解串行通讯的基本原理;2. 掌握SCI接口通信的工作原理和典型编程方法。

二.实验设备1.PC机一台,操作系统为WindowsXP (或Windows98、Windows2000),安装了ccs3.1;2.TI 2000系列的TMS320F2812 eZdsp开发板一块;3.扩展实验箱一台。

三.实验原理1.串行通信接口(SCI)是采用双线制通信的异步串行通信接口(UART)。

SCI模块采用标准非归零(NRZ)数据格式,能够实现多CPU之间或同其他具有兼容数据格式SCI端口的外设进行数据通信。

SCI的接收器和发送器都支持16级接受和发送FIFO,有着各自独立的中断和使能位,可以独立地操作实现半双工通信,或者同时操作实现全双工通信。

为保证数据完整,SCI模块对接受的数据进行间断、极性、超限和帧错误的检测。

为减少软件的负担,SCI采用硬件对通信数据进行极性和数据格式检测。

通过对16位的波特率控制寄存器进行编程,配置不同的SCI通信速率。

SCI与CPU的的接口结构如图5.1。

图5.1 SCI与CPU接口结构图2.SCI接口特点:2个外部引脚:SCITXD为SCI数据发送引脚;SCIRXD为SCI数据接收引脚。

两个引脚为多功能复用引脚,如果不使用可以作为通用数字量I/O。

●可编程通信速率,可以设置64K种通信速率。

●数据格式:1个启动位;1-8个可编程数据字长度;可选择奇校验、偶校验或无校验位模式;1或2位的停止位。

●4种错误检测标志位:奇偶错误、超时错误、帧错误和间断错误。

●2种唤醒多处理器方式:空闲线唤醒(Idle-line)和地址位唤醒(Address Bit)。

●全双工或半双工通信模式。

●双缓冲接收和发送功能。

●发送和接收可以采用中断和状态查询2种方式。

图5.2 SCI通信模块接口框图●独立的发送和接收中断使能控制。

●NRZ(非归零)通信格式。

●13个SCI模块控制寄存器,起始地址为7050H。

51单片机串行通讯

51单片机串行通讯在当今的电子世界中,单片机的应用无处不在,从家用电器到工业自动化,从智能仪表到航空航天,都能看到它的身影。

而在单片机的众多功能中,串行通讯是一项非常重要的技术。

首先,咱们来了解一下什么是串行通讯。

简单来说,串行通讯就是指数据一位一位地按顺序传送。

与并行通讯(数据的各位同时传送)相比,串行通讯虽然速度相对较慢,但它只需要少数几条线就能完成数据传输,大大降低了硬件成本和连线的复杂性。

51 单片机的串行通讯有两种工作方式:同步通讯和异步通讯。

异步通讯是比较常用的一种方式。

在异步通讯中,数据是以字符为单位进行传输的。

每个字符由起始位、数据位、奇偶校验位和停止位组成。

起始位是一个低电平信号,用于通知接收方数据即将开始传输。

数据位通常是 5 到 8 位,可以表示一个字符的信息。

奇偶校验位用于检验传输数据的正确性,而停止位则是高电平,标志着一个字符传输的结束。

同步通讯则是在发送和接收两端使用同一个时钟信号来控制数据的传输。

这种方式传输速度快,但硬件要求相对较高。

51 单片机的串行口结构包括发送缓冲器和接收缓冲器。

发送缓冲器只能写入不能读出,而接收缓冲器只能读出不能写入。

在进行串行通讯时,我们需要对 51 单片机的串行口进行初始化设置。

这包括设置波特率、数据位长度、奇偶校验位和停止位等参数。

波特率是指每秒传输的位数,它决定了数据传输的速度。

通过设置定时器 1 的工作方式和初值,可以得到不同的波特率。

在编程实现串行通讯时,我们可以使用查询方式或者中断方式。

查询方式相对简单,但会占用大量的 CPU 时间,影响系统的实时性。

中断方式则可以在数据接收或发送完成时触发中断,提高系统的效率。

比如说,我们要实现 51 单片机与 PC 机之间的串行通讯。

在 PC 端,我们可以使用串口调试助手等软件来发送和接收数据。

在单片机端,通过编写相应的程序,设置好串行口的参数,然后根据接收的数据执行相应的操作,或者将需要发送的数据发送出去。

AD转换和SCI异步串行通讯

1

实验目的 1、明确异步串行通讯接口SCI是MCU与PC之 间通讯最重要的接口。学习SCI模块中各个 硬件电路的原理。 2、了解RS-232通讯协议。学习RS-232通讯 接口电缆的连接。 3、掌握GP32微控制器AD转换原理。了解 AD模块各寄存器的设置。

5

;0,二极管全亮 ,

实验源程序(3) 实验源程序(

*启动 启动AD 启动 START: JSR GETDATA ;跳转到 跳转到GETDATA子程序,查询是否 子程序, 跳转到 子程序 SUB #$53 ;从SCI得到“S”启动信号 得到“ 启动信号 从 得到 BNE START AD: LDA #$50 ;若得到“S”信号,则启动 ,设置 若得到“ 信号 则启动AD, 信号, 若得到 STA ADCLK ;AD时钟为内部时钟 分频 时钟为内部时钟4分频 时钟为内部时钟 LDA #$21 ;启动 ,并将其设为连续转换 启动AD, 启动 STA ADSCR BRCLR 7,ADSCR,* ;查询 转换是否结束 查询AD转换是否结束 查询 LDA ADR ;若结束,读取转换结果 若结束, 若结束 JSR SENDATA ;跳转到 跳转到SENDATA子程序,输出结果 子程序, 跳转到 子程序 BRA AD

6

实验源程序(4) 实验源程序(

*SCI读取数据 读取数据 GETDATA: BRCLR 5,SCS1,GETDATA ;查询 查询SCI是否读入数据 查询 是否读入数据 LDA SCDR ;保存数据 保存数据 RTS ;返回主程序 返回主程序 *SCI传送数据 传送数据 SENDATA: BRCLR 7,SCS1,SENDATA ;查询是否输出数据 查询是否输出数据 STA SCDR ; 回 送 AD 转 换 结 果 显 示 到 CRT COMA ;二极管亮表示 “ 1”, 暗表 二极管亮表示“ , 二极管亮表示 示“0” STA PORTA ;二极管显示 转换结果 二极管显示AD转换结果 二极管显示 RTS ;返回主程序 返回主程序

异步串行通信

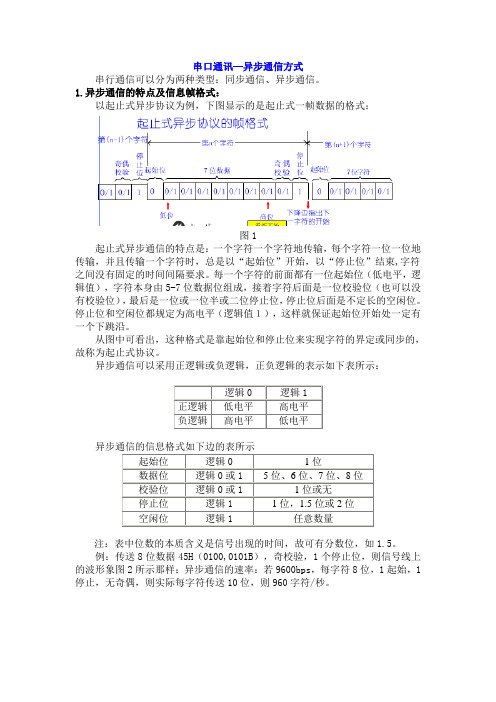

串口通讯—异步通信方式串行通信可以分为两种类型:同步通信、异步通信。

1.异步通信的特点及信息帧格式:以起止式异步协议为例,下图显示的是起止式一帧数据的格式:图1起止式异步通信的特点是:一个字符一个字符地传输,每个字符一位一位地传输,并且传输一个字符时,总是以“起始位”开始,以“停止位”结束,字符之间没有固定的时间间隔要求。

每一个字符的前面都有一位起始位(低电平,逻辑值),字符本身由5-7位数据位组成,接着字符后面是一位校验位(也可以没有校验位),最后是一位或一位半或二位停止位,停止位后面是不定长的空闲位。

停止位和空闲位都规定为高电平(逻辑值1),这样就保证起始位开始处一定有一个下跳沿。

从图中可看出,这种格式是靠起始位和停止位来实现字符的界定或同步的,故称为起止式协议。

异步通信可以采用正逻辑或负逻辑,正负逻辑的表示如下表所示:注:表中位数的本质含义是信号出现的时间,故可有分数位,如1.5。

例:传送8位数据45H(0100,0101B),奇校验,1个停止位,则信号线上的波形象图2所示那样:异步通信的速率:若9600bps,每字符8位,1起始,1停止,无奇偶,则实际每字符传送10位,则960字符/秒。

图22.异步通信的接收过程接收端以“接收时钟”和“波特率因子”决定一位的时间长度。

下面以波特率因子等于16(接收时钟每16个时钟周期,使接收移位寄存器移位一次)、正逻辑为例说明,如图3所示。

图3(1)开始通信时,信号线为空闲(逻辑1),当检测到由1到0的跳变时,开始对“接收时钟”计数。

(2)当计到8个时钟时,对输入信号进行检测,若仍为低电平,则确认这是“起始位”B,而不是干扰信号。

(3)接收端检测到起始位后,隔16个接收时钟,对输入信号检测一次,把对应的值作为D0位数据。

若为逻辑1, 作为数据位1;若为逻辑0,作为数据位0。

(4)再隔16个接收时钟,对输入信号检测一次,把对应的值作为D1位数据。

….,直到全部数据位都输入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Asynchronies Serial Communication

RS-232C Only for ASCII 3 wires connection: (25 pins D type Connector)

DTE / DCE 2 TxD 3 RxD 7 GND 4 RTS 5 CTS 6 DSR 8 DCD 20 DTR out in out in in in out TxD RxD GND RTS CTS DSR DCD DTR

OUTCH CHKSTS

Transmit

Routine OUTCH send an ASCII in B to SCI0 No

Read Status

If Empty? Yes

ORG BRCLR STAB RTS

$2000

Send [B]

OUTCH

SCI0SR1,#$80,* SCI0DRL ;Write Transmit Data to

Asynchronies Serial Communication

RS-232C

DTE ( 9 pins connector) in PC 1 protection ground 2 RxD in 3 TxD out 5 6 7 8 9 4 GND DSR RTS CTS DCD DTR

RxD (Receive Data) TxD (Transmit Data ) GND DSR RTS CTS DCD DTR

(9 pins D type Connectors)

TxD RxD GND RTS CTS DSR DCD DTR Transmit Data Receive Data Require To Send Clear To Send Data Set Ready Data Care Detected Data Terminal Ready

SCTIE=0 TCIE =0 SCRIE=0 IDLE =0 TE = 0 RE = 0 RWU =0 SBK = 0

Enable SCI0 T & R

LDAA # %00001100 ; Initial SCI STAA SCI0CR2 ; Enable T & R

OR you can use: BSET SCI0CR2, # %00001100 ;Enable T&R

Diff. Form MCU to MCU

SCI Control Register 1 : SCCR1

$CA LOOPS SCISWAI RSRC

Reset

0

0

0

M WAREILT 0 0 0

PE 0

PT 0

LOOPS=0 SCISWAI=0 RSRC =0 M=0 WARE=0 ILT =0 PE = 0 PT = 0

Nice to Use Default !

SCI Control Register 2 : SCCR2

B7

$CB SCTIE

6

5

4

3

2

1

0

TCIE SCRIE IDLE TE RE RWU SBK Transmit Buffer Empty IRQ Disabled Transmit Complete IRQ Disabled Receiver Buffer Full IRQ Disabled Idle Line IRQ Disabled Transmit Disabled Receive Disabled Receiver Is Not in Receiver Wake Up Mode Transmit Break Bit, Not Break.

(Transmit Data ) (Receive Data) (Ground) (Require to Send) (Clear to Send) (Data Terminal Ready) (Data Carry Detected) (Data Set Ready)

Ready always, or XON/XOFF protocol, ASCII only!

STAA SCI0BDL CLR SCI0CR1

Transmit & Receive with SCI

SCI States Register ($CD)

B7 $CD TDRE 6 TC 5 RDRF 4 IDLE 3 OR 2 NF 1 FE 0 PE

TDRE=1, TC RDRF=1, IDLE OR NF FE PE

(Ground) (Data Terminal Ready) (Require to Send) (Clear to Send)

in out in in out

(Data Carrier Detected)

(Data Set Ready)

No Handshake, should use XON/XOFF protocol,ASCII only

Use Macro in C : #define get_char() {_asm BRCLR $CC,#$80,*; _asm STAB $CF ; }

OUTCH

ORG LDA BITA BEQ STAB RTS $2000 #$80 SCI0SR1 CHKSTS SCI0DRL ; TDRE is at bit7 ; SCI0 Status Register ; If bit clear, check again ; Write Transmit Data to

Do Not in Self Loop Mode SCI not stopped in wait mode Receiver Source not from LOOP mode 8 Bits, not 9 Bits Wake up Mode IS Idle, Not Address Idle Counter form Start Bits No Parity If Parity, Use Even

SCI

Synchronize Communication Interface

RS-232 in S12

Asynchronies Serial Communication SCI

BUAD RATE: 1 Bit / Sec = 1 Buad (Bit Per Second, BPS) standard rate(very wide bound wades ):

SCI Based Other Communication Protocol

Modem 20 mA current loop RS-485 Local Intercommunication Network (LIN) Similar method to access other Modules like LIN, SPI, CAN, J1850, Ethernet……

Asynchronies Serial Communication

and RS-232C Signals Voltage Levers

1= -3V ~ - 15V 0 = +3V ~ + 15V (150 feet)

Signals definitions

– DTE 3 2 5 7 8 6 9 4 / DCE TxD RxD GND RTS CTS DSR DCD DTR out in out in in in out

Asynchronies Serial Communication

Use Not Return to Zero (NRZ) code T & R is synchronized by start bit detection R Clock = T Clock x 16 (baud rate x 16), slow 3,5,7 clock detect fowling edge of start bit 8,9,10 detect bit's value (Anti-Noise ) The maximum speed: bus rate /16 Duplex and Half Duplex

Discussion: 0 Not Valid! Maximum baud Rate = ?

SCI Initialization

Already did in the debug SCI0INIT LDAA #0C STAA SCI0CR2 LDAA #$9C ; Initial SCI ; Enable T & R ; Set Baud Rate to 9600 ; $4E for 19200... ; 8bit, No Parity…..Not necessary

S12 SCI Module Registers

SCI0BDH SCI0BDL SCI0CR1 SCI0CR2 SCI0SR1 SCI0SR2 SCI0DRH SCI0DRL EQU EQU EQU EQU EQU EQU EQU EQU $C8 $C9 $CA $CB $CC $CD $CE $CF ;Baud Rate Register High ; Low ;Control Register1 ;SCI Control Register 2 ;Status Register 1 ;Status Register 2(SCISR2 ;Data Register High ;SCI Data Register Low

OUTCH CHKSTS

Or: BRCLR STAB RTS SCI0SR1,#$80,* SCI0DRL ;Write Transmit in C

#define SCI0SR1 0xcc; #define SCI0DRL 0xcf; Put_Char(char a) { while ((*SCI0SR1 & 0x80) == 0); *SCI0DRL = c; }

Try if it works