SDRAM学习资料

917477-大学计算机基础-资料2-7认识DDR

DDR时代DDRSDRAM(Double Data Rate SDRAM)简称DDR,也就是“双倍速率SDRAM”的意思。

DDR可以说是SDRAM的升级版本,DDR在时钟信号上升沿与下降沿各传输一次数据,这使得DDR的数据传输速度为传统SDRAM的两倍。

由于仅多采用了下降缘信号,因此并不会造成能耗增加。

至于定址与控制信号则与传统SDRAM相同,仅在时钟上升缘传输。

DDR内存是作为一种在性能与成本之间折中的解决方案,其目的是迅速建立起牢固的市场空间,继而一步步在频率上高歌猛进,最终弥补内存带宽上的不足。

第一代DDR200规范并没有得到普及,第二代PC266DDR SRAM(133MHz时钟×2倍数据传输=266MHz带宽)是由PC133SDRAM内存所衍生出的,它将DDR内存带向第一个高潮,目前还有不少赛扬和AMD K7处理器都在采用DDR266规格的内存,其后来的DDR333内存也属于一种过度,而DDR400内存成为目前的主流平台选配,双通道DDR400内存已经成为800FSB 处理器搭配的基本标准,随后的DDR533规范则成为超频用户的选择对象。

DDR2时代随着CPU性能不断提高,我们对内存性能的要求也逐步升级。

不可否认,紧紧依高频率提升带宽的DDR迟早会力不从心,因此JEDEC组织很早就开始酝酿DDR2标准,加上LGA775接口的915/925以及最新的945等新平台开始对DDR2内存的支持,所以DDR2内存将开始演义内存领域的今天。

DDR2能够在100MHz的发信频率基础上提供每插脚最少400MB/s的带宽,而且其接口将运行于1.8V电压上,从而进一步降低发热量,以便提高频率。

此外,DDR2将融入CAS、OCD、ODT等新性能指标和中断指令,提升内存带宽的利用率。

从JEDEC组织者阐述的DDR2标准来看,针对PC等市场的DDR2内存将拥有400、533、667MHz等不同的时钟频率。

sdram知识讲解_华清远见

sdram知识讲解本篇文章为大家带来sdram知识讲解,sdram如何裸奔,希望看完对大家的学习之路有所帮助。

一、sdram的介绍SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

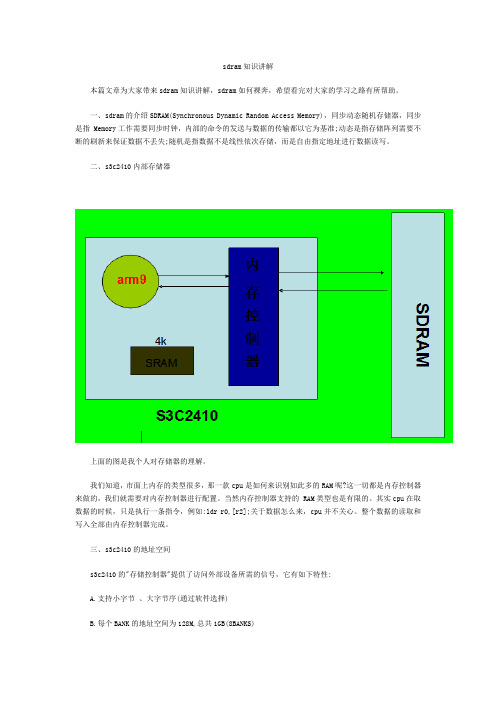

二、s3c2410内部存储器上面的图是我个人对存储器的理解。

我们知道,市面上内存的类型很多,那一款cpu是如何来识别如此多的RAM呢?这一切都是内存控制器来做的,我们就需要对内存控制器进行配置。

当然内存控制器支持的 RAM类型也是有限的。

其实cpu在取数据的时候,只是执行一条指令,例如:ldr r0,[r2];关于数据怎么来,cpu并不关心。

整个数据的读取和写入全部由内存控制器完成。

三、s3c2410的地址空间s3c2410的"存储控制器"提供了访问外部设备所需的信号,它有如下特性:A.支持小字节、大字节序(通过软件选择)B.每个BANK的地址空间为128M,总共1GB(8BANKS)C.可编程控制的总线位宽(8/16/32-bit),不过BANK0只能选择两种位宽(16/32-bit)D.总共8个BANK,BANK0-BANK5可以支持外接ROM,SRAM等,BANK6-BANK7 除可以支持ROM、SRAM外,还支持SDRAM等E.BANK0-BANK6共7个BANK的起始地址是固定的F.BANK7的起始地址可编程选择G.BANK6、BANK7的地址空间大小是可编程控制的H.每个BANK的访问周期均可编程控制I.可以通过外部的"wait"信号延长总线的访问周期 <J.在外接SDRAM时,支持自刷新(self-refresh)和省电模式(power down mode)S3C2410对外引出的27根地址线ADDR0-ADDR26的访问范围只有128MB,那么如何达到上面所说的1GB 的访问空间呢?CPU对外还引出了8根片选信号nGCS0-nGCS7,对应于BANK0-BANK7,当访问BANKx的地址空间时,nGCSx引脚输出低电平用来选中外接的设备。

SDRAM原理及应用

SDRAM原理及应用SDRAM (Synchronous Dynamic Random Access Memory) 是一种同步动态随机存取存储器,是当今计算机系统中最常用的存储器之一、它不同于传统的DRAM (Dynamic Random Access Memory),在访问数据时使用外部的时钟信号来协调存储器和控制器的运行。

1.存储单元:SDRAM由一系列的存储单元组成,每个存储单元都可以存储一个位(0或1)。

每个存储单元由一个电容和一个开关组成,电容负责存储位的值,而开关则负责读取和写入操作。

2.存储组织:SDRAM存储单元按矩阵的形式组织起来,其中每个存储单元都由一个行和一个列地址来标识。

每一行称为一个行地址空间,每一列称为一个列地址空间。

3.数据访问:在进行数据读取或写入操作时,控制器会发送相应的地址信号来选择存储单元。

这个信号包含行地址和列地址,控制器将存储单元的行地址发送给存储器,然后存储单元将该行中的所有存储单元都读取到内部缓冲区。

之后,控制器将列地址发送给存储器,并从内部缓冲区中选择相应的存储单元来读取或写入数据。

4.数据传输:在数据传输过程中,存储单元的电容会充电或放电,以表示数据的值。

读取操作会将电容的电压转换为数字信号,并传送给控制器。

写入操作则将数字信号转换为相应的电压,并充电或放电储存单元的电容。

5.时序控制:SDRAM使用外部时钟信号来控制存储器和控制器的操作,这样可以确保数据的传输和处理都在一个统一的时钟周期内完成。

1.个人计算机:SDRAM是个人计算机中最常用的内存类型。

它具有较高的数据传输速率和容量,可以满足计算机对大量数据的处理需求。

它还具有低功耗和高稳定性的特点,可以有效地提高计算机的性能和响应速度。

2.服务器和工作站:在服务器和工作站中,SDRAM通常用于存储大量的数据和处理复杂的任务。

SDRAM的高速数据传输和高容量存储能力可以帮助服务器和工作站快速处理大量的数据请求,并提供稳定的性能。

sdram工作原理

sdram工作原理

SDRAM,即同步动态随机存取存储器(Synchronous Dynamic Random Access Memory),是一种高速存储器。

它的工作原理基于许多相互关联

的电子电路组件,例如纠错代码、行/列地址选择逻辑、内部预取逻辑等。

SDRAM的主要特点是它同步工作。

这意味着SDRAM能够在内存总线时

钟信号的约束下进行工作。

SDRAM存在内部时钟,并在总线时钟的相应边

沿进行数据传输。

这种同步特性使得SDRAM能够以非常高的速度进行数据

传输。

SDRAM还具有被动刷新功能。

因为存储器中的数据不断地流失,因此SDRAM需要定期刷新它的内容以保持数据的正确性。

这个刷新过程可以通

过内部预取逻辑来完成。

即SDRAM会按照预定的规则自动预取一些数据,

以便在它们被访问时能够保持内部各种状态的正确性。

最后,SDRAM支持多通道技术,它能够同时处理多个数据包。

具体而言,SDRAM可以分为若干通道,每个通道可以同时进行一部分数据的读写

操作,从而提高存储器的带宽和吞吐量。

总之,SDRAM是一种高速存储器,它通过同步工作、被动刷新和多通

道技术来实现高效的数据传输和存储。

SDRAM内存详解(经典)

SDRAM内存详解(经典)我们从内存颗粒、内存槽位接口、主板和内存之间的信号、接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路... 虽然目前SDRAM内存条价格已经接底线,内存开始向DDR和Rambus内存过渡。

但是由于DDR内存是在SDRAM基础上发展起来的,所以详细了解SDRAM内存的接口和主板设计方法对于设计基于DDR内存的主板不无裨益。

下面我们就从内存颗粒、内存槽位接口、主板和内存之间的信号接口几个方面来详细阐述SDRAM内存条和主板内存系统的设计思路。

内存颗粒介绍对于DRAM(Dynamic Random Access Memory)内存我想凡是对于计算机有所了解的读者都不会陌生。

这种类型的内存都是以一个电容是否充有电荷来作为存储状态的标志,电容冲有电荷为状态1,电容没有电荷为状态0。

其最大优点是集成度高,容量大,但是其速度相对于SRAM (Static Random Access Memory) 内存来说慢了许多。

目前的内存颗粒封装方式有许多种,本文仅仅以大家常见的TSSOP封装的内存颗粒为例子。

其各个管脚的信号定义和我们所使用的DIMM插槽的定义是相同的,对于不同容量的内存,地址信号的位数有所不同。

另外一个需要注意的地方就是其供电电路。

Vcc和Vss是为内存颗粒中的存储队列供电,而VccQ和VssQ是为内存颗粒中的地址和数据缓冲区供电。

两者的作用不同。

我们对内存颗粒关心的问题主要是其颗粒的数据宽度(数据位数)和容量(寻址空间大小)。

而对于颗粒自检、颗粒自刷新等等逻辑并不需要特别深入的研究,所以对此我仅仅是一笔带过,如果读者有兴趣的读者可以详细研究内存颗粒的数据手册。

虽然内存颗粒有这么多的逻辑命令方式,但是由于目前北桥芯片和内存颗粒的集成度非常高,只要在布线和元器件的选择上严格按照内存规范来设计和制造,需要使用逻辑分析仪来调试电路上的差错的情况比较少,并且在设计过程中尽量避免出现这种情况。

sdram原理范文

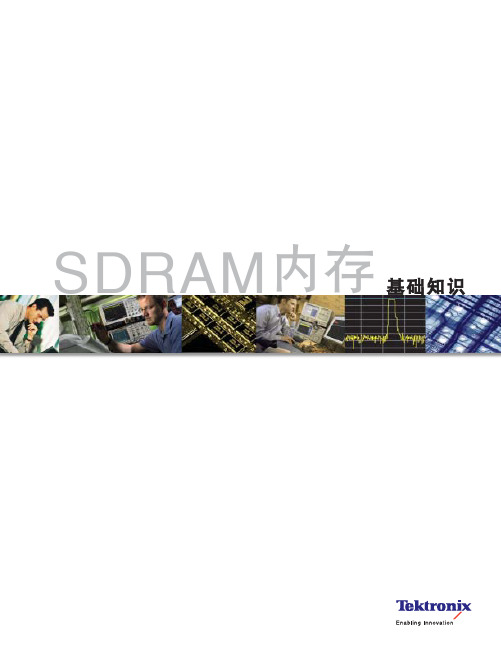

sdram原理范文SDRAM(同步动态随机存取存储器)是一种常见的计算机内存存储技术,主要用于存储和读取数据。

它是一种同步设备,其内部操作与系统时钟同步。

SDRAM的原理可以分为以下方面:1.存储单元组织:SDRAM以存储单元组成,每个存储单元由一个电容和一个寄存器组成。

电容用来存储位信息,寄存器用来控制和存储电容的电压。

2.数据读取:在数据读取过程中,SDRAM通过行列地址选择要读取的数据。

首先,内存控制器将行地址发送给SDRAM,SDRAM根据行地址选择其中一行进行读取。

然后,内存控制器发送列地址,并从选择的行中读取数据。

最后,数据传送到内存控制器,由CPU进一步处理。

3.数据写入:在数据写入过程中,与数据读取过程类似,内存控制器首先发送行地址,选择要写入的行。

然后,内存控制器发送列地址,并将要写入的数据传输到SDRAM的寄存器中。

最后,SDRAM根据内存控制器的命令,将数据存储到对应的存储单元中。

4.刷新操作:SDRAM属于动态随机存取存储器,电容中的电荷会逐渐消失,因此需要进行刷新操作,以保持数据的有效性。

SDRAM通过刷新控制线接收内存控制器的刷新命令,并定期刷新存储单元中的数据。

5.性能优化:为了提高SDRAM的性能,一些高级操作被引入。

例如,预取技术可以预先加载数据,提高数据读取速度。

再如,双端口SDRAM允许同时进行读取和写入操作,提高数据吞吐量。

6.控制信号:SDRAM通过控制信号与内存控制器进行通信。

控制信号包括时钟信号、地址信号、数据信号和命令信号,用于同步存储器的操作。

总的来说,SDRAM的工作原理是通过行列地址选择进行数据读取和写入操作,同时支持存储单元的刷新操作,以保证数据的有效性。

通过优化技术和控制信号的交互,提高了SDRAM的性能和数据吞吐量,使得它成为计算机内存存储技术中的主流。

SDRAM内存基础知识

SDRAMดࡀᒀဤSDRAM ดࡀᒀဤ۾ࣗᇕ/memory 3ഺࡴዔččččččččččččččččččččččč4-5 DRAM खᐱཋဴ4DRAM čččččččččččččččččččččč5-7SDRAM ččččččččččččččččččččč7-10DDR SDRAM 8DDR2 SDRAM 9DDR3 SDRAM 10DIMMs čččččččččččččččččččč10-15DIMM ᇕಯߛࡁ10DIMM ၫࣞ10DIMM 10DIMM ดࡀྏਜ਼Ⴅࣞ11DIMM உ৩11ࠈቲᆡᒙଶހ14ดࡀᇹᄻଐčččččččččččččččččč16-18ଐෝผ16ଐଶዩ16ଶዩݽ17SDRAM ଶዩ17ࠤܭččččččččččččččččččččč19-23SDRAMดࡀᒀဤ۾ࣗᇕዔDRAM(ࣅზႲ૦षᆰࡀ)࣪ଐཽᏋᄂܰᎌᇢೆLjፐᆐᄋ೫ਓमࡼቶถLj᎖ᒬଐႯ૦ਜ਼༊ྜྷါᇹᄻࡼࡀᇹᄻଐᒦă۾DRAMดࡀࣗᇕগ౪೫DRAMࡼগศLjᐱာ೫DRAM༅ᏴࡼᆚखᐱLj݀গ౪೫ᐏዹᄰਭଶዩখ࿖ดࡀଐăDRAMखᐱཋဴཽඣጙᒇᇧᆃଐႯ૦ดࡀܤࡻྏৎࡍĂႥࣞৎĂൈৎࢅĂᇕಯߛࡁৎቃăᑚቋኊཇᑵᅎࣅᓹDRAMଆၣݙࣥखᐱăᏴਭབྷଂฤᒦLjࣶࠨଆၣᐐ༓ጯளᅎ೫ᓍഗDRAMࡼखᐱLjྙSDRAM(ᄴݛDRAM)ĂDDR(ၷ۶ၫႥൈ)SDRAMĂDDR2(ၷ۶ၫႥൈ2)SDRAMਜ਼DDR3(ၷ۶ၫႥൈ3)SDRAMăᏴଐႯ૦ดࡀᇹᄻᒦဧࡼDIMMs(ၷᒇރดࡀෝ్)ጐጙᒇᅎࣅᓹᑚጙዝăDIMMဣሚऱښጯள࠭ऻࡀDIMM౫ᐱࡵ۞౪ࣶৈࡀDIMMਜ਼FB-DIMM(ཝෂદߡࡼDIMMs)ă݀ݙဵᒑᎌଐႯ૦ดࡀݣᎌྏৎࡍĂႥࣞৎĂൈৎࢅĂᇕಯߛࡁৎቃࡼኊཇă༊ྜྷါᇹᄻ።ጐᎌಢ႒ࡼገཇLjጐభጲဧDRAMăࡣဵLjดࡀᇹᄻᏴଐႯ૦ᒦࡼဣሚऱါݙᄴ᎖༊ྜྷါᇹᄻăጙۅႁLjଐႯ૦ดࡀڔᓤᏴభރڰDIMMLjDIMMᏴᔝᓤਭ߈ᒦ଼ܣڔᓤᏴଐႯ૦ᒦăଐႯ૦ઓభጲᏴ৪൰ଐႯ૦ᒄઁLjᄰਭᐐଝৎધDIMMဍଐႯ૦ดࡀăஉਫLjଐႯ૦ᒦဧࡼดࡀገཇࣞରྏࡩ༄ਜ਼ᆚଐႯ૦ૺᎧDIMMጙဧࡼࡩ༄ਜ਼ᆚดࡀăରྏถೆࡼᓍገऱෂᎌೝৈăጙLjดࡀܘኊରྏଐႯ૦ᒜᐆဧࡼᒬดࡀ఼ᒜǗऔLjᏴଐႯ૦ࡼᄴጙดࡀᇹᄻᒦဧݙᄴᒜᐆࡼดࡀဟLjดࡀܘኊถ৫ᑵཀྵᏥቲăఎहࡼดࡀܪᓰᎌᓐ᎖ۣᑺดࡀରྏถೆăऎ༊ྜྷါᇹᄻጙۅဧৼࢾࡼดࡀᒙLjፐࠥઓᏴ৪൰ޘອઁݙถখܤดࡀᇹᄻă༊ྜྷါᇹᄻᒜᐆభጲཝෂ఼ᒜ༊ྜྷါᇹᄻᒦဧቋᄂࢾᒜᐆࡼดࡀăᄰޟ્ဧጙଜดࡀᒜᐆࡼጙᒬᄂࢾดࡀLjᎁછ༊ྜྷါᇹᄻࡼቶถਜ਼߅۾ăஉਫLjᏴ༊ྜྷါᇹᄻᒦဣሚࣶࣞޣดࡀઑݷᔫถೆݙሷᏴଐႯ૦ᇹᄻᒦกዹᒮገăᄰਭࠎݧJEDECܪᓰࡼดࡀਖपLjJEDEC (ೊ࢟ᔇୈ߈ଐᆕᏋ્)ጙᒇᆐดࡀቲጓᄋۑᓐăJEDECဵጙଜऻ፦ಽᔝᒅLj߅Ꮛ۞౪ดࡀᒜᐆĂଐႯ૦ᒜᐆĂހ၂ᒜᐆࢀࢀăఎहࡼJEDECܪᓰਖࢾ೫ᒜᐆᏴဣሚดࡀޘອဟܘኊᔥ၆ࡼਖपLjጲܣถ৫Ꭷᒜᐆࡼดࡀਜ਼ଐႯ૦ดࡀ఼ᒜઑݷᔫăᑚቋܪᓰঙ೫ᇕಯᄂ࢛ĂDIMM࢟വۇݚĂ࢟ቧĂࡀࢾፃĂถݷᔫĂดࡀፇࢀăଶዩਜ਼ހ၂ดࡀဵ॥९JEDECਖपဵۣᑺดࡀᎧᒜᐆޘອጙభణᏥቲૺઑݷᔫࡼਈݛᒾă4 /memorySDRAM ดࡀᒀဤቤࡼDRAMଐ൸ᔗྏৎࡍĂႥࣞৎĂൈৎࢅਜ਼ᇕಯߛࡁৎቃࡼଐႯ૦ਜ਼༊ྜྷါᇹᄻดࡀገཇăஉਫLjखည೫ሆෂࡼDRAM ܤછǖดࡀྏᄋLjดࡀᄟၫᄋLjᅃखޠࣞᄋLj࢟࢟ኹሆଢ଼Lj൝࢟ኹڼ७ିቃLjဟᒩႥൈᄋLjၫႥൈᄋLjดࡀᄰࡸဣሚऱښ࠭ࡍࡼ݀ቲቧᓞሶၫ୷ࡼႥࠈቲቧLjดࡀᄰࡸၫᄋLj࢟വۇමࣞᄋࢀࢀăᑚቋखᐱཋဴࡴᒘଐཽᏋဧቤଆၣਜ਼ቤLjଐĂଶዩਜ਼ࢯ၂ᔈࡼดࡀᇹᄻăᎅ᎖ดࡀဟᒩႥൈᄋૺ൝࢟ኹڼ७ିቃLjቧᅲᑳቶৎࣶ߅ᆐభణᏥቲดࡀࡼᆰᄌăஉਫLjखᐱཋဴဵቤࡼDRAM ถ߲ሚLjጲᒮ࢛খ࿖ดࡀᇹᄻࡼቧᅲᑳቶăᑚቋถ۞౪ࣅზ఼ᒜࡼODT(ຢ࣡)LjOCD(በຢᅪདࣅ)ቅᓰૺࡒAMB(ดࡀદߡ)ࡼཝෂદߡࡼDIMM ăDRAMDRAM ୷ดࡀಢቯࡼጙৈᎁဴဵถ৫ጲIC(ૹ߅࢟വ)ඛৈดࡀᏄৎࡼ࢟വဣሚăDRAM ࡼดࡀᏄ᎖࢟ྏᓒࡀࡼ࢟ă࢜ቯࡼDRAM Ꮔဧጙৈ࢟ྏૺጙৈྯৈFET(ޝ።ᄏ)ᒜ߅ă࢜ቯࡼSRAM(ஸზႲ૦षᆰดࡀ)ดࡀᏄݧནങৈFET ୈLjଢ଼ࢅ೫ሤᄴߛࡁဟඛৈIC ࡼดࡀᏄၫăᎧDRAM ሤ܈LjSRAM ဧৎ଼ܣLjాৎྏጵLjၫषᆰဟମৎăDRAM ਖ਼ቦஉ৩ᎅࣶৈดࡀᏄᔝ߅LjᑚቋดࡀᏄॊ߅ᎅቲਜ਼ᔝ߅ࡼೝᆒᑫ(ݬᅄ1)ăषᆰดࡀᏄኊገೝݛăሌኰᑊ෭ৈቲࡼᒍLjઁᏴኡࢾቲᒦኰᑊᄂࢾࡼᒍăધ௪જႁLjሌᏴDRAM IC ดݝࣗནᑳৈቲLjઁᒍኡᐋDRAM IC I/O(ၒྜྷ/ၒ߲)ᑣ୭ገࣗནገቖྜྷকቲࡼጙăDRAM ࣗནᎌຼડቶLjጐဵႁLjᏴࣗݷᔫᒦ્ຼડดࡀᏄቲᒦࡼၫăፐࠥLjܘኊᏴকቲࡼࣗቖݷᔫஉၦဟLjڳቲၫቖૄࡵᄴጙቲᒦăᑚጙݷᔫ߂ᆐᎾߠ࢟Ljဵቲࡼᔢઁጙሲݷᔫăܘኍᅲ߅ᑚጙݷᔫᒄઁLjݣถषᆰቤࡼቲLjᑚጙݷᔫ߂ᆐਈܕࡌఎࡼቲă۾ࣗᇕ/memory 5ᅄ1.DRAMs ดࡀᏄॊ߅ᎅቲਜ਼ᔝ߅ࡼೝᆒᑫăSDRAMดࡀᒀဤ۾ࣗᇕ࣪ଐႯ૦ดࡀषᆰቲॊᇜઁܭීLjดࡀषᆰᒦᔢޟࡼಢቯဵࣗནၿኔࡼดࡀᒍăᑚဵಯࡼLjፐᆐࣗནଐႯ૦ᒎഎጙۅገ܈ၫࣗནቖྜྷৎଝޟăࠥᅪLjࡍࣶၫᒎഎࣗནᏴดࡀᒦၿኔቲLjᒇࡵखညࡵᒎഎॊᑽᄢࡵᔇಿ߈ăDRAMࡼጙৈቲ߂ᆐดࡀෂLjጙࡡࡌఎቲLjิభጲषᆰকቲᒦࣶৈၿኔࡼݙᄴࡼᒍăᑚᄋ೫ดࡀषᆰႥࣞLjଢ଼ࢅ೫ดࡀဟዓLjፐᆐᏴषᆰᄴጙৈดࡀෂᒦࡼดࡀᏄဟLjݙܘڳቲᒍᒮቤख႙DRAMăஉਫLjቲᒍဵଐႯ૦ࡼᒍᆡLjᒍဵࢅᒍᆡăᎅ᎖ቲᒍਜ਼ᒍᏴݙᄴࡼဟମख႙Ljፐࠥቲᒍਜ਼ᒍআࡵሤᄴࡼDRAMᑣ୭Ljጲଢ଼ࢅॖᓤᑣ୭ၫĂ߅۾ਜ਼ߛࡁăጙۅႁLjቲᒍߛࡁገࡍ᎖ᒍLjፐᆐဧࡼൈᎧၫᎌਈăᐁ໐ࡼDRAM፱ᎌ఼ᒜቧLjྙRAS#(ቲᒍኡᐋࢅᎌ)ਜ਼CAS#(ᒍኡᐋࢅᎌ)Ljኡᐋᒊቲࡼቲਜ਼ኰᒍݷᔫăDRAM఼ᒜቧ۞౪ኡᐋቖྜྷࣗནݷᔫࡼWE#(ቖࣅࢅᎌ)ĂኡᐋD R A MࡼC S#(በຢኡᐋࢅᎌ)ૺOE#(ၒ߲ࣅࢅᎌ)ăᐁ໐ࡼDRAM፱ᎌፊݛ఼ᒜቧLj݀ᎌᒬဟኔਖपLjঙ೫ኔਜ਼ဟମਈᇹLjጲཀྵࢾDRAMᔫෝါăᐁ໐ࡼDRAMࣗནᒲ໐ᎌ႐ৈݛᒾăጙݛLjRAS#ᎧᒍᔐሣࡼቲᒍܤࢅăऔݛLjCAS#ᎧᒍᔐሣࡼᒍܤࢅăྯݛLjOE#ܤࢅLjࣗནၫ߲ሚᏴDQၫᑣ୭ă࠭ጙݛࡵྯݛ(ᒇࡵࣗནࡼၫ߲ሚᏴDQᑣ୭)ࡼဟମဟዓ(Latency)ăᔢઁጙݛဵRAS#LjCAS#ਜ਼OE#ܤ(ݙࣅ)LjࢀࡗดݝᎾߠ࢟ݷᔫᏴຼડቶࣗནઁᅲ߅ቲၫࡼૂআᔫă࠭ጙݛఎဪࡵᔢઁጙݛஉၦࡼဟମဵดࡀᒲ໐ဟମăၤቧࡼቧဟኔᎧܟዘኔᎌਈLjဵፊݛࡼăᑚቋᐁ໐DRAMᎌᄴݛဟᒩݷᔫăDRAMดࡀᏄܘኊၮቤLjܜࣀပၫดྏăᑚገཇࣀပ࢟༄ၮቤ࢟ྏăၮቤดࡀᎅดࡀ఼ᒜঌᐊLjၮቤဟମᒎܪፐݙᄴDRAMดࡀऎݙᄴăดࡀ఼ᒜ࣪ቲᒍቲஞRAS#ክણLjቲၮቤăᏴஞRAS#ክણஉၦဟLjቲᎾߠ࢟ݷᔫLjૂআஞRAS#ክણᒦኰᒍࡼቲၫăጙۅႁLjดࡀ఼ᒜᎌጙৈቲଐၫLjၿኔည߅ஞRAS#ၮቤᒲ໐ჅኊࡼჅᎌቲᒍă6 /memorySDRAM ดࡀᒀဤၮቤݽᎌೝৈ(ݬᅄ2)ăጙৈၮቤݽဵดࡀ఼ᒜᏴၮቤᒲ໐ࡼጙৈᅃखᒦၿኔၮቤჅᎌቲLjઁڳดࡀ఼ᒜऩૄࠀಯLjጲቲᑵޟݷᔫăᏴࡵࡉᔢࡍၮቤဟମ༄Lj્खညሆጙৈၮቤݷᔫᅃखăऔৈၮቤݽဵดࡀ఼ᒜဧᑵޟࠀಯดࡀݷᔫୣᄐྸහၮቤᒲ໐ăᑚᒬၮቤऱजᏴᔢࡍၮቤဟମดᐱఎၮቤᒲ໐ăᐁ໐ࡼDRAM ዝૺဣሚ೫DRAM IC ࡼၮቤଐၫLjࠀಯၿኔည߅ࡼቲᒍăᏴDRAM IC ดݝLjၮቤଐၫဵআၒྜྷLj఼ᒜᓹดࡀᑫቲᒍăጙৈআၒྜྷᔈᅪݝᒍၒྜྷᑣ୭ࡼቲᒍăᑚৈดݝၮቤଐၫݙኊገดࡀ఼ᒜᒦࡼᅪݝၮቤଐၫ࢟വăݝॊDRAM ᏴRAS#ᒲ໐༄ᑽߒጙৈCAS#Ljጲဧดݝည߅ࡼቲᒍखၮቤᒲ໐ăSDRAM ᏴాࡵᄴݛࠀಯဟLjDRAM ࡼፊݛݷᔫࡒ೫ࣶଐᄞᐵăSDRAM(ᄴݛDRAM)ဵᆐڳDRAM ݷᔫᄴݛࡵଐႯ૦ᇹᄻݝॊLjऎݙኊገোCE#(በຢࣅࢅᎌ)ĂRAS#ĂCAS#ਜ਼WE#ܟዘᓞધၿኔࢾፃჅᎌดࡀݷᔫෝါऎଐࡼăSDRAM ᐐଝ೫ဟᒩቧਜ਼ดࡀෘഎࡼগศăดࡀෘഎࡼಢቯན᎖SDRAM ဟᒩဍዘࡼCE#LjRAS#LjCAS#ਜ਼WE#ቧᓨზăޘອᓾ೯োCE#LjRAS#LjCAS#ਜ਼WE#ቧᓨზLjጲܭৃተါහၤดࡀෘഎăಿྙLjActivate (૮)ෘഎሶSDRAM ख႙ጙৈቲᒍLjࡌఎดࡀࡼጙৈቲ(ෂ)ăઁဵጙৈDeselect(नኡ)ෘഎኔLjᏴ࣪ᒍख႙Read Write ෘഎ༄൸ᔗࢾဟገཇăጙࡡဧActivate ෘഎࡌఎดࡀࡼቲ(ෂ)LjกඐభጲᏴดࡀࡼকቲ(ෂ)ᏥቲࣶৈRead ਜ਼Write ෘഎăገཇPrecharge(Ꮎߠ࢟)ෘഎLjਈܕকቲLjઁݣถࡌఎጙቲă۾ࣗᇕ/signal_memory 7ᅄ2.DRAM ၮቤဣሚऱښ۞౪ॊݚါၮቤਜ਼ᅃखၮቤă(ᅄຢᎅMicron Technology ႊᄋ)SDRAMดࡀᒀဤ۾ࣗᇕDDR SDRAMᄰਭᄋဟᒩႥൈĂᅃखၫૺඛৈဟᒩᒲ໐ࠅ႙ೝৈၫᆡ(ݬܭ1)LjDDR(ၷ۶ၫႥൈ)SDRAMᄋ೫ดࡀၫႥൈቶถăDDR SDRAMᏴጙᄟࣗནෘഎጙᄟቖྜྷෘഎᒦᅃखࣶৈดࡀᆡᒙăࣗནดࡀݷᔫܘኊख႙ጙᄟActivateෘഎLjઁෂৌᓹጙᄟReadෘഎăดࡀᏴဟዓઁጲඛৈဟᒩᒲ໐ೝৈดࡀᆡᒙࡼၫႥൈ።ࡊᎅೝৈĂ႐ৈڭৈดࡀᆡᒙᔝ߅ࡼᅃखăፐࠥLj࠭ೝৈೌኚࡼဟᒩᒲ໐ᒦࣗན႐ৈดࡀᆡᒙLjڳ႐ৈดࡀᆡᒙቖྜྷೝৈೌኚࡼဟᒩᒲ໐ᒦăDDR SDRAMᎌࣶৈดࡀࡀెLjᄋࣶৈୣᄐྸහࡼดࡀषᆰLj࠭ऎᄋดࡀࡒăดࡀࡀెဵጙৈดࡀᑫLjೝৈดࡀࡀెဵೝৈดࡀᑫLj႐ৈดࡀࡀెဵ႐ৈดࡀᑫLjጞࠥಢᅎ(ݬᅄ3)ă႐ৈดࡀࡀెገཇೝৈᆡ᎖ดࡀᄟᒍ(BA0ਜ਼BA1)ăಿྙLjᎌ႐ৈดࡀࡀెࡼDDR SDRAMࡼᔫऱါྙሆă၅ሌLjActivateෘഎᏴጙৈดࡀࡀెᒦࡌఎጙቲăऔৈActivateෘഎᏴऔৈดࡀࡀెᒦࡌఎጙቲăሚᏴLjభጲڳReadWriteෘഎࡼྀፀᔝख႙ࡵࡌఎቲࡼጙৈดࡀࡀెऔৈดࡀࡀెăᏴดࡀࡀెࡼReadਜ਼WriteݷᔫஉၦဟLjPrechargeෘഎਈܕቲLjดࡀࡀె࣪Activateෘഎᓰ۸ኙLjభጲࡌఎጙৈቤቲăᓖፀLjDDR SDRAMገཇࡼൈᎧࡌఎቲࡼดࡀࡀెၫᎌਈăࡌఎࡼቲᏗࣶLjገཇࡼൈᏗLjቲߛࡁᏗࡍLjገཇࡼൈᏗăፐࠥLj࣪ࢅൈ።LjጙࠨᏴඛৈดࡀࡀెᒦᒑ።ࡌఎጙቲLjऎݙဵጙࠨࡌఎቲࡼࣶৈดࡀࡀెăᏴดࡀࡀెᒍᆡೌࡵดࡀᇹᄻᒦࡼࢅᒍᆡဟLjᑽߒୣᄐྸහೌኚดࡀࡀెᒦࡼೌኚดࡀᔊăᏴดࡀࡀెᒍᆡೌࡵดࡀᇹᄻᒦࡼᒍဟLjೌኚดࡀᔊᆡ᎖ᄴጙৈดࡀࡀెᒦă8 /memoryܭ1.DDR SDRAMၫႥൈਜ਼ဟᒩႥࣞăDDR SDRAM ၫႥൈดࡀဟᒩDDR-266 266Mb/s/ᑣ୭133MHzDDR-333 333Mb/s/ᑣ୭166MHzDDR-400 400Mb/s/ᑣ୭200MHzᅄ3.DDR SDAMᒦࣶৈดࡀࡀెᄋ೫षᆰഉቶLjখ࿖೫ቶถăSDRAM ดࡀᒀဤDDR2 SDRAMDDR2 SDRAM ୷DDR SDRAM ᎌࣶࠀখăDDR2 SDRAM ဟᒩႥൈৎLj࠭ऎᄋ೫ดࡀၫႥൈ(ݬܭ2)ăႲᓹဟᒩႥൈᄋLjቧᅲᑳቶ࣪భణࡼดࡀݷᔫܤࡻᏗᏗᒮገăႲᓹဟᒩႥൈᄋLj࢟വۇࡼቧਜ૭ܤ߅ࠅၒሣLjᏴቧਜ૭ᆘᑵཀྵݚਜ਼࣡ܤࡻৎଝᒮገăᒍĂဟᒩਜ਼ෘഎቧࡼ࣡ሤ଼࣪ීLjፐᆐᑚቋቧဵሶࡼLj݀࣡Ᏼ࢟വۇăၫቧਜ਼ၫኡᄰဵၷሶࡼăดࡀ఼ᒜᒦቦᏴቖྜྷݷᔫᒦདࣅᑚቋቧLjDDR2 SDRAM ᏴࣗནݷᔫᒦདࣅᑚቋቧăࣶৈDDR2 SDRAM ೌࡵᄴጙৈၫቧਜ਼ၫኡᄰLjጙݛᄋ೫আᏭࣞăࣶৈDDR2SDRAM భጲᆡ᎖ดࡀᇹᄻሤᄴࡼDIMM Ljጐభጲᆡ᎖ดࡀᇹᄻݙᄴࡼDIMM ăஉਫLjၫਜ਼ၫኡᄰདࣅਜ਼၃૦ݙࣥܤછLjᄏན᎖ࣗན/ቖྜྷݷᔫૺषᆰࡼဵৈDDR2SDRAM ăᄰਭᄋODT(ຢ࣡)Lj݀ᄋODT ቧLjဣሚຢ࣡Lj݀ถ৫ဧDDR2 SDRAM ౫ᐱෝါࡀ࣪ຢ࣡ᔜᒋቲܠ߈(75๏Ă150๏ࢀࢀ)LjDDR2 SDRAM খ࿖೫ቧᅲᑳቶăຢ࣡ᔜᒋਜ਼ݷᔫᎅดࡀ఼ᒜᒦቦ఼ᒜLjᎧDDR2 SDRAM DIMM ࡼᆡᒙૺดࡀݷᔫಢቯ(ࣗནቖྜྷ)ᎌਈăODT ݷᔫࡴᒘৎੑࡼቧᅲᑳቶLjဧၫᎌࠊాࠎৎࡍࡼዛᅄLjᄴဟᄋ࢟ኹĂᄋᓞધႥൈĂଢ଼ࢅਭߡĂଢ଼ࢅISI(൩ମছཷ)ăDDR2 SDRAM Ᏼ1.8V ݷᔫLjଢ଼ࢅ೫ดࡀᇹᄻࡼൈLjᑚጙൈဵDDR SDRAM ࡼ2.5V ൈࡼ72%ăᏴ෭ቋဣሚऱښᒦLjቲᒦࡼၫጯளሆଢ଼LjဧᏴᎌࡼቲࣗནቖྜྷဟଢ଼ࢅ೫ൈăଢ଼ࢅᔫ࢟ኹࡼጙৈᎁဴဵଢ଼ࢅ೫൝࢟ኹڼ७ăᏴᓞધႥൈሤᄴဟLj࢟ኹڼ७ሆଢ଼્ᄋ൝ᓞધႥࣞLjᑽߒৎࡼဟᒩႥൈăࠥᅪLjၫኡᄰభጲܠ߈ᆐތॊቧăဧތॊၫኡᄰቧଢ଼ࢅ೫ᐅဉĂࠈཷĂࣅზਜ਼EMI(࢟ࠟছཷ)Ljᄋ೫ᐅဉăDDR2 SDRAM ౫ᐱෝါࡀభ࣪ތॊ࣡ၫኡᄰቲᒙăDDR2 SDRAM ྜྷࡼጙᒬቤถဵএଝဟዓLjဧࡻดࡀ఼ᒜᒦቦถ৫ᏴActivate ෘഎઁLjৎഉख႙Read ਜ਼Write ෘഎăᑚᎁછ೫ดࡀᅔᅊLjᄰਭဧDDR2 SDRAM ౫ᐱෝါࡀ࣪এଝဟዓܠ߈ᒙăDDR2 SDRAM ဧڭৈดࡀࡀెLjᄋࡵ1Gb ਜ਼2Gb DDR2 SDRAM ࡼၫࡒăᄰਭୣᄐྸහݙᄴࡼดࡀࡀెݷᔫLjڭৈดࡀࡀహహᄋ೫षᆰࡍቯดࡀDDR2 SDRAM ࡼഉቶăࠥᅪLj࣪ࡍቯดࡀLjDDR2 SDRAM ᑽߒᔢࣶڭৈดࡀᅃखޠࣞăDDR2 SDRAM ޘອᓾ೯ᎌ100ࣶLjᓍገถဵᆸඣෂࡼDDR2 SDRAM ถăྙኊ೫ஊᅲᑳࡼถૺݷᔫᇼஂLj༿ݬᏞDDR2 SDRAM ޘອᓾ೯ă۾ࣗᇕ/memory 9ܭ2.DDR2 SDRAM ၫႥൈਜ਼ဟᒩႥࣞăDDR2 SDRAM ၫႥൈดࡀဟᒩDDR2-400 400Mb/s/ᑣ୭200MHz DDR2-533 533Mb/s/ᑣ୭266MHz DDR2-667 667Mb/s/ᑣ୭333MHz DDR2-800 800Mb/s/ᑣ୭400MHzSDRAMดࡀᒀဤ۾ࣗᇕDDR3 SDRAMDDR3 SDRAMዝިᏗ೫DDR2 SDRAMࡼቶถăDDR3SDRAMᑽߒሆጙৎࡼၫႥൈਜ਼ဟᒩႥࣞ(ݬܭ3)ăᎾଐܤછ۞౪ǖDDR3 SDRAMᔫ࢟ኹଢ଼ࢅࡵ1.5VLjᑚဵDDR2 SDRAM 1.8Vᔫ࢟ኹࡼ83%ăDDR3 SDRAMဵFB-DIMM2(ཝෂદߡࡼDIMM2)ဣሚऱښገဧࡼดࡀăDDR3 SDRAMਖपᑵᏴఎखᒄᒦLjᏴJEDECຒᓰᒄ༄થ્ܤછăิభጲଝྜྷJEDEC DDR3 SDRAMॊ્()LjۑᓐఎखDDR3 SDRAMਖपLjิభጲପހJEDECᆀᐶဵ॥ᐽᄣຒᓰࡼDDR3 SDRAMਖपăDIMMsၷᒇރดࡀෝ్(DIMMs)ဵଐႯ૦ဧࡼރྜྷါดࡀෝ్ăDIMMsᎌݙᄴࡼᇕಯߛࡁĂดࡀၫࣞĂĂดࡀྏĂดࡀႥࣞਜ਼ดࡀஉ৩ăJEDECጯளਖࢾ೫DIMMsܪᓰLj݀ଖኚᔫLjጲਖࢾ᎖ቤࡼดࡀಢቯਜ਼ดࡀஉ৩ࡼቤቯDIMMsăDIMMᇕಯߛࡁგါ૦Ăᔫᐶਜ਼ॲᇗᒦဧܪᓰDIMMߛࡁăSO-DIMMs(ቃቯDIMM)ဵ᎖܊۾࢟ฎਜ਼హମᎌሢࡼဣሚऱښᒦࡼቃቯDIMMăઉࢳᒙᒎࡼဵᎧଐႯ૦ᓍۇຳቲࡼೝৈSO-DIMMLjܟᏏೌጞࠨሤăሯሷጙሆೝৈܟᏏೌᔫᆐઉࢳᄏLjSO-DIMMᔫᆐᐱఎࡼઉࢳߝ۔ăධฝDIMMs(ᆈቯDIMMs)܈SO-DIMMቃLj᎖ۇଐႯ૦ᒦăVLP-DIMMs (ިቃቯDIMM)ࡼࣞ୷Lj᎖ຢॲᇗᒦăDIMMၫࣞDIMMၫࣞན᎖ECC(ெࡇ൩)ᑽߒăECCဵଶހਜ਼ቅᑵࡇᇙࡼ8ৈቅዩᆡăܪᓰDIMM ၫࣞᏴᎌECCဟᆐ64ᆡLjᏴᎌ8ৈECCᆡဟᆐ72ᆡăDIMMဵDIMMᅲᑳࡼጙᔝดࡀ۸Ljᑽߒ64ৈၫᆡࡒECCဟᑽߒ72ৈᆡăೝৈဵDIMMೝᔝดࡀ۸ă႐ৈࣩဵDIMM႐ᔝดࡀ۸ăܭ4መာ೫ᎌECCဟᑽߒ64ᆡၫࣞࡼD I M MᎌࣶৈดࡀI CăᏴ෭ৈ࢛LjDIMMೝݾᎌᆐჅᎌดࡀICᄋᔗ৫ࡼహମăᆐஊᑚৈᆰᄌLjดࡀICᏴࢻݝሤઑࣧࢶă10 /memoryܭ3.ᎾଐࡼDDR3 SDRAMၫႥൈਜ਼ဟᒩႥࣞăDDR3 SDRAM ၫႥൈดࡀဟᒩDDR3-800 800Mb/s/ᑣ୭400MHzDDR3-1066 1066Mb/s/ᑣ୭533MHzDDR3-1333 1333Mb/s/ᑣ୭667MHzDDR3-1600 1600Mb/s/ᑣ୭800MHzܭ4.᎖DIMMࡼᒦඛৈDIMMࡼดࡀICၫ(ᎌECC)ਜ਼ඛৈดࡀICࡼၫI/OၫăDIMM ඛৈIC 4ৈI/O ඛৈIC 4ৈI/O ඛৈIC 4ৈI/O1ৈ16ৈIC 8ৈIC 4ৈIC2ৈ32ৈIC 16ৈIC 8ৈIC4ৈ64ৈIC 32ৈIC 16ৈICDIMM ดࡀྏਜ਼ႥࣞDIMM ดࡀྏན᎖ဧࡼดࡀIC ࡼྏਜ਼DIMM ᒙă512M b (ᑏᆡ)ดࡀI C భጲଐ߅ݙᄴࡼᒙ(ݬܭ5)ăD I M M Ⴅࣞན᎖D I M M ဧࡼD D R ĂD D R 2ਜ਼D D R 3SDRAM ᑽߒࡼဟᒩႥࣞăDIMM உ৩DIMM ᓍገஉ৩ᎌྯৈǖUDIMMs LjRDIMMs ਜ਼FB-DIMMs ăඛৈDIMM உ৩࣒ᎌᔈࡼᎁ࢛ਜ਼ሢቶăUDIMM ဵऻࡀDIMM ăUDIMM ݙદߡDIMM ࡼDDR ĂDDR2ਜ਼DDR3 SDRAM ቧ(ݬᅄ4)ăUDIMM ဵጙৈDIMM ဣሚऱښă࣪ၷDIMM ดࡀᇹᄻLjUDIMM ࡼႥࣞᔢLj߅۾ᔢࢅăดࡀ఼ᒜᒦቦᒇ఼ᒜჅᎌDRAM ቧăUDIMM ᎌદߡࡀLjݙ્ዓߕดࡀ఼ᒜᒦቦਜ਼ᏴUDIMM ࡼSDRAM ᒄମࡼቧăดࡀ఼ᒜᒦቦดࡀᄰࡸ፱ᎌࡼUDIMM ၫ၊ࡵቧᅲᑳቶሢᒜăሆၤፐႤ્ଢ଼ࢅቧᅲᑳቶǖᄋดࡀဟᒩႥࣞLjᄋਜ૭ޠࣞLjᄋดࡀᄰࡸUDIMM ၫLjᄋUDIMM ࡼၫăดࡀ఼ᒜᒦቦއఘඛৈೌĂඛᄟਜ૭Ăඛᄟਜ૭ॊᑽਜ਼ඛৈSDRAM ᑣ୭ăၥᑼஉ৩ࡼᔜఝᆰᄌሢᒜᓹดࡀᄰࡸభጲభణᏥቲࡼဟᒩຫൈਜ਼UDIMM ၫăݧࣖดࡀᄰࡸࡼดࡀ఼ᒜᆐᄋดࡀᇹᄻᒦࡼUDIMM ၫᄋ೫ጙᄟᅆăೝᄟࣖࡼดࡀᄰࡸభጲᑽߒೝৈႥUDIMM LjඛᄟดࡀᄰࡸጙৈUDIMMăܭ5.ݙᄴࡼ512Mb(ᑏᆡ)ดࡀIC ᒙဣಿăෂߛࡁI/Oᑣ୭ၫดࡀࡀె32Mb 4 416Mb 8 48Mb 16 4ᅄ4.UDIMM ᏴDIMM ᎌદߡDRAM ቧăRDIMMဵࡀၷᒇރดࡀෝ్ăRDIMMᄰਭદߡRDIMMࡼRDIMM SDRAMဟᒩĂෘഎቧਜ਼ᒍቧLjିၥᑼஉ৩ᆰᄌ(ݬᅄ5)ăဟᒩቧဧჄሤણ(PLL)દߡLjෘഎቧਜ਼ᒍቧဧࡀჄࡀᓤᒙદߡă࢜ቯࡼࡀDIMMဧጙৈPLL ICૺೝৈࡒࡀࡼICဣሚăดࡀ఼ᒜᒦቦဟᒩĂෘഎቧਜ਼ᒍቧއఘᓍۇਜ૭ĂD I M MೌĂRDIMMࡀਜ਼RDIMM PLLࡼᔜఝăᑚଢ଼ࢅ೫ၥᑼஉ৩LjభጲᏴดࡀᄰࡸဧৎࣶࡼRDIMMLjᄋ೫Ⴅࣞă࣪ၷሶDQၫሣਜ਼DQSၫኡᄰሣLjᎌદߡଢ଼ࢅቧঌࡼᎁဴăࠥᅪLjRDIMMดࡀྜྷဟମ܈UDIMMൻጙৈဟᒩᒲ໐Ljፐᆐገཇጙৈဟᒩᒲ໐Ljڳෘഎਜ਼ᒍቧჄࡀࡵRDIMMࡼࡀᒦăF B-D I M MဵཝෂદߡࡼD I M MăF B-D I M MဧD D R2SDRAMLjFB-DIMM2ဧDDR3 SDRAMăჅᎌDDR2SDRAMsਜ਼DDR3 SDRAMsቧ࣒ᏴFB-DIMMਜ਼FB-DIMM2ᒦࡒᎌAMB(ดࡀદߡ)ࡼIC࠭ดࡀᇹᄻᒦદߡ(ݬᅄ6)ăFB-DIMMਜ਼FB-DIMM2ဧݙᄴࡼAMBăᅄ5.RDIMMદߡDIMMࡼDRAMဟᒩĂෘഎቧਜ਼ᒍቧăᅄ6.FB-DIMMદߡFB-DIMMࡼDDR2 SDRAMቧăᅄ7.FB-DIMM࢛ࡵ࢛Ⴅࠈቲஉ৩ăดࡀ఼ᒜᒦቦܟጙৈFB-DIMM ဧᔢࣶ24࣪ႥތॊቧLjᎧดࡀ఼ᒜᒦቦᄰቧLjᄴဟဧᔢࣶ24࣪ႥތॊቧLjᎧሤࡼFB-DIMM ᄰቧ(ݬᅄ7)ăᑚቋቧဵሶࡼLj࢛ࡵ࢛ࡼLjဧႥࠈቲଆၣLjख႙ෘഎਜ਼ၫă10࣪ቧڳฉሶጓᇗ࠭ดࡀ఼ᒜᒦቦࠅ႙ࡵAMB Lj12-14࣪ቧڳ۱ሶጓᇗ࠭AMB ሶૄࠅ႙ࡵดࡀ఼ᒜᒦቦăFB-DIMM உ৩ᔥ၆ሆෂࡼሚࡔႥၫᔊଐखᐱཋဴLjᎌጙቋ࢛ࡵ࢛Ⴅࠈቲᄰവஉ৩ࡔᄐ݀ቲᔐሣࡼၥᑼஉ৩ăFB-DIMM உ৩ᒒᏴጲཝݝดࡀႥࣞᄰਭAMB ࠭FB-DIMM ࡼDDR2ดࡀࠅ႙ၫLjઁࠅ႙ࡵࠈቲ۱ሶ࢛ࡵ࢛ቧLjઁࠅ႙ࡵดࡀ఼ᒜᒦቦăࠈቲᑷޠ12ᆡLjࣞᆐ10ᄟฉሶቧᄰവࡵ14ᄟ۱ሶቧᄰവăᏴጙৈDDR2ဟᒩᒲ໐ᒦࠅ႙12ৈࠈቲᆡăፐࠥLjิభጲڳDDR2ဟᒩຫൈ߇ጲ12LjࡻࡵႥࠈቲᄰവࡼၫႥൈăጐభጲڳDDR2ၫႥൈ߇ጲ6LjࡻࡵႥࠈቲᄰവࡼၫႥൈ(ݬܭ6)ăଐႯ૦ᓍۇดࡀᇹᄻဟᒩဵDDR2ဟᒩࡼጙۍăAMB ᄋ೫PLL ถLjጲೝ۶ࡼႥࣞདࣅDDR2 SDRAM ဟᒩăฉሶᄰവၫৼࢾᏴ10Lj۱ሶᄰവၫᏴ12-14ᒄମăభጲڳᄰവၫ߇ጲ12ৈࠈቲᆡLjࡻᑷᒦࡼᆡၫ(ݬܭ7)ăฉሶᄰവৼࢾᏴ10ৈLjፐࠥඛৈᑷᎌ120ৈᆡăোFB-DIMM ဵ॥ဧECC ૺဧࡼࠈቲCRC ᆡၫLj۱ሶᄰവၫ્ܤછăಿྙLjᏴᎌECC ဟLjኊገᏴጙৈ۱ሶᑷᒦࠅ႙ೝৈ64ᆡᔊ(ᔐᆡၫᆐ2x64=128ᆡ)ă12ᄟ۱ሶᄰവĂඛৈᑷᔐৢ144ᆡభጲࠀಯᑚጙၫႥൈăጙऱෂLjᏴᎌECC ဟLjኊገᏴጙৈ۱ሶᑷᒦࠅ႙ೝৈ72ᆡᔊ(ᔐᆡၫᆐ2x72=144ᆡ)ăኊገ13ᄟ14ᄟ۱ሶᄰവLjፐᆐ12ᄟ۱ሶᄰവĂඛৈᑷ144ᆡᔐᆡၫᎌᆐ144ৈၫᆡᅪଝࠈቲCRC ᆡᄋᔗ৫ࡼᆡၫăܭ7.FB-DIMM ࠈቲၫ۱ሶᑷࡼޠࣞན᎖ဧࡼ۱ሶᄰവၫăᄰവၫጙৈࠈቲᑷᒦࡼᆡၫ10ᄟฉሶᄰവ12012ᄟ۱ሶᄰവ14413ᄟ۱ሶᄰവ15614ᄟ۱ሶᄰവ168ܭ6.FB-DIMM ࢛ࡵ࢛ࠈቲᄰവࡼࠈቲၫႥൈན᎖FB-DIMM ࡼDDR2 SDRAM ࡼႥࣞăDDR2 SDRAM ၫႥൈDDR2ဟᒩࠈቲၫႥൈDDR2-533 533Mb/s/ᑣ୭266MHz 3.2Gb/s DDR2-667 667Mb/s/ᑣ୭333MHz 4.0Gb/s DDR2-800 800Mb/s/ᑣ୭400MHz 4.8Gb/sጙᄟFB-DIMMᄰࡸᑽߒᔢࣶڭৈFB-DIMMăFB-DIMMᓍۇݚገৎଝ଼ܣLjፐᆐดࡀ఼ᒜᒦቦᒑኊገඛᄟᄰࡸ24ᄟႥቧਜ૭Ljᑚቋਜ૭ࡼਜ૭ޠࣞݙጙࢾሤᄴăࡣဵLjUDIMMsRDIMMsኊገᔈดࡀ఼ᒜᒦቦࡼࡍࡼ݀ቲቧ(ෘഎLjᒍLjၫࢀࢀ)Ljᑚቋਜ૭ޠࣞܘኍປLjጲᑵཀྵᏥቲăᎅ᎖ି೫ඛᄟดࡀᄰࡸࡼFB-DIMMቧၫૺ଼છ೫࢟വۇਜ૭ݚLjดࡀ఼ᒜᒦቦభጲᑽߒৎࣶࡼFB-DIMMดࡀᄰࡸ(ݬᅄ8)ăᑚፀᆜᓹৎࡼดࡀࡒLjፐᆐభጲᄴဟ૮ඛᄟดࡀᄰࡸăFB-DIMM༄ᑵ᎖ॲᇗᒦLjገཇऻޟࡍࡼดࡀᇹᄻăᎾଐ࣡ᔫᐶጐဧF B-DIMMsăࠈቲࡀᏴᑤހჅᎌଐႯ૦DIMM࣒ᎌࠈቲࡀᏴᑤހ(SPD)ถLjᏴଐႯ૦ఎ૦ਭ߈ᒦᆐଐႯ૦BIOSᄋDIMMดࡀᒙቧᇦLjྙดࡀྏĂႥࣞĂဟዓĂဟኔĂᒜᐆࢀࢀ(ݬܭ8)ăᏴఎ૦ဟLjB I O S(۾ၒྜྷၒ߲ྟୈ)ဧS P DถࣗནඛৈDIMMࡼᒙቧᇦăઁဧᑚቋቧᇦᒙดࡀ఼ᒜᒦቦૺඛৈUDIMMਜ਼RDIMMࡼDRAMෝါਜ਼౫ᐱෝါࡀăJEDECܪᓰਖࢾ೫SPDถă࣪UDIMMsਜ਼RDIMMsLjSPDถᏴቃቯऻጵပดࡀICᒦဣሚLjࡒᎌࢅႥI2CాLjᆡ᎖ඛৈDIMMăᓍۇᎌጙৈI2CాLj࣪ඛৈDIMMރݹᎌጙৈᆎጙࡼᒍ(0-7)ăᏴఎ૦ဟLj્ဧI2CాቅዩඛৈDIMMރݹăྙਫࡀᏴDIMMLjกඐBIOSࣗནSPDᒋă࣪FB-DIMMsLjSPDถᏴAMBᒦဣሚLjAMBᎌI2CాăFB-DIMM I2Cా߂ᆐSMbus (ᇹᄻಯᔐሣ)ăSMbusᏴඛৈFB-DIMMᒦᒙAMBăᅄ8.FB-DIMMดࡀ఼ᒜᒦቦᑽߒ႐ᄟᄰࡸLjඛᄟᄰࡸᎌᔢࣶڭৈFB-DIMMsăဧ1GB FB-DIMMsభถᔐৢᎌ32GBࡼᇹᄻดࡀăᑚభጲဧ4GB FB-DIMMs଼ܣᐐޠࡵ128GBăᑚඐࡍࡼดࡀྏ࣪ቶถॲᇗਜ਼࣡ᔫᐶᇢೆăᔊஂၫถහၤSPDလങᒜᒋ0ࢾፃ೫ቖྜྷෝ్ᒜᐆࠈቲดࡀᒦࡼᔊஂၫ80 1SPDดࡀᔊஂᔐၫ08 2۾ดࡀಢቯ(FPMEDO)0102 3ดࡀ۸ࡼቲᒍၫ0C 4ดࡀ۸ࡼᒍၫ0A 5ᑚৈดࡀෝ్ᒦࡼᇕಯดࡀࡀెၫ01 6ᑚৈෝ్ࡼၫࣞ40 7ၫࣞ(ኚ)00 8ෝ్࢟ኹా࢟ຳ01 9ᑚৈᔝୈࡼRASྜྷဟମ3C 10ᑚৈᔝୈࡼCASྜྷဟମ0F 11ෝ్ெࡇᒙಢቯ(ऻໜ๔ቶ,ໜ๔ቶ,ECC)000102 12ၮቤႥൈ/ಢቯ0083 13ጙDRAMࣞ10 14ெࡇDRAMၫࣞ00 15-61Ꮎഔ0062SPDኀࢿ00 63ᔊஂ0-62ቅዩਜ਼ଐႯࡻ߲64ᒜᐆJEDEC IDࡔ൩2C 65-71ᒜᐆJEDEC IDࡔ൩(ኚ)00 72ᒜᐆᆡᒙ01-0873-90ᒜᐆݝୈܠభܤ91PCBဤܰ൩01-09 92PCBဤܰ൩(ኚ)0093ᒜᐆฤ॑భܤ94ᒜᐆᒲభܤ95-98ෝ్ኔభܤ99-125ᒜᐆᄂࢾၫభܤ126-127Ꮎഔ00128-255ᎌࢾፃఎहઓᔈᎅܭৃFFܭ8.ଐႯ૦BIOSဧࠈቲࡀᏴᑤހ(SPD)ాࣗནDIMMᒙăJEDECܪᓰਖࢾ೫SPDၫăดࡀᇹᄻଐޘອଐࡼ༄ଂݛဵޘອገཇĂޘອஉ৩ଐਜ਼ᔇᇹᄻଐăᔇᇹᄻଐᒄጙဵดࡀᇹᄻăดࡀᇹᄻଐན᎖ดࡀྏĂႥࣞĂൈĂሚᎌܪᓰĂቤࡼᑵᏴखᐱࡼܪᓰĂᒮሚᎌଐૺገཇăଐႯ૦በຢᔝᒜᐆ࣪ଐႯ૦ดࡀᇹᄻଐᎌᓹ੪ࡍ፬ሰă෭ቋଐႯ૦በຢᔝᒜᐆᎌᔈࡼހ၂߈ኔĂଶዩഗ߈ਜ਼ޘອހ၂ᇴۂăጙۅႁLjᑚቋଐႯ૦በຢᔝᒜᐆࡼᆀᐶ્ීᄰਭରྏถೆހ၂ࡼดࡀޘອăଐෝผดࡀᇹᄻଐࡼጙৈਈݝॊဵଐෝผă࣪ดࡀᇹᄻཝෂቲෝผࡼᒮገቶݙభࢅৰăளዩܭීLj࢟ᔜᒋᒑဵܤછଂ๏Ljభถ્ดࡀᇹᄻࡼభణᏥቲࡒීመ፬ሰăดࡀᇹᄻଐෝผ።۞౪ೌࡵᏇቯดࡀᇹᄻဟྀੜጥࡴᒘࡼყހঌᏲࡼ፬ሰăྙਫᏇቯᎅ᎖ყᄿঌᏲऎᄫᒏᏥቲLjଶዩਜ਼ࢯ၂ഗ߈ऻޟ౩ซăࠥᅪLjෝผ።ဧጥყᄿঌᏲLjॊᇜყᄿހ၂࢛ࡼቧăၫᎌࠊాዘᓹ࠭ดࡀ఼ᒜᒦቦདࣅࡵSDRAMᑣ୭ࡼቧਜ૭ܤછăყހ࢛።భถణத၃૦ᑣ୭Ljጲܣጥถ৫መာ၃૦އఘࡼቧăᎌဟᑚဵݙభถࡼLjገဧดރĂހ၂း࢟വۇਜ਼ᓜყހଚਜ਼ॺᓐᓤᒙLjଶჃ੪ซࡻࡵࡼቧăቧෝผᒦጐ።۞౪ᑚቋყހॺᓐᓤᒙLjጲ೫ஊ࣪SDRAMቧૺቧހࡼ፬ሰăଐଶዩᏴଐᒦဧቤࡼDRAMถገཇဧቤࡼଐऱजਜ਼ଆၣLj۞౪ଐෝผቤଆၣૺቤࡼBIOSݷᔫăஉਫLjDRAMଐဣሚऱښገཇཝෂଶዩਜ਼ހ၂Lj۞౪࢟വۇ৩ࡵྟୈݷᔫLjጲۣᑺดࡀభణᏥቲăྙਫดࡀᇹᄻᎅ᎖ଐဣሚऱښᎌཝෂଶዩऎखညਿႲ૦ࡇᇙLjกඐޘອభణቶ્ሆଢ଼ăࠥᅪLjఱઓభถገཇޘອ൸ᔗJEDECᒜᐆਖࢾࡼᒬጙᒘቶހ၂ገཇăଶዩݽ፱ᎌጙৈݽLjኸႥࢯ၂ྀੜଐဣሚऱښᒦࡼଐᆰᄌऻޟᒮገăଝޘອఎखᒲ໐ገཇᏴଐᒦᄋ༄ਖચଶዩ/ࢯ၂ăਖચᒦ።ཀྵࢾሆၤገཇǖljቋဵቤࡼଐᏄǛቋဵᒮࡼଐᏄǗljᏴਭབྷࡼଐገܜቋᏄǛገখܤቋᏄǛljኊገဠඐࢀࡼଶዩਜ਼ހ၂Ǜހ၂ဵ॥ገཇᓜݷᔫෝါቧ൩ቯǛljኊገቋᓜଐถǛ(ྙყހ࢛ހ၂ଚ)ෝผॊᇜဵ॥ጯளఠ೫ყހਜ਼ᏇቯǛဵ॥ኊገቧᏎǛဵ॥ኊገᓜྟୈ࣪፮ୈᒊቲހ၂Ǜljኊገቋણஹހ၂Ǜ(ྙᆨࣞLjဘࣞࢀ)ljኊገއఘቋ࢟വݷᔫቧᇦĂጲቲࢯ၂Ǜljገཇቋजਖܪᓰހ၂Ǜဵ॥ဧଶዩ/ࢯ၂ހ၂࢛Ljހ၂ᏴᒜޘອǛဵ॥ဧଶዩ/ࢯ၂ހ၂࢛ᆒኀဧᒦࡼޘອǛᐏዹಯ༄ݙᒀࡸࡼሲᒦࡼज़ሙǛಿྙLj෭ቋଶዩݽ۞౪৩ጙৈଶዩᏇቯLjᒦᎌࡍࡼყހހ၂࢛LjଶዩࡒᎌቤቯASIC/FPGA ࡼቤᇹᄻஉ৩ăଶዩᏇቯᔢੑጲཝႥᏥቲLjጲଶዩႥݷᔫਜ਼ቶถăআᏭࡼଐገཇৎଝཝෂއఘဣဟݷᔫLjጲኸႥཀྵࢾᆰᄌăጙࡡଶዩᏇቯᑵཀྵᏥቲ݀ᅲ߅ଶዩLjభጲৎࡼހ၂࢛ဣሚᔢᒫᏇቯăSDRAM ଶዩDRAM ଶዩਜ਼ހ၂ଆၣጞ౷ଐሲăDRAM ଐభॊᆐሆၤಢቯǖଐႯ૦ดࡀ఼ᒜᒦቦIC LjดࡀIC LjAMB ICs LjDIMMs LjଐႯ૦ᓍۇਜ਼༊ྜྷါᇹᄻăඛৈޘອಢቯ࣒ገཇݙᄴࡼଶዩݽĂݙᄴࡼଶዩހ၂ਜ਼ݙᄴࡼހ၂۸ăಿྙLjดࡀIC ଐཽᏋݙ્ଶዩ࢟വۇஉ৩LjऎDIMM ଐཽᏋᐌገଶዩDIMM ࢟വۇஉ৩ăᎅ᎖ࠀಯᄂࢾࠀಯࡼገཇૺࣖᄂࡼ༊ྜྷါᇹᄻၒྜྷ/ၒ߲ᒙLjดࡀ఼ᒜጙۅဵᎅ༊ྜྷါᇹᄻଐཽᏋଐࡼăஉਫLjଐᔫࡼීመᔝ߅ݝॊဵଐดࡀ఼ᒜૺଐดࡀ఼ᒜਜ਼ดࡀIC ᒄମࡼ࢟വۇݚăଶዩᑚݝॊଐ࣪భణᏥቲᒗਈᒮገăDRAMଶዩਜ਼ހ၂ଆၣገཇጙᇹހ၂ހ۸Ljྙནዹာ݆Ăာ݆Ă൝ॊᇜጥĂყᄿĂހ၂ଚĂॊᇜྟୈĂጙᒘቶހ၂ྟୈࢀࢀ(ݬܭ9)ăހ၂۸ܘኊᆐ࢟ቧਜ਼ፇށᄋறཀྵࡼყހĂறࣞݧૹਜ਼ᅲᑳࡼᇹᄻއఘถೆăᆐۑᓐଐཽᏋኸႥଶዩดࡀݷᔫLjથኊገ༓ࡍࡼॊᇜถăဧ൝ॊᇜጥପހଐႯ૦ᇹᄻ༊ྜྷါᇹᄻࠎᐆ೫ጙৈ༓ࡍࡼଶዩਜ਼ࢯ၂ఎखણஹă൝ॊᇜጥৌᔍਜ਼ਈೊࠀಯᔐሣࣅĂดࡀࣅਜ਼ၒྜྷ/ၒ߲ݷᔫă൝ॊᇜጥᎌཝෂࡼᇹᄻቧᇦLjᄋ೫ਈࡼଐ࣊ފೆLjጲއఘဣဟᇹᄻݷᔫăࠥᅪLjဧာ݆ਜ਼൝ॊᇜጥᔏყހĂ߿खਜ਼መာถభጲᏴᄴጙৈືࡼྟୈܭĂፇܭĂၫᔊ݆ተਜ਼ෝผ݆ተᒦཝෂއఘଐቧᇦăஉਫLjᄋ೫༓ࡍĂཝෂĂࡼᏇቯॊᇜถăდయᄋཝෂࡼጙᇹLj۞౪ጓดഌሌࡼာ݆ĂᑞᑵࡼތॊTDRਜ਼ᑽߒNexus Technologyดࡀࡼ൝ॊᇜጥLjဧࡻ༊ྜྷါਜ਼ଐႯ૦ଐཽᏋถ৫ኸႥறཀྵ࣪ดࡀଐቲ࢟ాހ၂LjଶዩดࡀଐࡼᏥቲ༽ౚăᔐᒄLjᑚᄁᄋ೫߲ࡼቶถਜ਼༄ჅᆚᎌࡼጵቶLjဧ߅ᆐ༊ྜྷါᇹᄻਜ਼ଐႯ૦ดࡀᇹᄻଶዩਜ਼ࢯ၂ࡼಯሯஊऱښăଶዩྀᇗጥ࢟വۇஉ৩࣡ਜ૭ᔜఝནዹာ݆,ࡒTDRތॊਜ૭ᔜఝནዹာ݆,ࡒTDRਜ૭ޠࣞནዹာ݆,ࡒTDRࠈཷནዹာ݆,ࡒTDT࢟ൈਜ਼ቧ࢟Ꮞᒠ,ᐅဉ,ඇࠦਜ਼ෂनᄢာ݆ဟᒩቧᒠ,ဍਜ਼ሆଢ଼ဟମ/ᓞધႥൈ,౫ຫဟᒩൔ౬ሣာ݆,ᓤᎌ࣌ࣅॊᇜྟୈෘഎ,ᒍਜ਼ၫᎌࠊా,ဟᒩ,ኡᄰਜ਼ၫቧມጤာ݆,ᓤᎌ࣌ࣅॊᇜྟୈFB-DIMMࠈቲቧၫᎌࠊాာ݆,ᓤᎌࠈቲၫጙᒘቶਜ਼ॊᇜྟୈ,ቧᏎਜ਼FB-DIMMଚፇኔਜ਼ဟኔดࡀᇹᄻఎ૦߱ဪછፇਜ਼ဟኔ൝ॊᇜጥ,ᓤᎌSDRAMᑽߒᄁୈSDRAMෝါࡀݷᔫ൝ॊᇜጥ,ᓤᎌSDRAMᑽߒᄁୈSDRAMෘഎፇਜ਼ဟኔ൝ॊᇜጥ,ᓤᎌSDRAMᑽߒᄁୈࣗ/ቖၫᎌࠊా൝ॊᇜጥ,ᓤᎌSDRAMᑽߒᄁୈၮቤݷᔫ൝ॊᇜጥ,ᓤᎌSDRAMᑽߒᄁୈดࡀᄰࡸጓᇗ൝ॊᇜጥ,ᓤᎌFB-DIMMᑽߒᄁୈܭ9.ଶዩྀᇗਜ਼ሤਈހ၂۸ăࠤܭᆐऱܣއᏞLj۾ࠤܭᒦથ۞౪۾ᆪᒦᎌဧࡼޟၣᎫăดࡀદߡ(AMB)ǖᄋᒝถฉሶਜ਼۱ሶᄰࡸ߱ဪછLjਈೊႥࠈቲဟᒩLjࢾᆡᑷܟஏLjଶዩᄰࡸೌถೆă७ࣞǖቧ༓ࣞăᏴ࢟ᔇୈᒦLj७ࣞᄰޟᒎ࢟ኹൈăෝผቧǖࡒᎌೌኚభܤ࢟ኹࡼቧăෝၫᓞધ(ADC)ǖڳ࢟ቧᓞધ߅ಭྲࡼऔᒜࡼጙᒬၫᔊ࢟ᔇୈăፊݛǖऻᄴݛă൝ॊᇜጥᏥቲᔈࡼནዹဟᒩăဟᒩࣖೂ᎖Ă༦ݙᒀࡸۻހ۸ࡼࢾဟăᑚဵĐࢾဟđݧૹෝါࡼăၱିǖቧ७ࣞᏴ࠭ጙৈ࢛ࠅၒࡵጙৈ࢛ࡼਭ߈ᒦሆଢ଼ăཆᐜᑫ(BGA)ǖጙᒬૹ߅࢟വॖᓤăࡒǖຫൈपᆍLjᄰޟሢࢾᆐ-3dB ăᆡǖጙৈऔᒜᔊ९Ljᓨზభጲဵ10ăᔊஂǖጙᒬၫᔊቧᇦᆡLjᄰޟᎅ8ৈᆡᔝ߅ăበຢࣅ(CE#)ǖ૮ୈăበຢኡᐋ(CS#)ǖኡᐋୈăဟᒩႥൈǖ۸ᒊቲ۾ݷᔫࡼႥൈLjᆡᆐඛᒲ໐ၫăᒍኡᐋ(CAS#)ǖኡᐋୈดঢቭབࡼᒍăܪǖືܪߛLjభጲڳᎧ݆ተ࣪Ljቲৎଝᓰཀྵࡼހăክણྑࡔ൩(CRC)ǖ࠭ၫ్ᒦᅎࡴ߲ࡼĂᎧၫ్ጙࡀࠅၒࡼၫᔊLjጲଶހၫૅႼăᄰਭᒮቤଐႯCRC Lj݀ڳᎧᔢ߱ख႙ࡼᒋቲ܈୷Lj၃૦భጲଶހࡵ෭ቋಢቯࡼࠅၒࡇᇙăॊ۴(dB)ǖܭာೝৈ࢟ቧᒄମൈሤ࣪ތࡼᆡLjࢀ᎖ೝৈ࢟ຳᒄ܈ޟ࣪ၫࡼ10۶ăۻހ۸(DUT)ǖހጥހ၂ࡼ۸ăၫᔊာ݆ǖጙᒬာ݆Ljဧෝၫᓞધ(ADC)ڳހࡻࡼ࢟ኹᓞધ߅ၫᔊቧᇦăॊ߅ྯᒬಢቯǖၫᔊࡀာ݆Ăၫᔊ፧ာ݆Ăၫᔊནዹာ݆ăၫᔊ፧ာ݆(DPO)ǖጙᒬၫᔊာ݆Ljத႒᎖ෝผာ݆ࡼመာᄂ࢛Ljᄴဟᄋࠅᄻၫᔊာ݆ࡼᎁဴ(݆ተࡀĂᔈࣅހࢀ)ăDPO ݧ݀ቲࠀಯஉ৩Ljڳቧࠅ႙ࡵᐜቯመာLjᑚᒬመာጲાࣞࢀऱါဣဟመာቧᄂ࢛ăDPO ጲྯৈᆒࣞመာቧǖ७ࣞĂဟମਜ਼७ࣞᏴဟମࡼॊݚăၫᔊནዹာ݆ǖጙᒬၫᔊာ݆LjݧࢀဟནዹऱजLjݔመာቧዹ࢛Ljᄂܰးறཀྵݔຫൈ߅ॊᏐᏐ᎖ာ݆ནዹႥൈࡼቧăၫᔊቧǖဧಭྲࡼऔᒜၫᔊܭာ࢟ኹዹ࢛ࡼቧăၫᔊࡀာ݆(DSO)ǖጙᒬၫᔊာ݆Ljᄰਭၫᔊནዹݧૹቧ(ဧෝၫᓞધ)ăဧࠈቲࠀಯஉ৩Lj఼ᒜݧૹĂઓஏෂਜ਼ᐜመာăၫᔊછǖၺຳᇹᄻᒦࡼෝၫᓞધ(ADC)Ᏼಭྲࡼဟ࢛࣪ቧནዹLj݀Ᏼᑚቋ࢛ڳቧ࢟ኹᓞધ߅ၫᔊᒋ(߂ᆐዹ࢛)ࡼਭ߈ăၷ۶ၫႥൈ(DDR)ǖख़ᒋၫႥൈဵෘഎڳဟᒩၒྜྷࡵୈࡼႥൈࡼೝ۶ăၷᒇރดࡀෝ్(DIMM)ǖPCຳგᒦࣅზႲ૦षᆰดࡀୈဧࡼഗቲࡼॖᓤऱښăࣅზႲ૦षᆰดࡀ(DRAM)ǖᏴࣖࡼ࢟ྏᒦࡀඛৈၫᆡࡼጙᒬดࡀăெࡇ൩(ECC)ǖଶࡇਜ਼ெࡇࡼ8ৈቅዩᆡăޝᄏ(FET)ǖᎅభܤ࢟ޝ఼ᒜၒ߲࢟ഗࡼᄏăறᇼମཆᐜᑫ(FBGA)ǖጙᒬૹ߅࢟വॖᓤăຫൈǖቧᏴጙดᒮআࡼࠨၫLjᆡᆐᓼ(ඛᒲ໐ၫ)ăຫൈࢀ᎖1/ᒲ໐ăཝෂદߡࡼၷᒇރดࡀෝ్(FB-DIMM)ǖጙᒬሆጙࡔดࡀஉ৩ăᑏᆡ(Gb)ǖ10ጸᆡቧᇦăᑏᔊஂ(GB): 10ጸᔊஂቧᇦăᓼ(GHz)ǖ10ጸᓼăඛᑏࠅ႙(GT/s)ǖඛࠅ႙10ጸࠨၫăඇࠦǖ࢟വᒦࡼମቌቶႥࡇᇙăᓼ(Hz)ǖඛጙৈᒲ໐LjຫൈࡼᆡăiCapture TMআǖᄰਭጙৈ൝ॊᇜጥყᄿᄴဟဣሚၫᔊݧૹਜ਼ෝผݧૹăiLink TMᇹǖᎅࣶৈᒒᏴଝᆰᄌଶހਜ਼ࢯ၂ࡼᏄᔝ߅Lj۞౪iCapture TMআĂiView TMመာਜ਼iVerify TMॊᇜăၒྜྷ/ၒ߲(I/O)ǖጙۅᒎቧ߲۸ăૹ߅࢟വ(IC)ǖጙᄁဢరಕ፝Ᏼበຢࡼୈૺઑೌăୣᄐྸහǖጲࢾ໐ମྲݚहᒙăiVerify TMॊᇜǖဧာ݆ည߅ࡼዛᅄᄋࣶᄰࡸᔐሣॊᇜਜ਼ଶዩހ၂ăiView TMመာǖᏴ൝ॊᇜጥመာືᄋ೫ဟମሤਈࡼ൝ॊᇜጥਜ਼ာ݆ᔏހถăೊ࢟ᔇ۸߈ଐᆕᏋ્(JEDEC)ǖ࢟ᔇቲጓೊට(EIA)ࡼۍࡴᄏ߈ଐܪᓰછဣᄏLjᑚጙඏጵ્ࡔܭᓹ࢟ᔇቲጓࡼჅᎌഌᎮă(kHz)ǖ1000Hzăဟዓǖ૮Ꮞਜ਼ሰ።ᒄମளਭࡼဟମăಿྙLjᏴDQᑣ୭ᄋၫဟLj࠭ࣗནᒲ໐ጙݛࡵྯݛࡼဟମăঌᏲǖყᄿਜ਼ာ݆Ꭷۻހ࢟വࡼĂဧቧပᑞࡼऻ৺ፀୣઑă൝ॊᇜጥǖއఘࣶৈၫᔊቧࡼ൝ᓨზႲဟମܤછࡼጥăॊᇜၫᔊၫLjభጲڳၫܭာᆐဣဟྟୈᒊቲĂၫഗᒋĂᓨზၿኔࢀăMagniVu TM ݧૹǖඛৈTLA ᇹ൝ॊᇜጥਖ਼ቦݧࡼࣖᄂࡼॊܦൈནዹஉ৩ăMagniVu ݧૹᏴ߿ख࢛ᒲᆍጲৎࡼॊܦൈᄋ೫ቧࣅࡼࣅზഺăᑏᆡ(Mb)ǖጙڻᅺ܈ᄂࡼቧᇦăᑏᔊஂ(MB)ǖጙڻᅺᔊஂࡼቧᇦăᑏ(MHz)ǖጙڻᅺᓼăᑏዹ࢛ඛ(MS/s)ǖནዹႥൈᆡLjඛጙڻᅺዹ࢛ăᑏࠅ႙ඛ(MT/s)ǖඛࠅ႙ጙڻᅺࠨၫăดࡀᒲ໐ဟମǖࣗྜྷᒲ໐ᒦ࠭ጙݛఎဪࡵᔢઁጙݛஉၦࡼဟମăᆈ(̂s)ǖဟମᆡLjࢀ᎖0.000001ă(ms)ǖဟମᆡLjࢀ᎖0.001ăᆈቯၷᒇރดࡀෝ్(ධฝDIMM)ǖ܈SO-DIMM ቃLjጙۅ᎖ۇଐႯ૦ᒦăᓍۇǖଐႯ૦ᓍገࡼᇹᄻ࢟വۇLj۞ࠀಯ, ดࡀ఼ᒜ,፮఼ᒜ, ၒྜྷ/ၒ߲ాበຢᔝࢀࢀă࢟വۇ(ྙDIMM ਜ਼၁ຫఌ)ރྜྷᓍۇᒦăฃ(ns)ǖဟମᆡLjࢀ᎖0.000000001ăᐅဉǖ࢟വᒦݙሯገࡼ࢟ኹ࢟ഗăာ݆ǖއఘ࢟ኹႲဟମܤછࡼጥăာ݆ጙࠤᏎᔈ፞ᆪĐᑩđLjፐᆐာ݆ᄰޟހᑩ࢟ኹăၒ߲ࣅ(OE#)ǖ૮۸ၒ߲ăᒲ໐ǖ݆ᅲᑳࡼጙৈᒲ໐Ⴥኊࡼဟମăᒲ໐ࢀ᎖1/ຫൈă߿ख༄އఘǖၫᔊጥݔ߿खူୈ༄࣪ቧቲݷᔫࡼถೆăࢾᓹ߿ख࢛ᒄ༄ਜ਼ᒄઁభጲއఘࡼቧޠࣞăᎾߠ࢟ǖDRAM षᆰᒲ໐ᒦࡼጙৈࣤLjᏴᑚৈࣤLjࡀ࢟ྏߠ࢟ࡵሤ።ᒋăყᄿǖጙᒬހጥၒྜྷ۸LjᄰޟᎌጙৈᎧ࢟വᏄဣሚ࢟߿ବ࣡ၢ࣡ݝĂೌ࢟വݬఠࡼጙᄟሣĂࠅၒቧਜ਼ࡼጙᄟྟ࢟಄ă൴ߡǖጙᒬޟ݆ተተᓨLjᎌႥဍዘĂࣞਜ਼Ⴅሆଢ଼ዘă൴ߡࠈǖጙࠅ႙ࡼ൴ߡૹă൴ǖ൴ߡ࠭ࢅࡵĂઁᏳૄࡵࢅჅኊࡼဟମLjጙۅᏖࢾᏴཝݝ࢟ኹࡼ50%ހࡻă༷ቓǖᑵሖ݆࢟ኹ࢟ຳᒄମጲੱࢾႥൈܤછࡼᓞધăႲ૦षᆰดࡀ(RAM)ǖభጲጲྀੜၿኔषᆰቧᇦࡼดࡀ۸ăࣗནᒲ໐ǖ࠭۸ᒦࣗནၫࡼࢾ໐ᒮআࡼူୈၿኔă/memory 21ഺޠࣞǖࠎቧഺࡼ݆ተ࢛ၫăၮቤǖᄰਭख႙ቤࡼ࢟൴ߡLj࣪በຢᒮቤߠ࢟ăࡀၷᒇރดࡀෝ్(RDIMM)ǖᄰਭદߡRDIMMࡼRDIMM SDRAMဟᒩĂෘഎቧਜ਼ᒍቧLjିၥᑼஉ৩ᆰᄌăဍဟମǖ൴ߡ༄ዘ࠭ࢅᒋဍࡵᒋჅࡼဟମLjጙۅᏴ࠭10%ဍࡵ90%ဟހࡻăቲᒍኡᐋ(RAS#)ǖኡᐋ۸ᒦঢቭབࡼᒍቲăዹ࢛ǖADCᒦଐႯ݆ተ࢛ࡼᏇဪၫăནዹႥൈǖᒎၫᔊހጥནቧዹ۾ࡼຫࣞLjඛዹ࢛ၫ(S/s)ܭာăནዹǖڳၒྜྷቧࡼጙݝॊᓞધ߅ࡍࡼॊྲࡼ࢟ᒋLjጲᎅጥቲࡀĂࠀಯਜ਼/መာăࠈቲࡀᏴᑤހ(SPD)ǖဧࣖࡼĂ࢟ᔇభݟ߹/భܠ߈ࡼᒑࣗดࡀ(EEPROM)۸Ljጲᒙෝ్මࣞĂࢾဟਜ਼ቶถݬၫăቧᅲᑳቶǖᓰཀྵᒮቧLjན᎖ጥࡼᇹᄻਜ਼ቶถፐႤૺݧૹቧဧࡼყᄿăቧᏎǖڳቧᓖྜྷ࢟വၒྜྷᒦࡼ۸Ǘઁᎅހጥࣗན࢟വၒ߲ăጐ߂ᆐቧखညăቃቯၷᒇރดࡀෝ్(SO-DIMM)ǖ܊۾࢟ฎਜ਼హମৼࢾࡼဣሚऱښᒦဧࡼቃቯDIMMăᄴݛǖᄴݛછă൝ॊᇜጥᓨზݧૹభጲႁဵᄴݛࡼLjፐᆐ൝ॊᇜጥ࠭ᅪݝᏎ၃ဟᒩቧᇦLjᅪݝᏎᄰޟဵDUTăᑚ્ࡴᒘೝৈᇹᄻᄴݛછLj൝ॊᇜጥᒑᏴDUT૮ဟݧૹၫăᑚ߂ᆐĐᓨზđݧૹෝါăᄴݛࣅზႲ૦षᆰดࡀ(SDRAM)ǖᒒᏴڳDRAMݷᔫᄴݛછࡵଐႯ૦ᇹᄻݝॊLjݙᏳኊገোCE#LjRAS#LjCAS#ਜ਼WE#ܟዘᓞધၿኔࢾፃჅᎌݙᄴࡼดࡀݷᔫෝါăۻހᇹᄻ(SUT)ǖހጥހ၂ࡼᇹᄻăဟᎮनଐ(TDR)ǖዘᓹࠅၒሣຶৰᔜఝᒋਜ਼ܤછࡼ଼ܣऱါLjྙPC࢟വۇࡼ࢟಄Ăೌᆈࡒă߿खǖݬఠހጥၺຳྸහࡼ࢟വă߿खျጴǖጙᒬ఼ᒜถLjᏴጥጙࠨᎌ߿खઁLjᏤࢯஂဟମጲஊጥݙถ߿खࡼᆰᄌă߿ख࢟ຳǖ߿खᏎቧᏴ߿ख࢟വखྸහ༄ܘኍࡉࡵࡼ࢟ኹ࢟ຳă22 /memoryऻࡀၷᒇރดࡀෝ్(UDIMM)ǖUDIMMဵDIMMࡼጙৈဣሚऱښăUDIMMݙถદߡDIMMࡼDDRLjDDR2ਜ਼DDR3 SDRAMቧăިቃቯၷᒇރดࡀෝ్(VLP-DIMM)ǖࣞ୷Ăᄰޟ᎖ຢॲᇗᒦࡼDIMMsă॰(V)ǖ࢟ᆡތᆡă࢟ኹǖೝ࢛ᒄମࡼ࢟ᆡތLj॰ܭာă݆ǖႲဟମᅎጤᒮআࡼ൩ቯࡼᄰၣᎫăޟಢቯ۞౪ǖᑵሖ݆Ăऱ݆Ăተ݆Ă௨ߙ݆Ăྯ୯݆ĂᏘĂ൴ߡĂᒲ໐Ăऻᒲ໐ĂᄴݛĂፊݛăቖྜྷ(WE#)ǖ૮۸ቖྜྷถă/signal_integrity 23დయపଆ(ᒦਪ)ᎌሢႊှ໌ࣁቤཌࠂ༙വ1227ᎆܠǖ201206࢟જǖ(86 21)5031 2000ࠅᑞǖ(86 21)5899 3156დయ۱யێူࠀ۱யှࢥཌઔᏊവ4ᄰੱࡍሇ1ണ101၀ᎆܠǖ100088࢟જǖ(86 10)6235 1210/1230ࠅᑞǖ(86 10)6235 1236დయێူࠀှஸڔཌዓڔᒦവ841ࣁऱᅪࡍሇ18ണ1802-06၀ᎆܠǖ200040࢟જǖ(86 21)6289 6908ࠅᑞǖ(86 21)6289 7267დయਓᒳێူࠀਓᒳှણှࣁവ403ਓᒳਪଔ࢟ᔇࡍሇ2807A ၀ᎆܠǖ510095࢟જǖ(86 20)8732 2008ࠅᑞǖ(86 20)8732 2108დయᚆێူࠀᚆှ൜ઌཌฉࣁവ5002ቧቭਓޝᅽጓࡍሇG1-02၀ᎆܠǖ518008࢟જǖ(86 755)8246 0909ࠅᑞǖ(86 755)8246 1539დయ߅࣒ێူࠀ߅࣒ှཽฉവጙࣤ86߃ှᒄቦ23ށD-F ᔭᎆܠǖ610016࢟જǖ(86 28)8620 3028ࠅᑞǖ(86 28)8620 3038დయᇝڔێူࠀᇝڔှࣁࡍᇝڔᏝ(ڄळড়)भࢢ322၀ᎆܠǖ710001࢟જǖ(86 29)8723 1794ࠅᑞǖ(86 29)8721 8549დయᇊੈێူࠀᇊੈှᇊޛཌᓍവ788ڹඑਕࡍௌࢢ924၀ᎆܠǖ430071࢟જǖ(86 27)8781 2760/2831 ࠅᑞǖ(86 27)8730 5230დయሧভێူࠀሧভᄵ൞ᅭᇧဇࡸ33ಽᏊ3501၀࢟જǖ(852)2585 6688ࠅᑞǖ(852)2598 6260ۈཚჅᎌ2005,Tektronix,Inc.ཝཚჅᎌăTektronix ޘອ၊ගਪਜ਼ᅪਪᓜಽཚ(۞౪ጯནࡻࡼਜ਼ᑵᏴ༿ࡼᓜಽཚDžࡼۣઐă۾ᆪᒦࡼቧᇦནࡔჅᎌጲ༄߲ۈࡼᓾ೯ᒦࡼቧᇦăۣഔৎখޘອਖৃਜ਼ଥৃࡼཚಽăTEKTRONIX ਜ਼TEK ဵTektronix,Inc.ࡼᓖݿܪăࡼჅᎌܪ߂ᆐჇඣᔈႊࡼॲᇗܪᒔĂܪᓖݿܪă1/06 DV/WOW 52C-19200-1೫ஊৎࣶቧᇦTEKTRONIX ᆒઐጙৈཝෂࡼਜ਼ݙࣥ౫ᐱࡼ።ᆪᐺLjଆၣ଼ਜ਼ჇᓾᏎࡼૹLjభۑᓐ߈နဧᔢቤࡼଆၣLj༿षᆰǖ©。

SDRAM工作原理

SDRAM工作原理1.读取操作:首先,外部设备通过总线将读取命令和地址发送给SDRAM控制器。

控制器接收到这些信号后,将地址传递给内部地址线路。

然后,内部地址线路通过行地址译码器将地址转换为行号,并将其发送到行地址线路。

行地址线路选择对应行的电容,并将其值放大。

接下来,列地址译码器将列地址转换为列号,并将其发送到列地址线路。

列地址线路选择对应列的电容,并将其值放大。

最后,放大器将电容值转换为数字信号并输出到总线,供外部设备读取。

2.写入操作:与读取操作类似,外部设备通过总线将写入命令、地址和数据发送给SDRAM控制器。

控制器接收到这些信号后,将地址传递给内部地址线路。

内部地址线路通过行地址译码器将地址转换为行号,并将其发送到行地址线路。

行地址线路选择对应行的电容,并将电容的值设置为输入的数据值。

接下来,列地址译码器将列地址转换为列号,并将其发送到列地址线路。

列地址线路选择对应列的电容,并将电容的值设置为输入的数据值。

3.刷新操作:动态随机存储器的特点是电容存储信息,但电容会慢慢放电,导致数据丢失。

因此,需要定期进行刷新操作来维持数据的准确性。

刷新操作主要是将所有的电容电压重新充放电一次。

刷新操作的频率取决于SDRAM的制造商和规格。

此外,SDRAM的速度取决于时钟信号的频率。

SDRAM使用一个外部时钟来同步控制器和存储器之间的通信。

时钟信号通过时钟线路传输,并控制着SDRAM数据的传输速度。

总结起来,SDRAM通过行地址译码器、列地址译码器和放大器实现读取和写入操作。

读取时,通过地址线路选择对应行和列的电容,并将其值放大后输出到总线。

写入时,通过地址线路选择对应行和列的电容,并将其值设置为输入的数据值。

另外,SDRAM还需要定期进行刷新操作来维持数据的准确性。

DDR,SDRAM中文入门教程

SDRAM 内存系统:嵌入式测试和测量挑战

入门手册

DRAM 的一个行称为内存页

面,一旦打开行,您可以访问该

行中多个顺序的或不同的列地 址。这提高了内存访问速度,降 低了内存时延,因为在访问同

分布式 刷新

一个内存页面中的内存单元时,

突发刷新

其不必把行地址重新发送给

时间

DRAM。结果,行地址是计算机 的高阶地址位,列地址是低阶

早期的 DRAM 读取周期有四个步骤。第一步,RAS# 与 地址总线上的行地址变低。第二步,CAS# 与地址总线 上的列地址变低。第三步,OE# 变低,读取数据出现在 DQ 数据针脚上。在 DQ 针脚上提供数据时,从第一步 第三步的时间称为时延。最后一步是 RAS#, CAS# 和 OE# 变高(不活动),等待内部预充电操作在破坏性读取 后完成行数据的恢复工作。从第一步开始到最后一步结

刷新策略有两个(参见图 2)。第一个策略内存控制器在 刷新周期突发中顺序刷新所有行,然后把内存控制返回 处理器,以进行正常操作。在到达最大刷新时间前,会 发生下一个刷新操作突发。第二个刷新策略是内存控制 器使用正常处理器内存操作隔行扫描刷新周期。这种刷 新方法在最大刷新时间内展开刷新周期。

/memory 5

入门手册

SDRAM 内存系统:

嵌入式测试和测量挑战

5

SDRAM 内存系统:嵌入式测试和测量挑战

入门手册

目录

引言⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯3-4 DRAM 发展趋势⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯3

DRAM⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯4-6 SDRAM⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯⋯6-9

DRAM 发展趋势

人们一直希望计算机内存变得容量更大、速度更快、功 率更低、物理尺寸更小。这些需求正推动着 DRAM 技 术不断发展。在过去几年中,多次技术增强已经推进了 主流 DRAM 的发展,如 SDRAM (同步 DRAM)、DDR (双倍数据速率)SDRAM、DDR2 (双倍数据速率 2) SDRAM和DDR3 (双倍数据速率3) SDRAM。计算机内 存在DIMM(双列直插内存模块)中的使用方式也一直推 动着这一演进。DIMM 实现方案已经从非寄存DIMM 扩 展到包括多个寄存 DIMM 和 FB-DIMM (全面缓冲的 DIMMs)。

SDRAM知识详解

3. SDRAM芯片容量 =MxW (M:存储单元总数;W:每个存储单元的容量,即芯片位宽) 存储单元总数M=行数(R)x 列数(C)不一样

3.SDRAM芯片结构:

三.SRAM基本操作与内部工作时序

1.芯片初始化 SDRAM逻辑控制单元中有模式寄存器(MR),开机需对其进行初始化操作。

4.数据输出/读 a: CL(CAS Latency) CAS潜伏期:从CAS与读取命令发出到第一笔数据输出的这 段时间。单位:时钟周期。 b: CAS响应时间快于RAS:一个位宽为n bit 的芯片,行地址要选通n x c(列数为 c)个存储体,而列地址只需选通n个存储体。 c: CL的产生原因: 1)存储体中晶体管的反应时间使数据和CAS在同一上升沿触发,至少延后一个 时钟周期; 2)tAC (Access time from clock)时钟触发后的访问时间:(由于存储电容小,故 信号需经S-AMP放大来保证被识别(事前还要进行电压比较来进行逻辑电平判断) 从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据已传向S-AMP,数 据已经被触发,经过一定的驱动时间最终向数据I/O总线传输(小于一个时钟周 期)。

8.突发长度 突发(Burst )是指在同一行中相邻的存储单元连续进行数据传输的方式,连续 传输所涉及到存储单元(列)的数量就是突发长度( Burst Lengths,简称BL )。 1)BL设置: 目前可 用的选项是 1、2、4、8、全页(Full Page ),常见 的设定是4 和 8。 Full Page (全页)突发传输是指L-Bank 里的一行中所有存储 单元从头到尾进行连续传输。 2)突发传输技术,只要指定起始列地址与突 发长度,内存就会依 次地自动对后 面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。 3)优点:提高传输效率(第一笔数据须 tRCD+CL,其后每个数据只需一个周期)

sdram内存的工作原理

sdram内存的工作原理SDRAM(Synchronous Dynamic Random Access Memory)是一种常见的计算机内存类型,其工作原理是通过同步时钟信号进行数据读写操作。

在计算机系统中,内存扮演着重要的角色,用于存储程序和数据,SDRAM作为一种高速、容量大的内存技术,被广泛应用于各种计算设备中。

SDRAM内存的工作原理可以简单概括为以下几个步骤:预充电、读写操作和刷新。

在进行读写操作之前,SDRAM需要进行预充电操作。

预充电是将内存电路中的电容充电至特定电压的过程,以确保内存电路处于稳定的工作状态。

预充电操作一般由内存控制器发出指令,并通过电源提供的电压来完成。

接下来是读写操作。

读取数据时,内存控制器根据指令将读取地址发送给SDRAM,同时启动同步时钟信号。

SDRAM根据接收到的地址和时钟信号,将对应数据发送给内存控制器。

写入数据时,内存控制器将写入地址、数据和控制信号发送给SDRAM,SDRAM 根据信号将数据写入指定地址。

在读写操作完成后,为了保持数据的稳定性,SDRAM需要进行刷新操作。

刷新操作是将电容中的电荷重新充电,以防止数据丢失。

SDRAM内部有一个刷新计数器,用于记录刷新的次数。

当计数器达到刷新阈值时,SDRAM会自动启动刷新操作,将所有数据重新写入内存电路。

除了基本的读写操作和刷新操作外,SDRAM还具有一些特殊的功能。

例如,SDRAM内部有多个存储区域,可以同时进行多个读写操作,提高内存访问效率。

另外,SDRAM还支持自动预充电和自动刷新功能,减少了控制信号的传输和处理时间,提高了数据传输速度。

总的来说,SDRAM内存的工作原理是通过同步时钟信号进行读写操作,并进行预充电和刷新操作,以确保数据的可靠性和稳定性。

SDRAM内存具有高速、容量大、低功耗等优点,广泛应用于个人电脑、服务器、手机和其他计算设备中,为计算机系统的性能提供了重要支持。

DDR2学习资料

DDR SDRAM最早是由三星公司于1996年提出,由日本电气、三菱、富士通、东芝、日立、德州仪器、三星及现代等八家公司协议订立的内存规格,并得到了AMD、VIA与SiS等主要芯片组厂商的支持。

它是SDRAM 的升级版本,因此也称为「SDRAM II」。

其最重要的改变是在界面数据传输上,他在时钟信号的上升沿与下降沿均可进行数据处理,使数据传输率达到SDR(Single Data Rate)SDRAM 的2倍。

至于寻址与控制信号则与SDRAM相同,仅在时钟上升沿传送。

DDR SDRAM模块部份与SDRAM模块相比,改为采用184针(pin),4~6 层印刷电路板,电气接口则由「LVTTL」改变为「SSTL2」。

在其它组件或封装上则与SDRAM模块相同。

DDR SDRAM模块一共有184个接脚,且只有一个缺槽,与SDRAM的模块并不兼容。

DDR SDRAM在命名原则上也与SDRAM不同。

SDRAM的命名是按照时钟频率来命名的,例如PC100与PC133。

而DDR SDRAM则是以数据传输量作为命名原则,例如PC1600以及PC2100,单位MB/s。

所以DDR SDRAM中的DDR200 其实与PC1600 是相同的规格,数据传输量为1600MB/s(64bit×100MHz×2÷8=1600MBytes/s),而DDR266与PC2100 也是一样的情形(64bit×133MHz×2÷8=2128MBytes/s)。

DDR SDRAM 在规格上按信号延迟时间(CL;CAS Latency,CL是指内存在收到讯号后,要等待多少个系统时钟周期后才进行读取的动作。

一般而言是越短越好,不过这还要看内存颗粒的原始设定值,否则会造成系统的不稳定)也有所区别。

按照电子工程设计发展联合协会(JEDEC)的定义(规格书编号为JESD79):DDR SDRAM一共有两种CAS延迟,分为2ns以及2.5ns(ns为十亿分之一秒)。

SDRAM原理与操作时序

SDRAM原理与操作时序SDRAM(Synchronous Dynamic Random Access Memory)是一种随机存取存储器,它在电路设计上采用了同步传输技术,能够与系统总线同步工作,提高了系统的数据传输效率和稳定性。

(1)命令预充电:在写操作之前,首先发送命令预充电(PRE)信号,在一个指定的列地址上对存储单元进行预充电操作,将存储单元的电荷置为一种中间状态,为后续写操作做准备。

(2)写命令:发送写命令(WRITE)信号,指示控制电路将数据写入指定的存储单元中。

同时,将数据写入数据总线上并等待控制电路的确认信号。

(3)写确认:控制电路收到写命令后,发送写确认(ACK)信号,表示已成功写入数据。

此时,数据总线上可以发送下一次写操作的数据。

(1)命令预充电:与写操作相同,在读操作之前需要对存储单元进行命令预充电,将存储单元的电荷置为中间状态。

(2)读命令:发送读命令(READ)信号,指示控制电路将指定列地址上的数据读取出来。

同时,将读命令发送给控制电路并等待确认信号。

(3)读数据:控制电路收到读命令后,将指定列地址上的数据发送给数据总线,并发送读确认(ACK)信号,表示数据已经准备好了。

除了读写操作时序,SDRAM还有一些其他的操作时序,例如刷新、自动预充电等。

刷新是为了防止存储单元电荷丧失而进行的周期性操作,自动预充电是为了加快写操作速度而进行的一种优化操作。

总结起来,SDRAM的原理是通过控制电路和存储单元的配合,实现对数据的读写操作。

操作时序是按照一定顺序进行的,以保证数据的稳定性和正确性。

同时,SDRAM还有其他的操作时序,例如刷新和自动预充电等,以进一步优化存储器的性能。

零基础学FPGA (二十三) SDR SDRAM(架构篇)

零基础学FPGA (二十三)SDR SDRAM(架构篇)今日我们来讲的是SDRAM的架构以及设计,这也是小墨第一次接触架构,也谈不上给大家讲,就是把我理解的当做一个笔记共享给大家,有什么错误也请乐观指正,究竟我也是没有教师教,也是自己试探的,难免有些不合理的地方。

一、SDRAM 工作部分1、上电初始化我们先来看第一部分,上电初始化。

上电初始化我们知道,上电之后我们需要等待200us的稳定期,这段时光我们可以用一个定时器来计数,这没什么问题,然后进入的是预充电部分,这个时候,预充电的时候,sdram_cmd模块会检测此时的初始化状态机的状态,若处于预充电状态,那么sdram_cmd模块向SDRAM发指令,详细指令sdram的datasheet 里面有,发的是一个precharge,即预充电,发完指令之后,需要等待一段时光,来确保这个指令被SDRAM捕捉,这等待的时光,特权教师用的方式我觉得很好用一个宏定义,当计数器计数到相应的时光后,预充电完成参数置位即end_trp 置位,下面的使用也是一样,即当时始化状态机进入预充电状态i_pre时,计数器开启,开头计数,计数完成,也就是预充电结束的时候,计数器复位,这个复位的控制,可以用case语句来检测初始化状态机的状态,在相应的状态赋予相应的复位与置位接下来是8个自刷新,操作和预充电一样到了模式寄存器的配置阶段,我们需要选定L_bank,以及SDRAM工作模式的配置,当sdram_cmd模块检测到初始化状态机到达模式寄存器配置阶段时,我们的给SDRAM的sdram_bank端口赋相应的值,并且设置地址当时始化结束的时候,标记位init_done置位,告知工作状态机,初始化状态机已经结束,进入工作状态。

下面是我用word做的上电初始化的状态转移图2、自刷新初始化结束之后,SDRAM为了防止数据走失,要举行自刷新,上一篇文章已经讲过了,刷新2^12行需要64ms,也就是每15us刷新一行,也就是我们需要每15us发送一次自刷新哀求给SDRAM工作状态机,状态机一旦检测到自刷新哀求信号,就告知sdram工作模块,然后工作模块就向SDRAM发送自刷新指令,即CMD_A_PEF下面是自刷新的状态转移图3、读写状态初始化结束以后,SDRAM就处于工作状态,每15us举行一次自刷新,这个时候,假如想要读或写数据的话,即向工作状态机sdram_work_FSM 发送读写哀求,假如是读哀求,那么工作状态机进入行有效状态,也即激活状态w_active,此时,sdram_cmd模块会发送行有效指令,即CMD_ACTIVEA同时,我们需要将我们的12位行地址送给我们的sdram地址总线sdram_addr,然后便是一个等待时光段,TRCD,这个时光段里我们是不需要做什么工作的,只需等待TRCD结束TRCD结束的时候,工作状态机进入读状态,此时,我们需要发送列地址选中我们的存储单元,并告知sdram_cmd模块发送读指令,这个过程是读指令和列地址同时发送的。

SDRAM工作原理

SDRAM工作原理

SDRAM有一个内部的时钟信号,用来控制存取数据的时序。

它与计算机系统的外部时钟进行同步,使得数据的读写操作能够按照规定的时序进行。

SDRAM的存储单元是由一个电容和一个开关组成,当给定指令时,电荷被存储在电容中,当需要读取数据时,电荷被转换为电流并通过开关输出。

1.预充电:在存储单元的开关关闭之前,需要预充电电容。

预充电过程是将电容上的电荷全部归零,为之后的读写操作做准备。

2.行选通:在读写数据之前,首先需要选中要操作的行。

行选通信号在特定时刻产生,将存储单元的开关打开,使得电荷可以存入电容。

3.数据读写:当行选通信号产生后,将对应列的开关打开,数据可以从电容中读取或写入。

如果是读操作,电荷从电容中转换为电流,并经过驱动电路输出;如果是写操作,需要将电流输入到电容中,改变电荷的状态。

4.刷新操作:由于SDRAM中的电荷会逐渐泄露,所以需要定时进行刷新操作,重新存储电荷。

刷新操作是通过按照预定顺序将所有行进行读取和写入来实现的。

需要注意的是,SDRAM的工作频率与电路的设计、质量、环境温度等因素有关。

较高的工作频率可能导致数据的读取或写入过程中出现错误。

因此,适当的调整工作频率和时序参数对于保证SDRAM的正常工作非常重要。

总结起来,SDRAM作为一种同步动态随机存取存储器,通过同步时钟控制内部的存取操作。

它的工作过程包括预充电、行选通、数据读写和刷

新操作。

通过合理配置读写时序参数,可以确保SDRAM能够按照指定频率工作,并提供稳定的数据读写能力。

DDR-SDRAM-基础知识学习

Chip 0

Chip 1

Row 0 Col 1

Cont’d

Rank 0

Chip 7

...

...

<0:7> <8:15> <56:63>

0x40

8B 8B

0x00

64B cache block

Data <0:63>

14

A 64B cache block takes 8 I/O cycles to transfer. During the process, 8 columns are read sequentially.

Read Access Step3 – Restore

Cont’d

2021/3/28

21

DRAM ACCESS FLOW

Read Access Step4 – Pre-charge

Cont’d

2021/3/28

22

DRAM ACCESS FLOW

Sense Amplifier Voltage Waveform – Read Flow

Downside of DRAM Refresh

Power Consume Performance degradation Refresh rate limits DRAM capacity scaling

Cont’d

32

DRAM BASIC COMMANDS

More about DRAM Refresh

2021/3/28

DRAM BASIC KNOWLEDGE

SUMMARY

1

Hulin Cao –源自2021/3/28DRAM BASIC KNOWLEDGE

SDRAM-高手进阶,终极内存技术指南-完整进阶版

高手进阶,终极内存技术指南作为电脑中必不可少的三大件之一(其余的两个是主板与CPU),内存是决定系统性能的关键设备之一,它就像一个临时的仓库,负责数据的中转、暂存……不过,虽然内存对系统性能的至关重要,但长期以来,DIYer并不重视内存,只是将它看作是一种买主板和CPU时顺带买的“附件”,那时最多也就注意一下内存的速度。

这种现象截止于1998年440BX主板上市后,PC66/100的内存标准开始进入普通DIYer的视野,因为这与选购有着直接的联系。

一时间,有关内存时序参数的介绍文章大量出现(其中最为著名的恐怕就是CL参数)。

自那以后,DIYer才发现,原来内存也有这么多的学问。

接下来,始于 2000年底/2001年初的VIA芯片组4路交错(4-Way Interleave)内存控制和部分芯片组有关内存容量限制的研究,则是深入了解内存的一个新开端。

本刊在2001年第2期上也进行了VIA内存交错控制与内存与模组结构的详细介绍,并最终率先正确地解释了这一类型交错(内存交错有多种类型)的原理与容量限制的原因。

从那时起,很多关于内存方面的深入性文章接踵而至,如果说那时因此而掀起了一股内存热并不夸张。

大量的内存文章让更多的用户了解了内存,以及更深一层的知识,这对于DIY当然是一件好事情。

然而,令人遗憾的是这些所谓的内存高深技术文章有不少都是错的(包括后来的DDR与RDRAM内存的介绍),有的甚至是很低级的错误。

在这近两年的时间里,国内媒体上优秀的内存技术文章可谓是寥若晨星,有些媒体还编译国外DIY网站的大篇内存文章,但可惜的是,外国网站也不见得都是对的(这一点,国内很多作者与媒体似乎都忽视了)。

就这样,虽然打开了一个新的知识领域,可“普及”的效果并不那么好,很多媒体的铁杆读者高兴地被带入内存深层世界,但也因此被引向了新的误区。

不过,从这期间(2001年初至今)各媒体读者对这类文章的反映来看,喜欢内存技术的玩家大有人在且越来越多,这是各媒体“培养”的成果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SDRAM學習資料目錄目錄一、DRAM構造及動作原理 (3)二、SDRAM整體結構 (8)三、SDRAM的信號 (9)四、SDRAM命令 (11)五、SDRAM存取動作 (15)六、SDRAM寫入動作 (16)一、DRAM構造及動作原理1.1 DRAM的定義及特點.1.1.1 定義. DRAM(Dynamic Random Access Memory)動態隨機存取記憶體.1.1.2 DRAM特點.a. 記憶單元(memory cell)較小,包括一個電晶體和一個電容器.構造簡單,易於提高集成度.b. 記憶具有揮發性,超過一段時間未做存取(Acess) 動作時記憶內容會消失,必須以一定周期執行記憶內容的更新(refresh).c. 揮發性:存儲于電容器內的電荷每次讀取後由於電荷移動而消失電荷內容,為破壞性讀出.因此,在資料讀出後將同一資料回寫,不過,在DRAM內部會自動執行此回寫動作.1.2 DRAM 記憶單元構造及工作原理.1.2.1 DRAM 記憶單元(cell)的構造. 如圖1-1所示.圖1-1 DRAM CellDRAM 記憶單元(memory cell)的構成如圖1-1所示.爲1Tr-1C 結構. FET 作爲存取(Access)用開關.電容器負責記憶資料. 圖1-2中左側爲FET 部分,右側爲電容器.氧化膜形成電容器的電介質,Poly silicon形成電容器的電極,二者構成電容器.圖1-2 DRAM Cell 構造1.2.2 DRAM 記憶單元的基本工作原理.由電容器內有無存儲電荷來判定資料的有無,即”0”和”1”.電容器一端接地,另一端連接至FET 的泄極.讀取資料時連接於FET 閘極上的word line 令FET ON,令電容器接通資料線,此時電荷在電容器及資料線中移動,通過判斷資料線電壓的變化判定資料的有無(”0”或”1”).Poly Silicon氧化膜閘極1.2.3 漏電流. Memory cell儲存電荷時,電容器兩端的電壓加在FET上形成逆向偏壓狀態,因而會有漏電流存在,此漏電流導致電容器放電,因此必須定期補充電荷以使記憶單元的狀態恢復原狀,稱之爲更新(Refresh).N+:加入五族元素,產生電子,剩餘電子狀態.圖1-2 DRAM Cell之漏電流1.3 DRAM的內部電路.1.3.1 DRAM內部構造DRAM內有記憶單元選擇用Word Line ,各記憶單元連接Data Line,此Data Line經由列選擇開關連接共通Data Line,此外經由預充電開關(Pre-Charge Switch)連接至預充電電源.預充電電源的電壓爲DRAM電源電壓(VDD)的一半左右. 感測放大器(Sense Amplifier)作用為判定data line的I/O狀態,並放大data line電壓.圖1-3 DRAM之基本構造1.4 DRAM記憶單元讀取動作基本原理資料寫入: 待data line之狀態確定後令FET ON即可向電容器充放電完成寫入動作.資料讀取: 因資料讀取首先需要驅動共通data line,但記憶用電容的電容量太小,不足以驅動data line,故需按照以下步驟進行.圖1-4 DRAM讀出動作(Pre-charge)a. Data line的預充電. (爲從DRAM讀出資料的準備動作.)Pre-charge SW關閉,將Data Line連接預充電電源,將Data Line的電壓設置爲預充電電壓,此時電荷儲存於寄生電容內,故當進行後面的動作時,即使Pre-charge SW關閉,電壓仍然可保持爲預充電電壓.此過程稱爲預充電.b. 資料取出及放大.預充電動作完畢後, Pre-charge SW關閉,然後選擇Word Line,當FET ON時被選中的記憶單元的電容器與與寄生電容器並聯,於是資料的1/0令預充電電壓起伏變化,因變化量不大,故利用感測放大器加以放大.感測放大器以預充電電壓爲基準,從輸入電壓的起伏做判定而輸出H/L位元准資料.如圖1-5所示.圖1-5 DRAM讀出動作(資料之取出及放大)c. 感測放大器的連接及輸出.感測放大器的輸出端受本身之輸出電壓驅動,形成”自我保持電路”,且感測放大器的輸出連接至Data Line,能充分驅動Data Line.此時,共通Data Line開關閉合,共通Data Line被驅動,資料送到外部介面.由於此時Word Line被選擇,FET處於ON狀態,DRAM Cell的電容器與Data Line連接,電容器恢復初期狀態(保持資料讀取前後的一致).如圖1-6所示.圖1-6 DRAM讀出動作(Sense Amp.之連接與資料輸出)二、SDRAM整體結構2-1. SDRAM整體結構如圖2-1所示.Memory Array(bank):基本存儲單元所在,如圖2-2所示2-2 Memory bank結構Memory bank組成: Memory Array, Sense Amp., Row& Column decoder Memory Array容量= row*column*bitSDRAM容量=bank*(row*column*bit)Mode Register:狀態寄存器,用來切換SDRAM的狀態(Mode),以位址設定.I/O Buffer:輸入/輸出數據緩存.Row & column address buffer:行/列地址緩存control logic& timing generator:控止邏輯及時序發生器.三、SDRAM的信號A0-A12(地址Address):將地址分為行地址和列地址2次輸入SDRAM.行地址輸入時使用A0-A12,列地址輸入時使用A0-A8,此時A9-A12為無效.A10還可作為命令輸入腳,後面會詳細介紹.BA0,BA1(Bank Address): Array各Bank可獨立動作,如右真值表所示:可將一個行地址輸入其中一個Bank,再將另一個行地址輸入另外一個Bank,再回到最初的Bank輸入列地址對其進行讀取動作.CLK(Clock):時控信號輸入,所有信號輸入輸出均與這個時控信號的上波波緣同步動作./CS(Chip Select):此腳輸入信號為高時,所有其他信號無效,但內部動作(Bank Activated及Burst動作)照常執行.輸入為低時,輸入控制信號及位址均為有效./RAS,/CAS,/WE由這三條信號線的組合來指示各種操作(Operation),後面詳細說明.DQMU/DQML(DQ Mask High/Low)輸入為高時,無法進行資料讀取動作,輸入為低時資料讀取照常進行. DQMU控制高八位DQ8-DQ15,DQML控制低八位DQ0-DQ7DQ0-DQ15(Data資料)資料輸入輸出,以8bit為單位輸入出.四、SDRAM命令在SDRAM中,以各條狀態線(Control Line)的狀態的組合代表命令,經由這一組信號線發送命令給SDRAM.SDRAM命令表如下如4-1所示.圖4-1 SDRAM Command Table下面詳細介紹各條命令:4-1. Mode Register Set(MRS)此命令寫入四個信息:OPCODE,LMODE,BT,BL如下圖所示:圖4-2 Mode Register bit配置(PSC)A7一直為0OPCODE: BA1,BA0,A12, A11, A10, A9, A8一般會用來設置OPCODE,OPCODE用來設定寫入方式.寫入方式分為兩種:Burst Read and Burst Write(寫入是採取連串資料轉送方式Burst Transfer,開始地址為開始寫入列地址Command Address),連串轉送的數目由Burst Length指定;Burst Read and Signal Write寫入時僅寫入一word 資料.圖4-3 OPCODE配置對PSC,從圖4-2看到,僅採用Burst Read and Burst Write方式.LMODE: 由A4—A6設定CAS LatencyBT:用以指定Burst Sequence,分為Sequential(Liner) Burst或Interleave Burst.做Burst 轉送時,主控方(Host)秩序將開始地址通知SDRAM即可,以後地址由SDRAM 自動產生.圖4-4 Burst SequenceBL: 由A0-A2設置Burst所傳送的Word數.如圖4-2所示.4-2. Auto Refresh (REF)若欲使SDRAM執行RER,必須令SDRAM內所有的Bank的狀態為IDLE,在存取Access進行中不能下達Auto Refresh指令.SDRAM內部自動產生更新地址(Refresh Address)及Bank Address. Auto Refresh只能執行一個位地址的更新,因此必須按照Data Sheet在指定期間發行指定次數的Auto Refresh Command(自動更新命令). 在Auto Refresh後會自動執行’預充電’,所以不用發出預充電命令,在更新完畢後自動回到IDLE狀態.4-3. Self Refresh開始(SELF)/結束(SELFX)在DRAM內部自動執行Refresh動作,以命令指示Self Refresh的開始/結束. 4-4. 啟動及行地址閂鎖(ACTV)此命令指定所要存取資料的Bank Address(BA n) 及行地址(Row Address)AX0-AX12.Bank Address所指定的Bank被驅動(Active),行地址(Row Address)被閂鎖.(以AX n表示行地址,以AY n表示列地址.AX n為A n Pin所指定的地址.4-5. Data Read(READ)及Auto Precharge的Data Read(READ-A)由BA n所指定的Bank的列地址(AY0-AY8)開始進入Data Read動作.由A10Pin 的狀態選擇是否在Burst Read後自動做Pre-charge(預充電).A10為高則在Burst Read後自動執行Pre-charge動作,A10為低時,不執行Pre-charge動作,主控方(Host,即DRAM Controller)必須另外下達Pre-charge命令.4-6. Data Write(WRITE)及Auto Precharge的Data Write(Write-A)從BA n所指定的Bank的列地址AY0-AY8開始進入Data Write動作,資料從DQ n Pin輸入,同時發行WRITE命令.在做Burst Write時,此地址為Start Address(開始地址),將Burst長度的資料取入SDRAM內,在做Signal Write(單次寫入)的場合,對此地址寫入一次資料就結束寫入動作.A10的狀態同樣決定在寫動作完畢後是否做Pre-charge.4-7. 指定Bank,Pre-charge(PRE)令SDRAM執行BA n Pin所指定的Bank的Pre-charge.4-8. Power Down狀態突入/復原當SDRAM處于IDLE狀態時,發行Power Down狀態突入命令時,輸入初級電路被切離而進入低功耗狀態,如欲令其從此狀態恢復必須發行還原命令,還原後SDRAM變成IDLE狀態.4-9. 輸入無效(DESL)不接受輸入的命令,不過內部狀態被保留.4-10. No-operation(NOP)SDRAM接受此命令,但此命令並非執行命令,SDRAM的狀態保持不變.五、SDRAM存取動作如圖5-1,為SDRAM資料讀出的一個例子,所有動作都以時鍾信號(Clock)的上升緣為時間的基準.圖5-1 SDRAM的Read動作5-1. ROW Address(行地址)與Bank號碼的指定.由於SDRAM處于IDLEZ狀態,所以利用/RAS,/CAS,/WE,/CS發出ACTV命令,同時分別將行地址A0-A12及BA0/BA1輸入到指定行地址及Bank號碼,啟動所指定的Bank,移轉至Row Active狀態,隨後等待Trcd期間後即可接受下一命令,Trcd在承認書中有規定.5-2. 列地址指定及讀出命令的發行.經過Trcd過,與時鐘信號的上升波緣同步,將Read command,列地址及所要讀取的Bank編號輸入SDRAM,在讀出動作時,可連續讀出Mode Register設定的Burst長度份的資料.5-3. CAS Lantency待機發出Read命令後,經過Mode Register所設定的CAS Latency Clock數後資料輸出.圖5-1所示為CAS Latency=3時的動作情形.5-4. 資料取入經過CAS Latency時間後,Mode Register所指定的Burst Length份的資料連續出來,將此資料如入,圖5-1所示為BL=4的動作情形.資料輸出結束後DRAM 的輸出緩衝器自動變為高阻抗狀態.六、SDRAM寫入動作圖6-1所示為一個SDRAM寫入動作的例子.圖6-1 SDRAM寫入動作6-1. 行地址及Bank寫入動作發送ACTV命令給處于IDLE狀態的SDRAM,同時發送行地址和Bank號碼輸入SDRAM,即可接受下面的寫入命令的狀態6-2. 寫入命令的發送.發送ACTV命令後,等待Trcd時間後變成可接受下一個命令的狀態,接著將列地址及所要寫入的資料輸入SDRAM,同時發送Write命令,和Read不同的是,不用在意Latency,可將命令和資料同時發送給SDRAM.6-3. 資料連續寫入執行Burst Write時,隨後連續輸入資料,只要將Mode Register的Burst Length 所指定的規模(size)的資料送給SDRAM,在DRAM內部自動更新要寫入的地址,執行Burst Write動作,圖中所示的為BL=4時的動作情況.。