IC datasheet pdf-1SS108 pdf datasheet

RS811 Datasheet

Manual Reset

The manual-reset input (MR) allows reset to be triggered by a push button switch. MR has an internal pullup resistor, so it

can be left open when not used.

Pin Configuration

Pin Description

Pin VCC Type Description Supply Voltage. Reset is asserted when VCC drops below the Reset Threshold Voltage (V RST). Reset remains asserted until VCC rises above VRST and keep asserted for the duration of the Reset Timeout Period (tRS) once VCC rises above VRST. Ground Active-Low Reset Output (Push-Pull). It goes low when Vcc is below the reset threshold. It remains low for about 200ms after Vcc rises above the reset threshold (VRST). Manual-Reset: (CMOS). Active low. Pull low to force a reset. Reset remains asserted for the duration of the Reset Timeout Period after MR transitions from low to high. Leave unconnected or connected to VCC if not used.

S108T01;S108T01F;S208T01;中文规格书,Datasheet资料

S108T01 Series S208T01 Series■ FeaturesI T (rms)≤8A, Non-Zero Cross type Low profile SIP 4pin Triac output SSR1. Output current, I T (rms)≤8.0A2. Non-zero crossing functionary3. Slim 4 pin low profile SIP package4. High repetitive peak off-state voltage (V DRM : 600V, S208T01 Series ) (V DRM : 400V, S108T01 Series )5. High isolation voltage between input and output (V iso (rms) : 3.0kV)6. Lead-free terminal components are also available (see Model Line-up section in this datasheet)7. Screw hole for heat sink■ DescriptionS108T01 Series and S208T01 Series Solid State Relays (SSR) are an integration of an infrared emitting diode (IRED), a Phototriac Detector and a main output Triac. These devices are ideally suited for controlling high voltage AC loads with solid state reliability while providing 3.0kV isolation (V iso (rms)) from input to out-put.Notice The content of data sheet is subject to change without prior notice.In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP ■ Agency approvals/Compliance1. Isolated interface between high voltage AC devices and lower voltage DC control circuitry.2. Switching motors, fans, heaters, solenoids, and valves.3. Phase or power control in applications such as light-ing and temperature control equipment.■ Applications1. Package resin : UL flammability grade (94V-0)∗Zero cross type is also available. (S108T02 Series/S208T02 Series)∗ : Do not allow external connection.( ) : Typical dimensions■Internal Connection DiagramOutput (Triac T1)Output (Triac T2)Input (+)Input (−)■ Outline Dimensions(Unit : mm)Date code (2 digit)Rank markThere is no rank mark indicator and currently there are no rank offered for this device.A.D.199019911992199319941995199619971998199920002001MarkABCDEFHJKLMN Mark P R S T U V W X A B C Mark 123456789O N DMonth January February March April May June July August September October November December A.D 20022003200420052006200720082009201020112012······2nd digitMonth of production 1st digitYear of productionCountry of originJapanrepeats in a 20 year cycle■ Electro-optical CharacteristicsParameter Symbol Unit InputOutput (T a =25˚C)Forward voltageReverse currentRepetitive peak OFF-state currentON-state voltageHolding currentCritical rate of rise of OFF-state voltageCritical rate of rise of OFF-state voltage at commutaion Minimum trigger currentIsolation resistanceTurn-on time Turn-off timeThermal resistanceI F =20mA V R =3V V D =V DRM I T (rms)=2A, Resistance load, I F =20mA −V D =2/3•V DRM T j =125˚C , V D =2/3•V DRM , dI T /dt =−4.0A/msV D =12V, R L =30ΩDC500V, 40 to 60%RH V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadV D (rms)=200V, AC50Hz, I F =20mAI T (rms)=2A, Resistance load V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadV D (rms)=200V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadBetween junction and case Between junction and ambience Conditions MIN.TYP.MAX.Transfer charac-teristicsS108T01S208T01S108T01S208T01V µA µA V mA V/µs V/µs mA Ωmsms˚C /W −−−−−305−1010−−−−−−1.2−−−−−−−−−−−−4.5401.41001001.550−−8−111010−−V F I R I DRM V T (rms)I H dV/dt(dV/dt)c I FT R ISO t ont off R th (j-c)R th (j-a)■ Absolute Maximum RatingsParameter Symbol Rating UnitInputOutput(T a =25˚C)Forward current Reverse voltage RMS ON-state current Peak one cycle surge current Repetitive peak OFF-state voltage Non-Repetitive peak OFF-state voltage Critical rate of rise of ON-state current Operating frequency Isolation voltage Operating temperature Storage temperature Soldering temperature *2*1I FV R I T (rms)I surge V DRMV DSMdI T /dt fV iso (rms)T opr T stg T solmA V A A VVA/µs Hz kV ˚C ˚C ˚C*3*3*45068804006004006005045 to 653.0−25 to +100−30 to +125260*1 40 to 60%RH, AC for 1minute, f =60Hz *2 For 10s*3 Refer to Fig.1, Fig.2*4 f =60Hz sine wave, T j =25˚C startS108T01S208T01S108T01S208T01Soldering areaShipping PackageModel No.Sleeve 25pcs/sleeve S108T01F S208T01FI FT [mA](V D =12V, R L =30Ω)MAX.8400MAX.8600V DRM [V]Please contact a local SHARP sales representative to see the actual status of the production.■ Model Line-up (1) (Lead-free terminal components)■ Model Line-up (2) (Lead solder plating components)Shipping PackageModel No.Sleeve 25pcs/sleeve S108T01S208T01I FT [mA](V D =12V, R L =30Ω)MAX.8400MAX.8600V DRM [V]F o r w a r d c u r r e n t I F (m A )Ambient temperature T a (˚C)060−2502550751001255040302010Fig.1 Forward Current vs. AmbientTemperatureFig.2 RMS ON-state Current vs.Ambient TemperatureR M S O N -s t a t e c u r r e n t I T (r m s )(A )Ambient temperature T a (˚C)0987654321−25100755025125(1)(2)(3)(4)(5)(1)With infinite heat sink(2)With heat sink (200×200×2mm Al plate)(3)With heat sink (100×100×2mm Al plate)(4)With heat sink (50×50×2mm Al plate)(5)Without heat sink(N ote)In natural cooling condition, please locate Al platevertically, spread the thermal conductive silicone grease on the touch surface of the device and tighten up the device in the center of Al plate at the torque of 0.4N•m.F o r w a r d c u r r e n t I F (m A )Forward voltage V F (mA)1010.1100Fig.4 Forward Current vs. Forward VoltageFig.3 RMS ON-state Current vs.Case TemperatureR M S O N -s t a t e c u r r e n t I T (r m s )(A )Case temperature T C (°C) 010−25255075100125987654321Fig.8-b Repetitive Peak OFF-state Current vs.Ambient Temperature (S208T01)Fig.8-a Repetitive Peak OFF-state Current vs.Ambient Temperature (S108T01)R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8Remarks : Please be aware that all data in the graph are just for reference.Fig.5 Surge Current vs. Power-on CycleFig.6 Minimum Trigger Current vs.Ambient TemperatureFig.7 Maximum ON-state Power Dissipationvs. RMS ON-state CurrentM i n i m u m t r i g g e r c u r r e n t I F T (m A )Ambient temperature T a (˚C)0108642S u r g e c u r r e n t I s u r g e (A )Power-on cycle (Times)10080604020120M a x i m u m O N -s t a t e p o w e r d i s s i p a t i o n (W )RMS ON-state current I T (rms)(A)010864297531■ Design ConsiderationsIn order for the SSR to turn off, the triggering current (l F ) must be 0.1mA or less.In phase control applications or where the SSR is being by a pulse signal, please ensure that the pulse width is a minimum of 1ms.When the input current (I F ) is below 0.1mA, the output Triac will be in the open circuit mode. However, if the voltage across the Triac, V D , increases faster than rated dV/dt, the Triac may turn on. To avoid this situation, please incorporate a snubber circuit. Due to the many different types of load that can be driven, we can merely recommend some circuit vales to start with : Cs=0.022µF and Rs=47Ω. The operation of the SSR and snubber circuit should be tested and if unintentional switching occurs, please adjust the snubber circuit component values accordingly.When making the transition from On to Off state, a snubber circuit should be used ensure that sudden drops in current are not accompanied by large instantaneous changes in voltage across the Triac.This fast change in voltage is brought about by the phase difference between current and voltage. Primarily, this is experienced in driving loads which are inductive such as motors and solenoids. Following the procedure outlined above should provide sufficient results.Any snubber or Varistor used for the above mentioned scenarios should be located as close to the main out-put triac as possible.The load current should be within the bounds of derating curve. (Refer to Fig.2) Also, please use the optional heat sink when necessary.In case the optional heat sink is used and the isolation voltage between the device and the optional heat sink is needed, please locate the insulation sheet between the device and the heat sink.When the optional heat sink is equipped, please set up the M3 screw-fastening torque at 0.3 to 0.5N•m.In order to dissipate the heat generated from the inside of device effectively, please follow the below sugges-tions.(a) Make sure there are no warps or bumps on the heat sink, insulation sheet and device surface.(b) Make sure there are no metal dusts or burrs attached onto the heat sink, insulation sheet and device sur-face.(c) Make sure silicone grease is evenly spread out on the heat sink, insulation sheet and device surface.● Design guide● Recommended Operating ConditionsParameterS108T01S208T01Symbol Unit InputOutputInput signal current at ON state Input signal current at OFF state Load supply voltage Load supply currentFrequencyOperating temperatureI F (ON)I F (OFF)V OUT (rms)I OUT (rms)f T oprmA mA V mA Hz ˚C−−−Locate snubber circuit between output terminals(Cs =0.022µF, Rs =47Ω)−−Conditions(∗) See Fig.2 about derating curve (I T (rms) vs. ambient temperature).16080800.147−20240.1120240I T (rms)×80%(∗)6380MIN.MAX.✩ For additional design assistance, please review our corresponding Optoelectronic Application Notes.● Standard CircuitV 1+V CCS108T01● DegradationIn general, the emission of the IRED used in SSR will degrade over time.In the case where long term operation and / or constant extreme temperature fluctuations will be applied to the devices, please allow for a worst case scenario of 50% degradation over 5years.Therefore in order to maintain proper operation, a design implementing these SSRs should provide at least twice the minimum required triggering current from initial operation.Silicone grease to be used is as follows;1) There is no aged deterioration within the operating temperature ranges.2) Base oil of grease is hardly separated and is hardly permeated in the device.3) Even if base oil is separated and permeated in the device, it should not degrade the function of a device. Recommended grease : G-746 (Shin-Etsu Chemical Co., Ltd.): G-747 (Shin-Etsu Chemical Co., Ltd.): SC102 (Dow Corning Toray Silicone Co., Ltd.) In case the optional heat sink is screwed up, please solder after screwed.In case of the lead frame bending, please keep the following minimum distance and avoid any mechanical stress between the base of terminals and the molding resin.Some of AC electromagnetic counters or solenoids have built-in rectifier such as the diode.In this case, please use the device carefully since the load current waveform becomes similar with rectangu-lar waveform and this results may not make a device turn off.■ Manufacturing Guidelines● Soldering MethodFlow Soldering (No solder bathing)Flow soldering should be completed below 260˚C and within 10s.Preheating is within the bounds of 100 to 150˚C and 30 to 80s.Please solder within one time.Other noticesPlease test the soldering method in actual condition and make sure the soldering works fine, since the impact on the junction between the device and PCB varies depending on the tooling and soldering conditions.分销商库存信息:SHARP-MICROELECTRONICSS108T01S108T01F S208T01。

IC datasheet pdf-ADS7846,pdf(Touch-Screen Controller)

"

"

"

"

"

"

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet, or see the TI web site at .

US Patent No. 6246394 QSPI and SPI are registered trademarks of Motorola.

+VCC

X+ X–

Temperature Sensor

SAR

Y+ Y–

ADS7846

DOUT BUSY

Comparator 6-Channel MUX CDAC Serial Data Out CS

ADS7846

ADS 7846

AD S784 6

®

AD

S784

6

SBAS125H – SEPTEMBER 1999 – REVISED JANUARY 2005

TOUCH SCREEN CONTROLLER

FEATURES

q SAME PATION q INTERNAL 2.5V REFERENCE q q q q DIRECT BATTERY MEASUREMENT (0V to 6V) ON-CHIP TEMPERATURE MEASUREMENT TOUCH-PRESSURE MEASUREMENT QSPITM/SPITM 3-WIRE INTERFACE

PENIRQ

IC datasheet pdf-ADC12C080,pdf datasheet (12-Bit, 65_80 MSPS A_D Converter)

August 2007 ADC12C08012-Bit, 65/80 MSPS A/D ConverterGeneral DescriptionThe ADC12C080 is a high-performance CMOS analog-to-digital converter capable of converting analog input signals into 12-bit digital words at rates up to 80 Mega Samples Per Second (MSPS). This converter uses a differential, pipelined architecture with digital error correction and an on-chip sam-ple-and-hold circuit to minimize power consumption and the external component count, while providing excellent dynamic performance. A unique sample-and-hold stage yields a full-power bandwidth of 1 GHz. The ADC12C080 may be oper-ated from a single +3.0V power supply and consumes low power. A separate +2.5V supply may be used for the digital output interface which allows lower power operation with re-duced noise. A power-down feature reduces the power con-sumption to very low levels while still allowing fast wake-up time to full operation. The differential inputs accept a 2V full scale differential input swing. A stable 1.2V internal voltage reference is provided, or the ADC12C080 can be operated with an external 1.2V reference. Output data format (offset binary versus 2's complement) and duty cycle stabilizer are pin-selectable. The duty cycle stabilizer maintains perfor-mance over a wide range of clock duty cycles.The ADC12C080 is available in a 32-lead LLP package and operates over the industrial temperature range of −40°C to +85°C.Features■ 1 GHz Full Power Bandwidth■Internal reference and sample-and-hold circuit■Low power consumption■Data Ready output clock■Clock Duty Cycle Stabilizer■Single +3.0V supply operation■Power-down mode■32-pin LLP package, (5x5x0.8mm, 0.5mm pin-pitch) Key Specifications■Resolution12 Bits ■Conversion Rate80 MSPS ■SNR (f IN = 170 MHz)68 dBFS (typ)■SFDR (f IN = 170 MHz)86 dBFS (typ)■Full Power Bandwidth 1 GHz (typ)■Power Consumption300 mW (typ) Applications■High IF Sampling Receivers■Wireless Base Station Receivers■Test and Measurement Equipment■Communications Instrumentation■Portable InstrumentationConnection Diagram20211101© 2007 National Semiconductor ADC12C080 12-Bit, 65/80 MSPS A/D Converter 电子发烧友 电子技术论坛Block Diagram20211102Ordering InformationIndustrial (−40°C ≤ T A ≤ +85°C)Package ADC12C080CISQ 32 Pin LLPADC12C080CISQE 32 Pin LLP,250-Piece Tape and ReelADC12C080EBEvaluation Board 2A D C 12C 080 电子发烧友 电子技术论坛Pin Descriptions and Equivalent CircuitsPin No.SymbolEquivalent CircuitDescriptionANALOG I/O5V IN +Differential analog input pins. The differential full-scale input signal level is 2V P-P with each input pin signal centered on a common mode voltage, V CM .6V IN -2V RP These pins should each be bypassed to AGND with a low ESL (equivalent series inductance) 0.1 µF capacitor placed very close to the pin to minimize stray inductance. A 0.1 µF capacitor should be placed between V RP and V RN as close to the pins as possible,and a 1 µF capacitor should be placed in parallel.V RP and V RN should not be loaded. V CMO may be loaded to 1mA for use as a temperature stable 1.5V reference.It is recommended to use V CMO to provide the common mode voltage, V CM , for the differential analog inputs, V IN + and V IN −.32V CMO1V RN31V REFReference Voltage. This device provides an internally developed 1.2V reference. When using the internal reference, V REF should be decoupled to AGND with a 0.1 µFand a 1 µF low equivalent series inductance (ESL) capacitor.This pin may be driven with an external 1.2V reference voltage.This pin should not be used to source or sink current.12OF/DCSThis is a four-state pin controlling the input clock mode and output data format.OF/DCS = V A , output data format is 2's complement without duty cycle stabilization applied to the input clockOF/DCS = AGND, output data format is offset binary, without duty cycle stabilization applied to the input clock.OF/DCS = (2/3)*V A , output data is 2's complement with duty cycle stabilization applied to the input clockOF/DCS = (1/3)*V A , output data is offset binary with duty cycle stabilization applied to the input clock.DIGITAL I/O11CLKThe clock input pin.The analog input is sampled on the rising edge of the clock input.30PDThis is a two-state input controlling Power Down.PD = V A , Power Down is enabled and power dissipation is reduced.PD = AGND, Normal operation.ADC12C080 电子发烧友 电子技术论坛Pin No.Symbol Equivalent Circuit Description15-19,23-29D0–D11Digital data output pins that make up the 12-bit conversion result.D0 (pin 15) is the LSB, while D11 (pin 29) is the MSB of the output word. Output levels are CMOS compatible.21DRDYData Ready Strobe. The data output transition is synchronized with the falling edge of this signal. This signal switches at the same frequency as the CLK input.ANALOG POWER 3, 8, 10V APositive analog supply pins. These pins should be connected to a quiet voltage source and be bypassed to AGND with 0.1 µF capacitors located close to the power pins.4, 7, 9,Exposed Pad AGNDThe ground return for the analog supply.The exposed pad on back of package must be soldered to ground plane to ensure rated performance.DIGITAL POWER20V DRPositive driver supply pin for the output drivers. This pin should be connected to a quiet voltage source and be bypassed to DRGND with a 0.1 µF capacitor located close to the power pin.22DRGNDThe ground return for the digital output driver supply. This pins should be connected to the system digital ground, but not be connected in close proximity to the ADC's AGND pins. 4A D C 12C 080 电子发烧友 电子技术论坛Absolute Maximum Ratings (Notes 1, 3)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V A , V DR )−0.3V to 4.2V Voltage on Any Pin (Not to exceed 4.2V)−0.3V to (V A +0.3V)Input Current at Any Pin other than Supply Pins (Note 4)±5 mA Package Input Current (Note 4)±50 mA Max Junction Temp (T J )+150°C Thermal Resistance (θJA )30°C/WESD Rating Human Body Model (Note 6)2500V Machine Model (Note 6)250V Storage Temperature −65°C to +150°C Soldering process must comply with National Semiconductor's Reflow Temperature Profilespecifications. Refer to /packaging.(Note 7)Operating Ratings(Notes 1, 3)Operating Temperature −40°C ≤ T A ≤ +85°CSupply Voltage (V A )+2.7V to +3.6V Output Driver Supply (V DR )+2.4V to V AClock Duty Cycle(DCS Enabled)30/70 %(DCS disabled)45/55 %V CM1.4V to 1.6V|AGND-DRGND|≤100mVADC12C080 Converter Electrical CharacteristicsUnless otherwise specified, the following specifications apply: AGND = DRGND = 0V, V A = +3.0V, V DR = +2.5V, Internal V REF =+1.2V, f CLK = 80 MHz, 50% Duty Cycle, DCS Disabled, V CM = V CMO , C L = 5 pF/pin. Typical values are for T A = 25°C. Boldface limits apply for T MIN ≤ T A ≤ T MAX . All other limits apply for T A = 25°C (Notes 8, 9)SymbolParameterConditionsTypical(Note 10)LimitsUnits (Limits)STATIC CONVERTER CHARACTERISTICSResolution with No Missing Codes 12Bits (min)INL Integral Non Linearity ±0.5 1.2LSB (max)-1.2LSB (min)DNL Differential Non Linearity ±0.350.7LSB (max)-0.6LSB (min)PGE Positive Gain Error 0.25±1.25%FS (max)NGENegative Gain Error0.15±1.25%FS (max)TC PGE Positive Gain Error Tempco −40°C ≤ T A ≤ +85°C -7 ppm/°C TC NGE Negative Gain Error Tempco −40°C ≤ T A ≤ +85°C -6 ppm/°C V OFF Offset Error0.065±0.55%FS (max)TC V OFF Offset Error Tempco−40°C ≤ T A ≤ +85°C 7.5 ppm/°CUnder Range Output Code 00Over Range Output Code40954095 REFERENCE AND ANALOG INPUT CHARACTERISTICS V CMO Common Mode Output Voltage 1.5 1.401.56V (min)V (max)V CM Analog Input Common Mode Voltage1.5 1.41.6V (min)V (max)C IN V IN Input Capacitance (each pin to GND)(Note 11)V IN = 1.5 Vdc ± 0.5 V (CLK LOW)8.5 pF (CLK HIGH)3.5 pF V REFInternal Reference Voltage1.18V TC V REF Internal Reference Voltage Tempco −40°C ≤ T A ≤ +85°C 18 ppm/°C V RPInternal Reference top(Note 13)1.981.892.06V (min)V (max)ADC12C080 电子发烧友 电子技术论坛Symbol ParameterConditionsTypical(Note 10)LimitsUnits (Limits)V RN Internal Reference bottom (Note 13)0.980.891.06V (min)V (max)EXT V REFExternal Reference Voltage(Note 13)1.201.1761.224V (min)V (max)ADC12C080 Dynamic Converter Electrical CharacteristicsUnless otherwise specified, the following specifications apply: AGND = DRGND = 0V, V A = +3.0V, V DR = +2.5V, Internal V REF =+1.2V, f CLK = 80 MHz, 50% Duty Cycle, DCS Disabled, V CM = V CMO , C L = 5 pF/pin, . Typical values are for T A = 25°C. Boldface limits apply for T MIN ≤ T A ≤ T MAX . All other limits apply for T A = 25°C (Notes 8, 9)SymbolParameterConditionsTypical(Note 10)LimitsUnits (Limits)(Note 2)DYNAMIC CONVERTER CHARACTERISTICS, A IN = -1dBFS FPBW Full Power Bandwidth -1 dBFS Input, −3 dB Corner1.0 GHz SNRSignal-to-Noise Ratiof IN = 10 MHz 71.2dBFS f IN = 70 MHz 70.5dBFSf IN = 170 MHz 68.567.8dBFS SFDRSpurious Free Dynamic Rangef IN = 10 MHz90 dBFS f IN = 70 MHz 88dBFS f IN = 170 MHz 8682dBFS ENOBEffective Number of Bitsf IN = 10 MHz11.5 Bits f IN = 70 MHz 11.3Bits f IN = 170 MHz 11.110.9Bits THDTotal Harmonic Disortionf IN = 10 MHz−88 dBFS f IN = 70 MHz −86dBFS f IN = 170 MHz −85-80.5dBFS H2Second Harmonic Distortionf IN = 10 MHz−95 dBFS f IN = 70 MHz −90dBFS f IN = 170 MHz −86-82dBFS H3Third Harmonic Distortionf IN = 10 MHz−90 dBFS f IN = 70 MHz −88dBFS f IN = 170 MHz −86-82dBFS SINAD Signal-to-Noise and Distortion Ratio f IN = 10 MHz71.1 dBFS f IN = 70 MHz 70dBFS f IN = 170 MHz68.567.6dBFS IMDIntermodulation Distortionf IN = 19.5MHz and 20.5MHz, each -7dBFS-82dBFSADC12C080 Logic and Power Supply Electrical CharacteristicsUnless otherwise specified, the following specifications apply: AGND = DRGND = 0V, V A = +3.0V, V DR = +2.5V, Internal V REF =+1.2V, f CLK = 80 MHz, 50% Duty Cycle, DCS Disabled, V CM = V CMO , C L = 5 pF/pin. Typical values are for T A = 25°C. Boldface limits apply for T MIN ≤ T A ≤ T MAX . All other limits apply for T A = 25°C (Notes 8, 9)SymbolParameterConditionsTypical (Note 10)LimitsUnits (Limits)DIGITAL INPUT CHARACTERISTICS (CLK, PD)V IN(1)Logical “1” Input Voltage V D = 3.6V 2.0V (min)V IN(0)Logical “0” Input Voltage V D = 3.0V 0.8V (max)I IN(1)Logical “1” Input Current V IN = 3.3V 10 µA I IN(0)Logical “0” Input Current V IN = 0V −10 µA C INDigital Input Capacitance5pF6A D C 12C 080 电子发烧友 电子技术论坛Symbol Parameter ConditionsTypical (Note 10)LimitsUnits (Limits)DIGITAL OUTPUT CHARACTERISTICS (D0–D11, DRDY)V OUT(1)(1)Logical “1” Output Voltage I OUT = −0.5 mA , V DR = 2.4V 2.0V (min)V OUT(0)(0)Logical “0” Output Voltage I OUT = 1.6 mA, V DR = 2.4V 0.4V (max)+I SC Output Short Circuit Source Current V OUT = 0V −10 mA −I SC Output Short Circuit Sink Current V OUT = V DR 10 mA C OUT Digital Output Capacitance5pFPOWER SUPPLY CHARACTERISTICSI A Analog Supply Current Full Operation100123mA (max)I DRDigital Output Supply Current Full Operation (Note 12)12 mA Power ConsumptionExcludes I DR (Note 12)300369mW (max)Power Down Power ConsumptionClock disabled7mWADC12C080 Timing and AC CharacteristicsUnless otherwise specified, the following specifications apply: AGND = DRGND = 0V, V A = +3.0V, V DR = +2.5V, Internal V REF =+1.2V, f CLK = 80 MHz, 50% Duty Cycle, DCS Disabled, V CM = V CMO , C L = 5 pF/pin. Typical values are for T A = 25°C. Timing measurements are taken at 50% of the signal amplitude. Boldface limits apply for T MIN ≤ T A ≤ T MAX . All other limits apply for T A = 25°C (Notes 8, 9)Symb ParameterConditionsTypical (Note 10)Limits Units (Limits) Maximum Clock Frequency 80MHz (max) Minimum Clock Frequency 20MHz (min)t CH Clock High Time 6 ns t CL Clock Low Time 6 ns t CONV Conversion Latency7Clock Cycles t OD Output Delay of CLK to DATA Relative to rising edge of CLK(Note 13) 5.537.3ns (min)ns(max)t SU Data Output Setup Time Relative to DRDY 6.5 5.5ns (min)t H Data Output Hold Time Relative to DRDY 65ns (min)t AD Aperture Delay 0.6 ns t AJAperture Jitter0.1ps rmsADC12C080 电子发烧友 电子技术论坛Dynamic Converter Electrical Characteristics at 65MSPSUnless otherwise specified, the following specifications apply: AGND = DRGND = 0V, V A = +3.0V, V DR = +2.5V, Internal V REF =+1.2V, f CLK = 65 MHz, 50% Duty Cycle, DCS Disabled, V CM = V CMO , C L = 5 pF/pin, . Typical values are for T A = 25°C. Boldface limits apply for T MIN ≤ T A ≤ T MAX . All other limits apply for T A = 25°C (Notes 8, 9)SymbolParameterConditionsTypical (Note 10)LimitsUnits (Limits)(Note 2)DYNAMIC CONVERTER CHARACTERISTICS, A IN = -1dBFSSNRSignal-to-Noise Ratiof IN = 10 MHz71.2dBFS f IN = 70 MHz 70.5dBFS f IN =170 MHz 68.5 dBFS SFDRSpurious Free Dynamic Rangef IN = 10 MHz90 dBFS f IN = 70 MHz 88dBFS f IN = 170 MHz 86 dBFS ENOBEffective Number of Bitsf IN = 10 MHz11.5 Bits f IN = 70 MHz 11.3Bits f IN = 170 MHz 11 Bits THDTotal Harmonic Disortionf IN = 10 MHz−88 dBFS f IN = 70 MHz −85dBFS f IN = 170 MHz −80 dBFS H2Second Harmonic Distortionf IN = 10 MHz-100 dBFS f IN = 70 MHz −95dBFS f IN = 170 MHz −85 dBFS H3Third Harmonic Distortionf IN = 10 MHz−90 dBFS f IN = 70 MHz −88dBFS f IN = 170 MHz −83 dBFS SINADSignal-to-Noise and Distortion Ratiof IN = 10 MHz71.1 dBFS f IN = 70 MHz 69.8dBFS f IN = 170 MHz67.7 dBFS POWER SUPPLY CHARACTERISTICS I A Analog Supply Current Full Operation90mA (max)I DRDigital Output Supply Current Full Operation (Note 12)14.5 mAPower ConsumptionExcludes I DR (Note 12)270mW (max)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.Note 2:Parameters specified in dBFS indicate the value that would be attained with a full-scale input signal.Note 3:All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified.Note 4:When the input voltage at any pin exceeds the power supplies (that is, V IN < AGND, or V IN > V A ), the current at that pin should be limited to ±5 mA. The ±50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.Note 5:The maximum allowable power dissipation is dictated by T J,max , the junction-to-ambient thermal resistance, (θJA ), and the ambient temperature, (T A ), and can be calculated using the formula P D,max = (T J,max - T A )/θJA . The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.Note 6:Human Body Model is 100 pF discharged through a 1.5 k Ω resistor. Machine Model is 220 pF discharged through 0 ΩNote 7:Reflow temperature profiles are different for lead-free and non-lead-free packages.Note 8:The inputs are protected as shown below. Input voltage magnitudes above V A or below GND will not damage this device, provided current is limited per(Note 4). However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. 8A D C 12C 080 电子发烧友 电子技术论坛20211111Note 9:With a full scale differential input of 2VP-P, the 12-bit LSB is 488 µV.Note 10:Typical figures are at TA = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are notguaranteed.Note 11:The input capacitance is the sum of the package/pin capacitance and the sample and hold circuit capacitance.Note 12:IDR is the current consumed by the switching of the output drivers and is primarily determined by load capacitance on the output pins, the supply voltage,V DR , and the rate at which the outputs are switching (which is signal dependent). IDR=VDR(Cx f+ C1x f1+....C11x f11) where VDRis the output driver powersupply voltage, Cn is total capacitance on the output pin, and fnis the average frequency at which that pin is toggling.Note 13:This parameter is guaranteed by design and/or characterization and is not tested in production. ADC12C080 电子发烧友 电子技术论坛Specification DefinitionsAPERTURE DELAY is the time after the falling edge of the clock to when the input signal is acquired or held for conver-sion.APERTURE JITTER (APERTURE UNCERTAINTY) is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.CLOCK DUTY CYCLE is the ratio of the time during one cycle that a repetitive digital waveform is high to the total time of one period. The specification here refers to the ADC clock input signal.COMMON MODE VOLTAGE (V CM ) is the common DC volt-age applied to both input terminals of the ADC.CONVERSION LATENCY is the number of clock cycles be-tween initiation of conversion and when that data is presented to the output driver stage. Data for any given sample is avail-able at the output pins the Pipeline Delay plus the Output Delay after the sample is taken. New data is available at every clock cycle, but the data lags the conversion by the pipeline delay.DIFFERENTIAL NON-LINEARITY (DNL) is the measure of the maximum deviation from the ideal step size of 1 LSB.EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS) is another method of specifying Signal-to-Noise and Distortion Ratio or SINAD. ENOB is defined as (SINAD -1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.FULL POWER BANDWIDTH is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.GAIN ERROR is the deviation from the ideal slope of the transfer function. It can be calculated as:Gain Error = Positive Full Scale Error − Negative Full ScaleError It can also be expressed as Positive Gain Error and Negative Gain Error, which are calculated as:PGE = Positive Full Scale Error - Offset Error NGE = Offset Error - Negative Full Scale ErrorINTEGRAL NON LINEARITY (INL) is a measure of the de-viation of each individual code from a best fit straight line. The deviation of any given code from this straight line is measured from the center of that code value.INTERMODULATION DISTORTION (IMD) is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time.It is defined as the ratio of the power in the intermodulation products to the total power in the original frequencies. IMD is usually expressed in dBFS.LSB (LEAST SIGNIFICANT BIT) is the bit that has the small-est value or weight of all bits. This value is V FS /2n , where “V FS ” is the full scale input voltage and “n” is the ADC reso-lution in bits.MISSING CODES are those output codes that will never ap-pear at the ADC outputs. The ADC is guaranteed not to have any missing codes.MSB (MOST SIGNIFICANT BIT) is the bit that has the largest value or weight. Its value is one half of full scale.NEGATIVE FULL SCALE ERROR is the difference between the actual first code transition and its ideal value of ½ LSB above negative full scale.OFFSET ERROR is the difference between the two input voltages [(V IN +) – (V IN -)] required to cause a transition from code 2047 to 2048.OUTPUT DELAY is the time delay after the falling edge of the clock before the data update is presented at the output pins.PIPELINE DELAY (LATENCY) See CONVERSION LATEN-CY.POSITIVE FULL SCALE ERROR is the difference between the actual last code transition and its ideal value of 1½ LSB below positive full scale.POWER SUPPLY REJECTION RATIO (PSRR) is a measure of how well the ADC rejects a change in the power supply voltage. PSRR is the ratio of the Full-Scale output of the ADC with the supply at the minimum DC supply limit to the Full-Scale output of the ADC with the supply at the maximum DC supply limit, expressed in dB.SIGNAL TO NOISE RATIO (SNR) is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sam-pling frequency, not including harmonics or DC.SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD) Is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral com-ponents below half the clock frequency, including harmonics but excluding d.c.SPURIOUS FREE DYNAMIC RANGE (SFDR) is the differ-ence, expressed in dB, between the rms values of the input signal and the peak spurious signal, where a spurious signal is any signal present in the output spectrum that is not present at the input.TOTAL HARMONIC DISTORTION (THD) is the ratio, ex-pressed in dB, of the rms total of the first six harmonic levels at the output to the level of the fundamental at the output. THD is calculated aswhere f 1 is the RMS power of the fundamental (output) fre-quency and f 2 through f 7 are the RMS power of the first six harmonic frequencies in the output spectrum.SECOND HARMONIC DISTORTION (2ND HARM) is the dif-ference expressed in dB, between the RMS power in the input frequency at the output and the power in its 2nd harmonic level at the output.THIRD HARMONIC DISTORTION (3RD HARM) is the dif-ference, expressed in dB, between the RMS power in the input frequency at the output and the power in its 3rd harmonic level at the output. 10A D C 12C 080 电子发烧友 电子技术论坛Timing Diagram20211109FIGURE 1. Output TimingTransfer Characteristic20211110FIGURE 2. Transfer CharacteristicTypical Performance Characteristics DNL, INL Unless otherwise specified, the followingspecifications apply: AGND = DRGND = 0V, VA = +3.0V, VDR= +2.5V, Internal VREF= +1.2V, fCLK= 80 MHz, 50% Duty Cycle,DCS disabled, VCM = VCMO, CL= 5 pF/pin. TA= 25°C.ADC12C080 电子发烧友 电子技术论坛DNL 20211141INL20211142DNL vs. f CLK 20211143INL vs. f CLK20211144DNL vs. Temperature 20211147INL vs. Temperature20211148A D C 12C 080 电子发烧友 电子技术论坛DNL vs. VA20211149INL vs. VA20211150ADC12C080 电子发烧友 电子技术论坛Typical Performance CharacteristicsUnless otherwise specified, the following specifications apply:AGND = DRGND = 0V, V A = +3.0V, V DR = +2.5V, Internal V REF = +1.2V, f CLK = 80 MHz, 50% Duty Cycle, DCS disabled, V CM =V CMO , f IN = 10 MHz, C L = 5 pF/pin. T A = 25°C.SNR, SINAD, SFDR vs. V A20211151Distortion vs. V A20211152SNR, SINAD, SFDR vs. V DR 20211153Distortion vs. V DR20211154SNR, SINAD, SFDR vs. f CLK 20211155Distortion vs. f CLK20211156A D C 12C 080 电子发烧友 电子技术论坛SNR, SINAD, SFDR vs. Clock Duty Cycle20211157Distortion vs. Clock Duty Cycle20211158SNR, SINAD, SFDR vs. Clock Duty Cycle, DCS Enabled20211159Distortion vs. Clock Duty Cycle, DCS Enabled20211160SNR, SINAD, SFDR vs. fIN20211163Distortion vs. fIN20211164ADC12C080 电子发烧友 电子技术论坛SNR, SINAD, SFDR vs. Temperature 20211165Distortion vs. Temperature20211166Spectral Response @ 10 MHz input 20211168Spectral Response @ 70 MHz input20211169Spectral Response @ 170 MHz input20211170Intermodulation Distortion, f IN 1= 19.5 MHz, f IN 2 = 20.5 MHz20211171A D C 12C 080 电子发烧友 电子技术论坛Power vs. fCLK20211172ADC12C080 电子发烧友 电子技术论坛Functional DescriptionOperating on a single +3.0V supply, the ADC12C080 uses a pipeline architecture and has error correction circuitry to help ensure maximum performance. The differential analog input signal is digitized to 12 bits. The user has the choice of using an internal 1.2V stable reference, or using an external 1.2V reference. Any external reference is buffered on-chip to ease the task of driving that pin.The output word rate is the same as the clock frequency. The analog input is acquired at the rising edge of the clock and the digital data for a given sample is delayed by the pipeline for 7 clock cycles. The digital outputs are CMOS compatible sig-nals that are clocked by a synchronous data ready output signal (DRDY, pin 21) at the same rate as the clock input. Duty cycle stabilization and output data format are selectable using the quad state function OF/DCS pin (pin 12). The output data can be set for offset binary or two's complement.Power-down is selectable using the PD pin (pin 30). A logic high on the PD pin reduces the converter power consumption.For normal operation, the PD pin should be connected to the analog ground (AGND).Applications Information1.0 OPERATING CONDITIONSWe recommend that the following conditions be observed for operation of the ADC12C080: 2.7V ≤ V A ≤ 3.6V 2.4V ≤ V DR ≤ V A20 MHz ≤ f CLK ≤ 80 MHz 1.2V internal referenceV REF = 1.2V (for an external reference) V CM = 1.5V (from V CMO )2.0 ANALOG INPUTS 2.1 Signal Inputs2.1.1 Differential Analog Input PinsThe ADC12C080 has one pair of analog signal input pins,V IN + and V IN −, which form a differential input pair. The input signal, V IN , is defined asV IN = (V IN +) – (V IN −)shows the expected input signal range. Note that the common mode input voltage, V CM , should be 1.5V. Using V CMO (pin 32)for V CM will ensure the proper input common mode level for the analog input signal. The positive peaks of the individual input signals should each never exceed 2.6V. Each analoginput pin of the differential pair should have a maximum peak-to-peak voltage of 1V, be 180° out of phase with each other and be centered around V CM .The peak-to-peak voltage swing at each analog input pin should not exceed the 1V or the out-put data will be clipped.20211115FIGURE 3. Expected Input Signal RangeFor single frequency sine waves the full scale error in LSB can be described as approximatelyE FS = 4096 ( 1 - sin (90° + dev))Where dev is the angular difference in degrees between the two signals having a 180° relative phase relationship to each other (see ). For single frequency inputs, angular errors result in a reduction of the effective full scale input. For complex waveforms, however, angular errors will result in distortion.20211116FIGURE 4. Angular Errors Between the Two Input SignalsWill Reduce the Output Level or Cause Distortion It is recommended to drive the analog inputs with a source impedance less than 100Ω. Matching the source impedance for the differential inputs will improve even ordered harmonic performance (particularly second harmonic).Table 1indicates the input to output relationship of the AD-C12C080.A D C 12C 080 电子发烧友 电子技术论坛。

S108T02;S108T02F;S208T02;中文规格书,Datasheet资料

S108T02 Series S208T02 Series■ FeaturesI T (rms)≤8A, Zero Cross type Low profile SIP 4pin Triac output SSR1. Output current, I T (rms)≤8.0A2. Zero crossing functionary (V OX : MAX. 35V)3. Slim 4 pin low profile SIP package4. High repetitive peak off-state voltage (V DRM : 600V, S208T02 Series ) (V DRM : 400V, S108T02 Series )5. High isolation voltage between input and output (V iso (rms) : 3.0kV)6. Lead-free terminal components are also available (see Model Line-up section in this datasheet)7. Screw hole for heat sink■ DescriptionS108T02 Series and S208T02 Series Solid State Relays (SSR) are an integration of an infrared emitting diode (IRED), a Phototriac Detector and a main output Triac. These devices are ideally suited for controlling high voltage AC loads with solid state reliability while providing 3.0kV isolation (V iso (rms)) from input to out-put.Notice The content of data sheet is subject to change without prior notice.In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP ■ Agency approvals/Compliance1. Isolated interface between high voltage AC devices and lower voltage DC control circuitry.2. Switching motors, fans, heaters, solenoids, and valves.3. Power control in applications such as lighting and temperature control equipment.■ Applications1. Package resin : UL flammability grade (94V-0)∗Non-zero cross type is also available. (S108T01 Series/S208T01 Series)∗ : Do not allow external connection.( ) : Typical dimensions■ Internal Connection Diagram+)−)■ Outline Dimensions(Unit : mm)Date code (2 digit)Rank markThere is no rank mark indicator and currently there are no rank offered for this device.A.D.199019911992199319941995199619971998199920002001MarkABCDEFHJKLMN Mark P R S T U V W X A B C Mark 123456789O N DMonth January February March April May June July August September October November December A.D 20022003200420052006200720082009201020112012······2nd digitMonth of production 1st digitYear of productionCountry of originJapanrepeats in a 20 year cycle■ Electro-optical CharacteristicsParameter Symbol Unit InputOutput (T a =25˚C)Forward voltageReverse currentRepetitive peak OFF-state currentON-state voltageHolding currentCritical rate of rise of OFF-state voltageCritical rate of rise of OFF-state voltage at commutaion Minimum trigger currentZero cross voltageIsolation resistanceTurn-on time Turn-off timeThermal resistanceV F I R I DRM V T (rms)I H dV/dt (dV/dt)c I FT V OX R ISO t ont off R th (j-c)R th (j-a)I F =20mA V R =3V V D =V DRM I T (rms)=2A, Resistance load, I F =20mA −V D =2/3•V DRM T j =125˚C , V D =2/3•V DRM , dI T /dt =−4.0A/msV D =6V, R L =30ΩI F =8mA DC500V, 40 to 60%RH V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance load V D (rms)=200V, AC50Hz, I F =20mA I T (rms)=2A, Resistance load V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadV D (rms)=200V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadBetween junction and case Between junction and ambience Conditions MIN.TYP.MAX.Transfer charac-teristics S108T02S208T02S108T02S208T02−−−−−305−−1010−−−−−−1.2−−−−−−−−−−−−−4.5401.41001001.550−−835−10101010−−V µA µA V mA V/µs V/µs mA V Ωmsms˚C /W ■ Absolute Maximum RatingsParameter Symbol Rating UnitInputOutput(T a =25˚C)Forward current Reverse voltage RMS ON-state current Peak one cycle surge current Repetitive peak OFF-state voltage Non-Repetitive peak OFF-state voltage Critical rate of rise of ON-state current Operating frequency Isolation voltage Operating temperature Storage temperature Soldering temperature *2*1I FV R I T (rms)I surge V DRMV DSMdI T /dt fV iso (rms)T opr T stg T solmA V A A VVA/µs Hz kV ˚C ˚C ˚C*3*3*45068804006004006005045 to 653.0−25 to +100−30 to +125260*1 40 to 60%RH, AC for 1minute, f =60Hz *2 For 10s*3 Refer to Fig.1, Fig.2*4 f =60Hz sine wave, T j =25˚C startS108T02S208T02S108T02S208T02Soldering areaShipping PackageModel No.Sleeve 25pcs/sleeve S108T02F S208T02FI FT [mA](V D =6V, R L =30Ω)MAX.8400MAX.8600V DRM [V]Please contact a local SHARP sales representative to see the actual status of the production.■ Model Line-up (1) (Lead-free terminal components)■ Model Line-up (2) (Lead solder plating components)Shipping PackageModel No.Sleeve 25pcs/sleeve S108T02S208T02I FT [mA](V D =6V, R L =30Ω)MAX.8400MAX.8600V DRM [V]F o r w a r d c u r r e n t I F (m A )Ambient temperature T a (˚C)060−2502550751001255040302010Fig.1 Forward Current vs. AmbientTemperatureFig.2 RMS ON-state Current vs.Ambient TemperatureF o r w a r d c u r r e n t I F (m A )Forward voltage V F (mA)1010.1100Fig.4 Forward Current vs. Forward VoltageFig.3 RMS ON-state Current vs.Case TemperatureR M S O N -s t a t e c u r r e n t I T (r m s )(A )Case temperature T C (°C)010−25255075100125987654321R M S O N -s t a t e c u r r e n t I T (r m s )(A )Ambient temperature T a (˚C)0987654321−25100755025125(1)(2)(3)(4)(5)(1)With infinite heat sink(2)With heat sink (200×200×2mm Al plate)(3)With heat sink (100×100×2mm Al plate)(4)With heat sink (50×50×2mm Al plate)(5)Without heat sink(N ote)In natural cooling condition, please locate Al platevertically, spread the thermal conductive silicone grease on the touch surface of the device and tighten up the device in the center of Al plate at the torque of 0.4N•m.Fig.8-b Repetitive Peak OFF-state Current vs.Ambient Temperature (S208T02)Fig.8-a Repetitive Peak OFF-state Current vs.Ambient Temperature (S108T02)R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8Remarks : Please be aware that all data in the graph are just for reference.Fig.5 Surge Current vs. Power-on CycleFig.6 Minimum Trigger Current vs.Ambient TemperatureFig.7 Maximum ON-state Power Dissipationvs. RMS ON-state CurrentM i n i m u m t r i g g e r c u r r e n t I F T (m A )Ambient temperature T a (°C)0108642S u r g e c u r r e n t I s u r g e (A )Power-on cycle (Times)10080604020120M a x i m u m O N -s t a t e p o w e r d i s s i p a t i o n (W )RMS ON-state current I T (rms)(A)010864297531■ Design ConsiderationsIn order for the SSR to turn off, the triggering current (l F ) must be 0.1mA or less.When the input current (I F ) is below 0.1mA, the output Triac will be in the open circuit mode. However, if the voltage across the Triac, V D , increases faster than rated dV/dt, the Triac may turn on. To avoid this situation, please incorporate a snubber circuit. Due to the many different types of load that can be driven, we can merely recommend some circuit vales to start with : Cs=0.022µF and Rs=47Ω. The operation of the SSR and snubber circuit should be tested and if unintentional switching occurs, please adjust the snubber circuit component values accordingly.When making the transition from On to Off state, a snubber circuit should be used ensure that sudden drops in current are not accompanied by large instantaneous changes in voltage across the Triac.This fast change in voltage is brought about by the phase difference between current and voltage. Primarily, this is experienced in driving loads which are inductive such as motors and solenoids. Following the procedure outlined above should provide sufficient results. For over voltage protection, a Varistor may be used.Any snubber or Varistor used for the above mentioned scenarios should be located as close to the main out-put triac as possible.Particular attention needs to be paid when utilizing SSRs that incorporate zero crossing circuitry.If the phase difference between the voltage and the current at the output pins is large enough, zero crossing type SSRs cannot be used. The result, if zero crossing SSRs are used under this condition, is that the SSR may not turn on and off irregardless of the input current. In this case, only a non zero cross type SSR should be used in combination with the above mentioned snubber circuit selection process.The load current should be within the bounds of derating curve. (Refer to Fig.2) Also, please use the optional heat sink when necessary.In case the optional heat sink is used and the isolation voltage between the device and the optional heat sink is needed, please locate the insulation sheet between the device and the heat sink.When the optional heat sink is equipped, please set up the M3 screw-fastening torque at 0.3 to 0.5N•m.In order to dissipate the heat generated from the inside of device effectively, please follow the below sugges-tions.● Design guide● Recommended Operating ConditionsParameterS108T02S208T02Symbol Unit InputOutputInput signal current at ON state Input signal current at OFF state Load supply voltage Load supply currentFrequencyOperating temperatureI F (ON)I F (OFF)V OUT (rms)I OUT (rms)f T oprmA mA V mA Hz ˚C−−−Locate snubber circuit between output terminals(Cs =0.022µF, Rs =47Ω)−−Conditions(∗) See Fig.2 about derating curve (I T (rms) vs. ambient temperature).16080800.147−20240.1120240I T (rms)×80%(∗)6380MIN.MAX.✩ For additional design assistance, please review our corresponding Optoelectronic Application Notes.● Standard CircuitV +V S108T02● DegradationIn general, the emission of the IRED used in SSR will degrade over time.In the case where long term operation and / or constant extreme temperature fluctuations will be applied to the devices, please allow for a worst case scenario of 50% degradation over 5years.Therefore in order to maintain proper operation, a design implementing these SSRs should provide at least twice the minimum required triggering current from initial operation.(a) Make sure there are no warps or bumps on the heat sink, insulation sheet and device surface.(b) Make sure there are no metal dusts or burrs attached onto the heat sink, insulation sheet and device sur-face.(c) Make sure silicone grease is evenly spread out on the heat sink, insulation sheet and device surface.Silicone grease to be used is as follows;1) There is no aged deterioration within the operating temperature ranges.2) Base oil of grease is hardly separated and is hardly permeated in the device.3) Even if base oil is separated and permeated in the device, it should not degrade the function of a device. Recommended grease : G-746 (Shin-Etsu Chemical Co., Ltd.): G-747 (Shin-Etsu Chemical Co., Ltd.): SC102 (Dow Corning Toray Silicone Co., Ltd.) In case the optional heat sink is screwed up, please solder after screwed.In case of the lead frame bending, please keep the following minimum distance and avoid any mechanical stress between the base of terminals and the molding resin.Some of AC electromagnetic counters or solenoids have built-in rectifier such as the diode.In this case, please use the device carefully since the load current waveform becomes similar with rectangu-lar waveform and this results may not make a device turn off.■ Manufacturing Guidelines● Soldering MethodFlow Soldering (No solder bathing)Flow soldering should be completed below 260˚C and within 10s.Preheating is within the bounds of 100 to 150˚C and 30 to 80s.Please solder within one time.Other noticesPlease test the soldering method in actual condition and make sure the soldering works fine, since the impact on the junction between the device and PCB varies depending on the tooling and soldering conditions.分销商库存信息:SHARP-MICROELECTRONICSS108T02S108T02F S208T02。

Schurter PG06 电源入口模块及线滤波器说明书

1IEC Appliance Inlet C14 with Filter, Fuseholder 2-pole, Line Switch 2-poleAluminum Nickel plated steelApprovals and CompliancesC1470° CDescription - Panel Mount :Screw-on mounting from front side - 4 Functions :Appliance Inlet Protection class I , Line Switch 2-pole , Fuseholder for fuse-links 5 x 20 mm 2-pole , Line filter in standard and medical ver-sion- Quick connect terminals 6.3 x 0.8 mmCharacteristics- Compact design with optimal shielding - All single elements are already wired- Plug removal necessary for fuse-link replacement - With EMC-shield- Suitable for use in equipment according to IEC/UL 60950Suitable for use in medical equipment according to IEC/UL 60601-1Other versions on request- Medical version M80Weblinkspdf datasheet , html-datasheet , General Product Information , Distributor-Stock-Check , Accessories , Detailed request for productT echnical DataRatings IEC1 - 10 A @ Ta 40 °C / 250 VAC; 50 Hz Ratings UL/CSA 1 - 10 A @ Ta 40 °C / 125 VAC; 60 Hz Leakage Current standard < 0.25 mA (250 V / 60 Hz) medical < 5 µA (250 V / 60 Hz)Dielectric Strength> 1.7 kVDC between L-N > 2.7 kVDC between L/N-PE Test voltage (2 sec)Allowable Operation Tempe-rature-25 °C to 85 °CClimatic Category 25/085/21 acc. to IEC 60068-1IP-Protection from front side IP 40 acc. to IEC 60529Protection Class Suitable for appliances with protection class I acc. to IEC 61140TerminalQuick connect terminals 6.3 x 0.8 mm Panel Thickness S Screw: max 8 mmMounting screw torque max 0.5 Nm Material: HousingThermoplastic, black, UL 94V-0appliance inlet/-outletC14 acc. to IEC 60320-1,UL 498, CSA C22.2 no. 42 (for cold conditions) pin-temperature 70 °C, 10 A, Protection Class IFuseholder2-pole, Shocksafe category PC2 acc. to IEC 60127-6,for fuse-links 5 x 20 mm Rated Power Acceptance @ Ta 23 °C5 x 20: 1.6 W (2-pole)Power Acceptance @ Ta > 23°C Admissible power acceptance at higher ambient temperature see derating cur-vesLine Switch2-pole, non-illuminated, acc. to IEC 61058-1Technical DetailsLine FilterStandard and Medical Version, IEC 60939, UL 1283, CSA C22.2 no. 8 Technical DetailsMTBF> 1'700'000 h acc. to MIL-HB-217 FApprovals and CompliancesDetailed information on product approvals, code requirements, usage instructions and detailed test conditions can be looked up in Details about ApprovalsApprovalsThe approval mark is used by the testing authorities to certify compliance with the safety requirements placed on electronic products. Approval Reference T ype: FKIApproval LogoCertificates Certification Body DescriptionVDE Approvals VDE Certificate Number: 40004665UL ApprovalsULUL File Number: E72928Product standardsProduct standards that are referencedOrganization Design StandardDescriptionDesigned according to IEC 60320-1Appliance couplers for household and similar general purposesDesigned according to IEC 60939Passive filters for suppressing electromagnetic interferenceDesigned according to IEC 60127-6Miniature fuses. Part 6. Fuse-holders for miniature fuse-linksDesigned according to IEC 61058-1Switches for appliances. Part 1. General requirements Designed according to UL 498Standard for Attachment Plugs and ReceptaclesDesigned according to UL 1283Electromagnetic interference filtersDesigned according to CSA C22.2 no. 42General Use Receptacles, Attachment Plugs, and Similar Wiring DevicesDesigned according to CSA C22.2 no. 8Electromagnetic interference (EMI) filters Application standardsApplication standards where the product can be usedOrganization Design StandardDescriptionDesigned for applications acc.IEC/UL 60950IEC 60950-1 includes the basic requirements for the safety of informationtechnologyequipment.Designed for applications acc.IEC 60601-1Medical electrical equipment - Part 1: General requirements for basicsafety and essential performanceDesigned for applications acc.IEC 60335-1Safety of electrical appliances for household and similar purposes. Meetsthe requirements for appliances in unattended use. This includes the en-hanced requirements of glow wire tests acc. to IEC 60695-2-12 and -13. CompliancesThe product complies with following Guide LinesIdentification Details Initiator DescriptionCE declaration of conformity SCHURTER AG The CE marking declares that the product complies with the applicablerequirements laid down in the harmonisation of Community legislation onits affixing in accordance with EU Regulation 765/2008.RoHS SCHURTER AG EU Directive RoHS 2011/65/EUChina RoHS SCHURTER AG The law SJ / T 11363-2006 (China RoHS) has been in force since 1 March2007. It is similar to the EU directive RoHS.REACH SCHURTER AG On 1 June 2007, Regulation (EC) No 1907/2006 on the Registration,Evaluation, Authorization and Restriction of Chemicals 1 (abbreviated as"REACH") entered into force.Medical Equipment SCHURTER AG Suitable for use in medical equipment according to IEC/UL 60601-1 Dimension [mm]Case 4523Case 50Diagrams Standard versionNLN’PE’L’1)2)R = 1M Ω1) Line2) only FKI 3) LoadMedical version (M5)NPELN’PE’L’1)2)1) Line 2) only FKI 3) Load4Derating Curves 2-poleA d m i s s i b l e p o w e r a c c e p t a n c e i n W a t tAmbient air temperature T a°CAttenuation Loss- - - - 50Ω differential mode _____ 50Ω common modeStandard version1 A2 A 4 A 6 A10 AMedical version (M5)1 A2 A 4 A 6 A10 AAll VariantsPackaging unit 10 Pcs AccessoriesDescriptionAssorted CoversRear Cover0859.0074Mating Outlets/ConnectorsCategory / DescriptionAppliance Outlet Overview completeIEC Appliance Outlet F, Screw-on Mounting, Front Side, Solder Terminal4787IEC Appliance Outlet F, Snap-in Mounting, Front Side, Solder or Quick-connect Terminal4788IEC Appliance Outlet F or H, Screw-on Mounting, Front Side, Solder, PCB or Quick-connect Terminal5091Appliance Outlet further types to FKI5Connector Overview complete4782 Mounting: Power Cord, 3 x 1 mm² / 3 x 18 AWG, Cable, Connector: IEC C1347824022 Mounting: Power Supply Cord, 3 x 1.5 mm², Screw clamps, Connector: IEC C1340224785 Mounting: Power Cord, 3 x 1 mm² / 3 x 18 AWG, Cable, Connector: IEC C1347854300-06 Mounting: Power Cord, 3 x 1 mm² / 3 x 18 AWG, Cable, Connector: IEC C134300-064012 Mounting: Power Supply Cord, 3 x 1.5 mm², Screw clamps, Connector: IEC C134012Connector further types to FKI...The specifications, descriptions and illustrations indicated in this document are based on currentinformation. All content is subject to modifications and amendments. Information furnished is believed2.12.2176。

IC datasheet pdf-CAT3606 pdf,datasheet

CAT36066-Channel Low Noise Charge Pump White LED DriverDescriptionThe CAT3606 controls up to four LEDs for the main display and two LEDs for the sub-display in cellular phones. The device is capable of operating in either 1x (LDO) mode or 1.5x charge pump mode. All LED pin currents are regulated and tightly matched to achieve uniformity of brightness across the LCD backlight. An external resistor (R SET) sets the nominal output current.The device can deliver as much as 20 mA per channel during low voltage operation (3 V), and 30 mA per channel during nominal operation (3.3 V). A constant high-frequency switching scheme (1MHz) provides low noise and allows the use of very small value ceramic capacitors.A “zero” quiescent current mode can be achieved via the chip enable pin EN. The Main and Sub LEDs each have their own dedicated ON/OFF control pins ENM, ENS. Dimming can be achieved using either a DC voltage to control the R SET pin current, or by applying a PWM signal on the ENM and ENS pins.The device is available in a 16−pad TQFN package with a max height of 0.8 mm.Features•Drives up to 4 Main LEDs and 2 Sub LEDs•Separate Control for Main and Sub LEDs •Compatible with Supply V oltage of 3 V to 5.5 V•Power Efficiency up to 90%•Output Current up to 30 mA per LED•High−frequency Operation at 1 MHz•2 Modes of Operation 1x and 1.5x•White LED Detect Circuitry on All Channels •Shutdown Current less than 1 m A•Small Ceramic Capacitors•Soft Start and Current Limiting•Short Circuit Protection•16−pad TQFN Package, 0.8 mm Max Height•These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS CompliantApplications•Cell Phone Main and Sub−display Backlight•Navigation •PDAs •Digital CamerasTQFN−16HV4 SUFFIXCASE 510AEPIN CONNECTIONS (Note 1)G366MARKING DIAGRAMSDevice Package ShippingORDERING INFORMATIONCAT3606HV4−T2TQFN−16(Note 2)2,000/Tape & ReelG366 = CAT3606HV4−T2CDBB = CAT3606HV4−GT21.The “exposed pad” under the package must beconnected to the ground plane on the PCB.2.Matte−Tin Plated Finish (RoHS−compliant).3.NiPdAu Plated Finish (RoHS−compliant).LED5LED4LED3LED2LED1C2+C2−C1−LED6ENENMENSRSETVOUTVINC1+1(4 x 4 mm) (Top View)CDBBCAT3606HV4−GT2TQFN−16(Note 3)GNDFigure 1. Typical Application Circuitm FLi −OUT Table 1. PIN DESCRIPTIONPin #Name Function1LED6LED6 cathode terminal2EN Enable/shutdown input, active high3ENM Enable “main” input for LED1 to LED4, active low 4ENS Enable “sub” input for LED5 and LED6, active low5RSET The LED output current is set by the current sourced out of the RSET pin 6VOUT Charge pump output connected to the LED anodes 7VIN Supply voltage8C1+Bucket capacitor 1 terminal 9C1Bucket capacitor 1 terminal 10C2Bucket capacitor 2 terminal 11C2+Bucket capacitor 2 terminal 12LED1LED 1 cathode terminal 13LED2LED 2 cathode terminal 14LED3LED 3 cathode terminal 15LED4LED 4 cathode terminal 16LED5LED 5 cathode terminal PADGNDGround referenceTable 2. ABSOLUTE MAXIMUM RATINGSParameter Rating Unit VIN, VOUT, LEDx voltage−0.3 to 7.0V EN, ENM, ENS voltage−0.3 to VIN V RSET voltage−0.3 to VIN V RSET current±1mA Ambient Temperature Range−40 to +85_C Storage Temperature Range−65 to +160_C Lead Temperature300_C ESD Rating HBM (Human Body Model)2,000V ESD Rating MM (Machine Model) (Note 4)200V Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.4.Machine model is with 200 pF capacitor discharged directly into each pin.Table 3. RECOMMENDED OPERATING CONDITIONSParameter Range Unit VIN 3.0 to 5.5V Ambient Temperature Range−40 to +85_C Input/Output/Bucket Capacitors 1 ±20% Typical m FI LED per LED pin0 to 30mAI OUT Total Output Current0 to 150mA Table 4. ELECTRICAL OPERATING CHARACTERISTICS(Limits over recommended operating conditions unless specified otherwise. Typical values at T A = 25°C, V IN = 3.5 V, I RSET = 5 m A.) Symbol Parameter Conditions Min Typ Max UnitI Q Quiescent Current V EN= 0 V1x Mode, No Load1.5x Mode, No Load 0.10.32.6115m AmAmAV RSET RSET Regulated Voltage 1.17 1.2 1.23VI LED Programmed LED Current I RSET = 5 m AI RSET = 37 m AI RSET = 78 m A 2.415.030.0mAI LED LED Current Range with 6 LEDs 3.3 ≤ VIN ≤ 4.5 V3.0 ≤ VIN ≤4.5 V 3020mAI LED LED Current Range with 4 LEDs 3.3 ≤ VIN ≤ 4.5 V30mAI LED−ACC LED Current Accuracy0.5 mA ≤ I LED≤ 3 mA3 mA ≤ I LED≤ 30 mA ±15±5%I LED−DEV LED Channel Matching(I LED – I LEDAVG) / I LEDAVG±3%R OUT Output Resistance(Open Loop)1x Mode,1.5x Mode, I OUT = 100 mA1.46.52.510Wf OSC Charge Pump Frequency0.8 1.0 1.3MHz T DROPOUT1x to 1.5x Mode Transition Dropout Delay0.40.60.9ms I EN−CTR Input Leakage Current On Inputs EN, ENM, ENS1m AV EN−CTR High Detect ThresholdLow Detect Threshold On Inputs EN, ENM, ENS0.40.80.71.3VI SC Input Current Limit VOUT = GND304560mA I LIM Maximum Input Current VOUT > 1 V200400600mABlock DiagramFigure 2. CAT3606 Functional Block Diagramm FVBasic OperationAt power-up, the CA T3606 starts operation in 1x mode. If it is able to drive the programmed LED current, it continues in 1x mode. If the battery voltage drops to a level where the LED current cannot be met, the driver automatically switches into 1.5x mode, to boost the output voltage high enough to achieve the nominal LED current.The above sequence is reinitialized each and every time the chip is powered up or is taken out of shutdown mode (via EN pin). The use of the Main and Sub display enable pins (ENM or ENS) does not affect the mode of operation. LED Current SettingThe LED current is set by the external resistor R SET connected between the RSET pin and ground. Table 5 lists various LED currents and the associated R SET resistor value for standard 1% precision surface mount resistors.Table 5. RSET Resistor SelectionLED Current (mA)R SET (k W)1649228751021049.91532.42023.73015.4The enable lines ENM and ENS allow to turn On or Off a group of LEDs as shown in Table 6.Table 6. LED SelectionControl Lines LED Outputs EN ENM ENSMainLED1 − LED4SubLED5 −LED6 0X X––111––101ON−110−ON100ON ON NOTES:1 = logic high (or VIN)0 = logic low (or GND)– = LED output OFFX = don’t careThe unused LED channels can also be turned off by connecting the respective LED pins to VOUT. In which case, the corresponding LED driver is disabled and the typical LED sink current is only about 0.2 mA. When the following equation is true on any channel, the driver turns off the LED channel:VOUT*V LED v1V(LED channel OFF) Note: The CA T3606 is designed to drive LEDs with forward voltage greater than 1 V and is not compatible with resistive loads.Figure 3. Efficiency vs. Input Voltage(6 LEDs)Figure 4. Efficiency vs. Total LED Current(6 LEDs)INPUT VOLTAGE (V)TOTAL LED CURRENT (mA)405060708090100405060708090100Figure 5. LED Current vs. Input VoltageFigure 6. LED Current Change vs.TemperatureINPUT VOLTAGE (V)TEMPERATURE (°C)−−−0.51.5−−Figure 7. Ground Current vs. Input Voltage(1x Mode)Figure 8. Ground Current vs. Temperature(1x Mode)INPUT VOLTAGE (V)TEMPERATURE (°C)0.10.20.30.40.500.10.20.30.40.5E F F I C I E N C Y (%)E F F I C I E N C Y (%)L E D C U R R E N T C H A N G E (%)L E D C U R R E N T C H A N G E (%)G R O U N D C U R R E N T (m A )G R O U N D C U R R E N T (m A )01.0−−Figure 9. Ground Current vs. Input Voltage(1.5x Mode)Figure 10. Supply Current vs. Input VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)134580120140Figure 11. Oscillator Frequency vs. InputVoltageFigure 12. Oscillator Frequency vs.TemperatureINPUT VOLTAGE (V)TEMPERATURE (°C)0.900.951.001.051.100.900.951.001.051.10Figure 13. Output Resistance vs. Input Voltage(1x Mode)Figure 14. Output Resistance vs. Input Voltage(1.5x Mode)INPUT VOLTAGE (V)INPUT VOLTAGE (V)1234246810G R O U N D C U R R E N T (m A )G R O U N D C U R R E N T (m A )C L O C K F R E Q U E N C Y (M H z )C L O C K F R E Q U E N C Y (M H z )O U T P U T R E S I S T A N C E (W )O U T P U T R E S I S T A N C E (W )2100Figure 15. Switching Waveforms in 1.5x Mode Figure 16. Operating Waveforms in 1x Mode400 nsec/div400 nsec/divCurrent Input 50mV/VIN 50mV/divVOUT Input 50mV/div VIN Figure 17. Power Up 6 LEDs at 15 mA,VIN = 3 V (1.5x Mode)Figure 18. Power Up 6 LEDs at 15 mA,VIN = 3.6 V (1x Mode)400 m sec/div400 m sec/div2V/divVOUT 2V/div EN 2V/divVOUT 100mA/divInput 2V/divEN Figure 19. LED Current vs. R SETFigure 20. Line Transient Responsein 1x ModeRSET (k W )200 m sec/div10,000100100.1101002V/div VOUT 5mA/div Input 1V/div3.6V to4.9VVinL E D C U R R E N T (m A )10mA/Input Current 100mA/divAC coupledCurrent 10mA/div AC coupledAC coupledVOUT 50mV/divdiv divCurrent Current 10001(V IN = 3.6 V, EN = V IN , ENM = ENS = GND, C IN = C OUT = 1 m F, T AMB = 25°C, unless otherwise specified.)Figure 21. Foldback Current Limiting OUTPUT CURRENT (mA)5004003002001000012345O U TP U T V O L T A G E (V )1x ModeFigure 22. RSET Pin Voltage vs. Temperature−50−2502550751001251.161.181.201.221.24R S E T P I N V O L T A G E (V )Figure 23. PWM Dimming at 1 kHz on ENM and ENS50mA/divCurrent Tot. LED 1V/divVOUT ENM & ENS5V/div200 m sec/divTEMPERATURE (°C)Recommended LayoutWhen the driver is in the 1.5x charge pump mode, the 1MHz switching frequency operation requires to minimize trace length and impedance to ground on all 4 capacitors. A ground plane should cover the area on the bottom side of the PCB opposite to the IC and the bypass capacitors.Capacitors Cin and Cout require short connection to ground which can be done with multiple vias as shown on Figure 24.A square copper area matches the QFN16 exposed pad (GND) and must be connected to the ground plane underneath. The use of multiple via will improve the heat dissipation.Figure 24. PCB LayoutPACKAGE DIMENSIONSTQFN16, 4x4CASE 510AE−01ISSUE AA3A1SIDE VIEWTOP VIEW BOTTOM VIEWDETAIL AFRONT VIEWNotes:(1) All dimensions are in millimeters.(2) Complies with JEDEC MO-220.SYMBOL MIN NOM MAXA0.700.750.80A10.000.020.05A30.20 REFb0.250.300.35D 3.90 4.00 4.10D2 2.00−−− 2.25E 4.00E2 2.00−−− 2.25e3.900.65 BSC4.10L0.45−−−0.65CAT3606Example of Ordering Information (Note 7)PrefixDevice #Suffix 5.All packages are RoHS −compliant (Lead −free, Halogen −free).6.The standard lead finish is NiPdAu.7.The device used in the above example is a CAT3606HV4−GT2 (TQFN, NiPdAu Plated Finish, Tape & Reel, 2,000/Reel).8.For Matte −Tin package option, please contact your nearest ON Semiconductor Sales office.9.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

IC datasheet pdf-THS5661A,pdf(12-Bit, 125 MSPS, CommsDAC Digital-to-Analog Converter)

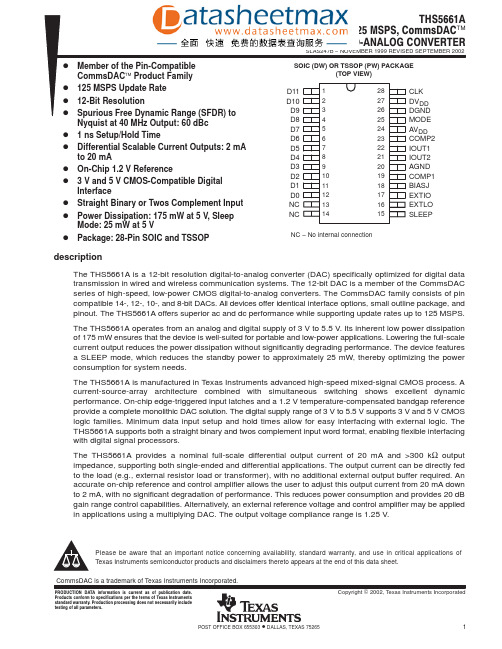

THS5661A 12ĆBIT, 125 MSPS, CommsDAC DIGITALĆTOĆANALOG CONVERTER

D Member of the Pin-Compatible D D D D D D D D D D

CommsDAC Product Family 125 MSPS Update Rate 12-Bit Resolution Spurious Free Dynamic Range (SFDR) to Nyquist at 40 MHz Output: 60 dBc 1 ns Setup/Hold Time Differential Scalable Current Outputs: 2 mA to 20 mA On-Chip 1.2 V Reference 3 V and 5 V CMOS-Compatible Digital Interface Straight Binary or Twos Complement Input Power Dissipation: 175 mW at 5 V, Sleep Mode: 25 mW at 5 V Package: 28-Pin SOIC and TSSOP

Copyright 2002, Texas Instruments Incorporated

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

1

SLAS247B − NOVEMBER 1999 REVISED SEPTEMBER 2002

THS5661A 12ĆBIT, 125 MSPS, CommsDAC DIGITALĆTOĆANALOG CONVERTER

AD9608 Datasheet说明书

ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

10位、125/105 MSPS 、1.8 V双通道模数转换器(ADC)AD9608Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.功能框图VIN+A VIN–AVREF SENSE VCM RBIAS VIN–BVIN+BORA D0A D9A DCOA DRVDDORB D9B D0B DCOBSDIO AGNDAVDDSCLK SPIPROGRAMMING DATAM U X O P T I O NPDWN DFS CLK+CLK–MODE CONTROLSDCS DUTY CYCLE STABILIZER SYNC DIVIDE 1TO 8OEBCSBREF SELECTADCC M O S /L VD S O U T P U T B U F FE RADCC M O S /L VD S O U T P U T B U F FE RAD9608NOTES1. PIN NAMES ARE FOR THE CMOS PIN CONFIGURATION ONLY; SEE FIGURE 7 FOR LVDS PIN NAMES.09977-001图1.1 该产品受美国专利保护。

IC datasheet pdf-ADS8410,pdf (16-Bit, 2-MSPS, LVDS Serial Interface, SAR ADC)(1)