FSB6726中文资料

2SA966资料

TOSHIBA Transistor Silicon PNP Epitaxial Type (PCT Process)2SA966Audio Power Amplifier Applications• Complementary to 2SC2236 and 3-W output applications.Absolute Maximum Ratings (Ta = 25°C)Characteristics Symbol Rating UnitCollector-base voltage V CBO −30 V Collector-emitter voltage V CEO −30 V Emitter-base voltage V EBO −5 V Collector current I C−1.5 AEmitter currentI E 1.5 A Collector power dissipation P C 900 mW Junction temperature T j 150 °C Storage temperature rangeT stg−55 to 150°CNote: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in thereliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings.Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook (“HandlingPrecautions”/Derating Concept and Methods) and individual reliability data (i.e. reliability test report and estimated failure rate, etc).Unit: mmJEDEC TO-92MOD JEITA ―TOSHIBA 2-5J1A Weight: 0.36 g (typ.)Electrical Characteristics (Ta = 25°C)Characteristics Symbol TestCondition MinTyp.Max UnitCollector cut-off current I CBO V CB = −30 V, I E = 0 ――−100nAEmitter cut-off current I EBO V EB = −5 V, I C = 0 ――−100nA Collector-emitter breakdown voltage V (BR) CEO I C = −10 mA, I B = 0 −30 ―― V Emitter-base breakdown voltage V (BR) EBO I E = −1 mA, I C = 0 −5 ―― VDC current gain h FE(Note)V CE = −2 V, I C = −500 mA 100 ― 320Collector-emitter saturation voltage V CE (sat)I C = −1.5 A, I B = −0.03 A ――−2.0V Base-emitter voltage V BE V CE = −2 V, I C = −500 mA ――−1.0V Transition frequency f T V CE = −2 V, I C = −500 mA ― 120 ― MHz Collector output capacitance C ob V CB = −10 V, I E = 0, f = 1 MHz ― 40 ― pF Note: h FE classification O: 100 to 200, Y: 160 to 320Markinglead (Pb)-free package orlead (Pb)-free finish.indicatorCollector current I C (mA)h FE – ICD C c u r re n t g a i n h F ECollector current I C (mA)V CE (sat) – I CC o l l e c t o r -e m i t t e r s a t u r a t i on v o l t a g eV C E (s a t ) (V )Base-emitter voltage V BE (V)I C – V BEC oll e c t o rc u r r e n t I C (m A )Ambient temperature Ta (°C)P C – TaC o l l e c t o r p owe r d i s s ip a t io n P C (W )Collector-emitter voltage V CE (V)Safe Operating AreaC o l l e c t o r c u r r e n t I C (A )1.00 0 20 40 60 80 100 120 140 160 1800.20.40.60.8−−−−−−−−−−−−−−−−−−Collector-emitter voltage V CE (V)I C – V CEC o l l e c t o r c u r r e n t I C (m A )−−−−−−−−−−−−−−−−−RESTRICTIONS ON PRODUCT USE20070701-EN •The information contained herein is subject to change without notice.•TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer’s own risk.•The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.• Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.。

MPS6726G;MPS6727;MPS6727G;MPS6726;中文规格书,Datasheet资料

VCEO VCBO VEBO

IC PD

−30 −40 −5.0 −1.0 1.0 8.0

Vdc Vdc Vdc Adc W mW/°C

Total Device Dissipation @ TC = 25°C

PD

2.5

W

Derate above 25°C

20

mW/°C

Operating and Storage Junction Temperature Range

0 Cobo Cibo

TJ = 25°C

Cibo

Cobo

-5.0

-10

-15

-20

-25

-1.0

-2.0

-3.0

-4.0

-5.0

VR, REVERSE VOLTAGE (VOLTS)

Figure 6. Capacitance

fT , CURRENT-GAIN - BANDWIDTH PRODUCT (MHz)

C, CAPACITANCE (pF)

VCE = -10 V

100

TJ = 25°C

80

f = 20 MHz

70

40 50

30 -10 -20

-50 -100 -200

-500 -1000

IC, COLLECTOR CURRENT (mA)

Figure 5. Current Gain — Bandwidth Product

Collector −Base Breakdown Voltage (IC = −100 mAdc, IE = 0)

Emitter −Base Breakdown Voltage (IE = −100 mAdc, IC = 0)

LM22676中文资料

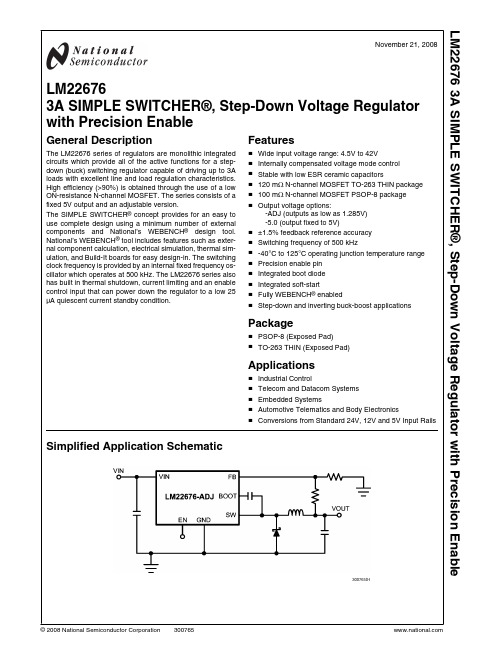

November 21, 2008 LM226763A SIMPLE SWITCHER®, Step-Down Voltage Regulator with Precision EnableGeneral DescriptionThe LM22676 series of regulators are monolithic integrated circuits which provide all of the active functions for a step-down (buck) switching regulator capable of driving up to 3A loads with excellent line and load regulation characteristics. High efficiency (>90%) is obtained through the use of a low ON-resistance N-channel MOSFET. The series consists of a fixed 5V output and an adjustable version.The SIMPLE SWITCHER® concept provides for an easy to use complete design using a minimum number of external components and National’s WEBENCH® design tool. National’s WEBENCH® tool includes features such as exter-nal component calculation, electrical simulation, thermal sim-ulation, and Build-It boards for easy design-in. The switching clock frequency is provided by an internal fixed frequency os-cillator which operates at 500 kHz. The LM22676 series also has built in thermal shutdown, current limiting and an enable control input that can power down the regulator to a low 25µA quiescent current standby condition.Features■Wide input voltage range: 4.5V to 42V■Internally compensated voltage mode control■Stable with low ESR ceramic capacitors■120 mΩ N-channel MOSFET TO-263 THIN package■100 mΩ N-channel MOSFET PSOP-8 package■Output voltage options:-ADJ (outputs as low as 1.285V)-5.0 (output fixed to 5V)■±1.5% feedback reference accuracy■Switching frequency of 500 kHz■-40°C to 125°C operating junction temperature range■Precision enable pin■Integrated boot diode■Integrated soft-start■Fully WEBENCH® enabled■Step-down and inverting buck-boost applications Package■PSOP-8 (Exposed Pad)■TO-263 THIN (Exposed Pad)Applications■Industrial Control■Telecom and Datacom Systems■Embedded Systems■Automotive Telematics and Body Electronics■Conversions from Standard 24V, 12V and 5V Input RailsSimplified Application Schematic30076501© 2008 National Semiconductor LM22676 3A SIMPLE SWITCHER®, Step-Down Voltage Regulator with Precision EnableConnection Diagrams300765408-Lead Plastic PSOP-8 Package NS Package Number MRA08B300765027-Lead Plastic TO-263 THIN PackageNS Package Number TJ7AOrdering InformationOutput VoltageOrder Number Package Type NSC Package DrawingSupplied As ADJ LM22676MR-ADJ PSOP-8 Exposed PadMRA08B95 Units in Rails ADJ LM22676MRE-ADJ 250 Units in Tape and Reel ADJ LM22676MRX-ADJ 2500 Units in Tape and Reel ADJ LM22676TJE-ADJ TO-263 THIN Exposed PadTJ7A250 Units in Tape and Reel ADJ LM22676TJ-ADJ 1000 Units in Tape and Reel5.0LM22676MR-5.0PSOP-8 Exposed PadMRA08B95 Units in Rails 5.0LM22676MRE-5.0250 Units in Tape and Reel 5.0LM22676MRX-5.02500 Units in Tape and Reel 5.0LM22676TJE-5.0TO-263 THIN Exposed PadTJ7A250 Units in Tape and Reel 5.0LM22676TJ-5.01000 Units in Tape and Reel 2L M 22676Pin DescriptionsPin Numbers PSOP-8Package Pin NumbersTO-263 THINPackageName Description Application Information13BOOT Bootstrap input Provides the gate voltage for the high side NFET.2, 35NC Not Connected Pins are not electrically connected inside the chip. Pins dofunction as thermal conductor.46FB Feedback pin Inverting input to the internal voltage error amplifier.57EN Precision enable pin When pulled low regulator turns off.64GND System ground Provide good capacitive decoupling between VIN and thispin72VIN Source input voltage Input to the regulator. Operates from 4.5V to 42V.81SW Switch pin Attaches to the switch nodeLM22676Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.VIN to GND 43VEN Pin Voltage-0.5V to 6V SW to GND (Note 2)-5V to V IN BOOT Pin Voltage V SW + 7V FB Pin Voltage -0.5V to 7V Power DissipationInternally LimitedJunction Temperature 150°CSoldering Information Infrared (5 sec.)260°CESD Rating (Note 3) Human Body Model±2 kVStorage Temperature Range -65°C to +150°COperating Ratings(Note 1)Supply Voltage (V IN )4.5V to 42V Junction Temperature Range-40°C to +125°CElectrical CharacteristicsLimits in standard type are for T J = 25°C only; limits in boldface type apply over thejunction temperature (T J ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at T A = T J = 25°C, and are provided for reference purposes only. Unless otherwise specified: V IN = 12V.Symbol ParameterConditionsMin (Note 5)Typ (Note 4)Max (Note 5)UnitsLM22676-5.0V FBFeedback VoltageV IN = 8V to 42V4.925/4.95.05.075/5.1VLM22676-ADJV FB Feedback Voltage V IN = 4.7V to 42V 1.266/1.2591.285 1.304/1.311V All Output Voltage VersionsI Q Quiescent Current V FB = 5V 3.46mA I STDBY Standby Quiescent Current EN Pin = 0V 2540µA I CL Current Limit3.4/3.354.25.3/5.5A I L Output Leakage Current V IN = 42V, EN Pin = 0V, V SW = 0V 0.22µA V SW = -1V0.13µA R DS(ON)Switch On-Resistance TO-263 THIN Package 0.120.16/0.22ΩPSOP-8 Package 0.100.16/0.20f O Oscillator Frequency 400500600kHz T OFFMIN Minimum Off-time 300 ns T ONMIN Minimum On-time100 ns I BIAS Feedback Bias Current V FB = 1.3V (ADJ Version Only) 230 nA V EN Enable Threshold Voltage1.3 1.6 1.9V I EN Enable Input Current EN Input = 0V 6 µA T SD Thermal Shutdown Threshold150 °C θJA Thermal Resistance TJ Junction to ambient temperature resistance (Note 6)22 °C/W θJAThermal ResistanceMR Package, Junction to ambient temperature resistance (Note 7)60°C/W 4L M 22676Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the recommended Operating Ratings is not implied. The recommended Operating Ratings indicate conditions at which the device is functional and should not be operated beyond such conditions.Note 2:The absolute maximum specification of the ‘SW to GND’ applies to DC voltage. An extended negative voltage limit of -10V applies to a pulse of up to 50ns.Note 3:ESD was applied using the human body model, a 100 pF capacitor discharged through a 1.5 k Ω resistor into each pin.Note 4:Typical values represent most likely parametric norms at the conditions specified and are not guaranteed.Note 5:Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National’s Average Outgoing Quality Level (AOQL).Note 6:The value of θJA for the TO-263 THIN (TJ) package of 22°C/W is valid if package is mounted to 1 square inch of copper. The θJA value can range from 20 to 30°C/W depending on the amount of PCB copper dedicated to heat transfer. See application note AN-1797 for more information.Note 7:The value of θJA for the PSOP-8 exposed pad (MR) package of 60°C/W is valid if package is mounted to 1 square inch of copper. The θJA value can range from 42 to 115°C/W depending on the amount of PCB copper dedicated to heat transfer.Typical Performance CharacteristicsUnless otherwise specified the following conditions apply: Vin =12V, T J = 25°C.Efficiency vs I OUT and V INV OUT = 3.3V30076527Normalized Switching Frequency vs Temperature30076504Current Limit vs Temperature30076503Normalized R DS(ON) vs Temperature30076508LM22676Feedback Bias Current vs Temperature30076505Normalized Enable Threshold Voltage vs Temperature30076510Standby Quiescent Current vs Input Voltage 30076506Normalized Feedback Voltage vs Temperature30076507Normalized Feedback Voltage vs Input Voltage30076509 6L M 22676Typical Application Circuit and Block Diagram30076514FIGURE 1. 3.3V VOUT, 3A LM22676Detailed Operating DescriptionThe LM22676 switching regulator features all of the functions necessary to implement an efficient high voltage buck regu-lator using a minimum of external components. This easy to use regulator integrates a 42V N-Channel switch with an out-put current capability of 3A. The regulator control method is based on voltage mode control with input voltage feed for-ward. The loop compensation is integrated into the LM22676so that no external compensation components need to be se-lected or utilized. Voltage mode control offers short minimum on-times allowing short duty-cycles necessary in high input voltage applications. The operating frequency is fixed at 500kHz to allow for small external components while avoiding excessive switching losses. The output voltage can be set as low as 1.285V with the -ADJ device. Fault protection features include current limiting, thermal shutdown and remote shut-down capability. The device is available in the TO-263 THIN and PSOP-8 packages featuring an exposed pad to aid ther-mal dissipation.The functional block diagram with typical application of the LM22676 are shown in Figure 1.The internal compensation of the -ADJ option of the LM22676is optimized for output voltages up to 5V. If an output voltage of 5V or higher is needed, the -5.0 fixed output voltage option with an additional external resistive feedback voltage divider may also be used.Precision EnableThe precision enable pin (EN) can be used to shut down the power supply. Connecting this pin to ground or to a voltage less than typical 1.6V will completely turn off the regulator.The current drain from the input supply when off is typically 25 µA with 12V input voltage. The power consumed during this off state is mostly defined by an internal 2 M Ω resistor to VIN. The enable pin has an internal pull-up current source of approximately 6 µA. When driving the enable pin, the high voltage level for the on condition should not exceed the 6V absolute maximum limit. When enable control is not required,the EN pin should be left floating. The precision feature en-ables simple sequencing of multiple power supplies with a resistor divider from another power supply.Maximum Duty-Cycle / Dropout VoltageThe typical maximum duty-cycle is 85% at 500 kHz switching frequency. This corresponds to a typical minimum off-time of 300 ns. When operating at switching frequencies higher than 500 kHz, the 300 ns minimum off-time results in a lower max-imum duty-cycle limit than 85%. This forced off-time is impor-tant to provide enough time for the Cboot capacitor to charge during each cycle.The lowest input voltage required to maintain operation is:Where V D is the forward voltage drop across the re-circulating Schottky diode and V Q is the voltage drop across the internal power N-FET of the LM22676. The R DS(ON) of the FET is specified in the electrical characteristics section of this datasheet to calculate V Q according to the FET current. F is the switching frequency.Minimum Duty-CycleBesides a minimum off-time, there is also a minimum on-time which will take effect when the output voltage is adjusted very low and the input voltage is very high. Should the operation require a shorter minimum on-time than the typical 100 ns,individual switching pulses will be skipped.where D is the duty-cycle.Current LimitWhen the power switch turns on, the slight capacitance load-ing of the Schottky diode, D1, causes a leading-edge current spike with an extended ringing period. This spike can cause the current limit comparator to trip prematurely. A leading edge blanking time (T BLK ) of 110 ns (typical) is used to avoid sampling the spike.When the switch current reaches the current limit threshold,the switch is immediately turned off and the internal switching frequency is reduced. This extends the off time of the switch to prevent a steady state high current condition. As the switch current falls below the current limit threshold, the switch cur-rent will attempt to turn on. If a load fault continues, the switch will again exceed the threshold and turn off. This will result in a low duty-cycle pulsing of the power switch to minimize the overall fault condition power dissipation.The switching frequency will reduce (fold back) if the overload condition causes the output voltage to be 72.4% (typical) of the adjusted output voltage.The current limit will only protect the inductor from a runaway condition if the LM22676 is operating in its safe operating area. A runaway condition of the inductor is potentially catas-trophic to the application. For every design, the safe operating area needs to be calculated. Factors in determining the safe operating area are the switching frequency, input voltage,output voltage, minimum on-time and feedback voltage dur-ing an over current condition.As a first pass check, if the following equation holds true, a given design is considered in a safe operating area and the current limit will protect the circuit:V IN x T BLK x F < V OUT x 0.724If the equation above does not hold true, the following sec-ondary equation will need to hold true to be in safe operating area:If both equations do not hold true, a particular design will not have an effective current limit function which might damage the circuit during startup, over current conditions, or steady state over current and short circuit condition. Oftentimes a reduction of the maximum input voltage will bring a design into the safe operating area.Soft-StartThe soft-start feature allows the regulator to gradually reach the initial steady state operating point, thus reducing start-up stresses and surges. The soft-start is fixed to 500 µs (typical)start-up time and cannot be modified.8L M 22676Boot PinThe LM22676 integrates an N-Channel FET switch and as-sociated floating high voltage level shift / gate driver. This gate driver circuit works in conjunction with an internal diode and an external bootstrap capacitor. A 0.01 µF ceramic capacitor connected with short traces between the BOOT pin and the SW pin is recommended to effectively drive the internal FET switch. During the off-time of the switch, the SW voltage is approximately -0.5V and the external bootstrap capacitor is charged from the internal supply through the internal boot-strap diode. When operating with a high PWM duty-cycle, the buck switch will be forced off each cycle to ensure that the bootstrap capacitor is recharged. See the maximum duty-cy-cle section for more details.Thermal ProtectionInternal Thermal Shutdown circuitry protects the LM22676 in the event the maximum junction temperature is exceeded.When activated, typically at 150°C, the regulator is forced into a low power reset state. There is a typical hysteresis of 15degrees.Internal CompensationThe LM22676 has internal compensation designed for a sta-ble loop with a wide range of external power stage compo-nents.Insuring stability of a design with a specific power stage (in-ductor and output capacitor) can be tricky. The LM22676stability can be verified over varying loads and input and out-put voltages using WEBENCH® Designer online circuit sim-ulation tool at . A quick start spreadsheet can also be downloaded from the online product folder.The internal compensation of the -ADJ option of the LM22676is optimized for output voltages below 5V. If an output voltage of 5V or higher is needed, the -5.0 option with an additional external resistor divider may also be used.The typical location of the internal compensation poles and zeros as well as the DC gain is given in Table 1. The LM22676has internal type III compensation allowing for the use of most output capacitors including ceramics.This information can be used to calculate the transfer function from the FB pin to the internal compensation node (input to the PWM comparator in the block diagram).TABLE 1.Corners Frequency Pole 1150 kHz Pole 2250 kHz Pole 3100 Hz Zero 1 1.5 kHz Zero 215 kHz DC gain37.5 dBFor the power stage transfer function the standard voltage mode formulas for the double pole and the ESR zero apply:The peak ramp level of the oscillator signal feeding into the PWM comparator is V IN /10 which equals a gain of 20dB of this modulator stage of the IC. The -5.0 fixed output voltage option has twice the gain of the compensation transfer func-tion compared to the -ADJ option which is 43.5dB instead of 37.5dB.Generally, calculation as well as simulation can only aid in selecting good power stage components. A good design prac-tice is to test for stability with load transient tests or loop measurement tests. Application note AN-1889 shows how to easily perform a loop transfer function measurement with only an oscilloscope and a function generator.Application InformationEXTERNAL COMPONENTSThe following design procedures can be used to design a non-synchronous buck converter with the LM22676.InductorThe inductor value is determined based on the load current,ripple current, and the minimum and maximum input voltage.To keep the application in continuous current conduction mode (CCM), the maximum ripple current, I RIPPLE , should be less than twice the minimum load current.The general rule of keeping the inductor current peak-to-peak ripple around 30% of the nominal output current is a good compromise between excessive output voltage ripple and ex-cessive component size and cost. When selecting the induc-tor ripple current ensure that the peak current is below the minimum current limit as given in the Electrical Characteris-tics section. Using this value of ripple current, the value of inductor, L, is calculated using the following formula:where F is the switching frequency which is 500 kHz (typical).This procedure provides a guide to select the value of the inductor L. The nearest standard value will then be used in the circuit.Increasing the inductance will generally slow down the tran-sient response but reduce the output voltage ripple amplitude.Reducing the inductance will generally improve the transient response but increase the output voltage ripple.The inductor must be rated for the peak current, I PK+, to pre-vent saturation. During normal loading conditions, the peak current occurs at maximum load current plus maximum ripple.Under an overload condition as well as during load transients,the peak current is limited to 4.2A typical (5.5A maximum).This requires that the inductor be selected such that it can run at the maximum current limit and not only the steady state current.Depending on inductor manufacturer, the saturation rating is defined as the current necessary for the inductance to reduce by 30% at 20°C. In typical designs the inductor will run at higher temperatures. If the inductor is not rated for enough current, it might saturate and due to the propagation delay of the current limit circuitry, the power supply may get damaged.Input CapacitorGood quality input capacitors are necessary to limit the ripple voltage at the VIN pin while supplying most of the switch cur-rent during on-time. When the switch turns on, the current into the VIN pin steps to the peak value, then drops to zero at turn-9LM22676off. The average current into VIN during switch on-time is theload current. The input capacitance should be selected forRMS current, IRMS, and minimum ripple voltage. A good ap-proximation for the required ripple current rating necessary isIRMS> IOUT/ 2.Quality ceramic capacitors with a low ESR should be selectedfor the input filter. To allow for capacitor tolerances and volt-age effects, multiple capacitors may be used in parallel. If stepinput voltage transients are expected near the maximum rat-ing of the LM22676, a careful evaluation of ringing and pos-sible voltage spikes at the VIN pin should be completed. Anadditional damping network or input voltage clamp may berequired in these cases.Usually putting a higher ESR electrolytic input capacitor inparallel to the low ESR bypass capacitor will help to reduceexcessive voltages during a line transient and will also movethe resonance frequency of the input filter away from the reg-ulator bandwidth.Output CapacitorThe output capacitor can limit the output ripple voltage andprovide a source of charge for transient loading conditions.Multiple capacitors can be placed in parallel. Very low ESRcapacitors such as ceramic capacitors reduce the output rip-ple voltage and noise spikes, while larger higher ESR capac-itors in parallel provide large bulk capacitance for transientloading conditions. An approximation for the output voltageripple is:where ΔILis the inductor ripple current.Cboot CapacitorThe bootstrap capacitor between the BOOT pin and the SWpin supplies the gate current to turn on the N-channel MOS-FET. The recommended value of this capacitor is 10 nF andshould be a good quality, low ESR ceramic capacitor.It is possible to put a small resistor in series with the Cbootcapacitor to slow down the turn-on transition time of the in-ternal N-channel MOSFET. Resistors in the range of 10Ω to50Ω can slow down the transition time. This can reduce EMIof a switched mode power supply circuit. Using such a seriesresistor is not recommended for every design since it will in-crease the switching losses of the application and makesthermal considerations more challenging.Resistor DividerFor the -5.0 option no resistor divider is required for 5V outputvoltage. The output voltage should be directly connected tothe FB pin. Output voltages above 5V can use the -5.0 optionwith a resistor divider as an alternative to the -ADJ option.This may offer improved loop bandwidth in some applications.See the Internal Compensation section for more details.For the -ADJ option no resistor divider is required for 1.285Voutput voltage. The output voltage should be directly con-nected to the FB pin. Other output voltages can use the -ADJoption with a resistor divider.The resistor values can be determined by the following equa-tions:-ADJ option:-5.0 option:Where VFB= 1.285V typical for the -ADJ option and 5V for the-5.0 option30076523FIGURE 2. Resistive Feedback DividerA maximum value of 10 kΩ is recommended for the sum ofR1 and R2 to keep high output voltage accuracy for the –ADJoption. A maximum of 2 kΩ is recommended for the -5.0 out-put voltage option. For the 5V fixed output voltage option, thetotal internal divider resistance is typically 9.93 kΩ.At loads less than 5 mA, the boot capacitor will not holdenough charge to power the internal high side driver. Theoutput voltage may droop until the boot capacitor isrecharged. Selecting a total feedback resistance to be below3 kΩ will provide some minimal load and can keep the outputvoltage from collapsing in such low load conditions.Catch DiodeA Schottky type re-circulating diode is required for allLM22676 applications. Ultra-fast diodes which are not Schot-tky diodes are not recommended and may result in damageto the IC due to reverse recovery current transients. The nearideal reverse recovery characteristics and low forward volt-age drop of Schottky diodes are particularly important diodecharacteristics for high input voltage and low output voltageapplications common to the LM22676. The reverse recoverycharacteristic determines how long the current surge lastseach cycle when the N-channel MOSFET is turned on. Thereverse recovery characteristics of Schottky diodes mini-mizes the peak instantaneous power in the switch occurringduring turn-on for each cycle. The resulting switching lossesare significantly reduced when using a Schottky diode. Thereverse breakdown rating should be selected for the maxi-mum VIN, plus some safety margin. A rule of thumb is to selecta diode with the reverse voltage rating of 1.3 times the max-imum input voltage.The forward voltage drop has a significant impact on the con-version efficiency, especially for applications with a low outputvoltage. ‘Rated’ current for diodes varies widely from variousmanufacturers. The worst case is to assume a short circuitload condition. In this case the diode will carry the output cur-rent almost continuously. For the LM22676 this current canbe as high as 4.2A (typical). Assuming a worst case 1V drop 10LM22676across the diode, the maximum diode power dissipation can be as high as 4.2W.Circuit Board LayoutBoard layout is critical for switching power supplies. First, the ground plane area must be sufficient for thermal dissipation purposes. Second, appropriate guidelines must be followed to reduce the effects of switching noise. Switch mode con-verters are very fast switching devices. In such devices, the rapid increase of input current combined with the parasitic trace inductance generates unwanted L di/dt noise spikes. The magnitude of this noise tends to increase as the output current increases. This parasitic spike noise may turn into electromagnetic interference (EMI) and can also cause prob-lems in device performance. Therefore, care must be taken in layout to minimize the effect of this switching noise.The most important layout rule is to keep the AC current loops as small as possible. Figure 3 shows the current flow of a buck converter. The top schematic shows a dotted line which rep-resents the current flow during the FET switch on-state. The middle schematic shows the current flow during the FET switch off-state.The bottom schematic shows the currents referred to as AC currents. These AC currents are the most critical since current is changing in very short time periods. The dotted lines of the bottom schematic are the traces to keep as short as possible. This will also yield a small loop area reducing the loop induc-tance. To avoid functional problems due to layout, review the PCB layout example. Providing 3A of output current in a very low thermal resistance package such as the TO-263 THIN is challenging considering the trace inductances involved. Best results are achieved if the placement of the LM22676, the by-pass capacitor, the Schottky diode and the inductor are placed as shown in the example. It is also recommended to use 2oz copper boards or thicker to help thermal dissipation and to reduce the parasitic inductances of board traces.It is very important to ensure that the exposed DAP on the TO-263 THIN package is soldered to the ground area of the PCB to reduce the AC trace length between the bypass ca-pacitor ground and the ground connection to the LM22676. Not soldering the DAP to the board may result in erroneous operation due to excessive noise on the board.30076524FIGURE 3. Current Flow in a Buck ApplicationThermal ConsiderationsThe two highest power dissipating components are the re-circulating diode and the LM22676 regulator IC. The easiestmethod to determine the power dissipation within theLM22676 is to measure the total conversion losses (Pin –Pout) then subtract the power losses in the Schottky diodeand output inductor. An approximation for the Schottky diodeloss is:P = (1 - D) x IOUTx VDAn approximation for the output inductor power is:P = IOUT2 x R x 1.1,where R is the DC resistance of the inductor and the 1.1 factoris an approximation for the AC losses. The regulator has anexposed thermal pad to aid power dissipation. Adding severalvias under the device to the ground plane will greatly reducethe regulator junction temperature. Selecting a diode with anexposed pad will aid the power dissipation of the diode. Themost significant variables that affect the power dissipated bythe LM22676 are the output current, input voltage and oper-ating frequency. The power dissipated while operating nearthe maximum output current and maximum input voltage canbe appreciable. The junction-to-ambient thermal resistance ofthe LM22676 will vary with the application. The most signifi-cant variables are the area of copper in the PC board, thenumber of vias under the IC exposed pad and the amount offorced air cooling provided. The integrity of the solder con-nection from the IC exposed pad to the PC board is critical.Excessive voids will greatly diminish the thermal dissipationcapacity. The junction-to-ambient thermal resistance of theLM22676 TO-263 THIN and PSOP-8 packages are specifiedin the electrical characteristics table under the applicable con-ditions. For more information regarding the TO-263 THINpackage, refer to Application Note AN-1797 at.LM22676。

内存同步

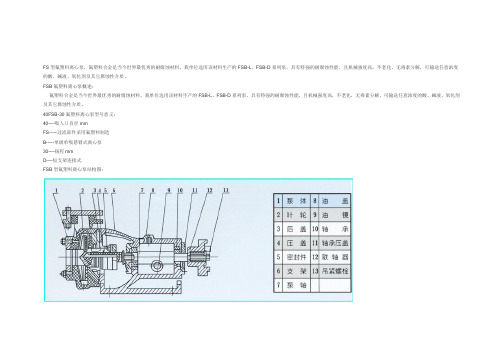

关于内存频率、内存带宽、CPU外频、FSB之间的关系现在的单通道内存控制器一般都是64bit的,8个2进制bit 相当于1个字节,换算成字节是64/8=8,再乘以内存的运行频率,如果是DDR内存就要再乘以2,因为它是以sd内存双倍的速度传输数据的,所以DDR266,运行频率为133MHz,带宽为133*2*64/8=2100MB/s=2.1GB/sDDR333,运行频率为166MHz,带宽为166*2*64/8=2700MB/s=2.7GB/sDDR400,运行频率为200MHz,带宽为200*2*64/8=3200MB/s=3.2GB/s所谓双通道DDR,就是芯片组可以在两个不同的数据通道上分别寻址、读取数据。

这两个相互独立工作的内存通道是依附于两个独立并行工作的,位宽为64-bit的内存控制器下,因此使普通的DDR内存可以达到128-bit的位宽,因此,内存带宽是单通道的两倍,因此双通道DDR266的带宽为133*2*64/8*2=4200MB/s=4.2GB/s双通道DDR333的带宽为166*2*64/8*2=5400MB/s=5.4GB/s双通道DDR400的带宽为200*2*64/8*2=6400MB/s=6.4GB/s关于瓶径问题:CPU与北桥芯片之间的数据传输速率称前端总线(FSB),对于intel的主流平台,其采用Q/P总线技术,FSB=CPU外频*4,如赛扬4的外频为100,其FSB为400,数据带宽为3.2GB/s,P4A 的外频为100,其FSB为400,数据带宽为3.2GB/s,P4B的外频为133,其FSB为533,数据带宽为4.2GB/s,P4C、P4E的外频为200,其FSB为800,数据带宽为6.4GB/s,对于AMD的主流平台,其采用EV6总线技术,FSB=CPU外频*2,对于Athlon XP,其外频为133,166,200,对应的FSB分别为266,333,400,数据带宽分别为2.1,2.7,3.2GB/sFSB与内存带宽相等的情况下,则不存在瓶径问题,如果内存带宽小于FSB则形成内存带宽瓶径,无法完全发挥系统的性能。

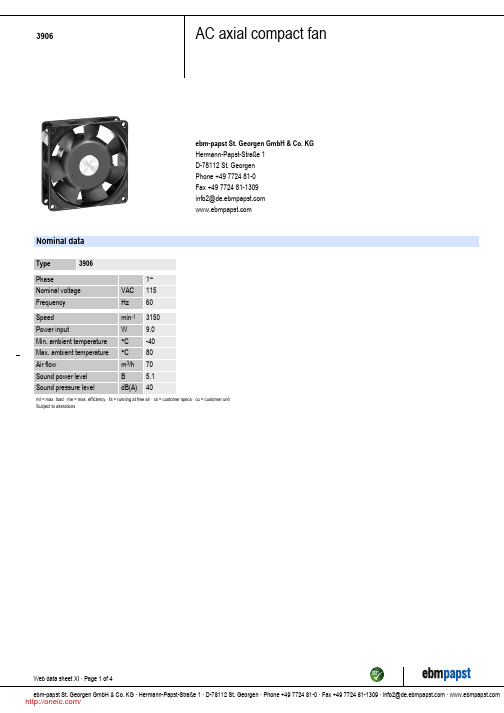

3906;中文规格书,Datasheet资料

Mass Dimensions Material of impeller Housing material Direction of air flow Direction of rotation Bearing Lifetime L10 at 40 °C Lifetime L10 at maximum temperature Connection line Motor protection Approval

3906

AC axial compact fan

ebm-papst St. Georgen GmbH & Co. KG Hermann-Papst-Straße 1 D-78112 St. Georgen Phone +49 7724 81-0 Fax +49 7724 81-1309 info2@

Web data sheet XI · Page 2 of 4 ebm-papst St. Georgen GmbH & Co. KG · Hermann-Papst-Straße 1 · D-78112 St. Georgen · Phone +49 7724 81-0 · Fax +49 7724 81-1309 · info2@ ·

/

3906

AC axial compact fan

Charts: Air flow

(in H ² O) 0,05 0,10 0,15 0,20

∆ pf ä

60 50 40 30 20 10

0

10

20

30

CFM

Vä

•

10

20

30

40

50

60

m³/h

66572资料

April 1996NEC Electronics Inc.A10616EU1V0DS00CMOS-8LHD3.3-Volt, 0.5-Micron CMOS Gate ArraysPreliminary DescriptionNEC's CMOS-8LHD gate-array family combines cell-based-level densities with the fast time-to-market and low development costs of gate arrays. With a unique heterogeneous cell architecture, CMOS-8LHD provides the very dense logic and RAM capabilities required to build devices for fast computer and communications systems.NEC delivers high-speed, 0.5-micron, drawn gate length (Leff=0.35-micron), three-level metal, CMOS technology with an extensive family of macros. I/O macros include GTL, HSTL, and pECL. TTL CMOS I/Os are provided with 5-V tolerance for applications requiring interface to 5-V logic. PCI signaling standards are also supported,including 3.3-V, 66 MHz PCI. The technology is enhanced by a set of advanced features, including phase-locked loops, clock tree synthesis, and high-speed memory. The CMOS-8LHD gate-array family of 3.3-V devices consists of 12 masters, offered in densities of 75K raw gates to 1.123 million raw gates. Usable gates range from 45K to 674K used gates.The gate-array family is supported by NEC's OpenCAD ®design system, a mixture of popular third-party EDA tools,and proprietary NEC tools. NEC proprietary tools include the GALET floorplanner, which helps to reduce design time and improve design speed, and a clock tree synthesis tool that automatically builds a balanced-buffer clock tree to minimize on-chip clock skew.Figure 1. CMOS-8LHD Package Options: BGA & QFPTable 1. CMOS-8LHD Family Features and BenefitsCMOS-8LHD ApplicationsThe CMOS-8LHD family is ideal for use in personal computer systems, engineering workstations, and telecommunications switching and transmission systems, where extensive integration and high speeds are primary design goals. With power dissipation of 0.21 µW/MHz/gate, CMOS-8LHD is also suited for lower-power applications where high performance is required.OpenCAD is a registered trademark of NEC Electronics Inc.CMOS-8LHD2Cell-Based Array ArchitectureThe CMOS-8LHD gate-array family is built with the Cell-Based Array (CBA) architecture licensed from the Silicon Architects Group of Synopsys. CBA architecture uses two types of cells: compute cells and drive cells.This heterogeneous cell architecture enables very high-density design. Compute cells are used to optimize intramacro logic. Drive cells are optimized for intermacro interconnect. The two cell types are also used to build macros with up to three different power/performance/area points.CBA has a rich macrocell library that is optimized for synthesis. RAM blocks are efficiently created from the CBA architecture, using compute cells as memory cores, and sense amplifiers and drive cells as word and address predecoder drivers.As shown in Figure 2, CBA is divided into I/O and array regions. The I/O region contains input and output buffers. The array region contains the gates used to build logic, RAM blocks, and other design features.Power Rail ArchitectureCMOS-8LHD provides additional flexibility for mixedvoltage system designs. As shown in Figure 2, the arrays contain two power rails: a 3.3-V rail, and V DD2.The V DD2 rail is used for interfaces such as 5-V PCI buffers where a clamping diode allows protection for up to an 11-V voltage spike, per the PCI revision 2.1specification.Figure 2. CBA Layout and Cell ConfigurationThe V DD2 rail is separated into sections to give flexibility for including two or more buses requiring special I/O voltage on one device. Each section can operate as an independent voltage zone, and sections can be linked together to form common voltage zones.Packaging and TestNEC utilizes BIST test structures for RAM testing. NEC also offers advanced packaging solutions including Plastic Ball Grid Arrays (PBGA), Plastic Quad Flat Packs (PQFP), and Pin Grid Arrays (PGA). Please call your local NEC ASIC design center representative for a listing of available master/package combinations.PublicationsThis data sheet contains preliminary specifications for the CMOS-8LHD gate-array family. Additional infor-mation will be available in NEC's CMOS-8LHD Block Library and CMOS-8LHD Design Manual . Call your local NEC ASIC design center representative or the NEC literature line for additional ASIC design information; see the back of this data sheet for locations and phone numbers.Table 2. CMOS-8LHD Base Array Line-upDevice Raw Gates Used Gates (1)Total Pads66562750404502416466563997925987518866565125216751292126656617963210777925266568202400121440268665692681281608763086657029792017875232466571359744215845356665725008643005184206657362054437232646866575802240481344532(1) Actual gate utilization varies depending on circuit implementation.Utilization is 60% for 3LM.3CMOS-8LHDInput/Output CapacitanceV DD =V I =0-V; f =1 MHzTerminal Symbol Typ Max Unit Input C IN 1020pF Output C OUT 1020pF I/OC I/O1020pF(1)Values include package pin capacitancePower ConsumptionDescription Limits Unit Internal gate (1)0.21µW/MHz Input buffer 2.546µW/MHz Output buffer10.60µW/MHzAbsolute Maximum RatingsPower supply voltage, V DD –0.5 to +4.6-VInput voltage, V I3.3-V input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 3.3-V fail-safe input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 5 V-tolerant (at V I < V DD + 3.0-V)–0.5 to +4.6-V Output Voltage, V O3.3-V output buffer (at V O < V DD + 0.5-V)–0.5 to +4.6-V 5-V-tolerant output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-V 5-V open-drain output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-VLatch-up current, I LATCH >1 A (typ)Operating temperature, T OPT –40 to +85°C Storage temperature, T STG–65 to +150°C (1) Assumes 30% internal gate switching at one timeCaution: Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.Recommended Operating ConditionsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C3.3-V Interface 5-V Interface5-V PCI 3.3-V PCIBlock BlockLevel LevelParameterSymbol Min Max Min Max Min Max Min Max Unit I/O power supply voltage V DD 3.0 3.6 3.0 3.6 3.0 5.5 3.0 3.6V Junction temperature T J 0+1000+1000+1000+100°C High-level input voltage V IH 2.0V DD 2.0 5.5 2.0V CC 0.5 V CCV CC V Low-level input voltage V IL 00.800.800.800.3 V CCV Positive trigger voltage V P 1.50 2.70 1.50 2.70————V Negative trigger voltage V N 0.60 1.60.60 1.6————V Hysteresis voltage V H 1.10 1.3 1.10 1.3————V Input rise/fall time t R , t F 0200020002000200ns Input rise/fall time, Schmittt R , t F1010————nsAC CharacteristicsV DD = 3.3-V ±0.3-V; T j = –40 to +125°C ParameterSymbol MinTypMax Unit Conditions Toggle frequency (F611)f TOG356MHzD-F/F; F/O = 2 mmDelay time2-input NAND (F322)t PD181ps F/O = 1; L = 0 mmt PD 186ps F/O = 2; L = typ (0.42 mm)Flip-flop (F611)t PD 573ps F/O = 1; L = 0 mm t PD 688ps F/O = 2; L = typ t SETUP 410ps —t HOLD 540ps —Input buffer (FI01)t PD 268ps F/O = 1; L = 0 mm t PD 312ps F/O = 2; L = typ Output buffer (9 mA) 3.3-V (FO01)t PD 1.316ns C L = 15 pF Output buffer (9 mA) 5-V-tolerant (FV01)t PD 1.228ns C L = 15 pF Output buffer (9 mA) 5-V-swing (FY01)t PD 1.517ns C L = 15 pF Output rise time (9 mA) (FO01)t R 1.347ns C L = 15 pF Output fall time (9 mA) (FO01)t F1.284nsC L = 15 pFCMOS-8LHD4(3)Rating is for only one output operating in this mode for less than 1 second.(4)Normal type buffer: I OH < I OL .(5)Balanced buffer: I OH = I OL .(6)Resistor is called 50ký to maintain consistency with previous families.Notes:(1)Static current consumption increases if an I/O block with on-chip pull-up/pull-down resistor or an oscillator is used. Call an NEC ASIC design center repre-sentative for assistance in calculation.(2)Leakage current is limited by tester capabilities. Specification listed representsthis measurement limitation. Actual values will be significantly lower.DC CharacteristicsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C ParameterSymbol Min Typ Max Unit Conditions Quiescent current (1)µPD66578I DDS 2.0300µA V I = V DD or GND µPD66575, 66573, 66572I DDS 1.0300µA V I = V DD or GND Remaining mastersI DDS 0.5200µA V I = V DD or GND Off-state output leakage current3.3-V buffers, 3.3-V PCII OZ ±10µA V O = V DD or GND 5-V-tolerant buffers, 5-V PCI I OZ ±14µA V O = V DD or GND 5-V open-drainI OZ ±14µA V O = V DD or GND Output short circuit current (3)I OS –250mA V O = GND Input leakage current (2)5-V PCI I IH +70, –70µA V IN = 2.7-V, 0.5-V 3.3-V PCI I I ±10µA V IN = V DD or GND RegularI I ±10–5±10µA V I = V DD or GND 50 k Ω pull-up I I –180–40µA V I = GND 5 k Ω pull-up I I –1400–350mA V I = GND 50 k Ω pull-down I I 30160µA V I = V DDResistor values50 k Ω pull-up (6)R pu 2075k Ω5 k Ω pull-upR pu 2.68.6k Ω50 k Ω pull-down (6)R pu 22.5100k ΩInput clamp voltageV IC –1.2V I I = 18 mA Low-level output current (ALL buffer types)3 mA I OL 3mA V OL = 0.4-V 6 mA I OL 6mA V OL = 0.4-V 9 mA I OL 9mA V OL = 0.4-V 12 mA I OL 12mA V OL = 0.4-V 18 mA I OL 18mA V OL = 0.4-V 24 mAI OL 24mA V OL = 0.4-V High-level output current (5-V-tolerant block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –3mA V OH = V DD –0.4-V 9 mA I OH –3mA V OH = V DD –0.4-V 12 mA I OH –3mA V OH = V DD –0.4-V 18 mA I OH –4mA V OH = V DD –0.4-V 24 mAI OH –4mA V OH = V DD –0.4-V High-level output current (3.3-V interface block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –6mA V OH = V DD –0.4-V 9 mA I OH –9mA V OH = V DD –0.4-V 12 mA I OH –12mA V OH = V DD –0.4-V 18 mA I OH -18mA V OH = V DD –0.4-V 24 mAI OH -24mA V OH = V DD –0.4-V Output voltage (5-V PCI)High-level output voltage V OH 2.4mA I OH = 2 mALow-level output voltage V OL 0.55mA I OL = 3 mA, 6 mA Output voltage (3.3-V PCI)High-level output voltage V OH 0.9 V DDmA I OH = 500 µA Low-level output voltage V OL 0.1 V DDmA I OL = 1500 µA Low-level output voltageV OL 0.1V I OL = 0 mA High-level output voltage, 5-V TTL V OH V DD –0.2V I OL = 0 mA High-level output voltage, 3.3-VV OHV DD –0.1VI OH = 0 mACMOS-8LHD5CMOS-8LHD6Document No. A10616EU1V0DS00For literature, call toll-free 7 a.m. to 6 p.m. Pacific time: 1-800-366-9782or FAX your request to: 1-800-729-9288©1996 NEC Electronics Inc./Printed in U.S.A.NEC ASIC DESIGN CENTERSWEST•3033 Scott Boulevard Santa Clara, CA 95054TEL 408-588-5008FAX 408-588-5017•One Embassy Centre9020 S.W. Washington Square Road,Suite 400Tigard, OR 97223TEL 503-671-0177FAX 503-643-5911THIRD-PARTY DESIGN CENTERSSOUTH CENTRAL/SOUTHEAST•Koos Technical Services, Inc.385 Commerce Way, Suite 101Longwood, FL 32750TEL 407-260-8727FAX 407-260-6227•Integrated Silicon Systems Inc.2222 Chapel Hill Nelson Highway Durham, NC 27713TEL 919-361-5814FAX 919-361-2019•Applied Systems, Inc.1761 W. Hillsboro Blvd., Suite 328Deerfield Beach, FL 33442TEL 305-428-0534FAX 305-428-5906NEC Electronics Inc.CORPORATE HEADQUARTERS2880 Scott Boulevard P.O. Box 58062Santa Clara, CA 95052TEL 408-588-6000No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALES ONLY. INCLUDING THE LIMITATION OF LIABILITY,WARRANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding informa-tion set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems,aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. “Standard” quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools,industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliabilty requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death.If customers wish to use NECEL devices in applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine NECEL’s willingness to support a given application.SOUTH CENTRAL/SOUTHEAST•16475 Dallas Parkway, Suite 380Dallas, TX 75248TEL 972-735-7444FAX 972-931-8680•Research Triangle Park2000 Regency Parkway, Suite 455Cary, NC 27511TEL 919-460-1890FAX 919-469-5926•Two Chasewood Park 20405 SH 249, Suite 580Houston, TX 77070TEL 713-320-0524FAX 713-320-0574NORTH CENTRAL/NORTHEAST•The Meadows, 2nd Floor 161 Worcester Road Framingham, MA 01701TEL 508-935-2200FAX 508-935-2234•Greenspoint Tower2800 W. Higgins Road, Suite 765Hoffman Estates, IL 60195TEL708-519-3945FAX 708-882-7564。

6732中文资料

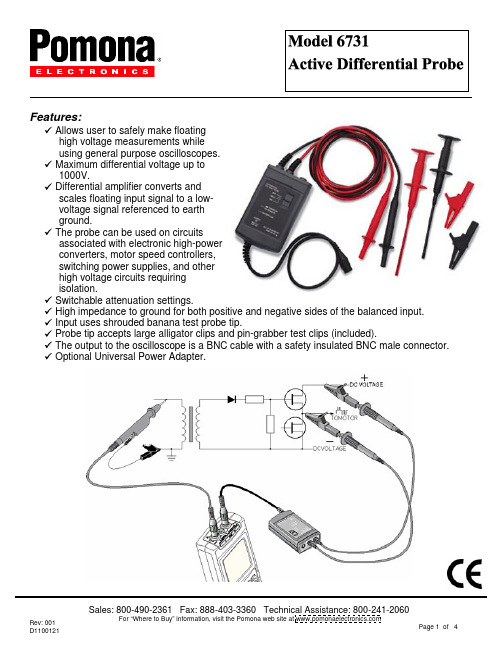

Features:Allows user to safely make floatinghigh voltage measurements whileusing general purpose oscilloscopes.Maximum differential voltage up to1000V.Differential amplifier converts andscales floating input signal to a low-voltage signal referenced to earthground.The probe can be used on circuitsassociated with electronic high-powerconverters, motor speed controllers,switching power supplies, and otherhigh voltage circuits requiringisolation.Switchable attenuation settings.High impedance to ground for both positive and negative sides of the balanced input.Input uses shrouded banana test probe tip.Probe tip accepts large alligator c lips and pin-grabber test clips (included).The output to the oscilloscope is a BNC cable with a safety insulated BNC male connector.Optional Universal Power Adapter.Specifications:Input CharacteristicsInput Probe Tip Style: Shrouded banana probe tipProbe Cable Length: 1.5 meter (60 inch)600V CAT III1000V CAT IIInstallation Category III refers to distribution level and fixed installation circuits inside a building. Installation Category II refers to local level, which is applicable for appliances, and portable equipment.1000 VDC, or1000 Vrms, or1200V (DC+AC peak)Note:(DC+AC peak) limit is determined by the point at which the differential voltage probe starts clipping.For derating of each input probe (red or black), see figure below.Output CharacteristicsOutput Cable: Safety designed BNC cableCable Length: 0.5 meter (20 inch)Max. Output Voltage Range: 6.5V into 1 MElectrical CharacteristicsAttenuation: 200x and 20xBandwidth: (into 1 M , 50 pF)200x: DC to 20 MHz (-3 dB)20x: DC to 20 MHz (-3 dB)Rise time:200x: 17.5 ns20x: 17.5 nsCMRR:200x: @60Hz= >80 dB, @1 MHz= >50 dB20x: @60Hz= >70 dB, @1 MHz= >40 dBInput Impedance:Between each input to shielding BNC: 5 M , 6 pFBetween the inputs: 10 M , 5 pFOutput Impedance: 50Noise:200x: <2 mVrms20x: <3 mVrmsOffset:10 mV into 1 MSwitch positions: OFF, 200x, 20xPowerExternal:Via power adapter 6732 (optional)Internal:Battery Power: Alkaline 9V, IEC6LR61Battery life measured @ 25 C with Duracell® alkaline battery. (Delivered with probe.)Battery Life: 8 hour operation400 hour in auto standbyPower indicators:Green LED: ON at normal operation.Blinks in standby.Red LED: ON when battery needs to be replacing. (To change from standby to normal operation turn switch from OFF to 20x or 200x.)Auto Stand By:After 30 minutes, only when battery operatedEnvironmentalMeets requirements of:MIL-T-28800E, Type III, Class 3.EN 50081-1, Electromagnetic Compatibility Generic Emission Standard: EN55022 and EN60555-2.EN 50082-2, Electromagnetic Compatibility Generic Immunity Standard: IEC801-2, -3, -4, -5. (see also Tables 1 and 2) This product is in conformity with Electromagnetic Compatibility Directive 89/336/EEC and Low Voltage Directive73/23/EEC.This conformity is indicated by the symbol , i.e. “Conformité Européenne”.Temperature:Operating: 0C to +50C (+32F to +122F)Storage: -10C to +60C (+14F to +140F)Altitude:Operating: 3 km (9850 feet)Storage: 12 km (40 000 feet)Safety SpecificationsMeets requirements of:EN61010-2-31 (IEC1010-2-31).Compliant with:UL3111-1 (including listing)CSA C22.2 No.1010.1-92 (including approval)Max. Floating Output Voltage:600V Category III, up to 400 Hz. (From shielding to ground)The 6731 conforms with the EEC directive 89/336 for EMC immunity, as defined by IEC801-3, with the addition of the following tables.Optional power adapter:Universal 115V/230V: Model 6732。

台电U盘工具

中文名:晶彩系列

英文名:

型号:CF512/1GB/2GB/4GB/8GBNCU-W2/B2 CF512NCA-B2

详细资料:更多产品>>

详细资料:

台电晶彩酷闪-CoolFlash Driver(USB Flash Disk)是一种基于闪存技术的移动存储产品。

晶彩u盘拥有十分精良的做工技术。

其深蓝色透明外壳使用最新的超声波无缝焊接技术,内壁采用喷砂工艺,牢固且耐磨损,具有极强的抗震性能。

盘体采用超薄设计,纤巧精致让人不得不感叹台电科技的产品工艺技术;USB帽采用紧缩工艺设计,能够有效防止松脱或丢失;先进的绝缘隔离设计,能够有效的防止静电和灰尘的侵袭;采用顶级闪存芯片,配合一流水准的电路设计,保证了晶彩系列U盘产品的实际可存储容量非常充分,比同类产品的实际可用存储容量要高很多;支持USB 2.0高速读写,为快速存储提供了有力保证。

晶彩(NCU)系列驱动程序

专用于晶彩NCU系列WIN98驱动程序及启动、分区、加密制作工具(支持Vista),适用于全系列(注:从包装彩盒右侧面型号贴纸上可查到产品名称)如:CF4GBNCU-B2

LOCK登入程序

此程序主要解决用户将LOCK程序删除后的解决方法,目前适用于欣喜(晶喜)系列、晶灵II代系列、晶彩系列、晶致系列、欣悦系列产品、晶灵III代系列

酷闪修复工具

此修复工具仅适合以下系列:晶彩系列、晶灵II代、天志系列、晶致系列、欣悦系列、欣喜(晶喜)系列、风尚系列、晶灵III代。

66206-2资料

66206-2 Product DetailsHome | Customer Support | Suppliers | Site Map | Privacy Policy | Browser Support© 2008 Tyco Electronics Corporation All Rights Reserved SearchProducts Documentation Resources My Account Customer Support Home > Products > By Type > Product Feature Selector > Product DetailsNo Image Available66206-2Active Taper Pins and BlocksNot reviewed for RoHS ComplianceProduct Highlights:?Taper Pins?Pin Type = Solid?Pin Style = Standard?53 Series?Loose PieceView all Features | Find SimilarProductsCheck Pricing &AvailabilitySearch for ToolingProduct FeatureSelectorContact Us AboutThis ProductQuick LinksDocumentation & Additional InformationProduct Drawings:?PIN, TAPER, ''53'' SERIES UNINSULATED(PDF, English)Catalog Pages/Data Sheets:?None AvailableProduct Specifications:?Contact, TAYP-AIR Pins and Blocks(PDF, English)?Contact, Taper Pins(PDF, English)Application Specifications:?None AvailableInstruction Sheets:?None AvailableCAD Files:?None AvailableList all Documents Additional Information:?Product Line InformationRelated Products:?ToolingProduct Features (Please use the Product Drawing for all design activity)Product Type Features:?Product Type = Taper Pins?Insulation Support = Un-Insulated Support?Insulation Diameter (mm [in]) = 1.14 – 1.58[0.045 –0.062]?Finish = Gold (30)?Comment = For Stranded Wire Only.Body Related Features:?Pin Type = Solid?Pin Style = Standard?Series = 53?Wire Range (mm [AWG]) = 0.08-0.24²[28-24] ?Overall Length (mm [in]) = 17.27 [0.680]?Mates With = 53 Series Connector Block Industry Standards:?RoHS/ELV Compliance = Not reviewed forELV/RoHS compliance?Lead Free Solder Processes = Not reviewed forlead free solder processPackaging Related Features:?Packaging Method = Loose PieceOther:?Brand = AMPProvide Website Feedback | Contact Customer Support。

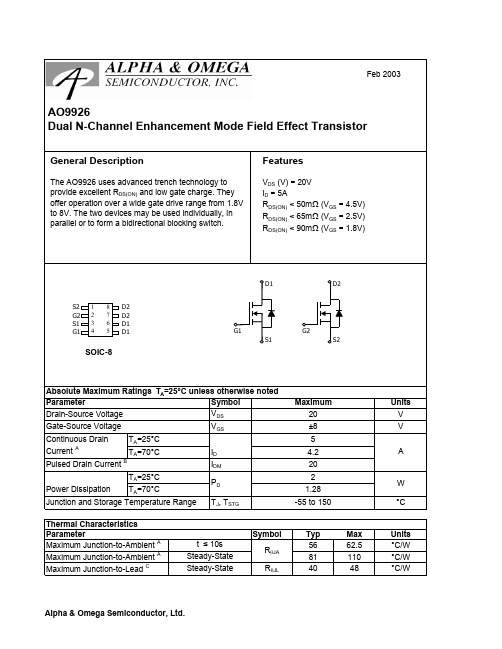

AO9926中文资料

SymbolTyp Max 5662.581110R θJL4048Steady-State °C/W Thermal Characteristics Maximum Junction-to-Lead CSteady-State°C/WParameterUnits Maximum Junction-to-Ambient A t ≤ 10s R θJA °C/W Maximum Junction-to-Ambient A AO9926SymbolMin TypMaxUnits BV DSS 20V 1T J =55°C5I GSS 100nA V GS(th)0.40.61V I D(ON)15A 4050T J =125°C56705465m Ω7290m Ωg FS 11S V SD 0.761V I S2A C iss 436pF C oss 66pF C rss 44pF R g3ΩQ g 5.54nC Q gs 1.26nC Q gd 0.52nC t D(on)5ns t r 7ns t D(off)29ns t f 6.2ns t rr 13.7ns Q rr3.8nCI F =5A, dI/dt=100A/µsI F =5A, dI/dt=100A/µsElectrical Characteristics (T J =25°C unless otherwise noted)ParameterConditions STATIC PARAMETERS Drain-Source Breakdown Voltage I D =250µA, V GS =0V I DSS Zero Gate Voltage Drain Current V DS =16V, V GS =0VµA Gate-Body leakage current V DS =0V, V GS =±8V Gate Threshold Voltage V DS =V GS I D =250µA On state drain currentV GS =10V, V DS =5V R DS(ON)Static Drain-Source On-ResistanceV GS =4.5V, I D =5Am ΩV GS =1.8V, I D =2AV GS =2.5V, I D =4A V GS =0V, V DS =0V, f=1MHzForward TransconductanceV DS =5V, I D =5ADiode Forward Voltage I S =1A,V GS =0V Maximum Body-Diode Continuous CurrentDYNAMIC PARAMETERS Input Capacitance V GS =0V, V DS =10V, f=1MHz Output Capacitance Reverse Transfer Capacitance Turn-On Rise Time Turn-Off DelayTime Gate resistanceBody Diode Reverse Recovery TimeBody Diode Reverse Recovery Charge Turn-Off Fall TimeSWITCHING PARAMETERS Total Gate Charge V GS =4.5V, V DS =10V, I D =5AGate Source Charge Gate Drain Charge Turn-On DelayTime V GS =5V, V DS =10V, R L =2Ω, R GEN =6ΩA: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.。

华硕主板

数字家庭主板M2NDH-支持AMD®SocketAM2Athlon64FX/Athlo64X2/Athlon64/Sempron -AMDLive!™Ready-强大扩充能力:1xPCI-Ex16、2xPCI-E、3xPCI-华硕WiFi-APSolo-华硕DHRemote™-华硕MP3-In™-华硕Q-Connector-高保真音频中央处理器支持AMD®SocketAM2Athlon64FX/Athlo64X2/Athlon64/Sempron 支持AMDCool'n'Quiet™技术AMD64架构,同时兼容32位和64位计算AMDLive!™Ready芯片组NVIDIAnForce®430MCP前端总线2000/1600MT/s内存双通道内存架构4x240-pinDIMM内存插槽,支持最大容量高达8GB的DDR2800/667/533ECC和non-ECC、un-buffered内存扩充插槽1xPCI-Expressx16插槽2xPCI-Expressx1插槽3xPCI2.2插槽存储装置/RAID-1xUltraDMA133/100/66/33-4xSerialATA3.0Gb/s-NVIDIAMediaShield™RAID通过SerialA TA设备支持RAID0、1、0+1、5和JBOD网络功能NVIDIAnForce®430内建GigabitMAC,支持externalAttansicPHY无线局域网:54MbpsIEEE802.11b/g(华硕WiFi-APSolo)音频功能ADI6声道高保真音频CODEC背板S/PDIF数字音频输出USB高达8个USB2.0/1.1接口M2N-VMDH-AMDSocketAM2-NVIDIAGeForce6100/nForce430-双通道DDR2800/667/533-1xPCIExpressx16+1xPCIExpressx1+2xPCI-双VGA:DVI-D和D-Sub-8声道高保真音频-2x1394a接口中央处理器支持AMD®SocketAM2Athlon64X2/Athlon64FX/Athlon64/Sempro nAMDCool'n'Quiet™技术AMD64架构,兼容32位和64位计算AMDLive!™Ready芯片组NVIDIAGeForce6100/nForce430前端总线2000/1600MT/s 内存双通道内存架构4x240-pinDIMM插槽,支持最大容量为8GB的DDR2800/667/533non-ECC,un-buffered内存显卡集成GeForce6100GPU高清晰视频处理,最高分辨率可达1920x1440(@75Hz)支持RGB显示;UXGA1600x1200(@60Hz)支持DVI-D显示支持双VGA输出:DVI-D和RGB注意:DVI-D不能用来输出RGB信号至CRT。

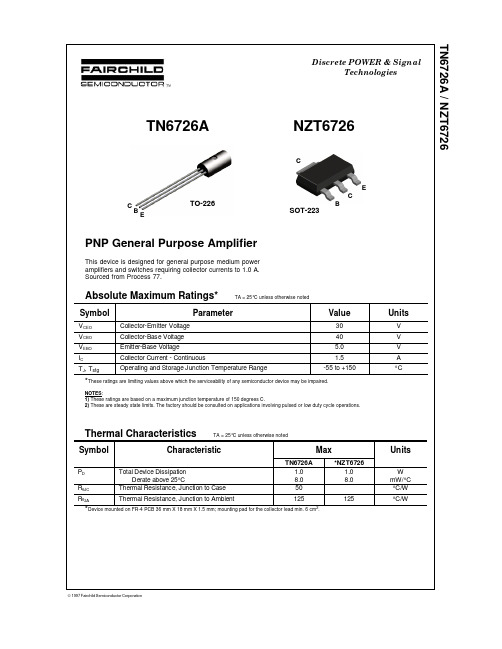

NZT6726中文资料

Absolute Maximum Ratings*

Symbol

VCEO VCBO VEBO IC TJ, Tstg Collector-Emitter Voltage Collector-Base Voltage Emitter-Base Voltage Collector Current - Continuous

Test Conditions

Min

Max

Units

OFF CHARACTERISTICS

V(BR)CEO V(BR)CBO V(BR)EBO ICBO IEBO Collector-Emitter Breakdown Voltage Collector-Base Breakdown Voltage Emitter-Base Breakdown Voltage Collector-Cutoff Current Emitter-Cutoff Current I C = 10 mA, IB = 0 I C = 100 µA, I E = 0 I E = 100 µA, IC = 0 VCB = 40 V, IE = 0 VEB = 5.0 V, IC = 0 30 40 5.0 0.1 0.1 V V V µA µA

1 PD - POWER DISSIPATION (W)

0.75

TO-226 SOT-223

0.5

0.25

0

0

25

50 75 100 o TEMPERATURE ( C)

125

150

SMALL SIGNAL CHARACTERISTICS

hfe Ccb Small-Signal Current Gain Collector-Base Capacitance I C = 50 mA, VCE = 10 V, f = 20 MHz VCB = 10 V, IE = 0, f = 1.0 MHz 2.5 25 30 pF

BA6406F-E2中文资料

Notes

No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD. The contents described herein are subject to change without notice. The specifications for the product described in this document are for reference only. Upon actual use, therefore, please request that specifications to be separately delivered. Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set. Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices. Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, no express or implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by ROHM CO., LTD. is granted to any such buyer. Products listed in this document are no antiradiation design.

SiI3726CBHU资料

Silicon Image, Inc.

Silicon Image, Inc.

June, 2006

Silicon Image, Inc. reserves the right to make changes to the product(s) or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable, but Silicon Image, Inc. shall not be responsible for any errors that may appear in this document. Silicon Image, Inc. makes no commitment to update or keep current the information contained in this document. However, no responsibility is assumed for its use; or any infringement of patents or other rights of third parties, which may result from its use. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information. Silicon Image, Inc. products are not designed or intended for use in Life Support Systems. A Life Support System is a product or system intended to support or sustain life, which if it fails, can be reasonably expected to result in significant personal injury or death. If Buyer or any of its direct or indirect customers applies any product purchased or licensed from Silicon Image, Inc. to any such unauthorized use, Buyer shall indemnify and hold Silicon Image, Inc., its affiliates and their respective suppliers, harmless against all claims, costs, damages and expenses arising directly or indirectly, out of any such unintended or unauthorized use, even if such claims alleges that Silicon Image, Inc. or any other person or entity was negligent in designing or manufacturing the product. Specifications are subject to change without notice

IS61LPS51236A中文资料