EDA软件在三相SPWM变频调制器电路设计中的应用

三相SPWM逆变器的调制建模和仿真

teiv r rT ru hteu eo t b/ i l ka dP w rS se B o k ( S )p we s m lc s t o lo i lt n h e e. h o g s fMal n t h a Smui n o e ytm lc n PB o r y t bo k e ob xs s e T muai o

到 最 终 实现设 计要 求 的 可 视 化 桥 梁 。 被 广 泛 应 用 于 线 性 系统 、 线 性 系统 及 数 字 信 号 处 理 的 建 模 和 仿 真 中。 非 关键 词 : P S WM; 三相 逆 变 器 ; t bSm l k 仿 真 Ma a /i ui ; l n 中 图分 类 号 : M4 4 T 6 文 献 标识 码 : A 文 章编 号 :1 7 — 2 6 2 1 ) l 0 3 — 3 6 4 6 3 (0 3 0 一 12 0

( lc o iI om t nSh o, aguU ie o cec n ehooy Z ejag2 2 0 ,C ia Eet nc n r ai c olJ ns nvr fSinead Tc nl , h n n 1 0 3 hn ) r f o i s g i

Ab t a t h s p p rb e y d s r e h o k n rn i l fte t r ep a e S W M n et rb h i lt n o r e sr c :T i a e r f e c b d te w r i g p i c pe o h e - h s P i l i h - i v r y t e smu ai ft e 。 e o h _ p a eS W M v r r D s r e ei p t n u p t h r c e s A ay i d t e c a a tr f h ot g n u r n h o g h s P i et . e c i d t u d o t u a a t r. n lss h h r ce so e v l e a d c re t r u h n e b h n a c e t a t

三相SPWM逆变器的调制建模和仿真详解

三相SPWM逆变器的调制建模和仿真详解随着电力电子技术的发展,SPWM正弦脉宽调制法正逐渐被人们熟悉,这项技术的特点是通用性强,原理简单。

具有开关频率固定,控制和调节性能好,能消除谐波,设计简单,是一种比较好的波形改善法。

它的出现为中小型逆变器的发展起了重要的推动作用。

由于大功率电力电子装置的结构复杂,若直接对装置进行实验,且代价高费时费力,故在研制过程中需要借助计算机仿真技术,对装置的运行机理与特性,控制方法的有效性进行试验,以预测并解决问题,缩短研制时间。

MATLAB软件具有强大的数值计算功能,方便直观的Simulink建模环境,使复杂电力电子装置的建模与仿真成为可能。

本文利用MATLAB/Simulink为SPWM逆变电路建立系统仿真模型,并对其输出特性进行仿真分析。

首先介绍的是三相电压型桥式逆变电路原理,其次阐述了SPWM逆变器的工作原理及特点,最后详细介绍了三相电压源SPWM逆变器的建模与仿真结构,具体的跟随小编一起了解一下。

一、三相电压型桥式逆变电路三相电压型桥式逆变电路如图1所示,电压型三相桥式逆变电路的基本工作方式也是180导电方式,即每个桥臂的导电角度为180,同一相上下2个桥臂交替导电,各相开始导电的角度依次相差120。

这样,在任一瞬间,将有3个桥臂同时导通。

可能是上面一个臂下面2个臂,也可能是上面两个臂下面一个臂同时导通。

因为每次换流都是在同一相上下两个桥臂之间进行的,因此也被称为纵向换流。

当urU》uc时,给上桥V1臂以导通信号,给下桥臂V4以关断信号,则U相相对于电源假想中点N的输出电压uUN=Ud/2。

当urU《uc时,给V4导通,给V1关断,则uUN=Ud/2。

V1和V4的驱动信号始终是互补的。

当给V1(V4)加导通信号时,可能是V1(V4)导通,也可能是二极管VD1(VD4)续流导通。

二、SPWM逆变器的工作原理及特点SPWM,他是根据面积等效原理,PWM波形和正弦波是等效的,对于正弦波的负半周,也可以用同样的方法得到PWM波形。

用EDA设计全数字三相昌闸管触发器IP软核

用EDA设计全数字三相昌闸管触发器IP软核 IP(Intellectual Propcrty)就是常说的知识产权。

美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。

IP核模块有行为(Behavior)、结构(Structure)和物理(Physical)_三级不同程度的设计。

根据描述功能行为的不同,IP核分为三类。

即软核(Soft IP Corc)、完成结构描述的固核(Firm IP Core)和基于物理描述并经过工艺验证的硬核(Hard IP Core)。

IP软核通常是用HDL文奉形式提交给用户,它经过RTL级设计优化和功能验证,但其中不含有任何具体的物理信息。

据此,用户可以综合出正确的门电路级设计网表,并可以进行后续的结构设计,具有很大的灵活性;借助于EDA综合工具可以很容易地与其他外部逻辑电路合成一体,根据各种不同半导体工艺,设计成具有不同性能的器件。

本文利用先进的EDA软件,用VHDL硬件描述语言采用自顶向下的模块化设计方法,完成了具有相序自适应功能的双脉冲数字移相触发器的IP软核设计。

1 三相全控桥整流电路 如图1所示,三相全控桥整流电路由6只晶闸管组成。

共阴极组侧和共阳级组侧的各3只晶闸管相互换流,在电源的一个周期内获得6次换流的脉动波形。

三相全控桥整流电路在任何时刻必须保证有两个不同组别的晶闸管同时导通才能构成回路。

换流只在本组内进行,每隔120°换流一次。

由于共阴级组与共阳级组的换流点相隔60°,所以每隔60°有一个元件换流。

同组内各晶闸管的触发脉冲相位差为120°,接在同一相的两个元件的触发脉冲相位差为180°,而相邻两脉冲的相位差是60°。

2 IP软核设计。

新型全数字三相SPWM信号产生芯片的设计与实现

第27卷 第1期2006年1月半 导 体 学 报CHIN ESE J OURNAL OF SEMICONDUCTORSVol.27 No.1J an.,20063陕西省教育厅归国人员研究基金资助项目(批准号:陕教外0177号) 通信作者.Email :dhz frank1@ 2005208203收到,2005209214定稿○2006中国电子学会新型全数字三相SPWM 信号产生芯片的设计与实现3高 勇 余宁梅 陈利杰 唐善强(西安理工大学电子工程系,西安 710048)摘要:针对电力电子领域的需要,自行研制了一种新型三相正弦脉宽调制信号产生芯片.该芯片采用了改进的直接数字频率合成算法、流水线结构与ROM 分时复用技术,保证了芯片的高性能和速度,节省了芯片面积.芯片系统时钟可达24M Hz ,输出信号的范围为DC 到4k Hz ,精度为65536级,控制功能齐全.采用0135μm COMS 工艺流片,测试结果显示芯片达到设计指标.关键词:数字频率合成;正弦脉宽调制;正弦波查找表;COMS EEACC :1210;1265A ;2570D 中图分类号:TN492 文献标识码:A 文章编号:025324177(2006)01201262061 引言正弦脉宽调制(sinusoidal p ulse widt h modula 2tion ,SPWM )是利用功率半导体器件的开关,把直流电压变成电压脉冲序列,控制电压脉冲的宽度和周期,以达到变压变频的目的,在电力电子领域有着广泛的应用.同类已有的芯片如H EF4752、SL E4520输出信号频率低最高为216k Hz ,控制精度低为模拟或256级控制,只有复位、输出禁止等简单功能,用法复杂需外接多个器件,不能适应电力电子高频化、高性能化的发展[1].若采用数字信号处理器(digital signal p rocessing ,DSP )、现场可编程逻辑阵列(field p rogrammable gate array ,FP GA )或复杂可编程逻辑器件(complex p rogrammable logi 2cal device ,CPLD )等方案产生SPWM 信号,无疑增加了设计的复杂性与成本.本文设计并实现了新型高性能SPWM 信号产生芯片.该芯片采用改进直接数字频率合成(DDS )算法,输出信号精度高,结构设计合理,控制功能齐全,用法简捷,为电力电子领域的交流电机变频调速、逆变电源、U PS 电源等系统提供了高性能的关键芯片.2 芯片主电路系统结构主电路的功能是用数字的方法生成三相正弦交流信号和三角波信号,通过它们的比较,产生三相六路的SPWM 脉冲.主电路的详细模块划分和各模块信号的连接关系如图1所示.主电路主要包括八个子模块:2n +1时钟分频、三角载波的生成、正弦波查找表、正弦波的生成、分相逻辑、乘法器、脉冲剔除和脉冲延迟.2.1 基于改进DDS 结构产生正弦波首先要设计产生频率范围能达到4k Hz 且精度为65536级(16位)控制的正弦波.采用的方法是DDS 技术.传统的DDS 由于是在频率固定的取样时钟控制下通过改变正弦波的采样点数来改变其频率,所以正弦波精度随频率的增大而减小.本设计提出的改进DDS 是通过改变正弦波数据的取样时钟频率来改变正弦波的频率,而每个周期正弦波的采样点数固定不变,解决了传统DDS 生成正弦波的精度随频率的增大而减小的问题.改进DDS 在本设计中的具体实现如下.系统时钟S YSCL K (system clock )由载波频率选择器CFS (carrier f requency selector )2n +1分频得到时钟驱动信号div (diver ),其频率为f div .累加器的容量为23位,每次累加值为16位的频率控制字FCW (f requency control word ).高七位用作低16位累加进位信号的计数器.每来一个div 脉冲,加法器将16位FCW 与16位累加寄存器输出数据相加,把相加的结果送到累加寄存器的输入端,在下一第1期何宝平等: 大规模集成电路浮栅ROM器件总剂量辐射效应图1 主电路结构图Fig.1 Main circuit architecture个时钟的作用下继续与频率控制字相加;累加器每次溢出产生一个溢出信号,其频率为f out =f div ×FCW216.选择累加器高七位mb sum (mo stbit s of sum )中的某一位,对溢出信号分频得到ROM 地址使能信号addr en (address enable ).每来一个addr en 信号产生一个同步地址发生器的使能信号syn addr en (synchronizatio n address enable ),分别输入到三相10位地址发生器,其中9位用来计数,1位作符号标志位.每来一个syn ad 2dr en 信号,各地址发生器进行一次加(减)1运算,当地址计数值为最小值0时,开始加计数,当地址计数值为最大值383时,开始减计数.在每次地址计数值为0时,12B IT 的符号标志位取反一次.在一、二象限,符号位记为1,在三、四象限,符号位记为0.地址发生器产生的计数值作为ROM 查找表地址,正弦ROM 查找表存储等相位取样的1/4周期正弦波的幅度量化值.ROM 表的尺寸随着地址位数或数据位数的增加呈指数增加,因此在满足信号性能的前提下,存储容量定为384×7位.根据实用要求ROM 内部存储了3种正弦波,由波形选择器WS(wave selector )选择.经过地址发生器的计数值从0到383的4次变化,得到一个周期的量化正弦波,再通过和符号标志位寄存器的合成,得到完整的正弦波.通过增加相位加减计数器,正弦波采样点存储器ROM 减少到传统结构的1/4,提高了资源利用率[2,3].正弦波频率为:f sin e =f div ×FCW 216×1384×4×127-m ,合适S YSCL K 输出频率即可达到4k Hz ,并且控制精度为65536级.DDS 生成正弦波时用到了23位累加器.寄存器传输级R TL (register t ransfer level )设计时为了提高计算速度,采用三级流水线结构来实现23位累加器,如图2所示.把一个时钟周期实现的电路逻辑分配到三个时钟周期完成.Pipe1,Pipe2,Pipe3是三个一位的寄存器,div 每来一个上升沿信号,它的状态就被锁到Pipe1,在下个系统时钟到来的时候把累加使能信号1accu en1(accumulate enable 1)传递给8位累加器(1),执行累加,同时把状态传递到Pipe2,把进位信号c1传递给8位累加器(2);在紧接着的时钟到来时,把累加使能信号2accu en2721半 导 体 学 报第27卷(accumulate enable 2)传递给8位累加器(2),执行累加,同时把状态传递给Pipe3,把进位信号c2传递给7位累加器;在紧接着的时钟到来时,把累加使能信号3accu en3(accumulate enable 3)传递给7位累加器,执行累加(加1).通过频率范围选择器FRS (frequency rang selector )来选择高七位中的某一位,分频得到需要的addren.图2 三级流水线结构Fig.2 Three 2stage pipeline architecture2.2 分相逻辑生成正弦波时三相都要从ROM 中取值,若用三个ROM 则芯片面积过大.为了提高资源利用率,ROM 采用分时复用.三相的地址同时产生,但从ROM 取值是分时的,取出数据后,分别送至乘法器与各自幅度AM P (amplit ude )相乘完成幅值控制.因此,只需要一个ROM 、一个乘法器即可得到幅值分别可控的三相正弦波.由于系统要求得到的三相SPWM 波形相位相差120°,可令三相正弦波起始地址相差120°.分相由一个6位的移位寄存器(Pipe1~Pipe6)控制完成.移位寄存器的时钟信号是S YSCL K ,触发信号是同步地址发生器的使能信号syn addr en (synchronization address enable ).当产生一个syn addr en 脉冲时,三个地址发生器在一个S Y 2SCL K 周期里产生三相地址.由这六个触发器控制,采用分时复用的方法查表读取正弦波的采样值,具体操作控制如表1所示.2.3 其他模块乘法器完成幅值控制每次只能输出一相的数据,因而将每次产生的数据利用寄存器先分别暂存.三角载波通过加减计数器产生.比较器对正弦波和三角波进行比较,得到SPWM 信号.脉冲剔除单元使脉冲宽度小于脉冲删除时间PD T (p ulse deletion time )的脉冲被删除掉,应用时可减少后级功率开关器件的动作次数.脉冲延迟单元设置脉冲延迟时间PD Y (p ulse delay time ),使得上下桥臂变化时不能同时为高,避免了后级功率器件同时导通而发生短路[4].表1 6位移位寄存器的控制Table 1 Function of six 2bit register有效位执行操作Pipe1有效选出红相地址Pipe2有效(1)选出红相符号(2)选出黄相地址(3)选出红相幅度控制字Pipe3有效(1)选出蓝相地址(2)选出黄相符号(3)选出黄相幅度控制字Pipe4有效(1)选出蓝相符号(2)选出蓝相幅度控制字Pipe5有效(无操作)Pipe6有效三相信号同时写入三相比较寄存器中3 芯片监控电路针对实用的要求,设计了功能齐全的监控电路.电路功能有:调制波频率信号ZPPR (zero p hase p ulse )输出与正弦波同频的方波,波形采样同步信号WSS (waveform sampling synchronization )ROM 每输出一个采样值WSS 取反一次,这两个信号可监视芯片工作是否正常.正/反向控制功能可改变输出正弦波的相序,正向时输出正弦波相序是红黄蓝,反向时是蓝黄红.输出禁止功能IN H (inhibit )可关断SPWM 输出,不影响内部的操作.软、硬复位可关断SPWM 输出,内部寄存器、计数器清零.故障处理报警功能可响应外部故障信号,越过微处理器MCU (microprogrammed cont rol unit )关断SPWM 输出,并向MCU 报警.看门狗功能可监视芯片与MCU 的联系状态,若失去联系关断SPWM 输出,并向MCU 报警.波形选择功能可选择ROM 内的821第1期高 勇等: 新型全数字三相SPWM 信号产生芯片的设计与实现三种正弦波之一输出.幅值控制功能可实现分别控制三相幅值.接口功能可自动适应IN TEL 和MO 2TOROL A 总线模式,使芯片与多种MCU 兼容,由内部寄存器接收MCU 写入的控制信息,得到生成SPWM 信号所需的参数.此外,芯片中集成了分频等模块使得用法简单,只需外接一个时钟源即可与MCU 配合工作.4 芯片实现和测试结果芯片功能仿真使用的软件是CADENCE 公司的NC Verilog.布局布线使用的软件是Synop sys 公司的Apollo ,通过布局规划、宏单元放置、电源规划、放置标准单元、时钟树综合、布线等流程得到了版图[5,6],如图3所示,核心面积只有175416μm ×174612μm.采用Charted 0135μm COMS 数字工艺流片.图3 芯片版图Fig.3 Chip layout芯片通过了实验室的详细测试,测试的主要设备有单片机A T89S8252、示波器TE KTRON IX TDS3034B 、逻辑分析仪TE KTRON IX TLA601、信号发生器Agilent 33220A .由单片机发控制信息到芯片,用示波器和逻辑分析仪观测输出波形.测试结果表明,芯片工作频率范围可达24M Hz ,芯片工作电压范围为217~515V.芯片以313V 电压供电时,功耗为42132mW.输出正弦波频率为319k Hz 时观测到的波形如图4所示.实测ZPPR 的频率为3190625k Hz ,误差为116%,符合要求.各信号的意义为红相上臂PU R (p ulse up arm of red )、红相下臂PDR (p ulse down arm of red )、黄相上臂PU Y (p ulse up arm of yellow )、黄相下臂PD Y (p ulse down arm of yellow )、蓝相上臂PUB (p ulse up arm of blue )、蓝相下臂PDB (p ulse down arm of blue ).当S YSCL K 为最高值24M Hz ,div 为12M Hz,图4 正弦波频率为319k Hz 时实测波形Fig.4 Testing result of sine waveform with f requen 2cy 319k Hz七选一选择器选最低位,FCW 为6666H 时,观测到的WSS 波形如图5所示.1/4周期内变化379次,与384次期望值相比,误差为113%,符合要求.WSS 每次反转需1168μs ,与期望值1164μs 相比,误差为214%,累加器的计算速度达到了设计要求,流水线结构的设计是成功的.图5 WSS 为1164μs 时的实测波形Fig.5 Testing result of WSS with 1164μs 脉冲延迟时间为1μs 时观测到的波形如图6所示,实测PU R 在PDR 为低后延迟了1μs 才为高,符合要求.图6 脉冲延迟时间为1μs 时实测波形Fig.6 Testing result of the delay time with 1μs 正转时各相上臂达到峰值(为1)的顺序由左至右为PU R ,PU Y ,PUB ,如图7所示,与正转时正弦波各相正半周达到峰值的顺序红黄蓝相同,符合要求.图7 正转实测波形Fig.7 Testing results of forward phase sequence反转时各相上臂达到峰值(为1)的顺序由左至右为PUB ,PU Y ,PU R ,如图8所示,与反转时正弦波各相正半周达到峰值的顺序蓝黄红相同,符合要求.图8 反转实测波形Fig.8 Testing results of reverse phase sequence最小脉宽为10μs 时观测的波形如图9,实测为10μs,符合要求.图9 最小脉宽为10μs 时实测波形Fig.9 Testing result of min plus width with 10μs 921半 导 体 学 报第27卷看门狗时间为20ms 时观测的波形如图10所示,三相正常输出20104ms 后被关断,ZPPR ,WSS 不受影响.误差为012%,符合要求.图10 看门狗时间为20ms 时实测波形Fig.10 T esting results of watch dog time with 20ms释放输出禁止位IN H 时观测的波形如图11所示,IN H 有效时三相输出全为低,ZPPR 、WSS 不受影响.IN H 释放后,所有的下桥臂都先输出一个载波周期的高电平,实测为160μs 与设定值166μs 接近,误差为3175%,符合要求.图11 释放输出禁止位IN H 时实测波形Fig.11 Testing results of release IN H总之,测试得到的数据和期望数据能很好地吻合,达到了设计要求.5 结论本文设计并实现了新型全数字三相SPWM 信号产生芯片.芯片采用改进DDS 算法,输出信号频率可达0~4k Hz ,精度可达65536级,超过同类功能芯片;芯片结构设计合理,采用ROM 分时复用、三级流水线结构使ROM 面积节省2/3,ROM 取值的速度可达1168μs ;芯片控制电路功能齐全,具有故障处理报警、看门狗、波形选择、三相幅值分别控制等功能,用法简单,只需外接一时钟源即可与MCU 配合工作.测试结果表明芯片达到了设计要求.该芯片可用于高性能的交流电机变频调速、逆变电源、U PS 电源等系统,使系统电路结构简单,实现了全数字控制.当修改运行参数时才需要MCU 干预,提高了MCU 的利用率.参考文献[1] Chen Guocheng.PWM variable voltage variable frequency andsoft switching power converter technology.1st edition.Bei 2jing :China Machine Press ,2001:50(in Chinese )[陈国呈.PWM 变频调速及软开关电力变换技术.第一版.北京:机械工业出版社,2001:50][2] Langlois J M P ,Al 2Khalili D.ROM size reduction wit h lowprocessing cost for direct digital frequency synt hesis.IEEE Pacific Rim Conference on Communications ,Computers and Signal Processing ,2001:287[3] Sodagar A M ,Roientan G.A novel architect ure for ROM 2lesssine 2output direct digital frequency synt hesizers by using t he 2nd 2order parabolic approximation.Proceedings of t he IEEE/EIA International Frequency Cont rol Symposium and Exhibi 2tion ,2000:284[4] Yao Suoxue ,Liu Chenchang.Closed 2loop SPWM control forgrid 2connected buck 2boost inverters.IEEE 35t h Annual Pow 2er Electronics Specialist s Conference ,2004,5:3366[5] Lin ment s on filling algorit hms and analyses forlayout density control.IEEE Transactions on Computer 2AidedDesign of Integrated Circuit s and Systems ,2002,21(10):9[6] Huang Lida ,Tang Xiaoping ,Xiang Hua ,et al.A polynomialtime 2optimal diode insertion/routing algorit hm for fixing an 2tenna problem.IEEE Transactions on Computer 2Aided Design of Integrated Circuit s and Systems ,2004,23(1):14131第1期高 勇等: 新型全数字三相SPWM信号产生芯片的设计与实现Design and Implementation of a Novel Chip for Full DigitalThree2Phase SPWM Signal G eneration3Gao Y ong,Yu Ningmei,Chen Lijie ,and Tang Shanqiang(Depart ment of Elect ronic Engi neeri ng,X i’an Uni versit y of Technolog y,X i’an 710048,Chi na)Abstract:A novel f ull digital three2phase sinusoidal pulse width modulation(SPWM)signal generation chip is presented for power electronics.A modified direct digital f requency synthesis(DDS),pipelined structure,and time2sharing ROM are adopted in the chip,for saving chip area and ensuring high performance and speed.The system clock is set at24M Hz,the output signals defined in65536equal steps cover a bandwidth f rom DC to4k Hz,and the multif unction is designed for control.The chip is fab2 ricated by using charted0135μm COMS technology.The test results show that the chip achieves the design specification.K ey w ords:DDS;SPWM;look2up table;COMSEEACC:1210;1265A;2570DArticle ID:025324177(2006)01201262063Project supported by t he Foundation for Returned Scholars of t he Education Depart ment of Shanxi Province(No.0177)Corresponding aut hor.Email:dhz frank1@ Received3August2005,revised manuscript received14September2005ν2006Chinese Institute of Electronics131。

关于SPWM的变频技术在变频器、UPS、EPS上的软硬件实现问题

关于SPWM的变频技术在变频器、UPS、EPS上的软硬件实现问题作者:zack在论坛上看了这么久,感觉大家的专业水平都非常高,很多高人使我非常佩服,成为我心中的偶像。

论坛上关于SPWM的话题也看见比较多了,但有些具体的问题,我想大家能根据各自的实践情况来谈谈看法。

关于SPWM的软硬件的具体实现问题,我想抛转引玉,一起来讲一讲。

先从最基本的开始吧。

大家都知道,所谓PWM,Pulse width modulation(脉冲宽度调制技术),通俗点讲就是一个阵列矩形波,(1)在频率不便的情况下改变矩形波的宽度可以改变输出的平均电压。

实现调压的目的,即VV,Variable V oltage;(2)在脉冲宽度不变的情况下,调节阵列矩形波的频率也以实现调节输出电压的目的,即VF,Variable Frequency 。

变频器就是VVVF用PWM波去直接控制主电路的功率器件(MOSFET、IGBT、、)可实现DC-AC转换。

但其输出的还是功率放大的一系列的矩形波,而不是正弦波,(通过傅立叶级数分解可知),其含有许多高次谐波成分,对于驱动电机,很不理想,容易造成旋转磁场畸变,运行不平稳。

因此,需要对这一系列的矩形波进行改进方法是将等宽的脉冲波变成宽度渐变的脉冲波,宽度的变化规律和正弦波的变化规律相符。

这种脉冲波成为SPWM,相比PWM大大减少了谐波成分,再驱动后级的功率器件带动电机可以得到满意的效果。

具体怎样得到SPWM波形呢,我想有3个方法可以做。

1,用模拟的方法,三角波发生电路、正弦波采样电路,然后通过比较器可以得到一组SPWM波型了。

2,采用MCU加专用SPWM电路实现,SPWM的芯片有SA4828,HEF4752, SLE4520等等。

MCU可以选择最常用的51构架的芯片ATMEL、PHLIPS、INTEL等等都可以,在抗干扰方面选择MOTOROLA比较好。

3,采用纯MCU软件算法实现。

通过计算载波和调制波的交点位置来输出,SPWM驱动波形。

基于DSP的三相SPWM变频电源的设计

基于DSP的三相SPWM变频电源的设计DSP(数字信号处理器)是一种专门用于实时数字信号处理的微处理器。

在电力电子领域中,DSP常用于三相SPWM(正弦波脉宽调制)变频电源的设计和控制。

三相SPWM变频电源是一种将直流电源转换为交流电源的装置,经过SPWM调制后可以有效地控制输出电压的频率和电压值。

设计一个基于DSP的三相SPWM变频电源需要考虑以下几个方面:1.系统拓扑设计:在设计之前,需要确定所采用的系统拓扑。

常用的变频电源拓扑包括单相桥式逆变器、三相桥式逆变器和电流源逆变器。

选择合适的拓扑结构将有利于系统的性能和控制。

2.DSP控制算法:DSP的控制算法是实现正弦波脉宽调制(SPWM)的核心部分。

SPWM是一种基于三角波的脉宽调制技术,通过控制三角波与正弦波的比较,可以得到合适的脉冲宽度,实现输出电压的调节。

常用的控制算法包括基于查表法和基于直接数字控制(DDC)的算法。

3.输出滤波设计:变频电源输出的电压是脉冲宽度调制信号,需要通过输出滤波电路将其转换为纯正弦波。

根据设计需求,可以选择合适的滤波电路结构,并选择合适的滤波器参数,以达到所需的输出电压波形和谐波含量。

4.保护回路设计:考虑到系统稳定性和操作安全性,需要设计合适的保护回路。

常见的保护回路包括过流保护、过温保护、过压保护等。

这些保护回路可以通过在DSP中实现相应的保护算法来实现。

5.DSP控制板设计:根据DSP的控制算法,设计相应的DSP控制板。

控制板包括DSP芯片、模数转换器(ADC)、数字模拟转换器(DAC)、输出滤波器、保护电路等。

在设计过程中需要考虑电路布局、信号隔离和噪声抑制等问题。

6.性能测试与优化:设计完成后,需要对系统进行性能测试,并根据测试结果进行系统优化。

主要测试项包括输出电压的纹波、变频电源的效率、稳定性和响应速度等。

总结:基于DSP的三相SPWM变频电源的设计需要考虑系统拓扑设计、DSP控制算法、输出滤波设计、保护回路设计、DSP控制板设计以及性能测试与优化。

三相FMSPWM软开关逆变器分析与设计

2007年 3 月电工技术学报Vol.22 No. 3 第22卷第3期TRANSACTIONS OF CHINA ELECTROTECHNICAL SOCIETY Mar. 2007三相FMSPWM软开关逆变器分析与设计朱忠尼1陈坚1王荣2(1. 华中科技大学电气与电子工程学院武汉 4300742. 空军雷达学院武汉 430019)摘要针对双极性FMSPWM逆变器只能用于单相变换器的问题,提出了一种三相FMSPWM 软开关逆变器拓扑结构,分析了三相FMSPWM实现软开关的原理,提出了最佳载波频率公式,对电路中主要元件参数进行了设计。

实验结果证明了该电路能实现三相逆变器开关管的软开关、改善输出波形质量。

关键词:软开关调频调宽逆变器中图分类号:TM461Analysis and Design of Three-Phase FMSPWM Soft-Switched InverterZhu Zhongni1 Chen Jian1 Wang Rong2(1. Huazhong University of Science and Technology Wuhan 430074 China2. Air Force Radar Academy Wuhan 430019 China)Abstract Because bipolar FMSPWM inverter can only be used in single-phase converter, this paper proposes a kind of circuit topology structure of three-phase inverter soft-switch and analyses the principle of the circuit, proposes the best carrier-wave frequency formulas and designs the main component parameter. The experimental results verify that the circuit mentioned above can realize the soft-switching, improve the quality of output wave.Keywords:Soft switching, modulating frequency and width, inverter1引言DC/AC正弦波逆变器是电力电子技术的最重要分支之一,也是应用最为广泛的一种电力电子装置。

三相SPWM逆变器仿真报告

电力电子建模仿真报告

一、仿真要求

设计一个三相SPWM逆变器,使得输出相电压100Hz,有效值220V,负载RL类型(R=50Ω,L=10mH)直流母线电压540V,观察输出电流波形,对电流电压进行谐波分析。

二、仿真模型

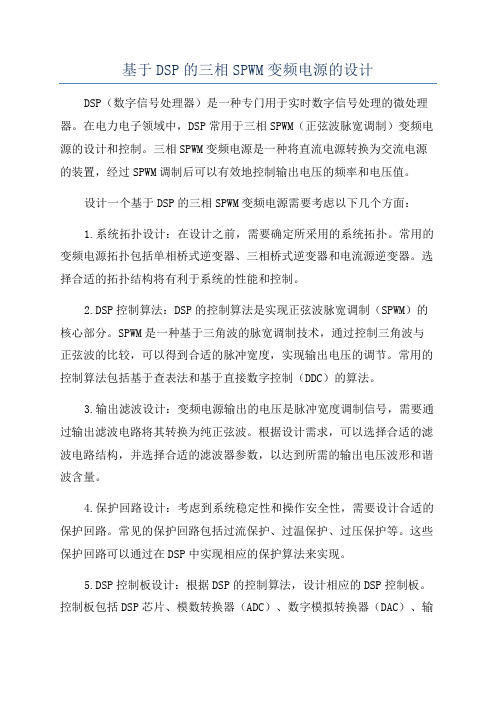

图1 SPWM三相逆变电路仿真模型

三、仿真分析

设置参数,即将调制波频率设为100Hz,载波频率设为基波的30倍(载波比N=30),即3000Hz,m=0.9,负载RL类型(R=50Ω,L=10mH),直流母线电压540V,在powergui 中设置为离散仿真模式,采样时间设为1e-006s,运行仿真模型。

双击powergui,选择FFT 分析。

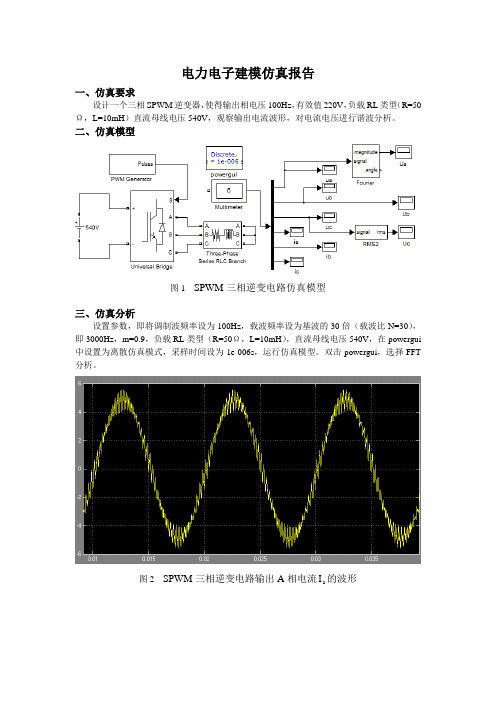

图2 SPWM三相逆变电路输出A相电流a I的波形

图3 SPWM三相逆变电路输出A相电流a I的FFT分析

U的波形图4 SPWM三相逆变电路输出A相电流a

U的FFT分析

图5 SPWM三相逆变电路输出A相电流a

由上面分析可知,电流谐波分布中最高的为28次谐波,最高频率为3000Hz时的THD=12.63%,输出电流近似为正弦波。

电压谐波分布中最高的为28次谐波,最高频率为3000Hz时的THD=79.22%。

四、仿真总结

通过适当的参数设置(如载波比N、调制度m等),运用SPWM控制技术,可以有效减小输出电压和输出电流的谐波分量,改善输出波形,可以很好的实现逆变电路的运行要求。

基于FPGA的三相SPWM控制器的设计

基于FPGA的三相SPWM控制器的设计黄玉健;甘国妹;黄永庆【摘要】研究者基于FPGA设计了一种三相SPWM控制器,该设计器以Altera公司的Cyclone III系列的EP3C25Q240C8芯片作为控制核心,结合直接数字频率合成技术(DDS),利用Verilog语言和LPM宏模块设计生成三相SPWM控制器.设计仿真结果以及用逻辑分析仪SignalTap II采样显示的结果表明,该三相SPWM控制器具有调制波频率、载波频率、调制度、载波比以及死区时间均可以灵活调节的优点,生成的三相SPWM波适应性强,可方便应用于逆变电源的变频调压以及电机变频调速等领域.【期刊名称】《玉林师范学院学报》【年(卷),期】2017(038)005【总页数】8页(P41-48)【关键词】三相SPWM控制器;FPGA;DDS【作者】黄玉健;甘国妹;黄永庆【作者单位】梧州学院图像处理与智能信息系统广西高校重点实验室,广西梧州543002;玉林师范学院电子与通信工程学院,广西玉林 537000;梧州学院图像处理与智能信息系统广西高校重点实验室,广西梧州 543002【正文语种】中文【中图分类】TN7411 引言PWM((Pulse Width Modulation)脉冲宽度调制技术是非常重要的电气控制技术,在高性能要求的电机变频调速、步进电机精细控制、变频调压电源、电力电子逆变控制等方面均有非常重要的应用[1]. 当进行脉冲宽度调制的时候,使系列脉冲的占空比按照正弦规则来排列,那么输出的信号经过D/A转换和滤波可以得到正弦波形的电压,就是正弦波脉冲宽度调制(Sinusoidal PWM),亦即SPWM[3]. 相比于其他方式的脉冲宽度调制,诸如空间矢量PWM、随机采样PWM、电流滞环PWM、自然采样PWM、等面积采样PWM或规则采样PWM 等,SPWM在电气控制技术等应用中,产生的谐波成分最小,所以应用也最广泛[1]. 在交流电机变频调速和逆变电源的变频调压等领域,SPWM控制技术已经得到非常广泛的应用.目前有多种能够产生SPWM脉宽调制波的方法,常用的方法中,一种是典型的传统的方法,即利用模拟电路对正弦调制波与三角载波进行比较来产生SPWM脉冲. 该种设计电路复杂,难以与数字系统连接,对于复杂要求很难满足;另一种是使用具有生成PWM波的专用芯片,如TI公司的DSP芯片TMS320F240和TMS320F2812等,该种方法也是数字化设计,但通常不够灵活,比如只能产生6路或12路的PWM信号[3]. 而基于FPGA的方法设计产生SPWM脉宽调制波,暨可以利用FPGA并发执行的速度优势来实现实时生成SPWM波形,也可以利用FPGA半定制电路的特点来实现快速灵活的硬件编程[2],使产生的SPWM波形具有调制波频率、载波频率、调制度、载波比以及死区时间均可以根据需要灵活调节的优点.本文的组织结构如下:第2节对SPWM产生技术原理、基于FPGA的数字直接频率合成(DDS)信号发生器产生调制波的正弦波技术原理进行理论分析;第3节应用FPGA内部丰富的半定制逻辑电路,根据技术原理设计出DDS三相正弦信号发生器、三角波发生器、幅度控制器、比较器以及死区控制电路;第四节对设计出来的三相SPWM控制器进行仿真和输出波形分析. 第5节对本文进行总结.2 基于FPGA的三相SPWM控制器设计原理2.1 SPWM波形产生技术原理图1 SPWM波生成原理图图1是SPWM波生成原理图,图1上方等腰三角波是载波,正弦波是调制波. 用数字方式生成SPWM波形原理是,先把载波等腰三角波和调制波正弦波均用数字方式产生,然后这两路数字波形信号通过一个数字比较器进行比较,如果三角波大于正弦波,则比较器输出0,反之,如果正弦波大于三角波,则比较器输出1.图1下方输出的脉冲波形就是产生的SPWM波形.从上述SPWM波形产生技术原理中知道,要产生三相SPWM波形,就必须要先生成三相调制波正弦波和载波三角波. 然后分别让三相正弦波和三角波通过比较器,按SPWM波生成原理输出相应的三个SPWM波形,就可以得到三相SPWM波形. 图2就是三相SPWM控制器电路模块图[1].图2中有5个部分构成,分别是DDS正弦波发生模块、三角波发生模块、幅度控制模块、比较器模块以及死区控制模块. 下面介绍这5个模块的作用.DDS正弦波发生模块主要是用来产生三相调制波正弦波,分别是0°正弦波、120°正弦波和240°正弦波.该模块也产生三角波发生模块所需的时钟信号tri_CLK,其实就是按DDS原理产生的一个方波信号. 该模块产生的另外一个时钟信号D_CLK是频率两倍于系统时钟信号CLK0频率的一个时钟信号,用来作为死区控制模块的系统时钟.图2 三相SPWM控制器电路模块图三角波发生模块就是用来产生载波三角波,在三角波的数据位已经确定的情况下,其频率由时钟信号tri_CLK的频率来决定,这可以通过DDS正弦波发生模块内部相对应的频率控制字来调节,也可以通过对应的频率控制字来调节三角波频率和三相正弦波频率的变化关系来决定是同步调制还是异步调制. 这里涉及一个参数是载波比,是指载波三角波频率ftri和调制波正弦波的频率fsin的比值,记为Kf,即理论上载波比越大输出精度也越高,也就是输出SPWM波形通过IGBT硬件电路后还原为正弦波的精度越高,但过大的载波比也要求IGBT的开关频率极高,导致开关管高功率损耗,甚至于无法满足过高的开关频率. 所以,载波比的选择要针对实际需要并结合具体的IGBT器件性能来选择. 通过改变DDS正弦波发生模块内部相对应的频率控制字,可以灵活调节正弦波和三角波的频率,进而调节载波比. 幅度控制模块的作用是用来调节正弦波和三角波的相对幅值度. 因为要灵活改变输出SPWM波形的调制度,就得通过改变正弦波和三角波的相对幅值大小来实现. 调制度,是指调制波正弦波的幅值Vsin和载波三角波幅值Vtri的比值[5],记为KA,即一般上,调制度KA的范围在0到1之间,实际的范围通常还要小. 如果KA>1,则称为过调制. 调制度反映了载波的幅度受低频调制信号控制的程度. 在应用SPWM设计的变频电源中,通过更改调制度KA可以方便的调节输出电压. 而在本设计中,可以通过改变正弦波的幅值系数AML_sin和三角波的幅值系数AML_tri 来实现调制度KA的灵活调节.比较器模块的作用,就是通过输入调整幅值之后的三相正弦波和三角波,通过比较器,按照SPWM生成原理来生成输出三相SPWM波形,分别为SPWM_A、SPWM_B和SPWM_C.死区控制模块是为了保护IGBT,防止上下桥臂同时导通而烧毁IGBT器件. 每一相SPMW波形控制一对IGBT器件,SPWM信号和SPWM相反状态的信号各控制一个,通过延迟上升沿变化信号的变化时间来防止这一对IGBT同时导通,设置的延迟时间就称为死区时间. 为了得到更精确的死区时间,死区控制模块的时钟D_CLK为系统时钟CLK0的两倍,通过锁相环技术得到. 本设计中,系统时钟CLK0为50MHz,D_CLK为100MHz.2.2 基于FPGA的DDS正弦波生成原理[6]图3 DDS结构原理图图3为基于FPGA的DDS正弦波生成结构原理图. 它的典型结构主要由相位累加器、相位调制器、正弦ROM查找表和DA转换器以及低通滤波器构成. 由于本设计的最终目的不是生成正弦波,生成数字化正弦波后还要结合数字化三角波最终生成SPWM波形,设计中整个过程都是数字化设计,所以图3中不需要DA转换器以及低通滤波器.在图3中,相位累加器是DDS波形信号发生器的核心,功能是完成信号的相位累加功能. 相位调制器的作用是对相位累加器的输出信号进行相位调制. 正弦波ROM 查找表的功能是完成一个周期离散正弦数据查表的转换,相位调制器的输出就是ROM的地址值,根据地址值找到相应的离散正弦数据,输出一个周期的离散正弦波数据就得到一个周期的数字化正弦波.根据DDS原理,输出正弦波的频率为[7]:式(3)中,fclk是系统基准时钟clk的频率,N是相位累加器的数据位宽度,B 是频率控制字,也称频率输入字. 在硬件已经确定,也就是fclk和N都已经设计定型的情况下,输出频率值就由当时输入的频率控制字B来确定. 而且频率控制字B的数据位宽度也是N.而对于DDS系统输出正弦波的频率分辨率Δf,即俗称输出频率最小步进值,就是频率控制字B步进一个最小间隔,亦即B=1对应的频率输出值. 由公式(3)得到:由公式(3)和公式(4)可知,只要基准频率fclk足够高频足够稳定,同时N足够大,利用DDS技术,可以实现输出任意频率和任意精度的正弦信号波形[4],而同在FPAG中利用锁相环技术,fclk实现高频高稳定基准时钟功能是很容易的,因而输出的正弦波的频率范围和精度要求都容易得到满足.3 基于FPGA的三相SPWM控制器设计3.1 DDS正弦波发生模块设计本设计依托的FPGA芯片是Altera公司的Cyclone III 系列的EP3C25Q240C8芯片. 根据图3 DDS正弦波结构原理图,可以得到本设计所需的基于FPAG的DDS三相正弦波发生模块设计电路图,如图4所示,系统时钟CLK为来自晶振的50MHz时钟信号.图4 DDS三相正弦波发生模块设计电路图图4中ADDER32是32位加法器,DFF32是32位寄存器,两者共同构成32位相位累加器. 正弦波ROM查找表分别由sin_rom01、sin_rom120和sin_rom240三个模块构成,它们的地址宽度和数据宽度均是10位,分别用来产生0°、120°和240°的正弦波. fangbo_rom是方波rom查找表,用来产生方波,地址宽度和数据宽度也都是10位. 由于产生的方波是作为产生载波三角波的驱动时钟信号,为了后续设置SPWM波的载波比和输出频率,在正弦波的频率字和方波频率字之间放置一个乘法器模块tra_sin_bilv. 乘法器的一个输入是正弦波频率字,另外一个输入是系数,输出的低32位作为方波的频率字. 由于三角波发生模块的地址宽度和数据宽度也都是10位,假设该系数为M,则M和载波比Kf的关系为:图4中PLL4M模块是锁相环模块,用来输出两个时钟信号,C0输出频率100MHz,用来作为死区控制模块的系统时钟. C1输出频率为10KHz,用来作为逻辑分析仪SignalTap II的时钟信号.图5是图4设计电路输出的三相正弦波以及方波在逻辑分析仪SignalTap II显示的波形,其中三相正弦波sin0、sin120和sin240分别是0°、120°和240°的正弦波,频率为50Hz. 方波TRA_CLK频率为1.024MHz.图5 DDS三相正弦波发生模块输出三相正弦信号和方波信号SignalTap II实时数据采样波形图根据式(3),图5中的正弦波频率可以通过改变正弦波输入频率字方式实现. 根据式(5),在确定载波比的情况下,通过改变乘法器输入系数M,可以改变输出方波的频率.3.2 三角波发生模块设计由于载波三角波是等腰三角形,所以可以利用地址计数器前半段的地址值作为等腰三角形的上升边,地址计数器后半段的地址值的取反值作为等腰三角形的下降边. 本设计的三角波发生器地址宽度和数据宽度也均是10位,因此三角波的计数器也是10位. 图6是三角波发生模块的设计电路图,其中counter10B模块是10位地址计数器,sanjiao模块是三角波发生模块.图6 三角波发生模块设计电路图3.3 死区控制模块设计幅度控制模块可以直接调用LPM中的宏模块乘法器,比较器模块也是可以直接调用LPM中的宏模块比较器. 这小节重点阐述死区控制模块设计.由2.1中死区控制模块的功能与原理可知,死区控制模块就是要实现对每一相SPWM波形控制的一对IGBT不能同时导通. 由于IGBT器件从导通到关断的过程中有时间延迟,因此防止同一个SPWM波形控制的一对上下桥臂IGBT同时导通的方法,是当一个IGBT从导通转变为关断时,对另外一个IGBT器件人为设置延长从关断到导通的过渡时间. 反映到SPWM波形,就是凡是上升沿的时刻都根据需要延迟其跳变时间,延迟的具体时间根据IGBT的性能指标来决定.图7 死区控制模块设计电路图图7是死区控制模块设计电路图. 其中SPWM_IN是输入的一相SPWM波,d_clk0是接DDS三相正弦波发生器模块输出的100MHz时钟信号. SIQU_CTRO是控制单个IGBT的死区控制电路. 输出out_H和out_L是经过死区控制之后的SPMW波形,分别控制一对IGBT的上下桥臂. 死区控制延迟时间可通过改变SIQU_CTRO电路里的参数来调节.4 基于FPGA的三相SPWM控制器顶层电路设计及输出波形分析4.1 基于FPGA的三相SPWM控制器顶层电路设计根据图2 三相SPWM控制器电路模块图和第3节各个子模块的设计电路图,可以得到基于FPGA的三相SPWM控制器顶层电路设计图,如图8所示.图8 基于FPGA的三相SPWM控制器顶层电路图图8中左边的clk0是系统总的输入系统时钟,频率为50MHz. DDS_ES是DDS三相正弦波发生模块,tra3是三角波发生模块. 四个AM_CTRO是乘法器,作为是幅度控制模块,M_tra[4..0]是三角波幅度控制系数,M_sin[4..0]是正弦波幅度控制系数. 由于产生的正弦波和三角波的数据位宽同样都是10位,根据式(2)可得调制度KA的具体表达式为:从式(6)可知,通过设置M_sin[4..0]和M_tra[4..0]可以灵活调节输出SPWM波形的调制度.CMP_10和CMP都是比较器模块,其输入是三角波和正弦波,输出是SPWM波. 其中CMP_10是10位比较器,CMP是14位比较器,后者是产生经过幅度控制的SPWM波形,前者是产生没有经过幅度控制的一路SPWM波形,是为了验证没有调制的SPWM波形和调制度小于1的SPWM波形的区别而设置的.4.2 输出波形分析图9是输出的三相SPWM波形SignalTap II实时数据采样波形图.图9 SPWM波形SignalTap II实时数据采样波形图图9中SPWM_A0是没有经过调制的A相SPWM波形,SPWM_A、SPWM_B和SPWM_C是调制度为90%的A、B、C三相SPWM波形. 其中产生SPWM_A和SPWM_A0两个波形的调制波是一样的,也就是用相同的0°正弦波作为调制波,不同的地方是产生SPWM_A的波形的调制度是90%,而产生SPWM_A0的波形的载波和调制波都没有经过幅度控制,调制度是100%. 在图9中可以明显看出两种波形SPWM_A0和SPWM_A的区别.图10 死区控制电路输入输出波形仿真图图8顶层电路图中SIQU_KONGZHI是死区控制模块,每个SIQU_KONGZHI模块输出上下桥臂一对IGBT器件所需的SPWM控制信号. 图10是死区控制电路输入输出波形仿真图,其中SPWM_A是A相SPWM波形,也是A相死区控制电路的输入SPWM波形,SPWM_AH和SPWM_AL分别是A相死区控制电路输出控制上桥臂和下桥臂的SPWM波形,SPWM_BH和SPWM_BL分别是B相死区控制电路输出控制上桥臂和下桥臂的SPWM波形.限于仿真图的大小,图10中没有给出C相死区控制电路输出控制上桥臂和下桥臂的SPWM波形. 从图10中可以看出SPWM_AH上升沿明显延迟于SPWM_AL的下降沿,也就是中间错开了一段死区时间. SPWM_BH上升沿也明显延迟于SPWM_AL的下降沿.图11 输出频率50Hz载波比20调制度90% 的三相SPWM波SignalTap II实时数据采样波形图图12 输出频率40Hz载波比15调制度85% 的三相SPWM波SignalTap II实时数据采样波形图图11和图12分别是输出频率50Hz载波比20调制度90% 和输出频率40Hz载波比15调制度85%的三相SPWM波SignalTap II实时数据采样波形图,均是经过死区控制输出的三相6路SPWM波形,满足了输出频率、调制度、载波比以及死区时间均可以灵活调节的设计目的.5 总结本文基于Altera公司的Cyclone III 系列的EP3C25Q240C8 FPGA芯片作为控制核心,结合直接数字频率合成技术(DDS),利用Verilog语言和LPM宏模块设计生成三相SPWM控制器. 设计仿真以及用逻辑分析仪SignalTap II采样显示的结果表明,该三相SPWM控制器具有调制波频率、载波频率、调制度、载波比以及死区时间均可以灵活调节的优点,达到了设计的目的. 该控制器可方便应用于逆变电源的变频调压以及电机变频调速等电气控制领域. ■【参考文献】[1]潘松,黄继业,潘明.EDA技术实用教程—Verilog HDL版(第5版)[M].北京:科学出版社,2013:354-356.[2]潘健,张小磊,张伯顺,王淑青.基于FPGA 的SPWM 变频调压电源研究[J].电源技术研究与设计,2015,39(2):386-388.[3]丁卫东,郭前岗,周西峰.一种基于FPGA的SPWM波的实时生成方法[J].计算机技术与发展,2011,22(2):211-214.[4]廖磊,何魏,周晓林.单片机与FPGA实训教程[M].北京:科学出版社,2016:310-317.[5]彭宏涛,基于FPGA的变频电源的设计与实现[D].昆明:云南大学.2012:7-9[6]黄继业,潘松.EDA技术及其创新实践(Verilog HDL版)[M].北京:电子工业出版社,2012:123-126.[7]黄玉健,黄永庆.基于FPAG的DDS多功能信号发生器的设计[J].梧州学院学报,2017,27(3):10-16.。

实验三 三相spwm变频原理实验

实验三三相正弦波脉宽度调制(SPWM)变频原理实验一、实验目的(1)掌握SPWM的调速基本原理和实现方法。

(2)熟悉与SPWM控制有关的信号波形。

二、实验所需挂件及附件三、实验内容(1)正弦波脉宽调制(SPWM)控制信号的观测;(2)正弦波脉宽调制(SPWM)变频调速实验三、实验方法(1)接通挂件电源,关闭电机开关,调制方式设定在SPWM方式下(将控制部分S、V、P的三个端子都悬空),然后开启电源开关。

(2)点动“增速”按键,将频率设定在0.5Hz,在SPWM部分观测三相正弦波信号(在测试点“2、3、4”),观测三角载波信号(在测试点“5”),三相SPWM调制信号(在测试点“6、7、8”);再点动“转向”按键,改变转动方向,观测上述各信号的相位关系变化。

(3)逐步升高频率,直至到达50Hz处,重复以上的步骤。

(4)将频率设置为0.5HZ~60HZ的范围内改变,在测试点“2、3、4”中观测正弦波信号的频率和幅值的关系。

(5)将DJ24电机与DJK13逆变输出部分连接,电机接成 形式,关闭电机开关,调制方式设定在SPWM方式下(将S、V、P的三端子都悬空)。

打开挂件电源开关,点动“增速”、“减速”和“转向”键,观测挂件工作是否正常,如果工作正常,将运行频率退到零,关闭挂件电源开关。

然后打开电机开关,接通挂件电源,增加频率、降低频率以及改变转向观测电机的转速变化。

四、实验报告(1)画出与SPWM调制有关信号波形,说明SPWM的基本原理。

(2)分析在0.5HZ~50Hz范围内正弦波信号的幅值与频率的关系。

(3)分析在50HZ~60Hz范围内正弦波信号的幅值与频率的关系。

(4)电机运行状况,并分析原因。

三相SPWM逆变器的仿真与研究

三相SPWM逆变器的仿真与研究[摘要]随着电力电子技术、计算机技术、自动控制技术的迅速发展,PWM技术得到了迅速发展,SPWM正弦脉宽调制法这项技术的特点是原理简单,通用性强,具有开关频率固定,控制和调节性能好,能消除谐波使输出电压只含有固定频率的高次谐波分量,设计简单等一系列优点,是一种比较好的波形改善法。

它的出现为中小型逆变器的发展起了重要的推动作用。

SPWM技术成为目前应用最为广泛的逆变用PWM技术。

因此,研究SPWM逆变器的基本工作原理和作用特性意义十分重大。

本论文介绍了三相电压型SPWM逆变器的工作原理,仿真电路及matlab仿真。

文中还给出了用此逆变器构成的三相交流电动机变频调速系统,并对仿真结果进行分析。

[关键词]正弦脉宽调制,逆变器,电机变频调速,matlab仿真Three-phase SPWM inverter simulation and researchAuthor: Huang Fei(Grade9, Class1, Major Automation , Electrical EngineeringDept, Shaanxi University of Technology , Hanzhong 723003,Shaanxi)Instructor: Zhang Peng Chao[Abstrac]With the power electronics technology, computer technology, the rapid development ofautomatic control technology, PWM technology is developing rapidly, SPWM sine pulse width modulation principle of this technology is characterized by simple, versatile, with a fixed switching frequency, control and regulation performance, eliminate harmonics thatcontain only a fixed output voltage of high frequency harmonic components, simple design and a series of advantages, is a good waveform improvement Act. It was a smallinverter played an important role. SPWM technology become the most widely usedinverter with PWM technology. Therefore, the study of SPWM inverter characteristics ofthe basic working principle and the role of great significance.This paper describes the three-phase voltage SPWM inverter works, simulate circuits and matlab simulation. The article also gives the composition with this three-phase ACinverter motor frequency control systems, and simulation results were analyzed.[Key words]Sinusoidal pulse width modulation, inverters, motor speed, matlab simulation目录引言经过大约30多年的发展,交流调速电气传动已经上升为电气调速传动的主流。

基于SPWM三相逆变器的仿真与设计-电路与系统专业论文

基于SPWM三相逆变器的仿真与设计-电路与系统专业论文本文介绍了基于SPWM(Sinusoidal ___)三相逆变器的仿真与设计。

论文首先阐述了研究的背景,包括三相逆变器在工业和电力系统中的应用。

然后确定了论文的目的,即通过仿真与设计探索SPWM三相逆变器的性能和特性。

根据此目的,采用了相应的方法,包括建立逆变器的数学模型、实施SPWM控制策略以及进行仿真和设计。

最后,通过实施所提出的仿真与设计方法,得出了相应的结果。

本文的研究对于理解和优化基于SPWM三相逆变器的电路与系统具有重要的意义。

关键词:SPWM,三相逆变器,仿真,设计,性能,特性该论文旨在研究基于SPWM(___)三相逆变器的仿真与设计。

本部分将介绍研究的背景和相关的文献综述,阐明研究的目的和意义。

该部分将介绍使用的研究方法和仿真工具,以及实验的设计和参数设置等。

该部分将介绍仿真和设计的过程,并展示结果和讨论。

在本研究中,我们采用了SPWM (Sinusoidal ___)技术,设计了一个三相逆变器电路。

我们使用了模拟仿真软件来验证电路的性能和波形输出。

首先,我们搭建了逆变器的电路图,并配置了相应的元件和参数。

然后,我们使用SPWM技术来产生需要的输出波形。

通过调整占空比和频率,我们可以调节输出电压的幅值和频率。

接下来,我们进行了仿真实验。

我们改变了载荷的变化情况,通过观察输出波形和性能参数,评估了逆变器的稳定性和效率。

根据我们的仿真实验,我们得出了以下设计结果:输出波形:通过SPWM技术,我们成功地实现了三相逆变器的正弦波输出。

输出波形的幅值和频率可以根据需要进行调节。

稳定性分析:我们对逆变器在不同载荷情况下的稳定性进行了分析。

结果表明,在正常工作范围内,逆变器可以稳定地输出所需电压,并且对载荷变化具有较好的适应性。

效率评估:我们还对逆变器的效率进行了评估。

根据我们的实验结果,逆变器在适当的设计参数下可以实现较高的效率。

根据我们的仿真和设计结果,我们可以得出以下结论:基于SPWM技术的三相逆变器具有良好的波形质量和稳定性,可以满足多种应用需求。

EDA软件在三相SPWM变频调制器电路设计中的应用

EDA软件在三相SPWM变频调制器电路设计中的应用1 SPWM变频调制器的模拟控制在变频调速技术中,作为两大难题之一的SPWM控制方式,虽然已经在先进的微机控制技术中得到很好的解决,但在调制中。

正弦波与三角波交点所对应在时间上的开关点的选择计算,是SPWM信号生成中的一个难点。

在采样法中,参数确定的实时计算与控制,因查表定时的相关参数需占用计算机太多内存和时间,而仅限于频率段较少的场合。

在最佳法中,为去掉指定阶次的谐波,使计算工作量很大。

而利用模拟、数字及模数混合集成器件等组成的三相对称SPWM调制器,可以既简单又方便的完成其主要功能。

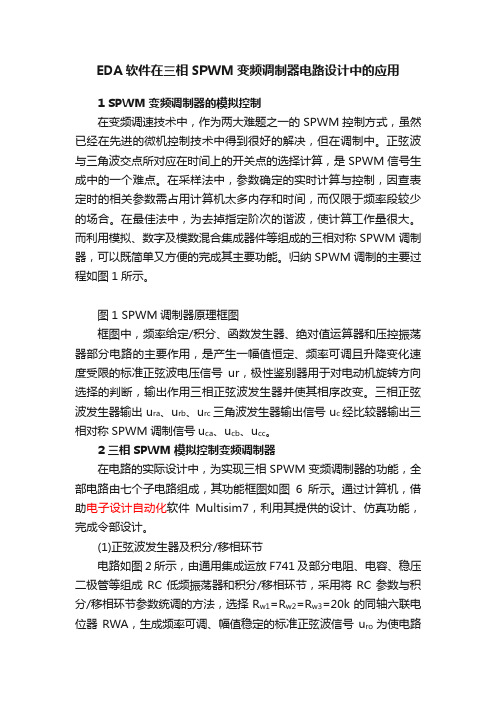

归纳SPWM调制的主要过程如图1所示。

图1 SPWM调制器原理框图框图中,频率给定/积分、函数发生器、绝对值运算器和压控振荡器部分电路的主要作用,是产生一幅值恒定、频率可调且升降变化速度受限的标准正弦波电压信号ur,极性鉴别器用于对电动机旋转方向选择的判断,输出作用三相正弦波发生器并使其相序改变。

三相正弦波发生器输出u ra、u rb、u rc三角波发生器输出信号u c经比较器输出三相对称SPWM调制信号u ca、u cb、u cc。

2 三相SPWM模拟控制变频调制器在电路的实际设计中,为实现三相SPWM变频调制器的功能,全部电路由七个子电路组成,其功能框图如图6所示。

通过计算机,借助电子设计自动化软件Multisim7,利用其提供的设计、仿真功能,完成令部设计。

(1)正弦波发生器及积分/移相环节电路如图2所示,由通用集成运放F741及部分电阻、电容、稳压二极管等组成RC低频振荡器和积分/移相环节,采用将RC参数与积分/移相环节参数统调的方法,选择R w1=R w2=R w3=20k的同轴六联电位器RWA,生成频率可调、幅值稳定的标准正弦波信号u ro为使电路能快速起振而输出波形又不失真,选择R2=100k≥2R1。

在负反馈回路上串入两并联的二极管,用于限幅。

综合限幅同路调节电阻R w3,对R1选用不同值时的输出波形进行计算机仿真,结果如图3所示,最终确定R1=9k。

学位论文-—基于波形发生器的三相spwm正弦脉宽调制电路设计

摘要本设计介绍一种以80C196KC单片机为控制核心的SPWM正弦脉宽调制电路。

80C196KC单片机能产生3相6路互补的PWM信号,结合该单片机运算速度快、集成度高、功能强大的特点,实现了PWM触发脉冲的精确控制。

该系统主要整流电路,滤波电路,逆变电路、驱动隔离电路、电源电路、保护电路以及单片机最小系统组成。

通过软件编程的方法,产生正弦脉冲宽度调制波形来控制绝缘栅双极晶体管的导通和关断,从而达到控制异步电动机转速的目的。

关键词:80C196KC;SPWM;单片机最小系统;逆变电路目录第1章绪论 (2)第2章SPWM变频调速系统基本原理 (3)2.1 SPWM变频调速系统基本原理 (3)2.2 常见SPWM信号产生方法 (4)第3章硬件设计 (5)3.1 系统硬件设计总方案的确定 (5)3.2 带有波形发生器的微处理器芯片的选择 (6)3.3 主电路的设计 (7)3.3.1 三相电压型桥式逆变电路 (7)3.3.2 SPWM主电路的设计 (8)3.4 隔离和驱动电路 (9)3.4.1 抗干扰电路 (9)3.4.2 光耦隔离驱动电路 (9)3.5 电源稳压电路 (10)3.6 过流过压保护电路 (12)3.7 系统总的硬件电路图 (13)第4章软件的设计 (14)4.1 系统软件设计流程图 (14)4.2 SPWM波的产生 (15)4.3 调速信号检测 (16)第5章课程设计总结 (18)参考文献 (19)第1章绪论二十世纪末以来,电力电子技术及大规模集成电路有了飞速的发展,在此技术背景下SPWM电路构成的变频调速系统以其结构简单、运行可靠、节能效果显著、性价比高等突出优点而得到广泛应用。

为了提高整个系统的控制效果,高性能SPWM脉冲形成技术一直是人们不断探索的课题。

而模拟电路和数字电路等硬件电路来产生SPWM波形是一种切实可行的方法,但是这种方法控制电路复杂、抗干扰能力差、实时调节比较困难。

随着集成电路技术的飞速发展,特别是单片机功能的日益强大和成熟,使得以前需要昂贵的专用SPWM芯片产生SPWM,现在用单片机产生SPWM已成为可能。

EDA设计三相交流电路的分析

三相交流电路的分析绪论EDA技术:20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

Multisim工具:Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。

Multisim提炼了SPICE仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。

用EDA软件Multisim仿真三相电路特性

用EDA软件Multisim仿真三相电路特性

郑步生

【期刊名称】《机械制造与自动化》

【年(卷),期】2003(000)001

【摘要】本文通过几个实例来介绍如何用EDA(Electronics Design Automation)软件Multisim进行三相电路特性仿真实验的方法.

【总页数】3页(P46-48)

【作者】郑步生

【作者单位】南京航空航天大学EDA中心,江苏,南京,210016

【正文语种】中文

【中图分类】TM721.2

【相关文献】

1.基于Multisim的三相电路特性仿真实验 [J], 代素梅;胡明明;张爱平

2.基于alpha-beta平面合成曲线特性的对称三相电路谐波分析 [J], 汤琳;冯宇;靳绍平;刘见;张春强;周翠娟

3.正弦交流电路中LC元件特性的Multisim仿真分析 [J], 祁国权

4.RC电路正弦稳态特性的Multisim仿真分析 [J], 腾香

5.基于EDA软件Multisim的三相电路分析和仿真 [J], 韩士杰

因版权原因,仅展示原文概要,查看原文内容请购买。

SPWM三相变频调速电路的谐波分析

・02・No 12 Vol 120过 SPWM 三相变频调速电路的谐波分析摘 要 :在理论分析和电路仿真实验数据的基础上 ,总结出 SPWM 三相变频器谐波的分布特点 ,为变频 器输出滤波器设计提供了理论依据 ,并通过电路仿真实验予以验证 。

关键词 :变频器 ;正弦脉宽调制 ;谐波分析 ;滤波器交流电动机变频调速以其高效节能 ,调速性能好 ,易实现数字化控制等显著优点 ,在现代电力拖动系统中已得到广泛应用 。

由于系统能量变换的主要形式为 AC —DC —AC ( 交 —直 —交) 变换 。

而实现 DC —AC 环节变换的变频器 ,以脉宽调制 ( PWM) 技术为主流 。

因 PWM 技术所固有的脉冲性质 ,使输 出电压中谐波含量高 ,由此引起的负面效应 :使电机过热 、 压导致绝缘提前老化甚至击穿 ,产生机械振 动和噪声以及电磁干扰现象等 。

特别是在中压 、高压 、大容量变频调速系统中尤其严重 。

为消除其影 响 ,最简便有效的措施就是在变频器输出端装设低通滤波器 。

本文对目前应用最多的基于 PWM 下的 正弦脉宽调制 ( SPWM) 变频电路进行谐波分析 ,为变频器输出滤波器的设计提供理论依据 。

1 SPWM 三相变频器的电路结构及调制特性SPWM 三相变频调速电路主回路拓扑结构如图 1 (a) 所示,功率开关 P —MOSFET 管 T1 T6 组成三 相桥式逆变电路 ,其控制端 G1 G6 受 SPWM 波控制 ; 变频器输入直流 电 压 为 VD ( 由 三 相 整 流 装 置 提供) ,输出端经 RL C 滤波器与交流电动机相连接 。

控制电路采用 SPWM 调制方式 ,如图 1 ( b) 所示 。

利 用三角载波 u c 和三相正弦调制信号 u r 进行比较 ,在交点处产生驱动信号 V G1V G6 ,即 SPWM 波 。

当 变频器三相桥臂功率开关 T1 T6 在驱动信号控制下 ,工作于适时 、适式的通断状态时 ,输入直流电压被 转换成等幅而脉冲宽度按正弦函数关系变化的三相脉冲序列电压输出 ,其相电压为双极性脉冲 ,线电压 为单极性脉冲 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

同 值时 的输 出波 形 进 行 计 算 机 仿 真 ,结

果 如 图 3所 示 ,最 终确 定 R。9 = k。 在 积 分/ 相 器 的 基 础 上 .增 加 由 移

R 组 成 的 负 反 馈 可 调 电 阻 ,构 成 比例 积 分 环 节 .用 于 在 改 变 R 参 数 进 行 变 C 频 时 ,抑 制 输 出 波 形 的 畸 变 。 使 其 迅 速 、稳 定 的 形 成 正 交 输 出 。 通 过 仿 真 ,

调 、幅 值 稳 定 的 标 准 正 弦 波 信 号 u。为 使 电 路 能 快 速 起 振 而 输 出 波 形 又 不 失 真 ,选 择 R = 0 k . 在 负 反 馈 回路 210 ≥2 。

上 串 人 两并 联 的 二极 管 ,用 于 限幅 。综 合 限 幅 回路 调 节 电阻 R , 对 R。 用 不 选

T 作 量 很 大 。 而 利 用 模 拟 、数 字 及 模 数 混 合集 成 器 件 等 组

成 的 j 相 对称 S WM 调 制 器 ,可 以既 简 单 又 方 便 的 完 成 其 P

主要 功 能 、归纳 S WM 调 制 的 主要 过 程 如 图 1 示 。 P 所

电 容 、稳 压 二 极 管 等 组 成 R 低 频 振 荡 器 和 积 分 / 相 环 C 移 节 .采 用将 R C参 数 与 积 分/ 相 环 节 参 数 统 调 的 方 法 ,选 移

择 R l尺w R 2 k的 同 轴 六 联 电 位 器 尺 ,生 成 频 率 可 : 2 = 0 =

框 图 中 , 频 率 给 定 / 分 、函 数 发 生 器 、绝 对 值 运 算 积 器 和 压 控 振 荡 器 部 分 电路 的 主 要 作 用 ,是 产 生 一 幅 值 恒

定 、频 率 可调 且升 降变 化 速 度受 限 的 标 准 正 弦 波 电压 信 号 “ 极 性 鉴 别 器 用 于 对 电 动 机 旋 转 方 向选 择 的 判 断 ,输 出

应 用

E A软件在三相 SWM变频调制器电路设计中的应用 D P

戴 冠洲

( 国投 新 集 能 源 股份 有 限公 司新 集 三 矿 , 安徽 淮 南 220 ) 3 10

Is 7 hbad ,采 用 模 拟 、数 字 及 模 数 混 合 集 成 器 组 成 的 i相 对 称 S WM 调 制 器 的设 计 、 t i &U ior7 im P

中 图分 类 号 :T 7 1 N 6

l S WM 变 频 调 制 器 的模 拟控 制 P

在 变 频 凋 速 技 术 中 ,作 为 两 大难 题 之 一 的 S WM 控 制 P

方式 .虽 然 已 经 在 先 进 的 微 机 控 制 技 术 中 得 到 很 好 的 解 决 ,但 在 调 制 中 ,正 弦 波 与 角 波 交 点 所 对应 在 时 间 上 的

开关 点 的 选择 计算 .是 S WM 信 号 生 成 中 的一 个 难 点 。 在 P

采 样 法 巾 .参 数 确 定 的 实 时 汁算 与 控 制 . 因查 表 定 时 的 相 关 参 数 需 占用 计 算 机 太 多 内 存 和 时 间 ,而 仅 限 于 频 率 段 较

少的 场 合 。在 最 佳 法 中 ,为 去 掉 指 定 阶次 的谐 波 ,使 计 算

加 法 器 的 放 大 倍 数 , 得 到 i 相 对 称 正

弦 交 流 电 压 波 形 , 为 S WM 调 制 提 供 P 三相基准 上弦信 号 。 E 4为 j 相 正 弦

波 高频 起 振 及 变频 调 谐 的 过程 。

( )三 角 波发 生 器 电 路 3

} 同 相 滞 【 较 器 和 单 时 间 常 数 } l l 口 ]比

有 源 积 分 构 成 三 角 波 发 生 器 ,输 出 载 波 电压 信 号 其频 率 和幅 值 由取样

作 用 乏相 正 弦波 发 生 器 并 使 其 相 序 改 变 。 三 相 正 弦 波 发 生 器 输 出 u 、u M 与 三 角 波 发 生器 输 出信 号 u 经 。 P

2三相 S WM 模 拟 控 制 变频 调 制器 P

在 电 路 的 实 际 设 计 中 ,为 实 现 三 相 S WM 变 频 调 制 器 P 的 功 能 . 全 部 电 路 由 七 个 子 电 路 组 成 ,其 功 能框 图 如 图 6 所 示 。 通 过 计 算 机 ,借 助 电子 设 计 自动 化 软 件 Mu i m , hs 7 i 利 用 其 提 供 的设 计 、仿 真 功 能 ,完成 全 部 设 计 。 ( )正 弦 波发 生 器 及 积 分/ 相 环 节 … 1 移 电 路 如 图 2所 示 .由通 用 集 成 运 放 F 4 7 1及 部 分 电阻 、

调 的三 相 对 称 正 弦 交 流 信号 的产 生 方 法 。 在 频 率 的 选择 与 显 示 、启 动/ 运

对 词 制 信 号 的 要 求 . 为 变频 器 在 低 端 用 户 的 推 广 使用 创造 了条 件 。 关t 词 : 相 S WM;模 拟 渊 制 器 ; 设 计 P 文献 标 识 码 :A 文 章 编 号 :10 — 4 2 (0 1 1 0 9 — 4 0 9 9 9 2 1)0 —0 7 0

调 出最 佳 数 值 。

( )三 相 对 称 正 弦波 发 生 器 电路 2 l S WM 凋 制 器 原 理框 图 P 以标 准 正 弦 波 电 压 u 为 参 考 相 量 ,

收 稿 日期 :2 1— 7 2 000—6

技 术

s i m7软 件 r 提 供 的 四 综 示 波 器 , 对 j { 1 相 波 形进 行 分 析 ,调 整 R 阻 值及 比例