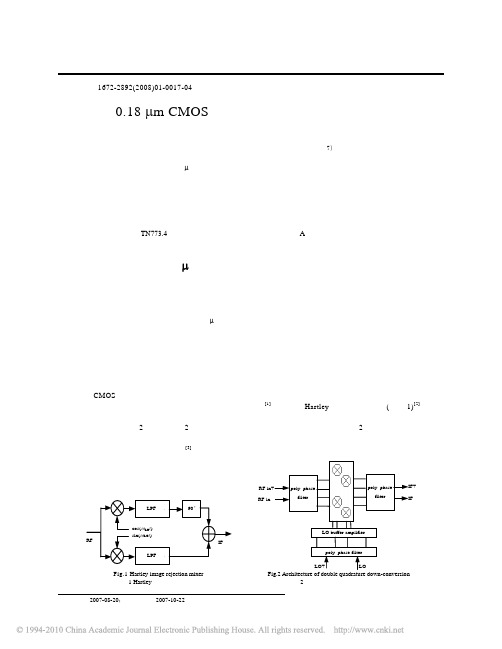

A CMOS 5GHz Image-Reject Receiver Front-End Architecture

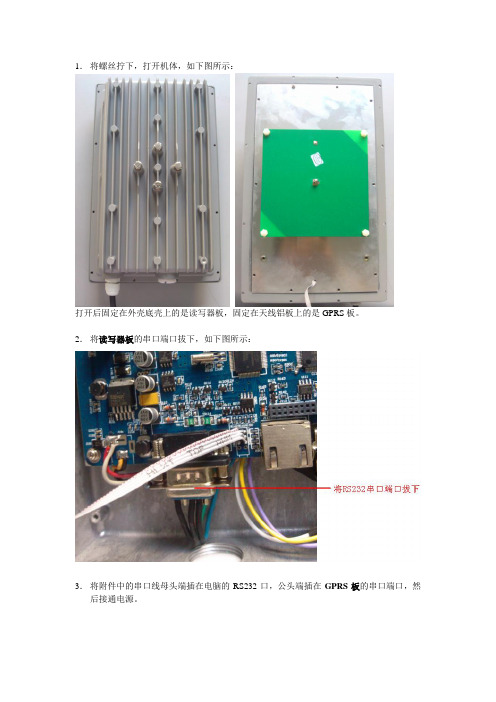

0_18_mCMOS宽带镜像抑制混频器的设计

RF

3.0~3.4

50

LO

3.225~3.625

50

IF

0.175~0.275

300

C1=860 C2=1 136

C1=994 C2=1 136 C1=1 930 C2=2 360 C3=3 130

RR11 CC11

RR2 1

c

CC22

CC11

CC22

CC11

CC22

CC11

CC22

Fig.3 Schematic of RF poly-phase filter 图 3 RF 多相滤波器原理图

Fig.6 Gain of the buffer amplifier 图 6 缓冲放大器的增益

2 宽带镜像抑制混频器的设计

2.1 核心混频器单元的设计

在有源 Gilbert 双平衡的设计中,最常用的就是 Gilbert 双平衡结构[6-7]。该设计中的混频器结构如图 7。 该结构具有较低的本振功率、较高的变频增益、高的 LO-IF 和 RF-IF 的端口隔离度的优点。混频器中,变 频电压增益为[8-9]:

(2)

式中: un 为电子迁移率; Cox 为单位面积的栅氧化层电容;W/L为宽长比; Vgs 为栅源间电压; Vth 为管子的阈值

电压; Id 为偏置电流。 采用 TSMC 0.18 µm CMOS 管工艺,在 ADS2003 中利用谐波仿真得到的结果如表 2。

RL

RL

VCC

M3 M4 Vbias_LOp

performance

Gilbert cell

this work

gain/dB noise figure/dB Image rejection/dB

P-1/dBm RF-IF isolation/dB IF-LO isolation/dB LO-RF isolation/dB

broadcast-probe reply disable

broadcast-probe reply disablebroadcast-probe reply disable是一种网络设置的功能,它可以禁用网络广播探测的回复。

广播探测是广播一条消息,然后等待网络上所有的设备回复,以确定网络上的设备数量和类型。

这可以帮助管理员识别网络中的设备并进行故障排查。

然而,在某些情况下,禁用广播探测的回复可能是有用的。

一种常见的情况是在网络中存在大量的设备,这样会导致广播探测的回复产生大量的网络流量。

在某些情况下,网络流量可能会造成网络拥塞,并影响正常的网络通信。

此时,禁用广播探测的回复可以有效减少网络流量,提高网络的性能和稳定性。

另一种情况是在网络中存在安全隐患的情况下,禁用广播探测的回复可以增加网络的安全性。

广播探测的回复可以泄露网络上存在的设备,包括类型、版本等信息,这可能会被黑客用来进行网络攻击和入侵。

通过禁用广播探测的回复,可以减少黑客获取有关网络设备的信息的机会,从而提高网络的安全性。

为了禁用广播探测的回复,可以按照以下步骤进行操作:1. 登录到网络设备的管理界面。

这通常需要管理员账户和密码。

2. 寻找关于广播探测的配置选项。

这在不同的设备上可能有所不同,可以参考设备的用户手册或询问设备制造商的技术支持。

3. 在广播探测的配置选项中,找到相关的设置项。

可能会有一个名为"broadcast-probe reply"的选项。

4. 将该选项的值设置为"disable"。

有些设备可能使用其他关键字或选项来实现相同的功能,可以根据设备的文档或技术支持找到正确的设置。

5. 保存更改并重新启动网络设备。

在重新启动后,网络设备将禁止回复广播探测。

需要注意的是,禁用广播探测的回复可能会影响一些网络的功能和管理任务。

例如,一些网络管理工具可能依赖广播探测来识别设备并进行管理操作。

在禁用广播探测的回复之前,应该对网络进行细致的分析和评估,以确保禁用这个功能不会对网络的正常运行造成不利影响。

GSM900DCS1800系统 ”题库

“GSM900/DCS1800系统”题库一. 选择题1、切换由____C____ 启动。

A MSB BTSC BSCD MSC2、以下____D____ 存储于HLR中。

A TMSIB 鉴权三人组C LAID 用户业务信息3.以下___B_____不用鉴权。

A 位置更新B 切换流程C 手机主叫D 手机被叫4.DCS 1800系统的ARFCN总数为(C)。

A 124B 376C 374D 3755、*下列____B ___条件下,BSC无法控制BTS 。

A BTS_TEL FLTB BTS_O&M FLTC CLLK FOSD RA FOS6、SBL____B______与OMC_R和G2 BSC之间的X.25 link 有关。

A DTC 5B CPR 4C ATR 5D CPR 17、BSS的告警级别中,最严重的级别是 _C_。

A DMAB MIC VPMAD PMA8、 G3 BTS信令静态复用情况下一根Abis线最多连__C____个TRE。

A 8B 10C 12D 149、以下( C )不可执行跳频操作。

A. SDCCHB. SACCHC. BCCHD. TCH10. 参数INTFBD1…INTFBD5 把基站在空闲信道上收到的上行干扰情况分为5个等级, 其中反映干扰最严重的是(D)A Interference Band 1B Interference Band 2C Interference Band 4D Interference Band 511.ALCATEL BTS设备接地电阻要求小于(B)A.3欧姆 B.5欧姆C.10欧姆 D.15欧姆12.ALCATEL BTS设备2M传输线距离一般为(B)A.20MB.25MC.30MD.50M13.在天线安装过程中,我们要求二个扇区天线夹角应(B)A.小于90°B.大于90°C.等于120°D.都可以14.在馈线布放过程中,应注意(C)A.7/8馈线不能大于75米 B.接地不能少于3点C.馈线不能有扭曲或破损 D.馈线只能采用7/8”15.G3 BTS电压适应范围是(D)A.-48~-60VB.-48~-72VC.-39~-54VD.-39~-72V16.小区选择C1算法跟以下那个因素有关?( C )A)Rxlev_minB)MS_Txpwr_MaxC)Rxlev_Access_MinD)BS_Txpwr_Max17.由于阻挡物而产生的类似阴影效果的无线信号衰落称为:CA)多径衰落B)快衰落C)慢衰落D)路径衰落18.如果一个网络运营商分别有15 MHz的上、下行频宽,那么他可以获得多少个GSM 频点 (减去一个保护频点)? DA)600B)599C)75D)7419. 1W=____C__dBmA)10B)20C)30D)3320.为避免因过多跨越LAC的小区重选而造成的SDCCH的阻塞,我们将与该小区有切换关系且与之LAC不同的相邻小区的( B )参数提高?A)T3212B)Cell_Reselect_HysteresisC)Cell_Reselect_offsetD)Rxlev_Access_Min21. CONFIG 4的G2 BSC 需接__B___块GS-1。

NuMicro N9H30系列开发板用户手册说明书

NuMicro®FamilyArm® ARM926EJ-S BasedNuMaker-HMI-N9H30User ManualEvaluation Board for NuMicro® N9H30 SeriesNUMAKER-HMI-N9H30 USER MANUALThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.Nuvoton is providing this document only for reference purposes of NuMicro microcontroller andmicroprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1OVERVIEW (5)1.1Features (7)1.1.1NuMaker-N9H30 Main Board Features (7)1.1.2NuDesign-TFT-LCD7 Extension Board Features (7)1.2Supporting Resources (8)2NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION (9)2.1NuMaker-N9H30 Board - Front View (9)2.2NuMaker-N9H30 Board - Rear View (14)2.3NuDesign-TFT-LCD7 - Front View (20)2.4NuDesign-TFT-LCD7 - Rear View (21)2.5NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB Placement (22)3NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS (24)3.1NuMaker-N9H30 - GPIO List Circuit (24)3.2NuMaker-N9H30 - System Block Circuit (25)3.3NuMaker-N9H30 - Power Circuit (26)3.4NuMaker-N9H30 - N9H30F61IEC Circuit (27)3.5NuMaker-N9H30 - Setting, ICE, RS-232_0, Key Circuit (28)NUMAKER-HMI-N9H30 USER MANUAL3.6NuMaker-N9H30 - Memory Circuit (29)3.7NuMaker-N9H30 - I2S, I2C_0, RS-485_6 Circuit (30)3.8NuMaker-N9H30 - RS-232_2 Circuit (31)3.9NuMaker-N9H30 - LCD Circuit (32)3.10NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 Circuit (33)3.11NuMaker-N9H30 - RMII_0_PF Circuit (34)3.12NuMaker-N9H30 - RMII_1_PE Circuit (35)3.13NuMaker-N9H30 - USB Circuit (36)3.14NuDesign-TFT-LCD7 - TFT-LCD7 Circuit (37)4REVISION HISTORY (38)List of FiguresFigure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation Board (5)Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board (6)Figure 2-1 Front View of NuMaker-N9H30 Board (9)Figure 2-2 Rear View of NuMaker-N9H30 Board (14)Figure 2-3 Front View of NuDesign-TFT-LCD7 Board (20)Figure 2-4 Rear View of NuDesign-TFT-LCD7 Board (21)Figure 2-5 Front View of NuMaker-N9H30 PCB Placement (22)Figure 2-6 Rear View of NuMaker-N9H30 PCB Placement (22)Figure 2-7 Front View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 3-1 GPIO List Circuit (24)Figure 3-2 System Block Circuit (25)Figure 3-3 Power Circuit (26)Figure 3-4 N9H30F61IEC Circuit (27)Figure 3-5 Setting, ICE, RS-232_0, Key Circuit (28)Figure 3-6 Memory Circuit (29)Figure 3-7 I2S, I2C_0, RS-486_6 Circuit (30)Figure 3-8 RS-232_2 Circuit (31)Figure 3-9 LCD Circuit (32)NUMAKER-HMI-N9H30 USER MANUAL Figure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit (33)Figure 3-11 RMII_0_PF Circuit (34)Figure 3-12 RMII_1_PE Circuit (35)Figure 3-13 USB Circuit (36)Figure 3-14 TFT-LCD7 Circuit (37)List of TablesTable 2-1 LCD Panel Combination Connector (CON8) Pin Function (11)Table 2-2 Three Sets of Indication LED Functions (12)Table 2-3 Six Sets of User SW, Key Matrix Functions (12)Table 2-4 CMOS Sensor Connector (CON10) Function (13)Table 2-5 JTAG ICE Interface (J2) Function (14)Table 2-6 Expand Port (CON7) Function (16)Table 2-7 UART0 (J3) Function (16)Table 2-8 UART2 (J6) Function (16)Table 2-9 RS-485_6 (SW6~8) Function (17)Table 2-10 Power on Setting (SW4) Function (17)Table 2-11 Power on Setting (S2) Function (17)Table 2-12 Power on Setting (S3) Function (17)Table 2-13 Power on Setting (S4) Function (17)Table 2-14 Power on Setting (S5) Function (17)Table 2-15 Power on Setting (S7/S6) Function (18)Table 2-16 Power on Setting (S9/S8) Function (18)Table 2-17 CMOS Sensor Connector (CON9) Function (19)Table 2-18 CAN_0 (SW9~10) Function (19)NUMAKER-HMI-N9H30 USER MANUAL1 OVERVIEWThe NuMaker-HMI-N9H30 is an evaluation board for GUI application development. The NuMaker-HMI-N9H30 consists of two parts: a NuMaker-N9H30 main board and a NuDesign-TFT-LCD7 extensionboard. The NuMaker-HMI-N9H30 is designed for project evaluation, prototype development andvalidation with HMI (Human Machine Interface) function.The NuMaker-HMI-N9H30 integrates touchscreen display, voice input/output, rich serial port serviceand I/O interface, providing multiple external storage methods.The NuDesign-TFT-LCD7 can be plugged into the main board via the DIN_32x2 extension connector.The NuDesign-TFT-LCD7 includes one 7” LCD which the resolution is 800x480 with RGB-24bits andembedded the 4-wires resistive type touch panel.Figure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation BoardNUMAKER-HMI-N9H30 USER MANUAL Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board1.1 Features1.1.1 NuMaker-N9H30 Main Board Features●N9H30F61IEC chip: LQFP216 pin MCP package with DDR (64 MB)●SPI Flash using W25Q256JVEQ (32 MB) booting with quad mode or storage memory●NAND Flash using W29N01HVSINA (128 MB) booting or storage memory●One Micro-SD/TF card slot served either as a SD memory card for data storage or SDIO(Wi-Fi) device●Two sets of COM ports:–One DB9 RS-232 port with UART_0 used 75C3232E transceiver chip can be servedfor function debug and system development.–One DB9 RS-232 port with UART_2 used 75C3232E transceiver chip for userapplication●22 GPIO expansion ports, including seven sets of UART functions●JTAG interface provided for software development●Microphone input and Earphone/Speaker output with 24-bit stereo audio codec(NAU88C22) for I2S interfaces●Six sets of user-configurable push button keys●Three sets of LEDs for status indication●Provides SN65HVD230 transceiver chip for CAN bus communication●Provides MAX3485 transceiver chip for RS-485 device connection●One buzzer device for program applicationNUMAKER-HMI-N9H30 USER MANUAL●Two sets of RJ45 ports with Ethernet 10/100 Mbps MAC used IP101GR PHY chip●USB_0 that can be used as Device/HOST and USB_1 that can be used as HOSTsupports pen drives, keyboards, mouse and printers●Provides over-voltage and over current protection used APL3211A chip●Retain RTC battery socket for CR2032 type and ADC0 detect battery voltage●System power could be supplied by DC-5V adaptor or USB VBUS1.1.2 NuDesign-TFT-LCD7 Extension Board Features●7” resolution 800x480 4-wire resistive touch panel for 24-bits RGB888 interface●DIN_32x2 extension connector1.2 Supporting ResourcesFor sample codes and introduction about NuMaker-N9H30, please refer to N9H30 BSP:https:///products/gui-solution/gui-platform/numaker-hmi-n9h30/?group=Software&tab=2Visit NuForum for further discussion about the NuMaker-HMI-N9H30:/viewforum.php?f=31 NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUAL2 NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION2.1 NuMaker-N9H30 Board - Front View Combination Connector (CON8)6 set User SWs (K1~6)3set Indication LEDs (LED1~3)Power Supply Switch (SW_POWER1)Audio Codec(U10)Microphone(M1)NAND Flash(U9)RS-232 Transceiver(U6, U12)RS-485 Transceiver(U11)CAN Transceiver (U13)Figure 2-1 Front View of NuMaker-N9H30 BoardFigure 2-1 shows the main components and connectors from the front side of NuMaker-N9H30 board. The following lists components and connectors from the front view:NuMaker-N9H30 board and NuDesign-TFT-LCD7 board combination connector (CON8). This panel connector supports 4-/5-wire resistive touch or capacitance touch panel for 24-bits RGB888 interface.Connector GPIO pin of N9H30 FunctionCON8.1 - Power 3.3VCON8.2 - Power 3.3VCON8.3 GPD7 LCD_CSCON8.4 GPH3 LCD_BLENCON8.5 GPG9 LCD_DENCON8.7 GPG7 LCD_HSYNCCON8.8 GPG6 LCD_CLKCON8.9 GPD15 LCD_D23(R7)CON8.10 GPD14 LCD_D22(R6)CON8.11 GPD13 LCD_D21(R5)CON8.12 GPD12 LCD_D20(R4)CON8.13 GPD11 LCD_D19(R3)CON8.14 GPD10 LCD_D18(R2)CON8.15 GPD9 LCD_D17(R1)CON8.16 GPD8 LCD_D16(R0)CON8.17 GPA15 LCD_D15(G7)CON8.18 GPA14 LCD_D14(G6)CON8.19 GPA13 LCD_D13(G5)CON8.20 GPA12 LCD_D12(G4)CON8.21 GPA11 LCD_D11(G3)CON8.22 GPA10 LCD_D10(G2)CON8.23 GPA9 LCD_D9(G1) NUMAKER-HMI-N9H30 USER MANUALCON8.24 GPA8 LCD_D8(G0)CON8.25 GPA7 LCD_D7(B7)CON8.26 GPA6 LCD_D6(B6)CON8.27 GPA5 LCD_D5(B5)CON8.28 GPA4 LCD_D4(B4)CON8.29 GPA3 LCD_D3(B3)CON8.30 GPA2 LCD_D2(B2)CON8.31 GPA1 LCD_D1(B1)CON8.32 GPA0 LCD_D0(B0)CON8.33 - -CON8.34 - -CON8.35 - -CON8.36 - -CON8.37 GPB2 LCD_PWMCON8.39 - VSSCON8.40 - VSSCON8.41 ADC7 XPCON8.42 ADC3 VsenCON8.43 ADC6 XMCON8.44 ADC4 YMCON8.45 - -CON8.46 ADC5 YPCON8.47 - VSSCON8.48 - VSSCON8.49 GPG0 I2C0_CCON8.50 GPG1 I2C0_DCON8.51 GPG5 TOUCH_INTCON8.52 - -CON8.53 - -CON8.54 - -CON8.55 - -NUMAKER-HMI-N9H30 USER MANUAL CON8.56 - -CON8.57 - -CON8.58 - -CON8.59 - VSSCON8.60 - VSSCON8.61 - -CON8.62 - -CON8.63 - Power 5VCON8.64 - Power 5VTable 2-1 LCD Panel Combination Connector (CON8) Pin Function●Power supply switch (SW_POWER1): System will be powered on if the SW_POWER1button is pressed●Three sets of indication LEDs:LED Color DescriptionsLED1 Red The system power will beterminated and LED1 lightingwhen the input voltage exceeds5.7V or the current exceeds 2A.LED2 Green Power normal state.LED3 Green Controlled by GPH2 pin Table 2-2 Three Sets of Indication LED Functions●Six sets of user SW, Key Matrix for user definitionKey GPIO pin of N9H30 FunctionK1 GPF10 Row0 GPB4 Col0K2 GPF10 Row0 GPB5 Col1K3 GPE15 Row1 GPB4 Col0K4 GPE15 Row1 GPB5 Col1K5 GPE14 Row2 GPB4 Col0K6GPE14 Row2GPB5 Col1 Table 2-3 Six Sets of User SW, Key Matrix Functions●NAND Flash (128 MB) with Winbond W29N01HVS1NA (U9)●Microphone (M1): Through Nuvoton NAU88C22 chip sound input●Audio CODEC chip (U10): Nuvoton NAU88C22 chip connected to N9H30 using I2Sinterface–SW6/SW7/SW8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5and J5)–SW6/SW7/SW8: 2-3 short for I2S function and connected to NAU88C22 (U10).●CMOS Sensor connector (CON10, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11)–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON10)Connector GPIO pin of N9H30 FunctionCON10.1 - VSSCON10.2 - VSSNUMAKER-HMI-N9H30 USER MANUALCON10.3 - Power 3.3VCON10.4 - Power 3.3VCON10.5 - -CON10.6 - -CON10.7 GPI4 S_PCLKCON10.8 GPI3 S_CLKCON10.9 GPI8 S_D0CON10.10 GPI9 S_D1CON10.11 GPI10 S_D2CON10.12 GPI11 S_D3CON10.13 GPI12 S_D4CON10.14 GPI13 S_D5CON10.15 GPI14 S_D6CON10.16 GPI15 S_D7CON10.17 GPI6 S_VSYNCCON10.18 GPI5 S_HSYNCCON10.19 GPI0 S_PWDNNUMAKER-HMI-N9H30 USER MANUAL CON10.20 GPI7 S_nRSTCON10.21 GPG2 I2C1_CCON10.22 GPG3 I2C1_DCON10.23 - VSSCON10.24 - VSSTable 2-4 CMOS Sensor Connector (CON10) FunctionNUMAKER-HMI-N9H30 USER MANUAL2.2NuMaker-N9H30 Board - Rear View5V In (CON1)RS-232 DB9 (CON2,CON6)Expand Port (CON7)Speaker Output (J4)Earphone Output (CON4)Buzzer (BZ1)System ResetSW (SW5)SPI Flash (U7,U8)JTAG ICE (J2)Power ProtectionIC (U1)N9H30F61IEC (U5)Micro SD Slot (CON3)RJ45 (CON12, CON13)USB1 HOST (CON15)USB0 Device/Host (CON14)CAN_0 Terminal (CON11)CMOS Sensor Connector (CON9)Power On Setting(SW4, S2~S9)RS-485_6 Terminal (CON5)RTC Battery(BT1)RMII PHY (U14,U16)Figure 2-2 Rear View of NuMaker-N9H30 BoardFigure 2-2 shows the main components and connectors from the rear side of NuMaker-N9H30 board. The following lists components and connectors from the rear view:● +5V In (CON1): Power adaptor 5V input ●JTAG ICE interface (J2) ConnectorGPIO pin of N9H30Function J2.1 - Power 3.3V J2.2 GPJ4 nTRST J2.3 GPJ2 TDI J2.4 GPJ1 TMS J2.5 GPJ0 TCK J2.6 - VSS J2.7 GPJ3 TD0 J2.8-RESETTable 2-5 JTAG ICE Interface (J2) Function●SPI Flash (32 MB) with Winbond W25Q256JVEQ (U7); only one (U7 or U8) SPI Flashcan be used●System Reset (SW5): System will be reset if the SW5 button is pressed●Buzzer (BZ1): Control by GPB3 pin of N9H30●Speaker output (J4): Through the NAU88C22 chip sound output●Earphone output (CON4): Through the NAU88C22 chip sound output●Expand port for user use (CON7):Connector GPIO pin of N9H30 FunctionCON7.1 - Power 3.3VCON7.2 - Power 3.3VCON7.3 GPE12 UART3_TXDCON7.4 GPH4 UART1_TXDCON7.5 GPE13 UART3_RXDCON7.6 GPH5 UART1_RXDCON7.7 GPB0 UART5_TXDCON7.8 GPH6 UART1_RTSCON7.9 GPB1 UART5_RXDCON7.10 GPH7 UART1_CTSCON7.11 GPI1 UART7_TXDNUMAKER-HMI-N9H30 USER MANUAL CON7.12 GPH8 UART4_TXDCON7.13 GPI2 UART7_RXDCON7.14 GPH9 UART4_RXDCON7.15 - -CON7.16 GPH10 UART4_RTSCON7.17 - -CON7.18 GPH11 UART4_CTSCON7.19 - VSSCON7.20 - VSSCON7.21 GPB12 UART10_TXDCON7.22 GPH12 UART8_TXDCON7.23 GPB13 UART10_RXDCON7.24 GPH13 UART8_RXDCON7.25 GPB14 UART10_RTSCON7.26 GPH14 UART8_RTSCON7.27 GPB15 UART10_CTSCON7.28 GPH15 UART8_CTSCON7.29 - Power 5VCON7.30 - Power 5VTable 2-6 Expand Port (CON7) Function●UART0 selection (CON2, J3):–RS-232_0 function and connected to DB9 female (CON2) for debug message output.–GPE0/GPE1 connected to 2P terminal (J3).Connector GPIO pin of N9H30 Function J3.1 GPE1 UART0_RXDJ3.2 GPE0 UART0_TXDTable 2-7 UART0 (J3) Function●UART2 selection (CON6, J6):–RS-232_2 function and connected to DB9 female (CON6) for debug message output –GPF11~14 connected to 4P terminal (J6)Connector GPIO pin of N9H30 Function J6.1 GPF11 UART2_TXDJ6.2 GPF12 UART2_RXDJ6.3 GPF13 UART2_RTSJ6.4 GPF14 UART2_CTSTable 2-8 UART2 (J6) Function●RS-485_6 selection (CON5, J5, SW6~8):–SW6~8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5 and J5) –SW6~8: 2-3 short for I2S function and connected to NAU88C22 (U10)Connector GPIO pin of N9H30 FunctionSW6:1-2 shortGPG11 RS-485_6_DISW6:2-3 short I2S_DOSW7:1-2 shortGPG12 RS-485_6_ROSW7:2-3 short I2S_DISW8:1-2 shortGPG13 RS-485_6_ENBSW8:2-3 short I2S_BCLKNUMAKER-HMI-N9H30 USER MANUALTable 2-9 RS-485_6 (SW6~8) FunctionPower on setting (SW4, S2~9).SW State FunctionSW4.2/SW4.1 ON/ON Boot from USB SW4.2/SW4.1 ON/OFF Boot from eMMC SW4.2/SW4.1 OFF/ON Boot from NAND Flash SW4.2/SW4.1 OFF/OFF Boot from SPI Flash Table 2-10 Power on Setting (SW4) FunctionSW State FunctionS2 Short System clock from 12MHzcrystalS2 Open System clock from UPLL output Table 2-11 Power on Setting (S2) FunctionSW State FunctionS3 Short Watchdog Timer OFFS3 Open Watchdog Timer ON Table 2-12 Power on Setting (S3) FunctionSW State FunctionS4 Short GPJ[4:0] used as GPIO pinS4Open GPJ[4:0] used as JTAG ICEinterfaceTable 2-13 Power on Setting (S4) FunctionSW State FunctionS5 Short UART0 debug message ONS5 Open UART0 debug message OFFTable 2-14 Power on Setting (S5) FunctionSW State FunctionS7/S6 Short/Short NAND Flash page size 2KBS7/S6 Short/Open NAND Flash page size 4KBS7/S6 Open/Short NAND Flash page size 8KBNUMAKER-HMI-N9H30 USER MANUALS7/S6 Open/Open IgnoreTable 2-15 Power on Setting (S7/S6) FunctionSW State FunctionS9/S8 Short/Short NAND Flash ECC type BCH T12S9/S8 Short/Open NAND Flash ECC type BCH T15S9/S8 Open/Short NAND Flash ECC type BCH T24S9/S8 Open/Open IgnoreTable 2-16 Power on Setting (S9/S8) FunctionCMOS Sensor connector (CON9, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11).–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON9).Connector GPIO pin of N9H30 FunctionCON9.1 - VSSCON9.2 - VSSCON9.3 - Power 3.3VCON9.4 - Power 3.3V NUMAKER-HMI-N9H30 USER MANUALCON9.5 - -CON9.6 - -CON9.7 GPI4 S_PCLKCON9.8 GPI3 S_CLKCON9.9 GPI8 S_D0CON9.10 GPI9 S_D1CON9.11 GPI10 S_D2CON9.12 GPI11 S_D3CON9.13 GPI12 S_D4CON9.14 GPI13 S_D5CON9.15 GPI14 S_D6CON9.16 GPI15 S_D7CON9.17 GPI6 S_VSYNCCON9.18 GPI5 S_HSYNCCON9.19 GPI0 S_PWDNCON9.20 GPI7 S_nRSTCON9.21 GPG2 I2C1_CCON9.22 GPG3 I2C1_DCON9.23 - VSSCON9.24 - VSSTable 2-17 CMOS Sensor Connector (CON9) Function●CAN_0 Selection (CON11, SW9~10):–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11) –SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensor connector (CON9, CON10)SW GPIO pin of N9H30 FunctionSW9:1-2 shortGPI3 CAN_0_RXDSW9:2-3 short S_CLKSW10:1-2 shortGPI4 CAN_0_TXDSW10:2-3 short S_PCLKTable 2-18 CAN_0 (SW9~10) Function●USB0 Device/HOST Micro-AB connector (CON14), where CON14 pin4 ID=1 is Device,ID=0 is HOST●USB1 for USB HOST with Type-A connector (CON15)●RJ45_0 connector with LED indicator (CON12), RMII PHY with IP101GR (U14)●RJ45_1 connector with LED indicator (CON13), RMII PHY with IP101GR (U16)●Micro-SD/TF card slot (CON3)●SOC CPU: Nuvoton N9H30F61IEC (U5)●Battery power for RTC 3.3V powered (BT1, J1), can detect voltage by ADC0●RTC power has 3 sources:–Share with 3.3V I/O power–Battery socket for CR2032 (BT1)–External connector (J1)●Board version 2.1NUMAKER-HMI-N9H30 USER MANUAL2.3 NuDesign-TFT-LCD7 -Front ViewFigure 2-3 Front View of NuDesign-TFT-LCD7 BoardFigure 2-3 shows the main components and connectors from the Front side of NuDesign-TFT-LCD7board.7” resolution 800x480 4-W resistive touch panel for 24-bits RGB888 interface2.4 NuDesign-TFT-LCD7 -Rear ViewFigure 2-4 Rear View of NuDesign-TFT-LCD7 BoardFigure 2-4 shows the main components and connectors from the rear side of NuDesign-TFT-LCD7board.NuMaker-N9H30 and NuDesign-TFT-LCD7 combination connector (CON1).NUMAKER-HMI-N9H30 USER MANUAL 2.5 NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB PlacementFigure 2-5 Front View of NuMaker-N9H30 PCB PlacementFigure 2-6 Rear View of NuMaker-N9H30 PCB PlacementNUMAKER-HMI-N9H30 USER MANUALFigure 2-7 Front View of NuDesign-TFT-LCD7 PCB PlacementFigure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement3 NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS3.1 NuMaker-N9H30 - GPIO List CircuitFigure 3-1 shows the N9H30F61IEC GPIO list circuit.Figure 3-1 GPIO List Circuit NUMAKER-HMI-N9H30 USER MANUAL3.2 NuMaker-N9H30 - System Block CircuitFigure 3-2 shows the System Block Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-2 System Block Circuit3.3 NuMaker-N9H30 - Power CircuitFigure 3-3 shows the Power Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-3 Power Circuit3.4 NuMaker-N9H30 - N9H30F61IEC CircuitFigure 3-4 shows the N9H30F61IEC Circuit.Figure 3-4 N9H30F61IEC CircuitNUMAKER-HMI-N9H30 USER MANUAL3.5 NuMaker-N9H30 - Setting, ICE, RS-232_0, Key CircuitFigure 3-5 shows the Setting, ICE, RS-232_0, Key Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-5 Setting, ICE, RS-232_0, Key Circuit3.6 NuMaker-N9H30 - Memory CircuitFigure 3-6 shows the Memory Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-6 Memory Circuit3.7 NuMaker-N9H30 - I2S, I2C_0, RS-485_6 CircuitFigure 3-7 shows the I2S, I2C_0, RS-486_6 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-7 I2S, I2C_0, RS-486_6 Circuit3.8 NuMaker-N9H30 - RS-232_2 CircuitFigure 3-8 shows the RS-232_2 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-8 RS-232_2 Circuit3.9 NuMaker-N9H30 - LCD CircuitFigure 3-9 shows the LCD Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-9 LCD Circuit3.10 NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 CircuitFigure 3-10 shows the CMOS Sensor,I2C_1, CAN_0 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit3.11 NuMaker-N9H30 - RMII_0_PF CircuitFigure 3-11 shows the RMII_0_RF Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-11 RMII_0_PF Circuit3.12 NuMaker-N9H30 - RMII_1_PE CircuitFigure 3-12 shows the RMII_1_PE Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-12 RMII_1_PE Circuit3.13 NuMaker-N9H30 - USB CircuitFigure 3-13 shows the USB Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-13 USB Circuit3.14 NuDesign-TFT-LCD7 - TFT-LCD7 CircuitFigure 3-14 shows the TFT-LCD7 Circuit.Figure 3-14 TFT-LCD7 CircuitNUMAKER-HMI-N9H30 USER MANUAL4 REVISION HISTORYDate Revision Description2022.03.24 1.00 Initial version NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUALImportant NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, anymalfunction or failure of which may cause loss of human life, bodily injury or severe propertydamage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomicenergy control instruments, airplane or spaceship instruments, the control or operation ofdynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all typesof safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claimsto Nuvoton as a result of customer’s Insecure Usage, custome r shall indemnify the damagesand liabilities thus incurred by Nuvoton.。

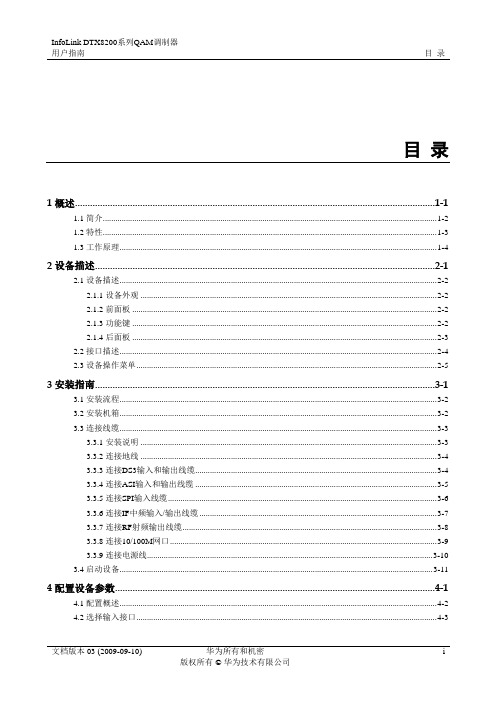

8200系列QAM调制器-用户手册课件

InfoLink DTX8200系列QAM调制器用户指南目录目录1 概述................................................................................................................................................ 1-11.1 简介............................................................................................................................................................... 1-21.2 特性............................................................................................................................................................... 1-31.3 工作原理....................................................................................................................................................... 1-42 设备描述........................................................................................................................................ 2-12.1 设备描述....................................................................................................................................................... 2-22.1.1 设备外观 ............................................................................................................................................. 2-22.1.2 前面板 ................................................................................................................................................. 2-22.1.3 功能键 ................................................................................................................................................. 2-22.1.4 后面板 ................................................................................................................................................. 2-32.2 接口描述....................................................................................................................................................... 2-42.3 设备操作菜单............................................................................................................................................... 2-53 安装指南........................................................................................................................................ 3-13.1 安装流程....................................................................................................................................................... 3-23.2 安装机箱....................................................................................................................................................... 3-23.3 连接线缆....................................................................................................................................................... 3-33.3.1 安装说明 ............................................................................................................................................. 3-33.3.2 连接地线 ............................................................................................................................................. 3-43.3.3 连接DS3输入和输出线缆................................................................................................................. 3-43.3.4 连接ASI输入和输出线缆 ................................................................................................................. 3-53.3.5 连接SPI输入线缆.............................................................................................................................. 3-63.3.6 连接IF中频输入/输出线缆 ............................................................................................................... 3-73.3.7 连接RF射频输出线缆....................................................................................................................... 3-83.3.8 连接10/100M网口 ............................................................................................................................. 3-93.3.9 连接电源线........................................................................................................................................ 3-103.4 启动设备..................................................................................................................................................... 3-114 配置设备参数................................................................................................................................ 4-14.1 配置概述....................................................................................................................................................... 4-24.2 选择输入接口............................................................................................................................................... 4-3目录InfoLink DTX8200系列QAM调制器用户指南4.3 设置DS3模式.............................................................................................................................................. 4-44.3.1 选择模式 ............................................................................................................................................. 4-44.3.2 设置主/备模式号 ................................................................................................................................ 4-54.3.3 搜索模式号.......................................................................................................................................... 4-6 4.4 输出设置....................................................................................................................................................... 4-64.4.1 设置输出频率...................................................................................................................................... 4-64.4.2 设置输出频道...................................................................................................................................... 4-74.4.3 设置QAM调制数 .............................................................................................................................. 4-84.4.4 设置符号率.......................................................................................................................................... 4-94.4.5 设置输出码率...................................................................................................................................... 4-94.4.6 设置射频控制.................................................................................................................................... 4-104.4.7 设置输出增益.................................................................................................................................... 4-114.4.8 设置频谱翻转.................................................................................................................................... 4-11 4.5 码流处理..................................................................................................................................................... 4-124.5.1 设置PID过滤 ................................................................................................................................... 4-124.5.2 设置PID映射 ................................................................................................................................... 4-134.5.3 设置PID插入 ................................................................................................................................... 4-155 配置网络参数................................................................................................................................ 5-15.1 组网简介....................................................................................................................................................... 5-25.2 设置网管IP地址 ......................................................................................................................................... 5-25.3 设置以太网口参数....................................................................................................................................... 5-35.3.1 设置IP地址 ........................................................................................................................................ 5-35.3.2 设置子网掩码...................................................................................................................................... 5-35.3.3 设置网关地址...................................................................................................................................... 5-45.3.4 设置网口模式...................................................................................................................................... 5-55.4 配置TS网口参数 ........................................................................................................................................ 5-55.4.1 打开网口 ............................................................................................................................................. 5-55.4.2 设置IP地址 ........................................................................................................................................ 5-65.4.3 设置子网掩码...................................................................................................................................... 5-65.4.4 设置网管PID ...................................................................................................................................... 5-75.5 配置透明传输网口参数............................................................................................................................... 5-75.5.1 透明传输示例...................................................................................................................................... 5-75.5.2 打开网口 ............................................................................................................................................. 5-85.5.3 设置IP地址 ........................................................................................................................................ 5-85.5.4 设置子网掩码...................................................................................................................................... 5-95.5.5 设置网关地址...................................................................................................................................... 5-95.5.6 设置网元IP ......................................................................................................................................... 5-95.5.7 设置源地址........................................................................................................................................ 5-105.5.8 设置目标地址.................................................................................................................................... 5-11InfoLink DTX8200系列QAM调制器用户指南目录6 典型业务配置................................................................................................................................ 6-16.1 配置复用....................................................................................................................................................... 6-26.2 配置调制....................................................................................................................................................... 6-57 升级指南........................................................................................................................................ 7-17.1 升级准备....................................................................................................................................................... 7-27.2 升级执行....................................................................................................................................................... 7-27.2.1 通过网管系统升级软件...................................................................................................................... 7-37.2.2 通过FTP服务器升级......................................................................................................................... 7-48 例行维护........................................................................................................................................ 8-18.1 设备例行维护项目....................................................................................................................................... 8-28.2 日维护项目................................................................................................................................................... 8-28.3 月维护项目................................................................................................................................................... 8-48.4 年维护项目................................................................................................................................................... 8-68.5 维护表........................................................................................................................................................... 8-78.5.1 日维护表 ............................................................................................................................................. 8-78.5.2 月维护表 ............................................................................................................................................. 8-88.5.3 年维护表 ............................................................................................................................................. 8-99 告警处理........................................................................................................................................ 9-19.1 告警信息处理............................................................................................................................................... 9-29.1.1 查看告警信息...................................................................................................................................... 9-29.1.2 保存告警信息...................................................................................................................................... 9-29.1.3 删除告警信息...................................................................................................................................... 9-29.2 常见告警及处理建议................................................................................................................................... 9-39.2.1 码流类告警.......................................................................................................................................... 9-39.2.2 升级类告警.......................................................................................................................................... 9-49.2.3 其它 ..................................................................................................................................................... 9-410 故障处理.................................................................................................................................... 10-110.1 输入输出故障处理................................................................................................................................... 10-210.1.1 射频信号无输出.............................................................................................................................. 10-210.1.2 射频信号输出偏低.......................................................................................................................... 10-210.1.3 设备输入码流中断.......................................................................................................................... 10-210.2 接收与显示节目故障处理....................................................................................................................... 10-310.2.1 STB不能正常解码节目.................................................................................................................. 10-310.2.2 混频后STB搜索不到节目............................................................................................................. 10-310.2.3 无电视信号...................................................................................................................................... 10-410.2.4 过滤后节目还存在.......................................................................................................................... 10-410.2.5 插入PSI/SI信息导致STB工作异常 ............................................................................................ 10-410.2.6 映射后的节目未能正常播放.......................................................................................................... 10-5目录InfoLink DTX8200系列QAM调制器用户指南10.2.7 图像显示马赛克或定帧.................................................................................................................. 10-5 10.3 网管管理设备故障处理........................................................................................................................... 10-610.3.1 网管不能提取PSI/SI信息 ............................................................................................................. 10-610.3.2 网管不能控制添加的设备.............................................................................................................. 10-610.3.3 网管软件未能成功提取PSI/SI表信息.......................................................................................... 10-711 FAQ ........................................................................................................................................... 11-111.1 名词解释FAQ .......................................................................................................................................... 11-211.2 操作应用FAQ .......................................................................................................................................... 11-3InfoLink DTX8200系列QAM调制器用户指南插图目录插图目录图1-1 DTX8200在数字电视前端的应用......................................................................................................... 1-2图1-2 DTX8200总体结构示意图..................................................................................................................... 1-4图2-1 DTX8200外观示意图............................................................................................................................. 2-2图2-2 DTX8200前面板示意图......................................................................................................................... 2-2图2-3 DTX8208后面板 .................................................................................................................................... 2-3图2-4 DTX8209后面板 .................................................................................................................................... 2-3图2-5 DTX8210后面板 .................................................................................................................................... 2-3图2-6 DTX8211与DTX8211E后面板............................................................................................................. 2-4图2-7 DTX8200接口图 .................................................................................................................................... 2-4图2-8 信息查询项 ............................................................................................................................................. 2-6图2-9 码流处理项 ............................................................................................................................................. 2-6图2-10 输出设置项 ........................................................................................................................................... 2-6图2-11 输入设置项............................................................................................................................................ 2-7图2-12 网络设置 ............................................................................................................................................... 2-7图2-13 系统设置 ............................................................................................................................................... 2-8图3-1 DTX8200安装流程................................................................................................................................. 3-2图3-2 DTX8200的固定 .................................................................................................................................... 3-2图3-3 连接地线 ................................................................................................................................................. 3-4图3-4 75Ω同轴线缆.......................................................................................................................................... 3-4图3-5 DS3输入、输出连接示意图.................................................................................................................. 3-5图3-6 ASI输入、输出连接示意图................................................................................................................... 3-6图3-7 SPI线缆................................................................................................................................................... 3-7图3-8 SPI线缆连接示意图............................................................................................................................... 3-7图3-9 IF输入、IF输出自环连接示意图......................................................................................................... 3-8图3-10 RF射频输出连接示意图...................................................................................................................... 3-9插图目录InfoLink DTX8200系列QAM调制器用户指南图3-11 10/100M网线 ........................................................................................................................................ 3-9图3-12 连接10/100M网口示意图 ................................................................................................................. 3-10图3-13 连接电源和地线.................................................................................................................................. 3-10图3-14 DTX8200启动显示............................................................................................................................. 3-11图4-1 设置过滤参数 ....................................................................................................................................... 4-13图4-2 设置映射参数 ....................................................................................................................................... 4-15图5-1 设置网口IP地址 .................................................................................................................................... 5-3图5-2 设置网口子网掩码.................................................................................................................................. 5-4图5-3 设置网关地址 ......................................................................................................................................... 5-4图5-4 设置网口模式 ......................................................................................................................................... 5-5图5-5 打开TS网口........................................................................................................................................... 5-6图5-6 设置TS网口IP地址.............................................................................................................................. 5-6图5-7 设置TS网口子网掩码 ........................................................................................................................... 5-6图5-8 设置网管PID .......................................................................................................................................... 5-7图5-9 透明传输示例 ......................................................................................................................................... 5-8图5-10 打开透明传输网口................................................................................................................................ 5-8图5-11 设置透明传输网口IP地址 .................................................................................................................. 5-9图5-12 设置透明传输网口子网掩码................................................................................................................ 5-9图5-13 设置透明传输网口网关地址................................................................................................................ 5-9图5-14 设置透明传输网元IP ......................................................................................................................... 5-10图5-15 设置透明传输网口源地址.................................................................................................................. 5-10图5-16 设置透明传输网口目标地址.............................................................................................................. 5-11图6-1 配置组网图 ............................................................................................................................................. 6-2图6-2 基本配置 ................................................................................................................................................. 6-3图6-3 提取表信息 ............................................................................................................................................. 6-4图6-4 复用接口配置 ......................................................................................................................................... 6-5图6-5 配置组网图 ............................................................................................................................................. 6-6图7-1 启动FTP服务器软件............................................................................................................................. 7-2图7-2 升级软件界面 ......................................................................................................................................... 7-3图7-3 选择升级软件 ......................................................................................................................................... 7-4图7-4 设置升级服务器IP地址 ........................................................................................................................ 7-4图7-5 启动程序升级 ......................................................................................................................................... 7-5InfoLink DTX8200系列QAM调制器用户指南表格目录表格目录表2-1 功能及方向键说明.................................................................................................................................. 2-2表2-2 设备接口描述 ......................................................................................................................................... 2-5表3-1 DTX8200安装可选项............................................................................................................................. 3-3表4-1 配置顺序 ................................................................................................................................................. 4-2表4-2 输入接口可选项...................................................................................................................................... 4-3表4-3 模式参数选择 ......................................................................................................................................... 4-5表4-4 DS3模式号.............................................................................................................................................. 4-6表4-5 可选项参数 ............................................................................................................................................. 4-7表4-6 输出频率规划 ......................................................................................................................................... 4-7表4-7 输出频道参数选项.................................................................................................................................. 4-8表4-8 QAM调制数参数选项 ........................................................................................................................... 4-8表4-9 符号率参数选项...................................................................................................................................... 4-9表4-10 输出码率参数选项.............................................................................................................................. 4-10表4-11 射频信号选项...................................................................................................................................... 4-10表4-12 输出增益选项 ..................................................................................................................................... 4-11表4-13 频谱翻转选项 ..................................................................................................................................... 4-12表4-14 PID过滤选项 ...................................................................................................................................... 4-12表4-15 PID映射选项 ...................................................................................................................................... 4-14表4-16 PID插入选项 ...................................................................................................................................... 4-16表5-1 网管组网方式 ......................................................................................................................................... 5-2表6-1 基本流PID .............................................................................................................................................. 6-2表8-1 设备例行维护周期和维护项目.............................................................................................................. 8-2表8-2 设备的日维护项目.................................................................................................................................. 8-3表8-3 指示灯状态及说明.................................................................................................................................. 8-4表8-4 设备的月维护项目.................................................................................................................................. 8-5。

5G无线维护考试题及答案-华为设备

5G无线试题一、判断题1.FANc和FANd风扇板可以放置在BBU5900机框中使用。

()2.BBU5900的槽位编号是从左往右编排,再从上到下编排。

()3.操作时必须确保正确的ESD防护措施,如佩戴防静电腕带或手套,以避免单板、模块或电子部件遭到静电损害。

( )4.5GAAU模块使用双电源线供电方案时需要外接ODM,输入2路电源线输出转成1路电源线。

( )5、BBU3900与BBU5900槽位分布一致。

()6.IMB05机框挂墙是只允许竖放,不允许横放。

( )7.当前NSA场景主流的组网方案是Option 3x方案。

( )8.5G标准站点解决方案中AAU拉远距离需小于100米,超出100米的场景需单独申请特殊场景方案。

( )9.5G AAU支持级联。

()10.AAU本身有保护接地,在安装好保护接地线的情况下,AAU的电源线不需要剥开露出电源线屏蔽层进行固定。

( )11.pRRU支持级联。

()12.安装AAU电源线应注意:必须先连接AAU端连接器,再连接供电设备端连接器。

如果连接顺序错误或电源线极性反接,可能导致AAU设备损坏或人身伤害。

()13.目前已经发布的5G试点频段低频主要有2.6G、3.5G、4.9G、10G。

( )14.UMPTe3单板支持GPS及北斗。

()15.UPEUd电源板不能放置在BBU5900机框中使用。

( )一、单选题1、5G基站主控板推荐优先部署在BBU5900几号槽位(D )A.0B.3C.6D.72、DCDU-12B 电源模块的输出规格为(A)A.10路30AB.10路20AC.7路30AD.7路20A3、5G AAU使用的eCPRI光模块带宽大小是多少(B)A.10GEB.25GEC.50GED.100GE4、按照标准5G站点解决方案,BBU5900部署大于等于2个UBBPfw1全宽基带板时,需要配置UPEUe电源模块的数量为(B )A.1个B.2个C.1个或者2个均可以D、以上均不对5、按照标准站点解决方案,无功分器、放大器场景GPS最大拉远距离为(C )A.50mB.70mC.150mD.170m6、BBU5900安装在第三方机柜时为防止系统风量不足,建议相邻BBU之间预留(A )U或以上间距,并安装挡风板,避免风道回流A.1UB.3UC.5UD.6U7、5G BBU5900与传输对接使用的光模块带宽大小是多少CA.100MB.1GEC.10GED.100GE8、BBU5900 UPEUe电源模块输入电源线需要几路(直流电源线正负算1路)BA.1路B.2路C.3路D.5路9、5G 全宽基带板推荐部署在BBU5900的槽位优先级顺序为AA.0>2>4B.4>2>0C.4>2>0>1>3>5D.5>3>110、UPEUe的输出功率是(D)A、350WB、650WC、1100WD、2000W11、5G频谱规划中属于C-Band的频率是(C)A、800MHZB、2.6GHZ C 4.9GHZ D、35GHZ12、在5G编码之争中,华为主导的(B)最终成为5G控制信道编码标准。

低功耗接收芯片MAX1471