Sunplus SPHE8202V Design Guide_for_zihuan

VSC8221芯片评估板用户指南说明书

VSC8221User Guide VSC8221 Evaluation BoardContents1Revision History (1)1.1Revision 1.0 (1)2Introduction (2)3General Description (3)3.1Hardware Features (3)3.1.1Power Connections (3)3.1.2Copper Port RJ45 Connections (3)3.1.3SFP or SMA SGMII MAC Interface (3)3.1.4Switches (3)3.1.5Taitien 25 MHz Crystal (3)3.1.6External RefClk Option (4)3.1.7Silabs Microcontroller (4)3.1.8EEPROM Option (4)3.1.9CMODE Pins (4)3.1.10CLOCKOUT SMA (4)3.2Software Requirements (4)4Quick Start (5)4.1Board Configuration (5)4.1.1Clock and Reset (5)4.1.2Power Up (5)4.2GUI and Driver Installation (5)4.3Using the GUI (6)4.4Test Cases (7)4.4.1CAT5 to 802.3z Serdes with Clause 37 AutoNeg Detection (7)4.4.2CAT5 to SGMII with Modified Clause 37 AutoNeg Disabled (8)4.5Useful Registers (8)4.5.1Ethernet Packet Generator (8)4.5.2Far-End Loopback (8)4.5.3Near-End Loopback (8)5Additional Information (9)1Revision HistoryThe revision history describes the changes that were implemented in the document. The changes arelisted by revision, starting with the most current publication.1.1Revision 1.0Revision 1.0 was the first release of this document. It was published in December 2013.2IntroductionThe VSC8221 device is a low-power, Gigabit Ethernet transceiver suited for Ethernet Switches with SGMII/SerDes MAC interfaces, Media Converter applications, and SFP/GBIC modules. The VSC8221 device alsoincludes Vitesse’s VeriPHY Cable Diagnostics feature.This document describes the operation of the VSC8221 Evaluation Board (VSC8221EV). The Quick Startsection describes how to install and run the graphical user interface (GUI) to fully control the evaluationboard.Figure 1 • VSC8221EVThe following reference documents provide additional information about the operation of the VSC8221evaluation board.VSC8221 DatasheetVSC8221 Evaluation Board GUIVSC8221 Evaluation Board Schematics3General DescriptionThe VSC8221EV provides the user a way to evaluate the VSC8221 device in multiple configurations. OneRJ-45 connector is provided for the copper media interface. The MAC interface is provided via SMAconnectors or alternatively through an SFP connector.The VSC8221’s internal registers are accessed via the MDIO bus from an external microcontroller drivenby an external PC via USB. The accompanying GUI enables the user to read and write the deviceregisters. Alternatively, the VSC8211EV also has the capability to configure the VSC8221 through anEEPROM or Rabbit microcontroller (not-provided).The evaluation board has the option to use VSC8221’s internal on-chip oscillator by connecting a 25MHzcrystal to XTAL1 and XTAL2 or an external reference clock signal through the REFCLK SMA (J11).3.1Hardware Features3.1.1Power ConnectionsFor convenience, the evaluation board runs off a single +5VDC power supply. On board DC-DCconvertors create the +3.3VDC rail for the board and optional +1.2VDC rail. Power is supplied to theupper right corner of the board. Power can be applied either to the 5.5 x 2.1 mm barrel connector (J20)or the banana receptacles (J21 and J15). The slide switch (SW-4) selects between the external (on-board) and internal (on-chip) regulator option. J22 is an optional monitor point for the 1.2 V rail. Whenpowered by a bench top supply the board may draw up to 3 A maximum, module included.3.1.2Copper Port RJ45 ConnectionsThe RJ45 copper media PHY port (J1) uses a generic RJ45 jack with a discrete Pulse H5008 magnetictransformer.3.1.3SFP or SMA SGMII MAC InterfaceThe default MAC interface is provided through an SFP port connector. When using the SFP port, theSigDet polarity must be swapped in the VSC8221. See register 19E.0. Note that the transmit disablesignals (TXDIS) are connected to ground, thus the laser is always turned on.An optional MAC interface through SMA connectors may be enabled by removal and re-soldering the ACcoupling caps (C7–C10) from horizontal to vertical position.3.1.4SwitchesThere are two switches on the board:SW4 to select between utilizing a +1.2V internal regulator or external regulator. The default optionfor the board is to use the external regulator.SW2 allows the user to select the mode of the EECLK/PLLMODE pin. In the on position a logic highvoltage (pull-up resistor) configures the device for a 125MHz reference clock while a logic lowvoltage (pull-down resistor) selects a 25MHz reference clock option. This is a momentary ON switchwhich requires the user to hold it in the on position for 3 seconds during board power up or devicereset.3.1.5Taitien 25 MHz CrystalThe evaluation board is shipped configured to use the VSC8221’s internal on-chip oscillator. The jumperon J12 should be installed in the XTAL (left) position, and the jumper on J24 should be installed in thePLL enable or VCC (right) position.Note: Review the required action for SW2 mentioned above.1. 1.2.3.1.6External RefClk OptionThe user may choose to provide an external PHY REFCLK via the SMA connector (J11). The user must configure the device by installing a jumper on J24 in the PLL disable or ground (left) position and installing a jumper on J12 in the SMA (right) position.3.1.7Silabs MicrocontrollerA Silabs F340 microcontroller is included to facilitate a software interface to the registers on the VSC8221through a USB port.3.1.8EEPROM OptionThe user may choose to configure theVSC8221 via an EEPROM load. In order to program the EEPROM properly, pull-up or pull-down resistors must be configured for either R7 – R9 or R15 – R17. See Section 19 of the datasheet regarding to EEPROM programming requirement.3.1.9CMODE PinsOn the lower center of the board, there is an option to change the CMODE pin pull-up or pull-down resistors, R6, R12 – R14, and R18 – R21. See Section 18 of the datasheet for the detail on how toprogram the desired operating condition parameters through the CMODE configuration bits and how to choose the value of each CMODE pull-up or pull-down resistor.3.1.10CLOCKOUT SMAThe user should observe a 125MHz output clock through this SMA if the internal PHY PLL is operating properly.3.2Software RequirementsThe VSC8221 GUI can be loaded on to any PC or laptop that complies with the following requirements:The PC must run a recent version of MS-Windows. According to the Microsoft website, the following operating systems can run .NET based applications:Windows 2000Windows XP Windows Vista Windows-7Note: The GUI may be slower when run on Windows 2000 operating system.Hardware requirements must be considered when deploying/installing .NET applications. The minimum hardware requirement for a system running a .NET application is a Pentium 90MHz with 32 MB of RAM. For best performance, a newer system is recommended along with a minimum of 1 GB of RAM.If the .NET Framework 2.0 is not already installed, it may be obtained from the following link: /downloads/details.aspx?FamilyID=0856EACB-4362-4B0D-8EDD-AAB15C5E04F5&displaylang=en4Quick Start4.1Board ConfigurationPrior to powering the board, ensure that the jumpers and switches are in the following positions.Table 1 • Switch and Jumper ConfigurationSwitch/Jumper PositionJ19 (MDC)Jumper installed connecting F340 MDC to DUT MDCJ19 (MDIO)Jumper installed connecting F340 MDIO to DUT MDIOJ14 (TRSTB)Jumper installed connecting to GND. This is not requiredwhen R48 is installed.J12 (XTAL1/REFCLK)Jumper installed connecting center pin to XTAL.J24 (PLL ENABLE/DISABLE)Jumper installed connecting center pin to PLL ENABLE.SW2Hold in the left position during power-up and reset.SW4Slide to the left to use the on-chip regulator.4.1.1Clock and ResetPower must be applied and the clock (either 25 MHz or 125 MHz) must be active at the correctfrequency for the prescribed period of time in the datasheet before the RESETB pin is released.PLLMODE and OSCDISB pins are sampled during the device power-up or on assertion of RESETB pin.The board will be shipped configured for use of the 25 MHz crystal thus OSCDISB must be pulled up andPLLMODE must be pulled down during power-up or assertion of RESETB by setting J24 to the PLL enableposition and holding SW-2 in the 25 MHz position upon power-up.4.1.2Power UpProvide +5VDC to the board by plugging in the power cable (included in the kit) to J20. Two green LEDsshould illuminate: D12 on the left side of the board indicating +3.3VDC present and D11 on the right sideof the board indicating +1.2VDC present.4.2GUI and Driver InstallationDownload the VSC8221EV GUI from Vitesse’s website onto a PC that has a USB port. Install the GUI bylaunching the setup.exe file. Once installed, connect the USB cable between the USB port of the PC andthe USB connector (J16) on the evaluation board. Ensure the MDIO and MDC jumpers are properlyplaced from DUT to F340 on J23 to establish the connection between the VSC8221’s SMI pins and theSiLab F340.USB communication is assisted by the Silabs USBXpress® drive. If not present on the PC, the user willneed to download the USBXpress Development Kit from the Silicon Labs website (URL: http://www./products/mcu/Pages/USBXpress.aspx). Follow the installation directions after downloading the development kit.To ensure the USBXpress driver is installed and properly recognizing the evaluation board, go to ControlPanel and click on System>Hardware>Device Manager, and inspect the Universal Serial Bus controllerslisted to see if “USBXpress Device” appears. The following figure shows that the PC recognizes that aUSBXpress Device is connected.Figure 2 • USBXpress as Seen from the Device Manager Window4.3Using the GUILaunch the GUI either by clicking on the Desktop shortcut or clicking on the “Start – Programs – VitesseSemiconductor Corp - VSC8221_Evaluation_System” icons. The initial window will detect the attachedUSB devices automatically. The following figure shows a typical EVB Connection window.Figure 3 • Connection WindowThe EVB serial number should appear. If not, click on “Scan For USB Devices.” Select that EVB serialnumber then click “Launch GUI”. The Register List window will appear as shown in the following figure.1. a. b. c. d.Figure 4 • Register List WindowVerify that the device is up and running by reading MII Register 0. It should read back 0x1040. Reading back “0000” or “FFFF” (all 0’s or all 1’s) indicates a problem.To read or write the extended MII registers click on the ExtMII tab.An initialization script may be used to configure multiple VSC8221 registers. The initialization script is simply a text file which contains a list of registers to be written. Select the Device item on the top pull down menu area and click on Load-All-Registers option. A pop-up window will appear. Navigate to and select the desired script to be loaded.As per Section 31.1 of the datasheet, there are a number of internal registers that must be changed from their default value during device initialization. Use this method to initialize the device by loading “vsc8221_workaround31_1.txt” included in the GUI package under the Script/ directory. GUI Setup4.4Test Cases4.4.1CAT5 to 802.3z Serdes with Clause 37 AutoNeg DetectionAfter power-up or reset, the VSC8221 will operate at CAT5 to 802.3z Serdes with clause 37 Auto Negotiation Detection mode. An SFP loopback module enables MAC side SGMII loopback. 1G Ethernet received by the VSC8221 RJ-45 port is routed through the VSC8221 and looped back via SGMII through the SFP Electrical Loopback module.Set up the copper Ethernet traffic source (e.g., IXIA or Smartbits).Connect an Ethernet cable to an RJ-45.Plug in a SFP loopback module.Monitor the link-up bit in MII Register 1, bit 2 (MII 1.2), read twice to update. Traffic should now be flowing.1. 2. 3. 4. 5. 6. 4.4.2CAT5 to SGMII with Modified Clause 37 AutoNeg DisabledTo configure the device for Clause 37 Auto-negotiation disabled, perform these steps:Set up the copper Ethernet traffic source (e.g., IXIA or Smartbits).Connect an Ethernet cable to an RJ-45.Plug in a SFP loopback module.Write 0xBA20 to “MII Register” (Port 0) Reg 23 (Extended PHY Control #1).Write 0x9040 to “MII Register” (Port 0) Reg 0 (SW Reset for PHY Control setting to take effect).Monitor the link-up bit in MII Register 1, bit 2 (MII 1.2), read twice to update. Traffic should now be flowing.4.5Useful Registers4.5.1Ethernet Packet GeneratorExtMII 29E is the Ethernet Packet Generator register. Refer to datasheet for configuration options.A bad-CRC counter is in ExtMII 23.7:0. This counter will be saturate at 0xFF and is cleared when read.4.5.2Far-End LoopbackWhen MII Register 23 bit 3 is set to 1, it forces incoming data from a link partner on the media side to be retransmitted back to the link partner on the media interface.4.5.3Near-End LoopbackWhen MII Register 0 bit 14 is set to 1, the transmit data (TDP/TDN) on the MAC side is looped back onto the receive data (RDP/RDN pins) to the MAC.5Additional InformationFor any additional information or questions regarding the device(s) mentioned in this document, contactyour local sales representative.Microsemi HeadquartersOne Enterprise, Aliso Viejo,CA 92656 USAWithin the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996Email:***************************© 2013 Microsemi. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www. .VPPD-03471。

Get格雅基于LabVIEW和DS820的多点温度测试系统—上位机部分

基于LabVIEW和DS820的多点温度测试系统—上位机部分毕业设计〔论文〕原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计〔论文〕,是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过奉献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计〔论文〕的规定,即:按照学校要求提交毕业设计〔论文〕的印刷本和电子版本;学校有权保存毕业设计〔论文〕的印刷本和电子版,并提供目录检索与阅览效劳;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的局部或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要奉献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承当。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保存、使用学位论文的规定,同意学校保存并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或局部内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日注意事项1.设计〔论文〕的内容包括:1〕封面〔按教务处制定的标准封面格式制作〕2〕原创性声明3〕中文摘要〔300字左右〕、关键词4〕外文摘要、关键词5〕目次页〔附件不统一编入〕6〕论文主体局部:引言〔或绪论〕、正文、结论7〕参考文献8〕致谢9〕附录〔对论文支持必要时〕2.论文字数要求:理工类设计〔论文〕正文字数不少于1万字〔不包括图纸、程序清单等〕,文科类论文正文字数不少于万字。

Yokogawa PH20和FU20 pH Redox和温度传感器用户手册说明书

Model PH20 and FU20pH/Redox and Temperature sensorThe PH20 is nicknamed “Tempress” because of the patented compensation for changes in the process temperature andpressure. This simple mechanical feature makes the sensor more accurate, and gives it a longer lifetime. The compensation panels flex to accommodate changes in the avoiding large differential pressures across the diaphragm. This prevents most problems associated with the reference junction. Made in chemically resistant PVDF, this all-in-one sensor has elements to measure pH, ORP and temperature. The reference system is Silver/Silver Chloride, with a double junction and a gelled electrolyte to combat pollution. The Platinum Redox electrode doubles as a solution ground, essential for uncompromising accuracy, and for sensor diagnostic measurements.The FU20 combination sensors show how Yokogawa applies the motto “Simply the Best” to sensor technology. The wide body sensors (26 mm diameter) hold four separate elements in one unbreakable PPS 40GF (RytonTM) body. Installation is simple with the integrated industrial 3/4” tapered thread. The large volume gelled electrolyte and the double junction reference system slows down depletion and poisoning therefore extending the lifetime. The system is targeted at those applications where simplicity will result in accurate and reliable pH- or redoxmeasurements. This means that in 90% of the know applications this sensor will be an excellent choice.Features• Simultaneous pH- and ORP measurement • I ntegral Pt1000 temperature element for enhanced accuracy • Available with VP connector • D ouble junction and long diffusional path for reference pollution resistance • E xtended life time by large volume of polymerized electrolyte and porous PTFE diaphragm • S olid Glass/Platinum electrode for solution ground or ORP measurement• Simple maintenance by comprehensive design • Direct in-line, immersion or off-line installation • Calibration certificate delivered with each sensorGeneralSpecificationsGeneral Specifications PH20Measuring elements: p H glass electrode and Silver/Silver chloride reference system.: P latinum electrode and Pt1000temperature sensor. Construction materialsBody : PVDFEarthing pin : Solid platinum/glassO-ring : VitonReference junction : Porous PTFECable : Coaxial with 4 extra leads Sheetmaterial : Thermoplastic rubber Functional specifications (at 25°C)Isothermal point : pH 7Reference system : Ag/AgCl with saturated KCl Glass impedance : 200 MΩ (nominal), G-glass Junction resistance : 1 to10 kΩTemperature element : Pt1000 to IEC 751 Asymmetry potential : < 15 mVSlope : > 96 % (of theoretical value) Dynamic specifications (at 25°C)Response time pH step (7 to 4): < 10 sec for 90%Response time temp. step (10°C): < 3 min for 90 %Stabilisation time (0.02 pH/10 s): < 1 minuteOperating rangepH : 0 - 14*Temperature : -10 to 105ºC (14 to 212 °F) Pressure : 0 to 10 bar ( 0 to 142 PSIG) Conductivity : > 50 µS/cmStorage temperature : -30 to 50ºC (-22 to 122 °F)The erratic trend of the standard sensor shows the progressive contamination of its reference junction. The graph indicates between 0.1 to 0.4 pH error with the conventional sensor while the readings from the PH20 are extremely stable.General Specifications FU20Measuring elements : p H glass electrode and silverchloride reference system.Platinum electrode and Pt1000temperature sensor. Construction materialsBody : R yton R4TM (PPS 40GF) with glassfillingEarthing pin : Solid platinumO-ring : NoneReference junction : Porous PTFECable : Coaxial with 4 extra leads Sheetmaterial : Thermoplastic rubber Functional specifications (at 25°C)Isothermal point : pH 7Reference system : Ag/AgCl with saturated KCI Glass impedance- Dome shape : 350MΩ, G-glass- Flat Surface : 750MΩ, G-glassJunction resistance : 0.5 to 5 kΩTemperature element : Pt1000 to IEC 751Asymmetry potential : < 15 mVSlope : > 96 % (of theoretical value) Dynamic specifications (at 25°C)Response time pH step (7 to 4): < 15 sec for 90%Response time temp step (10°C)- Dome shape : < 3 min for 90%- Flat surface : < 6 min for 90%Stabilisation time (0.02 pH/10 s): < 2 minutesOperating rangepH : 0 - 14*Temperature : -10 to 105ºC (14 to 212 °F) Pressure : 0 to 10 bar ( 0 to 142 PSIG) Conductivity : > 50 µS/cmStorage temperature : -30 to 50ºC (-22 to 122 °F)* T he pH range at room temperature is 0 -14 pH, but at high temperatures the lifetime will be seriously shortened outside 2 - 12 pH range.2GS 12B6J3-E-E3 Dimensions4Installation examples using the PH20 adapter rangeUsing the /SF4 adapter, the PH 20 can be mounted in the standard range of conductivity flow fitting (FF40..), the immersion fittings (FD40-..) and sub-assemblies (FS40..). The adapter can be mounted on the front thread, or the back thread dependent on the required insertion depth.GS 12B6J3-E-EFD40 fittings (/FPS or K1523DD)Note: old part K1523DC is not compatible with VP connector.5GS 12B6J3-E-EInstallation examples using the FU20 adapter range6Model and Suffux codesModel Suffix Option DescriptionCode codePH20 4-in-1 pH sensorMaterial -F PVDFMembrane -G Dome shapedCable length -02 2 meter-05 5 meter-10 10 meter-20 20 meter-30 30 meterTemp. element -T1 Pt1000-N -A Always -N -AOptions*/SN3 S tainless steel 3/4” NPT adapter (316L)/SR3 S tainless steel 3/4” R adapter (316L)/FN4 P VDF 1” NPT adapter/FR4 P VDF 1” R adapter/PH8 A dapter for PH8 combi sensor fittings (only)/SF4 S tainless steel adapter for FF40, FS40 and FD40 fitings/HCNF H astelloy cleaning system* Note: Option /Q: Quality Inspection certificate is always included with the product.Model Suffix Option DescriptionCode codeFU20 Wide body sensor-VP Variopin connectorCable length -03 3 meter-05 5 meter-10 10 meter-20 20 meterTemp. element -T1 Pt1000Model -NPT Dome shape model-FSM Flat surface modelOptions*/HCNF H astelloy cleaning system/FPS Adapter F*40 from noryl/NSS 1” NPT adapter, SS (316L)/NTI 1” NPT adapter, Titanium/BSS 1” BSP adapter, SS (316L)/BTI 1” BSP adapter, Titanium* Note: Option /Q: Quality Inspection certificate is always included with the product.Model Suffix Code DescriptionWU10Sensor cableConnector type -V VariopinCable type -S Single CoaxCable length -02 2 meters-05 5 meters-10 10 meters-15 15 meters-20 20 metersGS 12B6J3-E-ECleaning system for FU20 & PH20Some applications require frequent cleaning of the electrode. For these applications Yokogawa designed a chemical cleaning system that can either be used in the Yokogawa fitting range (HCN2, HCN3 or HCN4) or as back-end mounting option for the PH20 and FU20. The /HCNF option comes with a hastelloy cleaning nozzle, Stainless steel mounting (and ferrules) sets and a nylon tube of 10 meters.7GS 12B6J3-E-ESpare parts PH20, FU20 and cleaning systemPart no. DescriptionK1500EK O-rings viton 6.07x1.78 (5x2)K1500ER O-ring set Viton FF20-S22K1511DP O-rings viton 21.9x2.62 (5x2)K1511DQ O-rings EPDM 21.9x2.62 (5x2)K1547PC /FN4 for PH20K1547PD /FR4 for PH20K1547PE /PH8 for PH20K1547PG Nozzle and mounting HCN4K1547PP Spare Part EPDM spraying valves K1547QA /SN3 for PH20K1547QB /SR3 for PH20K1547QF /SF4 for PH20K1500FR O-rings Viton 29.82x2.62 (5)K1500FS O-rings EPDM 29.82x2.62 (5)K1500FT O-rings Silicon, 29.82x2.62 (5)K1520ZD Mounting nut for PS20K1523DD /FPS, FU20-mounting in F*40K1547PK Adapter 1” NPT, SS 316 for FU20K1547PL Adapter 1” BSP, SS 316 for FU20K1547PM Adapter 1” NPT, Ti for FU20K1547PN Adapter 1” BSP, Ti for FU20K1547PJ Hast. cleaning unit HCNFK1547PFNozzle and mounting HCN2/3/FAccessories Buffer powder 6C231 Buffer powder pH 1.68 ; IEC 60746-26C232 Buffer powder pH 4.01 ; IEC 60746-26C236 Buffer powder pH 9.18 ; IEC 60746-26C237 Buffer powder pH 6.87 ; IEC 60746-2Connection equipment BA10 Junction box for pH extension cables WF10-xxx-F p H signal cable with terminated ends. Specifylength in whole metersGS 12B6J3-E-ESubject to change without notice Printed in The Netherlands, 11-705 (A) ICopyright©Conventional pH (& ORP) wiringConnect the PH20 or FU20 to the EXA or EXAxt PH analyzer as shown. With this configuration, it is possible to measure ORP (or rH) at the same time (Refer to the EXA or EXAxt manual for appropriate impedance jumper and Service Code settings).Wiring for ORP measurement with pH referenceConnect the PH20 or FU20 to the EXA Glass PH analyzer as shown. Refer to the EXA manual for appropriate impedance jumper and Service Code settings.Wiring for ORP measurement with normal referenceRefer to the EXA manual for appropriate impedance jumper and Service Code settings.Wiring of the PH20 / FU20。

SPHE8203R - Des Guide

CARD Reader TVUSB 2.0CVBS/YUV/SCART(SD/MMC/MS)SPI FlashGameDVD Loader8203RICHDMI5.1CH AudioVFD/IRSPHE8203RFigure 2-2 計算特性阻抗SPHE8203RFigure 2-4 HDMI differential trace layoutSPHE8203RFigure 2-6 USB 2.0 differential trace layoutSPHE8203RR3Figure 2-8 建議系統的 Reset Circuit SPHE8203RFigure 2-10 A+5V Power(2) M+5V Power提供給 motor driver 的 power,由於為主要耗電元件,因此穩壓電容非常的重要,務必在進driver 前配置大型電解電容。

並注意此 power 分支不宜和其他 5VFigure 2-11 M+5V PowerClose to 8203RFigure 2-13 PHURF layoutFigure 2-14 高頻信號參考訊號走線計有 Vref1、Vref2等兩種參考訊號,Vref1需接Bulk and bypass 電容以保證訊號穩定性而針對VREF2,目前SPHE8203R是以一新架構來產生出所需VREF2訊號,所以在線路上請依照藍色框線內的設定值設置,其中,圖2-15中的470 ohm電阻需盡量靠近SPHE8203R擺放。

Figure 2-15 參考訊號Figure 2-16 Audio OP PowerFigure 2-18 Crystal layoutSPHE8203RFigure 2-19 Load control signals 2.13 PCB LayoutFigure 2-20 Power trace layoutFigure 2-21 Power trace with I/O connector(3) 要注意所有信號線不可有跨plane (power and ground plane) 的情形發生。

Solaris 8 (SPARC 平台版) 发行说明说明书

Solaris8(SP ARC平台版)10/00发行说明更新Sun Microsystems,Inc.901San Antonio RoadPalo Alto,CA94303-4900U.S.A.部件号码806-6267–102000年10月Copyright2000Sun Microsystems,Inc.901San Antonio Road,Palo Alto,California94303-4900U.S.A.版权所有。

本产品或文档受版权保护,其使用、复制、发行和反编译均受许可证限制。

未经Sun及其授权者事先的书面许可,不得以任何形式、任何手段复制本产品及其文档的任何部分。

包括字体技术在内的第三方软件受Sun供应商的版权保护和许可证限制。

本产品的某些部分可能是从Berkeley BSD系统衍生出来的,并获得了加利福尼亚大学的许可。

UNIX是通过X/Open Company,Ltd.在美国和其他国家独家获准注册的商标。

Sun、Sun Microsystems、Sun标志、、AnswerBook、AnswerBook2、Java,JDK,DiskSuite,JumpStart,HotJava,Solstice AdminSuite,Solstice AutoClient,SunOS,OpenWindows,XView,和Solaris是Sun Microsystems,Inc.在美国和其他国家的商标、注册商标或服务标记。

所有SPARC商标均按许可证使用,它们是SPARC International,Inc.在美国和其他国家的商标或注册商标。

带有SPARC商标的产品均以Sun Microsystems,Inc.开发的体系结构为基础。

PostScript是Adobe Systems,Incorporated的商标或注册商标,它们可能在某些管辖区域注册。

Netscape Navigator(TM)是Netscape Communications Corporation的商标或注册商标。

Silicon Labs Wi-SUN 软件开发套件和硬件产品说明书

Wi-SUN SDK 1.1.0.0 GAGecko SDK Suite 3.2July 21, 2021Wireless Smart Ubiquitous Network (Wi-SUN) is the leading IPv6 sub-GHz mesh technol-Array ogy for smart city and smart utility applications. Wi-SUN brings Smart Ubiquitous Networksto service providers, utilities, municipalities/local government, and other enterprises, byenabling interoperable, multi-service, and secure wireless mesh networks. Wi-SUN canbe used for large-scale outdoor IoT wireless communication networks in a wide range ofapplications covering both line-powered and battery-powered nodes.Silicon Labs' Wi-SUN hardware is certified by the Wi-SUN Alliance, a global industry as-sociation devoted to seamless LPWAN connectivity. Wi-SUN builds upon open standardinternet protocols (IP) and APIs, enabling developers to extend existing infrastructure plat-forms to add new capabilities. Built to scale with long-range capabilities, high-datathroughput and IPv6 support, Wi-SUN simplifies wireless infrastructure for industrial ap-plications and the evolution of smart cities.These release notes cover SDK versions:1.1.0.0 released July 21, 20211.0.1.0 released June 16, 20211.0.0.0 released May 10, 2021Compatibility and Use NoticesFor information about security updates and notices, see the Security chapter of the Gecko Platform Release notes installed with this SDK or on the Silicon Labs Release Notes page. Silicon Labs also strongly recommends that you subscribe to Security Advisories for up-to-date information. For instructions, or if you are new to the Silicon Labs Wi-SUN SDK, see Using This Release.Compatible Compilers:IAR Embedded Workbench for ARM (IAR-EWARM) version 8.50.9•Using wine to build with the IarBuild.exe command line utility or IAR Embedded Workbench GUI on macOS or Linux could result in incorrect files being used due to collisions in wine’s hashing algorithm for generating short file names.•Customers on macOS or Linux are advised not to build with IAR outside of Simplicity Studio. Customers who do should carefully verify that the correct files are being used.GCC (The GNU Compiler Collection) version 10.2.0, provided with Simplicity Studio.Contents Contents1Wi-SUN Stack (2)1.1New Items (2)1.2Improvements (2)1.3Fixed Issues (2)1.4Known Issues in the Current Release (2)1.5Deprecated Items (3)1.6Removed Items (3)2Wi-SUN Applications (4)2.1New Items (4)2.2Improvements (4)2.3Fixed Issues (4)2.4Known Issues in the Current Release (4)2.5Deprecated Items (5)2.6Removed Items (5)3Using This Release (6)3.1Installation and Use (6)3.2Security Information (6)3.3Support (7)1 Wi-SUN Stack1.1 New ItemsAdded in release 1.1.0.0•Added a new SL_WISUN_MSG_NETWORK_UPDATE_IND_ID event that is fired when the network is updated: ip address update, new primary parent or new secondary parent.•The stack library is now compiled with the preprocessor definition DEBUG_EFM_USER and provides a default implementation of assertEFM(). It will only be used if the application is also compiled with that same definition. The user can provide a custom imple-mentation. See assertEFM() documentation for more information.Added in release 1.0.0.0Wi-SUN stack and SDK initial release1.2 ImprovementsNone1.3 Fixed IssuesFixed in release 1.1.0.0710923 Fixed an issue causig the event SL_WISUN_MSG_CONNECTED_IND_ID to be fired although no new connection was established. It was fired after each network update.699627 Fixed an issue causing connections to fail after an operating class update.721399 Fixed an issue causing US-IE configuration to be invalid when excluding channels.Fixed in release 1.0.1.0701190Fixed an issue causing a parent to lose track of its child frequency hopping sequence. The child router was sending an incorrect IFSU misleading the parent router and forcing it to be one frequency hop interval late. Fixed in release1.0.0.0Wi-SUN stack and SDK initial release1.4 Known Issues in the Current ReleaseIssues in bold were added since the previous release.714402 Wi-SUN border routervery infrequently hits a hard fault. Thecommand line interface is non-responsive and the router will notadvertize anymore. Routers will eventually report a PAN timeout.1.5 Deprecated ItemsNone1.6 Removed ItemsRemoved in release 1.1.0.0•Removed internal type definitions from the API public headers2 Wi-SUN Applications2.1 New ItemsAdded in release 1.0.0.0New Applications:•Wi-SUN - SoC CLI•Wi-SUN - SoC Empty•Wi-SUN - SoC Ping•Wi-SUN - SoC UDP Server•Wi-SUN - SoC UDP Client•Wi-SUN - SoC TCP Server•Wi-SUN - SoC TCP Client•Wi-SUN - SoC Meter•Wi-SUN - SoC Collector•Wi-SUN - SoC CoAP Meter•Wi-SUN - SoC CoAP CollectorNew precompiled demos:•Wi-SUN - SoC Border Router•Wi-SUN - SoC Border Router with backhaulEasy to use features (components):•POSIX like Socket•Application Core (event handling, connection handling, network configuration, etc.)•CoAP (Constrained Application Protocol)Radio Configurator Support (19 PHYs)Simplicity Studio – Network Analyzer Wi-SUN Support2.2 ImprovementsAdded in release 1.1.0.0Wi-SUN - SoC Border Router•Added a new command that configures new certificates•Added a new command to exclude channels from the frequency hopping schedule2.3 Fixed IssuesFixed in release 1.1.0.0720367 Fixed an issue causig collectors from both CoAP and non-CoAP sample applications to remove meters from their meter list.720336 Fixed an issue causing sample application for non-radio board targets to miss a radio configuration.2.4 Known Issues in the Current ReleaseSimplicity Studio – Network Analyzer: Wi-SUN Encrypted Packets are not supported yet2.5 Deprecated Items None2.6 Removed Items None3 Using This ReleaseThis release contains the following•Wi-SUN stack library•Wi-SUN sample applications•Wi-SUN border router pre-compiled demos•DocumentationIf you are a first time user, see QSG181: Silicon Labs Wi-SUN Quick-Start Guide.3.1 Installation and UseA registered account at Silicon Labs is required in order to download the Silicon Labs Wi-SUN SDK. You can register at https:///apex/SL_CommunitiesSelfReg?form=short.SDK installation instructions are covered in the Simplicity Studio 5 User’s Guide and QSG181: Silicon Labs Wi-SUN Quick-Start Guide. Use the Silicon Labs Wi-SUN SDK with the Silicon Labs Simplicity Studio 5 development platform. Simplicity Studio ensures that most software and tool compatibilities are managed correctly. Install software and board firmware updates promptly when you are notified. Documentation specific to the SDK version is installed with the SDK.3.2 Security InformationSecure Vault IntegrationThis version of the stack does not integrate Secure Vault Key Management.Security AdvisoriesTo subscribe to Security Advisories, log in to the Silicon Labs customer portal, then select Account Home. Click HOME to go to the portal home page and then click the Manage Notifications tile. Make sure that ‘Software/Security Advisory Notices & Product Change Notices (PCNs)’ is checked, and that you are subscribed at minimum for your platform and protocol. Click Save to save any changes.3.3 SupportDevelopment Kit customers are eligible for training and technical support. Contact Silicon Laboratories support at /support.Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USAIoT Portfolio/IoTSW/HW/simplicityQuality /qualitySupport & Community/communityDisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software imple-menters using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and “Typical” parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the infor -mation supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A “Life Support System” is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs product in such unauthorized applications. Note: This content may contain offensive terminology that is now obsolete. Silicon Labs is replacing these terms with inclusive language wherever possible. For more information, visit /about-us/inclusive-lexicon-projectTrademark InformationSilicon Laboratories Inc.®, Silicon Laboratories ®, Silicon Labs ®, SiLabs ® and the Silicon Labs logo ®, Bluegiga ®, Bluegiga Logo ®, Clockbuilder ®, CMEMS ®, DSPLL ®, EFM ®, EFM32®, EFR, Ember ®, Energy Micro, Energy Micro logo and combinations thereof, “the world’s most energy friendly microcontrollers”, Ember ®, EZLink ®, EZRadio ®, EZRadioPRO ®, Gecko ®, Gecko OS, Gecko OS Studio, ISOmodem ®, Precision32®, ProSLIC ®, Simplicity Studio ®, SiPHY ®, Telegesis, the Telegesis Logo ®, USBXpress ® , Zentri, the Zentri logo and Zentri DMS, Z-Wave ®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Hold-ings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.。

Synopsys CODE V optical design software说明书

CODE V Optical Design Software Design, Optimize and Fabricate Reliable Imaging OpticsSynopsys’ Optical Solutions Group is one of the world’s leading developers of optical design and analysis tools, with CODE V®imaging design software, LightTools® illumination design software, LucidShape® products for automotive lighting design, and RSoft™ products for photonic and optical communication design. The group is also an independent supplier of optical systems design services, with more than 4,800 completed projects in imaging, illumination and optical systems engineering.Since its worldwide introduction in 1975, CODE V has been instrumental in the development of highly advanced optical systems, sometimes with profound effects on business and culture. It has been used in the development of revolutionary applications such as the compact disk player. CODE V algorithms are a keyand dominant technology in the design of the microlithographic lenses that permit the imaging of ultra-fine lines on computer chips—a necessary ingredient in the continuing improvement of computer speeds.CODE V software has contributed significantly to important technological advances across a wide spectrum of fields such as projection displays, medical instrumentation, advanced military technology and space exploration.Because of its established reputation for excellence and quality performance, CODE V is the software of choice when optics are critical to the success of a product or project.Exceptional Software SupportTechnical SupportWith CODE V, you get much more than the highest-rated optical design and analysis software available. You also get access to more than 50 person-years of optical engineering experience through our technical support staff. Whether you choose e-mail or our toll free phone number to request assistance, degreed optical engineering professionals are ready to answer your questions.Training, Documentation and Online ResourcesWe offer many options for learning CODE V. Attend classes at our Pasadena, California facility, attend classes offered worldwide by our international representatives, or schedule an onsite class at your facility that has been tailored to your needs. Complete, examples-based documentation and a dedicated customer website with video tutorials, FAQs, example models, macros, tips and training materials are also available to help you be successful with CODE V.OverviewUsing CODE V, our engineers played a key role in the design and implementation of all the primary null lenses used in the highly successful Hubble SpaceProgram UpdatesWe release extensive program updates approximately once ayear to add major new features. We also provide regular program updates with customer-requested enhancements. All software updates, ongoing technical support, and access to extensive content on our Customer Support Portal are included in our standard license.Pre-Tested and Pre-ApprovedOne of our most important strengths is the synergy between our optical engineering services and software development efforts. Our engineers provide ideas, guidance, testing and feedback for the development of CODE V . For example, expert tools based on unique algorithms developed by our engineers, such as Glass Expert and Asphere Expert, help automate the design process and save you time and effort. Most importantly, before you use the latest version of CODE V for engineering problem solving, you can be confident that the software has been put through its paces by a dedicated team of engineers working at the cutting edge of optical technology.Figure 1: CODE V utilizes a standard Windows ® user interface with many navigation and usability features.Navigation toolbarCommand window Status barNavigation toolbarStatus bar Command window Tabbed output windowsExtensive help capabilitiesLDM spreadsheet Customizable chartingApplicationsFrom the extreme UV to beyond the infrared and from consumer products to government hardware, CODE V will handle your optical imaging applications. CODE V’s state-of-the-art algorithms, user-friendly interface and intelligent defaults speed time to market and maximize the quality of your optical solution. Some applications and related CODE V features include:• Injection molded plastic lenses—environmental analysis and material tolerances• Grating spectrometers—wavelength dependent multi-configuration features• Digital camera lenses—tolerance and fabrication analysis features • High-NA lithography optics—polarization ray tracing • Reconnaissance lenses—glass optimization with partial dispersion control• Telescopes and other visual systems—true afocal modeling • Space-borne systems—environmental analysis • Laser scanning systems—diffraction beam propagation analysis• Infrared and UV systems—special material characterization • Telecommunication systems—fiber coupling efficiency computations• Segmented aperture systems—non-sequential ray tracing featuresView a gallery of CODE V applications at com/optical-solutions/codev/application-gallery.htmlApplications and DesignFigure 2: CODE V is the dominant software of choice to meet the stringent optimization, analysis and tolerancing demands of the integrated circuitmanufacturing industry.Figure 3: CODE V optimization delivers the best possible zoom lens designs. Global Synthesis is highly effective for zoom lenses and excellent chromatic correction is possible with powerful glass optimization. CODE Vincludes specialized features for zoom lens analysis that help youbuild the best lens, not just design one.Figure 4: Tilted and decentered reflective systems are easy to set up in CODE V. User-defined optimization constraints allow easy control of optical bundle and component clearances in off-axis reflective systems. CODE V optimized this “Before” system to this “After” system in a singleoptimization run in seconds on an Intel ®2.67 GHz dual-core PC.Figure 5: The winning design from the International Optical Design Conference “Camera in a Can” lens design contest was optimized using Global Synthesis. Synopsys optical engineers use Global Synthesis onevery applicable design project.Design OptimizationOptimization capabilities are often the most importantconsideration when choosing optical design software. CODE V’s award-winning, proprietary optimization algorithms are considered unsurpassed by industry leaders. Features include:• RMS blur, wavefront variance, MTF , fiber coupling efficiency and a fully user-defined error function• The Reduce Tolerance Sensitivity control (SAB) allows direct optimization of the as-built RMS wavefront error to reduce sensitivity of optical systems to manufacturing tolerances, improve as-built performance and minimize production costs • The best, most effective global optimization algorithm available • Step Optimization (STP) accelerates optimization convergence and navigates complicated solution spaces more effectively to find optical system solutions with smaller error functions compared to traditional damped-least-squares optimization • Intelligent optimization defaults and general constraints • Effective exact constraint handling• Support of weighted and penalty function constraint handling • Easy definition of user-defined constraints• Glass Expert and Asphere Expert that automatically choose the best set of glasses and optimal asphere locations• Significant feedback to allow you to confirm optimizationprogress and guide variable, constraint or optimization control changes if neededLike many optical design programs, CODE V’s local optimization (optimizing to find the local minimum of the error function) is based on damped least squares. However, several proprietary enhancements make CODE V’s optimization algorithm the most effective available. CODE V’s exact constraint handling, using Lagrange multipliers, separates control of constraints from the error function so that the error function optimization does not stall while attempting to hold heavily weighted constraints. You can develop the best solution—with the correct specifications—that fits the space available.CODE V’s intelligent optimization defaults work well for the vastmajority of systems, but can be overridden if desired. CODE V’s RMS blur, wavefront variance and MTF error functions cover the majority of applications, but you can also define you own merit function. CODE V offers smart defaults, with as little or as much control as you require and consistently yields the best designs. This efficiency results in more freedom to perform useful engineering work insteadof time-consuming tweaks of the error function.AnalysisCODE V’s analysis algorithms are recognized for their accuracy and speed, and match measurements of real-world hardware. Over tens of thousands of fabricated customer designs, more than 150 person-years of in-house engineering experience and thousands of daily development test cases assure the quality of CODE V performance predictions—even on the most complex optical systems.CODE V’s extensive suite of analysis capabilities include:• Many diagnostic evaluation options (for example, transverse ray aberration or OPD curves)• Many geometrical and diffraction-based image evaluation options (for example, spot diagrams and MTF)• Non-sequential ray tracing• Polarization ray tracing, including birefringent material modeling • General diffraction beam propagation • Partial coherence 1D and 2D image analysis • Fiber coupling efficiency • Illumination analysis• Thermal infrared narcissus analysis • 2D image simulationCODE V’s beam propagation analysis accurately predicts intensity, amplitude and phase characteristics of the diffracted optical beam anywhere in the optical system. Beam Synthesis Propagation(BSP), originally developed for NASA to solve the stringent accuracy challenges of the Terrestrial Planet Finder mission, sets an industry standard for accuracy, efficiency and ease of use. It uses a beamlet-based algorithm with proprietary enhancements designed to deliverextremely accurate and efficient modeling of diffracted wavefronts propagating through an optical system. BSP’s groundbreaking Pre-Analysis feature automatically recommends analysis settings based on your lens system and delivers an accurate answer in the shortest time possible.Partial coherence analysis can predict image structure of one- or two-dimensional objects based on fully coherent to fully incoherent illumination through an optical system. For photonic systems, fiber coupling efficiency of a diffraction image into a single mode fiber can be predicted, including the effects of misalignments and fiber tip cleavage angles.Analysis, Tolerancing and Fabrication SupportFor photonics systems, some useful CODE V features include gradient index materials, polarization ray Figure 6: Beam Synthesis Propagation’s beamlet-based wave propagation algorithm performs beam propagation analysis more accurately andefficiently than any other commercially available tool.Decompose initialCODE V is COM-enabled and can be used as a server application for other COM-enabled applications for specialized analysis tasks. CODE V’s Macro-PLUS is a powerful, yet easy-to-learn macro programming language with access to a broad range of lens constructional data and analysis output. It can greatly simplify repetitive tasks, and supports efficient generation of custom analysis, such as line and surface charts.Most CODE V analysis option inputs can be customized, butyou aren’t burdened with making all the choices. Intelligentinput defaults are provided in all options, based on our software knowledge of the computational algorithm and engineering knowledge about the appropriate defaults for real-world problems. You can have confidence in CODE V’s results. Tolerancing and Fabrication SupportCODE V is used to design optics destined for hardware and has many advanced capabilities to speed time to market and solve production problems before the design reaches manufacturing. You can be confident of delivering the best performing as-built optical design with minimized recurring and non-recurring costs. Features include:• Accurate and extremely fast tolerancing using CODE V’sproprietary wavefront differential algorithm• Optimization access to the fast wavefront differential algorithm for directly optimizing as-built RMS wavefront error• Singular Value Decomposition algorithm to determine the most effective compensator set• Interactive tolerancing spreadsheet to modify tolerance values and instantly see the effect on system performance andcompensator motion• Traditional finite differences and Monte Carlo tolerancingsupport• Interferogram interface for applying measured interferograms to the system model• Automatic system alignment optimization based on as-builtinterferogram analysis• CAD export using IGES, SAT and STEP file formats• Mechanical zoom lens CAM computation• Lens element weight and cost analysis (material andfabrication costs)CODE V’s sensitivity and inverse sensitivity (automatic error budgeting) tolerancing capabilities are based on measurable performance metrics such as RMS wavefront, MTF, distortion, Zernike wavefront coefficients and more. Multiple compensators can be declared and if desired, restricted to compensating subsets of tolerances. Boresight compensation can also be included. CODE V’s interferogram interface allows measured surface deformation or system wavefront data to be imported into CODE V and included as part of the lens model. CODE V’s alignment optimization is used to automatically guide the alignment of an as-built optical system using measured wavefront data. Whether your hardware is for the consumer, commercial or government markets, if you are planning to build your optical designs, then CODE V’s integrated design, analysis and fabrication support features make it the best optical software for the job.Figure 7: CODE V’s transverse ray aberration curves, pupil maps, spot diagrams, MTF curves and point spread function plots use advanced algorithms to ensure the most accurate results.Figure 8: A stellar interferometer showing interference fringes produced from separated apertures using non-sequential surface ray tracing anddiffraction analysis features.Comprehensive Features©2018 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks is。

使用手冊 V 1.00 InstaShow VS20 2说明书

使用手冊V 1.00 InstaShow™VS20版權版權所有 © 2023,BenQ Corporation。

所有權利受到保護。

未獲 BenQ Corporation 書面同意之前,不得將本出版品的任何部份以電子、機械、電磁、光學、化學、人工或其它任何方式重製、傳送、改寫、儲存於檢索系統,或翻譯成任何語言或電腦語言。

免責聲明對於本文之任何明示或暗示內容,BenQ Corporation 不做任何聲明或保證,亦明確拒絕提供任何保證、可交易性、或針對任何特定目的之適用性。

此外,BenQ Corporation 保留隨時修改或變更手冊內容之權利,且無須通知任何人士。

本使用手冊致力向客戶提供最新最精確的資訊,因此所有內容會不時修改而不另行通知。

如需本手冊的最新版,請造訪。

本指南的圖解及圖示僅供參考。

專利如需 BenQ 投影機專利項目的詳細資料,請造訪 /。

超連結與第三方網站相關聲明對於本產品所連結,且受協力廠商維護和控管之網站或類似資源內容,BenQ 概不負責。

提供上述網站或類似資源之連結,並不代表 BenQ 以明示或暗示方式針對其內容提供任何保證或聲明。

本產品預先安裝之所有協力廠商內容或服務皆採「原狀」提供。

對於協力廠商提供之內容或服務,BenQ 不提供任何明示或暗示保證。

對於協力廠商所提供內容或服務之精確性、有效性、更新性、合法性或完整性,BenQ 不提供任何擔保或保證。

無論在任何情況下,BenQ 對於協力廠商提供之內容或服務(包括其疏失)皆概不負責。

協力廠商提供之服務可能會暫時或永久終止。

BenQ 不擔保或保證協力廠商提供之所有內容或服務皆隨時可用,且對於這些內容和服務之終止概不負責。

此外,您在協力廠商營運之網站或類似資源所從事的任何交易,皆與 BenQ 無關。

如有任何問題、疑問或爭議,您應自行聯絡內容或服務供應商。

BenQ ecoFACTSBenQ has been dedicated to the design and development of greener product as part of its aspiration to realize the ideal of the “Bringing Enjoyment 'N Quality to Life” corporate vision with the ultimate goal to achieve a low-carbon society. Besides meeting international regulatory requirement and standards pertaining to environmental management, BenQ has spared no efforts in pushing our initiatives further to incorporate life cycle design in the aspects of material selection, manufacturing, packaging, transportation, using and disposal of the products. BenQ ecoFACTS label lists key eco-friendly design highlights of each product, hoping to ensure that consumers make informed green choices at purchase. Check out BenQ's CSR Website at / for more details on BenQ's environmental commitments and achievements.目錄版權 (2)免責聲明 (2)專利 (2)超連結與第三方網站相關聲明 (2)BenQ ecoFACTS (3)介紹 (6)產品功能 (7)包裝內容 (8)產品規格 (9)介紹 (11)Button (11)Host (11)Button 和 Host 的 LED 指示燈 (12)安裝 (14)環境檢查 (14)組裝 Host (15)設定 Host (15)將 Host 裝設至天花板 (15)將 Host 裝設至天花板安裝工具組上 (16)將 Host 放在桌上 (16)定位 Host 接收天線 (19)天花板安裝 (19)天花板安裝工具組安裝 (19)桌上放置 (20)連接 HDMI 纜線和電源 (21)組裝變壓器 (21)連接 HDMI 纜線 (22)透過電源變壓器獲得電源 (22)LAN 連線 (23)Wi-Fi 連線 (23)切換到 Button HDMI 纜線 (24)設定 Button 並開啟電源 (25)配對 Button 和 Host (27)將 Host 放在桌上時 (27)將 Buttons 和 USB 連接線收放在收納盒中 (30)重設 Host (30)重設 Button (31)啟用網路待機模式 (32)開始和停止投影 (33)準備就緒 (33)開始投影 (33)閒置投影 (34)分割畫面投影 (35)開始分割畫面投影 (35)從分割畫面切換到全螢幕投影 (36)操作行動裝置進行投影 (36)觸控返回 (37)在混合式會議中使用 InstaShow (38)設定視訊會議 (38)使用外接網路攝影機 (42)使用單一 InstaShow Button 作為麥克風 (44)使用多個 InstaShow Buttons 作為麥克風 (45)將另一個 WPS 連接到 Host (46)網頁管理 (47)存取網頁管理介面 (47)透過直接連線登入網頁管理介面 (47)透過區域網路登入網頁管理介面 (50)透過無線網路登入網頁管理介面 (50)入門 (52)頂端指令按鈕 (52)主欄 (52)資訊 (53)WAN (56)無線網路 (57)週邊裝置設定 (59)配對中 (62)顯示器 (64)進階設定 (65)排程中 (67)工具 (68)法律聲明 (80)疑難排解 (81)錯誤代碼 (83)介紹Instashow VS20 是無線會議解決方案,支援貴組織的 BYOM(自帶會議)。

优雅科技产品说明书

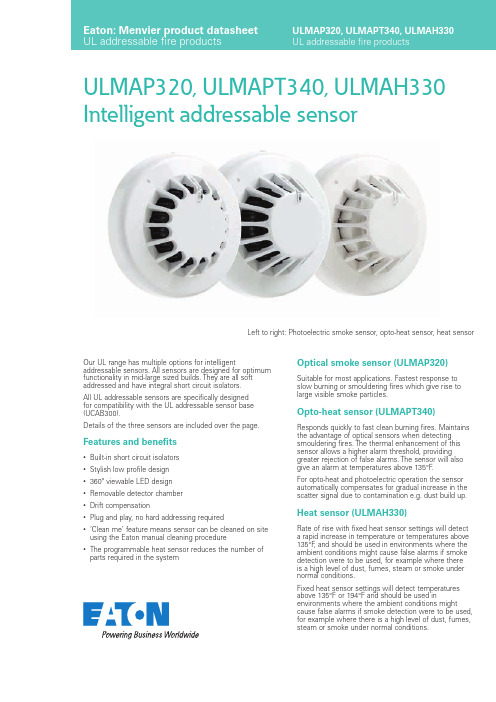

Optical smoke sensor (ULMAP320)Suitable for most applications. Fastest response to slow burning or smouldering fires which give rise to large visible smoke particles.Heat sensor (ULMAH330)Rate of rise with fixed heat sensor settings will detect a rapid increase in temperature or temperatures above 135°F , and should be used in environments where the ambient conditions might cause false alarms if smoke detection were to be used, for example where there is a high level of dust, fumes, steam or smoke under normal conditions.Fixed heat sensor settings will detect temperatures above 135°F or 194°F and should be used inenvironments where the ambient conditions mightcause false alarms if smoke detection were to be used, for example where there is a high level of dust, fumes, steam or smoke under normal conditions.ULMAP320, ULMAPT340, ULMAH330Intelligent addressable sensorOpto-heat sensor (ULMAPT340)Responds quickly to fast clean burning fires. Maintains the advantage of optical sensors when detecting smouldering fires. The thermal enhancement of this sensor allows a higher alarm threshold, providing greater rejection of false alarms. The sensor will also give an alarm at temperatures above 135°F .For opto-heat and photoelectric operation the sensor automatically compensates for gradual increase in the scatter signal due to contamination e.g. dust build up.Our UL range has multiple options for intelligentaddressable sensors. All sensors are designed for optimum functionality in mid-large sized builds. They are all soft addressed and have integral short circuit isolators.All UL addressable sensors are specifically designed for compatibility with the UL addressable sensor base (UCAB300).Details of the three sensors are included over the page.Features and benefits• Built-in short circuit isolators • Stylish low profile design • 360º viewable LED design • Removable detector chamber • Drift compensation• Plug and play, no hard addressing required•‘Clean me’ feature means sensor can be cleaned on site using the Eaton manual cleaning procedure•The programmable heat sensor reduces the number of parts required in the systemLeft to right: Photoelectric smoke sensor, opto-heat sensor, heat sensorT echnical specificationCodeULMAP320ULMAPT340ULMAH330Description Addressable sensor, photoelectric Addressable sensor, opto-heat Addressable sensor, multi-mode heat Standards UL268UL268, UL521UL521Supply ratings Working voltage 18 V dc to 30 V dc18 V dc to 30 V dc18 V dc to 30 V dcVoltage waveform Filtered dc +/- 1 V (max), ripple @120Hz Filtered dc +/- 1 V (max), ripple @120Hz Filtered dc +/- 1 V (max), ripple @120Hz Standby current 220 μμA (average)220 μμA (average)220 μμA (average)Alarm current 5 mA (max) 5 mA (max) 5 mA (max)Timings Start-up time 2 seconds2 seconds2 secondsReset time 2 seconds (max)2 seconds (max)2 seconds (max)Sensitivity Sensitivity2.55+/- 0.33%/ft2.55+/- 0.33%/ftN/ASensitivity checker Use No-Climb, TRUTEST, UL Listing 77TL Use No-Climb, TRUTEST, UL Listing 77TL Use No-Climb, TRUTEST, UL Listing 77TL Heat classHeat element rating N/A 135ºF135ºF ROR + Fixed, + Fixed 135ºF Fixed, 194ºF Fixed Heat detector spacing N/A50ft (heat alone operation)50ftPhysicalMounting position Ceiling in open areas Ceiling in open areas Ceiling in open areas IP ratingIP40IP40IP40EnvironmentalOperating temp. range 14° to 140° F (-10° to 60° C)14° to 122° F (-10° to 50° C)14° to 140° F (-10° to 60° C)UL listed temp. range 32° to 100° F (0° to 38° C)32° to 100° F (0° to 38° C)32° to 100° F/150° F (0° to 38° C/65° C)Humidity (non condensing)0% to 93% RH 0% to 93% RH 0% to 93% RH CompatibilityCompatibility identifier W002W002W002Compatible bases UCAB300UCAB300UCAB300Suitable for use with Eaton UL fire systems Eaton UL fire systems Eaton UL fire systems DimensionsDiameter (mm) (incl base)104104104Depth - D1 (mm) (incl base)455555Depth - D2 (mm) (excl base)334343Performance Heat classULMAP320ULMAPT340ULMAH330Heat element rating N/A 135°FROR + Fixed 135°F, Fixed 135°, Fixed 194°F Heat detector spacing N/A 50ft (heat alone operation)50ft Heat classN/AA2SA2RLED state LED state behaviour System eventOff LED is not illuminated.Global flash is disabled**.Slow flash Momentary flash approximately once every 30 seconds*.Global flash enabled. Detector is in quiescent state.Fast flash Momentary flash approximately 25 times per minute*.>24 detectors are in fire state.OnLED is constantly illuminated.Detector is in fire state.*Timing can vary depending on loop address quantities.**Detector flash in quiescent state can be disabled via control panel menu (ULDF6000).LEDsDescriptionCodeULMAP320 Optical smoke sensor 400005FIRE-0014X ULMAPT340 Opto-heat sensor 400006FIRE-0015X ULMAH330 Heat sensor 400007FIRE-0016X Addressable sensor baseUCAB300Catalogue numbers4AC8S24205S35885S35887EQUIPMENTEatonEMEA Headquarters Route de la Longeraie 7 1110 Morges, Switzerland Eaton.eu© 2020 EatonAll Rights ReservedPublication No. TD-EN-0820 August 2020Eaton is a registered trademark.All other trademarks are property of their respective owners.。

8202V_NEW_UI操作中文说明书_sunplus

第 3 页,共 60 页

8202V NEW UI 使用说明书 V1.0

存储设备(U 盘)可在本机上播放。

遥控器使用说明:

功能

功能描述

பைடு நூலகம்

OPEN/CLOSE 进/出仓 执行出仓、关仓、读碟功能

MUTE Media Type

P/N

l DISPLAY VOL+ tia VOL1~9、0、+10

n MENU e TITLE id RETURN f PLAY n STOP o PAUSE/STEP C ENTER

(一)SYSTEM SETUP(系统设置)....................................................................................... 40 (二)LANGUAGE SETUP(语言设置) ................................................................................... 46 (三)AUDIO SETUP(音频设置)......................................................................................... 48 (四)VIDEO SETUP(视频设定)......................................................................................... 52 (五)SPEAKER SETUP(视频设定)..................................................................................... 54

HRPWM