DE2-115所有引脚分配表

计算机组成原理4位二进制计数器实验报告

计算机组成原理实验一4位二进制计数器实验姓名:李云弟 学号:1205110115 网工1201【实验环境】1. Windows 2000 或 Windows XP2. QuartusII9.1 sp2、DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】1、熟悉VHDL 语言的编写。

2、验证计数器的计数功能。

【实验要求】本实验要求设计一个4位二进制计数器。

要求在时钟脉冲的作用下,完成计数功能,能在输出端看到0-9,A-F 的数据显示。

(其次要求下载到实验版实现显示)【实验原理】计数器是一种用来实现计数功能的时序部件,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。

计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS 触发器、T 触发器、D 触发器及JK 触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器按计数进制不同,可分为二进制计数器、十进制计数器、其他进制计数器和可变进制计数器,若按计数单元中各触发器所接收计数脉冲和翻转顺序或计数功能来划分,则有异步计数器和同步计数器两大类,以及加法计数器、减法计数器、加/减计数器等,如按预置和清除方式来分,则有并行预置、直接预置、异步清除和同步清除等差别,按权码来分,则有“8421”码,“5421”码、余“3”码等计数器,按集成度来分,有单、双位计数器等等,其最基本的分类如下:计数器的种类⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎪⎩⎪⎨⎧⎪⎩⎪⎨⎧⎩⎨⎧进制计数器十进制计数器二进制计数器进制可逆计数器减法计数器加法计数器功能异步计数器同步计数器结构N 、、、321 下面对同步二进制加法计数器做一些介绍。

同步计数器中,所有触发器的CP 端是相连的,CP 的每一个触发沿都会使所有的触发器状态更新。

DDR2内存引脚功能定义

《计算机维修技术第2版》易建勋编著清华大学出版社2009.8附件3-6:64位DDR2SDRAM Unb-DIMM内存条引脚功能定义(240脚)Pin Name Pin Name Pin Name Pin Name Pin Name Pin Name 1VREF41VSS81DQ33121VSS161NC(CB4)201VSS 2VSS42NC(CB0)*82VSS122DQ4162NC(CB5)*202DM4 3DQ043NC(CB1)*83DQS4123DQ5163VSS203NC 4DQ144VSS84DQS4124VSS164NC(DM8)*204VSS 5VSS45NC(DQS8)*85VSS125DM0165NC205DQ38 6DQS046NC(DQS8)*86DQ34126NC166VSS206DQ39 7DQS047VSS87DQ35127VSS167NC(CB6)*207VSS 8VSS48NC(CB2)*88VSS128DQ6168NC(CB7)*208DQ44 9DQ249NC(CB3)*89DQ40129DQ7169VSS209DQ45 10DQ350VSS90DQ41130VSS170VDDQ210VSS 11VSS51VDDQ91VSS131DQ12171CKE1211DM5 12DQ852CKE092DQS5132DQ13172VDD212NC 13DQ953VDD93DQS5133VSS173A15213VSS 14VSS54BA294VSS134DM1174A14214DQ46 15DQS155NC95DQ42135NC175VDDQ215DQ47 16DQS156VDDQ96DQ43136VSS176A12216VSS 17VSS57A1197VSS137CK1177A9217DQ52 18NC58A798DQ48138CK1178VDD218DQ53 19NC59VDD99DQ49139VSS179A8219VSS 20VSS60A5100VSS140DQ14180A6220CK2 21DQ1061A4101SA2141DQ15181VDDQ221CK222DQ1162VDDQ102NC,TEST1142VSS182A3222VSS23VSS63A2103VSS143DQ20183A1223DM624DQ1664VDD104DQS6144DQ21184VDD224NC25DQ1765VSS105DQS6145VSS185CK0225VSS26VSS66VSS106VSS146DM2186CK0226DQ5427DQS267VDD107DQ50147NC187VDD227DQ5528DQS268NC108DQ51148VSS188A0228VSS29VSS69VDD109VSS149DQ22189VDD229DQ6030DQ1870A10/AP110DQ56150DQ23190BA1230DQ6131DQ1971BA0111DQ57151VSS191VDDQ231VSS32VSS72VDDQ112VSS152DQ28192RAS232DM733DQ2473WE113DQS7153DQ29193S0233NC34DQ2574CAS114DQS7154VSS194VDDQ234VSS35VSS75VDDQ115VSS155DM3195ODT0235DQ6236DQS376S1116DQ58156NC196A13236DQ6337DQS377ODT1117DQ59157VSS197VDD237VSS38VSS78VDDQ118VSS158DQ30198VSS238VDDSPD 39DQ2679VSS119SDA159DQ31199DQ36239SA040DQ2780DQ32120SCL160VSS200DQ37240SA1DDR2内存引脚Front BackPin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol1VREF31DQ1961A491VSS121VSS151VSS181VDDQ211DM5/DQS14 2VSS32VSS62VDDQ92DQS5#122DQ4152DQ28182A3212NC/DQS14# 3DQ033DQ2463A293DQS5123DQ5153DQ29183A1213VSS4DQ134DQ2564VDD94VSS124VSS154VSS184VDD214DQ465VSS35VSS65VSS95DQ42125DM0/DQS9155DM3/DQS12185CK0215DQ476DQS0#36DQS3#66VSS96DQ43126NC/DQS9#156NC/DQS12#186CK0#216VSS7DQS037DQS367VDD97VSS127VSS157VSS187VDD217DQ528VSS38VSS68PAR_IN98DQ48128DQ6158DQ30188A0218DQ539DQ239DQ2669VDD99DQ49129DQ7159DQ31189VDD219VSS10DQ340DQ2770A10/AP100VSS130VSS160VSS190BA1220RFU11VSS41VSS71BA0101SA2131DQ12161CB4191VDDQ221RFU12DQ842CB072VDDQ102NC132DQ13162CB5192RAS#222VSS13DQ943CB173WE#103VSS133VSS163VSS193S0#223DM6/DQS15 14VSS44VSS74CAS#104DQS6#134DM1/DQS10164DM8/DQS17194VDDQ224NC/DQS15# 15DQS1#45DQS8#75VDDQ105DQS6135NC/DQS10#165NC/DQS17#195ODT0225VSS16DQS146DQS876S1#106VSS136VSS166VSS196NC/A13226DQ5417VSS47VSS770DT1107DQ50137RFU167CB6197VDD227DQ5518RESET#48CB278VDDQ108DQ51138RFU168CB7198VSS228VSS19NC49CB379VSS109VSS139VSS169VSS199DQ36229DQ6020VSS50VSS80DQ32110DQ56140DQ14170VDDQ200DQ37230DQ6121DQ1051VDDQ81DQ33111DQ57141DQ15171CKE1201VSS231VSS22DQ1152CKE082VSS112VSS142VSS172VDD202DM4/DQS13232DM7/DQS16 23VSS53VDD83DQS4#113DQS7#143DQ20173NC203NC/DQS13#233NC/DQS16# 24DQ1654NC/BA284DQS4114DQS7144DQ21174NC204VSS234VSS25DQ1755ERR_OUT85VSS115VSS145VSS175VDDQ205DQ38235DQ6226VSS56VDDQ86DQ34116DQ58146DM2/DQS11176A12206DQ39236DQ6327DQS2#57A1187DQ35117DQ59147NC/DQS11#177A9207VSS237VSS28DQS258A788VSS118VSS148VSS178VDD208DQ44238VDDSPD29VSS59VDD89DQ40119SDA149DQ22179A8209DQ45239SA030DQ1860A590DQ41120SCL150DQ23180A6210VSS240SA1Note:Pin196is NC for512MB,or A13for1GB and2GB;pin54is NC for512MB and1GB,or BA2for2GB.Pin DescriptionsPin numbers may not correlate with symbols;refer to Pin Assignment table above for more information.Pin Numbers Symbol Type Description195ODT0Input On-Die Termination:ODT(registered HIGH)enables termination resistance internal to the DDR2SDRAM.When enabled,ODT is only applied to each of the following pins:DQ,DQS,DQS#,RDQS,RDQS#,CB,and DM.The ODT input will be ignored if disabled via the LOAD MODE command.185,186CK0,CK0#Input Clock:CK and CK#are differential clock inputs.All address and control input signals are sampled on thecrossing of the positive edge of CK and negative edge of CK#.Output data(DQs and DQS/DQS#)isreferenced to the crossings of CK and CK#.52CKE0Input Clock Enable:CKE(registered HIGH)activates and CKE(registered LOW)deactivates clocking circuitry onthe DDR2SDRAM.The specific circuitry that is enabled/disabled is dependent on the DDR2SDRAMconfiguration and operating mode.CKE LOW provides PRECHARGE POWER-DOWN and SELFREFRESH operations(all device banks idle),or ACTIVE POWERDOWN(row ACTIVE in any device bank).CKE is synchronous for POWER-DOWN entry,POWER-DOWN exit,output disable,and for SELFREFRESH entry.CKE is asynchronous for SELF REFRESH exit.Input buffers(excluding CK,CK#,CKE,and ODT)are disabled during POWER-DOWN.Input buffers(excluding CKE)are disabled during SELFREFRESH.CKE is an SSTL_18input but will detect a LVCMOS LOW level once VDD is applied duringfirst power-up.After Vref has become stable during the power on and initialization sequence,it must bemaintained for proper operation of the CKE receiver.For proper self-refresh operation VREF must bemaintained to this input.193S0#Input Chip Select:S#enables(registered LOW)and disables(registered HIGH)the command decoder.Allcommands are masked when S#is registered HIGH.S#provides for external rank selection on systems withmultiple ranks.S#is considered part of the command code.73,74,192RAS#,CAS#,Input Command Inputs:RAS#,CAS#,and WE#(along with S#)define the command being entered.WE#54(2GB),71,190BA0,BA1,BA2(2GB)Input Bank Address Inputs:BA0–BA1/BA2define to which device bank an ACTIVE,READ,WRITE,or PRECHARGE command is being applied.BA0–BA1define which mode register including MR,EMR,EMR(2),and EMR(3)is loaded during the LOAD MODE command.57,58,60,61,63,70,176,177,179,180, 182,183,188,196(1GB,2GB)A0–A12(512MB)A0–A13(1GB,2GB)Input Address Inputs:Provide the row address for ACTIVE commands,and the column address and auto prechargebit(A10)for Read/Write commands,to select one location out of the memory array in the respective bank.A10sampled during a PRECHARGE command determines whether the PRECHARGE applies to one devicebank(A10LOW,device bank selected by BA0–BA1/BA2)or all device banks(A10HIGH).The addressinputs also provide the op-code during a LOAD MODE command.3,4,9,10,12,13,21,22,24,25,30,31,33,34,39,40,80,81,86,87,89,90,95,96,98,99,107,108,110,111,116,117,122,123,128,129,131,132,140,141,143,144,149,150,152,153,158,159,199,200,205,206,208,209,214,215,217,218,226,227,229,230,235,236DQ0–DQ63I/O Data Input/Output:Bidirectional data bus.6,7,15,16,27,28,36,37,45,46,83,84, 92,93,104,105,113,114,126,135,147, 156,165,203,212,224,233125,134,146, 155,164,202,211,223,232DQS0–DQS8,DQS0#–DQS17#,DM0–DM8(DQS9–DQS17)I/O Data Strobe:Output with read data,input with write data for source synchronous operation.Edge-alignedwith read data,center aligned with write data.DQS#is only used when differential data strobe mode isenabled via the LOAD MODE command.Input Data Mask:DM is an input mask signal for write data.Inputdata is masked when DM is sampled HIGH along with that input data during a WRITE access.DM issampled on both edges of DQS.Although DM pins are input-only,the DM loading is designed to match thatof DQ and DQS pins.If RDQS is disabled,DQS0–DQS17become DM0–DM8and DQS9#–DQS17#are notused.42,43,48,49,161,162,167,168CB0–CB7I/O Check Bits.68PAR_IN Input Parity bit for the address and control bus.55ERR_OUT Output Parity error found on the address and control bus.120SCL Input Serial Clock for Presence-Detect:SCL is used to synchronize the presence-detect data transfer to and fromthe module.101,239,240SA0–SA2Input Presence-Detect Address Inputs:These pins are used to configure the presence-detect device.119SDA I/O Serial Presence-Detect Data:SDA is a bidirectional pin used to transfer addresses and data into and out of thepresence-detect portion of the module.18RESET#Input Asynchronously forces all registered outputs LOW when RESET#is LOW.This signal can be used duringpower up to ensure that CKE is LOW and DQs are High-Z.VDD Supply Power Supply:1.8V±0.1V.53,59,64,67,69,172,178,184,187,189,197,51,56,62,72,75,78,170,175,181,191,VDDQ Supply DQ Power Supply:1.8V±0.1V.194,1VREF Supply SSTL_18reference voltage.VSS Supply Ground.2,5,8,11,14,17,20,23,26,29,32,35,38,41,44,47,50,65,66,79,82,85,88,91,94,97,100,103,106,109,112,115,118,121,124,127,130,133,136,139,142,145,148,151,154,157,160,163,166,169,198,201,204,207,210,213,216,219,222,225,228,231,234,237238VDDSPD Supply Serial EEPROM positive power supply:+1.7V to+3.6V.19,54(512MB,1GB),76,77,102,171,NC—No Connect:These pins should be left unconnected.196(512MB),173,174,137,138,220,221RFU—Reserved for future use.。

SD,DDR,DDR2引脚定义

SD内存插槽及测试点一、实物图上图中,黑色插槽就是SD内存插槽二、测试点SD内存插槽测试点:1个供电、4个时钟、6个信号测试点VCC:供电测试点,正常电压3.3V,由场管或橙色线提供CLK0、CLK1、CLK2、CLK3:时钟测试点,频率66/100/133MHZ,电压1.1V-1.6V,由北桥或时钟芯片提供6个信号测试点:CAS#:列选信号RAS#:行选信号/WE#:允许信号(高电平允许读,低电平允许写)/CS#:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压DDR内存插槽及测试点一、实物图上图就是DDR内存插槽实物图二、测试点DDR内存插槽测试点:2个供电、6个时钟、6个信号测试点VCC=2.5V,1.25V:供电测试点CLK0、CLK1、CLK2、CLK3、CLK4、CLK5:时钟测试点,频率266/333/400MHZ,电压1.1V-1. 6V,如果主板有两块时钟芯片,内存时钟由靠近内存的时钟芯片提供;如果只有一个时钟芯片,内存的时钟由北桥提供6个信号测试点:CAS:列选信号RAS:行选信号WE:允许信号(高电平允许读,低电平允许写)CS:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压D58、D56、D18等:是数据线,对地打阻值正常值300-800DDR2内存插槽测试点2009-10-2 10:37:43文/xiaowang 出处:电脑维修家园DDR2内存插槽实物图如下:1、时钟信号点,共有8个时钟信号点,分别位于52、137、138、171、185、186、220、221针脚,正常进,时钟信号点工作电压为1.1V。

2、电压信号点,DDR2内存插槽有2种电压,其中238针脚为3.3V供电脚,51、53、56、59、62、64、69、72、75、78、170、172、175、1 78、181、187、189、191、194针脚为1.8V供电脚。

DE2-115所有引脚分配表

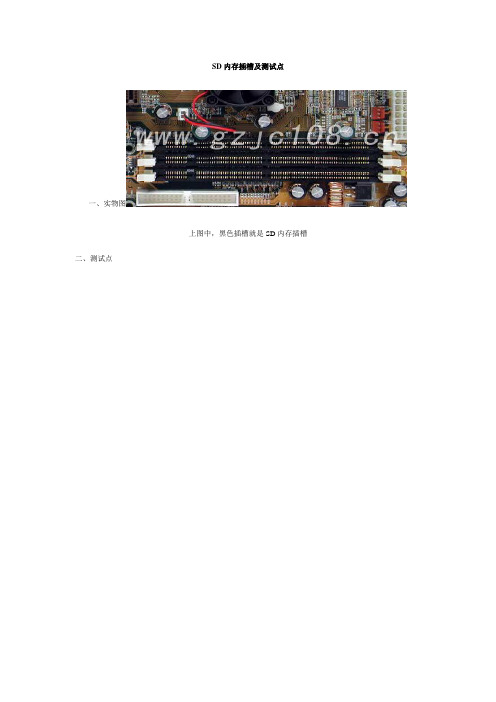

表1 拨动开关引脚配置

表2 按钮开关引脚配置

表3 LED 引脚配置

表4 七段数码管引脚配置

表5 时钟信号引脚配置信息

表6 LCD 模块引脚配置

表7 HSMC 接口引脚配置

表8 GPIO 引脚配置信息

表9 扩展接口引脚配置信息

表10 ADV7123 引脚配置

表11 音频编解码芯片引脚配置

表12 RS-232 引脚配置

表13 PS/2 引脚配置

表14 千兆以太网芯片引脚配置

表15 TV 解码芯片引脚配置

表16 USB (ISP1362)引脚配置

表17 IR 引脚配置

表18 SRAM 引脚配置

表19 SDRAM 引脚配置

表20 SDRAM 引脚配置

表21 Flash 引脚配置

表22 EEPROM 引脚配置

表23 SD 卡插槽引脚配置。

quartusII13_NiosII_Qsys下CFI flash程序下载教程(DE2_115)

NiosII Qsys下CFI flash程序下载教程(DE2_115)软件平台:OS: Windows 7 Ultimate sp1(64 bit)Altera software: Quartus II:13 suite( Qsys, Nios II software for Eclipse)硬件平台:DE2-115目标:将Nios程序放入flash中,flash是非易失性存储器,掉电后数据不会丢失,因此可以将程序放入flash中,使系统从flash中启动,成为独立系统。

在开发阶段我们可以使用JTAG 进行程序下载,而一旦进入实用阶段,则必须将程序固化到ROM中,而此时的flash可正好充当ROM的角色。

值得注意的是,一定要区分FPGA的配置和NIOS程序的配置。

FPGA本身的配置(i.e., 在Quartus中完成的部分,硬件的描述部分)可以通过EPCS64芯片通过AS模式写入,无需另外在NIOS中大费周章(虽然NIOS可以完成这个工作,但是没有必要)。

本文主要的任务是将NIOS程序(软件部分,由eclipse完成)下载到flash中。

另外值得关注的是,由于Quartus的改版,原有的很多教程显得不适用。

比如新版的Qsys器件列表中根本就找不到CFI控制器,对于flash芯片的管脚连接也不对应,时序的参数也很难找到,这是最大的难点。

具体步骤:一 准备工作:生成一个正常的NIOS CPU,包括时钟源,nios核等等,这些部分与本文关系不大,大家可以参考其他教程。

最下如下图二 添加CFI的相关器件首先了解原理,下图来自QuartusII 的handbook 11-6此图清楚的表明了存储器的连接方式,值得注意的是,如果有两个及其以上的存储器,则必须添加pin sharer,如果只是单独的添加Flash,是可以不需要pin sharer的。

了解原理之后,开始添加:1)添加Generic Tri-State Bridge然后直接选择添加,没有参数需要修改 2)添加Generic Tri-State Controller然后修改参数,先点击右边的CFI配置,在此基础上修改: 对于DE2-115,修改后signal Selection页面如下:主要是Adress width 和Data Width。

EDA实验指导(基于DE2-115)

EDA实验指导(基于DE2-115)信息科学与工程学院电子信息系徐雯娟编著EDA实验指导(基于DE2-115)实验一:一位全加器设计——原理图设计初步以下拟通过1位全加器的设汁,介绍原理图输入的基木设计方法。

软件基于quartus213.0版本。

1位全加器可以用两个半加器及一个或门连接而成,因此需要先完成半加器的设计。

下面将给出使用原理图输入的方法进行底层元件设计和层次化设计的主要步骤。

1.新建工程点击两次“next”后,如下图。

假设本项设计的文件夹取名为adder4,路径为:d:\ex\adder4(建议大家把所有的EDA实验都放在一个文件夹中,如ex,然后为每个实验在这个文件夹中新建一个文件夹,以实验名命名,如adder4)。

选择目标芯片:cycloneIVE系列的EP4CE11529C7,如图:直接next,之后到达完成界面,这里会看见关于整个工程的一些信息,核对一下是否正确,然后点击“finish”。

此时界面上会出现顶层文件名和项目名:2.新建原理图文件原理图编辑输入流程如下:(1)新建原理图文件。

打开QuartusII,选菜单“File”一“New”,在弹出的“New-”对话框中选择“Design Files”的原理图文件编辑输入项“Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

(2)在编辑窗中调入元件,完成半加器的原理图输入。

点击按纽“”或直接双击原理图空白处,从“Symbol”窗中选择需要的符号,或者直接在“name”文本框中键入元件名,如“and2”为2输入与门,点OK按钮,即将元件调入原理图编辑窗中。

例如为了设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。

并如图用点击拖动的方法连接好电路。

然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b,co和s。

附录DE2-115引脚表

SW[11]PIN_AB24Slide Switch[11]Depending on JP7 SW[12]PIN_AB23Slide Switch[12]Depending on JP7 SW[13]PIN_AA24Slide Switch[13]Depending on JP7 SW[14]PIN_AA23Slide Switch[14]Depending on JP7 SW[15]PIN_AA22Slide Switch[15]Depending on JP7 SW[16]PIN_Y24Slide Switch[16]Depending on JP7 SW[17]PIN_Y23Slide Switch[17]Depending on JP7表 2 按钮开关引脚配置Signal Name FPGA Pin No.Description I/O Standard KEY[0]PIN_M23Push-button[0]Depending on JP7KEY[1]PIN_M21Push-button[1]Depending on JP7KEY[2]PIN_N21Push-button[2]Depending on JP7KEY[3]PIN_R24Push-button[3]Depending on JP7表 3 LED引脚配置Signal Name FPGA Pin No.Description I/OS tandard LEDR[0]PIN_G19LED Red[0] 2.5VLEDR[1]PIN_F19LED Red[1] 2.5VLEDR[2]PIN_E19LED Red[2] 2.5VLEDR[3]PIN_F21LED Red[3] 2.5VLEDR[4]PIN_F18LED Red[4] 2.5VLEDR[5]PIN_E18LED Red[5] 2.5VLEDR[6]PIN_J19LED Red[6] 2.5VLEDR[7]PIN_H19LED Red[7] 2.5V LEDR[8]PIN_J17LED Red[8] 2.5V LEDR[9]PIN_G17LED Red[9] 2.5V LEDR[10]PIN_J15LED Red[10] 2.5V LEDR[11]PIN_H16LED Red[11] 2.5V LEDR[12]PIN_J16LED Red[12] 2.5V LEDR[13]PIN_H17LED Red[13] 2.5V LEDR[14]PIN_F15LED Red[14] 2.5V LEDR[15]PIN_G15LED Red[15] 2.5V LEDR[16]PIN_G16LED Red[16] 2.5V LEDR[17]PIN_H15LED Red[17] 2.5V LEDG[0]PIN_E21LED Green[0] 2.5V LEDG[1]PIN_E22LED Green[1] 2.5V LEDG[2]PIN_E25LED Green[2] 2.5V LEDG[3]PIN_E24LED Green[3] 2.5V LEDG[4]PIN_H21LED Green[4] 2.5V LEDG[5]PIN_G20LED Green[5] 2.5V LEDG[6]PIN_G22LED Green[6] 2.5V LEDG[7]PIN_G21LED Green[7] 2.5V LEDG[8]PIN_F17LED Green[8] 2.5V 表 4 七段数码管引脚配置Signal Na me FPGA Pin No.Description I/O StandardHEX0[0]PIN_G18Seven Segment Digit 0[0]2.5VHEX0[1]PIN_F22Seven Segment Digit 0[1] 2.5VHEX0[2]PIN_E17Seven Segment Digit 0[2] 2.5VHEX0[3]PIN_L26Seven Segment Digit 0[3]Depending onJP7HEX0[4]PIN_L25Seven Segment Digit 0[4]Depending on JP7HEX0[5]PIN_J22Seven Segment Digit 0[5]Depending on JP7HEX0[6]PIN_H22Seven Segment Digit 0[6]Depending on JP7HEX1[0]PIN_M24Seven Segment Digit 1[0]Depending on JP7HEX1[1]PIN_Y22Seven Segment Digit 1[1]Depending on JP7HEX1[2]PIN_W21Seven Segment Digit 1[2]Depending on JP7HEX1[3]PIN_W22Seven Segment Digit 1[3]Depending onJP7HEX1[4]PIN_W25Seven Segment Digit 1[4]Depending onJP7HEX1[5]PIN_U23Seven Segment Digit 1[5]Depending onJP7HEX1[6]PIN_U24Seven Segment Digit 1[6]Depending onJP7HEX2[0]PIN_AA25Seven Segment Digit 2[0]Depending onJP7HEX2[1]PIN_AA26Seven Segment Digit 2[1]Depending onJP7HEX2[2]PIN_Y25Seven Segment Digit 2[2]Depending on JP7HEX2[3]PIN_W26Seven Segment Digit 2[3]Depending on JP7HEX2[4]PIN_Y26Seven Segment Digit 2[4]Depending on JP7HEX2[5]PIN_W27Seven Segment Digit 2[5]Depending on JP7HEX2[6]PIN_W28Seven Segment Digit 2[6]Depending on JP7HEX3[0]PIN_V21Seven Segment Digit 3[0]Depending on JP7HEX3[1]PIN_U21Seven Segment Digit 3[1]Depending on JP7HEX3[2]PIN_AB20Seven Segment Digit 3[2]Depending onJP6HEX3[3]PIN_AA21Seven Segment Digit 3[3]Depending onJP6HEX3[4]PIN_AD24Seven Segment Digit 3[4]Depending onJP6HEX3[5]PIN_AF23Seven Segment Digit 3[5]Depending onJP6HEX3[6]PIN_Y19Seven Segment Digit 3[6]Depending onJP6HEX4[0]PIN_AB19Seven Segment Digit 4[0]Depending onJP6HEX4[1]PIN_AA19Seven Segment Digit 4[1]Depending on JP6HEX4[2]PIN_AG21Seven Segment Digit 4[2]Depending on JP6HEX4[3]PIN_AH21Seven Segment Digit 4[3]Depending on JP6HEX4[4]PIN_AE19Seven Segment Digit 4[4]Depending on JP6HEX4[5]PIN_AF19Seven Segment Digit 4[5]Depending on JP6HEX4[6]PIN_AE18Seven Segment Digit 4[6]Depending on JP6HEX5[0]PIN_AD18Seven Segment Digit 5[0]Depending on JP6HEX5[1]PIN_AC18Seven Segment Digit 5[1]Depending onJP6HEX5[2]PIN_AB18Seven Segment Digit 5[2]Depending onJP6HEX5[3]PIN_AH19Seven Segment Digit 5[3]Depending onJP6HEX5[4]PIN_AG19Seven Segment Digit 5[4]Depending onJP6HEX5[5]PIN_AF18Seven Segment Digit 5[5]Depending onJP6HEX5[6]PIN_AH18Seven Segment Digit 5[6]Depending onJP6HEX6[0]PIN_AA17Seven Segment Digit 6[0]Depending on JP6HEX6[1]PIN_AB16Seven Segment Digit 6[1]Depending on JP6HEX6[2]PIN_AA16Seven Segment Digit 6[2]Depending on JP6HEX6[3]PIN_AB17Seven Segment Digit 6[3]Depending on JP6HEX6[4]PIN_AB15Seven Segment Digit 6[4]Depending on JP6HEX6[5]PIN_AA15Seven Segment Digit 6[5]Depending on JP6HEX6[6]PIN_AC17Seven Segment Digit 6[6]Depending on JP6HEX7[0]PIN_AD17Seven Segment Digit 7[0]Depending onJP6HEX7[1]PIN_AE17Seven Segment Digit 7[1]Depending onJP6HEX7[2]PIN_AG17Seven Segment Digit 7[2]Depending onJP6HEX7[3]PIN_AH17Seven Segment Digit 7[3]Depending onJP6HEX7[4]PIN_AF17Seven Segment Digit 7[4]Depending on JP6HEX7[5]PIN_AG18Seven Segment Digit 7[5]Depending on JP6HEX7[6]PIN_AA14Seven Segment Digit 7[6] 3.3V表 5 时钟信号引脚配置信息Signal NameFPGA Pin N o.DescriptionI/O StandardCLOCK_50PIN_Y250 MHz clock input3.3V CLOCK2_50PIN_AG1450 MHz clock input 3.3V CLOCK3_50PIN_AG1550 MHz clock input Depending onJP6SMA_CLKOUT PIN_AE23External (SMA) clock o utputDepending onJP6SMA_CLKINPIN_AH14External (SMA) clock in put3.3V表 6 LCD 模块引脚配置Signal NameFPGAPinNo.DescriptionI/OLCD_DATA[7]PIN_M5LCD Data[7]StandardLCD_DATA[6]PIN_M3LCD Data[6]3.3VLCD_DATA[5]PIN_K2LCD Data[5]3.3VLCD_DATA[4]PIN_K1LCD Data[4]3.3VLCD_DATA[3]PIN_K7LCD Data[3]3.3VLCD_DATA[2]PIN_L2LCD Data[2]3.3VLCD_DATA[1]PIN_L1LCD Data[1]3.3VLCD_DATA[0]PIN_L3LCD Data[0]3.3VLCD_ENPIN_L4LCD Enable3.3VLCD_RWPIN_M1LCD Read/Write Select, 0 = Write, 1 = Read3.3VLCD_RSPIN_M2LCD Command/Data S elect, 0 = Command, 1= Data3.3VLCD_ONPIN_L5LCD Power ON/OFF3.3V LCD_BLONPIN_L6LCD Back Light ON/OF F 3.3V表 7 HSMC 接口引脚配置Signal NameFPGA Pin No.DescriptionI/O StandardHSMC_CLKIN0PIN_AH15Dedicated clock inputDepending on JP6HSMC_CLKIN_N1PIN_J28LVDS RX or C MOS I/O or diff erential clock inputDepending on JP7HSMC_CLKIN_N2PIN_Y28LVDS RX or C MOS I/O or diff erential clock inDepending on JP7putHSMC_CLKIN_P1PIN_J27LVDS RX or C MOS I/O or diff erential clock inputDepending on JP7HSMC_CLKIN_P2PIN_Y27LVDS RX or C MOS I/O or diff erential clock in put Depending on JP7HSMC_CLKOUT0PIN_AD28Dedicated clock output Depending on JP7HSMC_CLKOUT_N1PIN_G24LVDS TX or C MOS I/O or diff erential clock in put/output Depending on J P7HSMC_CLKOUT_N2PIN_V24LVDS TX or C MOS I/O or diff erential clock in put/output Depending on J P7HSMC_CLKOUT_P1PIN_G23LVDS TX or C MOS I/O or diff erential clock input/outputDepending on J P7HSMC_CLKOUT_P2PIN_V23LVDS TX or C MOS I/O or diff erential clock input/outputDepending on JP7HSMC_D[0]PIN_AE26LVDS TX or CDepending on JMOS I/O P7HSMC_D[1]PIN_AE28LVDS TX or CMOS I/O Depending on J P7HSMC_D[2]PIN_AE27LVDS TX or CMOS I/O Depending on J P7HSMC_D[3]PIN_AF27LVDS TX or CMOS I/O Depending on J P7HSMC_RX_D_N[0]PIN_F25LVDS RX bit 0n or CMOS I/O Depending on J P7HSMC_RX_D_N[1]PIN_C27LVDS RX bit 1n or CMOS I/O Depending on J P7HSMC_RX_D_N[2]PIN_E26LVDS RX bit 2n or CMOS I/O Depending on J P7HSMC_RX_D_N[3]PIN_G26LVDS RX bit 3n or CMOS I/O Depending on J P7HSMC_RX_D_N[4]PIN_H26LVDS RX bit 4n or CMOS I/O Depending on J P7HSMC_RX_D_N[5]PIN_K26LVDS RX bit 5n or CMOS I/O Depending on J P7HSMC_RX_D_N[6]PIN_L24LVDS RX bit 6n or CMOS I/O Depending on J P7HSMC_RX_D_N[7]PIN_M26LVDS RX bit 7n or CMOS I/O Depending on J P7HSMC_RX_D_N[8]PIN_R26LVDS RX bit 8n or CMOS I/O Depending on J P7HSMC_RX_D_N[9]PIN_T26LVDS RX bit 9n or CMOS I/O Depending on J P7HSMC_RX_D_N[10]PIN_U26LVDS RX bit 10n or CMOS I/O Depending on J P7HSMC_RX_D_N[11]PIN_L22LVDS RX bit 11n or CMOS I/O Depending on J P7HSMC_RX_D_N[12]PIN_N26LVDS RX bit 12n or CMOS I/O Depending on J P7HSMC_RX_D_N[13]PIN_P26LVDS RX bit 13n or CMOS I/O Depending on J P7HSMC_RX_D_N[14]PIN_R21LVDS RX bit 14n or CMOS I/O Depending on J P7HSMC_RX_D_N[15]PIN_R23LVDS RX bit 15n or CMOS I/O Depending on J P7HSMC_RX_D_N[16]PIN_T22LVDS RX bit 16n or CMOS I/O Depending on J P7HSMC_RX_D_P[0]PIN_F24LVDS RX bit 0or CMOS I/O Depending on J P7HSMC_RX_D_P[1]PIN_D26LVDS RX bit 1or CMOS I/O Depending on J P7HSMC_RX_D_P[2]PIN_F26LVDS RX bit 2or CMOS I/O Depending on J P7HSMC_RX_D_P[3]PIN_G25LVDS RX bit 3or CMOS I/O Depending on J P7HSMC_RX_D_P[4]PIN_H25LVDS RX bit 4or CMOS I/O Depending on J P7HSMC_RX_D_P[5]PIN_K25LVDS RX bit 5or CMOS I/O Depending on J P7HSMC_RX_D_P[6]PIN_L23LVDS RX bit 6or CMOS I/O Depending on J P7HSMC_RX_D_P[7]PIN_M25LVDS RX bit 7or CMOS I/O Depending on J P7HSMC_RX_D_P[8]PIN_R25LVDS RX bit 8or CMOS I/O Depending on J P7HSMC_RX_D_P[9]PIN_T25LVDS RX bit 9or CMOS I/O Depending on J P7HSMC_RX_D_P[10]PIN_U25LVDS RX bit 10 or CMOS I/O Depending on J P7HSMC_RX_D_P[11]PIN_L21LVDS RX bit 11 or CMOS I/O Depending on J P7HSMC_RX_D_P[12]PIN_N25LVDS RX bit 12 or CMOS I/O Depending on J P7HSMC_RX_D_P[13]PIN_P25LVDS RX bit 13 or CMOS I/O Depending on J P7HSMC_RX_D_P[14]PIN_P21LVDS RX bit 14 or CMOS I/O Depending on J P7HSMC_RX_D_P[15]PIN_R22LVDS RX bit 15 or CMOS I/O Depending on J P7HSMC_RX_D_P[16]PIN_T21LVDS RX bit 16 or CMOS I/O Depending on J P7HSMC_TX_D_N[0]PIN_D28LVDS TX bit 0n or CMOS I/O Depending on J P7HSMC_TX_D_N[1]PIN_E28LVDS TX bit 1n or CMOS I/O Depending on J P7HSMC_TX_D_N[2]PIN_F28LVDS TX bit 2n or CMOS I/O Depending on J P7HSMC_TX_D_N[3]PIN_G28LVDS TX bit 3n or CMOS I/O Depending on J P7HSMC_TX_D_N[4]PIN_K28LVDS TX bit 4n or CMOS I/O Depending on J P7HSMC_TX_D_N[5]PIN_M28LVDS TX bit 5n or CMOS I/O Depending on J P7HSMC_TX_D_N[6]PIN_K22LVDS TX bit 6n or CMOS I/O Depending on J P7HSMC_TX_D_N[7]PIN_H24LVDS TX bit 7n or CMOS I/O Depending on J P7HSMC_TX_D_N[8]PIN_J24LVDS TX bit 8n or CMOS I/O Depending on J P7HSMC_TX_D_N[9]PIN_P28LVDS TX bit 9n or CMOS I/O Depending on J P7HSMC_TX_D_N[10]PIN_J26LVDS TX bit 10n or CMOS I/O Depending on J P7HSMC_TX_D_N[11]PIN_L28LVDS TX bit 11n or CMOS I/Depending on J P7OHSMC_TX_D_N[12]PIN_V26LVDS TX bit 12n or CMOS I/O Depending on J P7HSMC_TX_D_N[13]PIN_R28LVDS TX bit 13n or CMOS I/O Depending on J P7HSMC_TX_D_N[14]PIN_U28LVDS TX bit 14n or CMOS I/O Depending on J P7HSMC_TX_D_N[15]PIN_V28LVDS TX bit 15n or CMOS I/O Depending on J P7HSMC_TX_D_N[16]PIN_V22LVDS TX bit 16n or CMOS I/O Depending on J P7HSMC_TX_D_P[0]PIN_D27LVDS TX bit 0or CMOS I/O Depending on J P7HSMC_TX_D_P[1]PIN_E27LVDS TX bit 1or CMOS I/O Depending on J P7HSMC_TX_D_P[2]PIN_F27LVDS TX bit 2or CMOS I/O Depending on J P7HSMC_TX_D_P[3]PIN_G27LVDS TX bit 3or CMOS I/O Depending on J P7HSMC_TX_D_P[4]PIN_K27LVDS TX bit 4or CMOS I/O Depending on J P7HSMC_TX_D_P[5]PIN_M27LVDS TX bit 5 Depending on Jor CMOS I/O P7HSMC_TX_D_P[6]PIN_K21LVDS TX bit 6or CMOS I/O Depending on J P7HSMC_TX_D_P[7]PIN_H23LVDS TX bit 7or CMOS I/O Depending on J P7HSMC_TX_D_P[8]PIN_J23LVDS TX bit 8or CMOS I/O Depending on J P7HSMC_TX_D_P[9]PIN_P27LVDS TX bit 9or CMOS I/O Depending on J P7HSMC_TX_D_P[10]PIN_J25LVDS TX bit 10 or CMOS I/O Depending on J P7HSMC_TX_D_P[11]PIN_L27LVDS TX bit 11 or CMOS I/O Depending on J P7HSMC_TX_D_P[12]PIN_V25LVDS TX bit 12 or CMOS I/O Depending on J P7HSMC_TX_D_P[13]PIN_R27LVDS TX bit 13 or CMOS I/O Depending on J P7HSMC_TX_D_P[14]PIN_U27LVDS TX bit 14 or CMOS I/O Depending on J P7HSMC_TX_D_P[15]PIN_V27LVDS TX bit 15 or CMOS I/O Depending on J P7HSMC_TX_D_P[16]PIN_U22LVDS TX bit 16 or CMOS I/O Depending on J P7表8 GPIO 引脚配置信息Signal Nam e FPGA Pin No.Description I/O StandardGPIO[0]PIN_AB22GPIO Connection DATA[0]Depending on JP 6GPIO[1]PIN_AC15GPIO Connection DATA[1]Depending on JP 6GPIO[2]PIN_AB21GPIO Connection DATA[2]Depending on JP 6GPIO[3]PIN_Y17GPIO Connection DATA[3]Depending on JP 6GPIO[4]PIN_AC21GPIO Connection DATA[4]Depending on JP 6GPIO[5]PIN_Y16GPIO Connection DATA[5]Depending on JP 6GPIO[6]PIN_AD21GPIO Connection DATA[6]Depending on JP 6GPIO[7]PIN_AE16GPIO Connection DATA[7]Depending on JP 6GPIO[8]PIN_AD15GPIO Connection DATA[8]Depending on JP 6GPIO[9]PIN_AE15GPIO Connection DATA[9]Depending on JP 6GPIO[10]PIN_AC19GPIO Connection DATA[10]Depending on JP 6GPIO[11]PIN_AF16GPIO Connection DATA[11]Depending on JP 6GPIO[12]PIN_AD19GPIO Connection DATA[12]Depending on JP 6GPIO[13]PIN_AF15GPIO Connection DATA[13]Depending on JP 6GPIO[14]PIN_AF24GPIO Connection DATA[14]Depending on JP 6GPIO[15]PIN_AE21GPIO Connection DATA[15]Depending on JP 6GPIO[16]PIN_AF25GPIO Connection DATA[16]Depending on JP 6GPIO[17]PIN_AC22GPIO Connection DATA[17]Depending on JP 6GPIO[18]PIN_AE22GPIO Connection DATA[18]Depending on JP 6GPIO[19]PIN_AF21GPIO Connection DATA[19]Depending on JP 6GPIO[20]PIN_AF22GPIO Connection DATA[20]Depending on JP 6GPIO[21]PIN_AD22GPIO Connection DATA[21]Depending on JP 6GPIO[22]PIN_AG25GPIO Connection DATA[22]Depending on JP 6GPIO[23]PIN_AD25GPIO Connection DATA[23]Depending on JP 6GPIO[24]PIN_AH25GPIO Connection DATA[24]Depending on JP 6GPIO[25]PIN_AE25GPIO Connection DATA[25]Depending on JP 6GPIO[26]PIN_AG22GPIO Connection DATA[26]Depending on JP 6GPIO[27]PIN_AE24GPIO Connection DATA[27]Depending on JP 6GPIO[28]PIN_AH22GPIO Connection DATA[28]Depending on JP 6GPIO[29]PIN_AF26GPIO Connection DATA[29]Depending on JP 6GPIO[30]PIN_AE20GPIO Connection DATA[30]Depending on JP 6GPIO[31]PIN_AG23GPIO Connection DATA[31]Depending on JP 6GPIO[32]PIN_AF20GPIO Connection DATA[32]Depending on JP 6GPIO[33]PIN_AH26GPIO Connection DATA[33]Depending on JP 6GPIO[34]PIN_AH23GPIO Connection DATA[34]Depending on JP 6GPIO[35]PIN_AG26GPIO Connection DATA[35]Depending on JP 6表9 扩展接口引脚配置信息Signal Name FPGA Pin No.Description I/O Standard EX_IO[0]PIN_J10Extended IO[0] 3.3VEX_IO[1]PIN_J14Extended IO[1] 3.3VEX_IO[2]PIN_H13Extended IO[2] 3.3VEX_IO[3]PIN_H14Extended IO[3] 3.3VEX_IO[4]PIN_F14Extended IO[4] 3.3VEX_IO[5]PIN_E10Extended IO[5] 3.3VEX_IO[6]PIN_D9Extended IO[6] 3.3V表10 ADV7123 引脚配置Signal Name FPGA Pin No.Description I/O Standard VGA_R[0]PIN_E12VGA Red[0] 3.3VVGA_R[1]PIN_E11VGA Red[1] 3.3VVGA_R[2]PIN_D10VGA Red[2] 3.3VVGA_R[3]PIN_F12VGA Red[3] 3.3VVGA_R[4]PIN_G10VGA Red[4] 3.3VVGA_R[5]PIN_J12VGA Red[5] 3.3VVGA_R[6]PIN_H8VGA Red[6] 3.3VVGA_R[7]PIN_H10VGA Red[7] 3.3VVGA_G[0]PIN_G8VGA Green[0] 3.3VVGA_G[1]PIN_G11VGA Green[1] 3.3VVGA_G[2]PIN_F8VGA Green[2] 3.3VVGA_G[3]PIN_H12VGA Green[3] 3.3VVGA_G[4]PIN_C8VGA Green[4] 3.3VVGA_G[5]PIN_B8VGA Green[5] 3.3VVGA_G[6]PIN_F10VGA Green[6] 3.3VVGA_G[7]PIN_C9VGA Green[7] 3.3VVGA_B[0]PIN_B10VGA Blue[0] 3.3VVGA_B[1]PIN_A10VGA Blue[1] 3.3VVGA_B[2]PIN_C11VGA Blue[2] 3.3VVGA_B[3]PIN_B11VGA Blue[3] 3.3VVGA_B[4]PIN_A11VGA Blue[4] 3.3VVGA_B[5]PIN_C12VGA Blue[5] 3.3VVGA_B[6]PIN_D11VGA Blue[6] 3.3VVGA_B[7]PIN_D12VGA Blue[7] 3.3VVGA_CLK PIN_A12VGA Clock 3.3VVGA_BLANK_N PIN_F11VGA BLANK 3.3VVGA_HS PIN_G13VGA H_SYNC 3.3VVGA_VS PIN_C13VGA V_SYNC 3.3VVGA_SYNC_N PIN_C10VGA SYNC 3.3V表11 音频编解码芯片引脚配置Signal Name FPGA Pin No.Description I/O Standard3.3VAUD_ADCLRCK PIN_C2Audio CODEC ADC LR ClockAUD_ADCDAT PIN_D2Audio CODEC ADC Data 3.3V3.3VAUD_DACLRCK PIN_E3Audio CODEC DAC LR ClockAUD_DACDAT PIN_D1Audio CODEC DAC Data 3.3VAUD_XCK PIN_E1Audio CODEC Chip Clock 3.3V3.3VAUD_BCLK PIN_F2Audio CODEC Bit-StreamClockI2C_SCLK PIN_B7I2C Clock 3.3VI2C_SDAT PIN_A8I2C Data 3.3V表12 RS-232 引脚配置Signal Name FPGA Pin No.Description I/O Standard UART_RXD PIN_G12UART Receiver 3.3VUART_TXD PIN_G9UART Transmitter 3.3VUART_CTS PIN_G14UART Clear to Send 3.3VUART_RTS PIN_J13UART Request to Send3.3V表13 PS/2 引脚配置Signal Name FPGA Pin No.Description I/O StandardPS2_CLK PIN_G6PS/2 Clock 3.3VPS2_DAT PIN_H5PS/2 Data 3.3VPS2_CLK2PIN_G5PS/2 Clock (reserved for second PS/2 device)3.3VPS2_DAT2PIN_F5PS/2 Data (reserved for second PS/2 device)3.3V表14 千兆以太网芯片引脚配置Signal Name FPGA Pin No.Description I/O StandardE NET0_GTX_CLK PIN_A17GMII Transmit Clock 12.5VENET0_INT_N PIN_A21Interrupt open drain2.5Voutput 13.3V ENET0_LINK100PIN_C14Parallel LED outputof 100BASE-TX link12.5V ENET0_MDC PIN_C20Management data clock reference 1ENET0_MDIO PIN_B21Management data 12.5V2.5V ENET0_RST_N PIN_C19Hardware reset signal 1ENET0_RX_CLK PIN_A15GMII and MII receiv2.5Ve clock 12.5V ENET0_RX_COL PIN_E15GMII and MII collision 1ENET0_RX_CRS PIN_D15GMII and MII carrie2.5Vr sense 12.5V ENET0_RX_DATA[0]PIN_C16GMII and MII receive data[0] 12.5V ENET0_RX_DATA[1]PIN_D16GMII and MII receive data[1] 12.5V ENET0_RX_DATA[2]PIN_D17GMII and MII receive data[2] 12.5V ENET0_RX_DATA[3]PIN_C15GMII and MII receive data[3] 12.5V ENET0_RX_DV PIN_C17GMII and MII receive data valid 1ENET0_RX_ER PIN_D18GMII and MII receiv2.5Ve error 1ENET0_TX_CLK PIN_B17MII transmit clock 12.5V ENET0_TX_DATA[0]PIN_C18MII transmit data[0]2.5V12.5V ENET0_TX_DATA[1]PIN_D19MII transmit data[1]12.5V ENET0_TX_DATA[2]PIN_A19MII transmit data[2]12.5V ENET0_TX_DATA[3]PIN_B19MII transmit data[3]12.5V ENET0_TX_EN PIN_A18GMII and MII transmit enable 12.5V ENET0_TX_ER PIN_B18GMII and MII transmit error 1ENET1_GTX_CLK PIN_C23GMII Transmit Cloc2.5Vk 22.5V ENET1_INT_N PIN_D24Interrupt open drainoutput 22.5V ENET1_LINK100PIN_D13Parallel LED outputof 100BASE-TX link22.5V ENET1_MDC PIN_D23Management data clock reference 2ENET1_MDIO PIN_D25Management data 22.5V ENET1_RST_N PIN_D22Hardware reset sig2.5Vnal 22.5V ENET1_RX_CLK PIN_B15GMII and MII receive clock 22.5V ENET1_RX_COL PIN_B22GMII and MII collision 22.5V ENET1_RX_CRS PIN_D20GMII and MII carrier sense 22.5V ENET1_RX_DATA[0]PIN_B23GMII and MII receive data[0] 22.5V ENET1_RX_DATA[1]PIN_C21GMII and MII receive data[1] 22.5V ENET1_RX_DATA[2]PIN_A23GMII and MII receive data[2] 2ENET1_RX_DATA[3]PIN_D21GMII and MII receiv2.5Ve data[3] 2ENET1_RX_DV PIN_A22GMII and MII receiv2.5Ve data valid 22.5V ENET1_RX_ER PIN_C24GMII and MII receive error 2ENET1_TX_CLK PIN_C22MII transmit clock 22.5V2.5V ENET1_TX_DATA[0]PIN_C25MII transmit data[0]2ENET1_TX_DATA[1]PIN_A26MII transmit data[1]2.5V2ENET1_TX_DATA[2]PIN_B26MII transmit data[2]2.5V2ENET1_TX_DATA[3]PIN_C26MII transmit data[3]2.5V22.5V ENET1_TX_EN PIN_B25GMII and MII transmit enable 22.5V ENET1_TX_ER PIN_A25GMII and MII transmit error 2ENETCLK_25PIN_A14Ethernet clock sour3.3Vce表15 TV 解码芯片引脚配置Signal Name FPGA Pin No.Description I/O Standard TD_ DATA [0]PIN_E8TV Decoder Data[0] 3.3VTD_ DATA [1]PIN_A7TV Decoder Data[1] 3.3VTD_ DATA [2]PIN_D8TV Decoder Data[2] 3.3VTD_ DATA [3]PIN_C7TV Decoder Data[3] 3.3VTD_ DATA [4]PIN_D7TV Decoder Data[4] 3.3VTD_ DATA [5]PIN_D6TV Decoder Data[5] 3.3VTD_ DATA [6]PIN_E7TV Decoder Data[6] 3.3VTD_ DATA [7]PIN_F7TV Decoder Data[7] 3.3VTD_HS PIN_E5TV Decoder H_SYNC 3.3VTD_VS PIN_E4TV Decoder V_SYNC 3.3V3.3VTD_CLK27PIN_B14TV Decoder Clock Input.TD_RESET_N PIN_G7TV Decoder Reset 3.3VI2C_SCLK PIN_B7I2C Clock 3.3VI2C_SDAT PIN_A8I2C Data 3.3V 表16 USB (ISP1362)引脚配置Signal Name FPGA Pin No.Description I/O StandardOTG_ADDR[0]PIN_H7ISP1362 Address[0] 3.3V OTG_ADDR[1]PIN_C3ISP1362 Address[1] 3.3V OTG_DATA[0]PIN_J6ISP1362 Data[0] 3.3V OTG_DATA[1]PIN_K4ISP1362 Data[1] 3.3V OTG_DATA[2]PIN_J5ISP1362 Data[2] 3.3V OTG_DATA[3]PIN_K3ISP1362 Data[3] 3.3V OTG_DATA[4]PIN_J4ISP1362 Data[4] 3.3V OTG_DATA[5]PIN_J3ISP1362 Data[5] 3.3V OTG_DATA[6]PIN_J7ISP1362 Data[6] 3.3V OTG_DATA[7]PIN_H6ISP1362 Data[7] 3.3V OTG_DATA[8]PIN_H3ISP1362 Data[8] 3.3V OTG_DATA[9]PIN_H4ISP1362 Data[9] 3.3V OTG_DATA[10]PIN_G1ISP1362 Data[10] 3.3V OTG_DATA[11]PIN_G2ISP1362 Data[11] 3.3V OTG_DATA[12]PIN_G3ISP1362 Data[12] 3.3V OTG_DATA[13]PIN_F1ISP1362 Data[13] 3.3V OTG_DATA[14]PIN_F3ISP1362 Data[14] 3.3V OTG_DATA[15]PIN_G4ISP1362 Data[15] 3.3V OTG_CS_N PIN_A3ISP1362 Chip Select 3.3VOTG_RD_N PIN_B3ISP1362 Read 3.3V OTG_WR_N PIN_A4ISP1362 Write 3.3V OTG_RST_N PIN_C5ISP1362 Reset 3.3V OTG_INT[0]PIN_A6ISP1362 Interrupt 0 3.3V OTG_INT[1]PIN_D5ISP1362 Interrupt 1 3.3V OTG_DACK_N[0]PIN_C4ISP1362 DMA Acknowledge 0 3.3V OTG_DACK_N[1]PIN_D4ISP1362 DMA Acknowledge 1 3.3V OTG_DREQ[0]PIN_J1ISP1362 DMA Request 0 3.3V OTG_DREQ[1]PIN_B4ISP1362 DMA Request 1 3.3V3.3V OTG_FSPEED PIN_C6USB Full Speed, 0 = Enable, Z= Disable3.3V OTG_LSPEED PIN_B6USB Low Speed, 0 = Enable, Z= Disable表17 IR 引脚配置Description I/O StandardSignal Name FPGA Pin No.IRDA_RXD PIN_Y15IR Receiver 3.3V表18 SRAM 引脚配置Signal Name FPGA Pin No.Description I/O Standard SRAM_ADDR[0]PIN_AB7SRAM Address[0] 3.3VSRAM_ADDR[1]PIN_AD7SRAM Address[1] 3.3VSRAM_ADDR[2]PIN_AE7SRAM Address[2] 3.3VSRAM_ADDR[3]PIN_AC7SRAM Address[3] 3.3VSRAM_ADDR[4]PIN_AB6SRAM Address[4] 3.3V SRAM_ADDR[5]PIN_AE6SRAM Address[5] 3.3V SRAM_ADDR[6]PIN_AB5SRAM Address[6] 3.3V SRAM_ADDR[7]PIN_AC5SRAM Address[7] 3.3V SRAM_ADDR[8]PIN_AF5SRAM Address[8] 3.3V SRAM_ADDR[9]PIN_T7SRAM Address[9] 3.3V SRAM_ADDR[10]PIN_AF2SRAM Address[10] 3.3V SRAM_ADDR[11]PIN_AD3SRAM Address[11] 3.3V SRAM_ADDR[12]PIN_AB4SRAM Address[12] 3.3V SRAM_ADDR[13]PIN_AC3SRAM Address[13] 3.3V SRAM_ADDR[14]PIN_AA4SRAM Address[14] 3.3V SRAM_ADDR[15]PIN_AB11SRAM Address[15] 3.3V SRAM_ADDR[16]PIN_AC11SRAM Address[16] 3.3V SRAM_ADDR[17]PIN_AB9SRAM Address[17] 3.3V SRAM_ADDR[18]PIN_AB8SRAM Address[18] 3.3V SRAM_ADDR[19]PIN_T8SRAM Address[19] 3.3V SRAM_DQ[0]PIN_AH3SRAM Data[0] 3.3V SRAM_DQ[1]PIN_AF4SRAM Data[1] 3.3V SRAM_DQ[2]PIN_AG4SRAM Data[2] 3.3V SRAM_DQ[3]PIN_AH4SRAM Data[3] 3.3V SRAM_DQ[4]PIN_AF6SRAM Data[4] 3.3V SRAM_DQ[5]PIN_AG6SRAM Data[5] 3.3V SRAM_DQ[6]PIN_AH6SRAM Data[6] 3.3VSRAM_DQ[7]PIN_AF7SRAM Data[7] 3.3VSRAM_DQ[8]PIN_AD1SRAM Data[8] 3.3VSRAM_DQ[9]PIN_AD2SRAM Data[9] 3.3VSRAM_DQ[10]PIN_AE2SRAM Data[10] 3.3VSRAM_DQ[11]PIN_AE1SRAM Data[11] 3.3VSRAM_DQ[12]PIN_AE3SRAM Data[12] 3.3VSRAM_DQ[13]PIN_AE4SRAM Data[13] 3.3VSRAM_DQ[14]PIN_AF3SRAM Data[14] 3.3VSRAM_DQ[15]PIN_AG3SRAM Data[15] 3.3VSRAM_OE_N PIN_AD5SRAM Output EnableSRAM_WE_N PIN_AE8SRAM Write EnableSRAM_CE_N PIN_AF8SRAM Chip SelectSRAM_LB_N PIN_AD4SRAM Lower Byte StrobeSRAM_UB_N PIN_AC4SRAM Higher Byte Strobe表19 SDRAM 引脚配置Signal Name FPGA Pin No.Description I/O Standard DRAM_ADDR[0]PIN_R6SDRAM Address[0] 3.3VDRAM_ADDR[1]PIN_V8SDRAM Address[1] 3.3VDRAM_ADDR[2]PIN_U8SDRAM Address[2] 3.3VDRAM_ADDR[3]PIN_P1SDRAM Address[3] 3.3VDRAM_ADDR[4]PIN_V5SDRAM Address[4] 3.3VDRAM_ADDR[5]PIN_W8SDRAM Address[5] 3.3V DRAM_ADDR[6]PIN_W7SDRAM Address[6] 3.3V DRAM_ADDR[7]PIN_AA7SDRAM Address[7] 3.3V DRAM_ADDR[8]PIN_Y5SDRAM Address[8] 3.3V DRAM_ADDR[9]PIN_Y6SDRAM Address[9] 3.3V DRAM_ADDR[10]PIN_R5SDRAM Address[10] 3.3V DRAM_ADDR[11]PIN_AA5SDRAM Address[11] 3.3V DRAM_ADDR[12]PIN_Y7SDRAM Address[12] 3.3V DRAM_DQ[0]PIN_W3SDRAM Data[0] 3.3V DRAM_DQ[1]PIN_W2SDRAM Data[1] 3.3V DRAM_DQ[2]PIN_V4SDRAM Data[2] 3.3V DRAM_DQ[3]PIN_W1SDRAM Data[3] 3.3V DRAM_DQ[4]PIN_V3SDRAM Data[4] 3.3V DRAM_DQ[5]PIN_V2SDRAM Data[5] 3.3V DRAM_DQ[6]PIN_V1SDRAM Data[6] 3.3V DRAM_DQ[7]PIN_U3SDRAM Data[7] 3.3V DRAM_DQ[8]PIN_Y3SDRAM Data[8] 3.3V DRAM_DQ[9]PIN_Y4SDRAM Data[9] 3.3V DRAM_DQ[10]PIN_AB1SDRAM Data[10] 3.3V DRAM_DQ[11]PIN_AA3SDRAM Data[11] 3.3V DRAM_DQ[12]PIN_AB2SDRAM Data[12] 3.3V DRAM_DQ[13]PIN_AC1SDRAM Data[13] 3.3V DRAM_DQ[14]PIN_AB3SDRAM Data[14] 3.3VDRAM_DQ[15]PIN_AC2SDRAM Data[15] 3.3V SRAM_OE_N PIN_AD5SRAM Output Enable 3.3V SRAM_WE_N PIN_AE8SRAM Write Enable 3.3V SRAM_CE_N PIN_AF8SRAM Chip Select 3.3V SRAM_LB_N PIN_AD4SRAM Lower Byte Strobe3.3VSRAM_UB_N PIN_AC4SRAM Higher Byte Strobe3.3V 表20 SDRAM 引脚配置Signal Name FPGA Pin No.Description I/O StandardDRAM_ADDR[0]PIN_R6SDRAM Address[0] 3.3V DRAM_ADDR[1]PIN_V8SDRAM Address[1] 3.3V DRAM_ADDR[2]PIN_U8SDRAM Address[2] 3.3V DRAM_ADDR[3]PIN_P1SDRAM Address[3] 3.3V DRAM_ADDR[4]PIN_V5SDRAM Address[4] 3.3V DRAM_ADDR[5]PIN_W8SDRAM Address[5] 3.3V DRAM_ADDR[6]PIN_W7SDRAM Address[6] 3.3V DRAM_ADDR[7]PIN_AA7SDRAM Address[7] 3.3V DRAM_ADDR[8]PIN_Y5SDRAM Address[8] 3.3V DRAM_ADDR[9]PIN_Y6SDRAM Address[9] 3.3V DRAM_ADDR[10]PIN_R5SDRAM Address[10] 3.3V DRAM_ADDR[11]PIN_AA5SDRAM Address[11] 3.3V DRAM_ADDR[12]PIN_Y7SDRAM Address[12] 3.3VDRAM_DQ[0]PIN_W3SDRAM Data[0] 3.3V DRAM_DQ[1]PIN_W2SDRAM Data[1] 3.3V DRAM_DQ[2]PIN_V4SDRAM Data[2] 3.3V DRAM_DQ[3]PIN_W1SDRAM Data[3] 3.3V DRAM_DQ[4]PIN_V3SDRAM Data[4] 3.3V DRAM_DQ[5]PIN_V2SDRAM Data[5] 3.3V DRAM_DQ[6]PIN_V1SDRAM Data[6] 3.3V DRAM_DQ[7]PIN_U3SDRAM Data[7] 3.3V DRAM_DQ[8]PIN_Y3SDRAM Data[8] 3.3V DRAM_DQ[9]PIN_Y4SDRAM Data[9] 3.3V DRAM_DQ[10]PIN_AB1SDRAM Data[10] 3.3V DRAM_DQ[11]PIN_AA3SDRAM Data[11] 3.3V DRAM_DQ[12]PIN_AB2SDRAM Data[12] 3.3V DRAM_DQ[13]PIN_AC1SDRAM Data[13] 3.3V DRAM_DQ[14]PIN_AB3SDRAM Data[14] 3.3V DRAM_DQ[15]PIN_AC2SDRAM Data[15] 3.3V DRAM_DQ[16]PIN_M8SDRAM Data[16] 3.3V DRAM_DQ[17]PIN_L8SDRAM Data[17] 3.3V DRAM_DQ[18]PIN_P2SDRAM Data[18] 3.3V DRAM_DQ[19] PIN_N3SDRAM Data[19] 3.3V DRAM_DQ[20]PIN_N4SDRAM Data[20] 3.3V DRAM_DQ[21]PIN_M4SDRAM Data[21] 3.3V DRAM_DQ[22]PIN_M7SDRAM Data[22] 3.3VDRAM_DQ[23]PIN_L7SDRAM Data[23] 3.3V DRAM_DQ[24]PIN_U5SDRAM Data[24] 3.3V DRAM_DQ[25]PIN_R7SDRAM Data[25] 3.3V DRAM_DQ[26]PIN_R1SDRAM Data[26] 3.3V DRAM_DQ[27]PIN_R2SDRAM Data[27] 3.3V DRAM_DQ[28]PIN_R3SDRAM Data[28] 3.3V DRAM_DQ[29]PIN_T3SDRAM Data[29] 3.3V DRAM_DQ[30]PIN_U4SDRAM Data[30] 3.3V DRAM_DQ[31]PIN_U1SDRAM Data[31] 3.3V DRAM_BA[0]PIN_U7SDRAM Bank Address[0] 3.3V DRAM_BA[1]PIN_R4SDRAM Bank Address[1] 3.3V DRAM_DQM[0]PIN_U2SDRAM byte Data Mask[0] 3.3V DRAM_DQM[1]PIN_W4SDRAM byte Data Mask[1] 3.3V DRAM_DQM[2]PIN_K8SDRAM byte Data Mask[2] 3.3V DRAM_DQM[3]PIN_N8SDRAM byte Data Mask[3] 3.3V DRAM_RAS_N PIN_U6SDRAM Row Address Strobe 3.3V3.3V DRAM_CAS_N PIN_V7SDRAM Column Address StrobeDRAM_CKE PIN_AA6SDRAM Clock Enable 3.3V DRAM_CLK PIN_AE5SDRAM Clock 3.3V DRAM_WE_N PIN_V6SDRAM Write Enable 3.3V DRAM_CS_N PIN_T4SDRAM Chip Select 3.3V 表21 Flash 引脚配置Signal Name FPGA Pin No.Description I/O StandardFL_ADDR[0]PIN_AG12FLASH Address[0] 3.3V FL_ADDR[1]PIN_AH7FLASH Address[1] 3.3V FL_ADDR[2]PIN_Y13FLASH Address[2] 3.3V FL_ADDR[3]PIN_Y14FLASH Address[3] 3.3V FL_ADDR[4]PIN_Y12FLASH Address[4] 3.3V FL_ADDR[5]PIN_AA13FLASH Address[5] 3.3V FL_ADDR[6]PIN_AA12FLASH Address[6] 3.3V FL_ADDR[7]PIN_AB13FLASH Address[7] 3.3V FL_ADDR[8]PIN_AB12FLASH Address[8] 3.3V FL_ADDR[9]PIN_AB10FLASH Address[9] 3.3V FL_ADDR[10]PIN_AE9FLASH Address[10] 3.3V FL_ADDR[11]PIN_AF9FLASH Address[11] 3.3V FL_ADDR[12]PIN_AA10FLASH Address[12] 3.3V FL_ADDR[13]PIN_AD8FLASH Address[13] 3.3V FL_ADDR[14]PIN_AC8FLASH Address[14] 3.3V FL_ADDR[15]PIN_Y10FLASH Address[15] 3.3V FL_ADDR[16]PIN_AA8FLASH Address[16] 3.3V FL_ADDR[17]PIN_AH12FLASH Address[17] 3.3V FL_ADDR[18]PIN_AC12FLASH Address[18] 3.3V FL_ADDR[19]PIN_AD12FLASH Address[19] 3.3V FL_ADDR[20]PIN_AE10FLASH Address[20] 3.3V FL_ADDR[21]PIN_AD10FLASH Address[21] 3.3V。

频率计课设指导及DE-115使用说明

待测信号

arithmetic

运算结果

图中 BZ_Counter 和 DC_Counter 是 2 个可控的 32 b 高速计数器 (100 MHz) , BZ_ENA 和 DC_ENA 分别是他们的计数允许信号端,高电平有效。基准频率信号从 BZ_Counter 的 时 钟 输 入 端 BZ_CLK 输 入 , 设 其 频 率 为 Fs; 待 测 信 号 从 与 BZ_Counter 相似的 32 b 计数器 DC_Counter 的时钟输入端 DC_CLK 输入,测量频 率为 Fx。 图中 arithmetic 为运算模块,由一个乘法器和一个触发器构成,可在 QuartusII 中直接调用相关模块。 测量开始,首先由按键产生一个清零信号 CLR,使 2 个 32 b 的计数器和 D 触发器置 0,然后再由经分频的系统时钟发出允许测频命令,即使预置门控信号 GATE 为高电平,这时 D 触发器要一直等到被测信号的上升沿通过时,Q 端才被置 1,即使 BZ_ENA 和 DC_ENA 同时为 1,将启动计算器 BZ_Counter 和 DC_Counter, 系统进入计算允许周期。这时,计数器 BZ_Counter 和 DC_Counter 分别对被测信 号和标准频率信号同时计数。当 T 秒过后,预置门控信号被单片机置为低电平, 但此时 2 个 32 b 的计数器仍然没有停止计数,一直等到随后而至的被测信号的 上升沿到来时,才通过 D 触发器将这 2 个计算器同时关闭。

由上图所示的测频时序图可见,GATE 的宽度和发生的时间都不会影响计数 使能信号允许计数的周期总是恰好等于待测信号 XCLK 的完整周期,这正是确保 XCLK 在任何频率条件下都能保持恒定测量精度的关键。因为,此时 GATE 的宽度 T 改变以及随机的出现时间造成的误差最多只有基准时钟 BCLK 信号的一个时钟 周期,由于 BCLK 的信号是由高稳定度的 50 MHz 晶体振荡器发出的,所以任何时 刻的绝对测量误差只有约 1/50 s,这也是系统产生主要的误差。 设在某一次预置门控时间 T 中对被测信号计数值为 Nx,对标准频率信号的 计数值为 Ns,则根据闸门时间相等,可得出公式: Fx Fs = Nx Ns 即 Fx = � � ∙ Nx

DE2-115中文使用手册

早上1目录第1章.关于DE2-115 工具包 (4)1.1包装内容 (4)1.2 DE2-115 的组装 (5)1.3获得帮助 (5)第2章.DE2-115 开发板简介 (7)2.1开发板布局和组件 (7)2.2 DE2-115 系统框图 (9)2.3 DE2-115上电 (11)第3章.DE2-115控制面板 (13)3.1 控制面板初始化 (13)3.2控制LED灯, 7段数码显示管和 LCD显示器 (15)3.3开关与按钮 (17)3.4 SDRAM/SRAM/EEPROM/Flash控制器和编程器 (18)3.5 USB 监测 (20)3.6 PS/2设备 (20)3.7 SD卡 (21)3.8 RS-232 通信 (22)3.9 VGA (23)3.10 HSMC (24)3.11红外接收器 (25)3.12 DE2-115 控制面板的整体结构 (26)第4章.使用DE2-115 (28)4.1 配置Cyclone IV E FPGA芯片 (28)4.2 使用按钮开关和拨动开关 (31)4.3 使用LED (32)14.5 时钟电路 (36)4.6 使用LCD模块 (37)4.7 HSMC接口 (39)4.8 使用通用扩展接头 (44)4.9 使用14脚扩展口 (49)4.10 使用VGA (49)4.11 使用24比特音频编解码芯片 (52)4.12 RS-232串口 (53)4.13 PS/2接口 (54)4.14 千兆以太网接口 (55)4.15 TV解码器 (58)4.16 TV编码器实现 (59)4.17 使用USB界面 (59)4.18 使用IR模块 (61)4.19 使用SRAM/SDRAM/Flash/EEPROM/SD 卡 (61)第5章.DE2-115 系统生成器 (68)5.1简介 (68)5.2一般设计流程 (68)第6章.高阶设计范例 (75)6.1 DE2-115默认配置 (75)6.2 TV 电视盒设计范例 (76)6.3 USB画笔 (78)6.4 USB设备 (80)6.5 卡拉OK机 (82)6.6 SD卡设计范例 (84)6.7 SD卡音乐播放器 (86)6.8 PS/2鼠标控制器设计范例 (89)6.9 IR接收器设计范例 (92)6.10 音乐合成器设计范例 (95)26.12 网页服务器设计范例 (101)第7章.附录1097.1 修改历史 (109)7.2 版权声明 (109)3第1章.关于DE2-115 工具包DE2-115 套装包含了所有使用开发板会用到的器件资源,您额外需要的仅是一台装有微软视窗操作系统的个人电脑。

通用电子管管脚接线图

常用电子管管脚接线图(1)管脚图例 管子型号 管子型号(1)管子型号(2) 6AQ8 A ECC856BQ7A ECC180 A6BZ7A A6CG7A6FQ7 ) A 脚为 NC (第 9 6DJ8 ECC88 A 6922 A E88CC7308 E188CC AE288CC 8223 AA Cea6H 16N1 n A66N2 H2n A6H 6nA 6N66H 23 6N11A n第(6240GA IC)脚为 96A H 30 n 2C51 Al5670 Al6H 6N33 Al n(A1))2常用电子管管脚接线图(.管脚图例管子型号管子型号(1)管子型号(2)12AT7 B ECC8112AU7 B ECC82B ECC83 12AX7B 12BH75751 BB 5814AB E81CC 6201E82CC 6189 BB E83CC 6681B 70256 B H412AY7 nB ECC99B E80CCB 6N46N10 B2025 B5687 Bl7119 E182CCBl)3常用电子管管脚接线图(.(C) (D)管脚图例管子型号管子型号(1)管子型号(2)6SL7GT C5691 CC 6SN7GTC 56926 H8C C 6N8P6H9C 6N9P cC ECC336AS7G C6080 C6H C 5 6N5P c6H13 C c 6N13P6BX7GT C6BL7GTA C6BQ5 D EL84D 71896nD 146P14 n)4常用电子管管脚接线图(.(E)管脚图例管子型号管子型号(1)管子型号(2)E 6F6GTE 6L6GE 6L6GC6V6GT E5881 E6550AEBCKT88 (第1E 脚为)E KT66E 16147581A E6n3E 6P3P c66P6P n 6 c E6G-B8 EF 2A32c4c F45 FF 50F 300BF 4300B)5常用电子管管脚接线图(.管脚图例管子型号管子型号(1)管子型号(2)211 G845 GH 6CA7 EL34常用电子管管脚接线图(6)管脚图例管子型号管子型号(1)管子型号(2)I 7027A(H)(I))8常用电子管管脚接线图(.K 7868常用电子管管脚接线图(7) (L) (M) 管脚图例管子型号管子型号(1) 管子型号(2)L 807r-807FU-7 LEF94 6AU6 MEF93 6BA6 M6BD6 M6»M 4 n6J46 來6 J5 5nM管脚图例管子型号管子型号(1)管子型号(2)Ml EF96 6AG5Ml EF95 6AK5Ml 6BC56>K1M1 n6Jl6>K M1 36J3 n6267 N EF866氷N 326J8 n常用电子管管脚接线图(9)管脚图例管子型号管子型号(1)G2KG3IS(M1)(N)(O))11常用电子管管脚接线图(・ 管子型号(2)N1 EF80 6BX6N1 6EJ7 EF1840 6SJ7GT0 56936 氷 8 c 6J8P 0常用电子管管脚接线图(10)管脚图例 管子型号 管子型号(1) 管子型号(2)GZ34 P 5AR45V4G P5Z4GT GZ30 PGZ32 PP GZ33GZ37 PP U545 u 45Z4P c P5U4G Q5U4GB Q5n3 Q c 5Z3P管脚图例管子型号管子型号(1) 管子型号(2)5R4GY R5Y3GT RR 274BR 5Z2PS 5Z3S 80常用电子管管脚接线图(12)管脚图例管子型号管子型号(1)管子型号(2)(S)(U)T EZ81 6CA4EZ80 T6X4 EZ90 U常用电子管管脚接线图(13)管脚图例管子型号管子型号(1)管子型号(2)6u 4n U1 6Z47591 V常用电子管管脚接线图(14)管脚图例管子型号管子型号(1) 管子型号(2) 6AN8 WECF80 X 6BL8X ECF82 6U8A常用电子管管脚接线图(15)(Y)管脚图例管子型号管子型号(1) 管子型号(2)7199 Y注:F一一灯丝G一一栅极G1- 一-控制栅G2-一-帘栅极G3-一-抑制栅极或集射屏H——热丝K—一阴极P—一屏极IC—管内没有电极连接的空脚,但管座上的焊片不能作中继连接端子用。

管脚分配图

CN2:26

PG5

KEY2

CN1:11

PD0

LED1

CN1:12

PD1

KEY1

CN1:15

PG3

LED2

CN1:16

PG2

LED3

CN1:19

PC7/C2-

频率比较?

触发/中断

CN1:20

PC6/C2+/c2o

-

CN2:3

PB4/C0-

电源比较

等待更改

CN2:5

PB6/C0+

-

内部使用

PA2

D0

CN1:26

PA3

D1

CN1:27

PA4

D2

CN1:28

PA5

CN2:25

PG4/CCP3

蜂鸣器

考虑做PWM脉冲ห้องสมุดไป่ตู้检

以及

CN2:26

PG5

KEY2

CN1:11

PD0

LED1

CN1:12

PD1

KEY1

CN1:15

PG3

LED2

CN1:16

PG2

LED3

CN1:17

PG0/U2TX

CN1:18

CN2:6

PE3

CS

片选中CS=0

CN2:10

PB3/I2C0SDA

IRQ

中断输出

CN2:13

PB0/CCP0

RS

CN2:12

PB1/CCP2

R/W

CN2:4

PB5

RST

等待更改

CN2:11

PB2//I2C0SCL

E

信号

含义

基于DE2-115开发板的FPGA入门设计实验

基于DE2-115开发板的FPGA入门设计实验1、Lab1: 4位加法器、减法器的设计1.1 摘要在文件add_sub里面的工程文件operation_4.v为顶层文件,该顶层文件包含了三个子模块,分别为数码管显示模块,4位带进位的二进制加法器模块和4位带借位的二进制减法器模块,最后通过DE2-115开发板显示实验结果。

1.2 程序1)add_4bits.v 加法器module adder_4bits(input clk,input rst_n,input [3:0] x,input [3:0] y,output reg [3:0] sum,output reg carry_out //溢出位);always@(posedge clk or negedge rst_n)beginif(!rst_n){carry_out, sum} <= 0;else{carry_out, sum} = x + y;endendmodule2)substractor_4bits.v减法器module subtractor_4bits(input clk,input rst_n,input [3:0] x,input [3:0] y,output r eg [3:0] sub,output r eg borrow_out);always@(posedge clk or negedge rst_n) beginif(!rst_n){borrow_out, sub} <= 0;elsebeginif(x >= y){borrow_out, sub} = {1'b0, x - y};else{borrow_out, sub} = {1'b1, x - y};endendendmodule3)seg7_lut.v 数码管显示译码模块module Seg7_lut(input [3:0] iDIG,output r eg [6:0] oSEG);always @(iDIG)begincase(iDIG)4'h1: oSEG = 7'b1111001; // ---t----4'h2: oSEG = 7'b0100100; // | |4'h3: oSEG = 7'b0110000; // lt rt4'h4: oSEG = 7'b0011001; // | |4'h5: oSEG = 7'b0010010; // ---m----4'h6: oSEG = 7'b0000010; // | |4'h7: oSEG = 7'b1111000; // lb rb4'h8: oSEG = 7'b0000000; // | |4'h9: oSEG = 7'b0011000; // ---b----4'ha: oSEG = 7'b0001000;4'hb: oSEG = 7'b0000011;4'hc: oSEG = 7'b1000110;4'hd: oSEG = 7'b0100001;4'he: oSEG = 7'b0000110;4'hf: oSEG = 7'b0001110;4'h0: oSEG = 7'b1000000;endcaseendendmodule1.3 结果本设计通过Verilog HDL硬件描述语言。

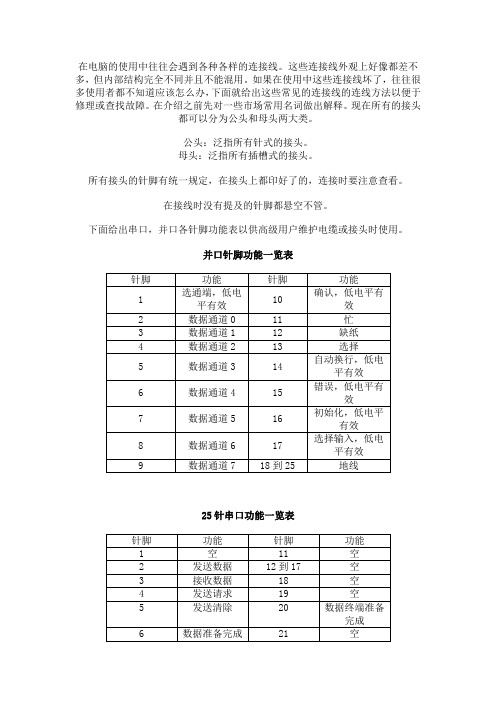

并口针脚功能一览表

在电脑的使用中往往会遇到各种各样的连接线。

这些连接线外观上好像都差不多,但内部结构完全不同并且不能混用。

如果在使用中这些连接线坏了,往往很多使用者都不知道应该怎么办,下面就给出这些常见的连接线的连线方法以便于修理或查找故障。

在介绍之前先对一些市场常用名词做出解释。

现在所有的接头都可以分为公头和母头两大类。

公头:泛指所有针式的接头。

母头:泛指所有插槽式的接头。

所有接头的针脚有统一规定,在接头上都印好了的,连接时要注意查看。

在接线时没有提及的针脚都悬空不管。

下面给出串口,并口各针脚功能表以供高级用户维护电缆或接头时使用。

并口针脚功能一览表25针串口功能一览表9针串口功能一览表联机线的连接方法联机线主要用于直接把两台电脑连接,分为串口(com1,com2)联机线和并口(lpt1)联机线。

比较早一点的AT架构的电脑的串口有为9针,和25针两种,现在的ATX架构的电脑两个串口全部是9针。

打印机的接口也是25针的但功能、外观上与AT架构的25针串口不一样。

于是联机线就分为4种(9针对9针串口联机线,9针对25针串口联机线,25针对25针串口联机线,25针对25针并口联机线)其中3种串口连接,一种并口连接。

并口联机线和串口联机线最大的差别就是速度,前者明显快于后者。

这些直接电缆连接线的两个头完全相同可以互换的连线方法如下表:首先我们必须准备2个连接头,以及大约1.5米的联机线,联机线应该选用带屏蔽的多芯线,把多余未用的芯全部接在接头的金属壳(地线)作为屏蔽用。

串口连机线一览表并口联机线一览表打印机连接线的现在使用的打印机连接线端口是25针公头的,和并口联机线使用的接头针脚数一样,但打印机连接线的两个头是不一样的,分别接电脑和打印机不能互换。

首先准备一个25针接头,和一个36线打印口接头。

并且先将25针接头的18-25针脚连接在一起。

把36线打印口接头的19-30脚连接在一起。

然后使用一根芯把这两组连接在一起。

常用芯片引脚图

附录三常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751AGND:A/D转换器参考地引脚XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

表1 拨动开关引脚配置

表2 按钮开关引脚配置

表3 LED 引脚配置

表4 七段数码管引脚配置

表5 时钟信号引脚配置信息

表6 LCD 模块引脚配置

表7 HSMC 接口引脚配置

表8 GPIO 引脚配置信息

表9 扩展接口引脚配置信息

表10 ADV7123 引脚配置

表11 音频编解码芯片引脚配置

表12 RS-232 引脚配置

表13 PS/2 引脚配置

表14 千兆以太网芯片引脚配置

表15 TV 解码芯片引脚配置

表16 USB (ISP1362)引脚配置

表17 IR 引脚配置

表18 SRAM 引脚配置

表19 SDRAM 引脚配置

表20 SDRAM 引脚配置

表21 Flash 引脚配置

表22 EEPROM 引脚配置

表23 SD 卡插槽引脚配置。