插指型SiO2电流阻挡层对大功率LED外量子效率的影响

半导体制造技术期末题库参考答案

(1) 、杂质分布形式:在表面浓度 Cs 一定的情况下,扩散时间越长,杂质 主要特点: 扩散的就越深,扩到硅内的杂质数量也就越多。

x 2 Dterfc 1 (2)、结深: j

CB A Dt Cs

x2

Cs 4 Dt C ( x, t ) | x ,t e (3)、杂质浓度梯度: x Dt

4、写出菲克第一定律和第二定律的表达式,并解释其含义。

费克第一定律 C 杂质浓度 D 扩散系数(单位为 cm2/s) J 材料净流量(单位时间内流过单位面积的原子个数) 解释:如果在一个有限的基体中杂质浓度 C(x, t)存在梯度分布,则杂质 将会产生扩散运动,杂质的扩散流密度 J 正比于杂质浓度梯度 C/ x,比 例系数 D 定义为杂质在基体中的扩散系数。 1、杂质的扩散方向是使杂质浓度梯度变小。如果扩散时间足够长,则杂质分布 逐渐变得均匀。 2、当浓度梯度变小时,扩散减缓。 3、D 依赖于扩散温度、杂质的类型以及杂质浓度等。 菲克第二定律

可得

代入第一定律方程则得到第二方程。即杂质在材料

中沿某一方向浓度随时间变化率是由于扩散所引起的。

5、以 P2O5 为例,多晶硅中杂质扩散的方式及分布情况。

由于 P2O5 的晶粒较大,因此主要形成 B 类分

6.分别写出恒定表面源扩散和有限表面源扩散的边界条件、初始条件、 扩散杂质的分布函数,简述这两种扩散的特点

如果假设扩散系数 D 为常数,这种假设在低杂质浓度情况下是正确的,则得

解释: 菲克第二定律即为一维扩散方程 沿扩散方向,从 x 到 x+Δx,面积为Δs 的一个小体积元内的杂质数量随时间的 变化情况。设在小体积元Δv=ΔxΔs 内的杂质分布是均匀的。体积元内的杂质 浓 度 为 C(x, t) , 经 过 Δ t 时 间 , 该 体 积 元 内 杂 质 变 化 量 为 ,杂质在 x 处的扩散流密度分别为 J(x,t)则 在 Δ t 时 间 内 通 过 x 处 和 x+ Δ x 处 的 杂 质 流 量 差 为 ,假设体积元内的杂质不产生也不消失,

半导体物理与器件考核试卷

B.硅化

C.硼化

D.镍化

17.在半导体工艺中,以下哪些步骤属于前道工艺?()

A.光刻

B.蚀刻

C.离子注入

D.镀膜

18.以下哪些材料常用于半导体器件的互连?()

A.铝

B.铜导线

C.镓

D.硅

19.在半导体物理中,以下哪些现象与载流子的复合有关?()

A.发射

B.复合

C.陷阱

D.所有上述现象

20.以下哪些因素会影响半导体激光器的阈值电流?()

半导体物理与器件考核试卷

考生姓名:__________答题日期:__________得分:__________判卷人:__________

一、单项选择题(本题共20小题,每小题1分,共20分,在每小题给出的四个选项中,只有一项是符合题目要求的)

1.半导体的导电性能介于导体和绝缘体之间,主要因为其()

C. Nitrogen(氮的)

D. Excess electrons(过剩电子)

5. P-N结在反向偏置时,其内部的电场强度()

A.减小

B.增大

C.消失

D.不变

6.以下哪个不是太阳能电池的工作原理?()

A.光电效应

B.热电效应

C.光生伏特效应

D.量子效应

7.在MOSFET(金属-氧化物-半导体场效应晶体管)中,MOS电容的C-V特性曲线中,积累区对应于()

18. A, B

19. D

20. D

三、填空题

1.禁带

2.电子

3.降低

4.金属-氧化物-半导体

5.温度

6.栅氧化层质量

7.紫外光

8.能级

9.玻尔兹曼分布

10.温度

势垒硅掺杂对GaN基LED极化电场及其光电性能的影响

势垒硅掺杂对GaN基LED极化电场及其光电性能的影响张正宜;王超【摘要】势垒硅掺杂对InGaN量子阱中的电场及LED器件的光电性能有着重要的影响.采用6×6 K·P方法计算了不同势垒硅掺杂浓度对量子阱中电场的变化,研究表明当势垒硅掺杂浓度>1e18 cm-3时,阱垒界面处的电场强度会变大,这主要是由于硅掺杂浓度过高导致量子阱中界面电荷的聚集.进一步发现随着势垒掺杂浓度的升高,总非辐射复合随之增加,其中俄歇复合增加,而肖克莱-霍尔-里德复合随之减少,这是由于点陷阱的增大形成了缺陷能级.电流电压曲线表明势垒掺杂可有效改善GaN基LED的工作电压,这归于掺杂浓度的提高改善了载流子的传输特性.当掺杂浓度为1e18 cm-3时,获得了较高的内量子效率,这主要是由于适当的势垒掺杂降低了量子阱中界面电荷的损耗.【期刊名称】《发光学报》【年(卷),期】2018(039)010【总页数】6页(P1445-1450)【关键词】势垒;量子阱;极化电场;光电性能【作者】张正宜;王超【作者单位】山西交通职业技术学院信息工程系, 山西太原 030031;兰州交通大学光电技术与智能控制教育部重点实验室,甘肃兰州 730070【正文语种】中文【中图分类】TN321.81 引言InGaN半导体材料具有纤锌矿晶体结构和直接能隙结构,通过改变In原子在InGaN中的比例,可实现从0.7 eV到6.2 eV的能隙调控,从而可以在整个可见光范围内通过电致发光[1-2]。

InGaN LED被广泛应用到通用照明和显示领域。

对于氮化物发光二极管器件来说,InGaN多量子阱结构是其最重要的组成部分。

目前,对于InGaN多量子阱的材料结构设计及机理方面做了大量的研究工作,其中,包括量子阱p型掺杂、梯度量子阱、三角量子阱的设计等改变量子阱内的极化电场,采用lnGaN或者InAlGaN作为势垒材料来调节多量子阱中的应力[3],对InGaN多量子阱垒层掺杂Si来改善器件的光学及电学性能[4-6]。

sio2介电损耗1ghz -回复

sio2介电损耗1ghz -回复关于SIO2介电损耗1GHz的介绍引言:SIO2是一种重要的无机化合物,具有广泛的应用领域。

其中,SIO2的介电损耗是一个关键参数,特别是在高频率下。

本文将介绍SIO2介电损耗1GHz的相关知识,并一步一步回答相关问题。

第一部分:SIO2介电损耗的基本概念和重要性(300-500字)1.1 SIO2介电损耗的定义SIO2介电损耗可以简单理解为材料在电场作用下,通过分子内部的摩擦和极化导致的能量损耗。

它通常是通过介电常数和介电耗散因子的乘积来表示。

1.2 SIO2介电损耗的高频特性SIO2在高频率下的介电损耗与晶体结构、晶体取向、微结构和杂质含量等因素密切相关。

尤其是在1GHz的高频率下,SIO2的介电损耗是一个十分重要的性能指标。

1.3 SIO2介电损耗的影响因素SIO2介电损耗的主要影响因素包括材料纯度、结晶度、相对密度、晶体取向和晶粒尺寸等。

这些因素对SIO2的介电性能产生显著的影响。

1.4 SIO2介电损耗的应用领域SIO2的低介电损耗使其在微电子器件、光学器件、高速通信设备和高频电子系统等领域得到广泛应用。

对于需要在高频率下传输信号的电子器件来说,低介电损耗是保证信号传输质量的关键之一。

第二部分:探究SIO2介电损耗1GHz的测试方法和结果(600-800字)2.1 SIO2介电损耗测试方法SIO2介电损耗的测试方法多种多样,例如谐振腔法、穿孔脉冲法、电内嵌法等。

其中,谐振腔法是最常用的方法之一。

该方法通过测量样品在电场作用下的回波损耗来计算介电损耗。

2.2 SIO2介电损耗1GHz的实验结果在设计实验时,我们选取了纯度较高的SIO2样品,并使用谐振腔法进行测试。

实验结果显示,在1GHz的频率下,SIO2的介电损耗较低,维持在0.001以下。

这表明SIO2在高频率下具有良好的介电性能。

第三部分:分析SIO2介电损耗1GHz的原因(400-600字)3.1 结晶度和相对密度对介电损耗的影响SIO2的结晶度和相对密度是影响其介电损耗的重要因素。

南京理工大学光电检测-习题解答

南京理工大学光电检测-习题解答南京理工大学光电检测课后习题答案第1章1、举例说明你说知道的检测系统的工作原理。

(1)光电检测技术在工业生产领域中的应用:在线检测:零件尺寸、产品缺陷、装配定位…(2)光电检测技术在日常生活中的应用:家用电器——数码相机、数码摄像机:自动对焦---红外测距传感器自动感应灯:亮度检测---光敏电阻空调、冰箱、电饭煲:温度检测---热敏电阻、热电偶遥控接收:红外检测---光敏二极管、光敏三极管可视对讲、可视电话:图像获取---面阵CCD医疗卫生——数字体温计:接触式---热敏电阻,非接触式---红外传感器办公商务——扫描仪:文档扫描---线阵CCD红外传输数据:红外检测---光敏二极管、光敏三极管(3)光电检测技术在军事上的应用:夜视瞄准机系统:非冷却红外传感器技术激光测距仪:可精确的定位目标光电检测技术应用实例简介点钞机钞票的荧光反映,可判别钞票真假。

(4)纸宽的检测—红外发光二极管及接收二极管的应用主要是用于根据钞票经过此红外发光及接收二极管所用的时间及电机的转速来间接的计算出钞票的宽度,并对机器的运行状态进行判断,比如有无卡纸等;同时也能根据钞票的宽度判断出其面值。

(5)喂钞台、接钞台传感器—红外对管的应用在点钞机的喂钞台和取钞台部分分别有一个作为有无钞票的发射接收红外对管,用来检测是否有钞票放入或取出。

2、如何实现非电量的测量?为实现非电量的电测量,首先要实现从非电量到电量的变换,这一变换是靠传感器来实现的。

传感器接口电路是为了与传感器配合将传感器输出信号转换成低输出电阻的电压信号以方便后续电路的处理。

一般说来,信号都需要进一步放大并滤除噪声。

放大后的信号经模拟/数字变换后得到数字信号,以便于微处理器或微控制器。

微处理器或微控制器是测控系统的核心,它主要有两个作用:一是对数字信号进行进一步处理并将信号输出显示、存储和控制。

二是管理测控系统的各个部分以实现测控系统的智能化,即根据信号和测量条件的变化,自动地改变放大器的增益、滤波器的参数及其它的电路参数。

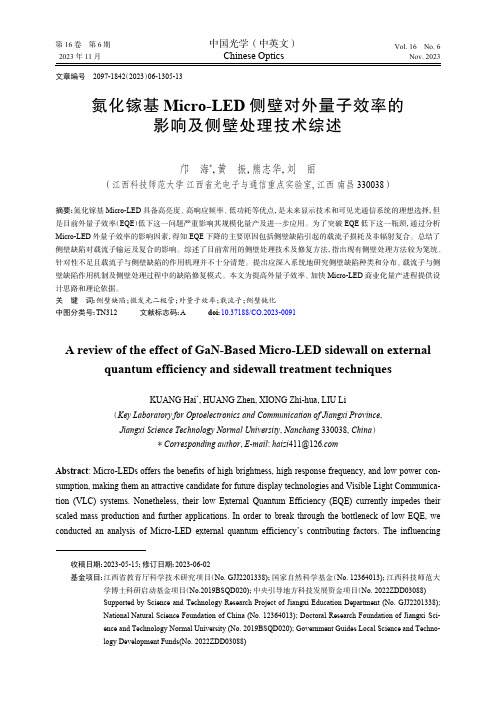

氮化镓基Micro-LED_侧壁对外量子效率的影响及侧壁处理技术综述

文章编号 2097-1842(2023)06-1305-13氮化镓基Micro-LED 侧壁对外量子效率的影响及侧壁处理技术综述邝 海*,黄 振,熊志华,刘 丽(江西科技师范大学 江西省光电子与通信重点实验室, 江西 南昌 330038)摘要:氮化镓基Micro-LED 具备高亮度、高响应频率、低功耗等优点,是未来显示技术和可见光通信系统的理想选择,但是目前外量子效率(EQE )低下这一问题严重影响其规模化量产及进一步应用。

为了突破EQE 低下这一瓶颈,通过分析Micro-LED 外量子效率的影响因素,得知EQE 下降的主要原因包括侧壁缺陷引起的载流子损耗及非辐射复合。

总结了侧壁缺陷对载流子输运及复合的影响。

综述了目前常用的侧壁处理技术及修复方法,指出现有侧壁处理方法较为笼统、针对性不足且载流子与侧壁缺陷的作用机理并不十分清楚。

提出应深入系统地研究侧壁缺陷种类和分布、载流子与侧壁缺陷作用机制及侧壁处理过程中的缺陷修复模式。

本文为提高外量子效率、加快Micro-LED 商业化量产进程提供设计思路和理论依据。

关 键 词:侧壁缺陷;微发光二极管;外量子效率;载流子;侧壁钝化中图分类号:TN312 文献标志码:A doi :10.37188/CO.2023-0091A review of the effect of GaN-Based Micro-LED sidewall on externalquantum efficiency and sidewall treatment techniquesKUANG Hai *,HUANG Zhen ,XIONG Zhi-hua ,LIU Li(Key Laboratory for Optoelectronics and Communication of Jiangxi Province ,Jiangxi Science Technology Normal University , Nanchang 330038, China )* Corresponding author ,E-mail : haizi 411@Abstract : Micro-LEDs offers the benefits of high brightness, high response frequency, and low power con-sumption, making them an attractive candidate for future display technologies and Visible Light Communica-tion (VLC) systems. Nonetheless, their low External Quantum Efficiency (EQE) currently impedes their scaled mass production and further applications. In order to break through the bottleneck of low EQE, we conducted an analysis of Micro-LED external quantum efficiency’s contributing factors. The influencing收稿日期:2023-05-15;修订日期:2023-06-02基金项目:江西省教育厅科学技术研究项目(No. GJJ2201338);国家自然科学基金(No. 12364013);江西科技师范大学博士科研启动基金项目(No.2019BSQD020);中央引导地方科技发展资金项目(No. 2022ZDD03088)Supported by Science and Technology Research Project of Jiangxi Education Department (No. GJJ2201338);National Natural Science Foundation of China (No. 12364013); Doctoral Research Foundation of Jiangxi Sci-ence and Technology Normal University (No. 2019BSQD020); Government Guides Local Science and Techno-logy Development Funds(No. 2022ZDD03088)第 16 卷 第 6 期中国光学(中英文)Vol. 16 No. 62023年11月Chinese OpticsNov. 2023factors for EQE are analyzed. It is concluded that the carrier loss and non-radiative recombination caused by sidewall defects are the main reasons for the decrease in EQE. In addition, we summarized the impact of sidewall defects on carrier transport and composites, and we also reviewed the commonly used sidewall treat-ment technology and repair methods, and pointed out that the existing sidewall treatment methods are helpful but insufficient for improving EQE, and the mechanism of carrier interaction with sidewall defects is not very clear. It is suggested to carry out a thorough and systematic study on the types and distribution of sidewall de-fects, the mechanism of carrier and sidewall defects, and the defect repair mode in the sidewall treatment pro-cess. Finally, future development trends are projected. This paper offers design ideas and theoretical founda-tions to enhance the external quantum efficiency and accelerate the process of commercialization and mass production of Micro-LEDs.Key words: defects on sidewall;micro-LED;external quantum efficiency;carriers;surface passivation1 引 言微发光二极管(Micro-Light-Emitting diode,Micro-LED)因具有其他光源不可比拟的优势而备受关注[1-6]。

先进集成电路后道工艺中扩散阻挡层的研究

先进集成电路后道工艺中扩散阻挡层的研究随着信息技术的快速发展,集成电路(IC)作为现代电子产品的核心组成部分,对其功能和性能提出了更高的要求。

为了满足这些要求,先进集成电路的制造工艺也在不断演进。

其中,后道工艺中的扩散阻挡层被认为是保障IC性能和可靠性的重要因素。

扩散阻挡层位于集成电路的制造过程的最后阶段,用于防止不同材料之间的扩散现象发生。

扩散现象是指材料中的原子在高温下通过晶格间隙迁移的过程。

如果不进行防止和控制,扩散现象可能会导致材料的成分发生变化,从而影响集成电路的性能和可靠性。

目前,先进集成电路中常用的扩散阻挡层主要有两种:硅氮化物(SiNx)和硅氧氮化物(SiON)。

研究表明,这两种材料在阻止扩散现象方面具有较好的性能。

硅氮化物具有较高的禁带宽度,能够有效阻挡原子的迁移;硅氧氮化物则具有较好的机械性能和化学稳定性,能够提高扩散阻挡层的耐久性。

然而,随着集成电路尺寸的不断缩小,扩散阻挡层的性能需求也在逐渐提高。

在研究中发现,传统的硅氮化物和硅氧氮化物在面对新一代集成电路的挑战时,存在一些问题。

例如,硅氮化物的应力效应容易引起晶体缺陷,从而影响电子迁移性能;硅氧氮化物的热稳定性较差,可能导致扩散阻挡层的性能退化。

为了解决这些问题,研究人员开始探索新型材料和工艺。

例如,一些学者提出了采用氮化高钛铝(TIN)材料作为扩散阻挡层的方法。

TIN材料具有较高的导电性和热稳定性,能够有效阻止扩散现象的发生,并且不易引起晶体缺陷。

此外,还有研究表明,采用磁控溅射技术制备的TIN材料在性能上更加稳定,可以满足高要求的集成电路制造。

总之,先进集成电路后道工艺中扩散阻挡层的研究对于保障IC的性能和可靠性具有重要意义。

通过探索新材料和工艺,可以不断提升扩散阻挡层的性能,为现代电子产品的发展提供更好的支撑。

半导体光电子学第6章 半导体发光二极管

半导体激光器与发光二极管在结构上的主要差别是前 者有光学谐振腔,使复合所产生的光子在腔内振荡和 放大;而后者则没有谐振腔。

正是由于它们在发光机理和上述这一基本结构上存在 差别,而使它们在主要性能上存在明显差别。

光谱宽度随有源层厚度的增 加而减小可归因于能为载流 子所填充的能带变窄。

面发光二极管的光谱宽度较宽。例如, 在高的注入电流下中心波长为1.3m 的面发光管,其Δ可达1300Å。但 它对温度不灵敏、高可靠性和低成本 等优点,却是光纤通信局部网(LAN) 中波分复用(WDM)光源所希望的。

然而,如此宽的谱宽限制了在保证邻 近信道之间有小的串音的前提下所能 供复用的波长数量。

防止发光管产生受激发射的另一种有效方法是将后端面弄斜, 以破坏由解理面形成的法布里-拍罗腔,如图6.2-2所示。其 基本结构与V沟衬底埋层异质结激光器相同,前端面镀增透 膜,后端面腐蚀成斜面。这种结构的特点是更能可靠地防止 受激发射,与前面采取非泵浦区结构的边发光管相比,更能 利用有源层的长度来产生自发辐射,获得较高输出功率。

1.不存在阈值特性,P-I线性好,因而有利于实现信 号无畸变的调制,这在高速模拟调制中是特别重要的;

2.虽然半导体发光二极管的光相干性很不好,但正因 为如此,避免了半导体激光器容易产生模分配噪声和 对来自于光纤传输线路中反射光较灵敏的缺点; 3.工作稳定,输出功率随温度的变化较小,不需要精 确的温度控制,因而驱动电源很简单;

三、发光二极管的发射谱

半导体发光二极管的自发发射的特点决定了它的发射光 谱是很宽的,要比半导体激光器的线宽高几个数量级。 而且光谱宽度Δ与峰值波长有关,可表示为

氧化硅热导率

氧化硅热导率概述氧化硅是一种常见的陶瓷材料,在热导率方面具有重要的应用价值。

热导率是描述材料导热性能的物理量,它对于热传导的理解和工程应用具有重要意义。

本文将对氧化硅的热导率进行全面、详细、完整地探讨,以加深对这一主题的理解。

原理热导率是描述材料导热性能的物理量,它是指在单位热量通过单位面积的材料厚度时,单位时间内通过此面积的热量。

热导率的数值越大,意味着材料具有更好的导热性能。

氧化硅的热导率主要受到晶格热传导和电子-声子散射的影响。

晶格热传导是指通过晶格振动传递热量的过程,它受到材料的晶格结构和缺陷的影响。

电子-声子散射是指电子与声子相互作用导致能量转移和散射的过程,它受到材料的电子结构和声子散射机制的影响。

影响因素氧化硅的热导率受到多种因素的影响,下面将介绍其中几个重要的因素:1.晶格结构:晶格结构是影响氧化硅热导率的关键因素之一。

氧化硅的晶格结构属于四方晶系,晶格中的硅氧键对热传导起到重要作用。

晶格结构的改变会影响硅氧键的形态和键能,从而影响热传导性能。

2.杂质:杂质是影响氧化硅热导率的另一个重要因素。

常见的杂质有铝、钙、锰等,它们的掺杂会影响晶格结构和缺陷,从而对热传导性能产生影响。

3.温度:温度是影响氧化硅热导率的重要因素之一。

通常情况下,随着温度的升高,热导率也会增加。

这是因为高温会增加晶格振动的频率和振幅,从而增强热传导效应。

4.有序列表–晶粒大小:氧化硅的晶粒大小对热导率有显著影响。

较大的晶粒有较少的晶界缺陷,导致较高的热导率。

–含水量:氧化硅的含水量对热导率有很大影响。

水分子可以附着在氧化硅表面,影响声子的传播,从而降低热导率。

–加工方法:氧化硅的加工方法也会对热导率产生一定影响。

常见的加工方法有热压法、溶胶-凝胶法等,不同的加工方法会导致氧化硅晶体结构和缺陷的差异,从而影响热导率。

应用氧化硅的热导率在多个领域具有重要的应用价值,下面将介绍其中几个典型应用:1.热管理:氧化硅的高热导率使其成为热管理领域的重要材料。

sio2介电损耗1ghz

sio2介电损耗1ghz(最新版)目录1.引言2.SiO2 的介电性质3.SiO2 的介电损耗4.1GHz 下的 SiO2 介电损耗5.总结正文1.引言二氧化硅(SiO2)是一种广泛应用于电子行业的材料,尤其是在集成电路和光电子器件中。

SiO2 具有优良的介电性能,但在高频率下,它的介电损耗会对器件的性能产生影响。

本文将探讨 SiO2 在 1GHz 下的介电损耗。

2.SiO2 的介电性质SiO2 是一种极性分子,其结构中包含氧原子和硅原子。

这种结构使得 SiO2 具有较高的介电常数,这意味着在电场作用下,SiO2 中的正负电荷会分离,形成一个电容。

这种性质使 SiO2 在电子行业中具有广泛的应用。

3.SiO2 的介电损耗介电损耗是指在电场作用下,介质中能量损耗的现象。

对于 SiO2 而言,其介电损耗主要是由于分子在电场作用下的极化和电荷在介质中的移动导致的。

在低频率下,SiO2 的介电损耗较小,但在高频率下,介电损耗会显著增加。

4.1GHz 下的 SiO2 介电损耗在 1GHz 的频率下,SiO2 的介电损耗会明显增加。

这是因为在高频率下,电场的变化速度很快,导致分子极化和电荷移动的速度跟不上电场的变化。

这就会产生较大的介电损耗,从而影响器件的性能。

5.总结二氧化硅(SiO2)在电子行业中具有广泛的应用,其优良的介电性能使其成为许多器件的关键材料。

然而,在高频率下,SiO2 的介电损耗会对器件的性能产生影响。

在 1GHz 的频率下,SiO2 的介电损耗会明显增加,这对设计和制造高频率器件提出了挑战。

非辐射复合损耗

非辐射复合损耗非辐射复合损耗(non-radiative recombination)指在半导体中,由于杂质、缺陷等非辐射诱导的载流子复合过程产生的能量损失。

相对于辐射复合(radiative recombination),非辐射复合是少数的不能被发光利用的损耗途径之一。

本文将从非辐射复合的机理、对半导体性能的影响以及如何减弱非辐射复合三个方面来进行讨论。

一、非辐射复合的机理半导体材料中的非辐射复合过程与辐射复合过程机理类似,都是在半导体内部的载流子与杂质、缺陷等庶杂的特殊结构之间相互作用,形成一个稳定的状态。

有两个常见的非辐射复合过程:激子的捕获(trap-assisted recombination)和碰撞复合(auger recombination)。

1.激子的捕获激子是由一个电子和一个空穴形成的电荷对,在半导体内部运动和相互作用。

激子复合是一种重要的能量损耗途径。

在激子捕获机制中,载流子会被陷阱所困,当两个被陷阱困住的激子相互结合时,就会产生非辐射复合现象。

此时,能量转化成了热能,而不是通过辐射损耗。

2.碰撞复合在单晶硅中,碰撞复合是非常常见的非辐射复合途径。

碰撞复合发生在电子和空穴之间,当二者具有足够高的能量时,它们就能相互结合形成一个稳定的复合态。

复合的产生需要大于载流子热能的能量,因此必须在系统中有像缺陷、原子杂质等陷阱来助威这一过程。

这样的重复结合是一个连锁反应,后续的非辐射复合会越来越多,而且一旦入侵缺陷状态的载流子数量足够多的时候,它甚至会迅速地弥漫整个半导体系统中。

二、非辐射复合对半导体性能的影响非辐射复合对半导体性能的影响是不容忽视的,它会导致低的外量子效率、低的电流增益、低的电容效应和弱耐受性能。

这些损耗效应可以通过增加暗电流和缩减载流子扩散长度来测量。

除此之外,由于非辐射复合过程很可能会降低发光效果,导致半导体发光二极管的发光效率很低,所以这种效应在LED中表现出的明显。

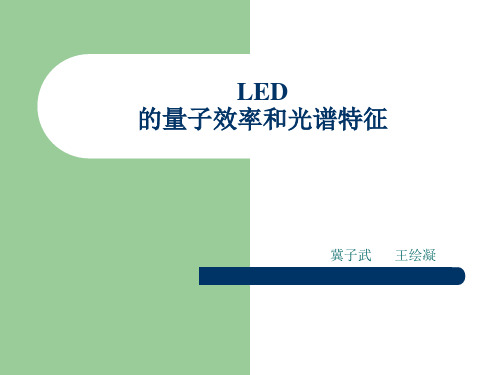

LED的量子效率和光谱特征

生长方法:MOCVD 样品质量:

高分辨X射线衍射仪(HRXRD) 用于评估该结构的界面质量、 结构参数。高级次的卫星峰被 清楚地观察到----反映了一个较 好的周期性。

AlGaN覆盖层(0.1μm)

12个周期的MQW (3 nm In0.18Ga0.82N势阱

4.5nm GaN势垒) GaN缓冲层(1.8μm)

Appl. Phys. Lett. 73,1370 (1998).

【论文概要】

InGaN/GaN MQWs 的PБайду номын сангаас光谱的温度依赖性:

随着温度的增加,峰值能量Ep发生红移 即所谓的 “S-shaped” 现象。

蓝移

红移 ,

当Ep红移时,光谱变窄;当Ep蓝移时,光谱变宽。 较高的温度导致了InGaN相关PL的淬灭。

LED的量子效率

常用的提高量子效率的主要方法

-----提高提取效率

五、芯片键合技术

对于GaAs和蓝宝石衬底,它们的导热性能都较差。为了更有效的散热和降 低结温,可通过减薄衬底或去掉原来用于生长外延层的衬底,然后将外延层 键合转移倒导电和导热性能良好热导率大的衬底上,如铜、铝、金锡合金、 氮化铝等。键合可用合金焊料如AuSn、PbSn、In等来完成(Si的热导率也比 GaAs和蓝宝石都好) 。

LED的量子效率

常见的分析、测量量子效率的方法(3)

-----变温PL谱测试

实例:

300 80 50

10 K

根据数据分析得出300K时的内 量子效率为14%。图中的拐点

出现在50-80 K附近。

(注:前页及本页内容参考: APL. 73, 1370 (1998),及与曲博士、朱 博士的相关交流)

LED的量子效率

影响太阳电池光电转换效率的因素和提高转换效率的主要措施

太阳能电池的基础与工艺课程期中考核论文题目:影响太阳电池光电转换效率的因素及提高太阳电池效率的主要措施学院:电子与电气工程学院班级:电子091班学号:0903741025姓名:易磊华影响太阳电池光电转换效率的因素及提高太阳电池效率的主要措施随着化石能源的日益枯竭、人们对环境保护问题的重视程度不断提高,寻找洁净的替代能源问题变得越来越迫切。

最新的资料表明,太阳光的充分利用,包括光热及阳光发电,是最清洁、环保,取之不尽用之不竭的可再生能源。

由研究、开发,直到建立规模化生产,光伏行业已经打造成为现今有声势的可再生能源领域。

当前太阳电池产业一直保持20%~30%的年增长率,并且已在2010年全球整体年产量达到了10GW。

预计到2025年,光伏能源占总能源的比例为22%。

可以预期,到21世纪中叶,光伏能源占到整个能源体系的34%的时候,人类生产、生活用电的三分之一将取自光伏发电。

然而,要想使太阳电池成为能源市场的主力之一,必须使太阳电池的制造成本和系统应用成本降低到可与现有能源可比拟的程度,世人才愿意使用,从而达到替代的目的。

因此“提高太阳电池和系统的效率,同时降低光伏系统的制造成本”是光伏界的终极目的,而效率是至关重要的因素。

那么如何提高太阳能电池的光电转换效率呢?首先我们需要知道太阳电池的工作原理。

光伏发电的基础是光生伏特效应,它是指当某种结构的半导体器件受到光照射时将产生直流电压(或电流),当光停止照射后电压(或电流)则立即消失的现象。

这个半导体器件的结构大体上就是一个大面积的平面的p-n结。

在光照射下,能量大于半导体禁带宽度的光子,使得半导体中原子的价电子受到激发,在p区、空间电荷区和n区都会产生光生电子-空穴对,也称光生载流子。

这样形成的电子-空穴对由于热运动,向各个方向迁移。

光生电子-空穴对在空间电荷区中产生后,立即被内建电场分离,光生电子被推进n区,光生空穴被推进p区。

在空间电荷区边界处总的载流子浓度近似为0。

基于混合型量子阱的GaN基垂直结构发光二极管性能

基于混合型量子阱的GaN基垂直结构发光二极管性能蔡镇准;胡晓龙;刘丽;王洪【摘要】为解决GaN基垂直结构发光二极管(VS-LEDs)在大电流驱动时效率下降的问题,制作了具有耦合量子阱(CQWs)和传统量子阱(NQWs)的混合型量子阱(HQWs)结构VS-LEDs.与NQWs结构VS-LEDs相比,HQWs结构VS-LEDs在350 mA输入电流下的正向偏压降低0.68 V,光输出功率提升53.0%,并有更好的电流响应效率.同时,NQWs结构和HQWs结构VS-LEDs的外量子效率分别下降到最大值的37.7%和67.5%,表明采用HQWs能使LEDs的效率下降得到大幅缓解.【期刊名称】《发光学报》【年(卷),期】2015(036)006【总页数】6页(P639-644)【关键词】GaN;垂直结构LEDs;混合型量子阱;效率下降【作者】蔡镇准;胡晓龙;刘丽;王洪【作者单位】华南理工大学物理与光电学院广东省光电工程技术研究中心,广东广州510640;华南理工大学物理与光电学院广东省光电工程技术研究中心,广东广州510640;华南理工大学物理与光电学院广东省光电工程技术研究中心,广东广州510640;华南理工大学物理与光电学院广东省光电工程技术研究中心,广东广州510640【正文语种】中文【中图分类】TN383+.1;TN312+.8近年来,GaN基LEDs获得了迅速的发展,由于其节能低耗、环保无污染、体积小、使用寿命长、驱动电压低、单色性强等诸多优点,被广泛应用于全彩色显示、液晶显示器背光源、建筑照明、家庭室内照明、汽车车灯照明等领域[1-2]。

目前蓝宝石衬底是使用最广泛的衬底材料,但其较差的导电、导热性能严重地限制了传统GaN基LEDs在通用照明领域的进一步发展[3-4]。

垂直结构LEDs (VS-LEDs) 一般是通过将GaN外延层从蓝宝石衬底转移至导电、导热性能好的基板上,并且VS-LEDs的电极分布于外延层两侧,因而可以解决衬底散热不佳、电流拥挤等问题。

集成电路的制造工艺改进考核试卷

6.光刻

7.塑料

8.屏蔽

9.热界面材料

10.丙酮

四、判断题

1. √

2. ×

3. √

4. ×

5. ×

6. ×

7. √

8. ×

9. √

10. ×

五、主观题(参考)

1.光刻工艺利用光刻胶在曝光后溶解度变化的特性,将掩模上的图案转移到硅片上。光刻胶的分辨率决定了图案转移的精细程度,直接影响集成电路的集成度和性能。

A.干法光刻

B.湿法光刻

C.极紫外光刻

D.电子束光刻

2.下列哪一项不是半导体材料的特点?()

A.电阻率介于导体和绝缘体之间

B.禁带宽度较大

C.随温度升高,电导率下降

D.可以通过掺杂改变电导率

3.在集成电路制造中,下列哪一项属于前道工艺?()

A.封装

B.焊接

C.光刻

D.老化测试

4.下列哪种材料常用作集成电路的绝缘层?()

B.光源波长

C.曝光时间

D.光刻机精度

12.以下哪些工艺节点代表了集成电路制造技术的进步?()

A. 180nm

B. 90nm

C. 45nm

D. 7nm

13.以下哪些材料可以用于集成电路的阻挡层和粘附层?()

A.镍

B.钛

C.铬

D.铜合金

14.以下哪些技术可以用于减少集成电路的功耗?()

A.低功耗设计

B.睡眠模式

B.光学显微镜

C. X射线透视

D.以上都是

17.在集成电路制造中,以下哪个参数会影响MOSFET器件的驱动能力?()

A.通道长度

B.通道宽度

C.沟道掺杂浓度

D.栅氧化层厚度

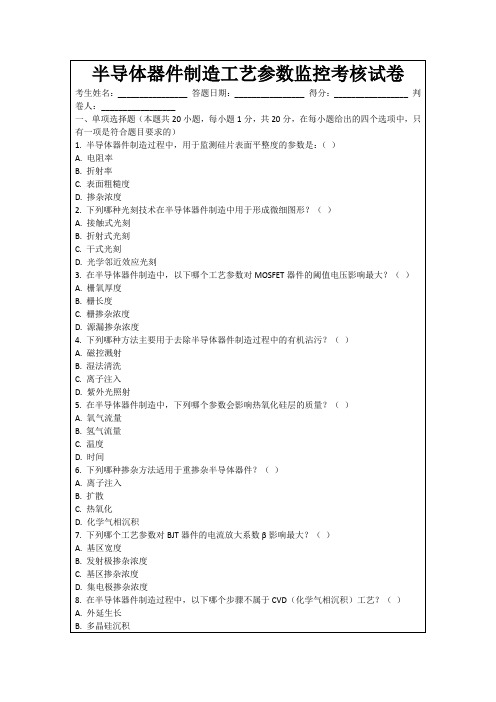

半导体器件制造工艺参数监控考核试卷

四、判断题(本题共10小题,每题1分,共10分,正确的请在答题括号中画√,错误的画×)

1.在半导体器件制造中,热处理可以改善硅片表面沾污问题。()

答案:

2.光刻工艺中,分辨率越高,器件尺寸就可以做得越小。()

答案:

3.在MOSFET器件中,亚阈值摆幅越小,器件的性能越好。()

答案:

4.离子注入可以在不破坏硅片表面钝化层的情况下进行掺杂。()

半导体器件制造工艺参数监控考核试卷

考生姓名:________________答题日期:________________得分:_________________判卷人:_________________

一、单项选择题(本题共20小题,每小题1分,共20分,在每小题给出的四个选项中,只有一项是符合题目要求的)

答案:

6.离子注入工艺中,注入能量和______是控制注入深度的两个关键参数。

答案:

7.在半导体器件中,______是一种常用的钝化材料。

答案:

8.评估半导体器件漏电特性的常用测试方法是______。

答案:

9.半导体器件制造中,为了减小短沟道效应,可以采用______和______等方法。

答案:

10.在半导体器件的金属化工艺中,常用的金属有______、______和______等。

5.下列哪些因素会影响半导体器件的刻蚀速率?()

A.刻蚀气体类型

B.刻蚀功率

C.刻蚀压力

D.硅片温度

6.下列哪些材料可以用作半导体器件的绝缘层?()

A.硅氧化物

B.硅氮化物

C.硅碳化物

D.高介电常数材料

7.在半导体器件制造中,以下哪些方法可以用来减小器件的尺寸?()

发光二极管光取出原理及方法

Si (111) 衬底上的InGaN/ GaN MQW的TEM (a) 明场像; (b) 高分辨像

从图中可以看出量子阱为5 个周期,且阱( InGaN) 和垒( GaN) 界面明锐,表明生长的量子阱 结构质量良好;图 ( b) 是该样品InGaN/ GaNMQW 的高分辨像,由于In 原子对电子的原子 散射因子比Ga 原子的大,黑色条纹为阱( InGaN) ,白色条纹为垒( GaN) . 从图中观察,阱和垒 的厚度较为均匀,由标尺量得阱( InGaN) 层厚约为2nm ,垒( GaN)层厚约为815nm ,

2 改进材料的质量

• 外延在异质衬底上的GaN失陪位错和线

性位错密度一般位

,其他的晶体

缺陷包括晶界、堆垛层错,这些缺陷都

是非复合中心。会在带隙中引入能量态

和降低少数载流子的寿命。

• 缺陷会提高器件的阈值电压和反向漏电 流,降低载流子迁移率和热导率。这些

不利效应将阻止理想性能的复杂结构的、 大面积大功率器件的制备

•这样,人们开始在LED 中生长不同种类的DBR 结构来减小衬底 对光的吸收。材料的折射率与DBR 的反射效果有直接关系,折

射率差(Δn)越大,反射率R(p)越大,反射效果越好:

•DBR 的周期数也与反射率成正比,式中的p 是DBR 的对数

(pair),对数越高,反射效果越好。

3 制作透明衬底LED(TS-LED)

• 当加正向偏压时,势垒降低。 但由于p区和n区的禁带宽度 不等,势垒是不对称的。

• 加上正向偏压,如图19 (b),当两者的价带达到 等高时,p区的空穴由于不 存在势垒,不断向n区扩散, 保证了空穴(少数载流子) 向发光区的高注入效率。

sio2介电损耗1ghz

sio2介电损耗1ghz摘要:1.SiO2介电损耗的基本概念2.1GHz频率下SiO2的介电性能3.SiO2在不同频率下的介电损耗差异4.影响SiO2介电损耗的因素5.SiO2在实际应用中的优势和局限6.提高SiO2介电损耗的策略正文:随着科技的飞速发展,材料科学的研究越来越深入,SiO2作为一种常见的无机非晶材料,其介电性能在各个领域中得到了广泛的应用。

本文将探讨SiO2在1GHz频率下的介电损耗特性,并分析影响其性能的因素,以期为实际应用提供有价值的参考。

首先,我们需要了解SiO2的基本性质。

SiO2,即二氧化硅,是一种无机非晶材料,具有良好的绝缘性能和较高的机械强度。

在电子、微波等领域,SiO2被广泛应用于基板、封装材料等。

其介电损耗是衡量其在高频应用中性能的关键指标。

在1GHz频率下,SiO2的介电损耗表现出良好的性能。

实验研究表明,SiO2在1GHz频率下的介电损耗约为0.01~0.03。

这一数值较小,说明SiO2在高频应用中具有较低的损耗,能够满足大部分微波器件的需求。

然而,SiO2的介电损耗在不同频率下存在一定的差异。

随着频率的升高,SiO2的介电损耗会逐渐降低。

这是因为高频信号会导致SiO2内部微观结构的极化,从而减小损耗。

反之,低频信号下SiO2的极化程度较低,导致损耗较大。

影响SiO2介电损耗的因素主要包括以下几点:1.SiO2的微观结构:SiO2内部的微晶结构、颗粒尺寸、孔隙率等对其介电损耗有重要影响。

通过调控这些因素,可以有效提高SiO2的介电性能。

2.制备工艺:制备SiO2的方法有很多,如溶胶-凝胶法、化学气相沉积法等。

不同的制备工艺会对SiO2的介电损耗产生影响。

优化制备工艺,可以降低SiO2的介电损耗。

3.环境条件:如温度、湿度等环境因素也会影响SiO2的介电损耗。

一般情况下,温度升高会导致SiO2的介电损耗增加,而湿度对SiO2的介电性能影响较小。

尽管SiO2在1GHz频率下具有较低的介电损耗,但在高频应用中仍存在一定的局限。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关

键

词: 大功率 L E D;插指型 S i O 电流阻挡层 ;电流拥挤 ; 外 量子效率

文献标识码 : A D OI :1 0 . 3 7 8 8 / f g x b 2 0 1 7 3 8 0 6 . 0 7 8 6

d i o d e s( L E D s )a n d i mp r o v e i t s e x t e r n a l q u a n t u m e ic f i e n c y( E Q E) ,a S i O 2 c u r r e n t b l o c k i n g l a y e r ( C B L )w a s d e p o s i t e d b e t w e e r e n t c o n d u c t i v e l a y e r a n d p - G a N b y p l a s ma e n h a n c e d c h e m i c a l v a p o r d e p o s i t i o n( P E C V D) .A n i n t e r d i g i t a t e d S i O 2 C B L p a t t e r n w a s t h e n f a b r i c a t e d b y

中 图分 类 号 : T N 3 8 3

Ef f e c t o f I n t e r di g i t a t e d S i O2 Cu r r e n t Bl o c k i ng La y e r o n

E x t e r n a l Qu a n t u m Ef ic f i e n c y o f Hi g h P o we r L E Ds

p ho t o l i t h o g r a ph y a n d BOE we t e t c h i n g p r o c e s s .T he e f f e c t o f i n t e r d i g i t a t e d S i O2 CBL o n t h e c u r r e nt s pr e a d i n g p e r f o r ma n c e o f h i g h p o we r L ED wa s a n a l y z e d u s i n g c o mm e r c i a l S i muL ED pa c k a g e .I t i s

L I U Me n g — l i n g , G A O Y i — l i n ,H U H o n g — p o , L I U X i n g — t o n g , L Y U J i a — j i a n g , Z H E N G C h e n — j u ,D I N G X i n g — h u o , Z HO U S h e n g — i n n

第3 8卷

第 6期

发 光 学 报

CHI NES E J oURNAL OF L UM I NES CENCE

V0 1 . 38 No .6

2 0 1 7年 6月

J u n e, 2 0 1 7

文章编号 : 1 0 0 0 - 7 0 3 2 ( 2 0 1 7 ) 0 6 - 0 7 8 6 - 0 7

Co r r e s p o n di n g Au t h o r ,E・ ma U:z h o @ wh u . e d u . c n

Ab s t r ac t:I n o r d e r t o a l l e v i a t e C t u T e n t c r o wd i ng a r o u n d p- e l e c t r o de o f h i g h p o we r bl ue l i g h t — e mi t t i n g

透 明导 电层 与 p - G a N间沉积插指型 S i O ,电流 阻 挡 层 。 采 用 等 离 子 体 增 强 化 学 气 相 沉 积 的 方 法 沉 积 S i O 薄

膜, 再经过光刻和 B O E湿 法刻蚀技术制备插指型 S i O 电流阻挡层 。采用 S i m u L E D仿真软件分析插指 型 S i O : 电流阻挡层对大功率 L E D芯片 电流扩展性 能的影响 , 研究插指 型 S i O : 电流阻挡层对大功率 L E D芯片外量 子 效 率的影响 。结果发现 , 插 指型 S i O 电流阻挡层结构 可以有 效改善 P电极 附近 的电流拥 挤现象 。与没有 沉 积插指 型 S i O 电流阻挡层的大功率 L E D芯 片相 比, 光输 出功率得 到显 著的提高 。在 3 5 0 l n A的输入 电流下 ,

( W u h a n U n i v e r s i t y, S c h o o l o f P o w e r a n d Me c h a n i c a l E n g i n e e r i n g,W u h a n 4 3 0 0 7 2 ,C h i n a )

插指型 S i O 2电 流阻 挡 层 对 大 功 率 L E D外 量 子 效 率 的影 响

刘 梦 玲 ,高 艺 霖 , 胡红坡 , 刘 星 童 ,吕家 将 , 郑 晨 居 ,丁 星 火 , 周圣 军

( 武汉 大学 动2- q ̄ k 械学 院,湖北 武汉 4 3 0 0 7 2 )

摘要 : 为了改善蓝光大功率 L E D芯片 P电极处的电流拥挤现象, 提高大功率 L E D芯片的外量子效率, 在I T O