NCV7517FTG;NCV7517FTR2G;中文规格书,Datasheet资料

NCV8450STT3G;中文规格书,Datasheet资料

NCV8450, NCV8450ASelf-Protected High Side Driver with Temperatureand Current LimitThe NCV8450/A is a fully protected High−Side Smart Discrete device with a typical R DS(on) of 1.0 W and an internal current limit of 0.8 A typical. The device can switch a wide variety of resistive, inductive, and capacitive loads.Features•Short Circuit Protection•Thermal Shutdown with Automatic Restart •Overvoltage Protection•Integrated Clamp for Inductive Switching•Loss of Ground Protection•ESD Protection•Slew Rate Control for Low EMI•Very Low Standby Current•NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q100 Qualified and PPAP Capable•This is a Pb−Free DeviceTypical Applications•Automotive•IndustrialPRODUCT SUMMARYSymbolCharacteristics Value Unit V IN_CL Overvoltage Protection54V V D(on)Operation Voltage 4.5 − 45V R on On−State Resistance 1.0WMARKINGDIAGRAM1AYWXXXXX GGXXXXX= V8450 or 8450AA= Assembly LocationY= YearW= Work WeekG= Pb−Free Package(Note: Microdot may be in either location)SOT−223(TO−261)CASE 318ESee detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.ORDERING INFORMATIONFigure 1. Block Diagram V (Pins 2, 4)OUT(Pin 3)IN(Pin 1)PACKAGE PIN DESCRIPTIONPin #Symbol Description1IN Control Input, Active Low2V D Supply Voltage3OUT Output4V D Supply VoltageMAXIMUM RATINGSRatingSymbol ValueUnit Min Max DC Supply Voltage (Note 1)V D −1645V Load Dump Protection(RI = 2 W , t d = 400 ms, V IN = 0, 10 V, I L = 150 mA, V bb = 13.5 V)V Loaddump100V Input CurrentIin −1515mAOutput Current (Note 1)I out Internally Limited A Total Power Dissipation@ T A = 25°C (Note 2)@ T A = 25°C (Note 3)P D1.131.60WElectrostatic Discharge (Note 4)(Human Body Model (HBM) 100 pF/1500 W )Input All other15kVSingle Pulse Inductive Load Switching Energy (Note 4)(V DD = 13.5 V, I = 465 mApk, L = 200 mH, T JStart = 150°C)E AS 29mJ Operating Junction Temperature T J −40+150°C Storage TemperatureT storage−55+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Reverse Output current has to be limited by the load to stay within absolute maximum ratings and thermal performance.2.Minimum Pad.3. 1 in square pad size, FR −4, 1 oz Cu.4.Not subjected to production testing.THERMAL RESISTANCE RATINGSParameterSymbol Max Value Unit Thermal Resistance (Note 5)Junction −to −Ambient (Note 2)Junction −to −Ambient (Note 3)R q JA R q JA11078.3K/W5.Not subjected to production testing.Figure 2. Applications Test CircuitELECTRICAL CHARACTERISTICS (6 v V D v 45 V; −40°C <T J < 150°C unless otherwise specified)Rating Symbol ConditionsValueUnit Min Typ MaxOUTPUT CHARACTERISTICSOperating Supply Voltage V SUPPLY 4.5−45VOn Resistance(Pin 1 Connected to GND)R ON T J = 25°C , I OUT = 150 mA, V D = 7 V − 45 VT J = 150°C, I OUT = 150 mA, V D = 7 V − 45 V(Note 6)T J = 25°C , I OUT= 150 mA, V D = 6 V1.01.41.1232.1WStandby Current (Pin 1 Open)I D V D v 20 VV D> 20 V 0.610100m AINPUT CHARACTERISTICSInput Current – Off State I IN_OFF V OUT v 0.1 V, R L = 270 W, T J = 25°CV OUT v 0.1V, R L= 270 W, T J = 150°C (Note 6)−50−40m AInput Current – On State(Pin 1 Grounded)I IN_ON 1.53mA Input Resistance (Note 6)R IN1k W SWITCHING CHARACTERISTICSTurn−On Time (Note 7)(V IN = V D to 0 V) to 90% V OUT t ON R L = 270 W(Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C30125100m sTurn−Off Time (Note 7)(V IN= 0 V to V D) to 10% V OUT t OFF R L = 270 W (Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C60175150m sSlew Rate On (Note 7)(V IN = V D to 0V) 10% to 30% V OUT dV/dt ON R L = 270 W(Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C0.744V/m sSlew Rate Off (Note 7)(V IN= 0 V to V D) 70% to 40% V OUT dV/dt OFF R L = 270 W (Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C0.944V/m sOUTPUT DIODE CHARACTERISTICS (Note 6)Drain−Source Diode Voltage V F I OUT = −0.2 A0.6V Continuous Reverse DrainCurrentI S T J = 25°C0.2A PROTECTION FUNCTIONS (Note 8)Temperature Shutdown (Note 6)T SD150175−°C Temperature ShutdownHysteresis (Note 6)T SD_HYST5°COutput Current Limit I LIM T J = −40°C, V D = 13.5 V, t m = 100 m s (Note 6)T J = 25 °C, V D = 13.5 V, t m = 100 m sT J = 150 °C , V D = 13.5 V, t m = 100 m s (Note 6)0.50.81.5AOutput Clamp Voltage(Inductive Load Switch Off)At V OUT = V D− V CLAMPV CLAMP I OUT = 4 mA4552VOvervoltage Protection V IN_CL I CLAMP = 4 mA5054V6.Not subjected to production testing7.Only valid with high input slew rates8.Protection functions are not designed for continuous repetitive operation and are considered outside normal operating rangeR D S (o n ) (W )TEMPERATURE (°C)Figure 3. R DS(on) vs. TemperatureR D S (o n ) (W )OUTPUT LOAD (A)Figure 4. R DS(on) vs. Output LoadV D (V)Figure 5. R DS(on) vs. V DR D S (o n ) (W )1020304050607080T U R N O N T I M E (m s )TEMPERATURE (°C)Figure 6. Turn On Time vs. TemperatureTEMPERATURE (°C)Figure 7. Turn Off Time vs. TemperatureT U R N O F F T I M E (m s )S L E W R A T E (O N ) (V /m s )TEMPERATURE (°C)Figure 8. Slew Rate (ON) vs. Temperature−40−20020406080100120140−40−20020406080100120140−TEMPERATURE (°C)Figure 9. Slew Rate (OFF) vs. Temperature S L E W R A T E (O F F ) (V /m s )TEMPERATURE (°C)Figure 10. Current Limit vs. TemperatureC U R R E N T L I M I T (A )P E A K S C C U R R E N T (A )V D , VOLTAGE (V)Figure 11. Peak Short Circuit Current vs. V DVoltageTEMPERATURE (°C)Figure 12. V D Leakage Current vs.Temperature Off −StateV D , L E A K A G E C U R R E N T (m A )V D , L E A K A G E C U R R E N T (m A )V D , VOLTAGE (V)Figure 13. V D Leakage Current vs. V D VoltageOff −State TEMPERATURE (°C)Figure 14. On −State Input Current vs.TemperatureI N P U T C U R R E N T (m A )V D , VOLTAGE (V)Figure 15. Output Voltage vs. V D VoltageO U T P U T V O L T A G E (V )V D , VOLTAGE (V)Figure 16. Input Current vs. V D VoltageOn −StateI N P U T C U R R E N T (m A )LOAD INDUCTANCE (mH)Figure 17. Single Pulse Maximum Switch −offCurrent vs. Load InductanceC U R R E N T (m A )V D , VOLTAGE (V)Figure 18. Input Current vs. V D VoltageOff −StateI N P U T C U R R E N T (m A )−S H U T D O W N T I M E (m s )TEMPERATURE (°C)Figure 19. Initial Short −Circuit Shutdown Timevs. TemperaturePULSE TIME (s)R (t ), E F F E C T I V E T R A N S I E N T T H E R M AL R E S P O N S ECOPPER HEAT SPREADER AREA (mm 2)R q J A (°C /W )06080100120140Figure 20. R q JA vs. Copper Area2040Figure 21. Transient Thermal ResponseISO PULSE TEST RESULTSTest PulseTest Level Test ResultsPulse Cycle Time and Generator Impedance1200 V C 500 ms, 10 W 2150 V C 500 ms, 10 W 3a 200 V C 100 ms, 50 W 3b 200 V C 100 ms, 50 W 5175 VE(100 V)400 ms, 2 WORDERING INFORMATIONDevicePackage Shipping †NCV8450STT3G SOT −223(Pb −Free)4000 / Tape & Reel NCV8450ASTT3GSOT −223(Pb −Free)4000 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSSOT −223 (TO −261)CASE 318E −04ISSUE MNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.DIM A MIN NOM MAX MIN MILLIMETERS1.50 1.63 1.750.060INCHESA10.020.060.100.001b 0.600.750.890.024b1 2.90 3.06 3.200.115c 0.240.290.350.009D 6.30 6.50 6.700.249E 3.30 3.50 3.700.130e 2.20 2.30 2.400.0870.850.94 1.050.0330.0640.0680.0020.0040.0300.0350.1210.1260.0120.0140.2560.2630.1380.1450.0910.0940.0370.041NOM MAX L1 1.50 1.75 2.000.0606.707.007.300.2640.0690.0780.2760.287H E−−e10°10°0°10°q*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息: ONSEMINCV8450STT3G。

ANALOG DEVICES ADV7513 英文产品数据手册

165 MHz, High PerformanceHDMI Transmitter Data Sheet ADV7513Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. O ne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.FEATURESGeneralIncorporates HDMI v1.4 features, including3D video support165 MHz supports all video formats up to 1080pand UXGASupports gamut metadata packet transmission Integrated CEC buffer/controllerCompatible with DVI v1.0 and HDCP v1.4Video/audio inputs accept logic levels from 1.8 V to 3.3 V Digital video3D video readyProgrammable, 2-way color space converterSupports RGB, YCbCr, and DDRSupports ITU-656-based embedded syncsAutomatic input video format timing detection (CEA-861-E) Digital audioSupports standard S/PDIF for stereo linear pulse codemodulation (LPCM) or compressed audio up to 192 kHz High bit rate (HBR) audio8-channel uncompressed LPCM I2S audio up to 192 kHz Special features for easy system design5 V tolerant I2C and Hot Plug™ detect (HPD) I/Os,no extra device neededNo audio master clock needed for supporting S/PDIFand I2SOn-chip MPU with I2C master performs HDCP operationsand EDID reading operationsOn-chip MPU reports HDMI events through interruptsand registersAPPLICATIONSGaming consolesPCsDVD players and recordersDigital set-top boxesA/V receiversFUNCTIONAL BLOCK DIAGRAM1225-1Figure 1.GENERAL DESCRIPTIONThe ADV7513 is a 165 MHz, High-Definition Multimedia Interface (HDMI®) transmitter that is ideal for DVD players/ recorders, digital set-top boxes, A/V receivers, gaming consoles, and PCs.The digital video interface contains an HDMI v1.4/DVI v1.0-compatible transmitter and supports all HDTV formats. The ADV7513 supports HDMI v1.4-specific features, including 3D video. The ADV7513 also supports x.v.Color™, high bit rate (HBR) audio, and the programmable auxiliary video information (AVI) InfoFrame features. With the inclusion of HDCP, the ADV7513 allows the secure transmission of protected content as specified by the HDCP v1.4 protocol.The ADV7513 supports both S/PDIF and 8-channel I2S audio. Its high fidelity 8-channel I2S interface can transmit either stereo or 7.1 surround audio up to 768 kHz. The S/PDIF interface can carry compressed audio, including Dolby® Digital, DTS®, and THX®. Fabricated in an advanced CMOS process, the ADV7513 is provided in a 64-lead LQFP surface-mount plastic package with exposed pad and is specified over the −25°C to +85°C temperature range.ADV7513Data SheetRev. 0 | Page 2 of 12TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Electrical Specifications (3)Absolute Maximum Ratings ............................................................5 Explanation of Test Levels ............................................................5 ESD Caution...................................................................................5 Pin Configuration and Function Descriptions ..............................6 Applications Information .................................................................8 Design Resources ..........................................................................8 Outline Dimensions ..........................................................................9 Ordering Guide .. (9)REVISION HISTORY11/11—Revision 0: Initial VersionData SheetADV7513Rev. 0 | Page 3 of 12SPECIFICATIONSELECTRICAL SPECIFICATIONSTable 1.Parameter Symbol Temp Test Level 1 Min Typ Max Unit DIGITAL INPUTS Data Inputs, Video and Audio, CEC_CLK Input Voltage, High V IH Full VI 1.35 3.5 V Input Voltage, Low V IL Full VI −0.3 +0.7 V Input Capacitance 25°C VIII 1.0 1.5 pFCEC_CLK Frequency 2Full VIII 3 12 100 MHz CEC_CL KAccuracy Full VIII −2 +2 % DDC I 2C Lines (DDCSDA, DDCSCL) Input Voltage, High V IH Full IV 1.4 5.5 V Input Voltage, Low V IL Full IV −0.3 +0.7 V I 2C Lines (SDA, SCL) Input Voltage, High V IH Full VI 1.4 5.5 V Input Voltage, Low V IL Full VI −0.3 +0.7 V CEC Pin Input Voltage, High V IH Full VI 2.0 5.5 V Input Voltage, Low V IL Full VI −0.3 +0.8 V Output Voltage, High V OH Full VI 2.5 3.63 V Output Voltage, Low V OL Full VI −0.3 +0.6 V HPD Pin Input Voltage, High V IH Full VI 1.3 5.5 V Input Voltage, Low V IL Full VI −0.3 +0.8 V THERMAL CHARACTERISTICS Thermal Resistance Junction-to-Case θJC Full V 20 °C/W Junction-to-Ambient θJA Full V 43 °C/W Ambient Temperature Full V −25 +25 +85 °C DC SPECIFICATIONS Input Leakage Current I IL 25°C VI −1 +1 μA POWER SUPPLY1.8 V Supply Voltage (DVDD, AVDD,PVDD, BGVDD)Full IV 1.71 1.8 1.90 V 3.3 V Supply Voltage (DVDD_3V) Full IV 3.15 3.3 3.45 V Power-Down Current 25°C IV 300 μATransmitter Total Power 3At 1.8 V Full VI 256 mW At 3.3 V Full VI 1 mW AC SPECIFICATIONS TMDS Output Clock Frequency 25°C IV 20 165 MHz TMDS Output Clock Duty Cycle 25°C IV 48 52 % Input Video Clock Frequency Full IV 165 MHzInput Video Data Setup Time 4t VSU Full IV 1.8 ns Input Video Data Hold Time 4 t VHLD Full IV 1.3 ns TMDS Differential Swing 25°C VII 800 1100 1200 mV Differential Output Timing Low-to-High Transition Time 25°C VII 75 95 ps High-to-Low Transition Time 25°C VII 75 95 ps VSYNC and HSYNC Delay From DE Falling Edge 25°C IV 1 UI 5 To DE Rising Edge 25°C IV 1 UI 5ADV7513Data SheetRev. 0 | Page 4 of 12Parameter Symbol Temp Test Level 1 Min Typ Max Unit AUDIO AC TIMING SCLK Duty Cycle N/2 Is an Even Number Full IV 40 50 60 % N/2 Is an Odd Number Full IV 49 50 51 % I2S[3:0], S/PDIF Setup Time t ASU Full IV 2 ns I2S[3:0], S/PDIF Hold Time t AHLD Full IV 2 ns LRCLK Setup Time t ASU Full IV 2 ns LRCLK Hold Time t AHLD Full IV 2 ns I 2C INTERFACE SCL Clock Frequency Full 400 kHz SDA Setup Time t DSU Full 100 ns SDA Hold Time t DHO Full 100 ns Setup Time for Start Condition t STASU Full 0.6 μs Hold Time for Start Condition t STAH Full 0.6 μs Setup Time for Stop Condition t STOSU Full 0.6 μs1 See the Explanation of Test Levels section.212 MHz crystal oscillator for default register settings. 31080p, 24-bit typical random pattern. 4The video data setup and hold times are measured at 0.9 V. The relationship between the clock and data is programmable in 400 ps steps. 5UI is the unit interval.Data SheetADV7513Rev. 0 | Page 5 of 12ABSOLUTE MAXIMUM RATINGSTable 2.Parameter RatingDigital Inputs (SDA, SCL, DDCSDA, DDCSCL,HPD, PD)−0.3 V to +5.5 V Audio/Video Digital Inputs (D[23:0], MCLK,CLK, LRCLK, CEC, CEC_CLK, SPDIF, I2S[3:0],SCLK, HSYNC, DE, VSYNC)−0.3 V to +3.63 V Digital Output Current 20 mAOperating Temperature Range −40°C to +100°CStorage Temperature Range −65°C to +150°C Maximum Junction Temperature 150°C Maximum Case Temperature 150°CStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. EXPLANATION OF TEST LEVELSI. 100% production tested. II. 100% production tested at 25°C and sample tested at specified temperatures. III. Sample tested only. IV . Parameter is guaranteed by design and characterizationtesting.V . Parameter is a typical value only. VI.100% production tested at 25°C; guaranteed by design and characterization testing.VII.Limits defined by HDMI specification; guaranteed by design and characterization testing.VIII. Parameter is guaranteed by design.ESD CAUTIONADV7513Data SheetRev. 0 | Page 6 of 12DVDD D12T X C –H S Y N CPIN CONFIGURATION AND FUNCTION DESCRIPTIONSD ED 0D 1D 2D 3D 4D 5D 6D 7D 8C L KD 9D V D DD 10D 11VSYNC SPDIF MCLK I2S0I2S1I2S2I2S3SCLKLRCLK PVDD DVDD BGVDD R_EXT AVDD HPD D13D14D15D16D17D18D19D20D21D22D23SDA SCL DDCSDA DDCSCLT X C +A V D DT X 0–T X 0+P DT X 1–T X 1+A V D DT X 2–T X 2+I N TD V D D _3VC E CD V D DC E C _C L KNOTES1. THE EXPOSED PAD IS THE ELECTRICAL GROUND FOR THE PART AND MUST BE SOLDERED TO THE PCB.10225-002Figure 2. Pin ConfigurationTable 3. Pin Function DescriptionsPin No. Mnemonic Type Description 1, 11, 31, 51 DVDD Power 1.8 V Power Supply. These pins should be filtered and as quiet as possible. 2 VSYNC Input Vertical Synchronization Input. 3 SPDIF Input S/PDIF (Sony/Philips Digital Interface) Audio Input. 4 MCLK Input Audio Reference Clock Input. 5 I2S0 Input I 2S Channel 0 Audio Data Input. 6 I2S1 Input I 2S Channel 1 Audio Data Input. 7 I2S2 Input I 2S Channel 2 Audio Data Input. 8 I2S3 Input I 2S Channel 3 Audio Data Input. 9 SCL KInput I 2S Audio Clock Input. 10 LRCLK Input Left/Right Channel Signal Input. 12 PVDD Power 1.8 V PLL Power Supply. 13 BGVDD Power 1.8 V Band Gap Power Supply. 14 R_EXT Input This pin sets the internal reference currents. 15, 19, 25 AVDD Power 1.8 V Power Supply for TMDS Outputs. 16 HPD Input Hot Plug Detect Signal Input. 17, 18 TXC−, TXC+ DifferentialoutputDifferential TMDS Clock Output. 20, 21 TX0−, TX0+ DifferentialoutputDifferential TMDS Output Channel 0. 22 PD Input Power-Down Control and I 2C Address Selection. 23, 24 TX1−, TX1+ DifferentialoutputDifferential TMDS Output Channel 1. 26, 27 TX2−, TX2+ DifferentialoutputDifferential TMDS Output Channel 2.Data SheetADV7513Rev. 0 | Page 7 of 12Pin No. Mnemonic Type Description 28 INT Output Interrupt Signal Output. 29 DVDD_3V Power 3.3 V Power Supply. 30 CEC Input/output CEC Data Signal. 32 CEC_CLK Input CEC Clock (Oscillator from 3 MHz to 100 MHz). 33 DDCSCL Control Serial Port Data Clock to Sink. 34 DDCSDA Control Serial Port Data Input/Output to Sink. 35 SCL Control Serial Port Data Clock Input. 36 SDA Control Serial Port Data Input/Output.37 to 50, 52, 54 to 62 D[23:0]Input Video Data Inputs. 53 CLK Input Video Input Clock. 63 DE Input Data Enable Signal for Digital Video. 64 HSYNC Input Horizontal Synchronization Input. EPAD Power The exposed pad is the electrical ground for the part and must be soldered to the PCB.ADV7513Data SheetRev. 0 | Page 8 of 12APPLICATIONS INFORMATIONDESIGN RESOURCESEvaluation kits, reference design schematics, hardware and soft-ware guides, and other support documentation are available under a nondisclosure agreement (NDA). For more information, contact ATV_VideoTx_Apps@ . Other references include the following: •EIA/CEA-861-E —this technical specification document describes audio and video InfoFrames, as well as the E-EDID structure for HDMI. It is available from the Consumer Electronics Association (CEA).•High-Definition Multimedia Interface SpecificationVersion 1.4, a defining document for HDMI v1.4, and the HDMI Compliance Test Specification (CTS) Version 1.3a are available from HDMI Licensing, LLC.•High-Bandwidth Digital Content Protection SystemRevision 1.4, the defining technical specification document for HDCP Revision 1.4, is available from Digital Content Protection, LLC.Data SheetADV7513Rev. 0 | Page 9 of 12OUTLINE DIMENSIONSCOMPLIANT TO JEDEC STANDARDS MS-026-BCD-HD03-16-2010-AVIEW AROTATED 90°CCWFOR PROPER CONNECTION OF THE EXPOSED PAD,REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONSSECTION OF THIS DATA SHEET.Figure 3. 64-Lead Low Profile Quad Flat Package [LQFP_EP](SW-64-2)Dimensions shown in millimetersORDERING GUIDEModel 1Temperature Range Package DescriptionPackage Option ADV7513BSWZ −25°C to +85°C 64-Lead Low Profile Quad Flat Package, Exposed Pad [LQFP_EP] SW-64-2 EVAL-ADV7513-AKZEvaluation kit with HDCP keys1Z = RoHS Compliant Part.ADV7513 Data Sheet NOTESRev. 0 | Page 10 of 12Data Sheet ADV7513 NOTESRev. 0 | Page 11 of 12ADV7513Data SheetRev. 0 | Page 12 of 12 NOTESI 2C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).HDMI, the HDMI Logo, and High-Definition Multimedia Interface are trademarks or registered trademarks of HDMI Licensing LLC in the United States and other countries.©2011 Analog Devices, Inc. All rights reserved. Trademarks andregistered trademarks are the property of their respective owners.D10225-0-11/11(0)。

NCV7517BFTR2G;中文规格书,Datasheet资料

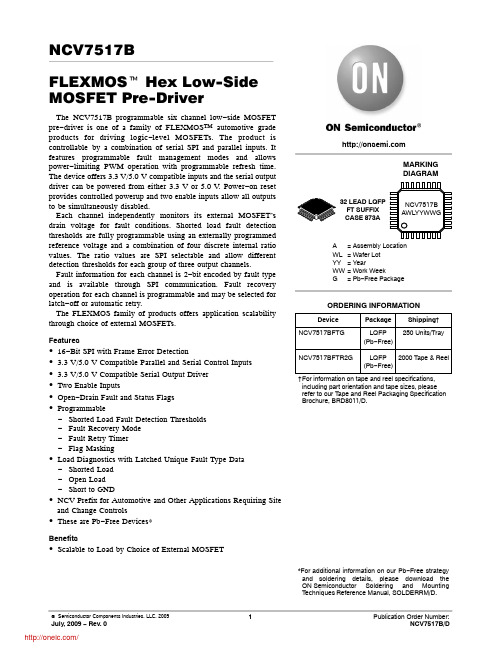

NCV7517BFLEXMOS t Hex Low-Side MOSFET Pre-DriverThe NCV7517B programmable six channel low−side MOSFET pre−driver is one of a family of FLEXMOS TM automotive grade products for driving logic−level MOSFETs. The product is controllable by a combination of serial SPI and parallel inputs. It features programmable fault management modes and allows power−limiting PWM operation with programmable refresh time. The device offers 3.3 V/5.0 V compatible inputs and the serial output driver can be powered from either 3.3 V or 5.0 V. Power−on resetprovides controlled powerup and two enable inputs allow all outputs to be simultaneously disabled.Each channel independently monitors its external MOSFET’s drain voltage for fault conditions. Shorted load fault detection thresholds are fully programmable using an externally programmed reference voltage and a combination of four discrete internal ratio values. The ratio values are SPI selectable and allow different detection thresholds for each group of three output channels.Fault information for each channel is 2−bit encoded by fault type and is available through SPI communication. Fault recovery operation for each channel is programmable and may be selected for latch−off or automatic retry.The FLEXMOS family of products offers application scalability through choice of external MOSFETs.Features•16−Bit SPI with Frame Error Detection•3.3 V/5.0 V Compatible Parallel and Serial Control Inputs •3.3 V/5.0 V Compatible Serial Output Driver•Two Enable Inputs•Open−Drain Fault and Status Flags•Programmable−Shorted Load Fault Detection Thresholds−Fault Recovery Mode−Fault Retry Timer−Flag Masking•Load Diagnostics with Latched Unique Fault Type Data−Shorted Load−Open Load−Short to GND•NCV Prefix for Automotive and Other Applications Requiring Site and Change Controls•These are Pb−Free Devices*Benefits•Scalable to Load by Choice of External MOSFET32 LEAD LQFPFT SUFFIXCASE 873AMARKINGDIAGRAMDevice Package Shipping†ORDERING INFORMATIONNCV7517BFTG LQFP(Pb−Free)250 Units/Tray†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specification Brochure, BRD8011/D.NCV7517BAWLYYWWGA= Assembly LocationWL= Wafer LotYY= YearWW= Work WeekG= Pb−Free PackageNCV7517BFTR2G LQFP(Pb−Free)2000 T ape & Reel*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting T echniques Reference Manual, SOLDERRM/D.Figure 1. Block DiagramFigure 2. Application DiagramPIN FUNCTION DESCRIPTIONSymbol DescriptionFLTREF Analog Fault Detect Threshold: 5.0 V Compliant DRN0 – DRN5Analog Drain Feedback: Internally ClampedGAT0 – GAT5Analog Gate Drive: 5.0 V CompliantENA1, ENA2Digital Master Enable Inputs: 3.3 V/5.0 V (TTL) CompatibleIN0 – IN5Digital Parallel Input: 3.3 V/5.0 V (TTL) CompatibleCSB Digital Chip Select Input: 3.3 V/5.0 V (TTL) CompatibleSCLK Digital Shift Clock Input: 3.3 V/5.0 V (TTL) CompatibleSI Digital Serial Data Input: 3.3 V/5.0 V (TTL) CompatibleSO Digital Serial Data Output: 3.3 V/5.0 V CompliantSTAB Digital Open−Drain Output: 3.3 V/5.0 V CompliantFLTB Digital Open−Drain Output: 3.3 V/5.0 V CompliantVCC1Power Supply − Low Power PathGND Power Return − Low Power Path – Device SubstrateVCC2Power Supply − Gate DriversVDD Power Supply − Serial Output DriverVSS Power Return – VCC2, VDD, Drain ClampsFigure 3. 32 Pin LQFP Pinout (Top View)MAXIMUM RATINGS(Voltages are with respect to device substrate.)Rating Value UnitDC Supply (V CC1, V CC2, V DD)−0.3 to 6.5V Difference Between V CC1 and V CC2"0.3V Difference Between GND (Substrate) and V SS"0.3VOutput Voltage (Any Output)−0.3 to 6.5VDrain Feedback Clamp Voltage (Note 1)−0.3 to 47VDrain Feedback Clamp Current (Note 1)10mAInput Voltage (Any Input)−0.3 to 6.5V Junction T emperature, T J−40 to 150°C Storage T emperature, T STG−65 to 150°CPeak Reflow Soldering T emperature: Lead−Free60 to 150 seconds at 217°C (Note 2)260 peak°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.ATTRIBUTESCharacteristic ValueESD CapabilityHuman Body Model Machine Model w" 2.0 kV w" 200 VMoisture Sensitivity (Note 2)MSL3 Package Thermal Resistance (Note 3)Junction–to–Ambient, R q JA Junction–to–Pin, R Y JL 86.0 °C/W 58.5 °C/W1.An external series resistor must be connected between the MOSFET drain and the feedback input in the application. Total clamp powerdissipation is limited by the maximum junction temperature, the application environment temperature, and the package thermal resistances.2.For additional information, see or download ON Semiconductor’s Soldering and Mounting T echniques Reference Manual, SOLDERRM/D, andApplication Note AND8003/D.3.Values represent still air steady−state thermal performance on a 4 layer (42 x 42 x 1.5 mm) PCB with 1 oz. copper on an FR4 substrate, usinga minimum width signal trace pattern (384 mm2 trace area).RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC1Main Power Supply Voltage 4.75 5.25V V CC2Gate Drivers Power Supply Voltage V CC1− 0.3V CC1+ 0.3VV DD Serial Output Driver Power Supply Voltage 3.0V CC1V V IN High Logic High Input Voltage 2.0V CC1V V IN Low Logic Low Input Voltage00.8VT A Ambient Still−Air Operating T emperature−40125°CELECTRICAL CHARACTERISTICS (4.75 V v V CCX v5.25 V, V DD = V CCX, −40°C v T J v125°C, unless otherwise specified.) (Note 4) Characteristic Symbol Conditions Min Typ Max Unit V CC1 SupplyOperating Current –V CC1= 5.25 V, V FLTREF=1.0 V ENA X= 0ENA1= ENA2= V CC1,V DRNX= 0 V, GAT X drivers offENA1= ENA2= V CC1,GAT X drivers on–––2.803.102.805.05.05.0mAPower−On Reset Threshold V CC1 Rising 3.65 4.20 4.60V Power−On Reset Hysteresis−0.1500.385–V Digital I/OV IN High ENA X, IN X, SI, SCLK, CSB 2.0––V V IN Low ENA X, IN X, SI, SCLK, CSB––0.8V V IN Hysteresis ENA X, IN X, SI, SCLK, CSB100330500mV Input Pullup Current CSB V IN= 0 V−25−10–m A Input Pulldown Current ENA2, IN X, SI, SCLK,V IN= V CC1–1025m A Input Pulldown Resistance ENA1100150200k W SO Low Voltage V DD= 3.3 V, I SINK= 5.0 mA–0.110.25VSO High Voltage V DD= 3.3 V, I SOURCE= 5.0 mA V DD−0.25V DD−0.11–VSO Output Resistance Output High or Low–22–W SO Tri−State Leakage Current CSB = 3.3 V−10–10m A STAB Low Voltage STAB Active, I STAB= 1.25 mA–0.10.25V STAB Leakage Current V STAB= V CC1––10m A FLTB Low Voltage FLTB Active, I FLTB= 1.25 mA–0.10.25V FLTB Leakage Current V FLTB= V CC1––10m A Fault Detection – GAT X ONFLTREF Input Current V FLTREF=0 V−1.0––m A FLTREF Input Linear Range(Note 5)0–V CC1−2.0V FLTREF Op−amp V CC1 PSRR(Note 5)30––dBDRN X Clamp Voltage V CL I DRNX= 10 m AI DRNX= I CL(MAX) = 10 mA 27–3442–47VDRN X Shorted Load Threshold GAT X Output HighV FLTREF= 1.0 V Register 2: R1= 0, R0= 0 orR4= 0, R3= 0202530%V FLTREF Register 2: R1= 0, R0= 1 orR4= 0, R3= 1455055%V FLTREF Register 2: R1= 1, R0= 0 orR4= 1, R3= 0707580%V FLTREF Register 2: R1= 1, R0= 1 orR4= 1, R3= 195100105%V FLTREFDRN X Input Leakage Current V CC1= V CC2= V DD= 5.0 V,ENA X= IN X= 0 V,V DRNX = V CL(MIN)V CC1= V CC2= V DD= 0 V,ENA X= IN X= 0 V,V DRNX = V CL(MIN)−1.0– 1.0m A4.Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100%parametrically tested in production.5.Guaranteed by design.Characteristic Symbol Conditions Min Typ Max UnitFault Detection – GAT X OFFDRN X Diagnostic Current I SG Short to GND Detection,V DRNX= 0.30 V CC1−27−20−10m AI OL Open Load Detection,V DRNX= 0.75 V CC1306080m A DRN X Fault Threshold Voltage V SG Short to GND Detection273033%V CC1V OL Open Load Detection727578%V CC1DRN X Off State Bias Voltage V CTR−–50–%V CC1 Gate Driver OutputsGAT X Output Resistance Output High or Low200350500W GAT X High Output Current V GATX = 0 V−26.25–−9.5mA GAT X Low Output Current V GATX = V CC29.5–26.25mATurn−On Propagation Delay t P(ON)IN X to GAT X (Figure 4)–– 1.0m sCSB to GAT X (Figure 5)Turn−Off Propagation Delay t P(OFF)IN X to GAT X (Figure 4)–– 1.0m sCSB to GAT X (Figure 5)Output Rise Time t R20% to 80% of V CC2,C LOAD = 400 pF(Figure 4, Note 5)––277nsOutput Fall Time t F80% to 20% of V CC2,C LOAD = 400 pF(Figure 4, Note 5)––277nsFault TimersChannel Fault Blanking Timer t BL(ON)V DRNX = 5.0 V; IN X rising toFLTB falling (Figure 6)112131m st BL(OFF)V DRNX = 0 V; IN X falling toFLTB falling (Figure 6)90120150m s Channel Fault Filter Timer t FF Figure 77.01217m sGlobal Fault Refresh Timer (Auto−retry Mode)t FR Register 2: Bit R2= 0 or R5= 07.51012.5ms Register 2: Bit R2 = 1 or R5 = 1304050msTimer Clock ENA1 = 1–500–kHzSerial Peripheral Interface (Figure 9) V ccx = 5.0 V, V DD = 3.3 V, F SCLK = 4.0 MHz, C LOAD = 200 pFSO Supply Voltage V DD 3.3 V Interface 3.0 3.3 3.6V5.0 V Interface 4.5 5.0 5.5VSCLK Clock Period−–250–nsMaximum Input Capacitance Sl, SCLK (Note 7)––12pFSCLK High Time SCLK = 2.0 V to 2.0 V125––nsSCLK Low Time SCLK = 0.8 V to 0.8 V125––nsSl Setup Time Sl = 0.8 V/2.0 V toSCLK = 2.0 V (Note 7)25––nsSl Hold Time SCLK = 2.0 V toSl = 0.8 V/2.0 V (Note 7)25––ns6.Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100%parametrically tested in production.7.Guaranteed by design.Characteristic Symbol Conditions Min Typ Max UnitSerial Peripheral Interface (continued) (Figure 9) V ccx = 5.0 V, V DD = 3.3 V, F SCLK = 4.0 MHz, C LOAD = 200 pF–2550ns SO Rise Time(20% V SO to 80% V DD)C LOAD = 200 pF (Note 9)––50ns SO Fall Time(80% V SO to 20% V DD)C LOAD = 200 pF (Note 9)CSB Setup Time CSB = 0.8 V to SCLK = 2.0 V60––ns(Note 9)75––ns CSB Hold Time SCLK = 0.8 V to CSB = 2.0 V(Note 9)CSB to SO Time CSB = 0.8 V to SO Data Valid–65125ns(Note 9)–65125ns SO Delay Time SCLK = 0.8 V to SO Data Valid(Note 9)Transfer Delay Time CSB Rising Edge to Next1.0––m sFalling Edge (Note 9)8.Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100%parametrically tested in production.9.Guaranteed by design.Figure 4. Gate Driver Timing Diagram – Parallel InputFigure 5. Gate Driver Timing Diagram – Serial InputFigure 6. Blanking Timing DiagramFigure 7. Filter Timing DiagramFigure 9. SPI Timing Diagram分销商库存信息: ONSEMINCV7517BFTR2G。

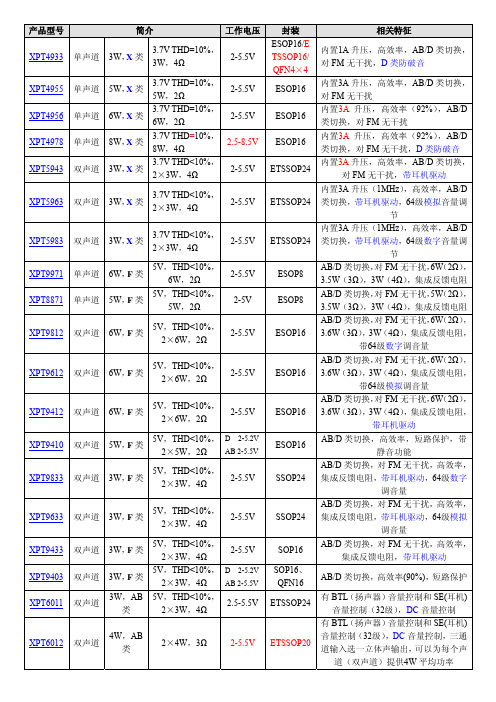

矽普特产品简介

XPT5983 XPT9971 XPT8871 XPT9812

XPT9612

XPT9412 XPT9410 XPT9833

XPT9633 XPT9433 XPT9403 XPT6011

XPT6012

道(双声道)提供4W 平均功率

产品型号 XPT6013 XPT6871 XPT6875 XPT4809

XPT9863

XPT8863

XPT2008

XPT2069

XPT2068 C

XPT4098 XPT4871

F XPT4890 XPT4990 XPT0030 XPT4066 XPT4088 XPT4068 XPT6872

4 SOP18/SS OP24/SOP

16

SOP16/QF N16/DIP16 MSOP8/SO P8/ESOP8/

DFN8 MSOP8/SO

P8/DFN

WCSP9

MSOP8/ES OP8/SOP8/

DFN

WCSP

备注 单端模式,5V,THD+N≤0.5%,75mW (32Ω)。XPT4963的 SD 是高电平工作,

封装

ETSSOP20

SOP8

ESOP8

MSOP8/SO P8

SOP16/DIP 16/ETSSO P16/ETSS OP20 SOP16/ET SSOP20/DI P16

SOP8/ ESOP8

SOP16/DIP 16/ESOP16

SOP16/ES OP16/DIP1

6

QFN16/SO P16/DIP16

完全兼容 LM4861/8002 ,XPT4871H

7512Manual

SN75175中文资料

p

p

Input Voltage – High Logic State (Three–State Control) Input Voltage – Low Logic State (Three–State Control) Input Current – High Logic State (Three–State Control) (VIH = 2.7 V) (VIH = 5.5 V) Input Current – Low Logic State (Three–State Control) (VIL = 0.4 V) Input Clamp Diode Voltage (Three–State Control) (IIK = –18 mA) Output Third State Leakage Current (VI(D) = 3.0 V, VIL = 0.8 V, VO = 0.4 V) (VI(D) = –3.0 V, VIL = 0.8 V, VO = 2.4 V) Output Short–Circuit Current (Note 5) (VI(D) = 3.0 V, VIH = 2.0 V, VO = 0 V) Power Supply Current (VIL = 0 V) (All Inputs Grounded)

QUAD EIA–485 LINE RECEIVER WITH THREE–STATE OUTPUTS

SEMICONDUCTOR TECHNICAL DATA

• • • • • • • • • •

Meets CCITT Recommendations V.10, V.11, X.26, and X.27 Designed for Multipoint Transmission on Long Bus Lines in Noisy Environments 3–State Outputs Common–Mode Input Voltage Range . . . –12 V to 12 V Input Sensitivity . . . ±200 mV Input Hysteresis . . . 50 mV Typ High Input Impedance . . . 1 EIA–485 Unit Load Operates from Single 5.0 V Supply Lower Power Requirements Plug–In Replacement for MC3486

VN751PT13TR;VN751PT;中文规格书,Datasheet资料

November 2009Doc ID 12137 Rev 81/17VN751PTHigh side driverFeatures■CMOS compatible input ■Thermal shutdown ■Shorted load protection■Undervoltage and overvoltage shutdown ■Protection against loss of ground ■Very low standby current■Compliance to 61000-4-4 IEC test up to 4 kV ■Open drain status outputDescriptionThe VN751PT is a monolithic device designed in STMicroelectronics VIPower M0-3 technology, intended for driving any kind of load with one side connected to ground. Active V CC pin voltage clamp protects the device against low energy spikes. Active current limitation combined with thermal shutdown and automatic restart protect the device against overload. Device automatically turns off in case of ground pin disconnection. This device is especially suitable for industrial applications in conformity with IEC 61131-2programmable controllers international standard.Type RDS(on)I out V CC VN751PT60 m Ω2.5 A36 VPPAKContents VN751PT Contents1Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 2Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 3Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 4Waveforms and truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 5Test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 6Application schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 7Reverse polarity protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 8Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 9Order code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 10Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162/17Doc ID 12137 Rev 8VN751PT Maximum ratingsDoc ID 12137 Rev 83/171 Maximum ratingsTable 1.Absolute maximum ratingSymbol ParameterValue Unit V CC DC supply voltage (overvoltage protected)45V - V CC Reverse DC supply voltage -0.3V - I GND DC reverse ground pin current -200mA I OUT DC output current Internally limitedA - I OUT Reverse DC output current -5A I IN DC input current +/- 10mA I STA T DC status current+/- 10mA V ESD Electrostatic discharge ( R = 1.5 k Ω; C = 100 pF )5000V P tot Power dissipation T C = 25 °C Internally limited W T J Junction operating temperature Internally limited °C T c Case operating temperature - 40 to 150°C T stg Storage temperature- 55 to 150°C E ASSingle-pulse avalanche energy0.8JTable 2.Thermal dataSymbol ParameterValue Unit R thJA Thermal resistance junction-ambient Max 50 (1) 1.When mounted on a FR-4 printed circuit board with 0.5 cm 2 of Cu (at least 35μm thick) connected to allV CC pins.°C/W R thJCThermal resistance junction-caseMax3°C/WPin connections VN751PT4/17Doc ID 12137 Rev 82 Pin connectionsFigure 2.Connection diagram (top view)Figure 3.Current and voltage conventionsVN751PT Electrical characteristicsDoc ID 12137 Rev 85/173 Electrical characteristics8 V < V CC < 36 V; -40 °C < T J < 125 °C, unless otherwise specified Table 3.PowerSymbol Parameter Test conditionsMin Typ Max Unit V CC Operating supplyvoltage 5.536V V USD Undervoltage shut-down 345.5V V OV Overvoltage shut-down36V R ONOn state resistanceI OUT = 2 A; T J = 25 °C I OUT = 2 A60180m Ωm ΩI S Supply currentOff state; V CC = 24 V; T CASE =25 °C On state; V CC = 24 VOn state; V CC = 24 V;T CASE =100 °C101.5201.8μA mA mA I L(off)Off state output current V IN = V OUT = 0 V10μATable 4.Switching ( V CC = 24 V )Symbol Parameter Test conditionsMin Typ Max Unitt d(on)T urn-on delay time R L = 12 Ω from V IN rising edge to V OUT = 2.4 V12μs t d(off)T urn-off delay timeR L = 12 Ω from V IN falling edge to V OUT = 21.6 V35μs dV OUT /dt (on)T urn -on voltage slope R L = 12Ω from V OUT = 2.4 V to V OUT = 19.2 V0.80V/μs dV OUT /dt (off)T urn -off voltage slopeR L = 12 Ω from V OUT = 21.6 V to V OUT = 2.4 V0.30V/μsElectrical characteristicsVN751PT6/17Doc ID 12137 Rev 8Table 5.Input pinSymbol Parameter Test conditionsMinTypMax Unit V IL Input low level 1.25V I IL Low level input current V IN = 1.25 V1μA V IH Input high level 3.25V I IH High level input currentV IN = 3.25 V10μA V hyst Input hysteresis voltage 0.5V I IN Input current V IN = V CC = 5 V 10μAV ICLInput clamp voltageI IN = 1 mA I IN = -1 mA66.8 -0.78 VVTable 6.Status pinSymbol Parameter Test conditionsMinTypMax Unit V STA T Status low output voltage I STAT = 1.6 mA0.5V I LSTAT Status leakage currentNormal operation; V STA T = 5 V 10µA C STAT Status pin input capacitance Normal operation; V STA T = 5 V 100pFV SCLStatus clamp voltageI STAT = 1 mA;I STAT =-1 mA6 6.8 -0.78 VVTable 7.ProtectionsSymbol Parameter Test conditionsMin Typ Max Unit T TSD Shut-downtemperature 150175200°C T R Reset temperature 135°C T hyst Thermal hysteresis 720°C I limCurrent limitation V CC = 24 V , R LOAD = 10 m Ω, t = 0.4 ms2.7 6.0AV demagTurn-off output clamp voltageR L =12 Ω; L = 6 mHV CC -47V CC -52V CC -57VVN751PT Waveforms and truth tableDoc ID 12137 Rev 87/174 Waveforms and truth tableFigure 4.Switching time waveformsTable 8.Truth tableConditions Input Output Status Normal operationL H L H H HCurrent limitationL H H L X X H(T J < T TSD ) H (T J > T TSD ) LOvertemperature L H L L H L Undervoltage L H L L X X OvervoltageL HL LH HttV OUTV IN80%10%dV OUT /dt (on)t d(off)90%dV OUT /dt (off)t d(on)Waveforms and truth table VN751PT8/17Doc ID 12137 Rev 8VN751PT Test circuitDoc ID 12137 Rev 89/175 Test circuitApplication schematic VN751PT10/17Doc ID 12137 Rev 86 Application schematicFigure 8.Application schematic分销商库存信息:STMVN751PT13TR VN751PT。

75176芯片

IMPORTANT NOTICETexas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”).TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.Copyright © 1996, Texas Instruments Incorporated。

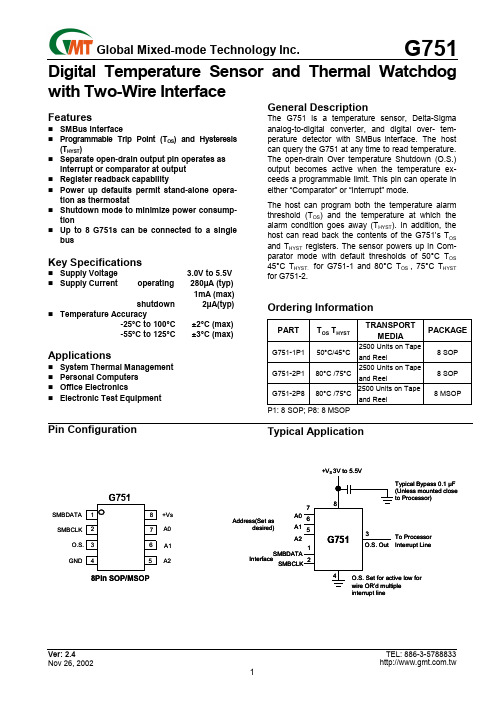

G751中文资料

with Two-Wire Interface FeaturesSMBus interfaceProgrammable Trip Point (T OS) and Hysteresis (T HYST)Separate open-drain output pin operates as interrupt or comparator at outputRegister readback capabilityPower up defaults permit stand-alone opera-tion as thermostatShutdown mode to minimize power consump-tionUp to 8 G751s can be connected to a single busKey SpecificationsSupply Voltage 3.0V to 5.5V Supply Current operating 280µA (typ)1mA (max)shutdown 2µA(typ) Temperature Accuracy-25°C to 100°C ±2°C (max)-55°C to 125°C ±3°C (max) ApplicationsSystem Thermal ManagementPersonal ComputersOffice ElectronicsElectronic Test Equipment General DescriptionThe G751 is a temperature sensor, Delta-Sigma analog-to-digital converter, and digital over- tem-perature detector with SMBus interface. The host can query the G751 at any time to read temperature. The open-drain Over temperature Shutdown (O.S.) output becomes active when the temperature ex-ceeds a programmable limit. This pin can operate in either “Comparator” or “Interrupt” mode.The host can program both the temperature alarm threshold (T OS) and the temperature at which the alarm condition goes away (T HYST). In addition, the host can read back the contents of the G751’s T OS and T HYST registers. The sensor powers up in Com-parator mode with default thresholds of 50°C T OS 45°C T HYST. for G751-1 and 80°C T OS , 75°C T HYST for G751-2.Ordering InformationPART T OS T HYSTTRANSPORTMEDIAPACKAGE G751-1P1 50°C/45°C2500 Units on Tapeand Reel8 SOPG751-2P1 80°C/75°C2500 Units on Tapeand Reel8 SOPG751-2P8 80°C/75°C2500 Units on Tapeand Reel8 MSOP P1: 8 SOP; P8: 8 MSOPTypical ApplicationSMBDATA8Pin SOP/MSOP +Vs A0 A1 A2SMBCLKGND Address(Set asInterfaceinterrupt line desired)A0A1A2Supply Voltage………….…………………-0.3V to 6.5V Voltage at any Pin……………….…-0.3V to +Vs +0.3V Input Current at any Pin…………………………….5mA Package Input Current…………………………….20mA O.S. Output Sink Current………………………….10mA O.S. Output Voltage…………………….…………..6.5V Storage Temperature…………………-65°C to +150°C Soldering Information, Lead TemperatureSOP PackageVapor Phase (60 seconds)……………………….215°C Infrared (15 seconds)……………………………..220°C ESD SusceptibilityHuman Body Model (2000V)Machine Model……………………………………...200V Specified Temperature Range…………….T MIN to T MAX-55°Cto+125°C Supply Voltage Range (+Vs)…………..+3.0V to +5.5VTemperature-to-Digital Converter CharacteristicsUnless otherwise noted, these specifications apply for +Vs=+3.3v Vdc. Boldface limits apply for T A=T J=T MIN toT MAX; all other limits T A=T J= +25°C, unless otherwise noted.PARAMETER CONDITIONSTYPICALLIMITSUNITSAccuracy TA=-25°C to +100°CTA=-55°C to +125°C±2.0±3.0 °C (max)Resolution9BitsTemperature Conversion Time 100 MsQuiescent Current SMBus InactiveSMBus ActiveShutdown Mode0.2511.0MamA (max)µAO.S. Output Saturation Voltage I OUT = 4.0mA 0.8 V (max)O.S. Delay 16Conversions (min)Conversions (max)T OS Default Temperature G751-1/G751-2 50/80 °C T HYST Default Temperature G751-1/G751-2 45/75 °CBlock DiagramA0SMBDATAA1A2SMBCLKDigital DC CharacteristicsUnless otherwise noted, these specifications apply for +Vs=+3.3 Vdc. Boldface limits apply for T A =T J =T MIN to T MAX ; all other limits T A =T J =+25°C, unless otherwise noted. SYMBOL PARAMETER CONDITIONS TYPICAL LIMITS UNITSV IN (1) Logical “1” Input Voltage +Vs × 0.7 +Vs + 0.5 V (min) V (max) V IN (0) Logical “0” Input Voltage-0.3 +Vs ×0.3V (min) V (max) I IN (1) Logical “1”Intput Current V IN =5V 0.005 1.0 µA I IN (0) Logical “0”Intput Current V IN =0V -0.005 -1.0µA C IN All Digital Inputs20 PF I OH High Level Output Current V OH =5V 100 µA (max) V OL Low Level Output Voltage I OL =3ma 0.4 V (max) t OFOutput Fall TimeC L =400pF,I O =3ma 250ns (max)SMBus Digital Switching CharacteristicsUnless otherwise noted, these specifications apply for +Vs = +3.3 Vdc and C L (load capacitance) on output lines = 80pF unless otherwise specified. Boldface limits apply for T A = T J = T MIN to T MAX ; all other limits T A = T J = +25°C, unless otherwise noted.The switching characteristics of the G751 fully meet or exceed the published specifications of the SMBus. The following parameters are the timing relationships between SMBCLK and SMBDATA signals related to the G751. They are not the SMBus specifications.SYMBOL PARAMETER CONDITIONS TYPICAL LIMITSUNITSt 1 SMBCLK (Clock) Period2.5 µs (min) t 2 Data in Set-Up Time to SMBCLK High 100 ns (min) t 3 Data Out Stable after SMBCLK Low0 ns (min) t 4 SMBDATA Low Set-Up Time to SMBCLK Low (Start Condition) 100 ns (min) t 5SMBDATA High Hold Time after SMBCLK High (Stop Condition)100ns (min)Pin DescriptionPIN LABELFUNCTIONTYPICAL CONNECTION1 SMBDATA SMBus Serial Bi-Directional Data Line From Controller2 SMBCLK SMBus Clock Input From Controller3 O.S. Overtemperature Shutdown Open Drain Output Pull Up Resistor, Controller Interrupt Line4 GND Power Supply GroundGround5,6,7 A0-A2 User-Set SMBus Address Inputs Ground (Low, “0”) or +Vs (High, “1”) 8 +Vs Positive Supply Voltage InputDC Voltage from 3V to 5.5VLogic Electrical CharacteristicsSMBDATASMBDATA SMBCLKData inData outTemperature-to-Digital Transfer Function (Non-linear scale for clarity)Functional DescriptionThe G751 temperature sensor incorporates a band-gap type temperature sensor and 9-bit ADC (Delta-Sigma Analog- to-Digital Converter). The temperature data output of the G751 is available at all times via the SMBus. If a conversion is in pro-gress, it will be stopped and restarted after the read.A digital comparator is also incorporated that com-pares a series of readings, the number of which is user-selectable, to user-programmable setpoint and hysteresis values. The comparator trips the O.S. output line, which is programmable for mode and polarity.O.S. Output, T OS and T HYST LimitsIn Comparator mode the O.S. Output behaves like a thermostat. The output becomes active when tem-perature exceeds the T OS limit, and leaves the active state when the temperature drops below the T HYST limit. In this mode the O.S. output can be used to turn a cooling fan on, initiate an emergency system shutdown, or reduce system clock speed. Shutdown mode does not reset O.S. state in a comparator mode.In interrupt mode exceeding T OS also makes O.S. active but O.S. will remain active indefinitely until reset by reading any register via the SMBus inter-face. Once O.S. has been activated by crossing T OS, then reset, it can activated again only by Tempera-ture going below T HYST. Again, it will remain active indefinitely until being reset by a read. Placing the G751 in shutdown mode also resets the O.S. output. Default ModesG751 always powers up in a known state. G751 power up default conditions are:1. Comparator mode2. T OS set to 50°C for G751-1, to 80°C for G751-23. T HYST set to 45°C for G751-1, to 75°C for G751-24. O.S. active low5. Pointer set to “00”; Temperature RegisterWith these operating conditions G751 can act as a stand-alone thermostat with the above temperature settings. Connection to an SMBus is not required. SMBus InterfaceThe G751 operates as a slave on the SMBus, so the SMBCLK line is an input (no clock is generated bythe G751) and the SMBDATA line is a bi-directional serial data path. According to SMBus specifications,the G751 has a 7-bit slave address. The four most significant bits of the slave address are hard wired inside the G751 and are “1001”. The three least sig-nificant bits of the address are assigned to pinsA2-A0, and are set by connecting these pins to ground for a low, (0); or to +Vs for a high, (1). Therefore, the complete slave address is:1 0 0 1 A2 A1 A0 MSB LSBFigure1 O.S. Output Temperature Response Diagram Temperature Data FormatTemperature data can be read from the Temperature, T OS Set Point, and T HYST Set Point registers; and written to the T OS Set Point, and T HYST Set Point reg-isters. Temperature data is representedby a 9-bit, two’s complement word with an LSB (Least Significant Bit) equal to 0.5°C:DIGITAL OUTPUTTEMPERATUREBINARY HEX+125°C 0 1111 1010 0FAh +25°C 0 0011 0010 032h +0.5°C 0 0000 0001 001h 0°C 0 0000 0000 000h -0.5°C 1 1111 1111 1FFh -25°C 1 1100 1110 1CEh -55°C 1 1001 0010 192hShutdown ModeShutdown mode is enabled by setting the shutdown bit in the Configuration register via the SMBus. Shut-down mode reduces power supply current to 1 µA typical. In interrupt mode O.S. is reset if previously set and is undefined in Compatator mode during shutdown. The SMBus interface remains active. Ac-tivity on the clock and data lines of the SMBus may slightly increase shutdown mode quiescent current. T OS , T HYST , and Configuration registers can be read from and written to in shutdown mode.Fault QueueA fault queue of up to 6 faults is provided to prevent false tripping of O.S. when the G751 is used in noisy environments. The number of faults set in the queue must occur consecutively to set the O.S. output. Comparator/Interrupt ModeAs indicated in the O.S. Output Temperature Re-sponse Diagram, Figure 1, the events that trigger O.S. are identical for either Comparator or Interrupt mode. The most important difference is that in Inter-rupt mode the O.S. will remain set indefinitely once it has been set. To reset O.S. while in Interrupt mode, perform a read from any register in the G751. O.S. OutputThe O.S. output is an open-drain output and does not have an internal pull-up. A ”high” level will not be observed on this pin until pull-up current is provided from some external source, typically a pull-up resis-tor. Choice of resistor value depends on many sys-tem factors but, in general, the pull-up resistor should be as large as possible. This will minimize any errors due to internal heating of the G751. The maximum resistance of the pull up, based on G751 specification for High Level Output Current, to pro-vide a 2V high level, is 30k Ω.O.S. PolarityThe O.S. output can be programmed via the con-figuration register to be either active low (default mode), or active high. In active low mode the O.S. output goes low when triggered exactly as shown on the O.S. Output Temperature Response Diagram, Figure 1. Active high simply inverts the polarity of the O.S. output.T T O ST H Y S TO .S .(C o m p a r a t o r M o d e )O .S .(I n t e r r u p t M o d e )e m p e r a t u S h o w nf o r O .S . s e t f o r a c t i v e l o w .*r e a d a n y r e g i s t e r o r p l a c e d i n s h u t d o w nThere are four data registers in the G751, selected by the Pointer register. At power-up the Pointer is set to “00”; the location for the Temperature Register. The Pointer register latches whatever the last loca-tion it was set to. In Interrupt Mode, a read from the G751, or placing the device in shutdown mode, re-sets the O.S. output. All registers are read and write, except the Temperature register which is read only. A write to the G751 will always include the address byte and the Pointer byte. A write to the Configura-tion register requires one data byte, and the T OS and T HYST registers require two data bytes.Reading the G751 can take place either of two ways: If the location latched in the Pointer is correct (most of the time it is expected that the Pointer will point to Temperature register because it will be the data most frequently read from the G751), then the read can simply consist of an address byte, followed by retrieving the corresponding number of data bytes. If the Pointer needs to be set, than an address byte, pointer byte, repeat start, and another address byte will accomplish a read.The first data byte is the most significant byte with most signification bit first, permitting only as much data as necessary to be read to determine tempera-ture condition. For instance, if the first four bits of the temperature data indicates an overtemperature con-dition, the host processor could immediately take action to remedy the excessive temperatures. At the end of a read, the G751 can accept either Acknowl-edge or No Acknowledge from the Master (No Ac-knowledge is typically used as a signal for the salve that the Master has read its last byte).An inadvertent 8-bit read from a 16-bit register, with the D7 bit low, can cause the G751 to stop in a state where the SDA line is held low as shown in Figure 2. This can prevent any further bus communication until at least 9 additional clock cycles have occurred. Al-ternatively, the master can issue clock cycles until SDA goes high, at which time issuing a “Stop” condi-tion will reset the G751.Figure 2. Inadvertent 8-Bit Read from 16-Bit Register where D7 is ZeroMaster but G751 locks SMBDATA low Master detects the errorSMBCLKSMBDATAIntended Stop byof its ways(Selects which registers will be read from or written to):P7 P6 P5 P4 P3 P2 P1 P00 0 0 0 0 0 RegisterSelectP0-P1 :Register Select:P1 P0 REGISTER0 0 Temperature (Read only) (Power-up default)Configuration(Read/Write)0 1T HYST (Read/Write)1 0T OS (Read/Write)1 1P2-P7 :Must be kept zero.Temperature Register(Read Only):D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0MSB Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 LSB X X X X X X XD0-D6 :UndefinedD7-D15 :Temperature Data. One LSB = 0.5°C. Two’s complement format.Configuration Register(Read/Write):D7 D6 D5 D4 D3 D2 D1 D0Cmp/IntShutdownPolarity0 0 0 FaultO.S.QueuePower up default is with all bits “0” (zero).D0 :Shutdown : When set to 1 the G751 goes to low power shutdown mode.D1 :Comparator / Interrupt mode : 0 is Comparator mode, 1 is Interrupt mode.D2 :O.S. Polarity : 0 is active low, 1 is active high. O.S. is an open-drain output under all conditions.D3-D4 :Fault Queue : Number of faults necessary to detect before setting O.S. output to avoid false tripping dueto noise :OFFAULTS D4 D3NUMBER0 0 1 (Power-up default)0 1 21 0 41 1 6D5-D7 :These bits are used for production testing and must be kept zero for normal operation.T HYST and T OS Register(Read/Write):D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0MSB Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 LSB X X X X X X XD0-D6 :UndefinedD7-D15 :T HYST Or T OS Trip Temperature Data. Power up default is T OS = 50°C /80°C for G751-1/G751-2, T HYST =45°C /75°C for G751-1/G751-2.StartG751AckStartG751Master NoCondRepeat Ack Ack No Cond StartG751G751CondbyMasterAddress Byte AckbyPointer BytebyG751byMasterAddress Byte AckbyMost Significant Data ByteAckbyAckbyMasterStopbyMasterLeast Significant Data ByteStartby Master Address BytebyG751Most Significant Data BytebyMasterAckbyMasterStopbyMasterLeast Significant Data BytebyMasterAddress Byte AckbyPointer ByteAckbyStopbyMasterS n S A A A S A A A C t o p C o d b y M a s t e rt a r t b y M a s t e rA d d r e s sB y t ec k b y G 751P o i n t e r B y t e c k b y M a s t e r N o A c k b y M a s t e r A d r e s s B y t e919199R e p e a t S t a r t b y M a s t e r D a t a B y t ec k b y G 751t a r t b y M a s t e rA d d r e s sB y t ec k b y G 751P o i n t e r B y t e c k b y M a s t e r c k b y G 751S t o p o n d b y M a s t e rC o n f i g u r a t i o n B y t et o p o n d b y s t e r1(a ) T y p i c a l P o i n t e r S e t f o l l o w e d b y I m m e d i a t e R e a d f r o m C o n f i g u r a t i o n R e g i s t e r(b ) C o n f i g u r a t i o n R e g i s t e r W r i t e(c ) T O S a n d T H Y S T W r i t e8 Pin SOP PackageNote:1. Package body sizes exclude mold flash and gate burrs2. Dimension L is measured in gage plane3. Tolerance 0.10mm unless otherwise specified4. Controlling dimension is millimeter converted inch dimensions are not necessarily exact.DIMENSION IN MM DIMENSION IN INCHSYMBOLMIN. NOM. MAX. MIN. NOM. MAX.A 1.35 1.60 1.75 0.053 0.063 0.069 A1 0.10 ----- 0.25 0.004 ----- 0.010 A2 ----- 1.45 ----- ----- 0.057 -----B 0.33 ----- 0.51 0.013 ----- 0.020C 0.19 ----- 0.25 0.007 ----- 0.010D 4.80 ----- 5.00 0.189----- 0.197 E 3.80 ----- 4.00 0.150 ----- 0.157 e ----- 1.27 ----- ----- 0.050 ----- H 5.80 ----- 6.20 0.228 ----- 0.244 L 0.40 ----- 1.27 0.016 ----- 0.050 y ----- ----- 0.10 ----- ----- 0.004 θ 0º ----- 8º 0º ----- 8ºVer: 2.4Nov 26, 2002TEL: 886-3-5788833 118 Pin MSOP PackageDIMENSION IN MM DIMENSION IN INCHSYMBOLMIN. NOM. MAX. MIN. NOM. MAX.A ----- ----- 1.10 ----- ----- 0.043 A1 0.05 ----- 0.15 0.002 ----- 0.006A2 0.81 0.86 0.91 0.032 0.034 0.036 b 0.25 ----- 0.40 0.008----- 0.012b1 0.25 0.30 0.35 0.010 0.012 0.014 c 0.13 ----- 0.23 0.005 0.009 c1 0.13 0.15 0.18 0.005 0.006 0.007 D 2.90 3.00 3.10 0.114 0.118 0.122 E1 2.90 3.00 3.10 0.1140.118 0.122 e 0.65 BSC 0.026 BSC E 4.90 BSC 0.193 BSC L 0.445 0.55 0.648 0.0175 0.0217 0.0255 θ1 0° ----- 6° 0° ----- 6° θ2 12 REF 12 REF θ3 12 REF 12 REF R 0.09 ----- ----- 0.004 ----- ----- R1 0.09 ----- ----- 0.004 ----- ----- JEDEC MO-187AATaping SpecificationGMT Inc. does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and GMT Inc. reserves the right at any time without notice to change said circuitry and specifications.Typical SOP/MSOP Package OrientationC b1E18E1DETAIL “A”Leb DA2AA1SEATING PLANEbWITH PLATINGBASE METALc1cθ1GAUGE PLANE0.25RR1Lθ3θ2元器件交易网。

VN751S中文资料

July 2008Rev 61/17VN751SHigh side driverFeatures■CMOS compatible input ■Thermal shutdown ■Shorted load protection■Undervoltage and overvoltage shutdown ■Protection against loss of ground ■Very low stand-by current■Compliance to 61000-4-4 IEC test up to 4 kVDescriptionThe VN751S is a monolithic device designed in STMicroelectronics VIPower M0-3 technology, intended for driving any kind of load with one side connected to ground. Active V CC pin voltage clamp protects the device against low energy spikes. Active current limitation combined with thermal shutdown and automatic restart protect the device against overload. Device automatically turns off in case of ground pin disconnection. This device is especially suitable for industrial applications in conformity with IEC 61131-2programmable controllers international standard.Type R DS(on)I out V CC VN751S60 m Ω2.5 A36 VFigure 1.Block diagramUNDERVOLTAGE OVERTEMPERATUREGNDINPUTOUTPUTOVERVOLTAGE CURRENTLIMITERLOGICDRIVERPowerCLAMPV CCCLAMPDETECTION DETECTIONDETECTIONV CCSTATUSContents VN751S2/17Contents1Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 2Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 3Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 4Waveforms and truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 5Test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 6Application schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 7Reverse polarity protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 8Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 9Order code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 10Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16VN751S Maximum ratings3/171 Maximum ratingsTable 1.Absolute maximum ratingSymbol ParameterValue Unit V CC DC supply voltage (overvoltage protected)45V - V CC Reverse DC supply voltage -0.3V - I GND DC reverse ground pin current -200mA I OUT DC output current Internally limitedA - I OUT Reverse DC output current -5A I IN DC input current +/- 10mA I STA T DC status current+/- 10mA V ESD Electrostatic discharge ( R = 1.5 k Ω; C = 100 pF )5000V P tot Power dissipation T C = 25 °C Internally limited W T J Junction operating temperature Internally limited °C T c Case operating temperature - 40 to 150°C T stg Storage temperature- 55 to 150°C E ASSingle-pulse avalanche energy0.8JTable 2.Thermal dataSymbol ParameterValue Unit R thJA Thermal resistance junction-ambient Max 93(1)1.When mounted on a standard single-sided FR-4 board with 0.5 cm 2 of Cu (at least 35µm) thick connected to allV CC pins. Horizontal mounting and no artificial air flow.°C/W82(2)2.When mounted on a standard single-sided FR-4 board with 2 cm 2 of Cu (at least 35µm) thick connected to allV CC pins. Horizontal mounting and no artificial air flow.R thJCThermal resistance junction-caseMax15°C/WPin connections VN751S4/172 Pin connectionsFigure 2.Connection diagram (top view)Figure 3.Current and voltage conventions3 Electricalcharacteristics8 V < V CC < 36 V; -40 °C < T J < 125 °C, unless otherwise specifiedTable 3.PowerSymbol Parameter Test conditions Min Typ Max UnitV CC Operating supplyvoltage5.536VV USD Undervoltageshut-down34 5.5VV OV Overvoltageshut-down36VR ON On state resistance I OUT = 2 A; T J = 25 °CI OUT = 2 A60180mΩmΩI S Supply current Off state; V CC = 24 V; T CASE =25 °COn state; V CC = 24 VOn state; V CC = 24 V;T CASE =100 °C101.5201.8µAmAmAI L(off)Off state outputcurrentV IN = V OUT = 0 V010µA Table 4.Switching ( V CC = 24 V )Symbol Parameter Test conditions Min Typ Max Unitt d(on)T urn-on delay time R L = 12 Ω from V IN rising edge toV OUT = 2.4 V12µst d(off)T urn-off delay time R L = 12 Ω from V IN falling edge toV OUT = 21.6 V35µsdV OUT/dt(on)T urn -on voltageslope R L = 12Ω from V OUT = 2.4 V toV OUT = 19.2 V0.80V/µsdV OUT/dt(off)T urn -off voltageslope R L = 12 Ω from V OUT = 21.6 V toV OUT = 2.4 V0.30V/µs5/17Table 5.Input pinSymbol Parameter Test conditions Min Typ Max Unit V IL Input low level 1.25VI IL Low level inputcurrentV IN = 1.25 V1µA V IH Input high level 3.25VI IH High level inputcurrentV IN = 3.25 V10µAV hyst Input hysteresisvoltage0.5VI IN Input current V IN =V CC = 5 V10µAV ICL Input clamp voltage I IN = 1 mAI IN = -1 mA6 6.8-0.78 VVTable 6.Status pinSymbol Parameter Test conditions Min Typ Max UnitV STA T Status low outputvoltageI STA T = 1.6 mA0.5VI LSTAT Status leakagecurrentNormal operation; V ST AT = 5 V10µAC STAT Status pin inputcapacitanceNormal operation; V ST AT = 5 V100pFV SCL Status clamp voltage I STA T = 1 mA;I STA T =-1 mA6 6.8-0.78 VVTable 7.ProtectionsSymbol Parameter Test conditions Min Typ Max UnitT TSD Shut-downtemperature150175200°C T R Reset temperature135°C T hyst Thermal hysteresis720°CI lim Current limitation V CC = 24 V, R LOAD = 10 mΩ,t = 0.4 ms2.7 6.0AV demag Turn-off output clampvoltageR L =12 Ω; L = 6 mHV CC-47V CC-52V CC-57V6/174 Waveforms and truth tableFigure 4.Switching time waveformsTable 8.Truth tableConditions Input Output StatusNormal operation LHLHHHCurrent limitation LHHLXXH(T J < T TSD) H(T J > T TSD) LOvertemperature LHLLHLUndervoltage LHLLXXOvervoltage LHLLHHttV OUTV IN80%10%dV OUT/dt(on)t d(off)90%dV OUT/dt(off)t d(on)7/178/17VN751S Test circuit9/175 Test circuitApplication schematic VN751S10/176 Application schematicFigure 8.Application schematicVN751SVN751S Reverse polarity protection11/177 Reverse polarity protectionA schematic solution to protect the IC against a reverse polarity condition is proposed.This schematic is effective with any type of load connected to the outputs of the IC.The RGND resistor value can be selected according to the following conditions to be met:1.R GND ≤ 600 mV / (I S in ON state max).2. R GND ≥ (-V CC ) / (-I GND )where -IGND is the DC reverse ground pin current and can be found in the absolute maximumrating section of the device datasheet.The power dissipation associated to R GNG during reverse polarity condition is:PD = (-V CC )2/R GNDThis resistor can be shared by several different ICs. In such case I S value on formula (1) is the sum of the maximum ON-state currents of the different devices.Please note that if the microprocessor ground and the device ground are separated then the voltage drop across the R GND (given by I S in ON state max * R GND ) produce a difference between the generated input level and the IC input signal level. This voltage drop will vary depending on how many devices are ON in the case of several high side switches sharing the same R GND .Package mechanical data VN751S 8 Package mechanical dataIn order to meet environmental requirements, ST offers these devices in ECOPACK® packages.These packages have a lead-free second level interconnect . The category of second levelinterconnect is marked on the package and on the inner box label, in compliance with JEDECStandard JESD97. The maximum ratings related to soldering conditions are also marked onthe inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at:12/17VN751S Package mechanical data13/17Figure 10.Package dimensionsTable 9.SO-8 mechanical dataDim.mminch MinTypMaxMinTypMaxA 1.75 0.068 a1 0.10.25 0.0030.009a2 1.65 0.064 a3 0.65 0.85 0.025 0.033 b 0.35 0.48 0.013 0.018 b1 0.19 0.25 0.007 0.010 C 0.25 0.5 0.0100.019c145 ( typ. )D 4.8 5.0 0.188 0.196E 5.86.2 0.2280.244 e 1.27 0.050 e3 3.81 0.150F 3.8 4.0 0.14 0.157 L 0.41.27 0.0150.050M 0.6 0.023 S 8º (max.)Package mechanical dataVN751S14/17Figure 11.SO-8 tape and reel informationVN751S Order code15/179 Order codeTable 10.Order codesOrder codes Package Packaging VN751S SO-8T ube VN751STRSO-8tape and reelRevision history VN751S16/1710 Revision historyTable 11.Document revision historyDateRevisionChanges18-Sep-20061Initial release12-Mar-20072Document reformatted, typo in Section Table 3.: Power onpage 5, updated P tot value T able 2.15-May-20073Typo in Table 1 on page 3 V ESD 18-Sep-20074Added I STAT valuein Table 1 on page 311-Oct-20075Updated Table 2 on page 308-Jul-20086Added Section 7 on page 11VN751SPlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNL ESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SAL E ST DISCL AIMS ANY EXPRESS OR IMPL IED WARRANTY WITH RESPECT TO THE USE AND/OR SAL E OF ST PRODUCTS INCL UDING WITHOUT L IMITATION IMPL IED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNL ESS EXPRESSL Y APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2008 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America17/17。

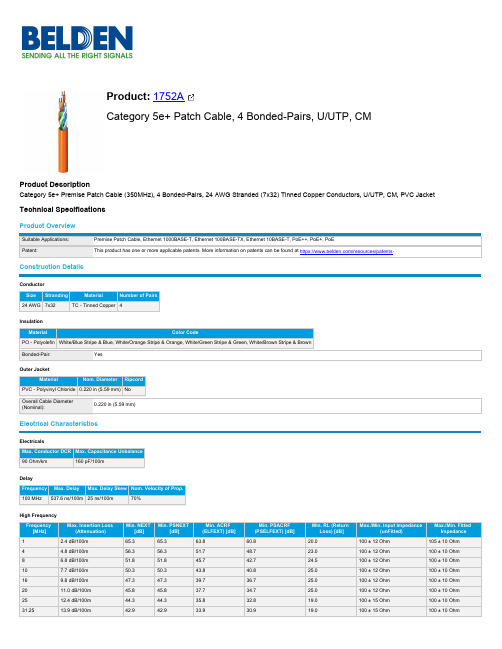

1752A Category 5e+ Patch Cable 商品说明书

Product:1752ACategory 5e+ Patch Cable, 4 Bonded-Pairs, U/UTP, CMProduct DescriptionCategory 5e+ Premise Patch Cable (350MHz), 4 Bonded-Pairs, 24 AWG Stranded (7x32) Tinned Copper Conductors, U/UTP, CM, PVC Jacket Technical SpecificationsProduct OverviewConstruction DetailsConductorInsulationOuter JacketElectrical CharacteristicsElectricalsDelayHigh Frequency62.520.1 dB/100m38.438.427.824.819.0100 ± 15 Ohm100 ± 10 Ohm 10026.1 dB/100m35.335.323.820.819.0100 ± 15 Ohm100 ± 10 Ohm 15533.3 dB/100m32.532.519.916.919.0100 ± 18 Ohm100 ± 10 Ohm 20038.4 dB/100m30.830.817.714.719.0100 ± 18 Ohm100 ± 10 Ohm 25043.7 dB/100m29.329.315.812.818.0100 ± 20 Ohm100 ± 10 Ohm 30048.6 dB/100m28.228.214.211.218.0100 ± 20 Ohm100 ± 10 Ohm 31049.5 dB/100m27.927.913.910.918.0100 ± 20 Ohm100 ± 10 Ohm 35053.2 dB/100m27.227.212.99.917.0100 ± 22 Ohm100 ± 10 OhmVoltageUL Voltage Rating300 V (CM)Mechanical CharacteristicsTemperatureUL Temperature Operating Installation Storage75°C-20°C To +75°C0°C To +50°C-20°C To +75°CBend RadiusStationary Min.Installation Min.1.0 in (25 mm)2.2 in (56 mm)Max. Pull Tension:40 lbs (18 kg)Bulk Cable Weight:21 lbs/1000ftStandards and ComplianceEnvironmental Suitability:Indoor, IndoorSustainability:Product Lens™, Environmental Product Declaration (EPD) AvailableFlammability / Reaction to Fire:UL 1685 (UL 1581) Vertical Tray, FT1, FT1NEC / UL Compliance:Article 800, CMCEC / C(UL) Compliance:CMICEA Compliance:S-90-661-2012IEEE Compliance:IEEE 802.3bt Type 1, Type 2, Type 3NEMA Compliance:NEMA WC-63.1Data Category:Category 5eTIA/EIA Compliance:ANSI/TIA-568.2-D Category 5eThird Party PerformanceCategory 5e PatchVerification:ISO/IEC Compliance:ISO/IEC 11801-1, IEC 61156-6European DirectiveEU CE Mark, EU Directive 2015/863/EU (RoHS 2 amendment), REACH, EU Directive 2011/65/EU (RoHS 2), EU Directive 2012/19/EU (WEEE), REACH: 2020-01-16 Compliance:APAC Compliance:China RoHS II (GB/T 26572-2011)Product NotesNotes:Electrical values are expected performance based on cable testing and representative performance within a typical Belden system. Print Includes Descending Footage Markings.Conductor strands are bonded together.HistoryUpdate and Revision:Revision Number: 0.408 Revision Date: 12-15-2021VariantsItem #Color Putup Type Length UPC1752A 0101000Black Reel1,000 ft6128251222101752A 010U1000Black UnReel1,000 ft6128251222031752A 0061000Blue Reel1,000 ft6128251221731752A 006U1000Blue UnReel1,000 ft6128251221661752A F2V1000Gray Reel1,000 ft6128251220741752A F2VU1000Gray UnReel1,000 ft6128251220671752A 0051000Green Reel1,000 ft6128251221591752A 005U1000Green UnReel1,000 ft6128251221421752A 0031000Orange Reel1,000 ft6128251221111752A 003U1000Orange UnReel1,000 ft6128251221041752A 007U1000Purple UnReel1,000 ft6128251221801752A 0021000Red Reel1,000 ft6128251220981752A 002U1000Red UnReel1,000 ft6128251220811752A 0041000Yellow Reel1,000 ft6128251221351752A 004U1000Yellow UnReel1,000 ft612825122128© 2022 Belden, IncAll Rights Reserved.Although Belden makes every reasonable effort to ensure their accuracy at the time of this publication, information and specifications described here in are subject to error or omission and to change without notice, and the listing of such information and specifications does not ensure product availability.Belden provides the information and specifications herein on an "ASIS" basis, with no representations or warranties, whether express, statutory or implied. In no event will Belden be liable for any damages (including consequential, indirect, incidental, special, punitive, or exemplary damages) whatsoever, even if Belden has been advised of the possibility of such damages, whether in an action under contract, negligence or any other theory, arising out of or in connection with the use, or inability to use, the information or specifications described herein.All sales of Belden products are subject to Belden's standard terms and conditions of sale.Belden believes this product to be in compliance with all applicable environmental programs as listed in the data sheet. The information provided is correct to the best of Belden's knowledge, information and belief at the date of its publication. This information is designed only as a general guide for the safe handling, storage, and any other operation of the product itself or the one that it becomes a part of. The Product Disclosure is not to be considered a warranty or quality specification. Regulatory information is for guidance purposes only. Product users are responsible for determining the applicability of legislation and regulations based on their individual usage of the product.。

751说明书

益。

(12)射频功率控制 RF PWR

此旋钮可改变射频输出功率,顺时针旋转可增加功率。

(13)功能开关 FUNCTION

此开关可以启动面板上由黑底字指示的第二开关功能。

(14)功能指示灯

存储器扫描方式可使你对所有的存储器信道或只对那些存储有工作频率和特定的工作方式的信道进 行扫描。编程扫描可以在任意两个编程指定的频率之间进行。方式扫描可自动地监视那些具有相同工作方 式的存储器。在所有情况下,当收到一个信号时,暂停功能会自动停止扫描。当该频率无信号时,恢复功 能会重新启动扫描功能继续扫描。 2、 32 个存储器

6

杂散发Hz 音频信号时,小于 55dB 以上。

话筒: 阻抗 600Ω。 输入电平,典型值为 12mV。

发射频率微调: ±9.9kHz。

2-3、接收机 接收机系统: 单边带,等幅报,移频电报,调幅,带有连续带宽控制的四次混频。 调频,三次混频。 接收方式: 单边带(J3E),上边带和下边带 等幅报(A1A) 调频话(F3E) 移频电报(F1A) 调幅话(A3E) 中频: 第一中频:70.4515MHz。 第二中频:单边带 9.0115MHz 等幅报、移频电报 9.0106MHz 调频、调幅 9.0100MHz 第三中频:455KHz 第四中频:单边带 9.0115MHz 等幅报、移频电报 9.0106MHz 调频、调幅 9.0100MHz 灵敏度:(接通前置放大器) 单边带、等幅报、移频电报: 在 100KHz~500kHz,信噪比为 10dB 时,不劣于 0.5uV。 在 500KHz~1.6MHz,信噪比为 10dB 时,不劣于 1uV。 在 1.6MHz~30MHz,信噪比为 10dB 时,不劣于 0.15uV。 调幅:(接通窄带滤波器时) 在 100KHz~500kHz,信噪比为 10dB 时,不劣于 3uV。 在 500KHz~1.6MHz,信噪比为 10dB 时,不劣于 6uV。 在 1.6MHz~30MHz,信噪比为 10dB 时,不劣于 1uV。 调频: 在 28MHz~30MHz,信噪比为 12dB 时,不劣于 0.3uV。 静噪灵敏度: 在 1.6MHz~30MHz,不劣于 0.3uV。 选择性: 单边带、等幅报、移频电报(接通宽带滤波器)、调幅(窄带) 在-6dB 处为 2.3KHz,

同洲机顶盒产品介绍new

同洲机顶盒产品介绍-永无止尽的质量追求目录一.合作伙伴篇二.标清产品线介绍三.高清产品线介绍四. 同洲电子带给运营商的增值业务五.机顶盒产品解决方案六.交流讨论同洲的优势人才优势9同洲公司总员工数逾5000人9拥有国内最大的数字电视专业研发队伍,研发人员1000多人9为国家人事部批准的企业博士后科研工作站技术优势9芯片开发平台:拥有ST、BROADCOM、ZORAN、LSI、FUJITSU、ATI、NEC ,Conexant,海思等多个开发平台。

9集成国内外主流CA:NDS、Irdeto、Mediaguard、Viaccess、Conax、同方、数码视讯、天柏、算通等;9VOD平台:新视通、Seachange、Enreach等;9浏览器:集成同洲、Seachange、ipanel、Enreach、佳创等浏览器。

管理优势9采用国际最先进的SAP管理系统,采用全球500强企业都采用的IPD开发流程系统9特聘台籍高级管理人员负责品质和生产线管理,并成立质保中心和品管中心,可靠性试验室中心,确保产品质量。

9产品获得国际和国家各项专业标准认证。

合作伙伴篇芯片厂商CA厂商数码视讯部分客户产品线篇CDVBC5800经济型N7700经济型N7300标清双向N7700标清双向N7300CCM平移机型CDVBC5800经济型主要应用马鞍山, 常州功能特点9基本数字电视节目收看9外观新颖漂亮,小巧,精致9支持同方,爱迪德加密方式9增加了红外接口,可随意放置机顶盒,不影响机顶盒接收遥控功能9支持壁挂,满足多用户的要求硬件配置9采用STx5119 处理器主频速率达到200MHZ9支持8~16MB内存配置9支持2~4MB FLASH配置9一路RCA视频输出9两路L/R音频输出N7700经济型功能特点9支持真待机功能9支持数据广播,Vod等增值服务9支持同方,爱迪德加密方式9增加了红外接口,可随意放置机顶盒,不影响机顶盒接收遥控功能9全塑机箱,支持壁挂,满足多用户的要求硬件配置9采用Hi3110E 处理器主频速率达到300MHZ 9支持32~256MB DDR2内存配置9支持2~16MB FLASH配置9一路RCA视频输出9两路L/R音频输出N7300双向有线机顶盒N7300双向有线机顶盒功能特点功能特点:9支持父母控制,真正做到节目观看权限任意控制9内置图片浏览器和播放器,浏览相片,享受音乐,轻松操控9强大的USB扩展功能,支持外接CableModem.9支持VOD和NVOD,务须等待,随时观看自己喜欢的节目9支持节目预定功能,轻轻松松就能让精彩的节目在播出之前提醒自己,每个精彩都不错过9支持节目时移,想看想停,随意回放9支持壁挂。

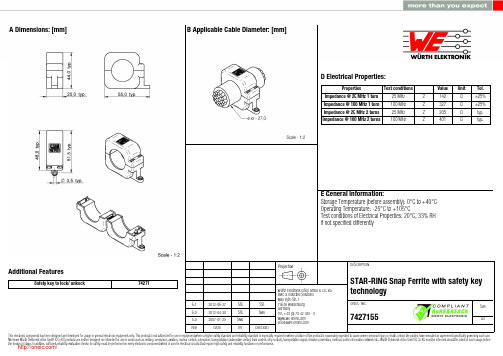

7427155;中文规格书,Datasheet资料