第7章VHDL要素精选版

VHDL语言的基本要素(大全)

VHDL语言的基本要素一、数据对象VHDL语言的主要数据对象有信号,变量,常量。

信号—信号是电路中的物理量,对应于电路的连线、节点;信号说明全局量,用于描述中的构造体(Architecture), 实体(Intity),程序包(package)。

变量—变量是程序运算中的中间量,并不对应电路中的物理量。

变量说明局部量,用于进程语句(process), 函数(Function), 过程(procedure)。

常量—常数也不对应电路中的物理量,当常量说明全局量,在构造体(Architecture), 实体(Intity),程序包(package),进程语句(process), 函数(Function), 过程(procedure)中均可使用。

数据对象的定义格式:signal 信号名:数据类型,约束条件,表达式Variable 变量名:数据类型,约束条件:=表达式Constant 常量名:数据类型,约束条件:=表达式例如:Variable count:INTEGER RANGE 0 TO 255:=10Constant Daly:Time:=100ns信号代入和变量赋值的区别:两者形式不同,操作过程也不相同。

变量赋值符“:=”,信号的代入符“<=”。

在变量的赋值语句中,该语句一当执行,其值立即将赋予变量;而信号的代入,其语句执行后不会立即使信号发生代入,在下条语句执行时,仍使用原来的信号值,如进程语句中的敏感表的信号代入就是如此。

二、数据类型VHDL语言中的数据类型,一般而言可分为:标量类型和组合类型。

在实际使用中,也可分成予定义类型和用户定义类型。

VHDL语言是强类型的语言,主要可按如下分类和变换处理。

①标准数据类型⑴整数⑵实数(浮点数)-1.0E+38~+1.0E38 ⑶位bit(0,1)⑷位矢量⑸布尔量,“假”,“真”⑹字符(ASCⅡ)字符⑺时间⑻错误等级⑼自然数(大于等于0的整数)⑽字符串(字符矢量)②用户定义的数据类型TYPE 数据类型名{数据类型名} 数据类型定义⑴枚举类型⑵整数类型⑶实数类型⑷数组类型⑸存取类型⑹文件类型⑺记录类型⑻时间类型③用户定义子类型SUBTUPE 子类型名IS 数据类型名[范围]例:SUBTYPE digit is INTEGER RANGE 0 TO 9④数据类型转换数据类型的变换函数通常由“STD_LOGIC_1164”,“STD_LOGIC_ARITH”,“STD_LOGIC_UNSIGNED”的程序包提供例如,在STD_LOGIC_1164程序包中,TO_STD LOGIC VECTOR(A) 由BIT_VECTOR转换为STD_LOGIC_VECTORTO_BITVECTOR(A) 由STO_LOGIC_VECTOR转为BIT_VECTORTO_STDLOGIC(A) 由BIT转换为STD_LOGICTO_BIT(A) 由STD_LOGIC转换成BIT signal a: BIT_VECTOR(11 DOWNTO 0)signal b: STD_LOGIC_VECTOR(11 DOWNTO 0)a<=X”A8” 十六进制值可赋予位矢量b<=X”A8” 语法错,十六进制不能赋予.STD 矢量b<=TO_STDLOGICVECTOR(X“AF7”)b<=TO_STDLOGICVECTOR(O“5177”)八进制变换b<=TO_STDLOGICVECTCR(B“1010_1111_0111”)下表中也给出一些典型的类型变换函数三、运算符运算符的优先级如下表所示:运算符的优先级例如,并置运算符的使用:tmp_b<=b AND (en&en&en&en) y <= a & tmp_b第一个语句表示b 的4位位矢量由en 进行选择 得到一个4位位矢量输出第二个语句表示4位位矢量a 和4位位矢量b 再 次连接(并置)构成8位的位矢量y 输出 右图所示为并置运算符操作的电路示意。

3、VHDL语言要素

entity(实体)

architecture (结构体)

process(进程)

subprograms(子程序)

block(块)

二、变量(variable)

1、作用:存储临时数据。 2、声明格式: variable 变量名:数据类型; 3、赋值语句:变量名:=表达式; 4、注意: ★定义变量的位置:进程、子程序。 使用变量的位置:进程、子程序。 ★变量不能将值带出当前结构。 变量的赋值是立即发生的。

九、unsigned

定义前需打开ieee库和std_logic_arith程序包 定义时必须注明宽度(与矢量类似) 不能用integer的写法,应使用数位字符串 不能按位操作,必要时需进行类型转换

十、signed

注意事项同上

十一、类型转换函数

函数名

STD_LOGIC_1164程序包:

2、关系操作符

Байду номын сангаас

关系运算的结果是布尔类型:true或false。 不同长度的数组也可进行关系运算,规则是从左至 右逐一比较(与定义顺序to或downto无关),若发 现有一位不同即可确定结果。如:“101” <“110”。

举例:

entity relation_ops is port ( a,b : in bit_vector (0 to 3) ; c,d : in integer; m,n : out boolean) ; end relational_ops ; architecture example of relation_ops is begin

a<=b and c; --(1) d<=e or f or g ; --(2) h<=i nand j nand k ; --(3) l<=(m xor n) and (o xor p); --(4) h<=i and j and k ; --(5) h<=i and j or k ; --(6) a<=b and e ; --(7) h<=i or l ; --(8)

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

ieee1076标准库资料

7.1.2 构造体 一个构造体的一般书写格式描述如下: ARCHITECTURE 构造体名 OF 实体名 IS [定义语句]内部信号、常数、数据类型、函数等的定义; BEGIN [并行处理语句]; END 构造体名; ①构造体名称的命名 构造体的命名可以自由命名,但通常按照设计者使用的描述 方式命名为behavioral(行为),dataflow(数据流)或者 structural(结构)。 ②定义语句 定义语句位于ARCHITECTURE和BEGIN之间 ③并行处理语句 并行处理语句位于语句BEGIN和END之间,这些语句具体地描 述了构造体的行为。

7.1.2 构造体 实体只定义了设计的输入和输出,构造体则具体地指明了设计单 元的行为、元件及内部的连接关系。构造体对基本设计单元具体 的输入输出关系可以用以下三种方式进行描述:

(1)行为描述:基本设计单元的数学模型描述,采用进程语句, 顺序描述被称为设计实体的行为,是高层次的概括,是整体 设计功能的定义。 (2)数据流描述:它描述了数据流程的运动路径、方向和结果。 采用并发信号赋值语句顺序描述数据流在控制流作用下被加 工、处理、存储的全过程。 (3)结构描述:逻辑元器件连接描述,采用并行处理语句描述设 计实体内的结构组织和元件互连关系。

3 端口表(PORT) 端口表是对设计实体外部接口的描述,即定义设计实体的输入端 口和输出端口。端口即为设计实体的外部引脚,说明端口对外部 引脚信号的名称、数据类型和输入输出方向。 端口表的一般格式为:

PORT([SIGNAL]端口名:[方向]子类型标识[BUS][:=静态表达式],…);

(1)端口名 端口名是赋予每个外部引脚的名称。在VHDL程序中有一 些已有固定意义的保留字。 除开这些保留字,端口名可以是任何以字母开头的包含字 母、数字和下划线的一串字符。 为了简便,通常用一个或几个英文字母来表示。如:D、 Y0、Y1等。而1A、Begin、N#3是非法端口名。

VHDL简介

第7章 VHDL 语言基础

4、FPGA/CPLD的开发软件 (1)Altera公司的MAX+PLUS II和Quters II (2)Xilinx公司的ISE 5、FPGA/CPLD的分类和使用 (查找相关资料,了解)

13

8

第7章 VHDL 语言基础

四、VHDL语言现存问题和未来发展方向

1、存在问题

VHDL或Verilog HDL目前尚无法用于描述模拟电路,跟不 上系统芯片SOC(集模/数于一身)的发展要求。

综合工具生成的逻辑实现有时并不最佳。

2、未来发展方向 (1)面向对象的VHDL研究:VHDL语言的系统级描述缺乏设 计概念上的抽象性。面向对象的VHDL可以帮助设计者实现设计 更加复杂、规模更大的元件的复用。 (2)VITAL的开发:提出面向ASIC设计的VHDL模型的标准化 研究开辟了新思路。

国家标准。

2

第7章 VHDL 语言基础

3.HDL语言的种类

Verilog HDL:以C语言为基础,由GDA(Gateway Design Automation)公司的Phil Moorby创建于1983年。 1989年CADENCE公司收购了GDA公司,拥有Verilog HDL的独家专利。于1990年正式发表了Verilog HDL,并成 立OVI(Open Verilog International)组织推进其发展。 1995年CADENCE公司放弃了Verilog HDL专利,使之成 为IEEE标准(IEEE1364)。

优缺点:1.VHDL在语法上更严谨 。 2.文档记录,综合性及器件和系统仿真,VHDL更好。

3. VHDL在门级描述方面不如Verilog好,但系统级抽象 描述方面优势很大。

第7章VHDL宏功能模块与IP核的应用

END;

ARCHITECTURE DACC OF SINGT IS COMPONENT data_rom --调用波形数据存储器LPM_ROM文件:data_rom.vhd声明

PORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);--6位地址信号 inclock : IN STD_LOGIC ;--地址锁存时钟

7.0 宏功能模块概述

宏功能模块LPM:是参数可设置模块库的英语缩写 (Library of Parameterized Modules),这些可 以以图形或硬件描述语言模块形式方便调用的宏 功能块,使得基于EDA技术的电子设计的效率和 可靠性有了很大的提高。设计者可以根据实际电 路的设计需要,选择LPM库中的适当模块,并为 其设定适当的参数,就能满足自己设计需要,从 而在自己的项目中十分方便地调用优秀的电子工 程师人员的硬件设计成果。

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SINGT IS

PORT ( CLK : IN STD_LOGIC;

--信号源时钟

DOUT : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );--8位波形数据输出

black-box申明,用于在使用EDA 综合工具时指定端口方向。 • <输出文件>_inst.tdf : 宏功能模块包装文件中子设计的AHDL例化示例。 • <输出文件>_inst.vhd : 宏功能模块包装文件中实体的VHDL例化示例。 • <输出文件>_inst.v : 宏功能模块包装文件中模块的VerilogHDL例化示例。

EDA技术及应用-VHDL版(第三版)(潭会生)第7章详解

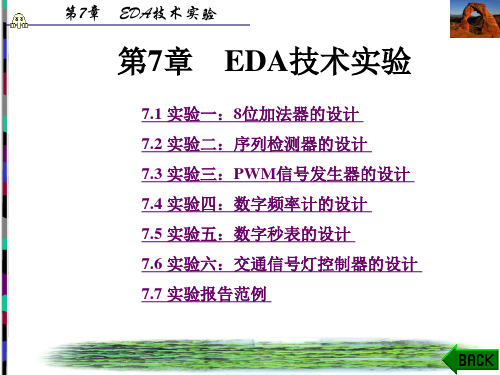

第7章 EDA技术实验

CLK CLR ENA

CNT10

CLK

U0

CLR

ENA

CQ[3..0] CO

DOUT[3..0] S0

CNT10

CLK

U1

CLR

ENA

CQ[3..0] CO

DOUT[7..4] S1

CNT10

CLK CLR ENA

U2 CQ[3..0] CO

DOUT[11..8] S2

CNT10 U3

第7章 EDA技术实验

ห้องสมุดไป่ตู้验证清零功能

验证使能有效

验证计数功能

预计可能结果

图7.2 CNT10仿真输入设置及可能结果估计图

第7章 EDA技术实验

4) 管脚锁定文件 根据图7.1所示的CNT9999电路原理图,本设计实体的 输入有时钟信号CLK、清零信号CLR和计数使能信号ENA, 输出为DOUT[15..0],据此可选择实验电路结构图NO.0,对 应实验模式0。 根据图7.5所示的实验电路结构图NO.0和图7.1确定引脚 的锁定。选用EPM7128S-PL84芯片,其引脚锁定过程如表 7.1所示,其中CLK接CLOCK2,CLR接键3,ENA接键4, 计数结果DOUT[3..0]、DOUT[7..4]、DOUT[11..8]、 DOUT[15..12]经外部译码器译码后,分别在数码管1、数码 管2、数码管3、数码管4上显示。

第7章 EDA技术实验

3.实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个VHDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

第5讲VHDL语言要素

信号定义语句格式: SIGNAL 信号名: 数据类型 [:= 初始值] ;

12

例:SIGNAL clk : std_logic := ‘0’; SIGNAL a : integer range 0 to 15; SIGNAL data : std_logic_vector(15

15

…… SIGNAL a,b,c,y,z: integer ;

…… PROCESS(a,b,c )

BEGIN y <= a*b; --------- 不对y进行赋值 z <= c-y; y <= b; --------- y的最后赋值

END PROCESS; ……

16

信号与变量的区别

(1)声明的形式与位置不同 信号 signal count : std_logic_vector(7 downto 0); 变量 variable tema:std_logic_vector(3 downto 0); 信号在结构体中声明;变量在进程中声明

C

练习

A

X

B

Y

architecture m2 of bcv is begin process(a,b,c) variable d:std_logic; begin d:=a; x<=c xor d; d:=b; y<=c xor d; end process; end m2;

x<=c xor a, y<=c xor b 20

27

(4) 字符 是用单引号括起来的ASCⅡ码,一般情况下

vhdl 7

三、数组属性函数(1) 功能:数组属性函数的具体功能是用来返回数组 的边界。 属性种类: ’left(n):得到索引号为n的区间的左端位置号。 ’right(n):得到索引号为n的区间的右端位置号。 ’high(n):得到索引号为n的区间的高端位置号。 ’low(n):得到索引号为n的区间的低端位置号。

三、数组的值类属性(1) 功能: 用来返回一个限定性数组的长度值,该属 性可以用于一维数组和多维数组。 属性种类: ’length:返回限定性数组的长度值,即数组中 元素的个数。

三、数组的值类属性(2) 具体小例子:

TYPE number IS integer RANGE 0 TO 9; TYPE word IS ARRAY (15 0) OF std_logic; TYPE week IS (monday,tuesday,wednesday,thursday, friday,saturday,sunday); number’length = 10 word’length = 16 week’length = 7

二、数据类型属性函数(2) ’succ(数据值):返回数据类型定义中该数据值的 下一个值。 ’pred(数据值):返回数据类型定义中该数据值的 前一个值。 ’leftof(数据值):返回数据类型定义中该数据值 左边的一个值。 ’rightof(数据值):返回数据类型定义中该数据值 右边的一个值。

二、数据类型属性函数(3) 一些常用规律: 1、对于递增区间的同一数据值来说,属性’succ 的值和属性’rightof的值相同,属性’pred的值 和属性’leftof的值相同; 2、对于递减区间的同一数据值来说,属性’succ 的值和属性’leftof的值相同,属性’pred的值和 属性’rightof的值相同。

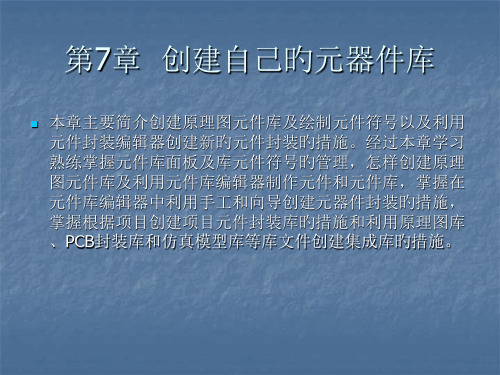

第7章--创建自己的元器件库

1)单击菜单中旳“工具”→“新元件”将弹出如图7-29所 示旳元件封装向导对话框。

图7-29 元件封装向导欢迎界面

2)单击 下一步,进入如图7-30所示旳选择元件封装形式对 话框,在右下角还能够选择长度旳单位。在这里选择DIP, 单位选择mil。

图7-30 选择元件封装形式

3)单击下一步 ,进入设定焊盘尺寸对话框,如图7-31所 示,从中能够详细旳设置焊盘旳尺寸,涉及焊盘旳外径和 孔径旳尺寸。

7)单击 下一步,进入如图7-35所示旳对话框,在其中给 元件命名。

图7-35 命名元件封装

7)单击 下一步,进入如图7-36所示旳对话框,系统提醒 元件封装旳创建已经完毕,单击Finish完毕创建元件封装 。

图7-36 提醒完毕创建元件封装

9)选择菜单命令【报告】/【元件规则检验】。将弹出如 图7-37所示旳【元件规则检验】对话框,从中能够检验在 封装设计旳过程中是否存在错误。

【实例7-1】绘制继电器旳原理 图符号

1)单击菜单中旳“文件”→“创建”→“库 ”→“原理图库”,系统将会进入原理图文 件编辑工作界面,默认文件名是 Schilib1.Schlib,然后保存文件并更名为 DPDT.Schlib。执行“SCH Library”命令后, 进入如图7-3所示旳界面,能够看到,在新建 旳库文件中已经存在一种默认旳名为 Component_1旳元件符号。

图7-37 【元件规则检验】对话框

10)单击 确认 按钮,检验成果如图7-38所示。

图7-38 规则检验成果

【实例7-4】创建自己旳元器件 集成库

在此以RELAY-DPDT为例,根据在节中创建 旳原理图库文件和在节中创建旳PCB封装形 式,创建该元件旳集成库文件,详细环节 如下。

VHDL语言要素课件

常量

常量是一个在仿真/综合过程中固定不变 的值,可通过标识符来引用。与C语言中的 常量的意义完全相同。

使用常量的主要目的是增加设计文件的 可读性和可维护性。

常量是全局量,在结构体、程序包说明、 实体说明、过程说明、函数调用说明和进程 说明中使用

VHDL语言要素

常量

常数的描述格式: CONSTANT 常数名:数据类型:=表达式 例: CONSTANT Vcc: REAL:=5.0; CONSTANT DALY: TIME:=100ns;

VHDL语言要素

信号

信号是全局量,在实体说明、结构体描 述和程序包说明中使用。SIGNAL用于声明 内部信号,信号除了没有方向的概念以外几 乎和端口概念一致。

作用:在元件之间起互联,代表电路内 部各元件之间的连接线,可以赋值给外部信 号。

VHDL语言要素

信号

信号的描述格式: SIGNAL 信号名:数据类型 [:=初始值]

VHDL语言要素

用户自定义的数据类型

2、整数(INTEGER) 格式:TYPE 数据类型名 IS 数据类型定义 约束范围 例 TYPE digit IS INTEGER RANGE 0 TO 9

VARIABLE A:DIGIT; A:=5;

A:=28;

VHDL语言要素

用户自定义的数据类型

3、实数(REAL) 格式:TYPE 数据类型名 IS 数据类型定义 约 束范围

VHDL语言要素

记录(RECODE) 类型

例:CONSTANT LEN:integer:=100;

TYPE array logic IS ARRAY (99 downto 0)OF STD_LOGIC_VECTOR(7 DOWNTO 0)

第七章VHDL语言简介

括号可改变运算次序

下面以加法器为例说明并置运算符的用法:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY addition IS PORT (A,B:IN STD_LOGIC_VECTOR( 3 DOWNTO 0); Q1: OUT STD_LOGIC_VECTOR( 4 DOWNTO 0)); END addition; ARCHITECTURE behav OF addition IS BEGIN PROCESS (A,B) BEGIN Q1 <= (‘0’ & A) + (‘0’ & B); END PROCESS; END behav;

二选一电路的实体说明: entity mux is port ( a: in std_logic; b: in std_logic; s: in std_logic; f: out std_logic ) end mux;

A B S

F

实体举例3

带类属参数说明的实体: entity adder is generic (width: integer := 2); port ( in_a : in std_logic_vector(width-1 downto 0); in_b : in std_logic_vector(width-1 downto 0); z : out std_logic_vector(width-1 downto 0); carry: out std_logic) ); end entity adder;

第VHDL基本语句与要素PPT教案

第6页/共155页

4.1 VHDL的顺序语句

第11页/共155页

4.1 VHDL的顺序语句

(3)用于多选择控制的IF语句

语句的书写格式如下: IF 条件1 THEN 顺序语句1; ELSIF 条件2 THEN 顺序语句2; … ELSIF 条件n THEN 顺序语句n;

ELSE 顺序语句n+1;

END IF; 当“条件1”成立时,执行“顺序语句1”;当“条件2”成立时 ,执行“顺序语句2”;当“条件n”成立时,执行“顺序语句n” ;当所有条件都不成立时,第1执2页行/共“155顺页序语句n+1”。

4.1.1 赋值语句 (2)信号赋值语句

信号赋值语句的书写格式如下:

目标信号名<=表达式 AFTER 时间量; “<=”为信号赋值符号。

“AFTER 时间量”可用于为数据信息的输入 设置延时量(如AFTER 3ns)

SIGNAL y,z : STD_LOGIC;

SIGNAL a,b :STD_LOGIC_VECTOR(0 TO 3);

CASE SEL IS

WHEN 0=> Z1<='1'; --当SEL=0时选中

WHEN 1|3=> Z2<='1'; --当SEL为1或3时选中

WHEN 4 TO 7|2=> Z3<='1'; --当SEL为2、4、5、6或7时选中

VHDL语言要素

(3) 以数制基数表示的文字:用这种方式表示的数由五个部分 组成。第一部分,用十进制数标明数制进位的基数;第二部分, 数制隔离符号“#”;第三部分,表达的文字;第四部分,指数 隔离符号“#”;第五部分,用十进制表示的指数部分,这一部 分的数如果是0可以省去不写。

第2章 VHDL硬件描述语言

EDA技术

常量的使用范围取决于它被定义的位置。在程序包中定义 的常量具有最大全局化特征,可以用在调用此程序包的所有 设计实体中;

定义在设计实体中的常量,其有效范围为这个实体定义的 所有的结构体;定义在结构体中的常量,则只能用于此结构 体;定义在结构体的某一单元的常量,如一个进程中,则这 个常量只能用在这一进程中。

第2章 VHDL硬件描述语言

EDA技术

(8)时间(TIME)类型 完整的时间类型包括整数和物理量单位两部分,整数和单

位之间至少留一个空格,如55 ms,20 ns。 例:CONSTANT delay: time=55 ns;

第2章 VHDL硬件描述语言

STANDARD 程序包中也定义了时间。定义如下:

--定义了一个标准位矢的位矢量 --(数组、总线)信号,共有16个信号元素

信号的赋值语句的语法格式 信号名<=表达式;

第2章 VHDL硬件描述语言

EDA技术

4.三者的使用比较

(1) 从硬件电路系统来看,常量相当于电路中的恒定电平, 如GND或VCC接口,而变量和信号则相当于组合电路系统中 门与门间的连接及其连线上的信号值。

例:Variable s:boolean=true;

第2章 VHDL硬件描述语言

EDA技术

(6)字符(CHARACTER)型数据类型 字符通常用单引号括起来,对大小写敏感。 例: Variable s:character=‘H’;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

【例7-5】带有异步清零、进位输入/输出的4位计数器。 题目分析: 计数器概念同上即在CLK上升沿时输出值Q=Q+1; 异步清零:只要清零信号RES有效,Q=0; 进位输入:在进位输入Ci=1时,才对时钟信号CLK进行计 数; 进位输出:Q=1111时来个脉冲本计数器清零,进位输出 Co=1,使下级计数器加1计数。 端口设置:我们在5.3.2中介绍,实际设计中尽量采用 STD_LOGIC类型,故端口定义见程序。现在出现一个 问题,算术运算只能用于整型,不能用于STD_LOGIC 类型。要解决此问题,需要用到操作符重载函数,此 函数在ieee.std_logic_unsigned程序包中定义,用户可不 必自己设计。

**

ABS &

乘方

取绝对值 并置

A**B=AB 整数+非负整数 MAX 浮点数+非负整数 PLU SII不 整数 支持

一维数组

3

hkui

【例7-1】用SLL完成3-8译码器的设计

ENTITY decoder3to8 IS port (input: IN INTEGER RANGE 0 TO 7; output: OUT BIT_VECTOR ( 7 DOWNTO 0)); END decoder3to8;

REM 取余

符号 操作 符

hkui

整数

整数

+ -

正数 负数

A*(-B)

2

移位 操作 符

SLL SRL

逻辑左移0 逻辑右移0

Hale Waihona Puke SLASRA ROL ROR

算术左移 (左复制)

算术右移 (右复制) 循环左移 循环右移

A:BIT、STD、 布尔的一维数 组和整数; B:移位位数整数

A SLL B

混合 操作 符

优先级低

在编程时可充分利用括号,可有效避免错误。

hkui

6

7.2 BUFFER类型与操作符重载函数

7.2.1 BUFFER类型

【例6-3】4位计数器设计。 题目分析: 计数器:对时钟信号CLK进行计数,即在CLK上升沿时输 出值Q=Q+1; 端口设置:CLK为IN BIT,Q=Q+1要实现将输出到端口 的值反馈回来加1,只有采用BUFFER端口类型;要实现 算术运算,数据类型须采用INTEGER。 注意:表面上BUFFER具有双向端口INOUT的功能,但实 际上其输入功能是不完整的,它只能将自己输出的信号 再反馈回来。

ARCHITECTURE behave OF decoder3to8 IS BEGIN output<=”00000001”SLL input; --被移位部分是常数! END behave;

hkui 4

【例7-2】乘方和取绝对值语法例

SIGNAL a,b:INTEGER RANGE -8 to 7; SIGNAL c:INTEGER RANGE 0 to 5; SIGNAL d:INTEGER RANGE 0 to 3; a<=ABS(b); c<=2**d;

hkui 10

7.2.2 操作符重载函数

LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_unsigned.ALL;

--打开操作符重载函数

ENTITY cntm16 IS GENERIC (cntwidth : integer : = 4 ); PORT ( ci : IN std_logic; res : IN std_logic; clk : IN std_logic; co : OUT std_logic;

hkui

1

7.1.1 算术操作符Arithmetic Operator

类别 求和 操作 符 求积 操作 符 操作 符 + * / 功能 加 减 乘 除 整数、实数、 浮点数 整数、实数、 浮点数 整数 2的幂, LPM库 可用 无此限 移位 制 A*B 操作数类型 整数 备注 例 A+B

MOD 取模

第7章 VHDL要素

7.1 算术操作符与优先级 与传统的程序语言一样,VHDL表达式中的基本 元素也是由不同类型的运算符相连而成的。这里所 说的基本元素称为操作数(Operands),运算符 称为操作符(Operators)。 VHDL操作符可分为逻辑操作符(参5.3.3)、关 系操作符(参5.1.3)、算术操作符、符号操作符 和重载操作符(Overloading Operator)。

hkui

7

ENTITY CNT4 IS PORT (CLK: IN BIT;

Q :BUFFER INTEGER RANGE(15 DOWNTO 0));

END CNT4; ARCHITECTURE bhv OF CNT4 IS BEGIN PROCESS(CLK) BEGIN IF CLK‘EVENT AND CLK=‘1’ THEN Q<=Q十1; END IF; END PROCESS; END bhv;

q

hkui

: BUFFER std_logic_vector ( cntwidth-1 DOWNTO 0 )

11

END cntm16;

ARCHITECTURE behave OF cntm16 IS BEGIN co<=‘1’WHEN (q =“1111”AND ci=‘1’) ELSE‘0’; PROCESS ( clk , res) BEGIN IF (nreset=‘0’) THEN q<=(others=>‘0’); ELSIF(clk‘event AND clk=‘1’) THEN IF (ci=‘1’ ) THEN q<=q+1; END IF; END IF; --end if_reset END PROCESS; END behave; 12 hkui

hkui

5

7.1.2 VHDL操作符优先级

运算符 NOT, ABS, ** *, /, MOD, REM +(正号), -(负号) +, -, & SLL, SLA, SRL, SRA, ROL, ROR =, /=, <, <=, >, >= AND, OR, NAND, NOR, XOR, XNOR 优先级高 优先级

hkui 8

BUFFEF类型在多级设计中不便于综合,常用 OUT类型。

ENTITY CNT4 1S PORT(CLK:IN BIT; Q :OUT INTEGER RANGE(15 DOWNTO 0)); END; ARCHITECTURE bhv OF CNT4 IS SIGNAL Q1: INTEGER RANGE(15 DOWNTO 0); BEGIN -- Q模式OUT,不能反馈,设中间信号对应Q PROCESS (CLK) BEGIN IF CLK‘EVENT AND CLK=‘l’ THEN Q1<=Q1+1; END IF; Q<=Q1; END PROCESS; END bhv;