Abstract Design and Implementation of a Coprocessor for Cryptography Applications

Design and Implementation of a Bionic Robotic Hand

Design and Implementation of a Bionic Robotic Hand with Multimodal Perception Based on ModelPredictive Controlline 1:line 2:Abstract—This paper presents a modular bionic robotic hand system based on Model Predictive Control (MPC). The system's main controller is a six-degree-of-freedom STM32 servo control board, which employs the Newton-Euler method for a detailed analysis of the kinematic equations of the bionic robotic hand, facilitating the calculations of both forward and inverse kinematics. Additionally, MPC strategies are implemented to achieve precise control of the robotic hand and efficient execution of complex tasks.To enhance the environmental perception capabilities of the robotic hand, the system integrates various sensors, including a sound sensor, infrared sensor, ultrasonic distance sensor, OLED display module, digital tilt sensor, Bluetooth module, and PS2 wireless remote control module. These sensors enable the robotic hand to perceive and respond to environmental changes in real time, thereby improving operational flexibility and precision. Experimental results indicate that the bionic robotic hand system possesses flexible control capabilities, good synchronization performance, and broad application prospects.Keywords-Bionic robotic hand; Model Predictive Control (MPC); kinematic analysis; modular designI. INTRODUCTIONWith the rapid development of robotics technology, the importance of bionic systems in industrial and research fields has grown significantly. This study presents a bionic robotic hand, which mimics the structure of the human hand and integrates an STM32 microcontroller along with various sensors to achieve precise and flexible control. Traditional control methods for robotic hands often face issues such as slow response times, insufficient control accuracy, and poor adaptability to complex environments. To address these challenges, this paper employs the Newton-Euler method to establish a dynamic model and introduces Model Predictive Control (MPC) strategies, significantly enhancing the control precision and task execution efficiency of the robotic hand.The robotic hand is capable of simulating basic human arm movements and achieves precise control over each joint through a motion-sensing glove, enabling it to perform complex and delicate operations. The integration of sensors provides the robotic hand with biological-like "tactile," "auditory," and "visual" capabilities, significantly enhancing its interactivity and level of automation.In terms of applications, the bionic robotic hand not only excels in industrial automation but also extends its use to scientific exploration and daily life. For instance, it demonstrates high reliability and precision in extreme environments, such as simulating extraterrestrial terrain and studying the possibility of life.II.SYSTEM DESIGNThe structure of the bionic robotic hand consists primarily of fingers with multiple joint degrees of freedom, where each joint can be controlled independently. The STM32 servo acts as the main controller, receiving data from sensors positioned at appropriate locations on the robotic hand, and controlling its movements by adjusting the joint angles. To enhance the control of the robotic hand's motion, this paper employs the Newton-Euler method to establish a dynamic model, conducts kinematic analysis, and integrates Model Predictive Control (MPC) strategies to improve operational performance in complex environments.In terms of control methods, the system not only utilizes a motion-sensing glove for controlling the bionic robotic hand but also integrates a PS2 controller and a Bluetooth module, achieving a fusion of multiple control modalities.整整整整如图需要预留一个图片的位置III.HARDWARE SELECTION AND DESIGN Choosing a hardware module that meets the functional requirements of the system while effectively controlling costs and ensuring appropriate performance is a critical consideration prior to system design.The hardware components of the system mainly consist of the bionic robotic hand, a servo controller system, a sound module, an infrared module, an ultrasonic distance measurement module, and a Bluetooth module. The main sections are described below.A.Bionic Mechanical StructureThe robotic hand consists of a rotating base and five articulated fingers, forming a six-degree-of-freedom motion structure. The six degrees of freedom enable the system to meet complex motion requirements while maintaining high efficiency and response speed. The workflow primarily involves outputting different PWM signals from a microcontroller to ensure that the six degrees of freedom of the robotic hand can independently control the movements of each joint.B.Controller and Servo SystemThe control system requires a variety of serial interfaces. To achieve efficient control, a combination of the STM32 microcontroller and Arduino control board is utilized, leveraging the advantages of both. The STM32 microcontroller serves as the servo controller, while the Arduino control board provides extensive interfaces and sensor support, facilitating simplified programming and application processes. This integration ensures rapid and precise control of the robotic hand and promotes efficient development.C.Bluetooth ModuleThe HC-05 Bluetooth module supports full-duplex serial communication at distances of up to 10 meters and offers various operational modes. In the automatic connection mode, the module transmits data according to a preset program. Additionally, it can receive AT commands in command-response mode, allowing users to configure control parameters or issue control commands. The level control of external pins enables dynamic state transitions, making the module suitable for a variety of control scenarios.D.Ultrasonic Distance Measurement ModuleThe US-016 ultrasonic distance measurement module provides non-contact distance measurement capabilities of up to 3 meters and supports various operating modes. In continuous measurement mode, the module continuously emits ultrasonic waves and receives reflected signals to calculate the distance to an object in real-time. Additionally, the module can adjust the measurement range or sensitivity through configuration response mode, allowing users to set distance measurement parameters or modify the measurement frequency as needed. The output signal can dynamically reflect the measurement results via level control of external pins, making it suitable for a variety of distance sensing and automatic control applications.IV. DESIGN AND IMPLEMENTATION OF SYSTEMSOFTWAREA.Kinematic Analysis and MPC StrategiesThe control research of the robotic hand is primarily based on a mathematical model, and a reliable mathematical model is essential for studying the controllability of the system. The Denavit-Hartenberg (D-H) method is employed to model the kinematics of the bionic robotic hand, assigning a local coordinate system to each joint. The Z-axis is aligned with the joint's rotation axis, while the X-axis is defined as the shortest distance between adjacent Z-axes, thereby establishing the coordinate system for the robotic hand.By determining the Denavit-Hartenberg (D-H) parameters for each joint, including joint angles, link offsets, link lengths, and twist angles, the transformation matrix for each joint is derived, and the overall transformation matrix from the base to the fingertip is computed. This matrix encapsulates the positional and orientational information of the fingers in space, enabling precise forward and inverse kinematic analyses. The accuracy of the model is validated through simulations, confirming the correct positioning of the fingertip actuator. Additionally, Model Predictive Control (MPC) strategies are introduced to efficiently control the robotic hand and achieve trajectory tracking by predicting system states and optimizing control inputs.Taking the index finger as an example, the Denavit-Hartenberg (D-H) parameter table is established.The data table is shown in Table ITABLE I. DATA SHEETjoints, both the forward kinematic solution and the inverse kinematic solution are derived, resulting in the kinematic model of the ing the same approach, the kinematic models for all other fingers can be obtained.The movement space of the index finger tip is shownin Figure 1.Fig. 1.Fig. 1.The movement space at the end of the index finger Mathematical Model of the Bionic Robotic Hand Based on the Newton-Euler Method. According to the design, each joint of the bionic robotic hand has a specified degree of freedom.For each joint i, the angle is defined as θi, the angular velocity asθi, and the angular acceleration as θi.The dynamics equation for each joint can be expressed as:τi=I iθi+w i(I i w i)whereτi is the joint torque, I i is the joint inertia matrix, and w i and θi represent the joint angular velocity and acceleration, respectively.The control input is generated by the motor driver (servo), with the output being torque. Assuming the motor input for each joint is u i, the joint torque τi can be mapped through the motor's torque constant as:τi=kτ∙u iThe system dynamics equation can be described as:I iθi+b iθi+c iθi=τi−τext,iwhere b i is the damping coefficient, c i is the spring constant (accounting for joint elasticity), and τext,i represents external torques acting on the joint i, such as gravity and friction.The primary control objective is to ensure that the end-effector of the robotic hand (e.g., fingertip) can accurately track a predefined trajectory. Let the desired trajectory be denoted as y d(t)and the actual trajectory as y(t)The tracking error can be expressed as:e(t)=y d(t)−y(t)The goal of MPC is to minimize the cumulative tracking error, which is typically achieved through the following objective function:J=∑[e(k)T Q e e(k)]N−1k=0where Q e is the error weight matrix, N is the prediction horizon length.Mechanical constraints require that the joint angles and velocities must remain within the physically permissible range. Assuming the angle range of the i-th joint is[θi min,θi max]and the velocity range is [θi min,θi max]。

设计与实现 英语

设计与实现英语Design and ImplementationDesign and implementation are two crucial stages in the development of any project, whether it be a product, system, or process. Each stage plays a pivotal role in ensuring that the end result meets the desired objectives and functions effectively.DesignThe design phase is the foundation upon which a successful project is built. It involves the conceptualization and planning of the project, translating ideas into tangible blueprints. This phase requires a thorough understanding of the requirements and constraints, as well as creativity and strategic thinking.Key aspects of the design phase include:1. **Requirements Analysis**: Understanding the needsand goals of the project. This involves gathering input from stakeholders and defining the scope of the project.2. **Concept Development**: Brainstorming and developing different approaches to meet the project requirements. This stage often includes creating prototypes or models to visualize potential solutions.3. **Detailed Planning**: Crafting detailed plans, including technical specifications, design documents, and timelines. This ensures that all aspects of the project are considered and addressed.4. **Evaluation**: Assessing design alternatives and making necessary adjustments to improve functionality, efficiency, and feasibility.**Implementation**Once the design is finalized, the implementation phase brings the plans to life. This stage involves the actualcreation, construction, or development of the project based on the design specifications.Key aspects of the implementation phase include:1. **Execution**: Carrying out the tasks and activities as outlined in the design plan. This could involve coding, manufacturing, or constructing, depending on the nature of the project.2. **Testing and Quality Assurance**: Ensuring that the project meets the required standards and functions as intended. This involves rigorous testing to identify and resolve any issues or defects.3. **Deployment**: Introducing the project to its intended environment or audience. This could involve launching a product, rolling out a new system, or integrating a new process into existing operations.4. **Monitoring and Maintenance**: Continuously monitoring the project's performance and makingnecessary adjustments to address any problems or improvements.**Conclusion**In summary, the design and implementation phases are interconnected and essential to the success of any project. A well-thought-out design provides a solid foundation for effective implementation, while careful execution ensures that the project meets its objectives and delivers value. Both stages require attention to detail, coordination, and adaptability to achieve a successful outcome.。

门户定制系统的设计与实现.

分类号UDC密级V853720学.位论支?]户定制系统的设计与实现作者姓名奎丝垦指导导师姓名盘逛到盈窒亟申请学位级别巫±学科类别圭些茔焦论文提交日期!QQi圭!旦论文答辩日期2QQj:!!:Qg学位授予日期…一制丝囤评阅人型盐垦塞壶送东北大学2005年7月东北大学硕士学位论文摘要、-]户定制系统的设计与实现摘要随着信息技术的发展,企业迫切的需要统一的信息处理平台来处理日常事务。

本系统就是定制企业信息门户的平台。

本系统可以面向管理员用户也可以面向系统的实施人员,可以二次开发,可以不断扩展,样式和内容可以灵活设置。

本文介绍了本系统设计的思路和具体实现的方式。

实现门户网站的个性化定义需要解决两个关键问题,样式和内容。

本文具体阐述了系统实现的难点问题。

本系统用XML存储布局的数据信息,通过布局信息和边框的配置信息,组合成最终的页面元素,使用Velocity模板引擎实现数据对象与HTML元素的整合。

针对接口编程,使系统可以灵活扩展。

通过门户构件(Portlet)的接口,可以与具体的应用模块相连。

本系统可以为页面风格相同的页面设定页面模版,实现模板的重用;整个子站可以导入和导出实现子站文件的重用;边框可以导入和导出实现边框的重用;整个子站有统一的图片管理,实现图片的重用。

系统框架充分应用设计模式,使用插件以及模板引擎技术,使得本系统能够灵活的扩展,能够对页面的层次、风格、布局、内容和菜单进行定制,管理员使用本系统能够快速搭建门户网站。

本文最后介绍了系统的特点和待解决问题,以及如何进一步的完善本系统。

关键词门户门户构件设计模式插件模板引擎布局定制一II—东北大学硕士学位论文ABSTRACTDesignandImplementationofPortalCustomizationSystemAbstractAlongwiththedevelopmentofinformationtechnology,thebusinessenterprisecryingneedtheinformationprocessingplatformtohandlethedailybusiness.ThissystemisaplatformwhichCancustomizePortalofbusinessenterpriseinformation.Thissystemisdesignedfortheadministratorandalsoforthedevelopertoextend.Thestyleandcontentintiffssystemcanbeflexiblycustomized.ThissystemsavesthedatainformationofthelayoutwithXML.Thepageelementsareconstitutedbythelayoutinformationandborderinformation.ThesystemusesthetemplateenginetomergethedataobjectandtheelementofHTML.Programmingtoallinterface,makethesystemcanbeextendedflexibly.ThroughtheinterfaceofPortlet,thesystemCanconilect、埔thaspecificapplicationmodule.Thesystemcansetthetemplateforthepageswithsamestyle,carryingoutthetemplate’Sreuse.Thewholesitefilescanbeexportedandimported.Thewholesitefilescatlbereused.Thebordercanbeexportedandimported.Thebordercarlbereused.Thewholesitecontainsuniformpicturesmanagement,carryingoutthepicture。

东北大学计算机科学与技术专业本科毕业设计(论文)示例

基于WebGIS的物流信息系统的设计与实现作者姓名:张三一指导教师:李四二教授单位名称:信息科学与工程学院专业名称:计算机科学与技术东北大学2008年6月Design and Implementation of WebGIS-Based Logistics Information Systemby ZHANG SanyiSupervisor: Professor LI SierNortheastern UniversityJune 2008东北大学本科毕业设计(论文)毕业设计(论文)任务书毕业设计(论文)任务书基于WebGIS的物流信息系统的设计与实现摘要随着经济的发展和通信技术的提高,物流作为一种先进的组织方式和管理技术,被广泛认为是企业在降低消耗和提高劳动生产率以外的重要的利润源泉,在国民经济和社会发展中发挥着重要作用。

本文在物流企业的正常运营中,基于GIS的信息系统已经成为不可或缺的管理工具。

在对WebGIS技术和物流企业需求进行分析的基础上,结合不同企业的业务流程的具体特点,设计了一套扩展性较强的基于WebGIS的物流信息系统。

系统的主要功能是将企业管理人员与运输车辆之间通过服务器连接起来,实现物流系统的监控和管理。

系统采用B/S架构,服务器端通过网络与车辆终端通信,向车辆发送控制信息并获取车辆的当前状态。

同时它还和Web客户端进行交互,向客户端提供地图服务,并执行Web客户端的请求。

Web客户端采用Ajax 技术与服务器端进行通信,通过动态地图监控车辆。

它还实现了发送货物、编辑线路、发送消息等功能。

考虑到可扩展性,系统重点实现了服务器端进行消息中转的消息队列,建立了Web客户端到车辆终端之间的消息通路,并可以随时更新消息队列中消息处理方式。

本系统实现了物流系统的主要功能,极大提高了企业的管理水平。

本文首先进行了系统的需求获取和业务分析。

然后,采用分层的方法对系统进行设计,叙述了消息队列框架的详细设计与实现,并叙述了服务器端和客户端功能模块的设计和实现。

多速率信号处理的设计与实现(Design and implementation of multirate signal processing)

多速率信号处理的设计与实现(Design and implementation ofmultirate signal processing)This paper makes a great contribution to Weihai mountain in ShandongPdf documents may experience poor browsing on the WAP side. It is recommended that you select TXT first or download the source file to the local machine.Sixth phase of experimental science and technology in December 2006Experimental garden for College StudentsThreeDesign and implementation of multirate signal processingChen Yiou, Li GuangjunUniversity of Electronic Science and technology of China, Chengdu, 610054Thirty-threeAbstract: the multi rate signal processing is the basic theory of software radio, this paper introduces an efficient processing method of multi rate signal, which uses C IC filter and HB filter, F IR filter and polyphase filters for decimation and interpolation in order to achieve the purpose of changingthe signal rate. This paper introduces the basic principle of various filters, analyzes the problems needing attention in the design and implementation, and gives the design results of digital down conversion with this multirate signal processing method. Keywords: multi rate signal processing; C IC filter; HB filter; decimation; interpolation; polyphase filtering in the graph classification number: TN92 document identification code: A article number: 1672-4550 (2006) 06 - 0113 - 04D esign and Rea Liza tion of M ulti - Ra te S igna L Processi g n(University of Electronic Science and Technology of China Chengdu Abstract: M ulti 610054) - Rate signal p rocessing is a basic theory in softw a re rad io. This paper introduces a m ethod of multi - rate signal p rocessing which uses C IC filters, HB filters, F I filters and polyphase fil2 R of using this technique to design a digital down converter ters reach the goal. To of decim ation and interpolation, in order to change the rate of digital signals It in2 troduces the structures of the. Typ ical filters, analyzes some relevant issues, and brings forward the result Key words: multi - rate signal p rocessing; C I filter; HB filter deci; ate; interpolate; polyphase C m CHEN Yi2, L I Guang2jun ouC IC1 IntroductionMake spectrum worse. Therefore, the essence of multirate signal processing is to cooperate with several typical filters throughdecimation and interpolation in time domain so as to achieve the purpose of signal rate conversion. A typical multirate signal processing architecture is shown in figure 1. Filter n.HB extractionMulti rate signal processing is the basic theory of software radio system, it through the interpolation and extraction rate of change of the digital signal in software radio system to adapt to the different modules of the signal to the different rates of [1 - 2], is an important technology for digital down conversion and digital frequency. In practical engineering, in order to change the rate of digital signals and avoid signal frequency aliasing, usually adopt the following filter: C IC decimation filter, HB filter 2 times extraction or within the multiphase structure of F filter and IR filter.Wave filterFilter n.F IRPolyphase filter bankFilter n.HB interpolationFig. 1 a typical multirate signal processing architectureAlgorithm and implementation of more than 2 rate signal processingBecause the C IC filter is simple in structure and high in frequency, it is used in the first stage of high speed digital signal processing. After its integer multiple decimation,The rate of high-speed signals is greatly reduced. HB decimation filter computation than the general F IR filter small half, processing rate is higher, but because each filtersection only 2 times the extraction, so using HB filters N cascade of signalsThe basis of multirate signal processing is decimation and interpolation, which can be directly extracted and interpolated in time domain, which leads to the expansion and compression of the frequency domain,Thirty-threeThree[ePub] 2006 - 08 - 02[author] Chen Yiou (1982 -), female, graduate student, the main research direction is digital signal processing and ASIC design.- 113-December 2006 Experim ent Science & Technology Sixth2 times decimation. Since the C IC filter and the HB filter are all aliasing filters, the signal needs to be filtered by the F IR filter to eliminate the unwanted frequency components, and then the next step is to be processed. The polyphase filter banks can convert the fractional sampling rate, make the rate conversion more flexible, and also make the output speed of the whole system meet the needs of special applications. After the polyphase filter bank, the cascaded HB interpolation filter can also be used to improve the time resolution of the output signal. Next, the algorithm of each filter and the problems to be noticed in the design and implementation are introduced in detail. 211 integral comb filter (C IC filter) C IC filter is composed of integrator H1 (z) and comb filter: Omega D, Omega, omega (1 - D) /2 J -1 J) x a () x E H (E = D * a (S S 22), where D is a decimation factor. Because the sidelobe level of single-stage C IC filter is only higher than that of the main lobe levelH2 (z) is cascaded, and its frequency response is[3]NBandwidth of non aliasing signal in decimation. In this case, the signal bandwidth can be improved by first interpolating the data and then using the C IC filter to extract the signal bandwidth. According to the correlation formula, there are two ways to increase the bandwidth of non aliasing signal undercertain stopband attenuation. One is to reduce the decimation factor D, and the other is to improve the sampling rate. 212 half band filter (HB filter)Graph 210 order HB filterHB filter is a special kind of F I low pass filter, blanking RIn addition to zero at zero, the excitation response is zero at the other even points. Compared with the conventional F IR filter, it requires only half the amount of computation, and can handle higher speed data. Therefore, HB filter is especially suitable for dealing with decimation or interpolation of 2 times rate. According to the HB filter coefficients and the properties of decimation or interpolation, the general structure of F IR filters is simplified. Taking the 10 order HB filter as an example, the simplified HB decimation filter and the HB interpolation filter are shown in Figure 2 (a) and Figure 2 (b), respectively. It is worth noting that the HB filter is also a aliasing filter, and after filtering, aliasing occurs in the frequency domain. Therefore, the passband must be carefully designed and the output of the HB filter will be fully modulated by the F IR filter.Small 13146 dB, stopband attenuation is very poor, it will cause serious aliasing, it is difficult to meet the practical requirements. Therefore, multilevel cascaded C IC filters are often used in engineering. In the specific implementation, we should pay attention to the following questions [4]. 21111 processing gainThe processing gain of Q cascaded C IC filter is DQWith the increase of Q and increase the series extraction factor D, processing gain becomes larger, so the realization of C IC filter, can be inserted into a barrel at the end of the input shape shifter to adjust the gain, to ensure that each class has enough precision, and output to full output.The 21112 phase nonlinear PI C IC filter in 0 ~ 2 of the interval is not completely linear PI, every 2 /D will produce a phase jump, but in each PI interval is 2 /D interval, it is a linear phase. Since the useful signal of PI lies in its linear phase region (0~2 /D), the signals in the rest of the range must be suppressed, so the nonlinear phase has no effect on the filtering and the extracted results. In view of the effect, the C IC filter is still a linear phase filter. 21113 stopband attenuation of PI in the main lobe near 2 /D digital frequency, attenuation than the much larger attenuation in the first sidelobe peak point filter, PI is close to the 2 /D, the greater the attenuation, as long as the attenuation value of PI is large enough at this frequency, when the signal bandwidth is less than (be selected /D - 2, omega) to generate the signal bandwidth from the aliasing can be neglected. 21114 improve the aliasing free bandwidth in some application environments, the sampling rate is higher than the back-endHB filter and F IR filter can handle the highest rate, while theThe fractional multiplication of sampling rate can be achieved by I interpolation [5] and then D times extraction. Before the interpolation is inserted, the baseband spectrum width of the intermediate sequence is not less than the baseband spectrum width of the original input sequence spectrum or the output sequence spectrum, otherwise it will cause the signal distortion. A polyphase interpolation filter with 192 orders and 32 phases is taken as an example. As shown in Fig. 3, the 192 order filter is in accordance with every other orderThe signal bandwidth is greater than C IC filter with the minimum stopband attenuation of 114-More than 213 phase filterSixth phase of experimental science and technology in December 2006The principle of 31 taps as a group was divided into 32 groups, 6 in each groupTap. Each set of corresponding taps is delayed by one clock cycle, i.e., the external inputs are sent to the 32 group. For each group, the inputs corresponding to the 6 taps are multiplied by the tap factor of 31 taps apart, and the rest of the inputs are multiplied by 0. In this way, each group has been interpolated 32 times. When the output is controlled, the toggle switch is rotated at different speeds to realize the extraction of different rates, and the purpose of fractional rate conversion is achieved.Figure 4 N order F IR filter using DA algorithmImplementation of 3 algorithmMulti rate signal processing is the basic theory of software radio, and digital down conversion is one of the keys to software radio. The author uses the multi rate signal processing method for a high performance digital down conversion circuit is implemented on the A ltera FPGA Stratix S40, and designed the demodulation module, automatic gain module and coordinate conversion module, its performance has reached the most widely used digital down conversion chip: Intersil 50214B the level of. The integrated tool Quartus II 510 gives a comprehensive report on the DDC design as shown in Figure 5 (a): a total of 31401 basic logic units are used. The key path shown in Figure 5 (b) shows that the circuit can work stably at a clock frequency of 80 MHz even if the 30% margin is retained. Figure 6 is using the simulation software ModelSim to design[6]Implementation of phase decimation filter in figure more than 3The waveform obtained by simulation is consistent with the result of M atlab simulation, which proves the design is correct.In the frequency domain, the filtering effect is veryunsatisfactory, so the F IR filter must be filtered to eliminate the redundant frequency components before the post processing. There are two choices for the implementation of F IR filters: one is the traditional multiply add structure, but the other is the traditional multiplication and addition structure,When the order of the filter is high, the circuit runs very slowly, and the resource consumption is amazing. The other is using DA algorithm (distributed algorithm). The essence of DA algorithm is a look-up table method. It changes the order of the operations, calculates all possible products before work, saves them in the table, and looks up the tables at work. TheF IR filter structure using the DA algorithm is shown in figure4.The processing speed of DA algorithm only depends on the data width of input signalFor large scale product sum operations, the computation speed has obvious advantages. When the data width of the input signal is too large, the data will be transferredDA algorithm is improved to parallel string structure, which can get faster processing speedDegree. The lookup table used in DA algorithm should be stored in SRAM.214 F IR filterBecause the C IC filter and the HB filter are aliasing filteringFigure 5 example of Quartus design- 115-December 2006 Experim ent Science & Technology SixthReference[1] Li Shixin, [Liu Luyuan 1 Research on wavelet domain median filter design 2] Ma said, Zhang Xiangguang, Yang Miao 1 multi structure element based on generalized morphological filter [3] Yang Xiaoniu, Lou Cai Yi, Xu Jianliang 1 software radio principle and application [4] Chen Yong 1 FPGA high speed dedicated DDC [D] 1 [5] [6] [1] Qin Honggen, based on Pan Ganghua, Mei Jianping think 1 laboratory construction should follow the sustainable [2] has jumped 1 on Higher Vocational Education [J] 1 China quality education theory [3] Dong Jiashou, Zhang Wengui 1 of the laboratory construction and management [J]1 [M] 1 University of Electronic Science and technology 2003, 32 (1): 18 - 211 Intersil - 831 Inc1 HSP50214BFigure 6 ModelSim simulation waveform4 ConclusionThis paper studies the implementation of multirate signal processing, that is, using C IC filter, HB filter, F IR filter and polyphase filter and other typical filters to achieve signal extraction and interpolation. This paper introduces the basic principle of the algorithm, and analyzes the importantproblems which should be paid attention to in the design and implementation. The digital down conversion realized by the multi rate signal processing method has successfully passed the FPGA verification.(up to fifty-eighth pages)Ping, improve the ability of scientific research and development, out of a new way to train "double qualified" teachers. This has laid a solid foundation for further development of training bases and improving the level of practical teaching, speeding up the transformation of scientific research resources into educational resources.The new platform, the theory relating to teaching, course design and graduation design on this platform, including the integrated substation automation, railway signals, railway engineering machinery detection, vehicle detection and maintenance, the train scheduling sub project of electrified railway traction, good training environment for training "iron talents, part of the sub project has started construction.5 training base expansion and improvement ideasAccording to the current situation of talent demand, the focus of personnel training in domestic transportation Colleges (including the Railway College) has shifted, which has weakened the cultivation of the original railway talents. However, with the continuous development of the country's western development, infrastructure construction has been rapid development, Metro, light rail construction has begunoperation in some large cities. All of these require a great deal of expertise in modern railway knowledge. Therefore, Emei Campus Based on its own characteristics, for the railway development, and actively adjust the direction of personnel training, invite the units involved in the development of plan of personnel training, running the main professional focus on the needs of setting and updating of the railway, with the railway engineering characteristics focus on training practical talents. According to the school laboratory investment plan,Southwest Jiao Tong University launched the "323 Engineering Laboratory (process" that is 2 to 3 years, investment of about 200 million yuan of funds, focusing on the construction of 20 ~ 30 based laboratory and transformation of 20 specialized laboratories), Emei campus actively seize the opportunity, based on the existing training base, apply with characteristics of railway engineering practice the training base construction project, as the original innovation of teaching content and teaching methods.6 concluding remarksTraining base, as an important place of practice in Colleges and universities, is the key link of transforming students' theoretical knowledge into practical skills, and also fully embodies the level, quality and characteristics of University running. Therefore, it is an important task for universities to build a good training base with distinctive characteristics, which is of great importance to the cultivation of highly skilled and practical talents. ReferenceTo read all good books is to speak to many noble men.- 116-All: University of Electronic Science and technology of China, 2005: 10-441, Beijing: Tsinghua University press, 20031 and practice, 2003, 9 (1): 2631: University of Electronic Science and Technology Press, 20041Www1 Intersil1 com, 1995 - 05 - 011Improved algorithm of wave [J] 1 Journal of University of Electronic Science and technology of China, 2004, 33 (4):391-3941 [M] 1 Beijing: Publishing House of electronics industry, 20011The road of development [J] 1 laboratory research and exploration, 2004, 5 (23): 82Uwe implementation of FPGA M Eyer - Baese1 digital signal processing [M] 1-- DescartesDatasheet [DB /OL] 11. This paper makes great contributions to Weihai mountain in ShandongPdf documents may experience poor browsing on the WAP side. It is recommended that you select TXT first or download the source file to the local machine.Sixth phase of experimental science and technology in December 2006Experimental garden for College StudentsThreeDesign and implementation of multirate signal processingChen Yiou, Li GuangjunUniversity of Electronic Science and technology of China, Chengdu, 610054Thirty-threeAbstract: the multi rate signal processing is the basic theory of software radio, this paper introduces an efficient processing method of multi rate signal, which uses C IC filter and HB filter, F IR filter and polyphase filters for decimation and interpolation in order to achieve the purpose of changing the signal rate. This paper introduces the basic principle of various filters, analyzes the problems needing attention in the design and implementation, and gives the design results of digital down conversion with this multirate signal processing method. Keywords: multi rate signal processing; C IC filter; HB filter; decimation; interpolation; polyphase filtering inthe graph classification number: TN92 document identification code: A article number: 1672-4550 (2006) 06 - 0113 - 04D esign and Rea Liza tion of M ulti - Ra te S igna L Processi g n(University of Electronic Science and Technology of China Chengdu Abstract: M ulti 610054) - Rate signal p rocessing is a basic theory in softw a re rad io. This paper introduces a m ethod of multi - rate signal p rocessing which uses C IC filters, HB filters, F I filters and polyphase fil2 R of using this technique to design a digital down converter ters reach the goal. To of decim ation and interpolation, in order to change the rate of digital signals It in2 troduces the structures of the. Typ ical filters, analyzes some relevant issues,并提出结果关键词:多速率信号处理;C我滤波器;HB滤波器;分吃;插值;陈相C M 2,我guang2jun欧C IC1引言使频谱变坏。

事业单位综合信息管理系统的设计与实现

事业单位综合信息管理系统的设计与实现Design and Implementation of Integrated Information Management System for PublicInstitutions工程领域:软件工程作者姓名:张洪指导教师:杨挺企业导师:夏东培天津大学软件学院二零一六年十一月独创性声明本人声明所呈交的学位论文是本人在导师指导下进行的研究工作和取得的研究成果,除了文中特别加以标注和致谢之处外,论文中不包含其他人已经发表或撰写过的研究成果,也不包含为获得天津大学或其他教育机构的学位或证书而使用过的材料。

与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示了谢意。

学位论文作者签名:张洪签字日期:2017 年5月16日学位论文版权使用授权书本学位论文作者完全了解天津大学有关保留、使用学位论文的规定。

特授权天津大学可以将学位论文的全部或部分内容编入有关数据库进行检索,并采用影印、缩印或扫描等复制手段保存、汇编以供查阅和借阅。

同意学校向国家有关部门或机构送交论文的复印件和磁盘。

(保密的学位论文在解密后适用本授权说明)学位论文作者签名:张洪导师签名:杨挺签字日期:2017年5 月16日签字日期:2017年5月16日摘要随着云计算、大数据、SOA(Service-Oriented Architecture)、数据库技术的快速发展和进步,设计院构建了先进的机房,部署了许多信息化系统,提升了设计院办公的信息化、共享化、智能化水平。

但是设计院信息化系统多采用C/S体系架构,各个系统开发和实现利用不同的程序,无法实现异构系统数据传输共享,亟需引入先进技术整合各个异构系统,旨在提升数据处理的共享能力。

首先,本文分析了设计院综合信息管理系统的研究背景,通过调研和文献阅读分析了系统国内外研究现状,提出了一个基于SOA的设计院综合管理系统。

其次,本文重点介绍了SOA、Webservice、JavaEE、Oracle数据库管理系统等技术,分析了这些技术在系统设计与开发中的应用优势,为系统开发提供铺垫。

Design and Implementation of Music Player based on Android

Design and Implementation of Music Playerbased on AndroidYU XiangSchool of Communication and Infor mation EngineeringChongqing University of Posts and TelecommunicationsChongqing, Chinae-mail: xiangyu@CHEN ChaoSchool of Communication and Information EngineeringChongqing University of Posts andTelecommunicationsChongqing, Chinae-mail: chenchao2886@QI JingSchool of Communication and Information EngineeringChongqing University of Posts andTelecommunicationsChongqing, Chinae-mail: qijing@Abstract—This paper gives our researching work on how to design a music player based on Android OS. The music player, which uses the front-back end architecture, is divided into the part of music playback and the part of player interface and music list. Besides the playback functions, the music player can also do music rating by user preferences, showing the previous and next music name with corresponding information and operating controller into a panel. The music player runs stably and conveniently during testing.Keywords-Android; music player; music rating; operating controlI.I NTRODUCTIONWith the rapid development of computer and communications technology, the mobile phone is more and more powerful. That is not just a mobile communication tool in our daily life, a variety of media applications begin to appear on cellphone, such as video calls, multimedia player, etc. In order to realize these applications, the support of a more powerful development platform is needed, so the research of smartphone operating system and its development has become one of the most active areas [1].In November 2007ˈOHA˄open Handset Alliance˅, which lead by Google, released a smartphone platform - Android. Android is an open and free platform for mobile terminals which includes operating system, middleware, user interface and application software [2]. Android has a good development and debugging environment, provides a variety of APIs and supports a variety of common audios/ videos decoding. The openness of Android platform can not only promote the technical innovation (including the platform itself), but also help to reduce development costs, and allow manufacturers to customize the characteristic product easily. Therefore, it has a large market potential [3].We designed and implemented a music player based on Android in this paper. According to the feature of mobile phone, the music player makes full use of screen to show more information. In addition to the basic functions of playback, the music player can also make music rating and display the previous and next music name of current music. The design of the player also has some significance for developing other applications on Android.II.A NDROID SOFTWARE PLATFORMA.System ArchitectureAndroid is a software stack and is divided into four layers which are applications, application framework, libraries and Android runtime, Linux kernel [4] from top to down. The applications are written using the Java programming language [4]. The application framework provides some APIs for developers, and developers use these APIs to develop applications. The libraries and Android runtime provide the support for the run and functions of applications, the libraries are invoked by application framework via JNI [5]. Linux kernel, which based on version 2.6, acts as a hardware manager and the base of upper layers.B.Application ComponentsApplication components are the essential building blocks of an Android application, there are four different types of application components [4].1)ActivityAn activity is an interface between application and user. An Activity represents a single screen, and each one is independent of others and communicates with others through intent [6].2)ServiceA service is a component that runs in the background to perform long-running operations. A service does not provide a user interface. Generally the application which runs in background will need service, such as music playback. In this design, the part of playback is achieved by using service.3)Content ProviderA content provider is used to share data. Android application data is private, and sometimes we need to share data between different programs, content provider is to provide this function. Through the content provider, other applications can query or even modify the data (if the content provider allows it) [4].4)Broadcast ReceiverA broadcast receiver is used to receive system-wide broadcast announcements. It gets a happening of event through receiving the broadcast announcements. In this design, the time’s update of player is achieved by broadcast receiver.2011 International Conference on Mechatronic Science, Electric Engineering and Computer August 19-22, 2011, Jilin, ChinaIII.D ESIGN AND I MPLEMENTATION OF MUSIC PLAYERA.Software ArchitectureThe music player adopted front-back end architecture. The front-end consists of player interface and music list and was achieved by activity for interacting with user. The back-end is the implementation of playback which based on service. The communications between front-end and back-end are via intent. The architecture is shown in Figure 1.B.software modulesThe music player consists of some modules which are tab, player interface, playback, music list, list, file, mp3 information, constant value and settings. The block diagram is shown in Figure 2.1)Tab moduleThe tab module is the first module the player runs when the player is opened, which is used to build two tabs which are player and music list. The player associated with player interface and the music list associated with music list, which not only make full use of screen of mobile phone, but also switch between player interface and music list easily. The function of closing player was implemented in tab module, onCreateOptionsMenu(Menu menu) function was called to create a menu, and onOptionsItemSelected (MenuItem item) was called to complete the menu’s functions. Because of the tab module is first module when the player runs, in addition to registering the module in AndroidManifest.xml, the settings of intent-filter should be done as follows:<intent-filter><action android:name="android.intent.action.MAIN" /><categoryandroid:name="UNCHER" /></intent-filter>2)Player interface moduleThe player interface module provides the player interface for user, and the control operations and display information of player are via it. The player interface consists of current music name, status, current/total time, progress bar, previous, play, pause, stop, next, play mode, music rating, previous and next music name. The music rating can be one of the features of this design, and its workflow is shown in Figure 3.The player interface module needs to interact with other modules. The information is sent to the playback module by invoking startService(intent) after encapsulating it into the intent. The player interface invokes the constant value module to use the constant value we defined, and invokes the settings module to achieve the function of getting and saving the setting information. In the design of display of current music name, we displayed the music name with the “marquee” style to avoid that it can’t display fully due to it is too long. The key XML code is shown as follows:<TextView···android:ellipsize="marquee"android:focusable="true"android:marqueeRepeatLimit="marquee_forever"android:focusableInTouchMode="true"···/>Music list moduleThe music list module is used to build music list by invoking list module. The music list is clickable, and the music will play when you click the music name in the list. The information of the music you clicked is encapsulated in intent and sent to playback module to play the music. 4)Playback moduleThe playback module is used to achieve playback and related operations, such as play, pause, stop, display the current, previous and next music name and update the progress bar. The playback module is the core module which based on service. In this module, we achieved that how to translate commands which come from the player interface module and music list module into operations and the information which is encapsulated in intent is sent through broadcast. The playback module invokes the constant value module to match the commands, and invokes the settings module to get and save the settings information.Updating the progress bar and time is an important function of player. In this design, TimeTask class was used to send the time information, and the workflow is shown in Figure 4. The original time is used to update the progress bar, and the translated time is used to update the current/total time. In order not to affect the music player, the separate thread was created to achieve acquisition, Figure 1. the architecture of music playerFigure 2. the block diagram of music playersending time is 500ms and implemented by invoking schedule(TimerTask task, long delay, long period) in Timer class.In addition to displaying the current music name, themusic player also can display the previous and next music name, the workflow is shown as follows:a)if the music list is not empty, encapsulate the current music name into intent and go on; else go to g)b)if there are at least two songs in the music list and playing the first one, set the previous music name to “nothing” and encapsulate it into intent, encapsulate the next music name into intent, and then go to f); else go onc)if there are at least two songs in the music list and playing the last one, encapsulate the previous music name into intent, set the next music name to “nothing” and encapsulate it into intent, and then go to f); else go ond)if there is only one song in the music list, set the previous and next music name to “nothing” and encapsulate these into intent, and then go to f); else go one)encapsulate the previous and next music name into intent, and go onf)send the intent via broadcastg)end5)Constant value moduleThe constant value module holds a variety of constants defined by ourselves, which represent the various commands and are used to send and receive the commands.6)Settings moduleSettings module is used to save and get a variety of setting values by using SharedPreferences [7]. SharedPreferences, which provided by Android, is a mechanism for data access, and data store in the XML file as key-value pairs.7)List moduleThe list module encapsulates the SimpleAdapter class, and that could be directly invoked by music list module to build music list.8)File moduleThe file module searches the music files in the SD card and saves the information which can be used to build the music list.9)Mp3 information moduleThe MP3 information module provides some operations about attributes of Mp3.Figure 3. the workflow of music ratingFigure 4. the workflow of updating timeIV.TEST OF M USIC PLAYERWe tested the music player after implementing it. The music player can achieve the functions we designed, such as showing the current music name with marquee style, playing status, the current/total time, progress bar, fast-forward and fast-backward, etc. the player will close if you choose the exit on menu. The player storages the current music automatically when the player is closed, and plays the music automatically when the player runs next time. The result is shown in Figure 5.V.CONCLUSIONAndroid provides a variety of APIs to help develop application on Android. We completed the design and implementation of music player after introducing the Android platform. The music player adopts the front–back end architecture. The tab is adopted in user interface for switching between the music interface and music list easily. In addition to the common functions of music player, the music rating and displaying the previous and next music name were achieved. The information display and main operations were integrated into a panel for easy use. The methods of design and implementation of the player also have the significance for the development of Android music player and other applications.A CKNOWLEDGMENTThe work was supported by Science and Technology Commission of Chongqing (No.CSTC,2009CA2003) and Scientific Research Fund of Municipal Education Commission of Chongqing in China (Approval No. KJ080507).R EFERENCES[1]Pan Yong-Cai, Liu Wen-chao, Li Xiao.Development and Researchof Music Player Application Based on Android[A].In:2010 International Conference on Communications and Intelligence Information Security[C].USA: IEEE Computer Society's Conference Publishing Services,2010:23-25[2]ZHANG Zheng-zheng,LIN Yao-rong.Development of Android-based Mediaplayer[J].Modern Electronics Technique,2011,34(2):5-6[3]LI Yang,FENG Gang,LI Liang,LUO Yong-hua.Development andResearch on Multimedia Application Based on Android [J].Computer and Modernization,2011(4):149-150[4]Google.Android developers[DB/OL]./guide/basics/what-is-android.html[5]Wikipedia.JNI[DB/OL]./wiki/Java_Native_Interface[6]Google.Android developers[DB/OL]./reference/android/content/Intent.html[7]Google.Android developers[DB/OL]./guide/topics/data/data-storage.html Figure 5. the test of music player。

好的设计与实施方案英文

好的设计与实施方案英文Good Design and Implementation PlanDesigning and implementing a good plan is crucial for the success of any project. It requires careful consideration of various factors and a well-thought-out strategy to ensure that the plan is not only effective but also efficient. In this document, we will discuss the key elements of a good design and implementation plan and provide some practical tips for creating one.First and foremost, a good design and implementation plan should have a clear and specific goal. This goal should be well-defined and measurable, so that progress can be tracked and evaluated. It is important to have a clear understanding of what the plan aims to achieve and how success will be measured.Secondly, a good plan should take into account the resources available for implementation. This includes not only financial resources, but also human resources, time, and technology. It is important to assess what is available and what is needed in order to achieve the desired outcome. This will help in creating a realistic and achievable plan.Another important aspect of a good design and implementation plan is risk assessment and mitigation. It is important to identify potential risks and develop strategies to mitigate them. This may involve developing contingency plans, setting up monitoring systems, or creating alternative solutions. By being proactive in addressing potential risks, the plan is more likely to be successful.Furthermore, a good plan should be flexible and adaptable. It is important to recognize that circumstances may change and that adjustments may need to be made along the way. By building flexibility into the plan, it can better respond to unexpected challenges and changes in the environment.In addition, communication is key to the successful implementationof any plan. It is important to clearly communicate the plan to all stakeholders and ensure that everyone understands their roles and responsibilities. Regular communication and feedback are also important for monitoring progress and making adjustments as needed.Finally, a good design and implementation plan should be supportedby a solid monitoring and evaluation system. This involves setting up clear indicators and benchmarks for measuring progress, as well as regular reviews to assess the effectiveness of the plan. This will help to ensure that the plan stays on track and that any necessary adjustments can be made in a timely manner.In conclusion, a good design and implementation plan is essential for the success of any project. By carefully considering the goals, resources, risks, flexibility, communication, and monitoring and evaluation, a plan can be developed that is not only effective but also adaptable and sustainable. With a well-thought-out plan in place, the chances of success are greatly increased.。

design and implementation of two-wheeled self-balancing vehicle

摘要近年来,两轮自平衡机器人的研究取得了快速的发展,两轮自平衡小车的动力学系统是一种多变量、非线性、强耦合的系统,是检验各种控制方法的典型装置。

同时由于它具有体积小、运动灵活、零转弯半径等特点,必将会在军用和民用领域有着广泛的应用前景。

本文主要介绍了基于Freescale MC9S12XS128单片机为控制核心的两轮自平衡小车系统,以验证经典的PID控制在动态平衡系统上的控制效果。

在该系统上,姿态传感器采用MPU6050,单片机在采集到姿态数据后,采用Kalman滤波器对得到的数据进行融合,并在此基础上分析不同滤波方法的效果。

借助增量式PID控制PWM的输出和利用TB6612FNG控制电机的转向以及转速,从而实现了小车的自平衡控制。

关键词:两轮自平衡系统; Kalman滤波;数据融合; HCS12; MPU6050 .Design and implementation of two-wheeled self-balancing vehicleAbstractIn recently years, the research of two-wheeled self-balancing robot has made a rapid development, the dynamics system of two-wheeled self-balancing vehicle is a multivariable, nonlinear, strong coupling system, and also ,it’s a typical devices to test a variety of control methods. Because of it has a small, flexible movement and zero turning radius. It will have a wide range of applications in military and civilian fields.In the article, it describes the Freescale MC9S12XS128 microcontroller-based control of two-wheeled self-balancing vehicle system to verify the classic PID control system in the dynamic balance . On this system, It used MPU6050 as the car state sensing system, and it used the Kalman filter to fuse the obtained angle data, and analyzed the effect of different filtering methods based on this. With incremental PID control PWM output and use TB6612FNG steering and speed control motors, enabling the car's self-balance control finally.Keywords: two-wheeled self-balancing system; the Kalman filter;HCS12;MPU6050目录摘要 (1)第1章绪论 (5)1.1 两轮自平衡机器人概述 (5)1.2 两轮自平衡机器人的发展 (5)1.3 方案论证及选择 (6)1.4 关键技术及目标 (7)1.4.1 姿态数据处理 (7)1.4.2 控制算法的实现 (8)1.4.3 目标 (8)第2章两轮自平衡小车的原理 (9)2.1 小车的直立控制 (9)2.2 倾角与角速度的测量 (13)2.3 本章小结 (13)第3章电路设计 (14)3.1 整体电路框图 (14)3.2 电源电路 (15)3.3 单片机最小系统 (16)3.3.1 S12单片机简介 (16)3.3.2 MC9S12XS128最小系统电路 (16)3.4 MPU6050 (17)3.4.1 MPU6050简介 (17)3.4.2 I2C通信 (18)3.5 电机驱动电路 (18)3.5.1 驱动芯片介绍 (18)3.5.2 驱动电路设计 (19)3.6 速度传感器电路 (20)3.6.1 光电编码器介绍 (20)3.7 无线遥控电路 (20)3.7.1 Pt2262简介 (20)3.7.2 Pt2262应用 (21)3.8 液晶显示电路 (22)3.8.1 LCD1602简介 (22)3.8.2 LCD1602电路 (22)3.9 车模控制电路全图 (23)3.10 本章小结 (25)第4章系统软件设计 (26)4.1 控制算法介绍 (26)4.2 S12单片机初始化 (27)4.2.1 锁相环初始化 (27)4.2.2 PWM模块初始化 (27)4.2.3 串行通信初始化 (27)4.2.4 外部中断初始化 (28)4.3 PID控制的实现 (28)4.4 姿态数据处理 (28)4.4.1 角度计算函数 (28)4.4.2 滤波方法分析与选择 (28)4.5 小车的运动控制 (32)4.6 无线遥控 (32)4.7 本章小结 (32)第5章系统调试 (34)5.1 软件调试工具 (34)5.2 系统调试工具 (34)5.3 系统硬件电路调试 (34)5.4 姿态检测模块调试 (34)5.5 Kalman滤波器参数的整定 (36)5.6 PID参数的整定 (36)5.7 本章小结 (37)第6章总结 (38)6.1 总结与展望 (38)参考文献 (40)附录 (42)附录一系统主控板 (42)附录二系统核心源码 (43)致谢 (46)第1章绪论两轮自平衡系统最早可追溯到上世纪80年代,日本电气通信大学的山藤一雄教授提出的基于倒立摆原理的自动站立机器人的模型被认为是两轮自平衡小车的构思起源。

Design and implementation of signal generator based on AD9850

gives the assembler source program of the serial input mode for your information only.

f0ut -output frequency,

978-l-61284-088-8/ll/$26.00 ©2011 IEEE

3853

12-14 August, 2011

by 1800,900,450,22.50,11.250,or the phase combines by them. The frequency control bit is counted by: JrxW,

AD9850 is divided into three parts, they are programmable DDS system, high-powered DAC converter and high-speed comparator. The programmable DDS system contains input register, data register and high-speed DDS [3] [4]. The High-speed DDS contains phase accumulator and sine lookup table , and the phase accumulator comprises by an adder and a 32-bits phase register. The address of sine lookup table is added by the output of phase register and a 5-bits outside phase control word. The sine lookup table contains the periodic digital amplitude information of a sine wave, and every address matches with a phase point which comes within 0^360.The output from sine lookup table drives lObit DAC converter which output two complementary electric current. The electric current amplitude can be adjusted by the external resistance Rset, the output electric current can be counted by Iset=32(1.248V/Rset),3.9K Q is a typical value of Rset.The output signal passes the external low pass filter, and then is connected to high-speed comparator which is inside the AD9850.At last the system produces a square wave with very little dithering has the same frequency of the sine wave [5].

电商系统的英文论文参考

注:格式内容可能不符合要求,可根据自己的需要更改Title: Design and Implementation of an E-commerce SystemAbstract: This paper presents the design and implementation of an Internet-based e-commerce system. The system aims to provide a convenient and secure platform for users to browse and purchase various goods and services. The paper describes the architecture and features of the system in detail and discusses the design principles and key technologies employed. By implementing a complete e-commerce system, we demonstrate the application and validation of these theories and technologies in a real-world setting.Introduction: E-commerce has experienced rapid growth over the past few decades and has become an integral part of modern business. With the widespread adoption of the Internet and mobile technology, more people are opting for online shopping, leading to the emergence of numerous e-commerce platforms. This paper aims to explore the design and implementation of an e-commerce system, providing a comprehensive solution to meet user needs while ensuring the reliability and security of the system.Methodology: The paper presents the overall architecture of the e-commerce system, including the organization and interaction of the front-end interface, backend servers, and database. By utilizing common development technologies and frameworks such as HTML, CSS, JavaScript, Python, and MySQL, we have implemented a feature-rich e-commerce system.Results: The implemented e-commerce system offers a user-friendly interface for browsing products, secure payment processing, order management, and personalized recommendations. The system also incorporates robust security measures to protect user data and transactions. Extensive testing and user feedback demonstrate the system's usability, performance, and reliability.Conclusion: This paper provides insights into the design and implementation of an e-commerce system, highlighting the key considerations and technologies involved. The developed systemserves as a practical solution for online businesses and showcases the effective application of e-commerce principles in a real-world context. Future work may involve enhancing the system's scalability, integrating advanced analytics for business intelligence, and exploring emerging technologies to further improve the e-commerce experience.Discussion: The discussion section explores the key design decisions and considerations taken during the development of the e-commerce system. It delves into topics such as user experience, system scalability, security measures, and integration with third-party services. The advantages and challenges of implementing specific features, such as product search, cart management, and order fulfillment, are also discussed in this section.Future Work: The paper concludes by outlining potential areas for future development and improvement of the e-commerce system. This may include integrating machine learning algorithms for personalized product recommendations, expanding the system's mobile compatibility, implementing social media integration for enhanced marketing and customer engagement, and exploring blockchain technology for secure and transparent transactions. The authors also emphasize the importance of continuously updating and evolving the system to keep up with changing user needs and technological advancements.Conclusion: In conclusion, this paper presents the design and implementation of an e-commerce system, showcasing its architecture, features, and key technologies. The system offers a user-friendly and secure platform for online shopping, demonstrating the effective application of e-commerce principles and technologies. The insights and lessons learned from this project can serve as a valuable reference for researchers and practitioners involved in the development of e-commerce systems.。

操作系统设计与实现 英文原版

操作系统设计与实现英文原版The book "Operating Systems: Design and Implementation" is a comprehensive guide to the design and implementation of operating systems. It covers a wide range of topics including process management, memory management, file systems, and device drivers. The book also discusses the design principles and trade-offs involved in building operating systems, as well as the practical implementation details.The authors of this book, Andrew S. Tanenbaum and Albert S. Woodhull, provide a detailed and in-depth exploration of the key concepts and techniques used in modern operating systems. They also present case studies of real-world operating systems, such as Linux and Windows, to illustrate how these concepts are applied in practice.The book is widely regarded as a classic in the field of operating systems and is used as a textbook in many computer science programs. It is written in a clear andaccessible style, making it suitable for both students and professionals in the field. Whether you are interested in learning about operating system design for the first time or looking to deepen your understanding of the subject, "Operating Systems: Design and Implementation" is an invaluable resource.。

Abstract Design and Implementation of Semi-preemptible IO

is thus undesirable. Making disk IOs preemptible would reduce blocking and improve the schedulability of realtime disk IOs. Another domain where preemptible disk access is essential is that of interactive multimedia such as video, audio, and interactive virtual reality. Because of the large amount of memory required by these media data, they are stored on disks and are retrieved into main memory only when needed. For interactive multimedia applications that require short response time, a disk IO request must be serviced promptly. For example, in an immersive virtual world, the latency tolerance between a head movement and the rendering of the next scene (which may involve a disk IO to retrieve relevant media data) is around 15 milliseconds [2]. Such interactive IOs can be modeled as higher-priority IO requests. However, due to the typically large IO size and the non-preemptible nature of ongoing disk commands, even such higherpriority IO requests can be kept waiting for tens, if not hundreds, of milliseconds before being serviced by the disk. To reduce the response time for a higher-priority request, its waiting time must be reduced. The waiting time for an IO request is the amount of time it must wait, due to the non-preemptibility of the ongoing IO request, before being serviced by the disk. The response time for the higher-priority request is then the sum of its waiting time and service time. The service time is the sum of the seek time, rotational delay, and data transfer time for an IO request. (The service time can be reduced by intelligent data placement [27] and scheduling policies [26]. However, our focus is on reducing the waiting time by increasing the preemptibility of disk access.) In this study, we explore Semi-preemptible IO (previously called Virtual IO [5]), an abstraction for disk IO, which provides highly preemptible disk access (average preemptibility of the order of one millisecond) with little loss in disk throughput. Semi-preemptible IO breaks the components of an IO job into fine-grained physical diskcommands and enables IO preemption between them. It

软件学院毕业设计(论文)排版样例

封面(在学校统一印制的封皮上打印相应的内容,以下为填写举例)论文题目 论文主标题(主副标题总字数不大于25)姓名 学生名学 院 软件学院专 业 专业名称指导教师备 注25)――论文子标题(可选)作者姓名:张松奇校内指导教师:柳洪义教授校外指导教师:张军工程师单位名称:软件学院专业名称:软件工程东北大学20XX年6月game-experience announcing subsystem insocial network site for game playersby Zhang SongqiNortheastern UniversityJune 20xxSupervisor: Professor Liu Hongyi Associate Supervisor: Engineer Zhang Jun摘 要 毕业设计(论文)是学生在校学习的最后阶段,是培养学生综合运用所学知识,发学术论文的编写格式》和东北大学论文格式制定此规范,本规范专为我院本科毕业设计(论文)撰写打印时使用。

本文主要介绍本科毕业设计(论文)的排版及打印规范,关于论文的撰写原则及内容指导请参考《本科毕业设计(论文)的撰写规范》一文。

学位论文主要部分由前头部分、主体部分和结尾部分组成。

前头部分主要包括:封面、中文题名页、英文题名页、任务书、中文摘要、英文摘要、目录。

主体部分主要包括:绪论、正文、总结及展望。

结尾部分包括:参考文献、致谢、附录(限必要时添加)。

希望通过本文的阐述,使同学们能够了解掌握东北大学软件学院本科毕业设计(论文)的排版及打印规范,并认真执行。

关键词:本科毕业设计,论文排版,论文打印,页面布局,段落格式,字体格式东北大学毕业设计(论文) AbstractAbstract In recent years, V oIP (VInternet. But IP network provides data transmitting service only in a “best effort” manner, it does not guarantee the quality of services to VoIP, as a real-time service. Then, QoS(Quality of Service) is becoming more and more important to V oIP, and it’s also a study focus to computer network for a long time.This article mainly discusses the QoS architecture, the principle of V oIP and the two related protocols: H.323, SIP. And then, introduce some QoS control mechanisms: packet classification, admission control, QoS route and queue management.………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………………….Key words: V oIP, QoS, H.323, SIP, RSVP, Diffserv摘要 (I)Abstract (II)第1章绪论 (1)1.1 论文排版总体要求 (1)1.1.1 打印 (1)1.1.2 页码编排 (1)1.1.3 页眉设置 (1)1.1.4 装订 (1)1.2 论文主要部分 (2)1.2.1 前头部分 (2)1.2.2 主体部分 (2)1.2.3 结尾部分 (3)1.3 本文结构 (3)第2章论文前头部分 (5)2.1 封面 (5)2.1.1 论文题目 (5)2.1.2 姓名 (5)2.1.3 论文封面日期 (5)2.2 中英文题名页 (5)2.2.1 题目 (6)2.2.2 姓名 (6)2.2.3 学校与日期 (6)2.3 毕业设计论文(任务书) (6)2.3.1 毕业设计(论文)题目 (6)2.3.2 基本内容 (6)2.3.3 毕业设计(论文)专题部分 (6)2.3.4 学生接受毕业设计(论文)题目日期 (6)2.4 中英文摘要 (7)2.4.1 题目 (7)2.4.2 摘要 (7)2.4.3 摘要内容 (7)2.4.4 关键词 (7)2.5 目录 (7)2.5.1 目录 (7)2.5.2 索引条目 (7)第3章正文部分 (9)3.1 各级标题 (9)3.2 正文 (9)3.3 图 (9)3.4 表 (10)3.5 程序代码 (11)3.6 公式 (11)第4章结尾部分 (12)4.1 参考文献 (12)4.2 参考文献格式 (12)4.3 参考文献举例 (12)参考文献 (13)致谢 (14)第1章 绪 论现、提出、分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的系统训练和考察过程。

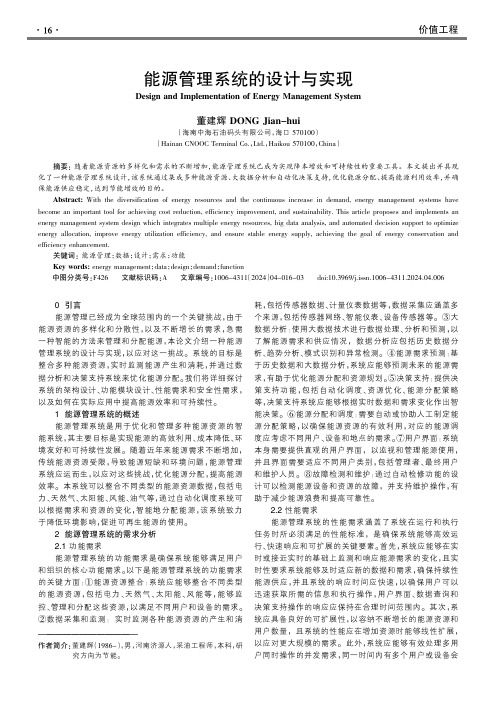

能源管理系统的设计与实现

0引言能源管理已经成为全球范围内的一个关键挑战,由于能源资源的多样化和分散性,以及不断增长的需求,急需一种智能的方法来管理和分配能源,本论文介绍一种能源管理系统的设计与实现,以应对这一挑战。

系统的目标是整合多种能源资源,实时监测能源产生和消耗,并通过数据分析和决策支持系统来优化能源分配。

我们将详细探讨系统的架构设计、功能模块设计、性能需求和安全性需求,以及如何在实际应用中提高能源效率和可持续性。

1能源管理系统的概述能源管理系统是用于优化和管理多种能源资源的智能系统,其主要目标是实现能源的高效利用、成本降低、环境友好和可持续性发展。

随着近年来能源需求不断增加,传统能源资源受限,导致能源短缺和环境问题,能源管理系统应运而生,以应对这些挑战,优化能源分配,提高能源效率。

本系统可以整合不同类型的能源资源数据,包括电力、天然气、太阳能、风能、油气等,通过自动化调度系统可以根据需求和资源的变化,智能地分配能源,该系统致力于降低环境影响,促进可再生能源的使用。

2能源管理系统的需求分析2.1功能需求能源管理系统的功能需求是确保系统能够满足用户和组织的核心功能需求。

以下是能源管理系统的功能需求的关键方面:①能源资源整合:系统应能够整合不同类型的能源资源,包括电力、天然气、太阳能、风能等,能够监控、管理和分配这些资源,以满足不同用户和设备的需求。

②数据采集和监测:实时监测各种能源资源的产生和消耗,包括传感器数据、计量仪表数据等,数据采集应涵盖多个来源,包括传感器网络、智能仪表、设备传感器等。

③大数据分析:使用大数据技术进行数据处理、分析和预测,以了解能源需求和供应情况,数据分析应包括历史数据分析、趋势分析、模式识别和异常检测。

④能源需求预测:基于历史数据和大数据分析,系统应能够预测未来的能源需求,有助于优化能源分配和资源规划。

⑤决策支持:提供决策支持功能,包括自动化调度、资源优化、能源分配策略等,决策支持系统应能够根据实时数据和需求变化作出智能决策。

学生管理系统外文文献

学生管理系统外文文献随着信息技术的快速发展,学生管理系统已经成为现代教育管理的重要组成部分。

学生管理系统是基于计算机网络技术和数据库技术实现的信息化管理系统,为学校提供了便捷高效的管理方式,同时也为学生提供了更好的学习和生活环境。

本文将介绍学生管理系统的相关外文文献,并探讨其在教育管理中的应用。

1. 'Design and Implementation of Student Attendance Management System Based on RFID Technology'该文献介绍了一种基于RFID技术的学生考勤管理系统。

该系统采用RFID读写器对学生的学号进行读取,实现了学生考勤的自动化管理。

该系统具有考勤准确、数据实时性好、使用方便等优点。

2. 'Design and Implementation of Student Information Management System Based on '该文献介绍了一种基于技术的学生信息管理系统。

该系统包括学生信息录入、查询、修改、删除等功能,同时还实现了教师、管理员的权限管理。

该系统具有界面美观、操作简单、数据安全性高等特点。

3. 'Design and Implementation of Comprehensive Evaluation System for College Students Based on Data Mining Technology' 该文献介绍了一种基于数据挖掘技术的大学生综合评价系统。

该系统采用聚类分析、决策树等数据挖掘算法对学生的各项指标进行评价,为学校提供了科学的评价依据。

该系统具有评价准确、数据分析能力强、操作简单等特点。

4. 'Research on Student Learning Management System Based on Cloud Computing'该文献介绍了一种基于云计算技术的学生学习管理系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。