P0口讲义

单片机IO端口工作原理(P0端口,漏极开路,推挽,上拉电阻,准双向口)

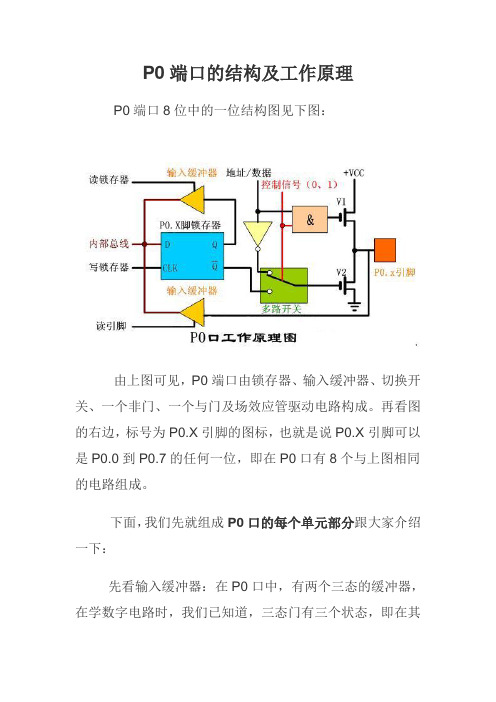

单片机IO端口工作原理(P0端口,漏极开路,推挽,上拉电阻,准双向口)一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:输入缓冲器:在P0口中,有两个三态的缓冲器,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态。

图中有一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

图中另一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

图中的锁存器,D 端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q 非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

那么这个多路选择开关就是用于选择是做为普通I/O口使用还是作为‘数据/地址’总线使用的选择开关了。

51系列单片机P0端口具体讲解

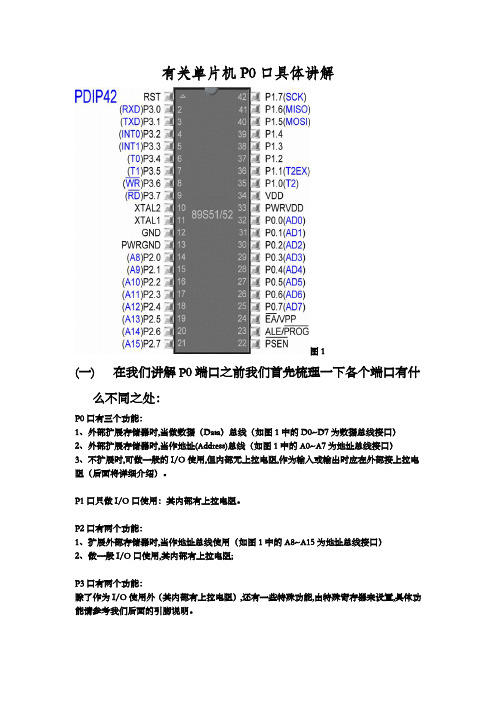

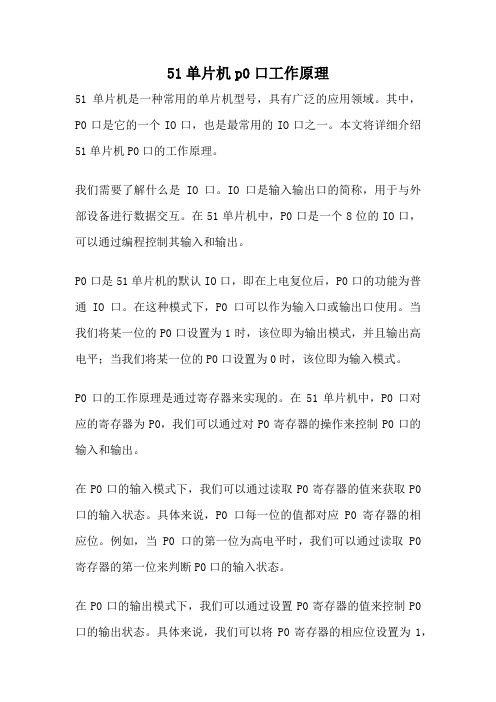

有关单片机P0口具体讲解图1(一)在我们讲解P0端口之前我们首先梳理一下各个端口有什么不同之处:P0口有三个功能:1、外部扩展存储器时,当做数据(Data)总线(如图1中的D0~D7为数据总线接口)2、外部扩展存储器时,当作地址(Address)总线(如图1中的A0~A7为地址总线接口)3、不扩展时,可做一般的I/O使用,但内部无上拉电阻,作为输入或输出时应在外部接上拉电阻(后面将详细介绍)。

P1口只做I/O口使用:其内部有上拉电阻。

P2口有两个功能:1、扩展外部存储器时,当作地址总线使用(如图1中的A8~A15为地址总线接口)2、做一般I/O口使用,其内部有上拉电阻;P3口有两个功能:除了作为I/O使用外(其内部有上拉电阻),还有一些特殊功能,由特殊寄存器来设置,具体功能请参考我们后面的引脚说明。

图2(注:该图只是P0口的一位,也就是说P0口有8个相同的这样的结构)图3(二)由图2可以看出每个P0口都有这些元件:一个锁存器,两个三态输入缓冲器和一个输出驱动电路组成在访问外部存储器时,P0是一个真正的双向口,当P0输出地址/数据信息时,CPU内部法控制电平“1”来打开上面的与门,又使模拟开关MUX把地址/数据信息经过反相器和T1接通(我们称上面的场效应晶体管FET为T1,下面的场效应管FET为T2);输出的地址/数据信息既通过与门去驱动T1,又通过反相器去驱动T2,是两个FET构成推拉输出电路;1.当P0口作为外部扩展存储器的数据地址总线时:●若地址数据信息为“0”,那么这个信号就使得T1截止,使T2导通(经过反反相器作用使得T2接收到的信号为“1”,根据场效应晶体管的特性,T2导通),若T2导通,那么T2的上下两个N极就导通,而发射极(下面的N极)接地信号则为“0”,这样P0口就相当于接收到了“0”信号;●若地址数据信息输入“1”,则该信号使T2截止,使T1导通,在T1导通情况下,T1的上下N极导通,使得VCC与P0相同,从而输出高电平,即“1”信号;●若从P0口输入信号,信号从引脚通过输入缓冲器进入内部总线;2.当P0口作为一般I/O口使用时:●CPU内部发布控制信号“0”,封锁与门,使得T1截止,同时使模拟开关MUX把锁存器的非Q端与T2端的栅极接通;●在P0口作为输出时,由于非Q端和T2的倒相作用,那么内部总线上的信息与到达P0口上的信息是同相的,只要写脉冲加到锁存器的CL端,内部总线上的信息就会P0的引脚上;●但是由于此时T2为漏极开路输出,所以要外接上拉电阻。

第5章 输入、输出接口P0~P3--1讲解

武汉科技大学

电信系

2. P1口 字节地址90H,位地址90H—97H

P1.0—P1.7: 准双向I/O口 输出时一切照常,输入时要先对其写“1”

读锁存器

内部 总线

写锁 存器

2

DQ CK /Q

1

读引脚

单片机及接口技术

Vcc 内部上拉电阻

引脚P1.X

17

第五章 输入、输出接口P0~P3

武汉科技大学

电信系

P1口

输入数据时,要先对其写“1”

读锁存器

Vcc 内部上拉电阻

内部 总线 1

写锁 存器

2

DQ

1

CK /Q

0

截 引脚P1.X 止

1

读引脚 =1

18

单片机及接口技术

第五章 输入、输出接口P0~P3

武汉科技大学

电信系

P1口

读锁存器

输出数据 1 时

内部 总线 1

写锁 存器

2

DQ

1

CK /Q

0

1

Vcc 内部上拉电阻

1

读引脚 =0

控制=1时,此脚作通用输出口: 输出=1时

23

单片机及接口技术

第五章 输入、输出接口P0~P3

武汉科技大学

电信系

P2口

读锁存器

内部 总线 0

写锁 存器

2

DQ CK /Q

地址高8位 控制 =1

Vcc 内部上拉电阻

0

1

3

=0

导 引脚P2.X 通

1 读引脚 =0

单片机及接口技术

控制=1 时,此脚作通用输出口: 输出=0 时

例5-1.设计一电路,监视某开关K,用发光二极 管LED显示开关状态,如果开关合上,LED亮、 开关打开,LED熄灭

单片机P0端口的结构及工作原理

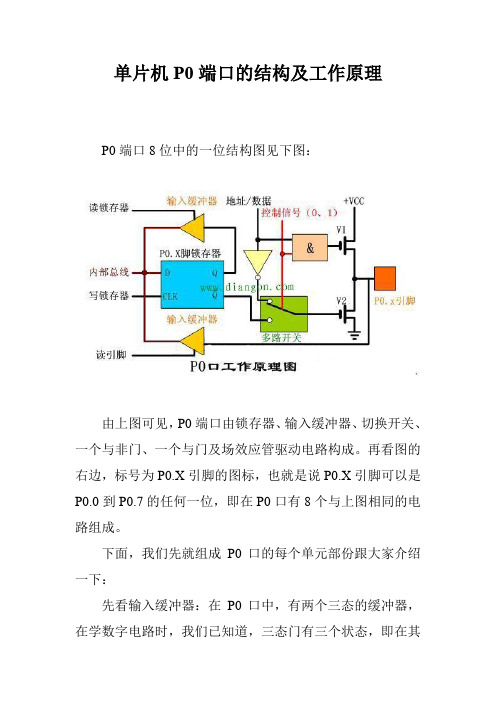

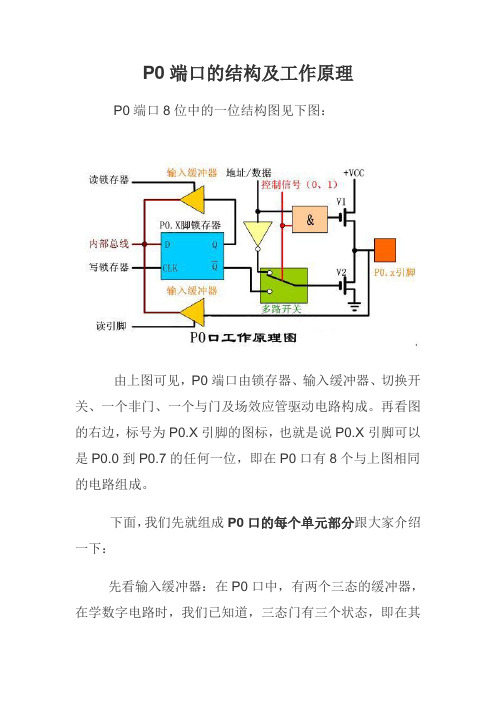

单片机P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X 引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

P0端口的结构及工作原理

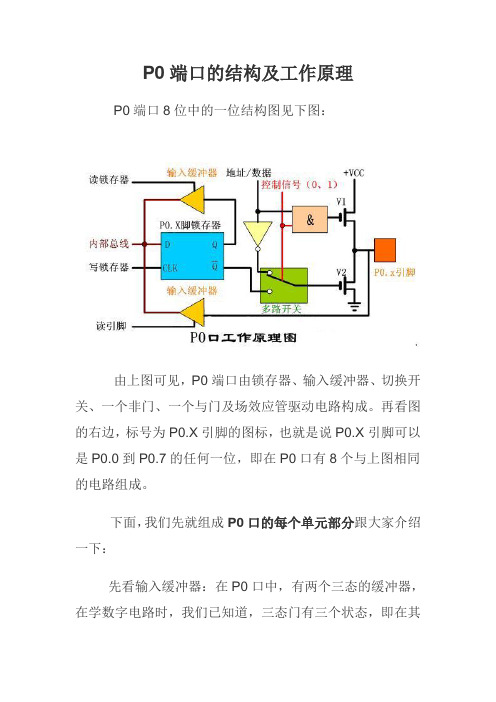

P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部分跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为…读锁存器‟端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为…读引脚‟的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D锁存器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q 非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为…地址/数据‟总线使用。

P0端口的结构及作工原理

P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部分跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为…读锁存器‟端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为…读引脚‟的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D锁存器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q 非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为…地址/数据‟总线使用。

51单片机p0口工作原理

51单片机p0口工作原理51单片机是一种常用的单片机型号,具有广泛的应用领域。

其中,P0口是它的一个IO口,也是最常用的IO口之一。

本文将详细介绍51单片机P0口的工作原理。

我们需要了解什么是IO口。

IO口是输入输出口的简称,用于与外部设备进行数据交互。

在51单片机中,P0口是一个8位的IO口,可以通过编程控制其输入和输出。

P0口是51单片机的默认IO口,即在上电复位后,P0口的功能为普通IO口。

在这种模式下,P0口可以作为输入口或输出口使用。

当我们将某一位的P0口设置为1时,该位即为输出模式,并且输出高电平;当我们将某一位的P0口设置为0时,该位即为输入模式。

P0口的工作原理是通过寄存器来实现的。

在51单片机中,P0口对应的寄存器为P0,我们可以通过对P0寄存器的操作来控制P0口的输入和输出。

在P0口的输入模式下,我们可以通过读取P0寄存器的值来获取P0口的输入状态。

具体来说,P0口每一位的值都对应P0寄存器的相应位。

例如,当P0口的第一位为高电平时,我们可以通过读取P0寄存器的第一位来判断P0口的输入状态。

在P0口的输出模式下,我们可以通过设置P0寄存器的值来控制P0口的输出状态。

具体来说,我们可以将P0寄存器的相应位设置为1,从而将对应的P0口输出高电平;或者将P0寄存器的相应位设置为0,从而将对应的P0口输出低电平。

需要注意的是,P0口的输入和输出可以同时进行。

也就是说,我们可以将P0口的某一位设置为输入模式,同时将其他位设置为输出模式,实现P0口的多功能使用。

除了普通的输入输出功能外,P0口还有其他特殊功能。

例如,P0口的第0位和第1位可以作为外部中断引脚使用。

当外部中断引脚检测到信号变化时,可以触发中断程序的执行。

这对于实时性要求较高的应用非常有用。

P0口的第2位和第3位还可以与定时器/计数器的控制信号相关联,用于定时和计数功能。

51单片机P0口是一个非常重要的IO口,具有广泛的应用。

2-07 P0口内部结构与特性

2-07

P0口内部结构与特性

Harbin Institute of Technology

1

P0口~ P3口

- 概述

AT89S51单片机共有4个I/O端口: P0~P3口 端口组成:每个端口8位,每位均由输出锁存器、输出驱动器和输入

缓冲器组成, 输出锁存器属特殊功能寄存器。 4个端口均可位寻址。

2

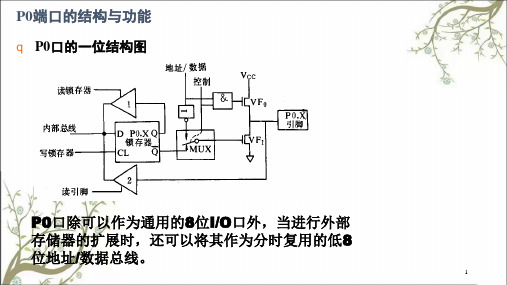

P0口

- 位电路结构 P0口为双功能的8位并行端口,字节地址为80H,位地址为80H~87H。

图 P0口位电路结构

3

P0口

- 工作原理

P0口工作过程分析 (1)P0口用作复用的地址/数据总线用

当作为地址或数据输出时,“控制”信号为1,硬件自动使转接开关MUX打向上 面,接通反相器的输出,同时使“与门” 开启。 当输出的地址/数据信息=1,“与门”输出为1,上方场效应管导通,下方场效 应管截止,P0.x引脚输出为1。 当输出的地址/数据信息=0,上方场效应管截止,下方场效应管导通,P0.x引 脚输出为0。

5

P0口

- 工作原理

具有高阻抗输入的I/O口应具有高电平、低电平和高阻抗3种状态的端口,是真正的双向 端口,简称双向口。 (2)P0口用作通用I/O口 对应的“控制”信号=0,MUX打向下面,接通锁存器的Q*端,“与门”输出为0,上方场 效应管截止,形成的P0口输出电路为漏极开路输出。 P0口作输出口时,CPU的“写”脉冲加在D锁存器的CP端,内部总线上的数据写入D锁存器, 并由引脚P0.x输出。

4

P0口

- 工作原理

由上、下两个场效应管形成的推拉式结构,大大提高负载能力,上方的场效应管这时起到内 部上拉电阻的作用。 当P0口作为数据输入时,仅从外部引脚读入信息,“控制”信号为0,MUX接通锁存器Q*端。 P0口作为地址/数据复用方式访问外部存储器时,CPU自动向P0口写入FFH,使下方场效应管 截止,上方场效应管由于控制信号为0也截止,从而保证数据信息的高阻抗输入,从外部输 入的数据直接由P0.x引脚通过输入缓冲器BUF2进入内部总线。

并行IO口及其应用课件

21

高电压光电隔离输入

22

23

I/O口的实例仿真

q 例4.3 报警器的proteus仿真及C语言程序设计

q 设计要求 :如图4.27所示,用P1.0输出1KHz和500Hz的 音频信号驱动扬声器,作报警信号,要求1KHz信号响 100ms,500Hz信号响200ms,交替进行,P1.7接一开关 进行控制,当开关合上报警信号响,当开关断开报警信 号停止。

25

4.3 I/O口应用实例与仿真

I/O口的实例仿真

q 例4.4广告灯(查表方式)的proteus仿真及程序设计

q 设计要求 :如图4.29所示,利用查表的方法,使端口P1 做单一灯的变化:左移2次,右移2次,闪烁2次(延时 的时间0.2秒)。

q 广告灯的仿真电路原理图 (见教材图4.29 ) q 元器件选取

q 灌电流和拉电流反应了管脚的带负载能力,灌电流比拉 电流大,因此灌电流带负载能力强。

q 限流电阻的选择要根据灌电流、拉电流的大小进行选择。

19

大功率负载驱动

q 当驱动大电流负载,或驱动高电压负载时,需要采用以 下的电路形式。

q 当驱动强电电路时,弱电电源与强电电源需要隔离,此 时需要使用光电隔离器件。

q 报警器的仿真电路原理图 (见教材图4.27) q 元器件选取

• ①AT89C52:单片机;②RES:电阻;③CRYSTAL:晶振; ④CAP、CAP-ELEC:电容、电解电容;⑤SPEAKER:扬 声器;⑥SW-SPDT:单刀双掷开关;⑦9012:PNP三极管

24

4.3 I/O口应用实例与仿真

I/O口的实例仿真

• 汇编语言步骤如下:①把控制码建成一个表TABLE;②利用 MOV DPTR,#TABLE指令来使数据指针寄存器指到表的开 头;③利用MOVC A,@A+DPTR的指令,根据累加器的值 再加上DPTR的值,就可以使程序计数器PC指到表格内所要 取出的数据。

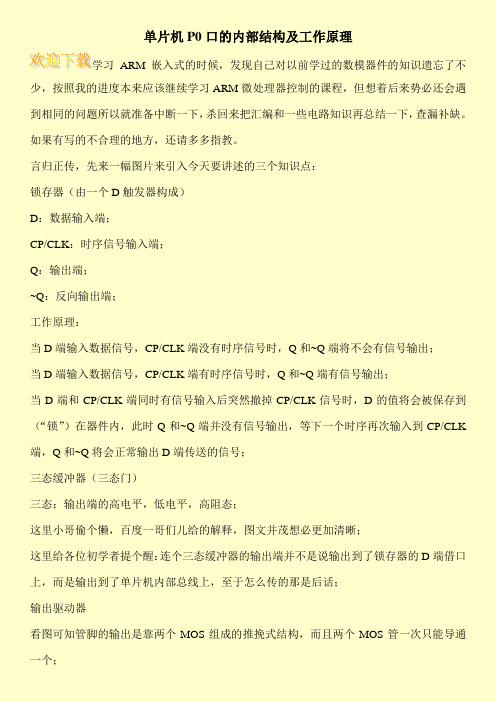

单片机P0口的内部结构及工作原理

单片机P0口的内部结构及工作原理

学习ARM嵌入式的时候,发现自己对以前学过的数模器件的知识遗忘了不少,按照我的进度本来应该继续学习ARM微处理器控制的课程,但想着后来势必还会遇到相同的问题所以就准备中断一下,杀回来把汇编和一些电路知识再总结一下,查漏补缺。

如果有写的不合理的地方,还请多多指教。

言归正传,先来一幅图片来引入今天要讲述的三个知识点:

锁存器(由一个D触发器构成)

D:数据输入端;

CP/CLK:时序信号输入端;

Q:输出端;

~Q:反向输出端;

工作原理:

当D端输入数据信号,CP/CLK端没有时序信号时,Q和~Q端将不会有信号输出;

当D端输入数据信号,CP/CLK端有时序信号时,Q和~Q端有信号输出;

当D端和CP/CLK端同时有信号输入后突然撤掉CP/CLK信号时,D的值将会被保存到(“锁”)在器件内,此时Q和~Q端并没有信号输出,等下一个时序再次输入到CP/CLK 端,Q和~Q将会正常输出D端传送的信号;

三态缓冲器(三态门)

三态:输出端的高电平,低电平,高阻态;

这里小哥偷个懒,百度一哥们儿给的解释,图文并茂想必更加清晰;

这里给各位初学者提个醒:连个三态缓冲器的输出端并不是说输出到了锁存器的D端借口上,而是输出到了单片机内部总线上,至于怎么传的那是后话;

输出驱动器

看图可知管脚的输出是靠两个MOS组成的推挽式结构,而且两个MOS管一次只能导通一个;。

P0端口的结构及工作原理

P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部分跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D锁存器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q 非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

单片机第五章课件输入输出接口P0 -P3

VSS

21

p 2 .0

MCS-51单片机内存配置 MCS-51单片机内存配置

MCS-51单片机的内存结构 单片机的内存结构

0FFFFH

0FFFFH

外部 ROM EA = 1

00FFH

特殊功

外部 RAM (64K)

能寄存器

1000H

0FFFH

0000 H

0080H

内部 ROM EA = 0

内部 RAM

MCS-51单片机内部结构 MCS-51单片机内部结构

内部结构框图如下: 内部结构框图如下:

频率基准源 计数器

振荡器及定 时电路

4 K /8K 存储器

字节程序 ROM

128 /256 节数据存储 器 RAM

字

2 个 16 位定 时器 / 计数器

内部总线 8051 CPU

64K 中断 中断

字节总

线扩展控制

一、P0口的结构 P0口的结构

下图为P0口的某位P0.n(n=0~7)结构图,它由一个 输出锁存器、两个三态输入缓冲器和输出驱动电路 及控制电路组成。从图中可以看出,P0口既可以作 为I/O用,也可以作为地址/数据线用。

地址/数据 地址/ 控制 VCC

读锁存器 内部总线 写锁存器 读引脚

D Q

T1 P0.n T2 MUX CLK Q

0000 H

0000 H

程序存储器

数据存储器

输入输出接口P 第五章 输入输出接口 0~P3 • 对单片机的控制,其实就是对I/O口的控制, 对单片机的控制,其实就是对 口的控制 口的控制, 无论单片机对外界进行何种控制, 无论单片机对外界进行何种控制,或接受 外部的何种控制,都是通过I/O口进行的 口进行的。 外部的何种控制,都是通过 口进行的。 51单片机总共有 、P1、P2、P3四个 位 单片机总共有P0、 、 、 四个 四个8位 单片机总共有 双向输入输出端口,每个端口都有锁存器、 双向输入输出端口,每个端口都有锁存器、 输出驱动器和输入缓冲器。 个 端口都能 输出驱动器和输入缓冲器。4个I/O端口都能 作输入输出口用,其中P0和 通常用于对 作输入输出口用,其中 和P2通常用于对 外部存储器的访问。 外部存储器的访问。

P0口讲义

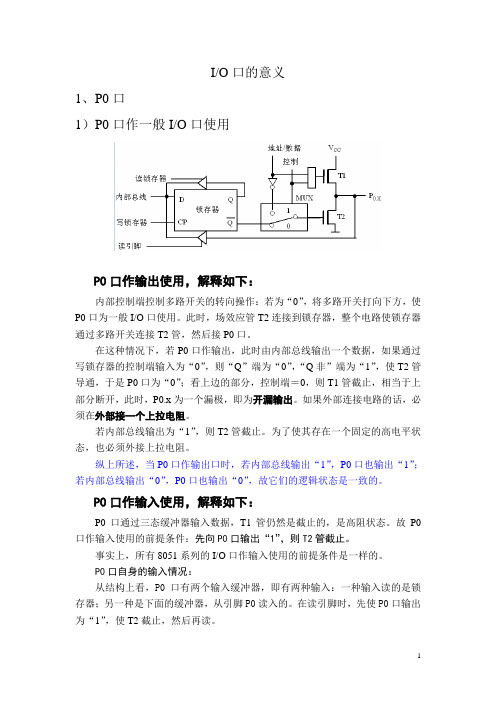

I/O口的意义1、P0口1)P0口作一般I/O口使用P0口作输出使用,解释如下:内部控制端控制多路开关的转向操作:若为“0”,将多路开关打向下方,使P0口为一般I/O口使用。

此时,场效应管T2连接到锁存器,整个电路使锁存器通过多路开关连接T2管,然后接P0口。

在这种情况下,若P0口作输出,此时由内部总线输出一个数据,如果通过写锁存器的控制端输入为“0”,则“Q”端为“0”,“Q非”端为“1”,使T2管导通,于是P0口为“0”;看上边的部分,控制端=0,则T1管截止,相当于上部分断开,此时,P0.x为一个漏极,即为开漏输出。

如果外部连接电路的话,必须在外部接一个上拉电阻。

若内部总线输出为“1”,则T2管截止。

为了使其存在一个固定的高电平状态,也必须外接上拉电阻。

纵上所述,当P0口作输出口时,若内部总线输出“1”,P0口也输出“1”;若内部总线输出“0”,P0口也输出“0”,故它们的逻辑状态是一致的。

P0口作输入使用,解释如下:P0口通过三态缓冲器输入数据,T1管仍然是截止的,是高阻状态。

故P0口作输入使用的前提条件:先向P0口输出“1”,则T2管截止。

事实上,所有8051系列的I/O口作输入使用的前提条件是一样的。

P0口自身的输入情况:从结构上看,P0口有两个输入缓冲器,即有两种输入:一种输入读的是锁存器;另一种是下面的缓冲器,从引脚P0读入的。

在读引脚时,先使P0口输出为“1”,使T2截止,然后再读。

读锁存器与读引脚是靠不同的命令来完成的。

读引脚时,直接读P0口;而其它的读锁存器,采用“读-修改-写”命令,先对P0口从锁存器读出来,再与累加器A中的数据相“与”。

2)P0口作地址/数据总线使用P0口可外扩存储器和I/O口。

当内部控制信号为“1”时,多路开关与非门输出端连接,输出端截止。

此时P0口为地址/数据总线工作状态。

此时地址/数据总线为“1”,则“与”门输出为“1”,T1导通,T2截止,把引脚拉为高电平;若地址/数据总线信号为“0”,则与门输出为“0”,则T1截止,T2导通,P0口输出为0。

P0端口

P0.0——P0.7是P0口的8位双向口线。

第一功能为基本输入输出;第二功能是在系统扩展时,分时做为数据总路线和低8位地址总线。

这里重点介绍一下P0口的结构及其工作过程:P0口的1位(例如:P0.0)结构如图它由一个输出锁存器、两个三态锁存器(1、2)、输出控制电路(一个非门(3)、一个与门(4)、一个多路控制开关(MUX))、输出驱动电路(两只场效应管Q1、Q2)组成。

功能1:做基本I/O口使用CPU发出的控制信号为低电平,使多路控制开关MUX接通B端,即与输出锁存器的“!Q”连接,同时使与门输出为低电平,场效应管Q1截止。

当P0输出数据时,写信号加在锁存器的R引脚上,内部总线上的数据通过S脚由锁存器的“!Q”端反相输出到Q2的栅极。

若内部总线上数据为1,则Q2栅极上为0,此时Q2截止,Q2处于漏极开路的开漏状态,因此为了保证P0.0输出高电平,必须外接上拉电阻,否则P0端口不能正常工作!若内部总线上数据为0,则Q2栅极为1,此时Q2导通,P0.0输出低电平。

当P0输入数据时,分为读引脚和读锁存器两种方式,分别用到两个输入缓冲器。

读引脚操作,即单片机执行端口输入指令(如MOV A,P0)时的操作。

这时由“读引脚”信号将三态缓冲器2打开,引脚上的数据经三态缓冲器2输入到内部总线。

读锁存器操作,即单片机执行“读—修改—写”类指令(如ANL A,P0)时的操作。

在执行这类指令时,由“读锁存器”信号使三态锁存器1打开,读入P0口在锁存器中的数据,然后与累加器A中的数据进行逻辑运算,再反结果写回到P0口。

这类操作不直接从P0口引脚上读入数据,而是从锁存器Q端读数据,其目的是为了防止出错,确保得到正确结果功能2:系统扩展时分时做为数据总路线和低8位地址总线此时控制信号为高电平,多路转换开关MUX接通A端,且与门的输出由“地址/数据”端的状态决定。

1. P0、P1、P2、P3四个均是___8__位的__并行____口(填“串行”还是“并行”) 其中P0的功能是____地址/数据分时复口___ P2口的功能是____高8位地址口_______ 而__P3__是双功能口 ___P1___是专门的用户口。

51系列单片机P0端口具体讲解

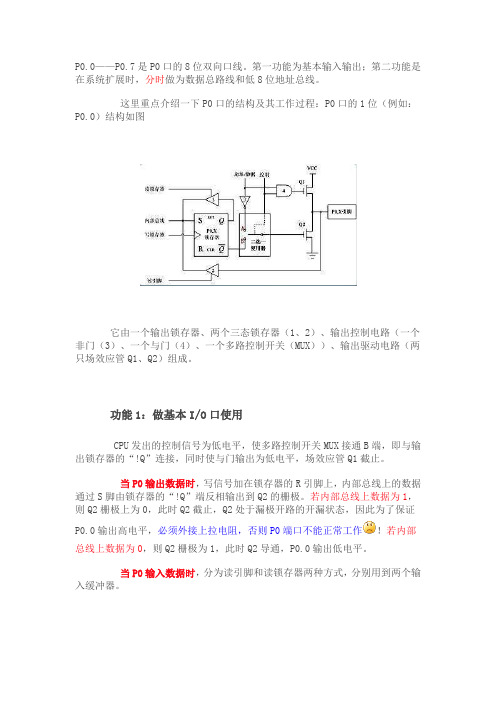

有关单片机P0口具体讲解图1(一)在我们讲解P0端口之前我们首先梳理一下各个端口有什么不同之处:P0口有三个功能:1、外部扩展存储器时,当做数据(Data)总线(如图1中的D0~D7为数据总线接口)2、外部扩展存储器时,当作地址(Address)总线(如图1中的A0~A7为地址总线接口)3、不扩展时,可做一般的I/O使用,但内部无上拉电阻,作为输入或输出时应在外部接上拉电阻(后面将详细介绍)。

P1口只做I/O口使用:其内部有上拉电阻。

P2口有两个功能:1、扩展外部存储器时,当作地址总线使用(如图1中的A8~A15为地址总线接口)2、做一般I/O口使用,其内部有上拉电阻;P3口有两个功能:除了作为I/O使用外(其内部有上拉电阻),还有一些特殊功能,由特殊寄存器来设置,具体功能请参考我们后面的引脚说明。

图2(注:该图只是P0口的一位,也就是说P0口有8个相同的这样的结构)图3(二)由图2可以看出每个P0口都有这些元件:一个锁存器,两个三态输入缓冲器和一个输出驱动电路组成在访问外部存储器时,P0是一个真正的双向口,当P0输出地址/数据信息时,CPU内部法控制电平“1”来打开上面的与门,又使模拟开关MUX把地址/数据信息经过反相器和T1接通(我们称上面的场效应晶体管FET为T1,下面的场效应管FET为T2);输出的地址/数据信息既通过与门去驱动T1,又通过反相器去驱动T2,是两个FET构成推拉输出电路;1.当P0口作为外部扩展存储器的数据地址总线时:●若地址数据信息为“0”,那么这个信号就使得T1截止,使T2导通(经过反反相器作用使得T2接收到的信号为“1”,根据场效应晶体管的特性,T2导通),若T2导通,那么T2的上下两个N极就导通,而发射极(下面的N极)接地信号则为“0”,这样P0口就相当于接收到了“0”信号;●若地址数据信息输入“1”,则该信号使T2截止,使T1导通,在T1导通情况下,T1的上下N极导通,使得VCC与P0相同,从而输出高电平,即“1”信号;●若从P0口输入信号,信号从引脚通过输入缓冲器进入内部总线;2.当P0口作为一般I/O口使用时:●CPU内部发布控制信号“0”,封锁与门,使得T1截止,同时使模拟开关MUX把锁存器的非Q端与T2端的栅极接通;●在P0口作为输出时,由于非Q端和T2的倒相作用,那么内部总线上的信息与到达P0口上的信息是同相的,只要写脉冲加到锁存器的CL端,内部总线上的信息就会P0的引脚上;●但是由于此时T2为漏极开路输出,所以要外接上拉电阻。

51单片机的P0口工作原理详细讲解

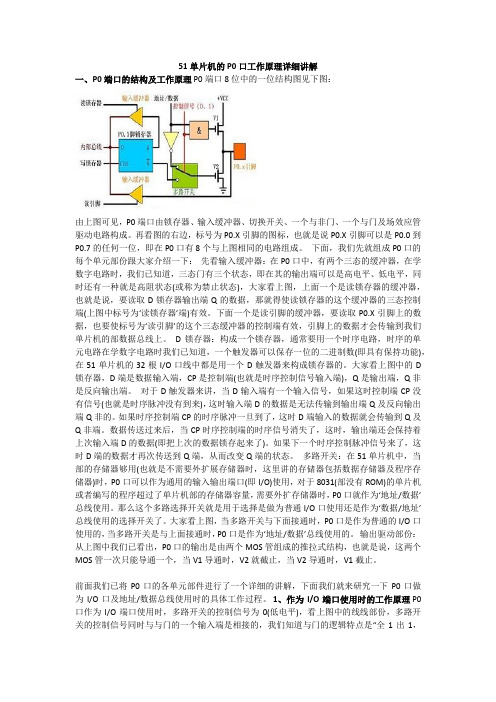

51单片机的P0口工作原理详细讲解一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D 锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

P0口上拉电阻及输入赋值解释

P0口的结构:说明:1. p0作为地址数据总线时,T1和T2是一起工作的,构成推挽结构。

高电平时,T1打开,T2截止;低电平时,T1截止,T2打开。

这种情况下不用外接上拉电阻.而且,当T1打开,T2截止,输出高电平的时候,因为内部电源直接通过T1输出到p0口线上,因此驱动能力(电流)可以很大,这就是为什么教科书上说可以"驱动8个TTL负载"的原因。

2. p0作为一般端口时,T1就永远的截止,T2根据输出数据0导通和1截止,导通时拉地,当然是输出低电平;要输出高电平,T2就截止,p0口就没有输出了,(注意,这种情况就是所谓的高阻浮空状态),如果加上外部上拉电阻,输出就变成了高电平1。

3. 其他端口p1,p2,p3,在内部直接将p1口中的T1换成了上拉电阻,所以不用外接,但内部上拉电阻太大,电流太小,有时因为电流不够,也会再并一个上拉电阻。

4. 在某个时刻,p0口上输出的是作为总线的地址数据信号还是作为普通I/O口的电平信号,是依靠多路开关MUX来切换的.而MUX的切换,又是根据单片机指令来区分的.当指令为外部存储器/IO口读/写时,比如 MOVX A,@DPTR , MUX是切换到地址/数据总线上;而当普通MOV传送指令操作p0口时,MUX是切换到内部总线上的。

5. p0(i/o),p1,p2,p3口用于输入时,需要写1使IO下拉的MOS管截止,以免MOS管导通将输入拉底为0,当一直用于输入时不用置1(先使用该IO输出,该IO锁存器里可能是0,再用该IO输入则会使MOS管导通),将IO写1后,该IO锁存器不会变了,所以再一直用于输入不用置1。

p0用于地址数据线时输入不用写1,因为MUX没和锁存器相连。

PS:Because Ports 1, 2, and 3 have fixed internal pullups, they are somet imes called “quasi- bidirectional” ports.因为端口1、2、3有固定的内部上拉,所以有时候他们被称为"准双向"口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

I/O口的意义

1、P0口

1)P0口作一般I/O口使用

P0口作输出使用,解释如下:

内部控制端控制多路开关的转向操作:若为“0”,将多路开关打向下方,使P0口为一般I/O口使用。

此时,场效应管T2连接到锁存器,整个电路使锁存器通过多路开关连接T2管,然后接P0口。

在这种情况下,若P0口作输出,此时由内部总线输出一个数据,如果通过写锁存器的控制端输入为“0”,则“Q”端为“0”,“Q非”端为“1”,使T2管导通,于是P0口为“0”;看上边的部分,控制端=0,则T1管截止,相当于上部分断开,此时,P0.x为一个漏极,即为开漏输出。

如果外部连接电路的话,必须在外部接一个上拉电阻。

若内部总线输出为“1”,则T2管截止。

为了使其存在一个固定的高电平状态,也必须外接上拉电阻。

纵上所述,当P0口作输出口时,若内部总线输出“1”,P0口也输出“1”;若内部总线输出“0”,P0口也输出“0”,故它们的逻辑状态是一致的。

P0口作输入使用,解释如下:

P0口通过三态缓冲器输入数据,T1管仍然是截止的,是高阻状态。

故P0口作输入使用的前提条件:先向P0口输出“1”,则T2管截止。

事实上,所有8051系列的I/O口作输入使用的前提条件是一样的。

P0口自身的输入情况:

从结构上看,P0口有两个输入缓冲器,即有两种输入:一种输入读的是锁存器;另一种是下面的缓冲器,从引脚P0读入的。

在读引脚时,先使P0口输出为“1”,使T2截止,然后再读。

读锁存器与读引脚是靠不同的命令来完成的。

读引脚时,直接读P0口;而其它的读锁存器,采用“读-修改-写”命令,先对P0口从锁存器读出来,再与累加器A中的数据相“与”。

2)P0口作地址/数据总线使用

P0口可外扩存储器和I/O口。

当内部控制信号为“1”时,多路开关与非门输出端连接,输出端截止。

此时P0口为地址/数据总线工作状态。

此时地址/数据总线为“1”,则“与”门输出为“1”,T1导通,T2截止,把引脚拉为高电平;若地址/数据总线信号为“0”,则与门输出为“0”,则T1截止,T2导通,P0口输出为0。

即把引脚拉为低电平。

故从引脚输出地址/数据信号。

2、P1口

P1口在口输出上有一个内部上拉电阻,本身就是一个准双向口。

无多路开关,只能作I/O口使用(在实际应用中,若选作I/O口,应首先选用P1口,其次考虑P3口)。

如果内部总线输出为1,T管截止,上拉电阻将引脚输出为1;

若内部总线输出为0,T管导通,输出为0,上拉电阻不起作用。

如果要输入时,原来内部总线输出为0,则T 管导通,这时,如果要把P1口作为输入口,那么输入的阻抗就极低,这样很容易被极低的上拉电阻拉为低电平。

故为了能保证正确的输入状态,首先内部总线输入为1,即T管截止,其输入阻抗就会很大,不会被拉为低电平。

3、P2口

P2口的逻辑电平与P1口相比,多了一个多路开关。

这个多路开关受内部控制信号的控制,当DPRT的高8位地址信号需由P2口输出时,内部控制信号将使输出驱动器接收地址信号。

(所有端口的输入状态与P0口都相同)注意:“地址”是单片机的高8位地址,与P0口共同组成了单片机的16位地址总线。

3、P3口

工作原理与其它端口类似。