LM3S9D90系列规格书,Datasheet 资料

M1A3P250-2VQ100IVQ100中文资料(Microsemi)中文数据手册「EasyDatasheet - 矽搜」

版本

器件手册章节可以有不同版本号. Actel目标是为客户提供及时事项最新信息.其结果是,该 表数据之前公布 已被充分表征.数据表被指定为"产品简介","高级",并 "生产".这些类别定义如下:

产品简介

产品简介是一个数据表摘要版本(高级或生产),包含 一般产品信息.本文给出具体设备和家庭概况 信息.

I / O说明和使用方法

I/在IGLOO和ProASIC3器件O结构. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1 I / O软件控制在低功耗闪存设备. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1 DDR为Actel低功耗闪存设备. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

封装和引脚说明 引脚说明. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1 包装. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

LM3S9L97-IBZ80-C3,LM3S9L97-IBZ80-C5,LM3S9L97-IQC80-C3,LM3S9L97-IQC80-C5, 规格书,Datasheet 资料

TEXAS INSTRUMENTS-PRODUCTION DATAStellaris®LM3S9L97MicrocontrollerDATA SHEETCopyright©2007-2012 DS-LM3S9L97-11425CopyrightCopyright©2007-2012Texas Instruments Incorporated All rights reserved.Stellaris and StellarisWare®are registered trademarks of Texas Instruments Incorporated.ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited.Other names and brands may be claimed as the property of others.PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.Texas Instruments Incorporated108Wild Basin,Suite350Austin,TX78746/stellaris/sc/technical-support/product-information-centers.htmStellaris®LM3S9L97MicrocontrollerTable of ContentsRevision History (41)About This Document (51)Audience (51)About This Manual (51)Related Documents (51)Documentation Conventions (52)1Architectural Overview (54)1.1Overview (54)1.2Target Applications (56)1.3Features (56)1.3.1ARM Cortex-M3Processor Core (56)1.3.2On-Chip Memory (58)1.3.3Serial Communications Peripherals (59)1.3.4System Integration (65)1.3.5Advanced Motion Control (71)1.3.6Analog (73)1.3.7JTAG and ARM Serial Wire Debug (74)1.3.8Packaging and Temperature (75)1.4Hardware Details (75)2The Cortex-M3Processor (76)2.1Block Diagram (77)2.2Overview (78)2.2.1System-Level Interface (78)2.2.2Integrated Configurable Debug (78)2.2.3Trace Port Interface Unit(TPIU) (79)2.2.4Cortex-M3System Component Details (79)2.3Programming Model (80)2.3.1Processor Mode and Privilege Levels for Software Execution (80)2.3.2Stacks (80)2.3.3Register Map (81)2.3.4Register Descriptions (82)2.3.5Exceptions and Interrupts (95)2.3.6Data Types (95)2.4Memory Model (95)2.4.1Memory Regions,Types and Attributes (97)2.4.2Memory System Ordering of Memory Accesses (98)2.4.3Behavior of Memory Accesses (98)2.4.4Software Ordering of Memory Accesses (99)2.4.5Bit-Banding (100)2.4.6Data Storage (102)2.4.7Synchronization Primitives (103)2.5Exception Model (104)2.5.1Exception States (105)2.5.2Exception Types (105)2.5.3Exception Handlers (108)Table of Contents2.5.4Vector Table (108)2.5.5Exception Priorities (109)2.5.6Interrupt Priority Grouping (110)2.5.7Exception Entry and Return (110)2.6Fault Handling (112)2.6.1Fault Types (113)2.6.2Fault Escalation and Hard Faults (113)2.6.3Fault Status Registers and Fault Address Registers (114)2.6.4Lockup (114)2.7Power Management (114)2.7.1Entering Sleep Modes (115)2.7.2Wake Up from Sleep Mode (115)2.8Instruction Set Summary (116)3Cortex-M3Peripherals (119)3.1Functional Description (119)3.1.1System Timer(SysTick) (119)3.1.2Nested Vectored Interrupt Controller(NVIC) (120)3.1.3System Control Block(SCB) (122)3.1.4Memory Protection Unit(MPU) (122)3.2Register Map (127)3.3System Timer(SysTick)Register Descriptions (129)3.4NVIC Register Descriptions (133)3.5System Control Block(SCB)Register Descriptions (146)3.6Memory Protection Unit(MPU)Register Descriptions (175)4JTAG Interface (185)4.1Block Diagram (186)4.2Signal Description (186)4.3Functional Description (187)4.3.1JTAG Interface Pins (187)4.3.2JTAG TAP Controller (189)4.3.3Shift Registers (189)4.3.4Operational Considerations (190)4.4Initialization and Configuration (192)4.5Register Descriptions (193)4.5.1Instruction Register(IR) (193)4.5.2Data Registers (195)5System Control (197)5.1Signal Description (197)5.2Functional Description (197)5.2.1Device Identification (198)5.2.2Reset Control (198)5.2.3Non-Maskable Interrupt (203)5.2.4Power Control (203)5.2.5Clock Control (204)5.2.6System Control (212)5.3Initialization and Configuration (213)5.4Register Map (214)5.5Register Descriptions (215)Stellaris®LM3S9L97Microcontroller 6Hibernation Module (304)6.1Block Diagram (305)6.2Signal Description (305)6.3Functional Description (306)6.3.1Register Access Timing (306)6.3.2Hibernation Clock Source (307)6.3.3System Implementation (308)6.3.4Battery Management (309)6.3.5Real-Time Clock (309)6.3.6Battery-Backed Memory (310)6.3.7Power Control Using HIB (310)6.3.8Power Control Using VDD3ON Mode (310)6.3.9Initiating Hibernate (310)6.3.10Waking from Hibernate (310)6.3.11Interrupts and Status (311)6.4Initialization and Configuration (311)6.4.1Initialization (311)6.4.2RTC Match Functionality(No Hibernation) (312)6.4.3RTC Match/Wake-Up from Hibernation (312)6.4.4External Wake-Up from Hibernation (313)6.4.5RTC or External Wake-Up from Hibernation (313)6.5Register Map (313)6.6Register Descriptions (314)7Internal Memory (331)7.1Block Diagram (331)7.2Functional Description (331)7.2.1SRAM (332)7.2.2ROM (332)7.2.3Flash Memory (334)7.3Register Map (339)7.4Flash Memory Register Descriptions(Flash Control Offset) (340)7.5Memory Register Descriptions(System Control Offset) (352)8Micro Direct Memory Access(μDMA) (368)8.1Block Diagram (369)8.2Functional Description (369)8.2.1Channel Assignments (370)8.2.2Priority (371)8.2.3Arbitration Size (371)8.2.4Request Types (371)8.2.5Channel Configuration (372)8.2.6Transfer Modes (374)8.2.7Transfer Size and Increment (382)8.2.8Peripheral Interface (382)8.2.9Software Request (382)8.2.10Interrupts and Errors (383)8.3Initialization and Configuration (383)8.3.1Module Initialization (383)8.3.2Configuring a Memory-to-Memory Transfer (383)Table of Contents8.3.3Configuring a Peripheral for Simple Transmit (385)8.3.4Configuring a Peripheral for Ping-Pong Receive (386)8.3.5Configuring Channel Assignments (389)8.4Register Map (389)8.5μDMA Channel Control Structure (390)8.6μDMA Register Descriptions (397)9General-Purpose Input/Outputs(GPIOs) (426)9.1Signal Description (426)9.2Functional Description (430)9.2.1Data Control (432)9.2.2Interrupt Control (433)9.2.3Mode Control (434)9.2.4Commit Control (434)9.2.5Pad Control (435)9.2.6Identification (435)9.3Initialization and Configuration (435)9.4Register Map (436)9.5Register Descriptions (439)10General-Purpose Timers (482)10.1Block Diagram (483)10.2Signal Description (483)10.3Functional Description (486)10.3.1GPTM Reset Conditions (487)10.3.2Timer Modes (487)10.3.3DMA Operation (493)10.3.4Accessing Concatenated Register Values (494)10.4Initialization and Configuration (494)10.4.1One-Shot/Periodic Timer Mode (494)10.4.2Real-Time Clock(RTC)Mode (495)10.4.3Input Edge-Count Mode (495)10.4.4Input Edge Timing Mode (496)10.4.5PWM Mode (497)10.5Register Map (497)10.6Register Descriptions (498)11Watchdog Timers (529)11.1Block Diagram (530)11.2Functional Description (530)11.2.1Register Access Timing (531)11.3Initialization and Configuration (531)11.4Register Map (531)11.5Register Descriptions (532)12Analog-to-Digital Converter(ADC) (554)12.1Block Diagram (555)12.2Signal Description (556)12.3Functional Description (558)12.3.1Sample Sequencers (558)12.3.2Module Control (559)Stellaris®LM3S9L97Microcontroller 12.3.3Hardware Sample Averaging Circuit (561)12.3.4Analog-to-Digital Converter (562)12.3.5Differential Sampling (565)12.3.6Internal Temperature Sensor (568)12.3.7Digital Comparator Unit (568)12.4Initialization and Configuration (573)12.4.1Module Initialization (573)12.4.2Sample Sequencer Configuration (574)12.5Register Map (574)12.6Register Descriptions (576)13Universal Asynchronous Receivers/Transmitters(UARTs) (634)13.1Block Diagram (635)13.2Signal Description (635)13.3Functional Description (637)13.3.1Transmit/Receive Logic (637)13.3.2Baud-Rate Generation (638)13.3.3Data Transmission (639)13.3.4Serial IR(SIR) (639)13.3.5ISO7816Support (640)13.3.6Modem Handshake Support (640)13.3.7LIN Support (642)13.3.8FIFO Operation (643)13.3.9Interrupts (644)13.3.10Loopback Operation (645)13.3.11DMA Operation (645)13.4Initialization and Configuration (645)13.5Register Map (646)13.6Register Descriptions (648)14Synchronous Serial Interface(SSI) (698)14.1Block Diagram (699)14.2Signal Description (699)14.3Functional Description (700)14.3.1Bit Rate Generation (701)14.3.2FIFO Operation (701)14.3.3Interrupts (701)14.3.4Frame Formats (702)14.3.5DMA Operation (709)14.4Initialization and Configuration (710)14.5Register Map (711)14.6Register Descriptions (712)15Inter-Integrated Circuit(I2C)Interface (740)15.1Block Diagram (741)15.2Signal Description (741)15.3Functional Description (742)15.3.1I2C Bus Functional Overview (742)15.3.2Available Speed Modes (744)15.3.3Interrupts (745)15.3.4Loopback Operation (746)Table of Contents15.3.5Command Sequence Flow Charts (747)15.4Initialization and Configuration (754)15.5Register Map (755)15.6Register Descriptions(I2C Master) (756)15.7Register Descriptions(I2C Slave) (769)16Inter-Integrated Circuit Sound(I2S)Interface (778)16.1Block Diagram (779)16.2Signal Description (779)16.3Functional Description (780)16.3.1Transmit (782)16.3.2Receive (786)16.4Initialization and Configuration (788)16.5Register Map (789)16.6Register Descriptions (790)17Controller Area Network(CAN)Module (815)17.1Block Diagram (816)17.2Signal Description (816)17.3Functional Description (817)17.3.1Initialization (818)17.3.2Operation (819)17.3.3Transmitting Message Objects (820)17.3.4Configuring a Transmit Message Object (820)17.3.5Updating a Transmit Message Object (821)17.3.6Accepting Received Message Objects (822)17.3.7Receiving a Data Frame (822)17.3.8Receiving a Remote Frame (822)17.3.9Receive/Transmit Priority (823)17.3.10Configuring a Receive Message Object (823)17.3.11Handling of Received Message Objects (824)17.3.12Handling of Interrupts (826)17.3.13Test Mode (827)17.3.14Bit Timing Configuration Error Considerations (829)17.3.15Bit Time and Bit Rate (829)17.3.16Calculating the Bit Timing Parameters (831)17.4Register Map (834)17.5CAN Register Descriptions (835)18Ethernet Controller (866)18.1Block Diagram (867)18.2Signal Description (868)18.3Functional Description (869)18.3.1MAC Operation (869)18.3.2Internal MII Operation (873)18.3.3PHY Operation (873)18.3.4Interrupts (875)18.3.5DMA Operation (876)18.4Initialization and Configuration (876)18.4.1Hardware Configuration (876)Stellaris®LM3S9L97Microcontroller 18.4.2Software Configuration (877)18.5Register Map (878)18.6Ethernet MAC Register Descriptions (880)18.7MII Management Register Descriptions (906)19Universal Serial Bus(USB)Controller (927)19.1Block Diagram (928)19.2Signal Description (928)19.3Functional Description (930)19.3.1Operation as a Device (930)19.3.2Operation as a Host (935)19.3.3OTG Mode (939)19.3.4DMA Operation (941)19.4Initialization and Configuration (942)19.4.1Pin Configuration (942)19.4.2Endpoint Configuration (942)19.5Register Map (943)19.6Register Descriptions (954)20Analog Comparators (1066)20.1Block Diagram (1066)20.2Signal Description (1067)20.3Functional Description (1068)20.3.1Internal Reference Programming (1068)20.4Initialization and Configuration (1070)20.5Register Map (1071)20.6Register Descriptions (1071)21Pulse Width Modulator(PWM) (1079)21.1Block Diagram (1080)21.2Signal Description (1081)21.3Functional Description (1084)21.3.1PWM Timer (1084)21.3.2PWM Comparators (1084)21.3.3PWM Signal Generator (1085)21.3.4Dead-Band Generator (1086)21.3.5Interrupt/ADC-Trigger Selector (1087)21.3.6Synchronization Methods (1087)21.3.7Fault Conditions (1088)21.3.8Output Control Block (1089)21.4Initialization and Configuration (1089)21.5Register Map (1090)21.6Register Descriptions (1092)22Quadrature Encoder Interface(QEI) (1151)22.1Block Diagram (1151)22.2Signal Description (1152)22.3Functional Description (1153)22.4Initialization and Configuration (1155)22.5Register Map (1156)22.6Register Descriptions (1157)Table of Contents23Pin Diagram (1174)24Signal Tables (1176)24.1100-Pin LQFP Package Pin Tables (1177)24.2108-Ball BGA Package Pin Tables (1209)24.3Connections for Unused Signals (1242)25Operating Characteristics (1245)26Electrical Characteristics (1246)26.1Maximum Ratings (1246)26.2Recommended Operating Conditions (1246)26.3Load Conditions (1247)26.4JTAG and Boundary Scan (1247)26.5Power and Brown-Out (1249)26.6Reset (1250)26.7On-Chip Low Drop-Out(LDO)Regulator (1251)26.8Clocks (1251)26.8.1PLL Specifications (1251)26.8.2PIOSC Specifications (1252)26.8.3Internal30-kHz Oscillator Specifications (1252)26.8.4Hibernation Clock Source Specifications (1253)26.8.5Main Oscillator Specifications (1253)26.8.6System Clock Specification with ADC Operation (1254)26.8.7System Clock Specification with USB Operation (1254)26.9Sleep Modes (1254)26.10Hibernation Module (1255)26.11Flash Memory (1256)26.12Input/Output Characteristics (1256)26.13Analog-to-Digital Converter(ADC) (1257)26.14Synchronous Serial Interface(SSI) (1258)26.15Inter-Integrated Circuit(I2C)Interface (1260)26.16Inter-Integrated Circuit Sound(I2S)Interface (1261)26.17Ethernet Controller (1262)26.18Universal Serial Bus(USB)Controller (1265)26.19Analog Comparator (1265)26.20Current Consumption (1266)26.20.1Nominal Power Consumption (1266)26.20.2Maximum Current Consumption (1267)A Register Quick Reference (1269)B Ordering and Contact Information (1320)B.1Ordering Information (1320)B.2Part Markings (1320)B.3Kits (1321)B.4Support Information (1321)C Package Information (1322)C.1100-Pin LQFP Package (1322)C.1.1Package Dimensions (1322)C.1.2Tray Dimensions (1324)C.1.3Tape and Reel Dimensions (1324)C.2108-Ball BGA Package (1326)C.2.1Package Dimensions (1326)C.2.2Tray Dimensions (1328)C.2.3Tape and Reel Dimensions (1329)List of FiguresFigure1-1.Stellaris LM3S9L97Microcontroller High-Level Block Diagram (55)Figure2-1.CPU Block Diagram (78)Figure2-2.TPIU Block Diagram (79)Figure2-3.Cortex-M3Register Set (81)Figure2-4.Bit-Band Mapping (102)Figure2-5.Data Storage (103)Figure2-6.Vector Table (109)Figure2-7.Exception Stack Frame (111)Figure3-1.SRD Use Example (125)Figure4-1.JTAG Module Block Diagram (186)Figure4-2.Test Access Port State Machine (189)Figure4-3.IDCODE Register Format (195)Figure4-4.BYPASS Register Format (195)Figure4-5.Boundary Scan Register Format (196)Figure5-1.Basic RST Configuration (200)Figure5-2.External Circuitry to Extend Power-On Reset (200)Figure5-3.Reset Circuit Controlled by Switch (201)Figure5-4.Power Architecture (204)Figure5-5.Main Clock Tree (207)Figure6-1.Hibernation Module Block Diagram (305)ing a Crystal as the Hibernation Clock Source (308)ing a Dedicated Oscillator as the Hibernation Clock Source with VDD3ONMode (308)Figure7-1.Internal Memory Block Diagram (331)Figure8-1.μDMA Block Diagram (369)Figure8-2.Example of Ping-PongμDMA Transaction (375)Figure8-3.Memory Scatter-Gather,Setup and Configuration (377)Figure8-4.Memory Scatter-Gather,μDMA Copy Sequence (378)Figure8-5.Peripheral Scatter-Gather,Setup and Configuration (380)Figure8-6.Peripheral Scatter-Gather,μDMA Copy Sequence (381)Figure9-1.Digital I/O Pads (431)Figure9-2.Analog/Digital I/O Pads (432)Figure9-3.GPIODATA Write Example (433)Figure9-4.GPIODATA Read Example (433)Figure10-1.GPTM Module Block Diagram (483)Figure10-2.Timer Daisy Chain (489)Figure10-3.Input Edge-Count Mode Example (491)Figure10-4.16-Bit Input Edge-Time Mode Example (492)Figure10-5.16-Bit PWM Mode Example (493)Figure11-1.WDT Module Block Diagram (530)Figure12-1.Implementation of Two ADC Blocks (555)Figure12-2.ADC Module Block Diagram (556)Figure12-3.ADC Sample Phases (560)Figure12-4.Doubling the ADC Sample Rate (561)Figure12-5.Skewed Sampling (561)Figure12-6.Sample Averaging Example (562)Figure12-7.ADC Input Equivalency Diagram (563)Figure12-8.Internal Voltage Conversion Result (564)Figure12-9.External Voltage Conversion Result (565)Figure12-10.Differential Sampling Range,V IN_ODD=1.5V (566)Figure12-11.Differential Sampling Range,V IN_ODD=0.75V (567)Figure12-12.Differential Sampling Range,V IN_ODD=2.25V (567)Figure12-13.Internal Temperature Sensor Characteristic (568)Figure12-14.Low-Band Operation(CIC=0x0and/or CTC=0x0) (571)Figure12-15.Mid-Band Operation(CIC=0x1and/or CTC=0x1) (572)Figure12-16.High-Band Operation(CIC=0x3and/or CTC=0x3) (573)Figure13-1.UART Module Block Diagram (635)Figure13-2.UART Character Frame (638)Figure13-3.IrDA Data Modulation (640)Figure13-4.LIN Message (642)Figure13-5.LIN Synchronization Field (643)Figure14-1.SSI Module Block Diagram (699)Figure14-2.TI Synchronous Serial Frame Format(Single Transfer) (703)Figure14-3.TI Synchronous Serial Frame Format(Continuous Transfer) (703)Figure14-4.Freescale SPI Format(Single Transfer)with SPO=0and SPH=0 (704)Figure14-5.Freescale SPI Format(Continuous Transfer)with SPO=0and SPH=0 (704)Figure14-6.Freescale SPI Frame Format with SPO=0and SPH=1 (705)Figure14-7.Freescale SPI Frame Format(Single Transfer)with SPO=1and SPH=0 (706)Figure14-8.Freescale SPI Frame Format(Continuous Transfer)with SPO=1and SPH=0 (706)Figure14-9.Freescale SPI Frame Format with SPO=1and SPH=1 (707)Figure14-10.MICROWIRE Frame Format(Single Frame) (708)Figure14-11.MICROWIRE Frame Format(Continuous Transfer) (709)Figure14-12.MICROWIRE Frame Format,SSIFss Input Setup and Hold Requirements (709)Figure15-1.I2C Block Diagram (741)Figure15-2.I2C Bus Configuration (742)Figure15-3.START and STOP Conditions (743)plete Data Transfer with a7-Bit Address (743)Figure15-5.R/S Bit in First Byte (744)Figure15-6.Data Validity During Bit Transfer on the I2C Bus (744)Figure15-7.Master Single TRANSMIT (748)Figure15-8.Master Single RECEIVE (749)Figure15-9.Master TRANSMIT with Repeated START (750)Figure15-10.Master RECEIVE with Repeated START (751)Figure15-11.Master RECEIVE with Repeated START after TRANSMIT with RepeatedSTART (752)Figure15-12.Master TRANSMIT with Repeated START after RECEIVE with RepeatedSTART (753)Figure15-13.Slave Command Sequence (754)Figure16-1.I2S Block Diagram (779)Figure16-2.I2S Data Transfer (782)Figure16-3.Left-Justified Data Transfer (782)Figure16-4.Right-Justified Data Transfer (782)Figure17-1.CAN Controller Block Diagram (816)Figure17-2.CAN Data/Remote Frame (818)Figure17-3.Message Objects in a FIFO Buffer (826)Figure17-4.CAN Bit Time (830)Figure18-1.Ethernet Controller (867)Figure18-2.Ethernet Controller Block Diagram (867)Figure18-3.Ethernet Frame (869)Figure18-4.Interface to an Ethernet Jack (877)B Module Block Diagram (928)Figure20-1.Analog Comparator Module Block Diagram (1066)Figure20-2.Structure of Comparator Unit (1068)parator Internal Reference Structure (1069)Figure21-1.PWM Module Diagram (1081)Figure21-2.PWM Generator Block Diagram (1081)Figure21-3.PWM Count-Down Mode (1085)Figure21-4.PWM Count-Up/Down Mode (1085)Figure21-5.PWM Generation Example In Count-Up/Down Mode (1086)Figure21-6.PWM Dead-Band Generator (1086)Figure22-1.QEI Block Diagram (1152)Figure22-2.Quadrature Encoder and Velocity Predivider Operation (1154)Figure23-1.100-Pin LQFP Package Pin Diagram (1174)Figure23-2.108-Ball BGA Package Pin Diagram(Top View) (1175)Figure26-1.Load Conditions (1247)Figure26-2.JTAG Test Clock Input Timing (1248)Figure26-3.JTAG Test Access Port(TAP)Timing (1248)Figure26-4.Power-On Reset Timing (1249)Figure26-5.Brown-Out Reset Timing (1249)Figure26-6.Power-On Reset and Voltage Parameters (1250)Figure26-7.External Reset Timing(RST) (1250)Figure26-8.Software Reset Timing (1250)Figure26-9.Watchdog Reset Timing (1251)Figure26-10.MOSC Failure Reset Timing (1251)Figure26-11.Hibernation Module Timing with Internal Oscillator Running in Hibernation (1256)Figure26-12.Hibernation Module Timing with Internal Oscillator Stopped in Hibernation (1256)Figure26-13.ADC Input Equivalency Diagram (1258)Figure26-14.SSI Timing for TI Frame Format(FRF=01),Single Transfer TimingMeasurement (1259)Figure26-15.SSI Timing for MICROWIRE Frame Format(FRF=10),Single Transfer (1259)Figure26-16.SSI Timing for SPI Frame Format(FRF=00),with SPH=1 (1260)Figure26-17.I2C Timing (1261)Figure26-18.I2S Master Mode Transmit Timing (1261)Figure26-19.I2S Master Mode Receive Timing (1262)Figure26-20.I2S Slave Mode Transmit Timing (1262)Figure26-21.I2S Slave Mode Receive Timing (1262)Figure26-22.External XTLP Oscillator Characteristics (1265)Figure C-1.Stellaris LM3S9L97100-Pin LQFP Package Dimensions (1322)Figure C-2.100-Pin LQFP Tray Dimensions (1324)Figure C-3.100-Pin LQFP Tape and Reel Dimensions (1325)Figure C-4.Stellaris LM3S9L97108-Ball BGA Package Dimensions (1326)Figure C-5.108-Ball BGA Tray Dimensions (1328)Figure C-6.108-Ball BGA Tape and Reel Dimensions (1329)List of TablesTable1.Revision History (41)Table2.Documentation Conventions (52)Table2-1.Summary of Processor Mode,Privilege Level,and Stack Use (81)Table2-2.Processor Register Map (82)Table2-3.PSR Register Combinations (87)Table2-4.Memory Map (95)Table2-5.Memory Access Behavior (98)Table2-6.SRAM Memory Bit-Banding Regions (100)Table2-7.Peripheral Memory Bit-Banding Regions (100)Table2-8.Exception Types (106)Table2-9.Interrupts (107)Table2-10.Exception Return Behavior (112)Table2-11.Faults (113)Table2-12.Fault Status and Fault Address Registers (114)Table2-13.Cortex-M3Instruction Summary (116)Table3-1.Core Peripheral Register Regions (119)Table3-2.Memory Attributes Summary (122)Table3-3.TEX,S,C,and B Bit Field Encoding (125)Table3-4.Cache Policy for Memory Attribute Encoding (126)Table3-5.AP Bit Field Encoding (126)Table3-6.Memory Region Attributes for Stellaris Microcontrollers (126)Table3-7.Peripherals Register Map (127)Table3-8.Interrupt Priority Levels (154)Table3-9.Example SIZE Field Values (182)Table4-1.JTAG_SWD_SWO Signals(100LQFP) (186)Table4-2.JTAG_SWD_SWO Signals(108BGA) (187)Table4-3.JTAG Port Pins State after Power-On Reset or RST assertion (188)Table4-4.JTAG Instruction Register Commands (193)Table5-1.System Control&Clocks Signals(100LQFP) (197)Table5-2.System Control&Clocks Signals(108BGA) (197)Table5-3.Reset Sources (198)Table5-4.Clock Source Options (205)Table5-5.Possible System Clock Frequencies Using the SYSDIV Field (208)Table5-6.Examples of Possible System Clock Frequencies Using the SYSDIV2Field (208)Table5-7.Examples of Possible System Clock Frequencies with DIV400=1 (209)Table5-8.System Control Register Map (214)Table5-9.RCC2Fields that Override RCC Fields (235)Table6-1.Hibernate Signals(100LQFP) (305)Table6-2.Hibernate Signals(108BGA) (306)Table6-3.Hibernation Module Clock Operation (312)Table6-4.Hibernation Module Register Map (314)Table7-1.Flash Memory Protection Policy Combinations (335)er-Programmable Flash Memory Resident Registers (339)Table7-3.Flash Register Map (339)Table8-1.μDMA Channel Assignments (370)Table8-2.Request Type Support (372)Table8-3.Control Structure Memory Map (373)Table8-4.Channel Control Structure (373)Table8-5.μDMA Read Example:8-Bit Peripheral (382)Table8-6.μDMA Interrupt Assignments (383)Table8-7.Channel Control Structure Offsets for Channel30 (384)Table8-8.Channel Control Word Configuration for Memory Transfer Example (384)Table8-9.Channel Control Structure Offsets for Channel7 (385)Table8-10.Channel Control Word Configuration for Peripheral Transmit Example (386)Table8-11.Primary and Alternate Channel Control Structure Offsets for Channel8 (387)Table8-12.Channel Control Word Configuration for Peripheral Ping-Pong ReceiveExample (388)Table8-13.μDMA Register Map (389)Table9-1.GPIO Pins With Non-Zero Reset Values (427)Table9-2.GPIO Pins and Alternate Functions(100LQFP) (427)Table9-3.GPIO Pins and Alternate Functions(108BGA) (429)Table9-4.GPIO Pad Configuration Examples (435)Table9-5.GPIO Interrupt Configuration Example (436)Table9-6.GPIO Pins With Non-Zero Reset Values (437)Table9-7.GPIO Register Map (437)Table9-8.GPIO Pins With Non-Zero Reset Values (450)Table9-9.GPIO Pins With Non-Zero Reset Values (456)Table9-10.GPIO Pins With Non-Zero Reset Values (458)Table9-11.GPIO Pins With Non-Zero Reset Values (461)Table9-12.GPIO Pins With Non-Zero Reset Values (468)Table10-1.Available CCP Pins (483)Table10-2.General-Purpose Timers Signals(100LQFP) (484)Table10-3.General-Purpose Timers Signals(108BGA) (485)Table10-4.General-Purpose Timer Capabilities (486)Table10-5.Counter Values When the Timer is Enabled in Periodic or One-Shot Modes (487)Table10-6.16-Bit Timer With Prescaler Configurations (488)Table10-7.Counter Values When the Timer is Enabled in RTC Mode (489)Table10-8.Counter Values When the Timer is Enabled in Input Edge-Count Mode (490)Table10-9.Counter Values When the Timer is Enabled in Input Event-Count Mode (491)Table10-10.Counter Values When the Timer is Enabled in PWM Mode (492)Table10-11.Timers Register Map (497)Table11-1.Watchdog Timers Register Map (532)Table12-1.ADC Signals(100LQFP) (556)Table12-2.ADC Signals(108BGA) (557)Table12-3.Samples and FIFO Depth of Sequencers (558)Table12-4.Differential Sampling Pairs (565)Table12-5.ADC Register Map (574)Table13-1.UART Signals(100LQFP) (636)Table13-2.UART Signals(108BGA) (636)Table13-3.Flow Control Mode (641)Table13-4.UART Register Map (647)Table14-1.SSI Signals(100LQFP) (700)Table14-2.SSI Signals(108BGA) (700)Table14-3.SSI Register Map (711)Table15-2.I2C Signals(108BGA) (741)Table15-3.Examples of I2C Master Timer Period versus Speed Mode (745)Table15-4.Inter-Integrated Circuit(I2C)Interface Register Map (755)Table15-5.Write Field Decoding for I2CMCS[3:0]Field (761)Table16-1.I2S Signals(100LQFP) (780)Table16-2.I2S Signals(108BGA) (780)Table16-3.I2S Transmit FIFO Interface (783)Table16-4.Crystal Frequency(Values from3.5795MHz to5MHz) (784)Table16-5.Crystal Frequency(Values from5.12MHz to8.192MHz) (784)Table16-6.Crystal Frequency(Values from10MHz to14.3181MHz) (785)Table16-7.Crystal Frequency(Values from16MHz to16.384MHz) (785)Table16-8.I2S Receive FIFO Interface (787)Table16-9.Audio Formats Configuration (789)Table16-10.Inter-Integrated Circuit Sound(I2S)Interface Register Map (790)Table17-1.Controller Area Network Signals(100LQFP) (817)Table17-2.Controller Area Network Signals(108BGA) (817)Table17-3.Message Object Configurations (823)Table17-4.CAN Protocol Ranges (830)Table17-5.CANBIT Register Values (830)Table17-6.CAN Register Map (834)Table18-1.Ethernet Signals(100LQFP) (868)Table18-2.Ethernet Signals(108BGA) (868)Table18-3.TX&RX FIFO Organization (871)Table18-4.Ethernet Register Map (878)B Signals(100LQFP) (928)B Signals(108BGA) (929)Table19-3.Remainder(MAXLOAD/4) (941)Table19-4.Actual Bytes Read (941)Table19-5.Packet Sizes That Clear RXRDY (941)Table19-6.Universal Serial Bus(USB)Controller Register Map (943)Table20-1.Analog Comparators Signals(100LQFP) (1067)Table20-2.Analog Comparators Signals(108BGA) (1067)Table20-3.Internal Reference Voltage and ACREFCTL Field Values (1069)Table20-4.Analog Comparators Register Map (1071)Table21-1.PWM Signals(100LQFP) (1082)Table21-2.PWM Signals(108BGA) (1083)Table21-3.PWM Register Map (1090)Table22-1.QEI Signals(100LQFP) (1152)Table22-2.QEI Signals(108BGA) (1153)Table22-3.QEI Register Map (1156)Table24-1.GPIO Pins With Default Alternate Functions (1176)Table24-2.Signals by Pin Number (1177)Table24-3.Signals by Signal Name (1187)Table24-4.Signals by Function,Except for GPIO (1196)Table24-5.GPIO Pins and Alternate Functions (1204)Table24-6.Possible Pin Assignments for Alternate Functions (1207)Table24-7.Signals by Pin Number (1209)。

三汇示波器说明书(Ver1.0)

DST4000 和 DST1000 系列数字存储示波器用户手册

i

目录

5.1 显示区 ........................................................................................ 20 5.2 信息区域..................................................................................... 23 5.3 波形显示..................................................................................... 23

三汇系列产品

DST4000 和 DST1000 系列 数字存储示波器

Version 1.0

杭州三汇科技有限公司 www.

目录

目录

目 录 ...........................................................................................................i 版权申明 .......................................................................................................................................................................v 第 1 章 安全事项......................................................................................... 1

6639S-1-103;6639S-1-102;6639S-1-104;6639S-1-202;6639S-1-203;中文规格书,Datasheet资料

22.23 (.875) DIA.

3.18 (.125)

6639

11.25 .38 (.443 .015)

1.57 (.062)

Байду номын сангаас

22.23 (.875) DIA.

.51 (.020) REF

19.81 (.780) DIA.

12.70 .79 (.500 .031)

10.317+.000/-.051 (.4062+.000/-.002)

DIA.

6.342+.000/-.008

(.2497+.0000/-.0003) DIA. SHAFT .25

45 5 (.010) CHAMFER 1.19 1.60

SLOT (.047) X (.063)

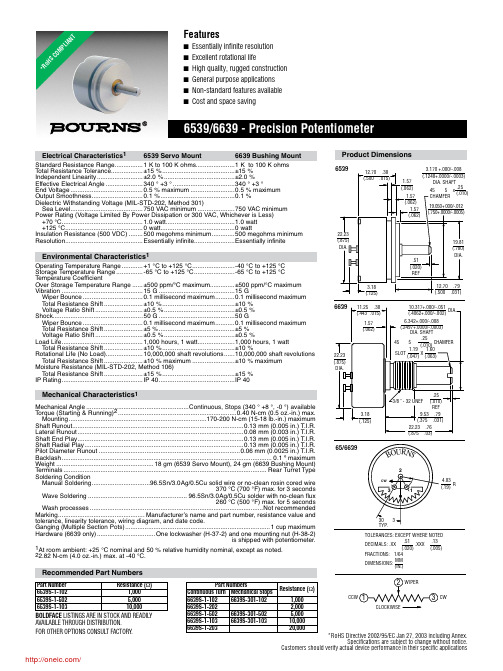

Mechanical Characteristics1

Mechanical Angle ..........................................................Continuous, Stops (340 ° +8 °, -0 °) available Torque (Starting & Running)2 ...................................................................0.40 N-cm (0.5 oz.-in.) max.

Sea Level......................................... 750 VAC minimum .....................750 VAC minimum Power Rating (Voltage Limited By Power Dissipation or 300 VAC, Whichever is Less)

德州仪器,LM3S9B90-I系列, 规格书,Datasheet 资料

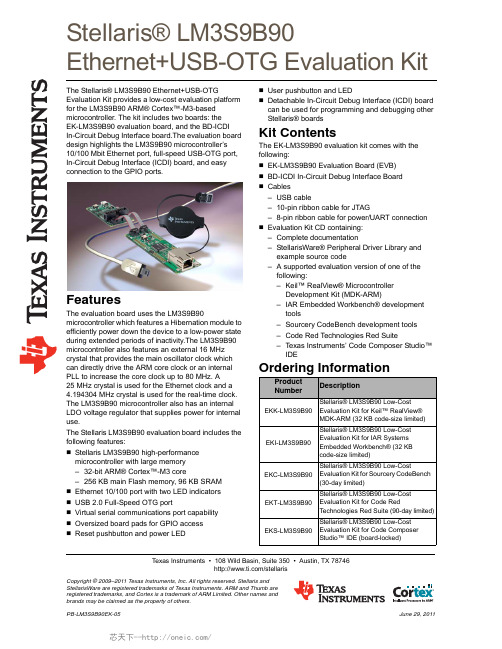

Texas Instruments •108 Wild Basin, Suite 350•Austin, TX 78746/stellarisCopyright © 2009–2011 Texas Instruments, Inc. All rights reserved. Stellaris andStellarisWare are registered trademarks of Texas Instruments. ARM and Thumb areregistered trademarks, and Cortex is a trademark of ARM Limited. Other names andbrands may be claimed as the property of others.PB-LM3S9B90EK-05June 29, 2011The Stellaris® LM3S9B90 Ethernet+USB-OTG Evaluation Kit provides a low-cost evaluation platform for the LM3S9B90 ARM® Cortex™-M3-based microcontroller. The kit includes two boards: the EK-LM3S9B90 evaluation board, and the BD-ICDI In-Circuit Debug Interface board.The evaluation board design highlights the LM3S9B90 microcontroller’s10/100 Mbit Ethernet port, full-speed USB-OTG port, In-Circuit Debug Interface (ICDI) board, and easy connection to the GPIO ports.Features The evaluation board uses the LM3S9B90 microcontroller which features a Hibernation module toefficiently power down the device to a low-power state during extended periods of inactivity.The LM3S9B90 microcontroller also features an external 16MHz crystal that provides the main oscillator clock which can directly drive the ARM core clock or an internalPLL to increase the core clock up to 80MHz. A 25MHz crystal is used for the Ethernet clock and a 4.194304MHz crystal is used for the real-time clock. The LM3S9B90 microcontroller also has an internal LDO voltage regulator that supplies power for internal use.The Stellaris LM3S9B90 evaluation board includes the following features: Stellaris LM3S9B90 high-performance microcontroller with large memory –32-bit ARM® Cortex™-M3 core –256KB main Flash memory, 96KB SRAM Ethernet 10/100 port with two LED indicators USB 2.0 Full-Speed OTG port Virtual serial communications port capability Oversized board pads for GPIO access Reset pushbutton and power LED User pushbutton and LEDDetachable In-Circuit Debug Interface (ICDI) board can be used for programming and debugging other Stellaris® boardsKit ContentsThe EK-LM3S9B90 evaluation kit comes with the following:EK-LM3S9B90 Evaluation Board (EVB)BD-ICDI In-Circuit Debug Interface BoardCables–USB cable–10-pin ribbon cable for JTAG–8-pin ribbon cable for power/UART connectionEvaluation Kit CD containing:–Complete documentation–StellarisWare® Peripheral Driver Library andexample source code– A supported evaluation version of one of thefollowing:–Keil™ RealView® MicrocontrollerDevelopment Kit (MDK-ARM)–IAR Embedded Workbench® developmenttools–Sourcery CodeBench development tools –Code Red Technologies Red Suite –Texas Instruments’ Code Composer Studio™ IDEOrdering InformationProductNumber Description EKK-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Keil™ RealView® MDK-ARM (32 KB code-size limited)EKI-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for IAR Systems Embedded Workbench® (32 KB code-size limited)EKC-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Sourcery CodeBench(30-day limited)EKT-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Code Red Technologies Red Suite (90-day limited)EKS-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Code ComposerStudio™ IDE (board-locked)Stellaris®LM3S9B90Ethernet+USB-OTG Evaluation Kit 芯天下--/IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated芯天下--/。

ISL9V3040D3ST;ISL9V3040S3ST;ISL9V3040D3S;ISL9V3040S3S;中文规格书,Datasheet资料

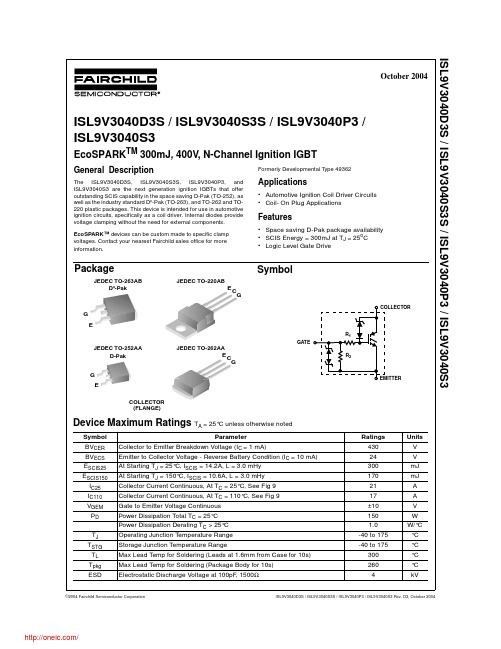

BVCES

Collector to Emitter Breakdown Voltage

390

420

450

V

BVECS BVGES ICER

Emitter to Collector Breakdown Voltage Gate to Emitter Breakdown Voltage Collector to Emitter Leakage Current

Package Marking and Ordering Information

Device Marking V3040D V3040S V3040P V3040S V3040D V3040S Device ISL9V3040D3ST ISL9V3040S3ST ISL9V3040P3 ISL9V3040S3 ISL9V3040D3S ISL9V3040S3S Package TO-252AA TO-263AB TO-220AA TO-262AA TO-252AA TO-263AB Reel Size 330mm 330mm Tube Tube Tube Tube Tape Width 16mm 24mm N/A N/A N/A N/A Quantity 2500 800 50 50 75 50

Applications

• Automotive Ignition Coil Driver Circuits • Coil- On Plug Applications

Features

• Space saving D-Pak package availability • SCIS Energy = 300mJ at TJ = 25oC • Logic Level Gate Drive

Package

LM3S8962 开发板 说明书

LM3S8962开发板用户手册目录1.概述 (4)2.电路及接口说明 (4)2.1. 电源模块 (4)2.2. 网络通信模块 (5)2.3. CAN通信模块 (5)2.4. RS485通信模块 (6)2.5. RS232通信模块 (8)2.6. SPI设备 (9)2.7. IIC设备 (10)2.8. LED驱动电路 (10)2.9. 按键检测电路 (11)2.10. AD测试电路 (11)2.11. 中文液晶接口 (12)2.12. 扩展接口 (12)3.软件使用说明 (13)3.1. K EIL MDK-ARM (13)3.1.1.搭建编译环境 (13)3.1.2.使用ULINK2仿真器的环境配置 (13)3.2. IAR编译环境 (16)3.2.1.搭建编译环境 (16)3.2.2.配置编译环境 (17)4.应用程序说明 (17)4.1. CODE\EK-LM3S8962目录下的程序说明 (17)4.1.1.EK-LM3S8962\RL\TCPnet\Http_demo (17)4.1.2.EK-LM3S8962\RL\TCPnet\ Http_upload (24)4.1.3.EK-LM3S8962\RL\TCPnet\ Telnet_demo (28)4.1.4.EK-LM3S8962\RL\TCPnet\ DNS_demo (29)4.1.5.EK-LM3S8962\RL\ FlashFS\SD_File (30)4.1.6.EK-LM3S8962\RL\ FlashFS\ CAN\ (31)4.2. CODE\S TELLARIS W ARE目录下的程序说明 (32)4.2.1.\StellarisWare\boards\ek-lm3s8962\uart_echo (32)4.2.2.\ StellarisWare\boards\ek-lm3s8962\blinky (33)4.2.3.\ StellarisWare\boards\ek-lm3s8962\timers (33)4.2.4.\ StellarisWare\boards\ek-lm3s8962\enet_uip (34)4.2.5.\ StellarisWare\boards\ek-lm3s8962\enet_ptpd (35)5.原理图 (36)6.联系方式 (36)1.概述文档适合购买LM3S8xxx系列开发板的用户使用,希望通过文档的描述可以使用户更快的进入产品的开发阶段。

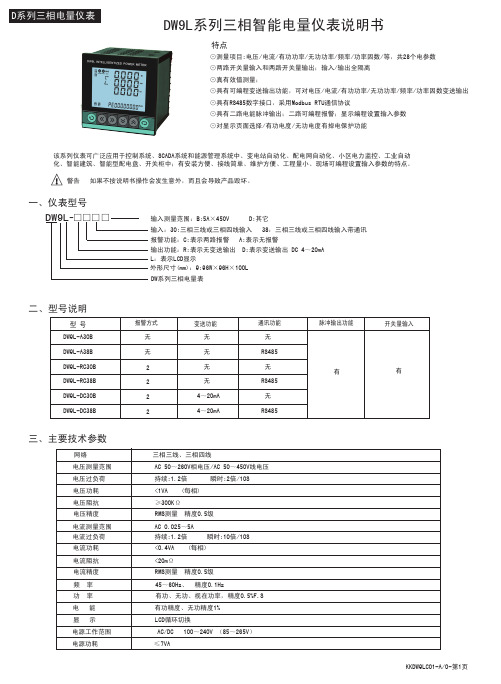

DW9L系列三相智能电量仪表说明书

菜单结构及功能描述

序号

第1级

1 系统设置SET

第2级 清除电能 功能屏蔽密码

第3级 密码数据 屏蔽密码

开关量设置AL

第2路报警方式

5 模拟输出

第2路报警动作值 第2路报警回差值 第2路报警值单位

变送模式选择 变送上限 变送下限 变送单位

第3层

描述 选择测量信号的输入网络

设置电压信号变比=1次侧电压/2次侧电压 设置电流信号变比=1次侧电流/2次侧电流

仪表地址范围

波特率4.8表示4800,9.6表示9600

线电压Ubc

线电压Uca

字长

2 2 2 2 2 2 2 2 2 2 2 2 2 2

取值范围 -1999~9999 -1999~9999 -1999~9999 -1999~9999

1~9999 1~9999 -1999~9999 -1999~9999 0~9999 0~9999 0~9999 0~9999 0~9999 0~9999

KKDW9LC01-A/0-第4页

连续多个变量时=变量个数*每个变量的数据字长

1 表地址 0x01

2 功能号 0x03

3 起始地址

高位

0x00

主机请求(读多寄存器)

4

5

起始地址 低位

数据字长 高位

0x00

0x00

6 数据字长

低位

0x02

7 CRC码 的低位

0xC4

8 CRC码 的高位

SEMIKRON ESD9L系列电路保护扇形电阻说明书

ESD9L, SESD9L Series Transient Voltage SuppressorsESD Protection Diodes with Ultra−Low CapacitanceThe ESD9L Series is designed to protect voltage sensitive components that require ultra−low capacitance from ESD and transient voltage events. Excellent clamping capability, low capacitance, low leakage, and fast response time, make these parts ideal for ESD protection on designs where board space is at a premium. Because of its low capacitance, it is suited for use in high frequency designs such as USB 2.0 high speed and antenna line applications.Specification Features:•Ultra Low Capacitance 0.5 pF •Low Clamping V oltage•Small Body Outline Dimensions:0.039″ x 0.024″(1.00 mm x 0.60 mm)•Low Body Height: 0.016″ (0.4 mm)•Stand−off V oltage: 3.3 V , 5 V •Low Leakage•Response Time is Typically < 1.0 ns •IEC61000−4−2 Level 4 ESD Protection•S and SZ Prefixes for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q101Qualified and PPAP Capable•These Devices are Pb−Free and are RoHS CompliantMechanical Characteristics:CASE: V oid-free, transfer-molded, thermosetting plasticEpoxy Meets UL 94 V−0LEAD FINISH: 100% Matte Sn (Tin)MOUNTING POSITION: AnyQUALIFIED MAX REFLOW TEMPERATURE: 260°CDevice Meets MSL 1 RequirementsMAXIMUM RATINGSRatingSymbolValue Unit IEC 61000−4−2 (ESD)ContactAir±10±15kVTotal Power Dissipation on FR−5 Board (Note 1) @ T A = 25°C P D 150mW Storage Temperature Range T stg −55 to +150°CJunction Temperature Range T J −55 to +150°C Lead Solder Temperature − Maximum(10 Second Duration)TL 260°CStresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.FR−5 = 1.0 x 0.75 x 0.62 in.See Application Note AND8308/D for further description of survivability specs.Device PackageShipping †ORDERING INFORMATIONSOD−923CASE 514ABESD9LxxxST5G SOD−923(Pb−Free)8000/T ape & Reel MARKING DIAGRAMSee specific marking information in the device marking column of the Electrical Characteristics tables starting on page 2 of this data sheet.DEVICE MARKING INFORMATION†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.X = Specific Device Code M = Date Code*Date Code orientation and/or position may vary depending upon manufacturing location.PIN 1.CATHODE2.ANODE12122SESD9LxxxST5G SOD−923(Pb−Free)8000/T ape & Reel SZESD9LxxxST5GSOD−923(Pb−Free)8000/T ape & ReelELECTRICAL CHARACTERISTICS(T A = 25°C unless otherwise noted)Symbol ParameterI PP Maximum Reverse Peak Pulse Current V C Clamping Voltage @ I PP V RWM Working Peak Reverse VoltageI R Maximum Reverse Leakage Current @ VRWM V BR Breakdown Voltage @ I T I T Test Current I F Forward Current V F Forward Voltage @ I F P pk Peak Power DissipationCMax. Capacitance @ V R = 0 and f = 1.0 MHz*See Application Note AND8308/D for detailed explanations of datasheet parameters.ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 1.0 V Max. @ I F = 10 mA for all types)Device*Device Marking V RWM (V)I R (m A)@ VRWM V BR (V) @ I T (Note 2)I T C (pF)V C (V)@ I PP = 1 AV CMax Max Min mA Typ Max Max Per IEC61000−4−2(Note 4)ESD9L3.3ST5G 6** 3.3 1.0 4.8 1.00.50.99.0Figures 1 and 2See Below ESD9L5.0ST5GD5.01.05.41.00.50.99.8Figures 1 and 2See Below*Includes S and SZ-prefix devices where applicable.**Rotated 180°.2.V BR is measured with a pulse test current I T at an ambient temperature of 25°C.3.Surge current waveform per Figure 5.4.For test procedure see Figures 3 and 4 and Application Note AND8307/D.Figure 1. ESD Clamping Voltage Screenshot Positive 8 kV Contact per IEC61000−4−2Figure 2. ESD Clamping Voltage Screenshot Negative 8 kV Contact per IEC61000−4−2IEC 61000−4−2 Spec.Level Test Volt-age (kV)First Peak Current (A)Current at 30 ns (A)Current at 60 ns (A)127.5422415843622.51264830168IEC61000−4−2 WaveformFigure 3. IEC61000−4−2 SpecOscilloscopeThe following is taken from Application NoteAND8308/D − Interpretation of Datasheet Parameters for ESD Devices.ESD Voltage ClampingFor sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000−4−2 waveform. Since the IEC61000−4−2 was written as a pass/fail spec for largersystems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes. For more information on how ON Semiconductor creates these screenshots and how to interpret them please refer to AND8307/D.Figure 5. 8 X 20 ms Pulse Waveform1009080706050403020100t, TIME (m s)% O F P E A K P U L S E C U R R E N TPACKAGE DIMENSIONSSOD−923CASE 514AB ISSUE CNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.DIM MIN NOM MAX MILLIMETERS A 0.340.370.40b 0.150.200.25c 0.070.120.17D 0.750.800.85E 0.550.600.650.95 1.00 1.05L 0.19 REF H E 0.0130.0150.0160.0060.0080.0100.0030.0050.0070.0300.0310.0330.0220.0240.0260.0370.0390.0410.007 REFMIN NOM MAX INCHEScADIMENSIONS: MILLIMETERS*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*See Application Note AND8455/D for more mounting details 2X0.252XOUTLINE2X0.08X YTOP VIEW2XBOTTOM VIEWL2XL20.050.100.150.0020.0040.006ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent PUBLICATION ORDERING INFORMATION。

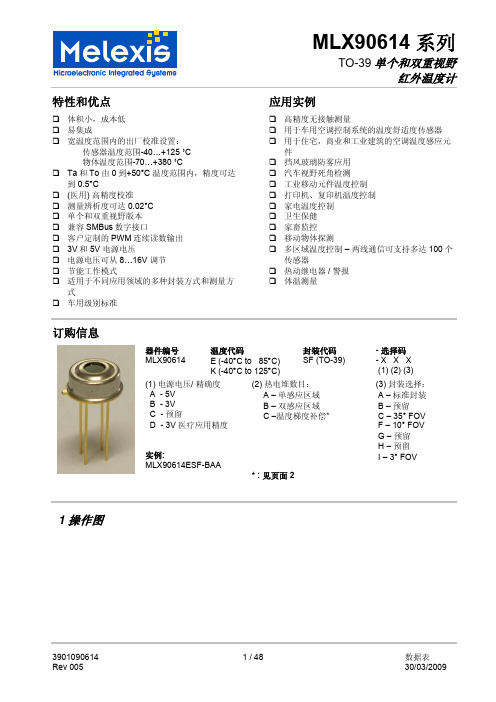

MLX90614红外温度计数据表

(20YX1739-03)扬声器规格书VIT90170-10W8--03

内置音响组件\VIT90170-10W8Ω-03\ROH 版本页数1.0 3 常规电声性能参数:序号项目测试条件单位技术要求1 额定正弦功率分别在1.5 f0和1000Hz,持续1小时; W 82 额定噪声功率粉噪,持续100小时。

W 103 长期最大功率按GB/T9396-1996中19.2项。

W 154 额定阻抗输入<1/4W。

(实测要求阻抗曲线上极小值不小于0.85R)。

Ω8±15%5 谐振频率f0测试电压统一为2V。

Hz 90±186 正弦纯音检听0.5 f0-2kHz扫频,馈以要求的正弦电压,无异常音V 8.97 特性灵敏度级1m,1w。

100Hz-12.5kHz内取平均值dB 78±28 有效频率范围1m,1w,测试频响-14dB Hz 100Hz-12.5k 1m,1w,测试频响-9dB Hz 125Hz-4k9 总谐波失真1W,1m,125Hz-5000Hz内按1/3oct取点。

≤7%10 总品质因素Qt通过阻抗曲线计算11 等效容积Vas按GB/T9396-1996中18.4.2项。

lts12 漏磁场轴向正面,以轭环上平面为起点。

μT/轴向背面,以后盖底面为起点。

mm 45度角,以上夹板外沿为起点。

13 极性扬声器接线板“+”接正向直流电,扬声器纸盆向前推极性标识正确14 绝缘电阻在端子与盆架间施加1分钟的100V 直流电≥1MΩ(打开音箱对扬声器单元进行检验)15 耐电压在扬声器引出端子与盆架和磁路的金属部分间加50Hz,100V交流电1分钟,试验中无打火击穿现象。

(打开音箱对扬声器单元进行检验)16 1-15项仅规定了扬声器常规技术参数要求,其他通用技术条件如外观、机械性能、可焊性、负荷试验、周期检验及包装等要求须符合GB/T 9396-1996和GB/T 9397-1996的要求。

机械性能指标:序号项目判定标准1 滑落冲击试验将扬声器依下图所示滑落1次,试验后扬声器不能有擦圈、破损、异常音,性能不能有改变内置音响组件\VIT90170-10W8Ω-03\ROH 版本页数1.0 5 频响曲线:内置音响组件\VIT90170-10W8Ω-03\ROH 版本页数1.0 6 阻抗曲线:。

A9s接收卡规格书-V1.1.0

集成网络变压器,简化设计,提高电磁兼容性,有助于用户产品顺利通过 EMC 认

子 证。 电 实用的软件设计:

支持 LVDS 传输(专用固件程序支持)。

瓦 支持智能模组(专用固件程序支持)。

支持快速修缝。

诺 支持 3D 功能。 安 支持模组自动校正。

有 3.3 提升硬件可靠性 ........................................................................................................................................... 5 技 3.4 提升软件可靠性 ........................................................................................................................................... 5

3 功能特性

3 功能特性

司

3.1 提升显示效果

公

特性 支持逐点亮色度校正

说明

限 配合 NovaLCT 和 NovaCLB,对每个灯点的亮度和 有 色度进行校正。

支持画面 90°倍数旋转 (不支持旋转后进行校正)

技 在 NovaLCT 上可以设置显示屏画面以 90°的倍数

B 术语 ...............................................................................................................................19

FAIRCHILD FQPF9N30 数据手册

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!F Q P F 9N 30FQPF9N30300V N-Channel MOSFETGeneral DescriptionThese N-Channel enhancement mode power field effect transistors are produced using Fairchild’s proprietary,planar stripe, DMOS technology.This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode. These devices are well suited for high efficiency switching DC/DC converters,switch mode power supply.TO-220FG SDFQPF9N30(Note 4)(Note 4, 5)(Note 4, 5) (Note 4)Electrical Characteristics T C= 25°C unless otherwise notedNotes:1. Repetitive Rating : Pulse width limited by maximum junction temperature2. L = 19.4mH, I AS = 6.0A, V DD = 50V, R G = 25 Ω, Starting T J = 25°C3. I SD ≤9.0A, di/dt ≤ 200A/µs, V DD ≤ BV DSS, Starting T J = 25°C4. Pulse Test : Pulse width ≤300µs, Duty cycle ≤2%5. Essentially independent of operating temperatureSymbol Parameter Test Conditions Min Typ Max UnitsOff CharacteristicsBV DSS Drain-Source Breakdown Voltage V GS = 0 V, I D = 250 µA300----V ∆BV DSS / ∆T J Breakdown Voltage Temperature CoefficientI D = 250 µA, Referenced to 25°C --0.28--V/°C I DSS Zero Gate Voltage Drain Current V DS = 300 V, V GS = 0 V ----1µA V DS = 240 V, T C = 125°C ----10µA I GSSF Gate-Body Leakage Current, Forward V GS = 30 V, V DS = 0 V ----100nA I GSSRGate-Body Leakage Current, ReverseV GS = -30 V, V DS = 0 V-----100nAOn CharacteristicsV GS(th)Gate Threshold Voltage V DS = V GS , I D = 250 µA 3.0-- 5.0V R DS(on)Static Drain-Source On-ResistanceV GS = 10 V, I D = 3.0 A --0.350.45Ωg FSForward TransconductanceV DS = 50 V, I D = 3.0 A--4.2--SDynamic CharacteristicsC iss Input Capacitance V DS = 25 V, V GS = 0 V, f = 1.0 MHz--570740pF C oss Output Capacitance--120155pF C rssReverse Transfer Capacitance--1620pFSwitching Characteristicst d(on)Turn-On Delay Time V DD = 150 V, I D = 9.0 A,R G = 25 Ω--1640ns t r Turn-On Rise Time --120250ns t d(off)Turn-Off Delay Time --2765ns t f Turn-Off Fall Time --48110ns Q g Total Gate Charge V DS = 240 V, I D = 9.0 A,V GS = 10 V--1722nC Q gs Gate-Source Charge -- 3.9--nC Q gdGate-Drain Charge--9.2--nCDrain-Source Diode Characteristics and Maximum RatingsI S Maximum Continuous Drain-Source Diode Forward Current ---- 6.0A I SM Maximum Pulsed Drain-Source Diode Forward Current----24A V SD Drain-Source Diode Forward Voltage V GS = 0 V, I S = 6.0 A ---- 1.5V t rr Reverse Recovery Time V GS = 0 V, I S = 9.0 A,dI F / dt = 100 A/µs--170--ns Q rrReverse Recovery Charge-- 1.4--µCF Q P F 9N 30FQPF9N30F Q P F 9N 30FQPF9N30F Q P F 9N 30TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationPreliminary No Identification Needed Obsolete This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.This datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Formative or In DesignFirst ProductionFull ProductionNot In ProductionDISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.QFET™QS™QT Optoelectronics™Quiet Series™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TinyLogic™UHC™FASTr™GlobalOptoisolator™GTO™HiSeC™ISOPLANAR™MICROWIRE™OPTOLOGIC™OPTOPLANAR™POP™PowerTrench ®Rev. F1ACEx™Bottomless™CoolFET™CROSSVOLT™DOME™E 2CMOS TM EnSigna TM FACT™FACT Quiet Series™FAST ®VCX™。

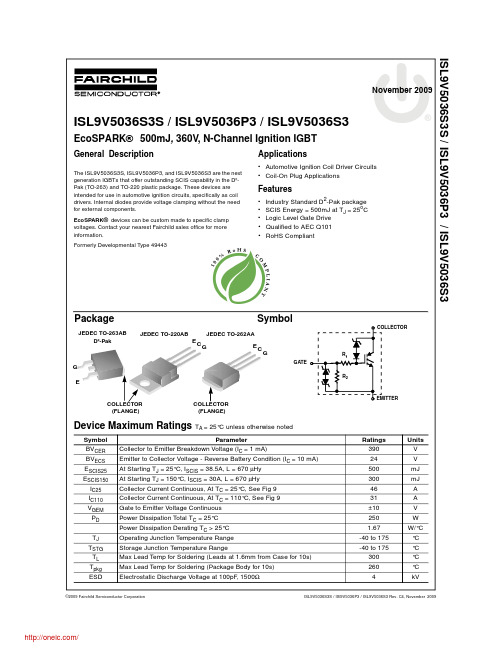

ISL9V5036P3;ISL9V5036S3;ISL9V5036S3ST;ISL9V5036P3_F085;中文规格书,Datasheet资料

ISL9V5036S3S / ISL9V5036P3 / ISL9V5036S3= 25°C unless otherwise noted ParameterCollector to Emitter Breakdown Voltage (I C = 1 mA)Emitter to Collector Voltage - Reverse Battery Condition (I SymbolE GCCOLLECTOR (FLANGE)JEDEC TO-262AAISL9V5036S3S / ISL9V5036P3 / ISL9V5036S3Package Marking and Ordering InformationElectrical Characteristics T A = 25°C unless otherwise notedOff State CharacteristicsOn State CharacteristicsDynamic CharacteristicsSwitching CharacteristicsThermal CharacteristicsDevice MarkingDevicePackage Reel Size Tape Width Quantity V5036SISL9V5036S3ST TO-263AB 330mm 24mm 800V5036P ISL9V5036P3TO-220AA Tube N/A 50V5036S ISL9V5036S3TO-262AA Tube N/A 50V5036SISL9V5036S3STO-263ABTubeN/A50SymbolParameterTest ConditionsMinTypMaxUnitsBV CERCollector to Emitter Breakdown VoltageI C = 2mA, V GE = 0, R G = 1K Ω, See Fig. 15T J = -40 to 150°C 330360390VBV CESCollector to Emitter Breakdown Voltage I C = 10mA, V GE = 0, R G = 0, See Fig. 15T J = -40 to 150°C 360390420VBV ECS Emitter to Collector Breakdown Voltage I C = -75mA, V GE = 0V ,T C = 25°C 30--V BV GES Gate to Emitter Breakdown Voltage I GES = ± 2mA ±12±14-V I CERCollector to Emitter Leakage CurrentV CER = 250V , R G = 1K Ω, See Fig. 11T C = 25°C --25µA T C = 150°C--1mA I ECS Emitter to Collector Leakage Current V EC = 24V , See Fig. 11T C = 25°C --1mA T C = 150°C--40mA R 1Series Gate Resistance -75-ΩR 2Gate to Emitter Resistance10K-30KΩV CE(SAT)Collector to Emitter Saturation Voltage I C = 10A, V GE = 4.0V T C = 25°C, See Fig. 4- 1.17 1.60V V CE(SAT)Collector to Emitter Saturation VoltageI C = 15A, V GE = 4.5VT C = 150°C- 1.501.80VQ G(ON)Gate ChargeI C = 10A, V CE = 12V , V GE = 5V , See Fig. 14-32-nC V GE(TH)Gate to Emitter Threshold VoltageI C = 1.0mA,V CE = V GE,See Fig. 10T C = 25°C 1.3- 2.2V T C = 150°C0.75- 1.8V V GEPGate to Emitter Plateau VoltageI C = 10A, V CE = 12V- 3.0-Vt d(ON)R Current T urn-On Delay Time-Resistive V CE = 14V , R L = 1Ω, V GE = 5V , R G = 1K ΩT J = 25°C, See Fig. 12-0.74µs t rR Current Rise Time-Resistive- 2.17µs t d(OFF)L Current T urn-Off Delay Time-Inductive V CE = 300V, L = 2mH , V GE = 5V , R G = 1K ΩT J = 25°C, See Fig. 12-10.815µs t fL Current Fall Time-Inductive - 2.815µs SCISSelf Clamped Inductive SwitchingT J = 25°C, L = 670 µH, R G = 1K Ω, V GE = 5V , See Fig. 1 & 2--500mJR θJCThermal Resistance Junction-CaseTO-263, TO-220, TO-262--0.6°C/WFigure 3. Collector to Emitter On-State Voltage vsJunction TemperatureFigure 4.Collector to Emitter On-State Voltage vsJunction TemperatureFigure 5. Collector Current vs Collector to EmitterOn-State Voltage Figure 6. Collector Current vs Collector to EmitterOn-State Voltage1.000.950.9025-2517512575-50050100150T J , JUNCTION TEMPERATURE (°C)V C E , C O L L E C T O R T O E M I T GE V GE = 5.0VV GE = 8.0VV GE = 4.5V0.8525-2517512575-500501001501.151.101.05V C E , C O L L E C T O R T O E M I T 1.00T J , JUNCTION TEMPERATURE (°C)V GE = 4.5VV GE = 5.0VV GE = 8.0VI C E , C O L L E C T O R T O E M I T T E R C U R R E N T (A )V CE , COLLECTOR TO EMITTER VOLTAGE (V)20402.01.03.04.05030100V GE = 4.0V V GE = 3.7VV GE = 4.5V V GE = 5.0V V GE = 8.0V T J = - 40°CI C E , C O L L E C T O R T O E M I T T E R C U R R E N T (A )V CE , COLLECTOR TO EMITTER VOLTAGE (V)4050302.01.03.04.02010V GE = 4.0VV GE = 3.7VV GE = 4.5V V GE = 5.0VV GE = 8.0V T J = 25°CFigure 15. Breakdown Voltage vs Series Gate ResistanceFigure 16. IGBT Normalized Transient Thermal Impedance, Junction to CaseB VC E R , B R E A KD O W N R G , SERIES GATE RESISTANCE (k Ω)35234810200010003000344100350346T J = 25°C342340Z t h J C , N O R M A L I Z E D T H E R M A L R E S P O N S ET 1, RECTANGULAR PULSE DURATION (s)10010-210-110-210-310-410-510-110-6t 1t 2P DDUTY FACTOR, D = t 1 / t 2PEAK T J = (P D X Z θJC X R θJC ) + T C0.50.20.10.050.020.01SINGLE PULSE10-310-4rtherm.rtherm1 th 6 = 1.0e-2rtherm.rtherm2 6 5 = 1.4e-1rtherm.rtherm3 5 4 = 1.0e-1rtherm.rtherm4 4 3 = 9.0e-2rtherm.rtherm5 3 2 = 9.4e-2rtherm.rtherm6 2 tl = 1.9e-2}RTHERM6RTHERM5CTHERM6CTHERM5tl 23CASEThe following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is notAuto-SPM™Build it Now™CorePLUS™CorePOWER™CROSSVOLT™CTL™Current Transfer Logic™ EcoSPARK®EfficientMax™ EZSWITCH™*™*DEUXPEED™®Fairchild®Fairchild Semiconductor®FACT Quiet Series™ FACT®FAST®FastvCore™FETBench™FPS™F-PFS™FRFET®Global Power Resource SMGreen FPS™Green FPS™ e-Series™G max™GTO™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MillerDrive™MotionMax™Motion-SPM™OPTOLOGIC®OPTOPLANAR®®PDP SPM™PowerTrench®PowerXS™Programmable Active Droop™QFET®QS™Quiet Series™RapidConfigure™™Saving our world, 1mW/W/kW at a time™SignalWise™SmartMax™SMART START™SPM®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SupreMOS™SyncFET™Sync-Lock™®*The Power Franchise®TinyBoost™TinyBuck™TinyCalc™TinyLogic®TINYOPTO™TinyPower™TinyPWM™TinyWire™TriFault Detect™TRUECURRENT™*μSerDes™UHC®Ultra FRFET™UniFET™VCX™VisualMax™XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) areintended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.分销商库存信息:FAIRCHILDISL9V5036P3ISL9V5036S3ISL9V5036S3ST ISL9V5036P3_F085。

DK-LM3S9B96-FPGA;中文规格书,Datasheet资料

K-LM3S9B96-FPGA) provides an easy way to ral Interface (EPI) using the highly elopment platform.RequirementsM3S9B96 development platformoftware CD oaded an SD Card in the DK-LM3S9B96’s SD card slot. This is only necessary opment board via the eral Interface connector and the LCD connection header. Before installing the GA LCD A expansion jumper POT/PB4 at be removed. See Figure 1. DK-LM3S9B96Development Board.With the jumpers removed, you must then remove any expansion board that is currently fitted to the expansion connector. Boards that may be installed in this location are the SDRAM daughter board, the EPI Signal Breakout board or the Flash/SRAM/LCD daughter board. Figure 1. DK-LM3S9B96 Development Board Stellaris ® FPGA Expansion BoardThe Stellaris ® FPGA expansion board (D evaluate the capabilities of the Stellaris External Periphe integrated DK-LM3S9B96 dev FPGA Expansion BoardYou have a DK-L You have the Stellaris LM3S9B96 Development Kit Documentation and S RecommendationsYou have l for the “Save Image” function.A JTAG Programming cable that supports Xilinx® Spartan3 devices.Board Set-UpThe FPGA expansion board interfaces to the h DK-LM3S9B96 devel Extended Perip the bottom left of the board must also FPGA expansion board, you must remove the jumpers from JP16-31 in the QV section of the development board. If you do not remove the jumpers, the FPG board cannot be installed on the DK-LM3S9B96 development board. TheOnce the jumpers and expansion boards have been removed, fit the FPGA expansion board onto the DK-LM3S9B96 development board. There is a male EPI expansion connector on the bottom side of the FPGA expansion board that connects to the female EPI expansion5V Powerough the PCB. included tely above the JTAG port on the daughter upper pins immediately below and to the right of the “EXT +5V” ith the FPGA and is elopment kit. The ion PROM comes pre-loaded with the binary image required by the videocap application, so no FPGA-specific tools are required.find the videocap supported he LM Flash cation, it automatically connects to the FPGA and begins displaying the camera image on the LCD.d the videocap application in version 5879 or later of the StellarisWareellaris web site at /mcu/docs/mcuorphan.tsp?contentId=87903gle d view and full screen view.Save Image to DiskIf an SD Card is installed, click the “Freeze” and then “Save” buttons to save the camera image as a .bmp file.Image Quality ControlsThe Controls panel allows for real-time adjustment of the brightness, saturation, and contrast of the image.connector of the DK-LM3S9B96 development board (J2). Since the FPGA expansion board also interfaces to the LCD, there are holes to fit the LCD header pins thrOnce the expansion board is connected to the EPI and LCD interfaces, use the jumper wire to provide 5 V power to J5 (immedia board) from any of the three connector on the development board (as shown in Figure 1).VideoCap ApplicationThe “videocap” example application illustrates communication w provided in the StellarisWare® software release for the DK-LM3S9B96 dev FPGA expansion board’s configurat If you installed StellarisWare in the default installation directory, you can application source in the following location:C:\StellarisWare\boards\dk-lm39b96\Lower level subdirectories contain binaries for the application built with each toolchain. These binaries can be downloaded to the dk-lm3s9b96 board using t Programmer tool. When you run the videocap appli You can fin distribution. Download the latest version of StellarisWare from the /stThe application has the following functions:Pan / ZoomTouch and Drag on the touchscreen to pan the image. Click the “Scale” button to tog between 2x scaleCopyright © 2010 Texas Instruments, Inc. All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments. ARM and Thumb are registered trademarks, and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property of others.Texas Instruments108 Wild Basin Rd., Suite 350Austin, TX 78746/stellarisRev. 1.0 4/19/2010s are included on the Stellaris LM3S9B96 Development Kit Documentation and Software CD and are also available for download at theReferencesThe following reference /stellaris web site:Stellaris LM3S9B96 Development Kit User's Manual (publication num DK-LM3S9B96)bertion number K-LM3S9B96) Stellaris ® Peripheral Driver Library User’s Guide (publication number SW-DRL-UG) Stellaris LM3S9B96 Microcontroller Data Sheet (publication number DS-LM3S9B96)DK-LM3S9B96 Firmware Development Package User’s Guide (publica SW-DK-LM3S9B96-UG)DK-LM3S9B96 Firmware Development Package (order number SW-DIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated分销商库存信息: TIDK-LM3S9B96-FPGA。

LM3S1138,LM3S1751,LM3S5632, 规格书,Datasheet 资料

Why choose the ARM architecture?

• With entry-level pricing at U.S. $1.00 for an ARM technology-based MCU, the Stellaris product line allows for standardization that eliminates future architectural upgrades or software tools changes. • With an ARM-based embedded market that is currently shipping at a rate of greater than 5 billion processors per year, the ARM ecosystem of third-party tools and solutions providers is the largest in the world. • With the ARM Cortex architecture, designers have access to an instructionset-compatible family that ranges from U.S. $1 to more than 1 GHz.

|2

Copyright © 2011 Texas Instruments Incorporated

芯天下--/

Stellaris Family of Microcontrollers

Stellaris is the industry’s leading family of robust, real-time microcontrollers (MCUs) based on the revolutionary ARM® Cortex™-M series MCU technology. The award-winning Stellaris 32-bit MCUs combine sophisticated, flexible, mixed-signal system-on-chip integration with unparalleled real-time multitasking capabilities. Complex applications previously impossible with legacy MCUs can now be accommodated with ease by powerful, cost-effective, and simpleto-program Stellaris MCUs. The Stellaris family is ideal for cost-conscious applications requiring significant control processing and connectivity capabilities, including smart grid, motion control, human machine interface, HVAC and building controls, power and energy monitoring and conversion, network appliances and switches, factory automation, electronic point-of-sale machines, test and measurement equipment, LED signage/control, and gaming equipment. Welcome to the future of microcontrollers!

诺旺电子Philips shavers系列9000型号说明书

Philips Shaver series 9000 Wet and dry electric shaverV-Track Precision Blades 50 min cordless use/1h chargeSmartClick beard styler SmartClean System PlusS9511/23Perfection in every passCuts up to 20% more hair* in a single passThe Shaver 9000 is our most advanced shaver yet. The unique contour detect technology offers exceptionally coverage over every contour of your face, and the V-Track system guides hairs into the best cutting position for the closest result.Easy to use•Monitor shaver functions at a glance•50 minutes cordless shaving after a one-hour charge•With 2 year guaranteeA comfortable shave•Lifts hairs to cut comfortably close•Personalize your shave by choosing between three settings•Get a comfortable dry or refreshing wet shave with AquatecDesigned for perfection•Blades perfectly guide hairs into position for a close shave•Heads flex in 8 different directions for a superb resultGet the most of your shaver•Keep your shaver like new with SmartClean•Click-on beard styler with 5 length settingsHighlightsV-Track precision blade systemGet the prefect close shave. The V-Track Precision Blades gently positions each hair in the best cutting position, even the flat laying and different length of hairs. Cuts 30% closer in less strokes leaving your skin in great condition.8-direction ContourDetectHeadsFollow every contour of your face and neck with 8-directional ContourDetect heads. You'll catch 20% more hairs with every pass. Resulting in an extremely close, smooth shave.Super Lift & Cut ActionShave closer with the dual-blade Super Lift & Cut action. The first blade raises each hair while the second blade comfortably cuts below skin level, for really smooth results.Personal comfort settings Choose between 3 modes to customize your shave: Sensitive – for a gentle, yet thorough shave. Normal – for a thorough, everyday shave. Fast – for a quick shave that saves you time.Aquatec Wet & DryChoose how you prefer to shave. With the Aquatec Wet & Dry seal, you can opt for a quick yet comfortable dry shave. Or you can shave wet – with gel or foam – even under the shower.SmartClean System PLUSAt the touch of a button SmartClean PLUS cleans, lubricates, dries and charges your shaver, so it’ll perform at its best every day.SmartClick beard stylerChange your look with the SmartClick Beard Styler attachment. Choose from 5 length settings to create anything from a perfect stubble look to a short, neatly trimmed beard. Rounded tips and combs are designed to prevent skin irritation.5 level LED displayYou can easily see how much power is left with the 5-level LED display. Your Philips close shaver will not only tell you when it's time to charge, it has indicators for locking, cleaning and replacing the head.50 minutes of cordless shavingOur advanced charging system gives you two convenient options: charge for one hour and you’ll get 50 minutes of running time, or do a quick charge for one full shave. All 9000 Series Shavers contain a powerful energy-efficient, long-lasting lithium-ion battery. They aredesigned to operate only in cordless mode, to ensure you’ll always be safe when shaving with water, even under the shower.Issue date 2022-07-24 Version: 3.0.1© 2022 Koninklijke Philips N.V.All Rights reserved.Specifications are subject to change without notice. Trademarks are the property of Koninklijke Philips N.V. or their respective owners.SpecificationsShaving Performance•Contour following: 8-direction ContourDetectHeads•SkinComfort: AquaTec Wet & Dry•Shaving system: V-Track Precision Blade System, Super Lift & Cut Action•Personal Comfort Settings: Sensitive-Normal-Fast settingsEase of use•Cleaning: Fully washable•Display: 5 level battery indicator, Cleaning indicator, Battery low indicator, Replace shaving heads indicator, Travel lock indicatorDesign•Handle: Ergonomic grip & handling•Color: Dark Caramel Accessories•SmartClick: Beard styler•Pouch: Travel pouch•SmartClean PLUS: Cleans, Dries, Charges,Lubricates, Cleaning cartridge (included)Power•Battery Type: Lithium-ion•Automatic voltage: 100-240 V•Run time: 50 min / 17 shaves•Charging: Rechargeable, Charge 1 hour for 50 minuse, Quick charge for 1 shave•Stand-by power: 0.1 W•Maximum power consumption: 9 WService•2-year guarantee•Replacement head: Replace every 2 yrs with SH90*Cuts up to 20% more hair - versus SensoTouch。

三频火焰探测器说明书

警示: 除了 DIP 开关,不要触摸内部元件(静电敏感装置(ESD)参考附件 A)

继电器 Phoenix 使用两组 DIP 开关 DIP 开关 #1 用于定义敏感性和延迟时间 DIP 开关#2 用于定义继电器设置;它只能用于继电器模式,并且只有位置 2 是可以用的。 见表格 7 和 8. 模拟 模拟(无继电器)Phoenix 只使用 DIP 开关#1 来定义敏感性和延迟时间的设置。DIP 开 关使用说明见表 7.

导线须使用外壳和保护层来使得每根导线周围都有密封。这能防止空气,气体和水从外壳的 里面泄漏到外罩的外面。

建议使用防爆排管和通透导管。温度和大气压的变化会导致‘渗透’使得水蒸汽进入导管。 连接头不足以防止通透渗漏。

连接 Phoenix 可以是模拟,模拟/数显,继电器或数显模式。各种模式的特定链接参考以下表格。 有需要的话,终端接线盒也可以由 Net Safety 提供。

功能 接地 Vdc (+) Com (-) 绝缘电源(+) 4-20mA 信号输出

功能 接地(GND) Vdc (+) Com (-) 报警继电器 报警继电器 故障继电器 故障继电器

警示: 如果在 Net Safety 多功能接线盒中制作了终端口,特殊终端设计请参考 MAN-0081

注意: 当和模拟/继电器接线盒(JB-IR3SAR-A/S)一起使用模拟装置(IR3S-A), 能使用 外置磁铁来重新设置和接线盒连接在一起的报警。 使用说明书见 MAN-0081。

零延迟时间只能用在须即时作出反应,控制地非常好,并且允许产生少量误报警的应用中。

延迟时间设为 3,5,10 秒 延迟时间设置是指探测器在发出火焰报警之前,火焰信号必须持续出现的时间长度。 当火 焰持续至设定的延迟时间,报警会在 5 秒之内发出。这一延迟到 5 秒的设置是用户不能自己 调节的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。