胡晓光数字电子技术基础课后答案

【数字电子技术基础】课后习题集与参考答案解析

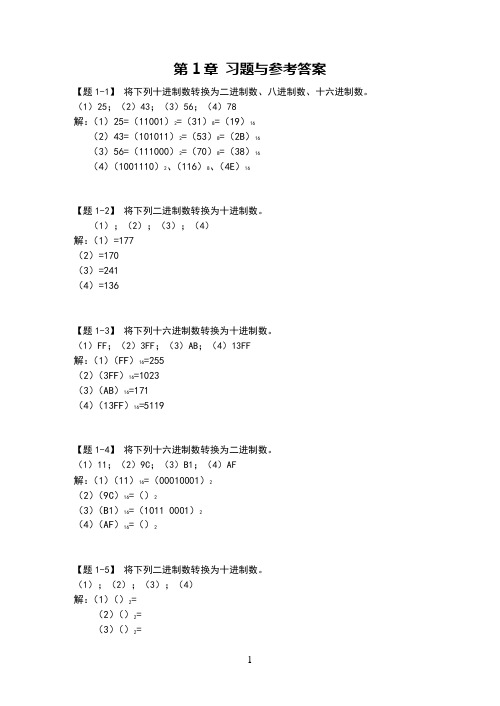

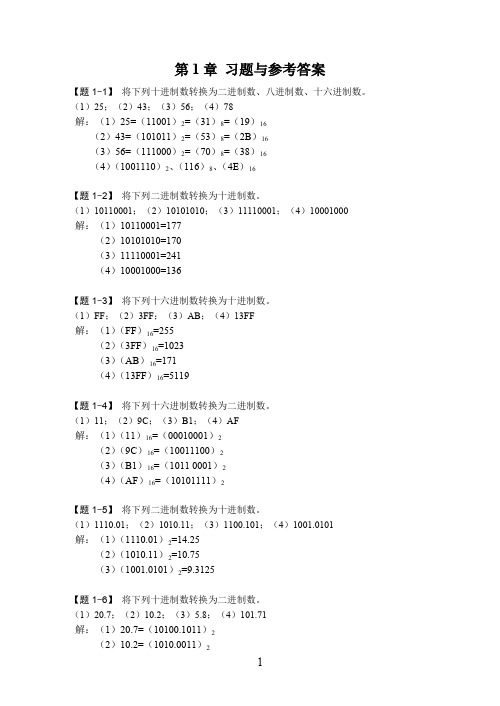

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

《数字电子技术基础》课后习题及参考答案

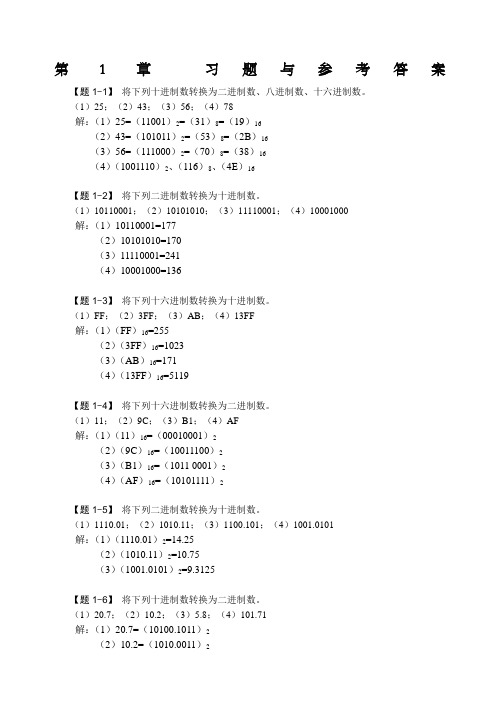

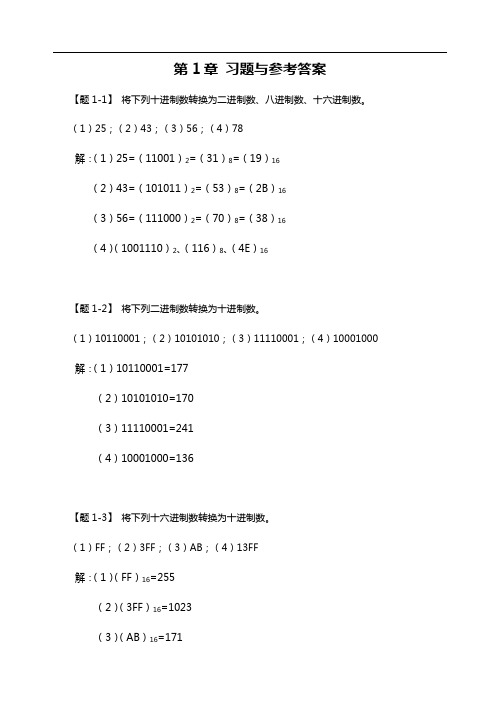

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

《数字电子技术基础》课后习题及参考答案

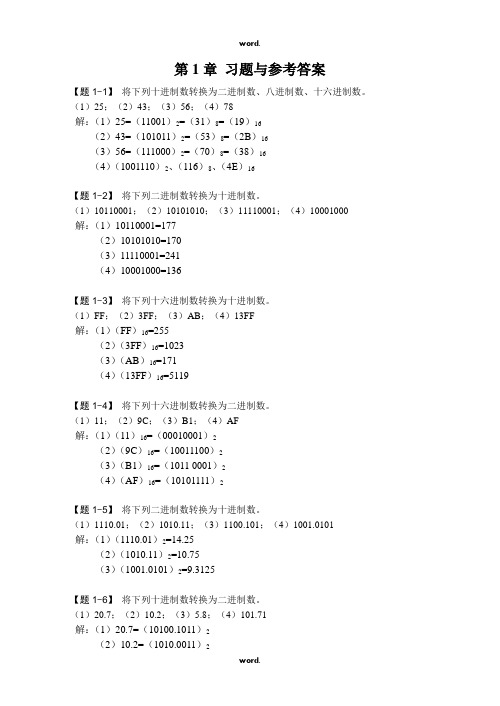

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

数字电子技术基础课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后答案

《数字电子技术基础教程》习题与参考答案第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后答案全解

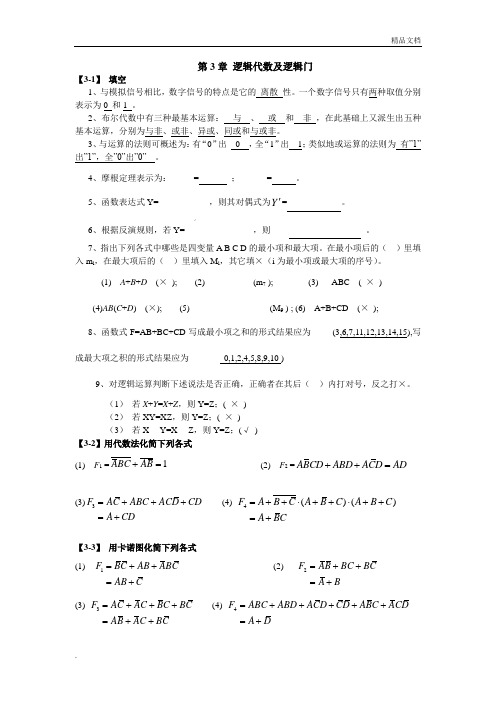

第3章 逻辑代数及逻辑门【3-1】 填空1、与模拟信号相比,数字信号的特点是它的 离散 性。

一个数字信号只有两种取值分别表示为0 和1 。

2、布尔代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算,分别为与非、或非、异或、同或和与或非。

3、与运算的法则可概述为:有“0”出 0 ,全“1”出 1;类似地或运算的法则为 有”1”出”1”,全”0”出”0” 。

4、摩根定理表示为:A B ⋅=A B + ;A B +=A B ⋅。

5、函数表达式Y=AB C D ++,则其对偶式为Y '=()A B C D +⋅。

6、根据反演规则,若Y=AB C D C +++,则Y =()AB C D C ++⋅ 。

7、指出下列各式中哪些是四变量A B C D 的最小项和最大项。

在最小项后的( )里填入m i ,在最大项后的( )里填入M i ,其它填×(i 为最小项或最大项的序号)。

(1) A +B +D (× ); (2) ABCD (m 7 ); (3) ABC ( × ) (4)AB (C +D ) (×); (5) A B C D +++ (M 9 ) ; (6) A+B+CD (× ); 8、函数式F=AB+BC+CD 写成最小项之和的形式结果应为m ∑(3,6,7,11,12,13,14,15),写成最大项之积的形式结果应为M (∏ 0,1,2,4,5,8,9,10 )9、对逻辑运算判断下述说法是否正确,正确者在其后( )内打对号,反之打×。

(1) 若X +Y =X +Z ,则Y=Z ;( × ) (2) 若XY=XZ ,则Y=Z ;( × ) (3) 若X ⊕Y=X ⊕Z ,则Y=Z ;(√ ) 【3-2】用代数法化简下列各式(1) F 1 =1ABC AB += (2) F 2 =ABCD ABD ACD AD ++=(3)3F AC ABC ACD CD A CD=+++=+ (4) 4()()F A B C A B C A B C A BC=++⋅++⋅++=+【3-3】 用卡诺图化简下列各式(1) 1F BC AB ABC AB C =++=+ (2) 2F AB BC BC A B=++=+(3) 3F AC AC BC BC AB AC BC =+++=++ (4) 4F ABC ABD ACD CD ABC ACD A D=+++++=+或AB AC BC ++(5) 5F ABC AC ABD AB AC BD =++=++ (6) 6F AB CD ABC AD ABC A BC CD=++++=++(7) 7F AC AB BCD BD ABD ABCD A BD BD =+++++=++ (8) 8 F AC AC BD BD ABCD ABCD ABCD ABCD=+++=+++(9) 9()F A C D BCD ACD ABCD CD CD =⊕+++=+(10)F 10=10F AC AB BCD BEC DEC AB AC BD EC =++++=+++ 【3-4】 用卡诺图化简下列各式 (1) P 1(A ,B ,C )=(0,1,2,5,6,7)m AB AC BC =++∑(2) P 2(A ,B ,C ,D )=(0,1,2,3,4,6,7,8,9,10,11,14)m AC AD B CD =+++∑ (3)P 3(A ,B ,C ,D )=(0,1,,4,6,8,9,10,12,13,14,15)m AB BC AD BD =+++∑(4) P 4 (A ,B ,C ,D )=17M M A BC BC D •=+++ 【3-5】用卡诺图化简下列带有约束条件的逻辑函数(1)()1,,,(3,6,8,9,11,12)(0,1,2,13,14,15)()d P A B C D m AC BD BCD ACD =+=++∑∑或 (2) P 2(A ,B ,C ,D )=(0,2,3,4,5,6,11,12)(8,9,10,13,14,15)dm BC BC D +=++∑∑(3) P 3 =()A C D ABCD ABCD AD ACD BCD ABD ++++=++或 AB +AC =0 (4) P 4 =A B ABCD ABCD +=+(A B C D 为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1) 【3-6】 已知: Y 1 =AB AC BD ++ Y 2 =ABCD ACD BCD BC +++ 用卡诺图分别求出Y Y 12⋅, Y Y 12+, Y Y 12⊕。

《数字电子技术基础》课后习题及参考答案#(精选.)

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后答案

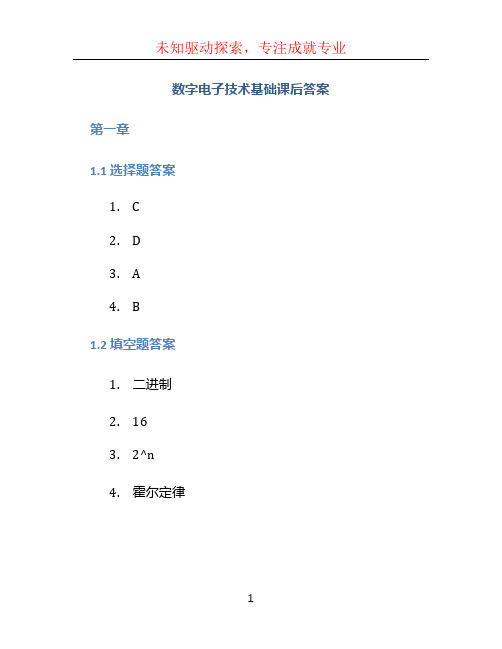

数字电子技术基础课后答案第一章1.1 选择题答案1.C2.D3.A4.B1.2 填空题答案1.二进制2.163.2^n4.霍尔定律1.3 简答题答案1.数字系统的特征:离散性、离散性变量、离散性元件。

2.多位二进制数的表示:每一位上的位权是2的倍数,从右到左依次是1、2、4、8、16,即从低到高位权递增。

3.数字电路中的常用逻辑门:与门、或门、非门、异或门。

4.二进制加法器:用于实现二进制数的加法操作,可以分为半加器和全加器两种。

第二章2.1 选择题答案1.B2.C3.A4.D2.2 填空题答案1.与非门2.非3.低电平4.与非门2.3 简答题答案1.逻辑代数的基本运算:与运算、或运算、非运算。

2.逻辑门的基本类型:与门、或门、非门。

3.逻辑电位表示:用两个不同的电平来表示逻辑0和逻辑1,常用的是低电平表示逻辑0,高电平表示逻辑1。

4.逻辑门的输入输出关系:根据输入的逻辑电平,逻辑门会产生对应的输出电平。

第三章3.1 选择题答案1.C2.B3.D4.A3.2 填空题答案1.或非门2.与非门3.反相器4.同或门3.3 简答题答案1.反相器的功能:将输入信号的逻辑电平反转。

2.与非门和或非门的功能:与非门将与门的输出进行反向,或非门将或门的输出进行反向。

3.同或门的功能:在输入信号相同的情况下,输出逻辑1;在输入信号不同的情况下,输出逻辑0。

4.逻辑门的级联:逻辑门可以通过级联连接,实现复杂的逻辑功能。

第四章4.1 选择题答案1.C2.D3.A4.B4.2 填空题答案1.半加器2.与非门3.非门4.不可用4.3 简答题答案1.半加器的功能:用于实现两个单独的二进制位的相加操作,产生和位和进位位。

2.全加器的功能:用于实现三个二进制位的相加操作,包括输入的两个二进制位和进位位,产生和位和进位位。

3.二进制加法器的级联:通过将多个全加器级联连接,可以实现多位二进制数的相加操作。

4.数字比较器的功能:用于比较两个多位二进制数的大小,根据比较结果输出大于、小于或等于的信号。

《数字电子技术基础》课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后答案全解

第3章 逻辑代数及逻辑门【3-1】 填空1、与模拟信号相比,数字信号的特点是它的 离散 性。

一个数字信号只有两种取值分别表示为0 和1 。

2、布尔代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算,分别为与非、或非、异或、同或和与或非。

3、与运算的法则可概述为:有“0”出 0 ,全“1”出 1;类似地或运算的法则为 有”1”出”1”,全”0”出”0” 。

4、摩根定理表示为:A B ⋅=A B + ;A B +=A B ⋅。

5、函数表达式Y=AB C D ++,则其对偶式为Y '=()A B C D +⋅。

6、根据反演规则,若Y=AB C D C +++,则Y =()AB C D C ++⋅ 。

7、指出下列各式中哪些是四变量A B C D 的最小项和最大项。

在最小项后的( )里填入m i ,在最大项后的( )里填入M i ,其它填×(i 为最小项或最大项的序号)。

(1) A +B +D (× ); (2) ABCD (m 7 ); (3) ABC ( × ) (4)AB (C +D ) (×); (5) A B C D +++ (M 9 ) ; (6) A+B+CD (× ); 8、函数式F=AB+BC+CD 写成最小项之和的形式结果应为m ∑(3,6,7,11,12,13,14,15),写成最大项之积的形式结果应为M (∏ 0,1,2,4,5,8,9,10 )9、对逻辑运算判断下述说法是否正确,正确者在其后( )内打对号,反之打×。

(1) 若X +Y =X +Z ,则Y=Z ;( × ) (2) 若XY=XZ ,则Y=Z ;( × ) (3) 若X ⊕Y=X ⊕Z ,则Y=Z ;(√ ) 【3-2】用代数法化简下列各式(1) F 1 =1ABC AB += (2) F 2 =ABCD ABD ACD AD ++=(3)3F AC ABC ACD CD A CD=+++=+ (4) 4()()F A B C A B C A B C A BC=++⋅++⋅++=+【3-3】 用卡诺图化简下列各式(1) 1F BC AB ABC AB C =++=+ (2) 2F AB BC BC A B=++=+(3) 3F AC AC BC BC AB AC BC =+++=++ (4) 4F ABC ABD ACD CD ABC ACDA D=+++++=+或AB AC BC ++(5) 5F ABC AC ABD AB AC BD =++=++ (6) 6F AB CD ABC AD ABC A BC CD=++++=++(7) 7F AC AB BCD BD ABD ABCD A BD BD =+++++=++ (8) 8 F AC AC BD BD ABCD ABCD ABCD ABCD=+++=+++(9) 9()F A C D BCD ACD ABCD CD CD =⊕+++=+(10)F 10=10F AC AB BCD BEC DEC AB AC BD EC =++++=+++ 【3-4】 用卡诺图化简下列各式 (1) P 1(A ,B ,C )=(0,1,2,5,6,7)m AB AC BC =++∑(2) P 2(A ,B ,C ,D )=(0,1,2,3,4,6,7,8,9,10,11,14)m AC AD B CD =+++∑ (3)P 3(A ,B ,C ,D )=(0,1,,4,6,8,9,10,12,13,14,15)m AB BC AD BD =+++∑(4) P 4 (A ,B ,C ,D )=17M M A BC BC D •=+++ 【3-5】用卡诺图化简下列带有约束条件的逻辑函数(1)()1,,,(3,6,8,9,11,12)(0,1,2,13,14,15)()d P A B C D m AC BD BCD ACD =+=++∑∑或 (2) P 2(A ,B ,C ,D )=(0,2,3,4,5,6,11,12)(8,9,10,13,14,15)dm BC BC D +=++∑∑(3) P 3 =()A C D ABCD ABCD AD ACD BCD ABD ++++=++或 AB +AC =0 (4) P 4 =A B ABCD ABCD +=+(A B C D 为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1) 【3-6】 已知: Y 1 =AB AC BD ++ Y 2 =ABCD ACD BCD BC +++ 用卡诺图分别求出Y Y 12⋅, Y Y 12+, Y Y 12⊕。

《数字电子技术基础》课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

《数字电子技术基础》课后习题及参考答案

第1章习题与参考答案【题1-1】将以下十进制数转换为二进制数、八进制数、十六进制数。

〔1〕25;〔2〕43;〔3〕56;〔4〕78解:〔1〕25=〔11001〕2=〔31〕8=〔19〕16〔2〕43=〔101011〕2=〔53〕8=〔2B〕16〔3〕56=〔111000〕2=〔70〕8=〔38〕16〔4〕〔1001110〕2、〔116〕8、〔4E〕16【题1-2】将以下二进制数转换为十进制数。

〔1〕10110001;〔2〕10101010;〔3〕11110001;〔4〕10001000 解:〔1〕10110001=177〔2〕10101010=170〔3〕11110001=241〔4〕10001000=136【题1-3】将以下十六进制数转换为十进制数。

〔1〕FF;〔2〕3FF;〔3〕AB;〔4〕13FF解:〔1〕〔FF〕16=255〔2〕〔3FF〕16=1023〔3〕〔AB〕16=171〔4〕〔13FF〕16=5119【题1-4】将以下十六进制数转换为二进制数。

〔1〕11;〔2〕9C;〔3〕B1;〔4〕AF解:〔1〕〔11〕16=〔00010001〕2〔2〕〔9C〕16=〔10011100〕2〔3〕〔B1〕16=〔1011 0001〕2〔4〕〔AF〕16=〔10101111〕2【题1-5】将以下二进制数转换为十进制数。

〔1〕1110.01;〔2〕1010.11;〔3〕1100.101;〔4〕1001.0101解:〔1〕〔1110.01〕2=14.25〔2〕〔1010.11〕2=10.75〔3〕〔1001.0101〕2=9.3125【题1-6】将以下十进制数转换为二进制数。

〔1〕20.7;〔2〕10.2;〔3〕5.8;〔4〕101.71解:〔1〕20.7=〔10100.1011〕2〔2〕10.2=〔1010.0011〕2〔3〕5.8=〔101.1100〕2〔4〕101.71=〔1100101.1011〕2【题1-7】写出以下二进制数的反码与补码〔最高位为符号位〕。

(全)数字电子技术基础课后答案

【题

(

解:(1)A=0,B=0

(2)A=0,B=1或C=1

(3)A=1,B=0,C=1

(4)A=0,B=1或C=0

【题

(

解:(1)

A

B

C

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

1

(2)

当A取1时,输出Y为1,其他情况Y=0。

【题

(

(

解:(1)左边 右边

【题

(1)

解:(1)25=(0010 0101)BCD

(

(

(

【题

解:4位数格雷码;

0000、0001、0011、0010、0110、0111、0101、0100、1100、1101、1111、1010、1011、1001、1000、

第

【题

图题2-1

解:

【题

图题2-2

解:

【题

图题2-3

解:

【题

图题2-4

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

《数字电子技术基础》课后习题答案

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1)十六进制转二进制:45 C010*********二进制转八进制:010*********2134十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2)十六进制转二进制:6D E.C8011011011110.11001000二进制转八进制:011011011110.1100100003336.62十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1758.78125)10所以:(6DE.C8)16=(011011011110. 11001000)2=(3336.62)8=(1758.78125)10(3)十六进制转二进制:8F E.F D100011111110.11111101二进制转八进制:100011111110.1111110104376.772十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10所以:(8FE.FD)16=(100011111110.11111101)2=(437 6.772)8=(2302.98828125)10 (4)十六进制转二进制:79E.F D011110011110.11111101二进制转八进制:011110011110.1111110103636.772十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10所以:(8FE.FD)16=(011110011110.11111101)2=(3636.772)8=(1950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则 二、 2、×4、× 三、 1、B 3、D5、C练习题:2.2:(4)解:Y =AB̅+BD +DCE +A D =AB̅+BD +AD +A D +DCE =AB̅+BD +D +DCE =AB̅+D (B +1+CE ) =AB̅+D (8)解:Y =(A +B ̅+C )(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅(A +B ̅+C +DE ) =[(A +B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅+(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅](A +B ̅+C +DE ) =(ABC +DE )(ABC ̅̅̅̅̅̅+DE ) =DE2.3:(2)证明:左边=A +A (B +C)̅̅̅̅̅̅̅̅̅̅̅̅ =A +A +(B +C)̅̅̅̅̅̅̅̅̅̅ =A +B̅C ̅ =右式所以等式成立(4)证明:左边= (A B +AB̅)⨁C = (A B +AB ̅)C + (A B +AB̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅C = (A BC +AB ̅C )+A B ̅̅̅̅⋅AB̅̅̅̅⋅C =A BC +AB̅C +(A +B ̅)(A +B )C =A BC +AB̅C +(AB +A B ̅)C =A BC +AB̅C +ABC +A B ̅C 右边= ABC +(A +B +C )AB̅̅̅̅⋅BC ̅̅̅̅⋅CA ̅̅̅̅ =ABC +(A +B +C )[(A +B̅)(B ̅+C )(C +A )]=ABC +(A +B +C )(A B̅+A C +B ̅+B ̅C )(C +A ) =ABC +(A +B +C )(A B̅C +A C +B ̅C +A B ̅) =ABC +AB̅C +A BC +A B ̅C 左边=右边,所以等式成立 2.4(1)Y ′=(A +B̅C )(A +BC) 2.5(3)Y ̅=A B ̅̅̅̅(C +D ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅ C D ̅̅̅̅̅(A +B ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 2.6:(1)Y =AB +AC +BC=AB (C +C̅)+AC (B +B ̅)+BC (A +A ̅) =ABC +ABC̅+AB ̅C +A ̅BC 2.7:(1)Y =A B̅+B ̅C +AC +B ̅C 卡诺图如下:所以,Y =B2.8:(2)画卡诺图如下:Y(A,B,C)=A +B̅+C2.9:(1)画Y (A,B,C,D )=∑m (0,1,2,3,4,6,8)+∑d(10,11,12,13,14)如下:Y (A,B,C,D )=A B̅+D ̅2.10:(3)解:化简最小项式:Y =AB +(A B +C )(A B̅+C ) =AB +(A B A B̅+A BC +A B ̅C +C C ) =AB (C +C )+A BC +A B̅C =ABC +ABC ̅+A BC +A B ̅C =∑m (0,3,6,7)最大项式:Y =∏M(1,2,4,5)2.13:(3)Y =AB̅+BC +AB ̅C +ABC D ̅ =AB̅(1+C )+BC (1+AD ̅) =AB ̅+BC =AB ̅+BC ̿̿̿̿̿̿̿̿̿̿̿̿ = AB ̅̅̅∙BC ̅̅̅̅̅̅̅̅̅̅̅技能题:2.16 解:设三种不同火灾探测器分别为A 、B 、C ,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:Y =AB +AC +BC =AB +AC +BC ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ =AB ̅̅̅̅⋅AC̅̅̅̅⋅BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ =(A +B ̅)(A +C )(B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ =A +B ̅̅̅̅̅̅̅̅+A +C ̅̅̅̅̅̅̅̅+B ̅+C̅̅̅̅̅̅̅̅第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空; 二、 1、√ 8、√; 三、 1、A 4、D练习题:3.2、解:(a)因为接地电阻4.7k Ω,开门电阻3k Ω,R>R on ,相当于接入高电平1,所以Y =A B 1̅̅̅̅̅̅=A +B +0=A +B (e) 因为接地电阻510Ω,关门电0.8k Ω,R<R off ,相当于接入高电平0,所以、 Y =A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅⋅B ̅∙1̅̅̅̅̅̅̅̅̅̅=A +B +0=A +B3.4、解:(a) Y 1=A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A +B ̅̅̅̅̅̅̅(c) Y 3=A +B +1̅̅̅̅̅̅̅̅̅̅̅̅̅=1̅=0(f) Y 6=A ⋅0+B ⋅1̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B̅3.7、解:(a) Y 1=A⨁B ⋅C =(A B +AB̅)C =A B C +AB ̅C3.8、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I N G 反相器可带17个同类反相器3.12EN=1时,Y 1=A , Y 2=B̅ EN=0时,Y 1=A̅, Y 2=B3.17根据题意,设A 为具有否决权的股东,其余两位股东为B 、C ,画卡诺图如下,则表达结果Y 的表达式为:Y =AB +AC =AB +AC ̿̿̿̿̿̿̿̿̿̿̿=AB ̅̅̅̅⋅AC̅̅̅̅̅̅̅̅̅逻辑电路如下:技能题:3.20:解:根据题意,A 、B 、C 、D 变量的卡诺图如下:Y =ABC +ABD =ABC +ABD ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=ABC̅̅̅̅̅̅⋅ABD ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a) Y =A⨁B +B ̅̅̅̅̅̅̅̅̅̅̅̅̅=A B +AB ̅+B ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A B +B ̅̅̅̅̅̅̅̅̅̅̅=A +B ̅̅̅̅̅̅̅̅=AB ,所以电路为与门。

胡晓光数字电子技术基础课本课后答案(北航考研必备)

第一章逻辑代数基础1.1 、用布尔代数的基本公式和规则证明下列等式。

1.2 、求下列函数的反函数。

1.3 、写出下列函数的对偶式。

1.4 、证明函数F 为自对偶函数。

1.5 、用公式将下列函数化简为最简“与或”式。

1.6 、逻辑函数。

若A 、B 、C 、D 、的输入波形如图所示,画出逻辑函数 F 的波形。

1.7 、逻辑函数F 1 、F 2 、F 3 的逻辑图如图2 — 35 所示,证明F 1 =F 2 =F 3 。

1.8 、给出“与非”门、“或非”门及“异或”门逻辑符号如图2 — 36 (a )所示,若A 、B 的波形如图2 — 36 (b ),画出F 1 、F 2 、F 3 波形图。

1.9 、用卡诺图将下列函数化为最简“与或”式。

1.10 、将下列具有无关最小项的函数化为最简“与或”式;1.11 、用卡诺图将下列函数化为最简“与或”式;1.12 用卡诺图化简下列带有约束条件的逻辑函数1.13 、用最少的“与非”门画出下列多输出逻辑函数的逻辑图。

第二章门电路2.1 由TTL 门组成的电路如图 2.1 所示,已知它们的输入短路电流为I is =1.6mA ,高电平输入漏电流I iH = 40。

试问:当A=B=1 时,G 1 的灌电流(拉,灌)为3.2mA ;A=0 时,G 1 的拉电流(拉,灌)为120。

2.2 图2.2 中示出了某门电路的特性曲线,试据此确定它的下列参数:输出高电平U OH = 3V ;输出低电平U OL = 0.3V ;输入短路电流I iS = 1.4mA ;高电平输入漏电流I iH = 0.02mA ;阈值电平U T = 1.5V ;开门电平U ON = 1.5V ;关门电平U OFF = 1.5V ;低电平噪声容限U NL = 1.2V ;高电平噪声容限U NH = 1.5V ;最大灌电流I OLmax = 15mA ;扇出系数N= 10 .2.3 TTL 门电路输入端悬空时,应视为高电平;(高电平,低电平,不定)此时如用万用表测量其电压,读数约为 1.4V (3.6V ,0V , 1.4V )。

数字电子技术基础课后答案全解

第3章 逻辑代数及逻辑门【3-1】 填空1、与模拟信号相比,数字信号的特点是它的 离散 性。

一个数字信号只有两种取值分别表示为0 和1 。

2、布尔代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算,分别为与非、或非、异或、同或和与或非。

3、与运算的法则可概述为:有“0”出 0 ,全“1”出 1;类似地或运算的法则为 有”1”出”1”,全”0”出”0” 。

4、摩根定理表示为:=;=。

5、函数表达式Y=,则其对偶式为Y '=。

6、根据反演规则,若Y=,则。

7、指出下列各式中哪些是四变量A B C D 的最小项和最大项。

在最小项后的( )里填入m i ,在最大项后的( )里填入M i ,其它填×(i 为最小项或最大项的序号)。

(1) A +B +D (× ); (2) (m 7 ); (3) ABC ( × )(4)AB (C +D ) (×); (5)(M 9 ) ; (6) A+B+CD (× );8、函数式F=AB+BC+CD 写成最小项之和的形式结果应为(3,6,7,11,12,13,14,15),写成最大项之积的形式结果应为0,1,2,4,5,8,9,10 )9、对逻辑运算判断下述说法是否正确,正确者在其后( )内打对号,反之打×。

(1) 若X +Y =X +Z ,则Y=Z ;( × ) (2) 若XY=XZ ,则Y=Z ;( × ) (3) 若X Y=X Z ,则Y=Z ;(√ ) 【3-2】用代数法化简下列各式(1) F 1 =1ABC AB += (2) F 2 =ABCD ABD ACD AD ++=(3)3F AC ABC ACD CD A CD=+++=+ (4) 4()()F A B C A B C A B C A BC=++⋅++⋅++=+【3-3】 用卡诺图化简下列各式(1) 1F BC AB ABC AB C =++=+ (2) 2F AB BC BC A B=++=+(3) 3F AC AC BC BC AB AC BC =+++=++ (4) 4F ABC ABD ACD CD ABC ACD A D=+++++=+或(5) 5F ABC AC ABD AB AC BD =++=++ (6) 6F AB CD ABC AD ABC A BC CD=++++=++(7) 7F AC AB BCD BD ABD ABCD A BD BD =+++++=++ (8) 8 F AC AC BD BD ABCD ABCD ABCD ABCD=+++=+++(9) 9()F A C D BCD ACD ABCD CD CD =⊕+++=+(10)F 10=10F AC AB BCD BEC DEC AB AC BD EC =++++=+++ 【3-4】 用卡诺图化简下列各式 (1) P 1(A ,B ,C )=(0,1,2,5,6,7)m AB AC BC =++∑(2) P 2(A ,B ,C ,D )=(0,1,2,3,4,6,7,8,9,10,11,14)m AC AD B CD =+++∑ (3)P 3(A ,B ,C ,D )=(0,1,,4,6,8,9,10,12,13,14,15)m AB BC AD BD =+++∑(4) P 4 (A ,B ,C ,D )=17M M A BC BC D •=+++ 【3-5】用卡诺图化简下列带有约束条件的逻辑函数(1)()1,,,(3,6,8,9,11,12)(0,1,2,13,14,15)()d P A B C D m AC BD BCD ACD =+=++∑∑或 (2) P 2(A ,B ,C ,D )=(0,2,3,4,5,6,11,12)(8,9,10,13,14,15)dm BC BC D +=++∑∑(3) P 3 =()A C D ABCD ABCD AD ACD BCD ABD ++++=++或 AB +AC =0 (4) P 4 =A B ABCD ABCD +=+(A B C D 为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1) 【3-6】 已知: Y 1 = Y 2 =用卡诺图分别求出,,。

《数字电子技术基本》课后知识题及参备考资料答案解析

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101 解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章逻辑代数基础1.1 、用布尔代数的基本公式和规则证明下列等式。

1.2 、求下列函数的反函数。

1.3 、写出下列函数的对偶式。

1.4 、证明函数F 为自对偶函数。

1.5 、用公式将下列函数化简为最简“与或”式。

1.6 、逻辑函数。

若 A 、B 、C 、D 、的输入波形如图所示,画出逻辑函数 F 的波形。

1.7 、逻辑函数F 1 、F 2 、F 3 的逻辑图如图2 — 35 所示,证明F 1 =F 2 =F 3 。

1.8 、给出“与非”门、“或非”门及“异或”门逻辑符号如图2 — 36 (a )所示,若A 、B 的波形如图2 — 36 ( b ),画出F 1 、 F 2 、 F 3 波形图。

1.9 、用卡诺图将下列函数化为最简“与或”式。

1.10 、将下列具有无关最小项的函数化为最简“与或”式;1.11 、用卡诺图将下列函数化为最简“与或”式;1.12 用卡诺图化简下列带有约束条件的逻辑函数1.13 、用最少的“与非”门画出下列多输出逻辑函数的逻辑图。

第二章门电路2.1 由TTL 门组成的电路如图2.1 所示,已知它们的输入短路电流为I is =1.6mA ,高电平输入漏电流I iH = 40。

试问:当A=B=1 时,G 1 的灌电流(拉,灌)为3.2mA ;A=0时,G 1 的拉电流(拉,灌)为120。

2.2 图2.2 中示出了某门电路的特性曲线,试据此确定它的下列参数:输出高电平U OH = 3V ;输出低电平U OL = 0.3V ;输入短路电流I iS = 1.4mA ;高电平输入漏电流I iH = 0.02mA ;阈值电平U T = 1.5V ;开门电平U ON = 1.5V ;关门电平U OFF = 1.5V ;低电平噪声容限U NL = 1.2V ;高电平噪声容限U NH = 1.5V ;最大灌电流I OLmax = 15mA ;扇出系数N= 10 .2.3 TTL 门电路输入端悬空时,应视为高电平;(高电平,低电平,不定)此时如用万用表测量其电压,读数约为1.4V (3.6V ,0V ,1.4V )。

2.4 CT74 、CT74H 、CT74S 、CT74LS 四个系列的TTL 集成电路,其中功耗最小的为CT74LS ;速度最快的为CT74S ;综合性能指标最好的为CT74LS 。

2.5 CMOS 门电路的特点:静态功耗极低(很大,极低);而动态功耗随着工作频率的提高而增加(增加,减小,不变);输入电阻很大(很大,很小);噪声容限高(高,低,等)于TTL 门。

2.6 集电极开路门(OC 门)在使用时须在输出与电源之间接一电阻(输出与地,输出与输入,输出与电源)。

2.7若G 2 的悬空的输入端接至0.3V ,结果如下表2.9 输入悬空时为高电平,M= “ 0 ” , V M =0.2V , 三态门输出为高阻, M 点电位由后面“与或非”门的输入状态决定,后面与门中有一输入为 0 ,所以 V M =0V 。

2.102.11 上图中门 1 的输出端断了,门 2 、 3 、 4 为高电平输入,此时 V M =1.6V 左右。

2.12 不能正常工作,因为不能同时有效,即不能同时为低电平。

2.13 图为由TTL “与非”门组成的电路,输入 A 、 B 的波形如图所示,试画出 V 0 的波形。

2.14 图中门 1 、 2 、 3 均为 TTL 门电路,平均延迟时间为 20ns ,画出 V O 的波形。

2--81 、 Y 1 =ABCDE Y2 =A+B+C+D+E2 、该扩展方法不适用于 TTL 门电路。

对与门而言,当扩展端 C=0.3V 时,其输入电压约为 1V ,已大于 U iLmax (0.8V) ;对或门而言,当扩展端 C=U OHmin =2.4V 时,其输入电压约为 1.7V ,已小于 U iHmin (2V) ;2--92--10 乙的说法正确,因为该点的电压有可能是变化的,此时万用表测得的是电压的平均值, 1.8V 的读数完全正常。

3.6 结果如下表:3.7 1. 真值表 : 3. 表达式: F 2 =M ,3.8 1 、真值表3.9 3.113.12 把 BCD 8421 码转换为 BCD 5421 码,前五个数码不需改变,后五个数码加 3 。

据此可得加数低两位的卡诺图,所以3.141 、2 、用八选一数据选择器和门电路实现。

3.15 用 8 选 1 数据选择器实现下列函数:第四章触发器和定时器4.14.2 ( 1 )特性表 (CP=0 时,保持; CP=1 时如下表 )(2) 特性方程(3) 该电路为锁存器(时钟型 D 触发器)。

CP=0 时,不接收 D 的数据; CP=1 时,把数据锁存。

( 但该电路有空翻 )4.3 (1) 、 C=0 时该电路属于组合电路; C=1 时是时序电路。

(2) 、(3) 、输出 Q 的波形如下图。

4.44.54.64.7 1 、 CP 作用下的输出 Q 1 Q 2 和 Z 的波形如下图; 2 、 Z 对 CP 三分频。

4.8 由得 D 触发器转换为 J-K 触发器的逻辑图如下面的左图;而将 J-K 触发器转换为 D 触发器的逻辑图如下面的右图。

4.11 1 、 555 定时器构成多谐振荡器。

2 、 u c, u o 1 , u o 2的波形3 、 u o 1 的频率,u o 2 的频率 f 2 =158H z4 、如果在 555 定时器的第 5 脚接入 4V 的电压源,则 u o 1 的频率变为4.12 图 (a) 是由 555 定时器构成的单稳态触发电路。

1 、工作原理(略);2 、暂稳态维持时间 t w =1.1RC=10ms(C 改为 1) ;3 、 u c 和 u o 的波形如下图:4 、若 u i 的低电平维持时间为 15m s ,要求暂稳态维持时间 t w 不变,可加入微分电路4.13 由 555 定时器构成的施密特触发器如图 (a) 所示1 、电路的电压传输特性曲线如左下图;2 、 u o 的波形如右下图;3 、为使电路能识别出 u i 中的第二个尖峰,应降低 555 定时器 5 脚的电压至 3V 左右。

4 、在 555 定时器的 7 脚能得到与 3 脚一样的信号,只需在 7 脚与电源之间接一电阻。

4.14 延迟时间 t d =1.1 × 1 × 10=11s扬声器发出声音的频率。

第五章时序数字电路5.1 解:5.2 解:5.3 解:逻辑功能:可自启动的同步五进制加法计数器。

5.4逻辑功能:移位寄存器型四进制计数器。

5.55.6 解:( 1 )当 X 1 X 2= “ 00 ” ;初始状态为“ 00 ” 时:逻辑功能:电路实现2 分频。

( 2 )当X 1 X 2 = “ 01 ”;初始状态为“ 00 ”时逻辑功能:电路实现 3 分频。

(3 )当X 1 X 2 = “ 11 ” ;初始状态为“ 00 ” 时:逻辑功能:电路实现 4 分频。

5.75.8 (1) 基本 R-S 触发器( × ) ; (2) 同步 R-S 触发器(× );(3) 主从 J-K 触发器 ( 能); (4) 维持阻塞 D 触发器 ( 能);(5) 边沿 J-K 触发器 ( 能 ) ; (6) CMOS 主从 D 触发器(能)。

5.9 根据题意,很容易画出下面的逻辑图:5.10 解:四种状态应使用 2 个触发器。

设: Q 1 =Y 1, Q 0 =Y 0用 D 触发器设计;5.11 解:用 J — K 触发器设计一个 4 进制计数器, Q 1 Q 0为变量译码器的输入。

5.12 解:5.13 解:设 S 0 :初始及检测成功状态; S 1 :输入一个“ 1 ” 状态; S 2 :输入“ 10 ” 状态;S 3 :输入“ 101 ” 状态; X :输入; Z :输出。

从 JK 的卡诺图可以看出电路的简化结果相似,以方案三画逻辑电路5.14 解:从时序图可得出状态图为:5.15 解:方法一:从时序图中可以看出将 Y 1 、 Y 2 、Z 为输出时,每经过 8 个时钟为一个循环。

同理,从卡诺图可以求出:方法二:从时序图中可以看出 Y 1 Y 2的状态为00 → 11 → 01 → 10 → 00 。

设:则状态图、状态表为:显然,方法二的结果比方法一的结果要简单得多。

其逻辑图为:5.16 解: ZW 的状态为 00 、 01 、 10 、 11 ,所以设:输出 Z=Q 1 ; W=Q 0 ;输入: X5.17 解: 1 、状态转换图2.Qd 对 CP 十分频, Qd 的占空比是 50% 。

5.18 答案:图 (a) 是七进制计数器,图 (b) 是十进制计数器,图 (c) 是十进制计数器 (6 7 ... 15 6)1 、若将图 (a) 中与非门 G 的输出改接至 C r 端,而令 L D =1 ,电路变为六进制2 、图 (b) 电路的输出采用的是余三码。

5.19 答案:方法是用90 ÷ 16=5 … 10 ,高位用 0101 作译码状态 , 低位用1010 作译码状态,由此得到了置数端L D 的连接方式。

5.20 答案:图 (a) 为三进制,图 (b) 为四进制,图 (c) 为七进制,图 (d) 为十二进制,图 (e) 为三十七进制5.21 解: 1. 对应 CP 的输出 Q a Q d Q c 和 Qb 的波形和状态转换图如下图:2 、按 Q a Q d Q c Qb 顺序电路给出的是 BCD 5421 码3 、按 Q d Q c QbQ a 顺序电路给出的编码如下图:5.22 答案:当 MN 为各种不同输入时,可组成四种不同进制的计数器第六章大规模集成电路6.1 填空1 、按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用正负剩磁来存储数据;而半导体存储器利用器件的开关状态来存储数据。

两者相比,前者一般容量较大;而后者具有速度快的特点。

2 、半导体存储器按功能分有 ROM 和 RAM 两种。

3 、 ROM 主要由地址译码器和存储矩阵两部分组成。

按照工作方式的不同进行分类, ROM 可分为固定内容的 ROM 、 PROM 和 EPROM 三种。

4 、某 EPROM 有 8 数据线, 13 位地址线,则其存储容量为 2 13 × 8 。

5 、 PLA 一般由与 ROM 、或 ROM 和反馈逻辑网络三部分组成。

6.26.36.4 6.5 6.6第七章数模与模数转换器7.1 填空1 、 8 位 D/A 转换器当输入数字量只有最高位为高电平时输出电压为 5V, 若只有最低位为高电平,则输出电压为 40mV 。

若输入为 10001000 ,则输出电压为 5.32V 。