单片机原理与技术第5章80C51的并行端口

单片机原理及应用第6章80C51单片机的串行口

单片机原理及应用第6章80C51单片机的串行口80C51单片机是一种基于哈佛架构的8位单片机,具有强大的串行口功能。

串行口是一种通信接口,可以通过单根线传输数据。

本章将介绍80C51单片机的串行口原理及其应用。

一、80C51单片机的串行口原理80C51单片机的串行口包含两个寄存器,分别是SBUF(串行缓冲器)和SCON(串行控制寄存器)。

SBUF寄存器用来存储待发送或接收到的数据,SCON寄存器用来配置和控制串行口的工作模式。

80C51单片机的串行口有两种工作模式:串行异步通信模式和串行同步通信模式。

1.串行异步通信模式串行异步通信是指通信双方的时钟频率不同步,通信的数据按照字符为单位进行传输,字符之间有起始位、数据位、校验位和停止位组成。

80C51单片机的串行口支持标准的RS-232通信协议和非标准通信协议。

在串行异步通信模式下,SCON寄存器需要配置为相应的工作模式。

首先,需要选择串行口的工作模式。

80C51单片机支持第9位,即扩展模式,可以用来检测通信错误。

其次,需要设置波特率。

波特率是指数据每秒传输的位数,用波特率发生器(Baud Rate Generator,BRGR)来控制。

然后,需要设置起始位、数据位和停止位的配置,包括数据长度(5位、6位、7位或8位)、停止位的个数(1位或2位)。

在发送数据时,将待发送的数据通过MOV指令传送到SBUF寄存器,单片机会自动将数据发送出去。

在接收数据时,需要检测RI(接收中断)标志位,如果RI为1,表示接收到数据,可以通过MOV指令将接收到的数据读取到用户定义的变量中。

2.串行同步通信模式串行同步通信是指通信双方的时钟频率同步,在数据传输时需要时钟信号同步。

80C51单片机的串行同步通信支持SPI(串行外设接口)和I2C(串行总线接口)两种协议。

在串行同步通信模式下,SCON寄存器需要配置为相应的工作模式。

首先,需要选择串行口的工作模式。

80C51单片机支持主从模式,可以作为主设备发送数据,也可以作为从设备接收数据。

2.3 80C51单片机的并行端口结构

80C51单片机的并行端口结构80C51共有4个8位的并行I/O口,分别记作P0、P1、P2、P3。

被归入专用寄存器。

I/O端口有串行和并行之分,串行I/O端口一次只能传送一位二进制信息,并行I/O端口一次能传送一组二进制信息。

(1)并行I/O口的功能①PO口:电路中包括一个数据输出锁存器和两个三态数据输入缓存器,另外还有一个数据输出的驱动和控制电路。

这两组端口用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口的总线接口,而不像P1、P3直接用做输出口。

P0.0~P0.7,P0口是8位双向I/O口,P0.i引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

该8位都是漏极开路(漏极开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态)输出,每个引脚可以驱动8个LS型TTL负载且内部没有上拉电阻,执行输出功能时外部必须接上拉电阻(10K 即可)。

若要执行输入功能,必须先输出高电平方能读取该端口所连接的外部数据;若在访问外部存储器(RAM、ROM)和扩展的I/O口时,P0可作为地址总线(A0~A7)和数据总线(D0~D7),分时进行工作。

在指令的前半周期,P0口作为地址总线的低8位,在指令的后半周期为8位的数据总线。

P1口的各个单元:输入缓冲器:在P0口中,有两个三态的缓冲器,三态门有三个状态,即在其输出端可以是高电平、低电平和高阻状态(或称为禁止状态)。

上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为…读锁存器‟端)有效。

要读取P0.i引脚上的数据,也要使标号为…读引脚‟的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:存储器中可以存放电荷,加一个小的存储器的单元,并在它的面前加一个开关,要让这一位输出时,就把开关打开,信号就进入存储器的单元,然后马上关闭开关,这一位的状态就被保存下来,直到下一次命令让它把开关再打开为止,这就是锁存器。

80c51单片机定时器计数器工作原理

80c51单片机定时器计数器工作原理80C51单片机是一种常用的微控制器,其定时器/计数器(Timer/Counter)是实现定时和计数功能的重要组件。

以下简要介绍80C51单片机定时器/计数器的工作原理:1. 结构:定时器/计数器由一个16位的加法器构成,可以自动加0xFFFF(即65535)。

定时器/计数器的输入时钟可以来自系统时钟或外部时钟源。

2. 工作模式:定时模式:当定时器/计数器的输入时钟源驱动加法器不断计数时,可以在达到一定时间后产生中断或产生其他操作。

计数模式:当外部事件(如电平变化)发生时,定时器/计数器的输入引脚可以接收信号,使加法器产生一个增量,从而计数外部事件发生的次数。

3. 定时常数:在定时模式下,定时常数(即定时时间)由预分频器和定时器/计数器的初值共同决定。

例如,如果预分频器设置为1,定时器/计数器的初值为X,那么实际的定时时间 = (65535 - X) 预分频系数输入时钟周期。

在计数模式下,定时常数由外部事件发生的时间间隔决定。

4. 溢出和中断:当加法器达到65535(即0xFFFF)时,会产生溢出,并触发中断或其他操作。

中断处理程序可以用于执行特定的任务或重置定时器/计数器的值。

5. 控制寄存器:定时器/计数器的操作可以通过设置相关的控制寄存器来控制,如启动/停止定时器、设置预分频系数等。

6. 应用:定时器/计数器在许多应用中都很有用,如时间延迟、频率测量、事件计数等。

为了充分利用80C51单片机的定时器/计数器功能,通常需要根据实际应用需求配置和控制相应的寄存器,并编写适当的软件来处理定时器和计数器的操作。

串行通信及80C51中的串行端口

串行通信的原理是将待传送的数据按位依次进行传输。在异步通信中,数据以字符为单位进行传送,字符间通过 起始位和停止位进行同步;而在同步通信中,数据以数据块为单位进行传送,通过同步字符或同步信号实现数据 块间的同步。

串行通信协议及标准

协议

串行通信协议规定了数据传输的格式和规则,包括起始位、数据位、校验位和停 止位等。常见的串行通信协议有RS-232、RS-422、RS-485等。

增加信号放大和整形电路

在接收端增加信号放大和整形电路,提高信号的稳定性和可靠性。

实现软件容错机制

在编程时实现软件容错机制,如重发机制、超时处理等,以提高通 信的可靠性。

06 总结与展望

课程总结回顾

1 2

串行通信基本原理

介绍了串行通信的基本概念、工作原理、传输方 式(异步/同步)以及常见的串行通信接口标准 (如RS-232、RS-485等)。

特点

80c51单片机具有高性能、低功耗、易于扩展和低成本等特点。其指令系统丰富,支持位操作,适用 于各种控制领域。

80c51单片机应用领域

工业控制

80c51单片机可用于工业自动化控制 系统中,如温度控制、电机控制、数 据采集与处理等。

智能家居

通过80c51单片机可以实现家居环境 的智能化控制,如灯光控制、窗帘控 制、安防监控等。

标准

串行通信标准规定了信号的电平、传输速率、接口电路等参数。例如,RS-232标准 定义了负逻辑电平,即逻辑“1”对应-3V~-15V的电平,逻辑“0”对应+3V~ +15V的电平;传输速率一般为9600bps、19200bps、38400bps等;接口电路通 常采用DB9或DB25连接器。

串行通信优缺点分析

80C51单片机原理

80C51单片机原理RAM地址寄存器 RAM 128B 程序地址寄存器P0驱动器 P2锁存器 P2驱动器P1锁存器 暂存器2 B 寄存器 4KB ROM暂存器1ACC SP P0锁存器 PC PC 增1 缓冲器 P3锁存器 OSC中断、串行口及定时器PSW ALU DPTRP1驱动器 P3驱动器XTAL1XTAL2 P0.0~P0.7 P2.0~P2.7 P3.0~P3.7 P1.0~P1.7 RST ALEV CCV SS定时控制 指令译码器 指令寄存器 PSEN EA表2-1 P3口各引脚与第二功能表PSW 的各位定义见表80C51 P0~P3接口功能简见大多数口线都有双重功能,介绍如下: 1、P0口具有双重功能:(1) 作为通用I/O ,外接I/O 设备。

(2) 作为地址/数据总线。

在有片外扩展存储器的系统 中,低8位地址和数据由P0口分时传送。

PSW 位地址 PS W.7PSW .6PSW .5 PSW .4 PSW .3 PSW .2 PSW .1 PSW .0 位标志CY ACF0RS1RS0OVF1P2、P1口是唯一的单功能口:作为输入/输出口,P1口的每一位都可作为输入/输出口。

3、P2口具有双重功能:(1)作为输入/输出口。

(2)作为高8位地址总线。

在有片外扩展存储器的系统中,高8位地址由P2口传送。

4、P3口具有双重功能:(1)作第一功能使用时,其功能为输入/输出口。

(2)作第二功能使用时,每一位功能定义如表2.1所示。

80C51单片机的4个I/O口都是8位双向口,这些口在结构和特性上是基本相同的,但又各具特点,以下将分别介绍之。

图2-9 P0口某位的结构图2-10 P1口某位的结构1D CPQQ MUX& T1T2锁存器地址/数据控制信号C V CC内部总线写锁存器读锁存器读引脚P0.X引脚12DCPQQ T锁存器V CC内部总线写锁存器读锁存器读引脚P1.X引脚12图2-11 P2口某位的结构图2-12 P3口某位的结构P0~P3口使用时应注意事项1、如果80C51单片机内部程序存贮器ROM 够用,不需要扩展外部存贮器和I/O接口,80C51的四个口均可作I/O 口使用。

单片机原理与接口技术 80C51 单片机的硬件结构

(2)控制器电路 控制器电路包括程序计数器PC、PC加1寄存器、指令

寄存器、指令译码器、数据指针DPTR、堆栈指针SP、 缓冲器以及定时与控制电路等。控制电路完成指挥控制 工作,协调单片机各部分正常工作。

2. 存储器 80C51单片机的存储器包括数据存储器和程序存储

任一时刻,cpu只能使用其中的一组寄存器,称为当 前工作寄存器组,由程序状态字寄存器PSW中的RS1, RS0位的组合来决定。没有选中的单元也可作为一般的 数寄据存缓器存:使用。系统上电复位时,默认选中第0组寄存器。 1、可用8位地址寻址; 2、在指令中既可用名称表示,也可以使用单元地址表示。

docin/sundae_meng

串行通信接口,可以同时发送和接收数据。

docin/sundae_meng

6. 中断控制系统

80C51共有5个中断源,即外中断2个,定时/计数中断2个, 串行中断1个。

7. 时钟电路

80C51芯片内部有时钟电路,但晶体振荡器和微调电容 必须外接。时钟电路为单片机产生时钟脉冲序列,振荡器的 频率范围为1.2MHz~33MHz,典型取值为6MHz。

器装备、飞机导航系统。 (6)计算机外部设备及电器方面:打印机、硬盘驱动器、

彩色与黑白复印机、磁带机等。 (7)多机分布式系统:可用单片机构成分布式测控系统,

它使单片机应用进入了一个全新的阶段。 (测控系统,智能仪表,智能玩具,计算机外设)

docin/sundae_meng

4.典型单片机产品简介 (1) MCS-51单片机系列

2、位寻址区 在工作寄存器后的16个数据单元(20H~2FH),它

们既可以作为一般的数据单元使用,又可以按位对每个单 元进行操作,因此这16个数据单元又称作位寻址区。位寻 址区共计128位,其位地址为00H~7FH。

第5章 80C51单片机中的输入输出口

一、并行I/O口的功能结构

作为I/O口应用的一个实例,下面介绍80C31 单片机的最小应用系统如下图所示:

80C31

一、并行I/O口的功能结构

二、产生接口控制信号的指令

80C51指令系统中能与接口打交道的指令 大体可分两类:

1、一般的输入/输出指令 2、“读-修改-写”指令

二、产生接口控制信号的指令

发送缓冲器和接收缓冲器共用一个地址,但它 们是独立的物理空间。

二、80C51单片机的串行通信接口

1、 功能特点 3)可用程序控制

内部有专用寄存器SCON(98H)和PCON(87H) 用于控制串行通信,包括方式的选择、接收控制、 多机通信控制、波特率是否加倍等;定时器T1可作 为串行口的波特率发生器,可改变串行口通信的定 时。

P1口一位的结构如下图所示:

一、并行I/O口的功能结构

(一)P1口

1、接口结构

锁存器起输出锁存作用,8位锁存器组成 特殊功能寄存器P1;

场效应管和上拉电阻组成输出驱动器,以 增大负载能力;

三态门1和三态门2分别用于控制输入引脚 和锁存器的状态。

一、并行I/O口的功能结构

2、接口功能

(一)P1口

P1口只有一种功能——通用输入输出接口, 有以下三种工作方式:输出、输入和端口操 作。 (1)输出方式:

二、80C51单片机的串行通信接口

1、功能特点 4)有四种工作方式能适应不同用途 (1)方式0 为移位寄存器I/O方式,数据从RXD端串行输入 或输出,以8位为一帧,按先低位后高位依次传送; 同步信号从TXD端输出,波特率固定为fosc/12。

二、80C51单片机的串行通信接口

1、功能特点 4)有四种工作方式能适应不同用途 (2)方式1 为8位的异步通信接口,传送一帧信息为10位,其 中,1位起始位(0),8位数据位(低位在前),1 位停止位(1)。

80C51的结构和原理-简答题

1、PC机和单片机都是微型机,两者有什么区别?答:PC机和单片机都是微型机,是微型计算机技术发展的两大分支。

PC机以满足海量高速数值计算为主,兼顾控制功能。

单片机以满足测控对象的测控功能,嵌入式应用为主,兼顾数据处理能力。

2、MCS-51单片机的I/O口有什么特点?解:8051单片机的4个I/O口在结构上是基本相同的,但又各具特点。

这四个端口都是8位双向口,每个端口都包括一个锁存器、一个输出驱动器和输入缓冲器。

在无片外扩展存储器的系统中,这四个端口的每一位都可以作为双向通用I/O端口使用。

在作为一般的通用I/O输入时,都必须先向锁存器写入“1”,使输出驱动场效应管FET截止,以免误读数据。

各自特点如下:(1)P0口为双向8位三态I/O口,它既可作为通用I/O口,又可作为外部扩展时的数据总线及低8位地址总线的分时复用口。

作为通用I/O口时,输出数据可以得到锁存,不需外接专用锁存器;输入数据可以得到缓冲,增加了数据输入的可靠性。

每个引脚可驱动8个TTL负载。

(2)P1口为8位准双向I/O口,内部具有上拉电阻,一般作通用I/O口使用,它的每一位都可以分别定义为输入线或输出线,作为输入时,锁存器必须置1。

每个引脚可驱动4个TTL负载。

(3)P2口为8位准双向I/O口,内部具有上拉电阻,可直接连接外部I/O设备。

它与地址总线高8位复用,可驱动4个TTL负载。

一般作为外部扩展时的高8位地址总线使用。

(4)P3口为8位准双向I/O口,内部具有上拉电阻,它是双功能复用口,每个引脚可驱动4个TTL负载。

作为通用I/O口时,功能与P1口相同,常用第二功能。

作为第二功能使用时,各位的作用见教材P.13表1.2.5所示。

3、MCS-51系列单片机的引脚中有多少根I/O线?它们与单片机对外的地址总线和数据总线之间有什么关系?其地址总线和数据总线各有多少位?对外可寻址的地址空间有多大?解:80C51单片机有4个I/O端口,每个端口都是8位双向口,共占32根引脚。

单片机原理与接口技术复习题及答案

复习题及答案(一)一、选择题(在每一个小题四个备选答案中选出一个正确答案,填在题的括号中)1、80C51基本型单片机内部程序存储器容量为(C)。

(A)16K (B)8K (C)4K (D)2K2、在80C51单片机应用系统中,可以作为时钟输出的是(C)引脚。

(A)(B)RST (C)ALE (D)3、在80C51的4个并行口中,能作为通用I/O口和高8位地址总线的是(C)。

(A)P0 (B)P1 (C)P2 (D)P34、当优先级的设置相同时,若以下几个中断同时发生,(D)中断优先响应。

(A)(B)T1 (C)串口(D)T05、在80C51中,要访问SFR使用的寻址方式为(A)。

(A)直接寻址(B)寄存器寻址(C)变址寻址(D)寄存器间接寻址6、以下的4条指令中,不合法的指令为(D)。

(A)INC A (B)DEC A (C)I NC DPTR (D)SWAP ACC7、当需要扩展一片8K的RAM时,应选用的存储器为(B)。

(A)2764 (B)6264 (C)6116 (D)621288、若想扩展键盘和显示,并希翼增加256字节的RAM时,应选择(A)芯片。

(A)8155 (B)8255 (C)8279 (D)74LS1649、80C51单片机要进行10位帧格式的串行通讯时,串行口应工作在(B )。

(A)方式0 (B)方式1 (C)方式2 (D)方式310、80C51复位初始化时未改变SP的内容,第一个入栈的单元地址为(A)。

(A)08H (B)80H (C)00H (D)07H二、填空题1、计算机的经典结构由存储器、运算器、控制器、输入设备、输出设备组成。

2、80C51单片机基本型内部RAM有128 个字节单元,这些单元可以分为三个用途不同的区域,一是工作寄存器区,二是位寻址区,三是数据缓冲区。

3、在8051单片机中,由2 个振荡周期组成1个状态周期,由6 个状态周期组成1个机器周期。

4、8051的堆栈是向地址的高端生成的。

单片机80c51引脚

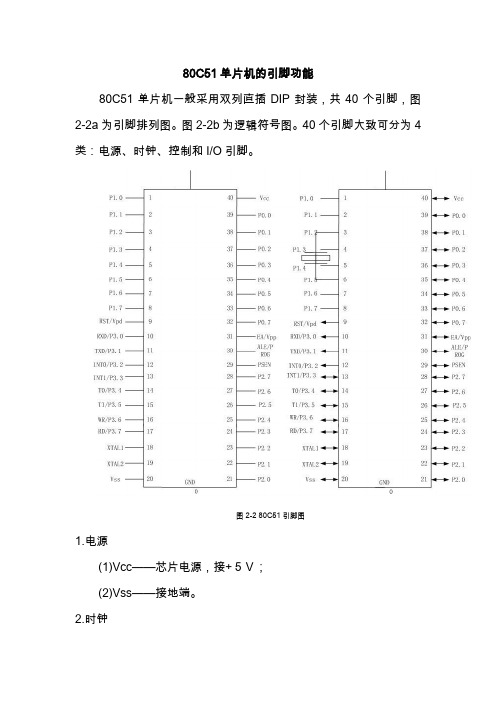

80C51单片机的引脚功能80C51单片机一般采用双列直插DIP封装,共40个引脚,图2-2a为引脚排列图。

图2-2b为逻辑符号图。

40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。

图2-2 80C51引脚图1.电源(1)Vcc——芯片电源,接+5V;(2)Vss——接地端。

2.时钟XTAL1、XTAL2——晶体振荡电路反相输入端和输出端。

使用内部振荡电路时外接石英晶体。

3.控制线控制线共有4根,其中3根是复用线。

所谓复用线是指具有两种功能,正常使用时是一种功能,在某种条件下是另一种功能。

(1)ALE/PROG——地址锁存允许/片内EPROM编程脉冲。

①ALE功能:用来锁存P0口送出的低8位地址。

80C51在并行扩展外存储器(包括并行扩展I/O口)时,P0口用于分时传送低8位地址和数据信号,且均为二进制数。

那么如何区分是低8位地址还是8位数据信号呢?当ALE信号有效时,P0口传送的是低8位地址信号;ALE信号无效时,P0口传送的是8位数据信号。

在ALE信号的下降沿,锁定P0口传送的内容,即低8位地址信号。

需要指出的是,当CPU不执行访问外RAM指令(MOVX)时,ALE以时钟振荡频率1 / 6的固定频率输出,因此ALE信号也可作为外部芯片CLK时钟或其他需要。

但是,当CPU执行MOVX指令时,ALE将跳过一个ALE脉冲。

ALE端可驱动8个LSTTL门电路。

②PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。

(2)PSEN——外ROM读选通信号。

80C51读外ROM时,没个机器周期内PSEN两次有效输出。

PSEN可作为外ROM芯片输出允许OE的选通信号。

在读内ROM 或读外RAM时,PSEN无效。

PSEN可驱动8个LSTTL门电路。

(3) RST/Vpd——复位/备用电源。

①正常工作时,RST(Reset)端为复位信号输入端,只要在该引脚上连续保持两个机器周期以上高电平,80C51芯片即实现复位操作,复位后一切从头开始,CPU从0000H开始执行指令。

大工14秋《单片机原理及应用》在线作业1答案

A. 10H

B. 20H

C. 30H

D. 50H

?

正确答案:B

10.下列不是单片机总线的是()。

A.地址总线

B.控制总线

C.数据总线

D.输出总线

?

正确答案:D

二,判断题

1. P1口的每一位能驱动4个TTL低电平负载。

A. P0

B. P1

C. P2

D. P3

?

正确答案:A

6. 80C51单片机中,晶振频率为12MHz时机器周期为()。

A. 0.5μs

B. 1.0μs

C. 1.5μs

D. 2.0μs

?

正确答案:B

7.若(DPTR)=3000H,(3000H)=30H,执行指令MOVX A,@DPTR后,累加器A的内容为()。

A.错误

B.正确

?

正确答案:B

10. 80C51单片机在芯片内部有128B的掩膜ROM。

A.错误

B.正确

?

正确答案:A

A. 30H

B. 00H

C. 3000H

D. 3030H

?

正确答案:A

8.若(A)=C9H,(R2)=54H,(CY)=1,执行指令SUBB A,R2之后()。

A. (CY)=0,(OV)=0

B. (CY)=0,(OV)=1

C. (CY)=1,(OV)=0

D. (CY)=1,(OV)=1

?

正确答案:B

A.错误

B.正确

?

正确答案:B

6. MCS-51上电复位时,SBUF=00H。

80C51并口结构与操作详解

外部 时钟 信号

内部时钟方式

外部时钟方式

20/43

20

80C51单片机CPU的时钟与时序

80C51的时钟信号

振荡周期:也称时钟周期,是指为单片机提供时钟脉冲 信号的振荡源的周期,TX实验板上为11.0592MHZ。 状态周期:每个状态周期为时钟周期的2倍,是振荡周期 经二分频后得到的。 机器周期:一个机器周期包含6个状态周期S1-S6,也就 是12个时钟周期。在一个机器周期内,CPU可以完成一个 独立的操作。 指令周期:它是指CPU完成一条操作所需的全部时间。每 条指令执行时间都是有一个或几个机器周期组成。MCS51系统中,有单周期指令、双周期指令和四周期指令。

10/43

10

80C51单片机CPU的功能单元

控制器

控制器由指令寄存器IR、指令译码及控制逻辑电

路组成。

指令寄存器IR:执保存当前正在执行的一条指令。 译码与控制逻辑:完成读指令、执行指令、存取操作 数或运算结果等操作,向其他部件发出各种微操作控 制型号,协调各部件的工作。

11/43

11

器)、存储器和I/O口组成。其内部逻辑结构如图 缓冲器 所示。

B寄存器 ACC 暂存器2 ALU 暂存器1 堆栈指示器SP PC加1寄存器 PCON SCON TMODTCON TH0 TL0 TH1 TL1 SBUF SBUF IE (TX) (RX) 中断、串行口和定时器 程序计数器PC

PSEN ALE

内含: CPU 存储器 I/O接口

单片机

3/43

3

回 顾

单片机应用系统开发过程

开发过程(★使用Proteus软件进行电路设计与仿真) 电路板制作

使用Protel99SE软件设计 制版、安装器件、焊接

AT80C51的工作原理

AT80C51的工作原理AT80C51是一款8位微控制器,其工作原理如下:1. 寄存器:AT80C51包含了多个内部寄存器,用于存储数据和控制微控制器的操作。

这些寄存器可以通过特定的地址访问,并且用于存储输入/输出端口、时钟控制、中断向量等信息。

2. CPU:AT80C51的中央处理器(CPU)负责执行指令和处理数据。

它包含一个累加器(ACC)和多个通用寄存器(R0-R7),用于进行算术和逻辑运算。

CPU通过从寄存器中读取数据、执行指令、写入结果来完成计算。

3. 存储器:AT80C51具有内部存储器和外部存储器接口。

内部存储器包括程序存储器(ROM)和数据存储器(RAM)。

ROM用于存储程序指令,RAM用于存储临时数据和变量。

外部存储器接口可以连接额外的存储器设备,以扩展存储容量。

4. 时钟:AT80C51使用时钟来驱动CPU和其他部件的操作。

时钟可以通过内部时钟源或外部时钟源提供。

时钟速度决定了AT80C51的工作频率和指令执行速度。

5. 输入/输出(I/O)端口:AT80C51具有多个可编程输入/输出端口。

这些端口可以连接外部设备,如传感器、显示器、键盘等。

通过读取和写入I/O端口的状态,AT80C51可以与外部设备进行通信。

6. 中断:AT80C51支持中断功能,可以响应外部信号的触发。

当发生中断信号时,CPU会立即暂停当前的任务,并跳转到对应的中断处理程序。

中断可以用于实时响应外部事件,提高系统的实时性能。

总结起来,AT80C51的工作原理是通过CPU执行指令,从寄存器和存储器中读取数据,进行计算和处理,并与外部设备进行通信。

时钟驱动整个系统的运行,而中断机制能够实现实时响应外部事件。

《单片机原理及接口技术》(第二版)余锡存著-课后习题答案

第二章51、87C51、80C51和80C31单片机的主要区别在那里?答:相同之处是:制造工艺都为CHMOS,都有128字节片内RAM、两个定时/计数器、4个8位I/O并行口,一个串行口和5个中断源。

主要区别:①89C51片内4K字节FLASHROM;②87C51片内4K字节EPROM;③80C51片内4K字节掩膜ROM;④80C31片内无程序存储器。

2.MCS-51单片机引脚有多少I/O线?它们和单片机对外的地址总线和数据总线有何关系?答:4个8位I/O并行口,一个串行口;其中P0口为外接程存和数存的地址低8位和数据总线的时分复用接口;其中P2口为外接程存和数存的地址高8位总线接口;其中P1口为真正的用户口线;其中P3口有第2功能;以上4个口线在没有专用功能时,也可以做通用I/O口线用。

3.简述8031片内RAM区地址空间的分配特点。

答:MCS-51 单片机片内RAM 为 256 字节, 地址范围为00H ~FFH, 分为两大部分: 低 128 字节(00H ~7FH )为真正的RAM 区; 高 128 字节(80H ~FFH )为特殊功能寄存器区SFR 。

在低 128 字节RAM 中, 00H ~1FH 共 32 单元是 4 个通用工作寄存器区。

每一个区有 8 个通用寄存器R0~R7。

4. MCS-51单片机由哪几个部分组成。

答:① 一个8位CPU ;② 4KB ROM or EPROM(8031无ROM);③ 128字节RAM 数据存储器;④ 21个特殊功能寄存器SFR ;⑤ 4个8位并行I/O 口,其中P0、P2为地址/数据线,可寻址64KB 程序存储器和64KB 数据存储器;⑥ 一个可编程全双工串行口;⑦ 具有5个中断源,两个优先级,嵌套中断结构;⑧ 两个16位定时器/计数器;⑨ 一个片内振荡器及时钟电路。

5. MCS-51单片机的,,EA ALE PSEN 信号各自的功能是什么?答:都是控制总线① PP V EA /:访问内部程序存储器的控制信号/编程电压输入端。

单片机原理与技术第5章80C51的并行端口

图5-25 P3端口引脚等效电路

5.4.5

•

并行端口特性小结

现在将80C51系列单片机并行I/O端口 的特性总结归纳如下。单片机应用项目开 发人员了解了这些端口特性以后,会对端 口引脚的开发利用和外接电路的设计起到 参考和提示作用。

•

① 4个端口之间,其电路结构均不完 全相同,并且性能和用途也各有侧重。

3.控制(control)

• 控制信息控制输入/输出设备启动或停 止等。

图5-4 80C51与外设之间的接口

5.2.2

• • •

输出

口输出可使用: MOV A,数据 MOV P0,A

•

小程序段:

图5-5 用发光二极管显示输出的数据

5.2.3

•

输入

从并行端口输入数据也是很简单的, 可以直接用MOV指令从指定的端口输入数 据。但由于80C51并行端口的硬件特点, 在从端口输入前,要把端口置为输入方式。 例如:

•

不过,前提是数据锁存器的内容预先 必须设定为“1”,使得输出驱动级对外呈 现高阻抗状态。否则,N-FETl导通后将引 脚电平钳制在低电平上,而不能随着外来 逻辑电平的改变而变化。

•

因此,必须注意,欲从引脚读取输入 信号时,一定事先向锁存器写“1”方可实 现。这也是这种“准双向”端口的一个弱 点。由于仅当从引脚读取输入信号时,才 需要事先做准备动作,因此,这种端口结 构被称为“准双向口”。

•

CMOS单片机的端口引脚也只能提供 几个毫安的输出驱动电流。在驱动LED或 继电器时,一般均需要外加功率驱动器件。 不过,对于近年来出现的一些新型号,其 驱动电流大大增加。

•

例如Philips公司近几年推出的51LPC 系列和LPC900系列的驱动电流均达到 20mA。这使得在驱动LED或小型继电器时, 可免用外接功率器件。

80C51单片机的串行口

80C51单片机的串行口在单片机的世界里,80C51 单片机凭借其稳定性和广泛的应用一直占据着重要的地位。

而串行口作为 80C51 单片机的重要通信接口,发挥着至关重要的作用。

要理解 80C51 单片机的串行口,首先得知道串行通信的概念。

简单来说,串行通信就是数据一位一位地依次传输,相比并行通信,它只需要较少的数据线,这在很多场景下能大大减少硬件成本和布线难度。

80C51 单片机的串行口有 4 种工作方式,分别是方式 0、方式 1、方式 2 和方式 3。

方式 0 是同步移位寄存器输入/输出方式。

在这种方式下,数据以 8 位为一帧,低位在前,高位在后,没有起始位和停止位。

它通常用于扩展并行 I/O 口,例如外接串入并出的移位寄存器 74LS164 或并入串出的移位寄存器 74LS165。

方式 1 是 8 位异步通信方式,波特率可变。

这是最常用的串行通信方式之一。

一帧数据由 1 位起始位(低电平)、8 位数据位(低位在前)和 1 位停止位(高电平)组成。

发送和接收都是通过专门的寄存器来实现的。

方式 2 是 9 位异步通信方式,波特率固定。

一帧数据由 1 位起始位、8 位数据位、1 位可编程的第 9 位数据和 1 位停止位组成。

这种方式常用于多机通信,第 9 位数据可以作为地址/数据的标识位。

方式 3 与方式 2 类似,也是 9 位异步通信方式,但波特率可变。

串行口的波特率是一个非常关键的概念。

波特率决定了数据传输的速度。

在 80C51 单片机中,方式 0 和方式 2 的波特率是固定的,而方式 1 和方式 3 的波特率则是由定时器 T1 的溢出率来决定的。

通过设置定时器 T1 的工作方式和初值,可以得到不同的波特率,以适应不同的通信需求。

在实际应用中,要使用 80C51 单片机的串行口进行通信,还需要对相关的寄存器进行配置。

比如,串行控制寄存器 SCON 用于设置串行口的工作方式、接收/发送控制等;电源控制寄存器 PCON 中的 SMOD 位用于控制方式 1、2、3 的波特率加倍。

80C51 串行口多机通信_单片机原理与接口技术(第2版)_[共4页]

![80C51 串行口多机通信_单片机原理与接口技术(第2版)_[共4页]](https://img.taocdn.com/s3/m/0e3c95cac281e53a5902ff40.png)

80C51系列单片机的串行通信 162 第6章 MOV A , SBUF ;读回复信号CPL A ;回复信号取反JNZ TRLP ;非全0(回复信号≠FFH ,错误),转重发INC R0;全0(回复信号=FFH ,正确),指向下一数据存储单元 CJNE R0, #60H ,TRLP ;判断16个数据发送完否?未完继续 RET乙机程序如下。

RXD2:MOV SCON , #80H;置串行方式2,允许接收MOV PCON , #80H ;SMOD=1MOV R0, #40H ;置接收数据区首地址SETB REN ;启动接收 RWAP :JNB RI , $ ;等待一帧数据接收完毕CLR RI ;清接收中断标志MOV A , SBUF ;读接收数据,并在PSW 中产生接收数据的奇偶值JB P , ONE ;P=1,转另判 JB RB8, ERR ;P=0,RB8=1,接收有错;P=0,RB8=0,接收正确,继续接收RLOP :MOV @R0, A ;存接收数据INC R0 ;指向下一数据存储单元RIT :MOV A , #0FFH ;置回复信号正确FDBK :MOV SBUF , A ;发送回复信号CJNE R0, #50H ,RWAP ;判断16个数据接收完否?未完继续 CLR REN ;16个数据正确接收完毕,禁止接收RET ONE :JNB RB8, ERR ;P=1,RB8=0,接收有错SJMP RIT ;P=1,RB8=1,接收正确,继续接收ERR :CLRA ;接收有错,置回复信号错误标志SJMP FDBK ;转发送回复信号 6.3.4 80C51串行口多机通信80C51串行口的方式2和方式3可用于多机通信。

多机通信有主机和从机之分,是指一台主机和多台从机之间的通信。

主机发送的信息可传送到各个从机,而各从机发送的信息只能被主机接收,从机和从机之间不能进行通信,如图6-13所示。

多机通信的实现主要依靠主、从机之间正确的设置与判断SM2和接收或发送的第9位数据来完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.1

80C51的引脚功能 基本输入/输出功能 简单的人机接口

5.2

5.3

5.4

80C51并行端口的特点

CPU与外设间数据传送的方式

5.5

5.1 80C51的引脚功能

图5-1 PDIP40封装80C51引脚布局图

图5-2 PDIP40封装80C51全功能逻辑地址符号

3.控制(control)

• 控制信息控制输入/输出设备启动或停 止等。

图5-4 80C51与外设之间的接口

5.2.2

• • •

输出

口输出可使用: MOV A,数据 MOV P0,A

•

小程序段:

图5-5 用发光二极管显示输出的数据

5.2.3

•

输入

从并行端口输入数据也是很简单的, 可以直接用MOV指令从指定的端口输入数 据。但由于80C51并行端口的硬件特点, 在从端口输入前,要把端口置为输入方式。 例如:

图5-12 4个显示管的静态LED显示电路

图5-13 8个LED动态显示原理图

•

→7FH→BFH→DFH→EFH→F7H→FBH→FDH→FEH→ 循环

3.用软件译码的8位动态LED显示接口电路

(1)软件译码的动态显示硬件接 口设计

图5-14 8个LED动态显示接口电路

(2)8位动态LED显示程序设计

续表

续表

续表

5.2 基本输入/输出功能

5.2.1 80C51与I/O设备之间 的接口信息

1.数据(data)

• • • ① 数字量。 ② 模拟量。 ③ 开关量。

图5-3 80C51与I/O之间传送的信息

2.状态(status)

• 在输入时,有输入设备是否准备好 (ready)的状态信息;在输出时,有输出 设备是否有空(empty)的状态信息,若 输出设备正在输出,则以忙(busy)指示 等。

•

如果X=0,则=1,N-FETl栅极加高电 平而饱和导通,引脚电平被拉低;如果X=1, 则=0,N-FETl栅极加低电平而截止,引脚 电平被上拉电阻拉高。在分析电路原理时, N沟道场效应管N-FETl在这里可以看做是 人们更熟悉的一只发射极接地的NPN双极 型三极管。

2.从端口引脚输入数据

• CPU经过RP线送来一个“读”脉冲, G2被打开,引脚上的逻辑信号经过G2被传 送到内部数据总线上。

• • • 动态显示程序设计要点如下。 ① 代码转换。 ② 位选码的形成。

图5-15 LED数字显示缓冲区

图5-16 8位动态LED显示子程序流程图

5.4 80C51并行端口的特点

5.4.1 并行端口的内部结构

图5-17 一条端口引脚内部的基本结构模型

图5-18 并行端口模块的基本结构模型

图5-10 8行×4列矩阵式非编码键盘接口电路

• • • •

(2)矩阵式非编码键盘接口及程序设计 ① 子程序 键盘扫描程序中要调用两个子程序。 DIS显示子程序(程序见后面的LED显示子 程序):该程序具有延时功能,其延时时 间为8ms。

5.3.2

7段LED显示

1.7段LED显示器结构与原理

图5-11 7段LED显示器件

表5-3 LED段选码和显示字符之间的关系

显示字符 0 共阴极段 选码 3FH 共阳极段 选码 C0H 显示字符 A 共阴极段 选码 77H 共阳极段 选码 88H

1

2 3 4 5 6 7

06H

5BH 4FH 66H 6DH 7D9H 92H 82H F8H

b

C d E F P .

7CH

39H 5EH 79H 71H 73H 80H

83H

C6H A1H 86H 8EH 82H 7FH

8

9

7FH

6FH

80H

90H

=.

“全灭”

C8H

00H

37H

FFH

2.LED显示器的两种显示方式

(1)LED静态显示方式

•

所谓静态显示就是将N位共阴极LED显 示器的阴极连在一起接地,每一位LED的8 位段选线与一个8位并行口相连,当显示某 一个字符时,相应的发光二极管就恒定地 导通或截止。4个显示管的静态显示电路如 图5-12所示。

(2)LED动态显示方式

• 所谓“动态显示”就是用扫描方式一 位一位地轮流点亮LED显示器的各个位。

•

特点是:将多个7段LED显示器同名端 的段选线复接在一起,只用一个8位I/O端口 控制各个LED显示器公共阴极轮流接地的 方法,逐一扫描点亮,使每个LED显示该 位应当显示的字符。恰当地选择点亮LED 的时间间隔(1ms~5ms),会给人一种 视觉暂停效应,似乎多位LED都在“同时” 显示。

图5-6 利用按钮提供信息输入

图5-7 因抖动产生的信号

图5-8 单片机键输入处理流程图

图5-9 主程序流程图

(1)能实现按键输入并控制几种LED 显示方式的汇编程序如下:

5.3 简单的人机接口

5.3.1 非编码键盘

(1)矩阵式键盘工作原理

图5-19 每条引出脚都有钳位保护二极管

5.4.2

并行端口的工作原理

1.从端口引脚输出数据

• CPU把欲输出的数据“X”(可以为0 或1)放到数据总线上,接着由控制线WL 送来“写”脉冲,将“X”锁入锁存器中, 并且其反相数据立刻呈现到端上,再经过 N-FETl驱动管反相一次把“X”映射到外部 引脚上。

•

不过,前提是数据锁存器的内容预先 必须设定为“1”,使得输出驱动级对外呈 现高阻抗状态。否则,N-FETl导通后将引 脚电平钳制在低电平上,而不能随着外来 逻辑电平的改变而变化。

•

因此,必须注意,欲从引脚读取输入 信号时,一定事先向锁存器写“1”方可实 现。这也是这种“准双向”端口的一个弱 点。由于仅当从引脚读取输入信号时,才 需要事先做准备动作,因此,这种端口结 构被称为“准双向口”。

3.读取端口数据锁存器内容

• 从端口的数据锁存器读回原有的数据。 CPU经过RL线送来一个“读”脉冲,G1被 打开,锁存器的内容经过Q端被转送到内部 数据总线IOD上。

5.4.3

并行端口的操作指令

(1)读锁存器指令

表5-4

具有“读—改—写”功能的指令

类 型

指 令

注 释 ;Pm和A内容按位逻辑“与”,结果送回 Pm(m=0,1,2,3) ;Pm和A内容按位逻辑“或”,结果送回 Pm