电磁兼容在集成电路中的设计应用

电路中的电磁兼容性设计

电路中的电磁兼容性设计电磁兼容性(Electromagnetic Compatibility,缩写为EMC)是指在一定环境中,电子设备能够在互不干扰的条件下协同工作的能力。

在现代社会中,电子设备的普及和使用广泛,因此电磁兼容性设计变得愈发重要。

1. 电磁兼容性的重要性当多个电子设备在相同的频率下共同工作时,电磁相互干扰的问题可能会出现。

例如,在医院的手术室中,存在着大量的医疗设备,如果这些设备之间没有达到良好的电磁兼容性,就可能导致干扰,从而影响医生的工作效率和患者的安全。

因此,电磁兼容性设计对于确保设备的正常运行和人身安全起到至关重要的作用。

2. 电磁兼容性设计的原则为了实现电磁兼容性设计,我们可以遵循以下原则:2.1 分隔与屏蔽为了减少电磁相互干扰,我们可以通过物理分隔和电磁屏蔽来降低信号的传播。

物理分隔可以通过合理布局电路板或设备的方式来实现,以减少同一设备内部的相互干扰。

而电磁屏蔽则使用金属外壳或金属层对电磁场进行阻挡,从而防止电磁泄露和外部干扰。

2.2 压制噪音与干扰源在电路中,存在着各种各样的噪音和干扰源,如电源噪声、开关电流等。

通过采用滤波器、隔离器和衰减器等方法,可以有效地抑制噪音和干扰源的影响,从而降低电磁干扰。

2.3 路径优化与电磁耦合在电路设计中,路径走向和电磁耦合也是需要重点考虑的因素。

通过合理的电路布局和优化路径,可以降低电磁泄露和电磁干扰的风险。

此外,对于有源元件(如晶体管、集成电路等),还可以采取电磁屏蔽和内部接地方式,以减少对周围电路的干扰。

3. 电磁兼容性测试与验证在电磁兼容性设计完成后,还需要进行相应的测试和验证,以确保设计是否符合要求。

这些测试通常包括辐射测试和传导测试。

辐射测试主要是针对设备对周围空间的电磁泄露进行测试,传导测试则是检测设备内部电路对外部电磁干扰的敏感性。

测试结果通常使用规定的电磁兼容性标准进行评估,并根据所在行业或地区的规定,对测试结果进行分析和判定。

集成电路技术发展对电磁兼容的影响

92020年第6期 安全与电磁兼容1 概述集成电路(IC)是电子设备EMC 问题中的关键要素,它们既是干扰源又是被干扰的对象。

尽管半导体器件不受欧洲EMC 指令或FCC 15等EMC 法规约束,但集成电路终端用户将电子设备级的EMC 限制延伸到芯片级,迫使集成电路研发人员在芯片设计之初就必须考虑电磁兼容问题。

同时,随着集成电路的快速发展,MOS 器件尺寸的不断缩小,同一电路或封装内异构功能的集成度以及数据交换速率得到不断提高。

这些技术进步使集成电路可靠性面临巨大挑战,也促进了集成电路电磁兼容技术的快速发展。

40多年来,研究人员和工程师们致力于提高集成电路的电磁兼容性能,不断在测量方法、预测寿命和设计技术等领域展开研究[1],旨在促进低辐射和高抗扰集成电路的发展。

本文是E.Sicard 根据自己在EMC Compo 2019 国际会议(中国海宁市)上的主题演讲整理成文的第一部分;第二部分是“提高集成电路电磁兼容性的研究方法”,将刊登在下一期的“新视角”栏目。

摘要介绍了集成电路制造业发展的主要趋势,包括复杂度、工作频率、器件性能、供电电压以及器件之间数据交换等。

总结了微米级到纳米级CMOS 工艺集成电路性能对应的工艺发展节点,讨论了技术演变对集成电路电磁兼容(EMC)的影响,并基于最近几年发表的一系列学术论文综述了集成电路电磁兼容的研究现状。

关键词集成电路; 电磁兼容; 封装工艺;发展趋势AbstractThis paper presents the major trends in the development of the IC manufacturing industry, which include complexity, operating frequency, device performance, supply voltage, and data exchange between devices. The process development nodes corresponding to the performance of CMOS integrated circuits from micro to nano levels are summarized, the influence of technological evolution on the electromagnetic compatibility (EMC) of integrated circuits is discussed, and the current status of research on EMC of integrated circuits is reviewed through a series of academic papers published in recent years.Keywordsintegrated circuit; electromagnetic compatibility; packaging technology; technological trends集成电路技术发展对电磁兼容的影响The Influence of Integrated Circuit Technology Development onElectromagnetic Compatibility 法国国立应用科学学院1 法国国家科学研究中心系统分析与架构实验室2国防科技大学3艾·西加1 亚历山大·博耶1,2 吴建飞 *,3 郑亦菲3E.Sicard (艾·西加) 法国图卢兹大学教授、IRIT 实验室副研究员、 LURCO 实验室研究总监,EMC Compo 国际研讨会创始人。

集成电路设计中的电磁兼容问题分析

集成电路设计中的电磁兼容问题分析集成电路是现代电子技术中最重要的一个分支,它可以完整地集成了电子器件和电路系统。

由于大多数集成电路的实现方式都是使用半导体材料,从而大大提高了集成度和性能。

但是,集成电路的应用也给当前复杂的电磁兼容问题带来了很大挑战。

本文将介绍集成电路设计中的电磁兼容问题与分析方法。

一、电磁兼容性基本概念电磁兼容性(EMC)是在电磁环境下,电子设备完成预期功能的能力。

其主要内容包括电磁辐射和电磁感应两方面。

电磁辐射是指电子设备在工作中产生的电磁波,它会向周围环境扩散,并对周围电路和上下游电子设备产生干扰。

电磁感应是指电子设备受到来自周围环境电磁波的影响,产生误动作或工作性能降低的现象。

在集成电路设计中,电磁兼容性主要是指电磁辐射问题。

由于集成电路的工作频率越来越高,电磁辐射问题也愈加突出。

为了避免电磁辐射的影响,需要在电路设计阶段考虑电磁兼容性问题,保证集成电路在工作时尽可能避免电磁辐射产生。

二、集成电路电磁兼容性分析1. EM半模式理论EM半模式理论是一种分析电磁辐射问题的方法,它通过对电路结构进行建模和分析,预测电路在工作状态下可能产生的电磁辐射。

EM半模式理论的基本思想是将电路结构看成一组媒介传输线,按照电磁场的分布特点在其上分离出电磁辐射半模式和电磁辐射半模式。

电磁辐射半模式是一种电磁波的传输模式,它在电路结构上分布成某种空间形态,可以通过传输线的辐射电场进行传递。

根据EM半模式理论,当电路结构中存在辐射模式时,电路将具有辐射能力,并能够向周围环境辐射电磁波。

因此,通过分析电路结构上的辐射模式,可以预测电磁辐射的发生情况,有助于进行电磁兼容性设计。

2. 传输线模型集成电路通常采用互联线的形式来实现不同电路之间的连接。

传输线模型是用来分析电路中传输线辐射问题的方法,它主要是通过对电路上的传输线进行建模和分析,来预测电路的辐射情况。

传输线模型的基本思想是将传输线看作是一条具有电容和电感性质的线路,在这条线路上通过电流和电压信号的传输,从而达到不同电路之间的信息交换。

集成电路技术发展对电磁兼容的影响

集成电路技术发展对电磁兼容的影响摘要:但是,随着高科技技术的进步,近年来,集成电路的机会越来越多,但是由于它们的兼容性,只能更快,更有效地使用它们。

本文的底线是内置兼容性的定义和原则,可导致采取措施和解决方案。

为了减少冲击和耦合效应,必须观察喷射功能的科学性和公正性,从而加强集成电路的功能并扩展其功能。

关键词:集成电路技术发展;电磁兼容;影响引言集成电路(IC)是电子设备EMC问题中的关键要素,它既是干扰源又是被干扰的对象。

尽管半导体器件不受欧洲EMC指令或FCC15等EMC法规约束,但集成电路终端用户将电子设备级的EMC限制延伸到芯片级,迫使集成电路研发人员在芯片设计之初就必须考虑电磁兼容问题。

同时,随着集成电路的快速发展,MOS 器件尺寸的不断缩小,同一电路或封装内异构功能的集成度以及数据交换速率不断提高。

这些技术进步使集成电路可靠性面临巨大挑战,也促进了集成电路电磁兼容技术的快速发展。

1行业面临的机遇1)技术正在逐渐增加。

近年来,中国集成电路(芯片)市场的快速发展,加速了该国芯片的产业发展和技术创新。

2)将集成电路的产能转移到中国大陆。

集成电路(供应链)逐渐从美国,日本,欧洲和台湾转移到中国和东南亚,从而使本地企业更容易开发先进技术并获得管理经验,并使自己的企业快速发展。

供应链搬迁的全球趋势为中国大陆的集成电路产业发展提供了新的机会。

中国大陆新电路的逐步建设通过降低成本,扩大产能和提高地域效率为集成电路产业提供了支持,从而为集成电路的发展做出了贡献。

大陆市场旺盛的需求和投资热潮鼓励了集成电路专业人士的发展,这些专业人士为这些行业的发展做出了贡献,并开始对其进行补充。

3)集成电路产线愈加昂贵加剧头部企业集中趋势。

在摩尔定律的推动下,元器件集成度的大幅提高要求集成电路线宽不断缩小,导致生产技术与制造工序愈加复杂,制造成本呈指数级上升趋势。

当技术节点向5纳米甚至更小的方向升级时,普通光刻机受其波长的限制,其精度已无法满足工艺要求。

集成电路中的电磁兼容性问题研究

集成电路中的电磁兼容性问题研究集成电路是现代电子技术的核心部件,随着电子技术的飞速发展,集成电路的尺寸逐渐减小,功能逐渐强大,集成度逐渐提高。

但是,这样的发展也带来了一个重要的问题——电磁兼容性问题。

电磁兼容性问题指一个电子设备在其工作过程中,所产生的电磁干扰是否会影响到周围的其他电子设备,或是容易受到周围其他电子设备产生的电磁干扰,从而导致整个设备的工作受到干扰或是失效。

在集成电路中,电磁兼容性问题极为重要。

因为一块集成电路内部有成千上万个电子器件,而这些电子器件在工作时必然会产生电磁辐射,这些电磁辐射又会互相影响,从而容易导致电磁干扰问题。

电磁兼容性问题的研究是极其重要的,因为不论是在通讯、计算机、汽车、航空航天、医疗等各个领域,都有着大量的电子设备,而这些电子设备的复杂度、功能性和紧密度不断提高,使得电磁干扰问题日益严重,也越来越难解决。

电子设备的电磁兼容性问题主要有两种类型,分别是辐射干扰和传导干扰。

辐射干扰是指电子设备在工作时会产生电场和磁场的辐射,从而对周围的其他电子设备造成影响。

传导干扰则是指电子设备之间通过共同的电源和接地线而发生的相互干扰。

在集成电路中,一些电子器件的小尺寸和高密度集成导致它们之间的距离非常近,存在较大的交互关系,因此电磁干扰问题也日益严重。

为了解决这些问题,需要从设计、加工、测试等多个环节进行综合研究。

集成电路的设计是解决电磁兼容性问题的基础。

设计中需要充分考虑电磁干扰问题,例如通过布线规划来降低干扰噪声、采用屏蔽技术来隔离干扰源以及选用尽可能低的工作电压等措施。

设计中还需要考虑到加工的工艺条件,例如印刷电路板的钻孔、焊接、引线等操作,错误的操作可能会导致电路板的电磁特性或物理尺寸发生变化,进而导致电磁兼容性问题出现。

在测试环节,电磁兼容性问题也需要得到充分关注。

测试需要涉及整个电路,包括其中每一个单独的器件。

提前检测和预防可能出现的电磁干扰问题是必要的,这样可以通过进行更改设计、重新制作电路板或是选择性器件的方式来从根本上解决问题。

集成电路设计中的电磁兼容问题分析与解决

集成电路设计中的电磁兼容问题分析与解决随着科技的不断发展,电子产品已经成为我们生活中的必需品。

而集成电路(Integrated Circuit,IC)也是许多电子产品的核心,它能将数百万个元器件、电路和电源等集成成一个小芯片。

但在集成电路设计中,电磁兼容(Electromagnetic Compatibility,EMC)问题却时常出现,其不仅会影响电路的性能,还会严重威胁电路的安全性。

本文将对集成电路设计中的电磁兼容问题进行分析,并探讨解决方案。

一、电磁兼容问题的意义电磁兼容问题是指在电子产品中,不同电路之间电磁辐射和电磁感应引起的相互影响。

在集成电路设计中,电磁兼容问题的解决是非常重要的,这不仅能保证电路正常运行,还可以防止电路发生故障,甚至发生火灾等安全事件。

由于集成电路中的电流和电压非常小,如果不加以处理,会导致电磁波干扰周围的其他电路,影响设备的正常使用。

而电磁辐射的波长很短,可以穿过铜箔、屏蔽壳等表面屏蔽措施。

因此,彻底解决集成电路中的电磁兼容问题是非常重要的。

二、电磁兼容问题的检测与分析在集成电路设计的过程中,电磁兼容问题的检测与分析是非常关键的步骤。

常用的检测方法包括模拟和数字仿真等。

其中,数字仿真的检测结果更加准确,具有更高的可重复性,因此被广泛采用。

数字仿真中的电磁兼容问题分为导线辐射和共模电磁干扰两种情况。

导线辐射是指在导线上产生的电磁辐射问题,而共模电磁干扰是指当两个电路共用地线时产生的电磁干扰问题。

在数字仿真中,我们可以通过计算电磁波的能量分布、电磁干扰的传输路径、电磁兼容问题的发生概率等多种方式来检测电磁兼容问题。

这些仿真结果可以指导工程师进行电路的设计和优化。

三、电磁兼容问题的解决方案在集成电路设计中,电磁兼容问题的解决方案主要包括两个方面:一是增强电路的抗电磁干扰能力,另一个是减少电路的电磁辐射。

1.增强电路的抗电磁干扰能力在集成电路设计中,可以通过以下措施增强电路的抗电磁干扰能力:(1)引入滤波器。

现代电子电路与系统的分析设计与实现方法

现代电子电路与系统的分析设计与实现方法现代电子电路与系统的分析、设计与实现方法是指在设计电子电路和系统时,采用的一系列技术和工具,以确保电路和系统能够达到设计要求,并满足性能、可靠性和经济性等各方面的需求。

在现代电子技术的快速发展下,电子电路和系统设计面临着越来越多的挑战,因此分析、设计和实现方法变得越来越重要。

下面是一些常用的现代电子电路与系统的分析设计与实现方法:1. 基于硬件描述语言的设计:硬件描述语言(HDL)是一种用来描述电子系统硬件行为的语言。

通过使用HDL,设计人员可以对电路进行更高层次的抽象描述,从而更容易进行电路的分析和验证。

常用的HDL包括VHDL和Verilog。

2.元件级设计:元件级设计是指在电路设计中将电路拆分为可独立分析和设计的基本元件。

通过对各个元件的分析和设计,可以实现对整个电路的分析和设计。

3.数字信号处理(DSP)技术:数字信号处理技术在现代电子电路和系统中应用广泛。

通过使用DSP技术,可以对电路中的信号进行精确和高效的处理,以满足各种应用需求。

4.模拟电路分析与设计:模拟电路的分析与设计主要涉及电路的建模、分析和优化。

通过对电路元器件的特性进行数学建模,可以对电路的行为进行准确的分析,并通过各种优化方法来改进电路的性能。

5.电磁兼容性(EMC)设计:在现代电子电路和系统设计中,电磁兼容性是一个重要的考虑因素。

通过采用适当的布线和屏蔽技术,可以有效地减少电磁干扰和抗干扰能力,提高整个电路系统的EMC性能。

6.集成电路设计:集成电路设计是指将多个电路和系统集成到同一芯片上的设计方法。

通过采用现代的集成电路设计流程和工具,可以实现高度集成、低功耗和高性能的电子系统设计。

7.系统级设计和建模:系统级设计是指对整个电子系统进行高层次的建模和设计。

通过对系统功能、性能和约束进行详细分析和建模,可以优化整个电子系统的设计过程。

8.可靠性设计与分析:在现代电子电路和系统设计中,可靠性是一个重要的考虑因素。

集成电路设计中的电磁兼容性分析

集成电路设计中的电磁兼容性分析随着现代电子设备的普及,人们对电磁兼容性的关注度也日益提高。

电磁兼容性(EMC)是指电子设备在电磁环境下的工作能力,其包括两个方面,即电磁兼容(EMI)和抗干扰(EMS)。

其中,EMI指的是电子设备产生的电磁辐射或传导干扰到其他设备和系统,而EMS则是指电子设备能够在电磁干扰环境下工作正常。

在电子工程中,EMC问题的解决是非常重要的,因为如果电子设备没有EMC,将会对周围的电子设备和系统产生严重的干扰,影响设备的正常工作。

集成电路设计中,电磁兼容性分析尤其重要。

集成电路(IC)是一种电子器件,是许多电子设备的核心部件。

集成电路设计的目标是保证新产品的性能、功能和生产成本。

在设计阶段,确保电磁兼容性可以帮助设计人员预测和解决IC的EMI和EMS问题。

本文将讨论在集成电路设计中,如何进行电磁兼容性分析。

一、减少辐射干扰首先,要减少IC产生的辐射干扰,设计人员需要采取一些措施。

其中,最重要的是结构分析。

设计人员需要分析IC的结构,确定哪些部分更有可能产生辐射干扰。

然后,对这些部分进行优化,找出并消除潜在的干扰源。

此外,布线也是一个重要的方面。

通常情况下,IC的铜层和信号层必须严格分开。

同时,布线也需要尽可能地降低EMI的影响。

例如,在互连线路上,可以采用缠绕在一起的方式,这样可以减少线路之间的EMI。

二、降低传导干扰在集成电路设计中,另一个关键问题是如何降低传导干扰。

传导干扰是指电路之间通过传导方式发生相互干扰。

再次,结构分析和信号线路都是非常关键的。

在结构分析方面,设计人员需要注意两个方面。

首先,不同信号之间应该尽可能远离。

其次,电路的光源和灯光源应该远离敏感器件。

在信号线路方面,设计人员需要采取预防措施来降低传输EMI。

首先,信号线应该尽可能地短,这有助于降低信号线上的电磁辐射。

其次,为了降低传导干扰,可以采用屏蔽线路技术,即在信号线的周围加上屏蔽层,以减少传输时的EMI。

电路设计中的EMC问题与解决方法

电路设计中的EMC问题与解决方法导言在电路设计与开发的过程中,电磁兼容性(Electromagnetic Compatibility,简称EMC)问题是一个必须重视的方面。

EMC问题的存在可能导致电子设备间的互相干扰,甚至造成设备的损坏。

因此,了解EMC问题的原因和解决方法对于电路设计师来说至关重要。

EMC问题的原因1. 电磁辐射(Electromagnetic Radiation):当电流在电路中流动时,会产生磁场,这个磁场会在空间中扩散并形成电磁波。

如果电磁波强度较高,就会造成电磁干扰,影响其他电子设备的正常工作。

2. 电磁感应(Electromagnetic Induction):当设备接收到外部电磁波时,其内部的电子元器件可能产生感应电流,从而引起设备的故障或异常。

3. 外部电压(External Voltages):在电路设计过程中,如果没有正确处理设备外部电源供电、地线引入等问题,外部电压可能会导致电磁兼容性问题。

EMC问题的解决方法1. 接地设计(Grounding Design):合理的接地设计能够有效降低电路的电磁辐射以及电磁感应。

在接地设计中,需要注意将设备的接地点与电源的接地点相连,以保证信号的返回路径更加稳定。

2. 滤波设计(Filtering Design):通过在电路中加入滤波电路,可以降低电磁干扰的频率范围,使设备对外界干扰的影响减小。

滤波器的选择和设计需要根据实际情况进行,合理选择滤波器的参数和频率范围。

3. 屏蔽设计(Shielding Design):通过在电路设计中添加屏蔽罩或屏蔽材料,可以阻挡或吸收外界的电磁波,减少电磁干扰。

在屏蔽设计中,需要注意材料的选择和屏蔽罩的结构设计,以提高屏蔽效果。

4. 引线布局(Routing Layout):电路引线的布局和走线方式也会对电磁兼容性产生影响。

合理布局电路引线,减小引线之间的交叉和谐振现象,可以有效减少电磁辐射和电磁感应。

集成电路设计中的数据通信和网络设计

集成电路设计中的数据通信和网络设计集成电路设计是现代电子工程的核心部分,它涉及到许多不同的领域,其中数据通信和网络设计是至关重要的。

本文将详细讨论这些领域,并提供有关其原理和应用的深入见解。

数据通信数据通信是集成电路设计中的一个关键概念,它涉及到数据的传输和处理。

在集成电路中,数据通信主要通过数字信号进行,这些信号通常是由逻辑门和电路组成的。

数据通信的过程可以分为以下几个步骤:1.数据采集:在集成电路中,数据采集通常涉及到从各种传感器或其他输入设备收集数据。

这些数据可以来自各种不同的来源,例如温度传感器、光线传感器、声音传感器等。

2.数据处理:收集到的数据需要进行处理,以便执行所需的操作。

这可能包括数据转换、滤波、放大、计算等。

数据处理通常由集成电路中的各种逻辑门和电路完成。

3.数据传输:处理后的数据需要传输到其他集成电路或其他设备。

这可以通过各种通信协议和接口实现,例如串行通信、并行通信、USB、以太网等。

4.数据存储:在集成电路中,数据通常需要存储在各种存储设备中,例如RAM、ROM、Flash等。

数据存储允许集成电路在需要时访问和处理数据。

网络设计网络设计是集成电路设计中的另一个关键领域,它涉及到集成电路内部和外部的通信网络。

网络设计的目标是创建一个高效、可靠且可扩展的网络,以支持集成电路中的数据通信和控制信号传输。

1.通信协议:在集成电路设计中,通信协议是定义数据传输和控制信号传输的一组规则和标准。

这些协议可以包括I2C、SPI、UART等,它们允许不同的设备通过串行或并行接口进行通信。

2.网络拓扑:网络拓扑是定义集成电路中通信网络结构的图形表示。

常见的网络拓扑包括总线型、星型、环型和分布式网络。

选择正确的网络拓扑可以提高通信效率和可靠性。

3.网络互联:在集成电路设计中,网络互联涉及到将不同的网络和设备连接在一起,以实现数据和控制信号的传输。

这可以通过各种通信接口和连接器实现,例如光纤、同轴电缆、无线通信等。

集成电路的电磁兼容——低发射、低敏感度技术

集成电路的电磁兼容——低发射、低敏感度技术随着互联网技术的飞速发展和日益普及,电子产品的应用越来越广泛,电磁兼容问题也变得越来越严重,特别是集成电路的电磁兼容问题。

由于集成电路内部集成的数目增大,工作频率逐渐升高,高速电路的电磁辐射和电磁敏感度也变得越来越严重,因此,如何在保证性能的同时,控制电磁辐射和敏感度是电子设计人员亟需解决的难题。

低发射技术低发射技术是指在尽可能不降低集成电路性能的前提下,采取一系列措施降低电路对外界环境的电磁辐射。

主要措施包括:1、减小电路尺寸随着电路尺寸的减小,电磁辐射也会相应降低。

尽可能地减小电路的面积、线路长度和元器件的尺寸,从而减少电磁辐射强度。

2、加强屏蔽采用金属罩、屏蔽盖、屏蔽膜等方法来减小辐射噪声。

金属罩是屏蔽电路最常用的方法之一。

通过在电路周围围上金属罩,可以有效地屏蔽其产生的辐射。

同时,对于一些重要信号的线路,采用单独的金属屏蔽,可以有效地减少干扰。

3、降低信号上升/下降时间信号的上升/下降时间越短,其频谱中高频分量越多,电磁辐射也越强。

因此,采用一些改善上升/下降时间的技术,如缓冲器、扼流圈、瞬态电压抑制器等,可以降低电磁辐射。

4、减小信号频率信号频率越高,电磁辐射也就越大。

因此,采用一些减小信号频率的技术,如分频电路、低通滤波器等,可以有效地减小电磁辐射。

低敏感度技术1、增强静电保护静电是集成电路敏感度问题的主要来源之一。

因此,在设计过程中应该增强静电保护,采用静电保护元器件来保护电路不受静电伤害。

2、加强电源电路设计电源电路的稳定性对于集成电路的干扰抗性非常重要。

因此,在设计过程中应该充分考虑电源电路的稳定性,避免电源电压的波动对电路的影响。

3、增加滤波器添加适当的滤波器,可以减少外界信号对电路的影响。

采用低通滤波器可以减少高频噪声的干扰,采用带通滤波器可以保留需要的信号。

除了降低电磁辐射外,屏蔽也可以有效地减少电路受外界环境干扰的能力。

同样可以采用金属罩、屏蔽盖、屏蔽膜等方法来实现屏蔽。

电磁兼容在电路设计中的原则和方法

电磁兼容在电路设计中的原则和方法电磁兼容设计要求在元器件级、部件级、设备级、系统级都达到互不干扰,正常工作。

元器件、部件级上的电磁干扰主要来自不同的元件之间的电磁耦合,电路设计的任务之一就是要消除元件和部件级上发生的电磁干扰影响。

设备级,系统级所发生的电磁干扰与电子设备所处的电磁环境,各电子设备之间的相互影响,以及电子设备内部的元件和部件之间的电磁耦合有关。

1 电磁兼容的分层设计原则这主要是按照电磁兼容设计的先后顺序来考虑的,从先到后可分为以下几层:(1) 元器件的选择和PCB设计,这是关键的;(2) 接地设计,这是主要的手段。

以上两层如果设计的好,可完成电磁兼容的80%以上的工作。

(3) 屏蔽设计;(4) 滤波设计和瞬态骚扰抑制。

以上两层是辅助手段,多为事后补救措施,也是我们最不提倡的。

(5) 可根据实际电路需要,结合以上几层来综合设计。

2 保证电磁兼容的方法主要根据构成干扰的三要素从下几方面来保证电磁兼容。

2.1 在不同等级上保证电磁兼容1) 从元器件级上来说,当是无源元件时,考虑(1)工作频带以外的元件参数与工作频带上的有很大的区别;(2)插件元件的末端引线有电感存在,当高频时这个电感易发生电磁兼容问题;(3)元件有寄生电容,寄生电感,在电路上表现为分布参数,在分析电路时也要考虑由它带来的等效电路。

当是有源元件时,工作中产生的电磁辐射也会以传导电流的方式成为干扰源,当是非线性元件时还可能发生频谱成分的变化,这种变化也会引起干扰。

2) 从设备级上来说,主要是保证减少对敏感设备的耦合,可考虑(1)增加脉冲前沿时间以减少干扰的频宽;(2)消除电路中震荡器产生的谐波及信号的谐波;(3)限制干扰辐射或消除干扰的传播途径。

3) 从系统级上来说,主要是靠组织或系统工程的方法来保证,因为有可能在单个设备上的电磁兼容得到了改善,但同时却影响了其它设备的工作条件,使得其它设备的性能指标变坏,此时需要从系统上折中考虑,另外,重要的一点是电磁兼容设计必须得到系统总体设计的高度重视。

集成电路电磁兼容性测试与实现

2 标准产生背景

1997年10月,国际电工委员会(IEC)第47A技术分委会下属第九工 作组(WG9)成立,专门负责对各种已建议的测试方法进行分析,最 终出版了针对EMI和EMS的工具箱式的测试方法集合——IEC61967系列 和IEC62132系列标准。

History

第一份IC标准:IEC 60748-3:1986 Analogue integrated circuits

SC47A/WG9成立:1997年

第一份EMC标准:IEC 61967-1:2002 集成电路 150kHz-1GHz电磁辐射的测量 第1部分:通用条件和定义

3 IEC61967 & IEC62132介绍

标准概览:

IEC61967-1与IEC62132-1分别是集成电路EMI和EMS测试的通用条件与定 义,对测试的环境条件、仪器、配置和过程做出了规定。其中,IEC61967-1 对承载待测集成电路的PWB做出了详细的描述,涉及了机械结构、电气特性、 接地、过孔以及电源去耦等细节。

¾北美的汽车工程协会(SAE)建议的使用TEM小室测量集成电路的辐射发射; ¾SAE提出的磁场探头和电场探头表面扫描测量集成电路的辐射发射; ¾荷兰某公司建议的使用工作台法拉第笼(WBFC)进行集成电路传导发射测量; ¾德国标准化组织VDE建议的使用1Ω电阻进行地回路传导电流测量; ¾日本的研究人员建议的使用磁场探头进行传导发射测量; ¾Lubineau和Fiori等人对抗扰度测试方法和试验结果的研究等等。

在给定系统内部的分系统设备及部件相互之间的电磁兼容性。影响系统内 的电磁兼容性的主要因素是耦合。耦合方式有导线间的电感、电容、电场 及磁场耦合,还有系统内公共阻抗耦合及天线与天线之间的耦合。

系统间的电磁兼容性(Inter-system EMC):

电磁兼容电路的设计

射与耦合。 (8) 单面板和双面板用单点接电源和单点接地;电源线、地线尽量粗。

1.2.3 复位引脚:

不恰当的复位将导致MCU工作的紊乱,复位电路不允许受到干扰,独立的复位控制芯片 或低阻抗的复位电阻加上大容量低泄漏,高频反应性能好的陶瓷电容复位电路是较好的 选择。

1.3 电子线路设计一般规则

每种单元都可以描述为接收一个输入信号、并对输入信号进行加 工,然后在输出端输出加工过的信号。

连接每个引脚到地或者到供电电平,以便确保一个可知的逻辑状态。

1.2.2 IRQ口引脚:

IRQ是MCU元件中最敏感的引脚之一。确保与中断请求引脚的任何连线都有瞬时静电放电 保护是非常重要的。在IRQ连线上有双向二极管、TVS或金属氧化变阻器端接通常就足够 了。即便是对价格很敏感的应用,IRQ线上的电阻端接也同样不可缺少。

必须考虑在输入端可能存在的不希望有的信号,也要考虑经过输 入端之外的其它通路进入的无用信号。

最好在输入点上处理这些无用信号。

1.4 其他设计规则:

(1) 去耦 消除公共阻抗耦合有害影响的措施是去耦。去耦滤波器的关键元件

是引线尽可能短的高频电容器。 (2) 隔离 ①注意地环路形成共模骚扰。 ②用隔离变压器切断地环路,最适用于信号不含直流分量时。宽带信

号不宜用它。 在使用隔离变压器时,必须加静电屏蔽并接地,这可减小分布电容,

能降低初次级间传导骚扰。 为了更好地降低分布电容,提高开关变压器的共模抑制性能,可采

用三层屏蔽:第一层屏蔽连接到初级的低电位端;第二层屏蔽连接 到次级的低电位端;中心法拉第屏蔽连接到变压器的外壳及安全地。 ③光电耦合器隔离法。 因输入和输出线性关系差,不宜直接用于模拟信号,但最适于传输 数字信号。用光脉宽调制法,就能传输含直流分量的模拟信号,而 且有优良的线性效果。

集成电路设计中的常见问题及解决方案

集成电路设计中的常见问题及解决方案随着科技的不断发展,集成电路设计在各个行业中扮演着至关重要的角色。

然而,在集成电路设计的过程中,常常会遇到一些问题,这些问题可能会给设计师带来诸多困扰。

本文将会探讨一些在集成电路设计中常见的问题,并提供解决方案,帮助设计师更好地应对这些挑战。

1. 工艺节点选择与优化在集成电路设计中,选择合适的工艺节点对于芯片的性能和功耗至关重要。

然而,面对不断更新的工艺技术和产品要求,设计师常常被困扰于选择合适的工艺节点。

解决这个问题的方法是进行细致的工艺选择和优化分析。

设计师需要考虑的因素包括成本、功耗、性能、可靠性和市场需求。

通过充分了解各种工艺节点的优劣势,并根据产品需求进行权衡,设计师可以选择最佳的工艺节点。

2. 效应晶体管模型选择与建模效应晶体管是集成电路设计中常用的元件,正确选择和建模效应晶体管模型对于设计的准确性至关重要。

在实际设计中,常常会遇到模型的误差以及不足之处,导致设计结果和实际测试结果相差较大。

解决这个问题的方法是通过实验、测量和模拟验证模型的准确性,并根据需要进行修正和优化。

3. 模拟和数字混合信号设计问题集成电路设计中常常需要处理模拟和数字信号的混合设计,但模拟和数字电路的设计方法和要求有很大的差异。

在混合信号设计过程中,常常会遇到模拟和数字之间的干扰、噪声等问题。

解决这个问题的方法是采用合适的布局和布线技术,实施电源和地线的分离,以及进行模拟和数字信号的隔离和滤波等措施。

4. 时序和时钟设计问题在高性能集成电路设计中,时序和时钟设计问题是比较常见的挑战。

时钟信号的稳定性和延迟对于信号的传输速度和电路的工作频率至关重要。

设计师需要注意时钟资源的分配和调度,确保时钟信号稳定、延迟小,并满足设计的时序要求。

此外,也需要注意数据的同步和时序的优化,以避免数据损坏和传输错误。

5. 功耗优化问题随着移动设备的普及,功耗成为了集成电路设计中的重要问题。

功耗的优化需要在设计的各个层次进行考虑。

集成电路设计中的设计方法和策略

集成电路设计中的设计方法和策略集成电路设计是电子工程中的重要分支,它涉及到电路设计、芯片设计、器件设计等多个领域。

随着集成电路技术的进步,设计方法和策略也在不断发展,本文将从三个方面探讨集成电路设计中的设计方法和策略。

一、集成电路设计方法在集成电路设计中,常用的设计方法包括原理图设计、硬件描述语言(HDL)设计和模拟设计等。

原理图设计是一种传统的设计方法,它是通过绘制电路图来完成电路设计的。

这种方法适用于设计简单的电路,但在设计复杂的电路时,容易出现设计错误和调试困难的问题。

HDL设计是一种比较新的设计方法,它是以编程语言的形式来描述电路,可以减少设计错误和提高设计效率。

其中常用的编程语言有Verilog和VHDL等。

相比于原理图设计,HDL设计可以在更高的抽象层次上进行设计,使得设计中的电路结构更清晰、更易于管理。

模拟设计是一种基于仿真器件验证电路功能和性能的设计方法。

在模拟设计中,可以通过仿真器件模拟电路的运行过程,验证电路的正确性和性能指标。

这种方法可以在设计过程中发现电路的潜在问题,并及时纠正。

二、集成电路设计策略在集成电路设计中,有一些常用的设计策略可以帮助设计师快速、高效地完成电路设计。

其中,最常用的策略包括设计复用、规范化设计和设计自动化等。

设计复用是指在设计过程中,复用已经设计好的电路模块。

这种方法可以减少设计时间和成本,并提高电路的可靠性和稳定性。

复用设计的电路模块可以通过电子设计自动化工具进行管理,方便设计师快速选择和调用,提高设计的效率和质量。

规范化设计是指在设计过程中,采用统一的标准和规范进行设计。

这种方法可以减少设计过程中的错误和不必要的重复,提高设计的可维护性和可扩展性。

在设计过程中,可以采用设计模板和设计规范来指导设计师进行设计,使得设计更加标准化和规范化。

设计自动化是指通过电子设计自动化工具完成电路设计的过程。

这种方法可以减少人工干预,提高设计的效率和质量。

在设计过程中,可以采用自动布线、自动布局等工具来完成电路设计,同时也可以采用模拟器件、SPICE仿真等工具来验证电路的正确性和性能。

集成电路设计中的电磁兼容性设计与电磁辐射抑制方法

与集成电路设计中的电磁兼容性设计与电磁辐射抑制方法相关的行业和领域,其核心要素和特征包括微电子技术、电磁场理论、电路设计技术、材料科学以及系统集成技术等。

微电子技术是集成电路设计的基础,它的发展推动了集成度的提高和器件尺寸的减小。电磁场理论为分析和解决电磁兼容性问题提供了理论基础,而电路设计技术则是实现电磁兼容性的关键。材料科学的发展为电磁辐射抑制提供了新的材料和工艺,系统集成技术则关注如何在整体系统层面实现电磁兼容性。

-材料与工艺:新型材料和工艺的不断涌现,对电磁兼容性设计提出了新的要求,如何在设计中充分利用这些新材料和工艺,是一个待解决的问题。

影响行业/领域发展的关键因素包括:

-技术进步:微电子技术的快速发展,推动电磁兼容性设计与电磁辐射抑制方法的研究不断深入。

-市场需求:随着电子产品性能和功能的不断提高,市场对电磁兼容性设计的要求也越来越高。

可能面临的机遇和挑战:

1.机遇:

-国家政策支持:国家对科技创新的大力支持,为电磁兼容性设计与电磁辐射抑制技术的发展提供了良好的外部环境。

-市场需求增长:电子产品性能提升和功能拓展,使得电磁兼容性设计市场需求持续增长。

-技术进步:微电子技术、材料科学等领域突破,为电磁兼容性设计提供了更多可能性。

2.挑战:

七、市场与竞争分析

当前,集成电路设计中的电磁兼容性设计与电磁辐射抑制领域市场现状如下:

市场现状:

-市场规模:随着电子产品种类的不断丰富和性能的不断提高,电磁兼容性设计与电磁辐射抑制市场需求持续增长。

-市场分布:主要集中在北美、欧洲、亚洲等地区,其中我国市场增长迅速。

竞争格局:

-竞争者:包括国际知名企业如英特尔、高通、博通等,以及国内企业如华为、中兴、紫光等。

大规模集成电路设计中的电磁兼容分析

大规模集成电路设计中的电磁兼容分析大规模集成电路(VLSI)设计是现代电子工业发展的基础,它的高集成度以及复杂性,使得电路间的电磁兼容问题日益严重。

电磁兼容问题主要表现为电磁干扰及电磁容忍度,在电路设计中的分析与解决成为关键。

本文将重点探讨大规模集成电路设计中的电磁兼容分析。

一、电磁干扰分析电磁干扰(EMI)是由于电路中的电磁波产生的电流和电压干扰而引起,在VLSI设计中电磁波的传播路径、电源电压及电流等多种因素导致EMI的产生。

EMI可能会影响电路的性能并导致系统故障,所以分析和解决EMI问题非常重要。

在设计VLSI时,如何减少EMI产生?首先,尽量避免时钟信号等重要信号的传输路径过长,减少电路的小回路,避免可能引起的电磁辐射;其次,可以用屏蔽结构或地平面来降低干扰电压及电流的传播;最后,在电路级别可以采用低功率和低速等措施来减少EMI产生。

二、电磁容忍度分析电磁容忍度(EMT)是指电路能够承受的电磁波干扰程度,即可正常工作的电磁环境。

在VLSI设计中,EMT分析包含了电路的抗干扰能力以及外部电磁干扰下的稳定性等。

在EMT分析中,最主要的指标是抗噪声容限(SNR)。

SNR指信号与噪声之间的比值,代表了电路的信号传输准确性。

因此,设计中需要考虑噪声的来源及其幅度,采取相应的措施来提高电路的EMT。

三、改善电磁兼容性的方法为改善电磁兼容性,一些有效的措施和方法:电路层面,通过电导/辐射屏蔽结构的设计,可以降低电磁辐射及电磁波的传播;同时在电路设计过程中加入电容、电感、抑制网络等设备,抵抗EMI干扰,进一步提高电路的EMC性能。

在板级设计阶段,信号接口需采用标准接口标准,同时做好接口板的布线、电源设计等工作,以保证板间层间互不干扰,保证系统工作的稳定性。

四、总结电磁兼容分析是大规模集成电路设计中非常重要的一环。

EMI和EMT都是电磁兼容问题的重要指标,需要通过一系列有效的措施来分析、评估和优化电路的EMC性能,以确保电路的正常、稳定工作。

芯片集成电路电磁兼容测试技术

芯片集成电路电磁兼容测试技术摘要:当今,集成电路的电磁兼容性越来越受到重视,芯片电磁兼容(EMC)技术关乎整机电子系统及其周围电子器件的运行的安全可靠性,电磁兼容性。

电子设备和系统的生产商努力改进他们的产品以满足电磁兼容规范,降低电磁发射和增强抗干扰能力, 集成电路(IC)的电磁兼容性(EMC)的测试方法正受到越来越多的关注,文章基于国内外资料调研和课题组的研究成果, 介绍了器件级(IC)EMC测试方面的发展现状,测试标准,详细介绍了器件级(IC)主要的电磁兼容测试方法。

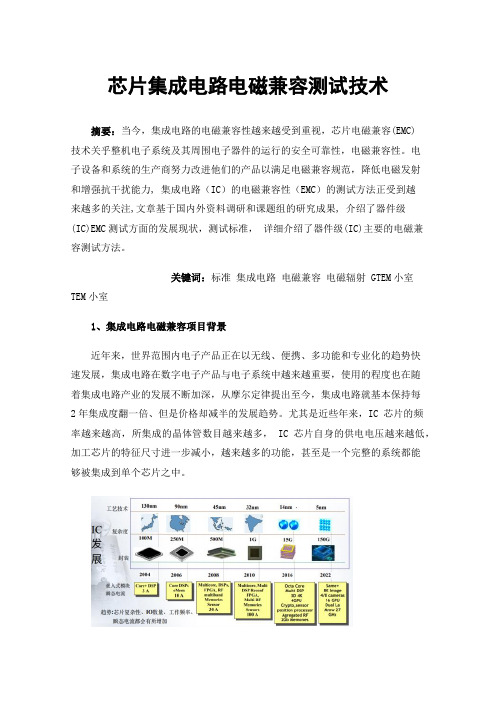

关键词:标准集成电路电磁兼容电磁辐射 GTEM小室TEM小室1、集成电路电磁兼容项目背景近年来,世界范围内电子产品正在以无线、便携、多功能和专业化的趋势快速发展,集成电路在数字电子产品与电子系统中越来越重要,使用的程度也在随着集成电路产业的发展不断加深,从摩尔定律提出至今,集成电路就基本保持每2年集成度翻一倍、但是价格却减半的发展趋势。

尤其是近些年来,IC 芯片的频率越来越高,所集成的晶体管数目越来越多, IC芯片自身的供电电压越来越低,加工芯片的特征尺寸进一步减小,越来越多的功能,甚至是一个完整的系统都能够被集成到单个芯片之中。

图1 IC发展总体趋势图2 IC性能发展趋势根据SEMI的分析报告,全球半导体市场从2015到2025年的预期份额,包括了各类型芯⽚所占的份额。

相⽚2015年的3427亿美元,预计在2025的市场份额将会达到6556亿美元,复合增长率为6.7%。

集成电路的快速发展,这为集成电路的大范围、多层次应用奠定了基础。

尤其在消费类产品领域,这种发展趋势尤为明显,各种数码类产品的普及就是很好的说明。

图3各类型芯⽚所占的份额图4 各尺寸芯⽚所占的份额这种快速发展也造成了电子系统电磁兼容性问题的日益突出,芯⽚复杂性、IO口的数量、⽚作频率、瞬态电流都会有所增加,这些发展均使得芯片级电磁兼容显得尤为突出,更高的集成度和使用密度,是片内和片外耦合的发生几率大大提高。

电子信息工程中的SIP集成电路设计与应用

电子信息工程中的SIP集成电路设计与应用随着科技的不断发展,电子信息工程在现代社会中扮演着重要的角色。

而其中,SIP(System in Package)集成电路的设计与应用更是引人注目。

本文将探讨SIP集成电路在电子信息工程中的重要性,并深入探讨其设计和应用方面的一些关键问题。

一、SIP集成电路的概念与特点SIP集成电路是一种将多个芯片、模块或器件集成在一个封装内的技术。

相比于传统的单芯片封装(CSP)和多芯片模块(MCM)封装,SIP集成电路具有更高的集成度和更小的尺寸。

它将多个功能模块整合在一个封装内,实现了电路的紧凑和高效。

此外,SIP集成电路还具有更好的电磁兼容性和热管理能力,能够提高系统的性能和稳定性。

二、SIP集成电路的设计过程SIP集成电路的设计过程可以分为几个关键步骤。

首先是电路设计,包括功能模块的选择和电路原理图的设计。

在这一步骤中,设计师需要充分了解系统需求,并根据需求选择合适的功能模块。

然后,设计师需要绘制电路原理图,明确各个功能模块之间的连接关系。

接下来是PCB设计,即将电路原理图转化为实际的PCB布局。

在这一步骤中,设计师需要考虑封装的选择、信号的传输和电磁兼容性等因素。

通过合理的布局和层次分割,可以提高电路的性能和可靠性。

最后是封装设计,即将PCB布局转化为实际的封装结构。

在这一步骤中,设计师需要选择合适的封装材料和技术,并进行封装结构的设计和优化。

通过合理的封装设计,可以提高电路的散热性能和可靠性。

三、SIP集成电路的应用领域SIP集成电路在电子信息工程中有着广泛的应用。

首先是通信领域。

SIP集成电路可以实现多个通信模块的集成,提高通信设备的性能和可靠性。

例如,手机中的无线通信模块、GPS模块和传感器模块等都可以通过SIP集成电路实现。

其次是消费电子领域。

SIP集成电路可以实现多个功能模块的集成,提高消费电子产品的性能和功能。

例如,智能手表中的传感器模块、显示模块和通信模块等都可以通过SIP集成电路实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

机电工程技术 !""# 年第 $% 卷第 &" 期

电磁兼容在集成电路中的设计应用

黄明华,周耀坤

(广州市公路交通设施厂, 广东广州

#&"’#" )

摘要: 本文就实际工程中普遍存在的电磁干扰问题,结合电磁兼容思想,从电磁干扰的产生、种类以及耦合途径出发,对集成 电路的电磁兼容性设计方法进行了总结和归纳。 关键词: 电磁兼容;干扰源;耦合;滤波 中图分类号: ()&# 文献标识码: * 文章编号: &""+,+%+! -!""#. &",""’!,"%

;电磁干扰源,是指产生电磁干扰的电

气、电子设备或雷电等自然现象,如:电网的波动、雷 电、继电器的起停、电 机 起 停 、 高 频 时 钟 , 电 路 中 I! J I",

I# J I" 较 大 的 部 位 等

[!]

。耦合表征电路与电路之间电的联

系,即一个电路的电压或电 流 通 过 耦 合 , 使 得 另 一 个 电 路 产生相应的电压或电流,耦 合 起 着 电 磁 能 量 从 一 个 电 路 传 输到另一个电路的作用。 在电磁兼容性理论中把被干扰对象统称为敏感设备 (或敏感器) ,它是对干扰对象 总 称 , 可 以 是 一 个 很 小 的 元 件或一个电路板组件,也可 以 是 一 个 单 独 的 用 电 设 备 甚 至 可以是一个大型系统。电磁干扰通过电路中的耦合途径 (或 称 耦 合 通 道 ) 把 能 量 从 干 扰 源 耦 合 (或 传 输 ) 到 敏 感 设备上。

表示信号源电 压 和 内 阻 , ), 、 -, 表 示 噪 音 电 压 源 和 阻 抗 ,

+. 表示负载阻抗。

通常,当两电路间 形 成 交 链 、 两 电 路 共 用 同 一 电 流 通 路、两个相互靠近的回路以 及 接 触 不 良 或 电 路 寄 生 振 荡 等 产生的噪音给电路引入差模干扰。 共模干扰又成为对 地 干 扰 、 不 平 衡 干 扰 等 , 它 是 相 对 于公共地电位产生的工作信 号 之 外 的 信 号 变 化 , 是 相 对 于 公共电位基准点在接受电路的两个输入端同时出现的干

(低) 图&

(高) 低、高噪音阻抗差模干扰等效电路图

开关操作产生的浪涌以及工 作 产 生 的 交 流 磁 场 , 雷 电 等 均 能引起电子设备供电电源的波动

[#]

。此外,对设备本身而

言,许多电子芯片对电源波 动 相 当 敏 感 , 电 源 干 扰 逐 渐 成 为危害最严重的干扰之一, 因 此 对 于 电 源 的 抗 干 扰 设 计 应 予以充分的重视。 电源抗干扰设计主要有:

’!

机电工程技术 !""# 年第 $% 卷第 &" 期

技术应 用

一般来说电磁干扰 源 分 为 两 大 类 : 自 然 干 扰 源 和 人 为 干扰源。自然干扰源主要来 源 于 大 气 层 的 电 子 噪 音 、 天 电 噪声、地球外噪声、沉积静 电 噪 音 和 雷 电 干 扰 等 。 人 为 干 扰源只要指机械电子设备或 其 他 人 工 装 置 产 生 电 磁 能 量 干 扰,如广播、电视、通信、 雷 达 和 导 航 等 无 线 电 设 备 以 及 架空输电线、照明器具、电动机械、家用电器以及工业、 医用射频等。 研究表明,不管复 杂 系 统 还 是 简 单 装 置 , 任 何 一 个 电 磁干扰的形成必须具备三个 基 本 要 素 : 电 磁 干 扰 源 、 对 电 磁干扰源敏感的接收装置以及电磁耦计中 , 对 应 于 电 磁 干 扰 形 成 的 三 个 基 本 要素,进行硬件抗干扰设计 基 本 思 想 为 : 抑 制 干 扰 源 、 切 断干扰耦合和提高器件抗干扰能力

[$]

,保证电子设备具有

一定的抗电磁干扰能力,在 其 工 况 下 能 正 常 工 作 , 电 子 设 备自身尽可能少对周围其它 设 备 产 生 电 磁 干 扰 , 影 响 其 它 设备正常运行,从而达到电 磁 兼 容 的 理 想 状 态 。 由 于 电 磁 干扰源及电磁干扰现象普遍 存 在 , 如 果 在 一 个 系 统 中 各 种 用电设备能和谐正常工作而 不 致 相 互 发 生 电 磁 干 扰 造 成 性 能改变和损坏,人们就称这 个 系 统 中 所 用 的 设 备 是 相 互 兼 容的。 (& )电源抗干扰设计 在供电电网中,电 网 内 部 的 波 动 、 电 网 短 路 暂 态 过 程 的脉冲,交流传动装置引起 的 谐 波 , 各 种 大 功 率 用 电 设 备

[&]

。 ”

% 电磁干扰源种类

在介绍电磁干扰之 前 先 解 释 几 个 相 关 名 词 : 电 磁 干 扰 指影响或者限制电子设备、 信 息 技 术 设 备 有 效 性 能 正 常 使 用的电磁能量

[&]

&??& 年 英 国 科 学 家 希 维 赛 德 发 表 了 “ 论 干 扰 ” 的 文

章,标志着电磁兼容性研究的开端, &??+ 年英国邮电部门 研究了通信中的干扰问题, 使 电 磁 兼 容 性 研 究 开 始 走 向 工 程化, &+%% 年德国电气工程师协会制订了世界上第一个电 磁 兼 容 性 规 范 @A/"?B? , &+%# 年 美 国 颁 布 了 第 一 个 电 磁 兼 容 性 军 用 规 范 C*D,E,!!# 。 世 界 多 数 发 达 国 家 早 已 开 始 以 法 令 (如 欧 共 体 指 令 ) 、 法 规 (如 : 美 国 F;; 规 程 ) 形 式进行管理控制,在我国电 磁 兼 容 理 论 和 技 术 的 研 究 起 步 较 晚 , 从 &+?$ 年 开 始 陆 续 颁 布 了 一 系 列 有 关 电 磁 兼 容 性 标准和规范。自此以后,电 磁 兼 容 技 术 迅 速 发 展 成 为 非 常 活跃的学科领域之一。

费用将增加 &"" 倍;到用 户 发 现 问 题 后 才 解 决 时 , 费 用 可 能 高 达 &""" 倍 。 而 在 产 品 开 发 阶 段 同 时 进 行 电 磁 兼 容 性 设 计 , 就 可 望 把 ?"GH+"G 的 电 磁 兼 容 性 问 题 解 决 在 产 品 定型之前。只按常规进行产 品 功 能 设 计 , 不 仅 在 技 术 上 带 来一系列的难题,而且还会造成人力、财力的极大浪费。 就产品本身功能和 市 场 占 有 而 言 , 电 磁 兼 容 性 设 计 的 意义也是不可估量的。其一 , 电 子 设 备 工 作 的 可 靠 性 依 赖 于其电磁抗干扰性。电磁兼 容 性 表 征 电 子 设 备 在 电 磁 环 境 中正常工作的能力。其二, 电 子 设 备 国 内 外 市 场 的 开 拓 需 要其具有良好的电磁兼容性 。 电 磁 兼 容 性 达 标 认 证 已 由 一 个国家范围向全球地区发展,成为一个国际标准。其三, 安全因素,存在电磁辐射的 电 子 产 品 可 能 会 引 起 如 设 备 误 操作、通讯设施电磁泄密、电爆装置误爆、误燃等危险。

! 电磁兼容技术的发展

电 磁 兼 容 (/012345678913:2 ;56<73:=:0:3> 简 写 为 /); ) 是指 “设备在共同的电磁环 境 中 能 一 起 执 行 各 自 功 能 的 共 存状态,即该设备不会由于 受 到 处 于 同 一 电 磁 环 境 中 的 其 他设备的电磁发射导致或遭 受 不 允 许 的 降 级 , 它 也 不 会 使 同一电磁环境中其它设备因 受 其 电 磁 发 射 而 导 致 或 遭 受 不 允许的降级

&) 使 用 隔 离 变 压 器 可 将 屏 蔽 层 良 好 接 地

制电网中的干扰信号有较好的效果。

[%]

,并对抑

!) 使 用 电 源 滤 波 器 ; 电 源 滤 波 器 在 一 定 频 率 范 围 内

有一定的抗电网干扰作用,也可以与隔离变压器配合使 用,先用合适的电源滤波器 滤 波 , 然 后 用 隔 离 变 压 器 进 行

$ 电磁兼容的地位及意义

经验证明,如果记 在 产 品 开 发 阶 段 解 决 电 磁 干 扰 问 题 的费用为 & 个单位,那么等 到 产 品 设 计 定 型 后 再 解 决 其 问 题 , 费 用 将 增 加 &" 倍 ; 而 到 产 品 批 量 生 产 后 再 解 决 时 ,

收稿日期: !""# — "& — "%

0$

技 术应用

机电工程技术 !""# 年第 $% 卷第 &" 期

隔离可达到良好的电源滤波 器 效 果 。 如 图 $ 所 示 为 效 果 较 好 的 一 种 交 流 电 源 滤 波 器 , 其 中 &""!’ 电 感 和 "(&!) 电 容 组 成 高 频 滤 波 器 抑 制 高 频 干 扰 ; "(#’ 电 感 和 &"!) 电 容 组成低频滤波器吸收电源电压波形畸变产生的谐波干扰; 压敏电阻 *+ 用于吸收过压干扰。

环路干扰等;对共地阻抗产 生 的 电 磁 干 扰 , 可 以 用 降 低 共 地阻抗的方法,以减少共地阻抗产生的共阻抗耦合。 工作接地按设备工 作 频 率 采 用 不 同 的 接 地 方 式 。 工 作 频 率 低 (小 于 &.’>) 的 设 备 采 用 单 点 接 地 式 , 即 把 整 个 电路系统中的一个结构点看 作 接 地 参 考 点 , 所 有 对 地 连 接 都接到这一点上,并设置一 个 安 全 接 地 螺 栓 ; 多 个 电 路 的 单点接地式又分为串联和并 联 两 种 , 由 于 串 联 接 地 产 生 共 地阻抗耦合,所以低频电路最好采用并联的单点接地形 式。为防止工频和其它杂散电流在信号地线上产生干扰, 信号地线应与功率地线和机壳地线相绝缘。 图 % (串)中所示串联地阻抗耦合时, !&?"&@#&A B "&A