2位10进制计数器

两位十进制计数资料

两位十进制计数器

电路结构及原理

用CD4518完成两位十进制计数,其中第一个十进制计数器接成:IEN端做计数允许端(高电平有效),1CP做计数时钟输入端(上升沿触发有效),进行个位数计数;第二个十进制计数器接成:2CP端做计数允许端(低电平有效),2EN做计数时钟输入端(下降沿触发有效,从第一个十进制计数器的1Q3做进位脉冲提供,异步计数连接方式),进行十进数的计数。

两位计数器输出的8421BCD码直接输入各自的译码驱动芯片CD4511进行译码。

序号元件名称标称参数型号数量。

10进制计数器课程设计

10进制计数器课程设计一、课程目标知识目标:1. 学生能理解10进制计数器的基本概念,掌握10进制数的组成和计数规律。

2. 学生能运用10进制计数器进行数值的加减运算,并正确表达计算过程和结果。

3. 学生了解10进制计数器在日常生活和科学技术中的应用。

技能目标:1. 学生能够独立操作10进制计数器,进行简单的数值计算。

2. 学生通过实际操作,培养观察、分析、解决问题的能力。

3. 学生通过小组合作,提高沟通、协作和团队意识。

情感态度价值观目标:1. 学生对10进制计数器产生兴趣,激发学习数学的积极性。

2. 学生在探索过程中,培养耐心、细致、勇于尝试的精神。

3. 学生认识到数学知识在实际生活中的重要性,增强学以致用的意识。

课程性质:本课程属于数学学科,旨在帮助学生掌握10进制计数器的运用,提高数学运算能力和实际应用能力。

学生特点:四年级学生具有一定的数学基础,好奇心强,喜欢动手操作,但注意力集中时间较短。

教学要求:注重理论与实践相结合,以学生为主体,激发学生兴趣,培养动手操作能力和团队协作精神。

通过分解课程目标为具体的学习成果,使学生在愉快的氛围中掌握知识,提高能力。

二、教学内容1. 引入10进制计数器概念,介绍其在数学运算中的应用。

- 教材章节:第三章《数的认识》- 内容:10进制计数器的定义、计数规律、数位顺序表。

2. 学习10进制计数器的操作方法,进行数值的加减运算。

- 教材章节:第四章《简单的数学计算》- 内容:10进制计数器操作方法、数值加减运算、进位与退位。

3. 实践与应用,运用10进制计数器解决实际问题。

- 教材章节:第五章《生活中的数学》- 内容:运用10进制计数器进行购物找零、时间计算等实际问题的解决。

4. 小组合作,探讨10进制计数器在科学技术领域的应用。

- 教材章节:第六章《数学与科技》- 内容:10进制计数器在计算机、电子设备等领域的应用案例。

教学进度安排:第一课时:引入10进制计数器概念,学习计数规律和数位顺序表。

同步十进制计数器

同步与异 步十进制计数 器的功能和工 作波形相同, 但时钟控制方 式及电路构成 不同。 计数顺序 0 1 2 3 4 5 6 7 8 9 10 计

Q3 0 0 0 0 0 0 0 0 1 1 0

数 器 状 Q2 Q1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 0

本节小结:

计数器是一种应用十分广泛的时序电路,除 用于计数、分频外,还广泛用于数字测量、运算 和控制,从小型数字仪表,到大型数字电子计算 机,几乎无所不在,是任何现代数字系统中不可 缺少的组成部分。 计数器可利用触发器和门电路构成。但在实 际工作中,主要是利用集成计数器来构成。在用 集成计数器构成N进制计数器时,需要利用清零 端或置数控制端,让电路跳过某些状态来获得N 进制计数器。

Q0高 Q1高 Q2高 Q3高 CTT CT74LS161 CO CTP (高位) CR LD D0 D1 D2 D3 1 1 × ×××

1

1

1 × ×××

讨论

将上图中的“161”换成“160”,则构成几进制计数器?

讨论总结

(1)两个十进制计数器级联构成 100 进制计数器。从高位 Q3 Q2 Q1 Q0 读出的是十位数,而从低位 Q3 Q2 Q1 Q0 读出 的是个位数。 (2)两个 4 位二进制计数器级联则构成 8 位二进制计数器, 即 256 进制计数器。从高位 Q3 Q2 Q1 Q0 读出的是高 4 位 二进制数,而从低位 Q3 Q2 Q1 Q0 读出的是低 4 位二进制

方案 2: 用 “160” 的后七个状态 0011 ~ 1001 实现七进制计数。 计数顺序 0 1 2 3 4 5 6 7 8 9 10 计 数 器 状 态 进位输出 Q3 Q2 Q1 Q0 CO 0 0 0 0 0 D3D2D1D0=0011 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 LD = Q3 Q0或CO 0 1 1 1 0 1 0 0 0 0 1 0 0 1 1 0 0 0 0 0

十进制加法计数器

在数字系统中,常需要对时钟脉冲的个数进行计数,以实现测量、运算和控制等功能。

具有计数功能的电路,称为计数器。

计数器是一种非常典型、应用很广的时序电路,计数器不仅能统计输入时钟脉冲的个数,还能用于分频、定时、产生节拍脉冲等。

计数器的类型很多,按计数器时钟脉冲引入方式和触发器翻转时序的异同,可分为同步计数器和异步计数器;按计数体制的异同,可分为二进制计数器、二—十进制计数器和任意进制计数器;按计数器中的变化规律的异同,可分为加法计数器、减法计数器和可逆计数器。

二进制加法计数器运用起来比较简洁方便,结构图和原理图也比其它进制的简单明了,但二进制表示一个数时,位数一般比较长。

十进制是我们日常生活中经常用到的,不用转换,所以设计十进制加法计数器比设计二进制加法计数器应用广泛,加法器是以数据的累加过程,日常生活中,数据的累加普遍存在,有时候需要一种计数器对累加过程进行运算处理,所以设计十进制加法计数器应广大人们生活的需要,对我们的生活有一个积极地促进作用,解决了生活中许多问题,所以会设计十进制加法计数器使我们对数字电路的理论和实践知识的充分结合,也使我们对电子技术基础有了深刻的了解,而且增强了我们对电子技术基础产生了浓厚的兴趣,这次课程设计使我受益匪浅!一、设计题目 (3)二、设计目的 (3)三、设计依据 (3)四、设计内容 (3)五、设计思路 (4)六、设计方案 (7)七、改进意见 (10)八、设计总结 (11)九、参考文献 (12)一、设计题目十进制加法计数器二、设计目的1.学习电子电路设计任务。

2.通过课程设计培养学生自学能力和分析问题、解决问题的能力。

3.通过设计使学生具有一定的计算能力、制图能力以及查阅手册、使用国家技术标准的能力和一定的文字表达能力。

三、设计依据1.用JK触发器组成。

2.实现同步或异步加法计数。

四、设计内容1.复习课本,收集查阅资料,选定设计方案;2.绘制电气框图、电气原理图;3.对主要元器件进行计算选择,列写元器件的规格及明细表;4.设计总结及改进意见;5.参考资料;6.编写说明书。

人教版-十进制计数法教学设计2024-2025学年四年级上册数学

《十进制计数法》教学设计一、核心素养目标1.数感通过对十进制计数法的学习,增强学生对数字大小和数量关系的感知能力,培养数感。

2.逻辑推理引导学生理解十进制计数法的原理和规律,培养逻辑推理能力。

3.应用意识让学生将十进制计数法应用到实际问题中,提高应用意识。

二、教学重点难点1.教学重点认识十进制计数法,理解其计数规则。

掌握十进制计数法中的数位顺序表。

2.教学难点理解十进制计数法的本质和进位规则。

体会十进制计数法在数学和生活中的广泛应用。

三、教学设想以问题导入,激发学生的好奇心和求知欲。

通过实例分析、小组讨论、自主探究等方式,引导学生逐步理解十进制计数法。

利用多媒体课件和实物教具辅助教学,增强直观性和趣味性。

四、教学方法1.问题驱动法提出一系列问题,引导学生思考十进制计数法的特点和应用。

2.直观演示法利用计数器、数位顺序表等教具进行直观演示,帮助学生理解十进制计数法。

3.合作学习法组织学生进行小组合作学习,共同探讨问题,培养合作意识和交流能力。

五、教学准备1.多媒体课件。

2.计数器、数位顺序表等教具。

六、教学课时1课时七、教学过程(一)问题导入(5分钟)1.提出问题:“我们在数数的时候,为什么是十个十个地数,或者一百一百地数呢?”引导学生思考计数方法的规律,引出十进制计数法的话题。

(二)探究新知(20分钟)1.认识十进制计数法讲解十进制计数法的概念:每相邻两个计数单位之间的进率都是十的计数方法叫做十进制计数法。

举例说明十进制计数法在生活中的应用,如人民币的计数、时间的计数等。

利用计数器演示十进制计数法的进位过程,让学生直观感受“满十进一”的规则。

2.学习数位顺序表展示数位顺序表,介绍各个数位的名称和计数单位。

让学生填写数位顺序表,巩固对不同数位的认识。

强调数位顺序表的重要性,它是进行十进制计数的基础。

(三)巩固练习(10分钟)1.完成课本上的“做一做”练习题。

让学生根据十进制计数法进行数的读写和转换。

十进制同步加法计数器

性能测试

测试环境

为保证测试结果的准确性和可靠 性,需要搭建一个标准的测试环 境,包括适当的电源、时钟源、

输入信号和输出负载等。

测试方法

按照规定的测试方法,对计数器的 各项性能指标进行测试,如计数范 围、计数速度、功耗和集成度等。

测试数据记录

详细记录测试过程中的各项数据, 如输入信号的频率、电源电压、输 出信号的状态等。

THANK YOU

感谢各位观看

发。

十进制同步加法计数器是一种同步计数 器,它可以在时钟信号的控制下进行加

法运算,并输出十进制数的计数值。

Hale Waihona Puke 02十进制同步加法计数器的工作原理

同步计数器的概念

同步计数器

一种数字逻辑电路,能够按照给 定的时钟信号进行计数操作。

工作原理

在每个时钟周期内,同步计数器 对输入的时钟信号进行检测,并 根据时钟信号的变化进行计数操 作。

05

十进制同步加法计数器的性能分析

性能指标

计数范围

计数速度

计数器的最大计数值和最小计数值,即其 能计数的十进制数的范围。

计数器完成一次计数操作所需的时间,通 常以纳秒或微秒为单位。

功耗

集成度

计数器在工作过程中消耗的电能,通常以 毫瓦或瓦为单位。

计数器内部电路的规模和复杂度,通常以 门电路的数量来表示。

进位输出

当计数器达到9态时,会产生一个 进位输出信号,表示需要将这个 进位值加到更高位的计数器中。

回零操作

在每个时钟周期结束时,计数 器会自动回零,即回到0态,准

备进行下一次计数操作。

03

十进制同步加法计数器的设计

设计步骤

确定计数器的进制

有时钟使能的两位十进制计数器设计

EDA技术及应用实验报告——有时钟使能的两位十进制计数器设计班级:XXX姓名:XXX学号:XXX一、实验目的:1、学习MAX+PLUSⅡ软件的使用,包括软件安装及基本的使用流程。

2、掌握用原理图输入法设计简单组合电路的方法和详细设计流程。

3、掌握原理图的层次化设计方法。

二、实验原理:频率计的核心元件之一是含有时钟使能及进位扩展输出的十进制计数器。

为此这里拟用一个双十进制计数74390和其它一些辅助元件来完成。

电路原理图应该如图所示。

图中,74390连接成两个独立的十进制计数器,待测频率信号clk通过一个与门进入74390的计数器1的时钟输入端1CLKA,与门的另一端由计数使能信号enb控制:当enb = '1' 时允许计数;enb = '0' 时禁止计数。

计数器1的4位输出q[3]、q[2]、q[1]和q[0]并成总线表达方式即q[3..0],由图3-24左下角的OUTPUT输出端口向外输出计数值,同时由一个4输入与门和两个反相器构成进位信号进入第2个计数器的时钟输入端2CLKA。

第2个计数器的4位计数输出是q[7]、q[6]、q[5]和q[4],总线输出信号是q[7..4]。

这两个计数器的总的进位信号,即可用于扩展输出的进位信号由一个6输入与门和两个反相器产生,由cout输出。

clr是计数器的清零信号。

三、实验内容和步骤:1、打开原理图编辑器,有时钟使能的两位十进制计数器的设计。

2、编译3、波形仿真,由上图仿真得到电路的仿真波形。

由波形图可见,电路的功能完全符合原设计要求:当clk输入时钟信号时,clr信号具有清0功能,当enb为高电平时允许计数,低电平时禁止计数;当低4位计数器计到9的向高4位计数器进位,另外由于图中没有显示高4位计数器计到9,故看不到count的进位信号。

4、引脚锁定并下载。

实验总结通过本实验,学习了有时钟使能的两位十进制计数器原理图输入的设计,进一步熟练掌握了原理图输入设计的方法。

8421十进制加法计数器真值表

这意味着它的输入可以是0到255之间的任何整数。

为了得到真值表,我们可以遍历0到255的所有整数,并计算它们的8421编码。

8421十进制加法计数器的真值表如下:

输入十进制数

8421编码

0

00000000

1Leabharlann 00000001200000010

3

00000011

...

...

255

10111001

8421十进制加法计数器真值表

我们要找出8421十进制加法计数器的真值表。

首先,我们需要理解什么是8421十进制加法计数器。

8421十进制加法计数器是一种电子设备,它使用8421编码来处理十进制数。

8421编码是一种二进制编码方式,其中每一位的权值代表了十进制数中的每一位。

例如,第0位代表十进制的个位,第1位代表十进制的十位,第2位代表十进制的百位,以此类推。

实验2`有时钟输入的两位十进制计数器原理图输入设计

三、实验注意事项 1、输入文件名不能用汉字或关键字、非法字符; 、输入文件名不能用汉字或关键字、非法字符; 2、注意文件在编译连接时的路径; 、注意文件在编译连接时的路径; 3、注意引脚分配与对应的 芯片相匹配; 、注意引脚分配与对应的FPGA芯片相匹配; 芯片相匹配 4、注意信号标号与总路线的表达方式。 、注意信号标号与总路线的表达方式。 四、实验设备 GW48EDA系统,计算机一台,打印机一台 系统, 系统 计算机一台, 五、实验思考 1、用VHDL编写有时钟输入的两位十进制计数器源程序。 编写有时钟输入的两位十进制计数器源程序。 、 编写有时钟输入的两位十进制计数器源程序 2、 对仿真波形结果进行分析。 、 对仿真波形结果进行分析。 3、写出验证性实验报告 、写出验证性实验报告.

图3-4 用74390设计一个有时钟使能的两位十进制计数器原理

图3-5 调出元件74390

图3-6 从Help中了解74390的 详细功能

1、设计电路原理图,频率计的核心元件之一是含有时钟使能及进位扩展输出的十进 、设计电路原理图, 制计数器。为此这里拟用一个双十进制计数74390和其它一些辅助元件来完成。电路 和其它一些辅助元件来完成。 制计数器。为此这里拟用一个双十进制计数 和其它一些辅助元件来完成 原理图如图3-4所示。图中,74390连接成两个独立的十进制计数器,待测频率信号 原理图如图 所示。图中, 连接成两个独立的十进制计数器, 所示 连接成两个独立的十进制计数器 clk通过一个与门进入 通过一个与门进入74390的计数器 的时钟输入端 的计数器1的时钟输入端 通过一个与门进入 的计数器 的时钟输入端1CLKA,与门的另一端由计数使 , 能信号enb控制:当enb = '1' 时允许计数;enb = '0' 时禁止计数。计数器 的4位输出 控制: 时允许计数; 时禁止计数。计数器1的 位输出 能信号 控制 q[3]、q[2]、q[1]和q[0]并成总线表达方式即 并成总线表达方式即q[3..0],由图 左下角的 左下角的OUTPUT输出 、 、 和 并成总线表达方式即 ,由图3-4左下角的 输出 端口向外输出计数值,同时由一个4输入与门和两个反相器构成进位信号进入第 输入与门和两个反相器构成进位信号进入第2个计 端口向外输出计数值,同时由一个 输入与门和两个反相器构成进位信号进入第 个计 数器的时钟输入端2CLKA。 数器的时钟输入端 。 个计数器的4位计数输出是 第2个计数器的 位计数输出是 个计数器的 位计数输出是q[7]、q[6]、q[5]和q[4],总线输出信号是 、 、 和 ,总线输出信号是q[7..4]。这 。 两个计数器的总的进位信号,即可用于扩展输出的进位信号由一个6输入与门和两个 两个计数器的总的进位信号,即可用于扩展输出的进位信号由一个 输入与门和两个 反相器产生, 输出。 是计数器的清零信号 是计数器的清零信号。 反相器产生,由cout输出。clr是计数器的清零信号。 输出 2、计数器电路实现,在此首先从实现图 所示的电路的绘制和测试开始,用鼠标双 所示的电路的绘制和测试开始, 、计数器电路实现,在此首先从实现图3-4所示的电路的绘制和测试开始 击“Enter Symbol”窗中 窗中Symbol Libraries栏的 栏的e:\maxplus2\max2lib\mf的宏功能元 的宏功能元 窗中 栏的 件库,于是可以在Symbol Files栏中看到绝大多数 系列的元件(图3-5)。这些器 栏中看到绝大多数74系列的元件 )。这些器 件库,于是可以在 栏中看到绝大多数 系列的元件( )。 件的详细功能及其它们的逻辑真值表可以通过查阅“ 选项来获得。 件的详细功能及其它们的逻辑真值表可以通过查阅“Help”选项来获得。为了查阅 选项来获得 74390的功能,可如图 所示,在Help菜单中选 的功能, 所示, 菜单中选Old-Style Macrofunctions项,然后 的功能 可如图3-6所示 菜单中选 项 选Counters项。 项

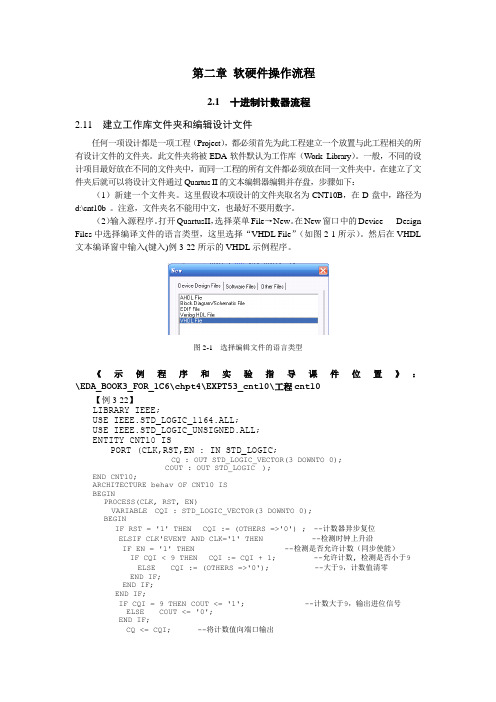

十进制计数器VHDL描述及操作流程6

第二章软硬件操作流程2.1 十进制计数器流程2.11 建立工作库文件夹和编辑设计文件任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有设计文件的文件夹。

此文件夹将被EDA软件默认为工作库(Work Library)。

一般,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

在建立了文件夹后就可以将设计文件通过Quartus II的文本编辑器编辑并存盘,步骤如下:(1)新建一个文件夹。

这里假设本项设计的文件夹取名为CNT10B,在D盘中,路径为d:\cnt10b 。

注意,文件夹名不能用中文,也最好不要用数字。

(2)输入源程序。

打开QuartusII,选择菜单File→New。

在New窗口中的Device Design Files中选择编译文件的语言类型,这里选择“VHDL File”(如图2-1所示)。

然后在VHDL 文本编译窗中输入(键入)例3-22所示的VHDL示例程序。

图2-1 选择编辑文件的语言类型《示例程序和实验指导课件位置》:\EDA_BOOK3_FOR_1C6\chpt4\EXPT53_cnt10\工程cnt10【例3-22】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT (CLK,RST,EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );END CNT10;ARCHITECTURE behav OF CNT10 ISBEGINPROCESS(CLK, RST, EN)VARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST = '1' THEN CQI := (OTHERS =>'0') ; --计数器异步复位ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN = '1' THEN --检测是否允许计数(同步使能)IF CQI < 9 THEN CQI := CQI + 1; --允许计数, 检测是否小于9 ELSE CQI := (OTHERS =>'0'); --大于9,计数值清零END IF;END IF;END IF;IF CQI = 9 THEN COUT <= '1'; --计数大于9,输出进位信号ELSE COUT <= '0';END IF;CQ <= CQI; --将计数值向端口输出END PROCESS;(3)文件存盘。

实验十九。十进制计数器CD4017

实验十九、十进制计数器CD4017逻辑功能测试一、实验目的1、学习用集成触发器构成计数器的方法2、掌握中规模集成计数器的使用及其测试方法3、掌握CD4017计数器的逻辑功能及使用方法二、实验预习要求1、复习有关计数器部分内容2、拟出各实验内容所需的测试记录表格3、查手册,给出并熟悉实验所用各集成的引脚排列及逻辑功能。

三、实验设备与器件1、+5V直流电源2、双踪示波器3、连续脉冲源4、单次脉冲源5、逻辑电平开关6、逻辑电平显示器7、译码显示器8、CD4017B四、实验原理1、计数器是一个用以实现计数功能的时序部件,它不仅可用来计数脉冲数,还常用作数字系统定时、分频和执行数字运算以及其他特定的逻辑功能。

计数器种类很多,按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

2、中规模十进制计数器CD4017B有清除和置数等功能,其引脚排列及逻辑符号如CD4017:十进制计数器/脉冲分配器CD4017 是5 位Johnson 计数器,具有10 个译码输出端,CP、CR、INH 输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH 为低电平时,计Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为解码后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo 电位。

b、CARRY OUT 数器在时钟上升沿计数;反之,计数功能无效。

CR 为高电平时,计数器清零。

CD4017有16支脚,除电源脚VDD及VSS为电源接脚,输入电压范围为3–15V之外,其余接脚为:A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。

两位十进制加法计数器真值表

两位十进制加法计数器真值表引言在数字电路中,计数器是一种非常重要的组件,用于计算和记录输入脉冲的数量。

其中,加法计数器是一种特殊的计数器,它可以实现对输入信号进行加法运算,并输出加法结果。

本文将详细介绍两位十进制加法计数器的真值表及其相关内容。

什么是两位十进制加法计数器?两位十进制加法计数器是一种数字电路组件,用于实现两个十进制数的加法运算。

它由一系列逻辑门和触发器组成,可以将两个十进制数相加,并输出加法结果。

该计数器通常由两个4位二进制加法器和一些辅助逻辑门构成。

两位十进制加法计数器的真值表真值表是一种用于展示逻辑电路输入输出关系的表格。

对于两位十进制加法计数器来说,真值表展示了输入信号和输出结果之间的对应关系。

下面是一个简化的两位十进制加法计数器的真值表:输入A 输入B 进位输出和进位输出0 0 0 00 00 0 1 01 00 1 0 01 00 1 1 10 01 0 0 01 01 0 1 10 01 1 0 10 01 1 1 11 1从上表可以看出,输入A和输入B对应的是两个待相加的十进制数,进位是上一位相加的结果进位,输出和是相加的结果,进位输出表示是否有进位产生。

通过真值表,我们可以清晰地了解两位十进制加法计数器的工作原理和输出结果。

两位十进制加法计数器的工作原理两位十进制加法计数器的工作原理可以通过以下步骤来说明:步骤1:输入信号首先,将待相加的两个十进制数分别输入到两个4位二进制加法器中,并将上一位的进位输入到第一个加法器中。

步骤2:二进制加法两个4位二进制加法器将输入的十进制数转换为二进制,并进行二进制加法运算。

其中,第一个加法器的输出和进位输出作为第二个加法器的输入。

步骤3:输出结果根据两个加法器的输出和进位输出,得到两个十进制数的相加结果和进位输出结果。

步骤4:输出信号将得到的相加结果和进位输出结果输出到外部电路,以供后续处理或显示。

通过以上步骤,两位十进制加法计数器可以实现对两个十进制数的相加操作,并输出相加结果。

两位十进制计数器VHDL.

电子科技大学实验报告学生姓名:范仁森学号:2011032030016 指导教师:杜涛学生姓名:李彦龙学号:2012032030019学生姓名:万金山学号:2011032030030一、实验室名称:计算机大楼309二、实验项目名称:两位十进制计数器在7段数码管显示的设计三、实验原理:用FPGA板上的晶振频率为33.86MHz的时钟进行2的25次方分频作为基准频率,然后用两位十进制计数器计数,计数结果输出至七段数码管显示器的数据端。

再将时钟进行2的19次方分频作为数码管扫描频率,接到数码管的共阴极端。

其中七段数码管由8个(a,b,c,d,e,f,g,dp)按照一定位置排列的发光二极管构成,通常采取共阴极或者共阳极的设计,将8个二极管的同一极接在一起,通过分别控制另外的8个电极的电平,使二极管导通(发光)或截止(不发光)。

四、实验目的:1、掌握七段数码管译码器的工作原理;2、掌握设计两位十进制计数器。

3、学会运用波形仿真测试检验程序的正确性。

五、实验内容:用VHDL设计两位十进制计数器在7段数码管显示的设计,并在VHDL描述的测试平台下对译码器进行功能仿真,给出仿真的波形,并在FPGA板上测试。

六、实验器材(设备、元器件):电脑一台,Active-HDL,30MHz FPGA开发板七、实验步骤:程序:顶层BDE设计U1部分:div25:将晶振信号进行2的25次方分频作为计数基准频率library IEEE;use IEEE.STD_LOGIC_1164.all;use ieee.std_logic_unsigned.all;entity div25 isport(clk : in STD_LOGIC;clr : in STD_LOGIC;div_25 : out STD_LOGIC);end div25;architecture div25 of div25 issignal count:std_logic_vector(24 downto 0);----为分频器设置一个中间信号beginprocess(clk,clr)beginif(clr='1')thencount<="0000000000000000000000000"; ----初始化elsif(clk'event and clk='1')then ----上升延触发if (count="1111111111111111111111111")then ----将时钟频率分频至接近1Hzcount<="0000000000000000000000000";---进位elsecount<=count+1; ---计数end if ;end if;end process;div_25<=count(24);----输出1Hz信号end div25;U3部分:count ---十进制的个位计数器library IEEE;use IEEE.STD_LOGIC_1164.all;use ieee.std_logic_unsigned.all;entity count isport(clk : in STD_LOGIC;clr : in STD_LOGIC;en : in STD_LOGIC;count_4:out std_logic_vector(3 downto 0);cin:out std_logic);end count;architecture count of count issignal count_3:std_logic_vector(3 downto 0); ----计数十位数需要4位2进制begincount_4<=count_3;process(clk,clr)beginif(clr='1')thencount_3<="0000";初始化cin<='0';初始化elsif(clk'event and clk='1')then-----上升沿触发if(en='1')thenif(count_3="1001")then-----进位count_3<="0000";----进位cin<='1';-----输出进位信号elsecount_3<=count_3+1;计数cin<='0';重置进位信号end if;end if;end if;end process;end count;U4部分:count 十进制的十位计数器library IEEE;use IEEE.STD_LOGIC_1164.all;use ieee.std_logic_unsigned.all;entity count isport(clk : in STD_LOGIC;clr : in STD_LOGIC;en : in STD_LOGIC;count_4:out std_logic_vector(3 downto 0);cin:out std_logic);end count;architecture count of count issignal count_3:std_logic_vector(3 downto 0);begincount_4<=count_3;process(clk,clr)beginif(clr='1')thencount_3<="0000";-----初始化cin<='0';elsif(clk'event and clk='1')thenif(en='1')thenif(count_3="1001")then-----十进制计数count_3<="0000";----进位重置cin<='1';----输出进位信号elsecount_3<=count_3+1;-----计数cin<='0';-----进位信号重置end if;end if;end if;end process;end count;U2部分:div19 -----将晶振信号进行2的19次方分频作为扫描频率library IEEE;use IEEE.STD_LOGIC_1164.all;use ieee.std_logic_unsigned.all;entity div19 isport(clk : in STD_LOGIC;clr : in STD_LOGIC;div_19 : out STD_LOGIC);end div19;architecture div19 of div19 issignal count:std_logic_vector(18 downto 0);beginprocess(clk,clr)beginif(clr='1')thencount<="0000000000000000000";-----初始化elsif(clk'event and clk='1')thenif (count="1111111111111111111")thencount<="0000000000000000000";-----进位重置elsecount<=count+1;------计数end if ;end if;end process;div_19<=count(18);-----出接近64Hz的扫描信号end div19;U5部分:mux2----将两位十进制进行扫描输出library IEEE;use IEEE.STD_LOGIC_1164.all;entity mux2 isport(a : in STD_LOGIC;counter1 : in STD_LOGIC_VECTOR(3 downto 0);counter2 : in STD_LOGIC_VECTOR(3 downto 0);dout : out STD_LOGIC_VECTOR(3 downto 0));end mux2;architecture rtl of mux2 isprocess(a,counter1,counter2)beginif (a='0')thendout<=counter1;----输出个位elsif(a='1')thendout<=counter2;------输出十位end if;end process;end rtl;U6部分:decoder -----将两位十进制的数转换为七段显示码输出至显示管library IEEE;use IEEE.STD_LOGIC_1164.all;entity decoder7 isport(din : in STD_LOGIC_VECTOR(3 downto 0);dout : out STD_LOGIC_VECTOR(6 downto 0));end decoder7;architecture rtl of decoder7 issignal indata:std_logic_vector(3 downto 0);indata<=din;----载入数据process(indata)begincase indata iswhen"0000"=>dout<="1111110";------输出0when"0001"=>dout<="0110000";-----输出1when"0010"=>dout<="1101101";-----输出2when"0011"=>dout<="1111001";-----输出3when"0100"=>dout<="0110011";----输出4when"0101"=>dout<="1011011";-----输出5when"0110"=>dout<="0011111";-----输出6when"0111"=>dout<="1110000";-----输出7when"1000"=>dout<="1111111";-----输出8when"1001"=>dout<="1111011";-----输出9when others=>dout<="0000000";-----输出0 end case;end process;end rtl;仿真:在ise上FPGA板上I/O接口选择clk P79, clr P109, en P114, com1 P135, com2 P133,dout1 P138,dout2 P139,dout3 P140,dout4 P141,dout5 P143,dout6 P144,dout7 P146.在ise上继续编译,最后program下载进FPGA。

2位10进制加法计数器课程设计

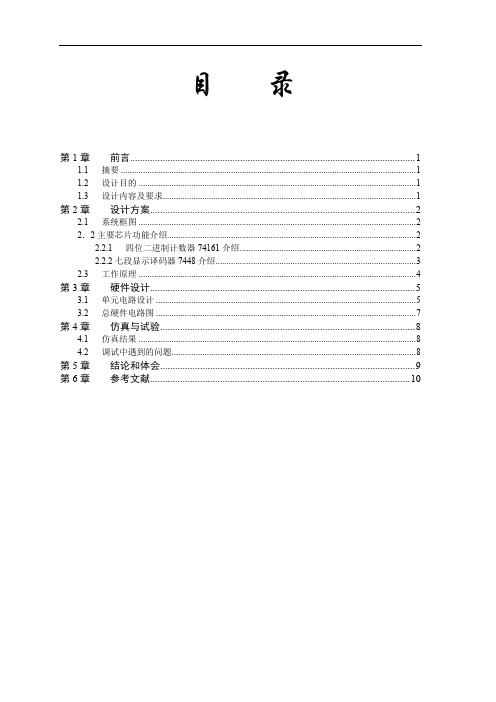

目录第1章前言 (1)1.1 摘要 (1)1.2 设计目的 (1)1.3 设计内容及要求 (1)第2章设计方案 (2)2.1 系统框图 (2)2.2主要芯片功能介绍 (2)2.2.1 四位二进制计数器74161介绍 (2)2.2.2七段显示译码器7448介绍 (3)2.3 工作原理 (4)第3章硬件设计 (5)3.1 单元电路设计 (5)3.2 总硬件电路图 (7)第4章仿真与试验 (8)4.1 仿真结果 (8)4.2 调试中遇到的问题 (8)第5章结论和体会 (9)第6章参考文献 (10)第1章前言1.1 摘要在数字电路技术的课程中,计数器的功能是记忆脉冲的个数,它是数字系统中应用最广泛的基本时序逻辑构件。

计数器在微型计算机系统中的主要作用就是为CPU和I/O设备提供实时时钟,以实现定时中断、定时检测、定时扫描、定时显示等定时控制,或者对外部事件进行计数。

一般的微机系统和微机应用系统中均配置了定时器/计数器电路,它既可当作计数器作用,又可当作定时器使用,其基本的工作原理就是"减1"计数。

计数器:CLK输入脉冲是一个非周期事件计数脉冲,当计算单元为零时,OUT输出一个脉冲信号,以示计数完毕。

本十进制加法计数器是基于74161芯片而设计的,依靠传感器感应外界信号,传感器在感应范围内有物体时输出低电位,反之则是高电位。

当传感器的感应范围内有物体移过时,传感器电位由高到低再到高,出现上跳沿。

计数器会自动加一,并将在数码管上显示。

本十进制加法计数器有两位七段数码管。

可计数0~99个物体,并易于扩展。

该十进制加法计数器设计理念是用于工厂流水线上产品计数,自动计数,方便简单。

1.2 设计目的1、综合运用相关课程中所学到的理论知识去独立完成某一设计课题;2、学习用集成触发器构成计数器的方法;3、进一步熟悉常用芯片和电子器件的类型及特性,并掌握合理选用器件的原则;5、初步了解电路设计、仿真的过程和方法;4、锻炼分析问题解决问题的能力;1.3 设计内容及要求1、具有2位10进制计数功能;2、利用传感器,不接触计数;3、每一个物体经过,计数器自动加1;4、具有显示功能;5、并用相关仿真软件对电路进行仿真。

人教版数学四年级上册《十进制计数法》参考教案二

人教版数学四年级上册《十进制计数法》参考教案二一. 教材分析《十进制计数法》是人教版数学四年级上册的一章内容,主要让学生掌握十进制计数法的概念和应用。

通过本章的学习,学生将能够理解十进制计数法的组成,掌握数的读写方法,以及能够进行简单的数的运算。

二. 学情分析四年级的学生已经具备了一定的数学基础,对于数的读写和基本的运算有一定的了解。

但是,对于十进制计数法的概念和原理还需要通过本节课的学习来掌握。

此外,学生对于抽象的概念可能理解起来有一定的困难,因此需要通过具体的情景和实例来帮助学生理解和掌握。

三. 教学目标1.知识与技能:学生能够理解十进制计数法的概念,掌握数的读写方法,以及能够进行简单的数的运算。

2.过程与方法:学生通过观察、操作、交流等活动,培养数感和逻辑思维能力。

3.情感态度与价值观:学生培养对数学的兴趣和好奇心,培养合作和探究的精神。

四. 教学重难点1.重点:十进制计数法的概念和数的读写方法。

2.难点:十进制计数法的原理和应用。

五. 教学方法采用问题驱动法、情景教学法、合作学习法等教学方法。

通过提问引导学生思考,通过情景和实例帮助学生理解,通过合作学习促进学生交流和探究。

六. 教学准备1.教具:计数器、卡片、投影仪等。

2.学具:练习本、铅笔、橡皮等。

七. 教学过程导入(5分钟)教师通过提问方式引导学生回顾已学的数的读写方法,为新课的学习做好铺垫。

呈现(10分钟)教师通过计数器演示和讲解,向学生介绍十进制计数法的概念和原理。

通过具体的例子,让学生观察和理解十进制计数法的组成和特点。

操练(15分钟)教师给出一些数的读写题目,学生独立完成,然后进行小组讨论和交流。

教师通过提问和解答学生的疑问,帮助学生巩固对十进制计数法的理解和掌握。

巩固(10分钟)教师设计一些数的运算题目,学生独立完成,然后进行小组讨论和交流。

教师通过提问和解答学生的疑问,帮助学生巩固对十进制计数法的理解和掌握。

拓展(10分钟)教师提出一些与十进制计数法相关的问题,引导学生进行思考和探究。

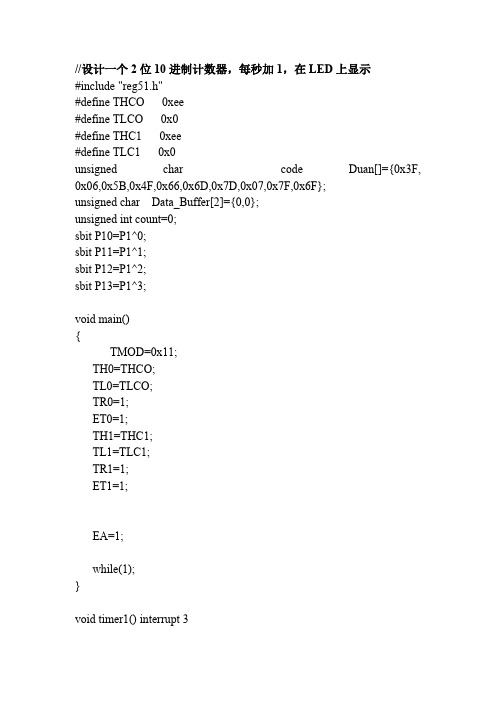

2位10进制计数器

//设计一个2位10进制计数器,每秒加1,在LED上显示#include "reg51.h"#define THCO 0xee#define TLCO 0x0#define THC1 0xee#define TLC1 0x0unsigned char code Duan[]={0x3F, 0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F};unsigned char Data_Buffer[2]={0,0};unsigned int count=0;sbit P10=P1^0;sbit P11=P1^1;sbit P12=P1^2;sbit P13=P1^3;void main(){TMOD=0x11;TH0=THCO;TL0=TLCO;TR0=1;ET0=1;TH1=THC1;TL1=TLC1;TR1=1;ET1=1;EA=1;while(1);}void timer1() interrupt 3{static unsigned char Bit1;TH1=THC1;TL1=TLC1;count++;if(count>200){count=0;Bit1++;if(Bit1>99)Bit1 = 0;Data_Buffer[0]=Bit1/10;Data_Buffer[1]=Bit1%10; }}void timer0() interrupt 1{static unsigned char Bit=0;TH0=THCO;TL0=TLCO;Bit++;if(Bit>=2)Bit=0;P1|=0x0f;P0=Duan[Data_Buffer[Bit]]; switch(Bit){case 0: P10=0;break;case 1: P11=0;break;}}实验5思考题#include "reg51.h"#define THCO 0xee#define TLCO 0x00#define THC1 0xee#define TLC1 0x00unsigned char code Duan[]={0x3F, 0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F};unsigned char Data_number[4]={1,2,3,4};unsigned char Data_time[2]={0,0};sbit P10=P1^0;sbit P11=P1^1;sbit P12=P1^2;sbit P13=P1^3;sbit key=P3^2;int mode=0,Bit1=0,Bit=0;void main(){TMOD=0x11;TH0=THCO;TL0=TLCO;TR0=1;ET0=1;EX0=1;IT0=1;TH1=THC1;TL1=TLC1;TR1=0;ET1=1;EA=1;while(1);}void tans_mode() interrupt 0{int t;if(key==0){for(t=0;t<1000;t++);if(key==0){while(!key);mode++;if(mode==3)mode=0;Bit=0;if(mode==2){TR1=1;Bit1=0;}else{TR1=0;}}}}void timer1() interrupt 3{static unsigned int count=0;TH1=THC1;TL1=TLC1;count++;if(count>200){count=0;Bit1++;if(Bit1>99)Bit1=0;Data_time[0]=Bit1/10;Data_time[1]=Bit1%10; }}void timer0() interrupt 1{TH0=THCO;TL0=TLCO;P1=0x0f;if(mode==0){P0=Duan[0];}if(mode==1){Bit++;if(Bit>=4)Bit=0;P0=Duan[Data_number[Bit]]; }if(mode==2){Bit++;if(Bit>=2)Bit=0;P0=Duan[Data_time[Bit]];}switch(Bit){case 0: P10=0;break; case 1: P11=0;break; case 2: P12=0;break; case 3: P13=0;break; }}。

十进制计数器74hc390

DATA SHEETProduct specificationFile under Integrated Circuits, IC06December 199074HC/HCT390Dual decade ripple counterFor a complete data sheet, please also download:•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications •The IC06 74HC/HCT/HCU/HCMOS Logic Package Information •The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURES•Two BCD decade or bi-quinary counters•One package can be configured to divide-by-2, 4, 5, 10,20, 25, 50 or 100•Two master reset inputs to clear each decade counter individually•Output capability: standard •I CC category: MSI GENERAL DESCRIPTIONThe 74HC/HCT390 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT390 are dual 4-bit decade ripple counters divided into four separately clocked sections. The counters have two divide-by-2 sections and two divide-by-5sections. These sections are normally used in a BCD decade or bi-quinary configuration, since they share a common master reset input (nMR). If the two master reset inputs (1MR and 2MR) are used to simultaneously clear all 8 bits of the counter, a number of counting configurations are possible within one package. The separate clocks (nCP 0and nCP 1) of each section allow ripple counter or frequency division applications of divide-by-2, 4, 5, 10, 20,25, 50 or 100.Each section is triggered by the HIGH-to-LOW transition of the clock inputs (nCP 0and nCP 1). For BCD decade operation, the nQ 0output is connected to the nCP 1 input of, the divide-by-5 section. For bi-quinary decadeoperation, the nQ 3 output is connected to the nCP 0input and nQ 0becomes the decade output.The master reset inputs (1MR and 2MR) are active HIGH asynchronous inputs to each decade counter whichoperates on the portion of the counter identified by the “1”and “2” prefixes in the pin configuration. A HIGH level on the nMR input overrides the clocks and sets the four outputs LOW.QUICK REFERENCE DATAGND =0V; T amb =25°C; t r =t f =6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in µW):P D =C PD ×V CC 2×f i +∑ (C L ×V CC 2×f o ) where:f i =input frequency in MHz f o =output frequency in MHz∑(C L ×V CC 2×f o )=sum of outputs C L =output load capacitance in pF V CC =supply voltage in V 2.For HC the condition is V I =GND to V CCFor HCT the condition is V I =GND to V CC −1.5VSYMBOL PARAMETERCONDITIONSTYPICAL UNITHC HCT t PHL / t PLHpropagation delay C L =15pF; V CC =5VnCP 0 to nQ 01418ns nCP 1 to nQ 11519ns nCP 1to nQ 22326ns nCP 1to nQ 31519ns nMR to Q n1618ns f max maximum clock frequency nCP 0,nCP 16661MHz C I input capacitance3.5 3.5pF C PD power dissipation capacitance per counternotes 1 and 22021pFORDERING INFORMATIONSee“74HC/HCT/HCU/HCMOS Logic Package Information”.PIN DESCRIPTIONPIN NO.SYMBOL NAME AND FUNCTION1, 151CP0, 2CP0clock input divide-by-2 section (HIGH-to-LOW, edge-triggered)2, 141MR, 2MR asynchronous master reset inputs (active HIGH)3, 5, 6, 71Q0 to 1Q3flip-flop outputs4, 121CP1, 2CP1clock input divide-by-5 section (HIGH-to-LOW, edge triggered)8GND ground (0V)13, 11, 10, 92Q0 to 2Q3flip-flop outputs16V CC positive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.Fig.3 IEC logic symbol.Fig.4 Functional diagram.BCD COUNT SEQUENCEFOR 1/2 THE “390”Notes1.Output Q0 connected to nCP1with counter input on nCP0.H=HIGH voltage levelL=LOW voltage levelCOUNTOUTPUTSQ0Q1Q2Q30L L L L1H L L L2L H L L3H H L L4L L H L5H L H L6L H H L7H H H L8L L L H9H L L HBI-QUINARY COUNT SEQUENCEFOR 1/2 THE “390”Note1.Output Q3 connected to nCP0with counter input on nCP1.COUNTOUTPUTSQ 0Q1Q2Q30L L L L1L H L L2L L H L3L H H L4L L L H5H L L L6H H L L7H L H L8H H H L9H L L H Fig.5 Logic diagram (one counter).DC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standardI CC category: MSIAC CHARACTERISTICS FOR 74HCGND=0V; t r=t f=6ns; C L=50pFSYMBOL PARAMETERT amb (°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25−40to+85−40 to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delaynCP0 to nQ0471714145292518036312204438ns 2.04.56.0Fig.6t PHL/ t PLH propagation delaynCP1 to nQ1501814155312619539332354740ns 2.04.56.0Fig.6t PHL/ t PLH propagation delaynCP1 to nQ2742722210423626553453156354ns 2.04.56.0Fig.6t PHL/ t PLH propagation delaynCP1 to nQ3501814155312619539332354740ns 2.04.56.0Fig.6t PHL propagation delaynMR to nQ n 521915165332820541352505043ns 2.04.56.0Fig.7t THL/ t TLH output transition time19767515139519161102219ns 2.04.56.0Fig.6t W clock pulse widthnCP0, nCP1801614197610020171202420ns 2.04.56.0Fig.6t W master reset pulse widthHIGH 8017142810810521181302622ns 2.04.56.0Fig.7t rem removal timenMR to nCP n 75151322869519161102219ns 2.04.56.0Fig.7f max maximum clock pulsefrequencynCP0, nCP16.030352060714.824284.02024MHz 2.04.56.0Fig.6DC CHARACTERISTICS FOR 74HCTFor the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.Output capability: standard I CC category: MSI Note to HCT typesThe value of additional quiescent supply current (∆I CC ) for a unit load of 1 is given in the family specifications.To determine ∆I CC per input, multiply this value by the unit load coefficient shown in the table below.AC CHARACTERISTICS FOR 74HCT GND =0V; t r =t f =6ns; C L =50pFINPUT UNIT LOAD COEFFICIENT nCP 0nCP 1, nMR0.450.60SYMBOLPARAMETERT amb (°C)UNIT TEST CONDITIONS74HCTV CC (V)WAVEFORMS+25−40to +85−40 to +125min.typ.max.min.max.min.max.t PHL / t PLH propagation delay nCP 0 to nQ 021344351ns 4.5Fig.6t PHL / t PLH propagation delay nCP 1 to nQ 122384857ns 4.5Fig.6t PHL / t PLH propagation delay nCP 1 to nQ 230516477ns 4.5Fig.6t PHL / t PLH propagation delay nCP 1 to nQ 322384857ns 4.5Fig.6t PHL propagation delay nMR to nQ n 21364554ns 4.5Fig.7t THL / t TLH output transition time 7151922ns 4.5Fig.6t W clock pulse width nCP 0, nCP 11882327ns 4.5Fig.6t W master reset pulse width HIGH 17102126ns 4.5Fig.7t rem removal time nMR to nCP n 1581922ns 4.5Fig.7f maxmaximum clock pulse frequency nCP 0, nCP 127552218MHz4.5Fig.6AC WAVEFORMS(1)HC: V M=50%; V I=GND to V CC.HCT: V M=1.3V; V I=GND to 3V.Fig.6Waveforms showing the clock (nCP n) to output (nQ n) propagation delays, the clock pulse width, the output transition times and the maximum clock frequency.(1)HC: V M=50%; V I=GND to V CC.HCT: V M=1.3V; V I=GND to 3V.Fig.7Waveforms showing the master reset (nMR) pulse width, the master reset to output (nQ n) propagation delays and the master reset to clock (nCP n) removal time.PACKAGE OUTLINESSee“74HC/HCT/HCU/HCMOS Logic Package Outlines”.。

实验十五集成二~五~十进制计数器的应用

实验十五集成二~五~十进制计数器的应用一、实验目的:1.掌握集成二~五~十进制计数器的逻辑功能;2.学会集成二~五~十进制计数器的应用。

二、实验原理:1.集成二~五~十进制计数器7490简介:集成二~五~十进制计数器内部电路如图1所示,其由四个J、K触发器及控制门电路组成。

其中FF0为T’触发器,在CP0作用下,Q完成一位二进制计数;FF3~FF1组成异步五进制计数器,在CP1作用下,Q3Q2Q1按421码完成五进制计数;在计数基础上,集成计数器还附加S91、S92两个置9功能端和R0l、R02两个置0功能端,当S91S92=1时,计数器Q3Q2Q1Q完成置9功能;S91S92=0、R01R02=1时,计数器Q3Q2Q1Q完成置0功能。

2.集成二~五~十进制计数器7490功能表:3.集成二~五~十进制计数器7490的应用:(1)构成8421BCD十进制加法异步计数器:由于集成二~五~十进制计数器内的二~五进制计数器均为下降沿触发,故在构成十进制计数器时,只需将421码五进制加法计数器的时钟CP1接二进制计数器的输出Q,则当Q从1返回0时,CP1得到下降沿,使Q3Q2Q1进行加1计数,故CP在时钟信号作用下,Q3Q2Q1Q完成8421BCD十进制加法异步计数器功能。

(2)构成5421BCD十进制加法异步计数器:集成二~五~十进制计数器构成5421BCD十进制加法异步计数器连接图如图3所示。

当CP1在时钟信号作用下,Q3Q2Q1按421码完成五进制计数;在Q3从1返回0时,CP得到下降沿Q 0按一位二进制计数;故CP1在时钟信号作用下,QQ3Q2Q1完成5421BCD十进制加法异步计数器功能。

(3)构成模10以内任意进制计数器①反馈置0法:由于集成二~五~十进制计数器具有附加异步“入1”复位端R01、R02,因此在将集成计数器构成模10(8421BCD十进制加法异步计数器、5421BCD十进制加法异步计数器)计数器基础上,适当利用计数器输出反馈回R01、R02,使计数器进入反馈端输出为1状态时,计数器复位,达到改变计数器计数时序,完成模10内任意进制计数功能。