基于FPGA的全数字调制解调技术的研究

基于FPGA和MATLAB的QPSK调制解调硕士学位论文

3)毕业论文须用A4单面打印,论文50页以上的双面打印

4)图表应绘制于无格子的页面上

5)软件工程类课题应有程序清单,并提供电子文档

5.装订顺序

1)设计(论文)

作者签名:日 期:

学位论文原创性声明

本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。本人完全意识到本声明的法律后果由本人承担。

本文首先介绍了QPSK调制解调系统的基本原理,系统主要包括QPSK调制,Costas载波同步环,Gardner位同步环,自适应AGC。并对每个模块做了简单的介绍。然后对每个模块进行理论研究与分析,并进行MATLAB仿真,得到其中一些设计参数。由于整个系统,同步技术占有重要位置,为了突出其重要性,我们对载波同步和位同步进行了详细的理论分析。最后提出了系统的FPGA设计方案。整个系统以ISE10.1为软件开发平台,通过verilog HDL和xilinx公司的ip核进行设计与实现,并对每个模块进行了modelsim仿真,仿真包括功能仿真与时序仿真。最后将设计完的解调模块下载到Spartan 3AN1400的软件无线电开发平台上进行测试,发送信号则通过E4438C产生,测试不同噪声,频偏,时偏的情况下,系统的工作情况。并采用chipscope进行实时观察,获得硬件测试结果。

2)附件:按照任务书、开题报告、外文译文、译文原文(复印件)次序装订

指导教师评阅书

基于FPGA的数字调制解调器设计与实现

基于FPGA的数字调制解调器设计与实现数字调制解调器(Digital Modulation Demodulator)是一种用于数字通信系统中的关键组件,它负责将原始的数字信号转换为适合在传输媒介上传输的调制信号,以及将接收到的调制信号转换回原始的数字信号。

随着通信技术的不断发展,数字调制解调器在无线通信、光纤通信以及卫星通信等领域中起着至关重要的作用。

本文旨在介绍基于FPGA的数字调制解调器的设计与实现过程。

FPGA(Field Programmable Gate Array)是一种集成电路,具有可编程的逻辑门和存储器单元,可以根据需要进行配置和重构,因此非常适合用于数字调制解调器的开发。

首先,我们需要确定使用的调制解调器的类型。

常见的数字调制解调器有幅移键控调制(ASK)、频移键控调制(FSK)、相移键控调制(PSK)以及正交振幅调制(QAM)等。

在设计过程中,我们需要根据实际需求选择合适的调制解调器类型。

接下来,我们需要进行数字信号的调制和解调过程。

调制过程将原始的数字信号转换为调制信号,解调过程将接收到的调制信号还原为原始的数字信号。

对于ASK调制解调器,调制过程可以根据原始数字信号的高低电平分别对应于调制信号的高低幅值。

解调过程则通过比较接收到的调制信号幅值与设定的阈值,将其还原为相应的数字信号。

对于FSK调制解调器,调制过程中,不同频率的载波波形将分别对应于不同的数字信号值。

解调过程中,接收到的调制信号将通过频率检测,还原为对应的数字信号。

对于PSK调制解调器,调制过程中,不同相位的载波波形将分别对应于不同的数字信号值。

解调过程中,接收到的调制信号将通过相位检测,还原为对应的数字信号。

对于QAM调制解调器,调制过程中,将同时利用幅度和相位信息来表示数字信号。

解调过程将通过同时检测接收到的调制信号的幅度和相位信息,还原为相应的数字信号。

最后,我们需要在FPGA上实现数字调制解调器的功能。

FPGA调制解调技术综述

FPGA调制解调技术综述近年来,随着通信技术的飞速发展,FPGA调制解调技术作为一项重要的通信技术应用得到了广泛的关注和研究。

本文将对FPGA调制解调技术进行综述,介绍其概念、特点、应用以及发展趋势。

一、概述FPGA(Field-Programmable Gate Array)调制解调技术是一种利用FPGA芯片实现数字信号的调制和解调的技术手段。

与传统的硬件模块相比,FPGA调制解调技术具有灵活性高、可重构性强、设计周期短、成本低等优点。

它通过对FPGA芯片的可编程性,实现了数字调制解调算法的灵活配置和快速实现。

因此,在无线通信、光纤通信、通信协议等领域均有广泛的应用。

二、FPGA调制解调技术特点1. 灵活性高:FPGA芯片具有良好的模块化特性,可根据实际需求进行灵活配置和组合,实现不同调制解调算法的定制化设计。

2. 可重构性强:由于FPGA芯片可编程性的特点,其调制解调功能可以根据需求进行重构和优化,实现不同通信标准的兼容性。

3. 设计周期短:相对于传统的硬件开发方式,FPGA调制解调技术采用了软件化的设计方法,设计和验证过程更加简便、高效,可以大幅缩短产品开发周期。

4. 成本低:FPGA芯片的价格相对较低,且一块FPGA芯片可以实现多种不同的调制解调算法,有效降低了设备制造成本。

三、FPGA调制解调技术应用1. 无线通信领域:FPGA调制解调技术广泛应用于蜂窝通信、无线局域网(WLAN)、卫星通信、无线传感器网络等无线通信系统中。

通过合理配置FPGA芯片,可以实现多种调制方式(如QAM、PSK、FSK等),提高通信系统的适应性和性能。

2. 光纤通信领域:在光纤通信系统中,FPGA调制解调技术可以用于实现光的相位和强度调制,提高光纤通信的传输容量和速率,同时还可以降低系统的成本和功耗。

3. 通信协议领域:FPGA调制解调技术在通信协议的实现中起到了关键作用。

通过对FPGA芯片的灵活配置,可以实现不同协议的解析和封装,以及数据包的解码和编码等功能,提升了通信系统的稳定性和可扩展性。

基于FPGA的数字信号解调技术研究

基于FPGA的数字信号解调技术研究随着信息技术的快速发展,数字信号处理技术逐渐得到了广泛应用。

在数字通信系统中,数字信号在传输过程中会受到一定的干扰和失真,因此需要利用解调技术对信号进行处理,以保证信息的可靠性和准确性。

基于FPGA的数字信号解调技术是目前应用广泛的一种数字信号处理技术,在本文中我们将介绍其基本原理、技术特点以及应用场景等方面。

一、基本原理FPGA(Field Programmable Gate Array)是一种集成电路芯片,也是目前应用最广泛的一种可编程逻辑器件。

FPGA集成了大量的可编程逻辑单元和存储器单元,并且具有高度的灵活性和可重构性,因此在数字信号处理领域中有着广泛的应用。

数字信号解调是指在数字通信系统中将经过了调制的数字信号解开,以提取其包含的信息内容。

基于FPGA的数字信号解调技术主要利用FPGA芯片的高度可编程性,实现对数字信号的解调和处理。

数字信号通常会被调制成为调幅(AM)、调频(FM)或者相移键控(PSK)等多种形式。

在数字信号解调过程中,需要针对不同的调制方式采用相应的解调算法和技术。

以调幅解调为例,需要将经过调幅调制后的信号,进行解调得到原始信息信号。

解调过程需要用到相干解调、非相干解调、同步解调等多种技术,依据不同的应用需求选择不同的解调方式。

基于FPGA的数字信号解调技术又可以进一步分为软件解调和硬件解调两种方式。

软件解调是指利用软件来实现数字信号解调的技术,可以实现多种不同类型数字信号的解调,但是需要具备较高的算法处理能力和时间复杂度,因此处理速度相对较慢。

硬件解调是指利用FPGA芯片内置的逻辑单元来实现数字信号解调,具有高速、高效的特点,但是需要芯片具备较强的可编程性和逻辑单元的数量足够多。

二、技术特点基于FPGA的数字信号解调技术具有以下几个技术特点:1. 高度可重构性。

FPGA芯片自身具有高度的可编程性,因此可以根据不同的应用需求进行不同的配置和编程。

基于FPGA的数字调制解调器设计.

基·于FPGA的数字调制解调器设计摘要本设计使用FPGA在EDA技术开发软件QuartusⅡ上实现以正弦信号为载波的三种调制信号ASK、FSK、PSK的调制和解调。

系统采用ALTERA公司生产的DE2开发板,Cyclone II EP2C35F672C6型号的FPGA和EPCS16系列的配置驱动,使用VHDL硬件描述语言实现,系统时钟为50MHZ,经四分频产生一路时钟信号经过DDS波形发生器形成ASK,PSK及FSK的一路载波,FSK的另一路载波由系统时钟经八分频后经过DDS波形发生器后产生。

由于ASK和PSK调制特性相近,载波都为一路信号。

因此在设计时将ASK 和PSK调制放在同一模块里设计,用一个选择键和两个基带信号控制端来控制。

系统时钟经过512分频后经过随机信号模块产生一路周期为15的伪随机序列作为数字调制的基带信号。

在解调时,用非相干解调法解调ASK和PSK 信号,用过零检测法解调FSK信号。

经过功能仿真和验证后,测试输出信号与基带信号是否相符。

关键词:FPGA, ASK, PSK, FSKDigital modulation and demodulation based on FPGAAbstractThis design uses FPGA on EDA technology development platform QuartusⅡto achieve the generation and the demodulation of three modulation signal——ASK,FSK,PSK as carrier through sinusoidal signals.The system uses the ALTERA company's DE2 development board,FPGA of Type Cyclone II EP2C35F672C6FPGA and driver configuration of EPCS16 series.This system is realized in VHDL hardware description language,whose ASK,PSK and FSK carrier is generated when the four frequency produces a clock signal through the DDS waveform generator,and the system clock is 50MHZ.Because the characteristics of ASK and PSK modulation are similar to each other,which means their carrier are both one way signal,the modulation of ASK and PSK are put on the same model when designed,with a selection key and the two baseband signal control ends controlling.System clock generates pseudo random sequence baseband signals whose one road cycle is 15 as baseband signals through random signal model after the 512 frequency division.When in modulation,we use non coherent demodulation to demodulate ASK and PSK signal,and the zero crossing detection method for FSK signal demodulation.After the system is tested through the function simulation and verification,whether the output signal and the baseband signal are conformed to each other or not will be testedKey words: FPGA, ASK, PSK, FSK目录1 绪论 (1)1.1课题背景与研究现状 (1)1.1.1数字调制解调背景知识 (1)1.1.2 FPGA背景知识 (2)1.2课题的主要研究工作 (4)1.3本论文的结构 (4)2.EDA技术简介 (6)2.1Q UARTUS II简介 (6)2.1.1 Quartus II的使用及主要设计流程 (7)2.1.2 Quartus II的原理图输入设计流程 (10)2.1.2 SignalTap II逻辑分析仪的使用 (11)2.2VHDL语言简介 (13)2.2.1 VHDL的基本结构 (14)2.2.2 VHDL的基本语法 (19)3.数字调制解调原理 (21)3.1ASK的调制与解调 (21)3.1.1 ASK调制原理 (21)3.1.2 ASK解调原理 (23)3.2PSK的调制与解调 (23)3.2.1 PSK调制原理 (23)3.2.2 PSK解调原理 (25)3.3FSK的调制与解调 (26)3.3.1 FSK调制原理 (26)3.3.2 FSK解调原理 (28)4硬件模块方案设计与实现 (30)4.1DDS(直接数字式频率合成器) (30)4.1.1 DDS原理 (30)4.1.2硬件模块设计图 (31)4.1.3 频率控制模块 (32)4.1.4 波形选择模块 (32)4.1.5 波形存储模块 (33)4.1.6 顶层实体模块 (33)4.1.7 程序及仿真结果分析 (34)4.2 M序列发生器 (35)4.2.1 m序列原理 (35)4.2.2 m序列发生器设计 (37)4.2.3 m序列产生模块 (40)4.2.4 m序列仿真结果分析 (40)4.3分频器设计 (41)4.4ASK/PSK调制与解调 (42)4.4.1 ASK/PSK调制方案 (42)4.4.2 ASK/PSK调制模块 (43)4.4.3 ASK/PSK调制仿真结果分析 (43)4.4.4 ASK/PSK解调方案 (44)4.4.5 ASK/PSK解调模块 (45)4.4.6 ASK/PSK解调仿真结果分析 (46)4.5FSK调制与解调 (47)4.5.1 FSK调制方案 (47)4.5.2 FSK调制模块 (48)4.5.3 FSK仿真结果分析 (48)4.5.4 FSK解调方案 (49)4.5.5 FSK解调模块 (50)4.5.6 FSK解调仿真结果分析 (50)5 系统调试 (51)5.1系统电路图 (51)5.2系统仿真结果 (51)结论 (54)致谢 (55)参考文献 (56)附录:源代码 (46)外文资料翻译(附原文) ........................... 错误!未定义书签。

基于FPGA的QPSK高速数字调制系统的研究与实现

基于FPGA的QPSK高速数字调制系统的研究与实现摘要:介绍了一种基于FPGA的QPSK的高速数字调制系统的实现方案。

先从调制系统的基本框图入手,简要介绍其实现原理及流程;然后着重介绍FPGA功能模块的软件编程、优化及整个系统的性能。

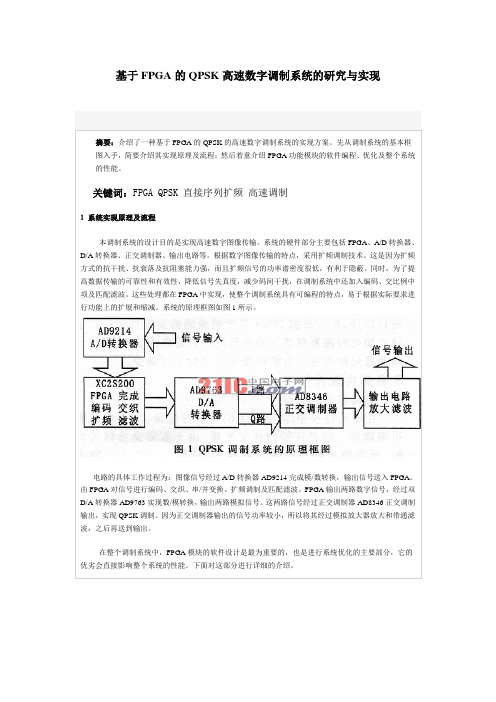

关键词:FPGA QPSK 直接序列扩频高速调制1 系统实现原理及流程本调制系统的设计目的是实现高速数字图像传输。

系统的硬件部分主要包括FPGA、A/D转换器、D/A转换器、正交调制器、输出电路等。

根据数字图像传输的特点,采用扩频调制技术。

这是因为扩频方式的抗干扰、抗衰落及抗阻塞能力强,而且扩频信号的功率谱密度很低,有利于隐蔽。

同时,为了提高数据传输的可靠性和有效性,降低信号失真度,减少码间干扰,在调制系统中还加入编码、交比例中项及匹配滤波。

这些处理都在FPGA中实现,使整个调制系统具有可编程的特点,易于根据实际要求进行功能上的扩展和缩减。

系统的原理框图如图1所示。

电路的具体工作过程为:图像信号经过A/D转换器AD9214完成模/数转换,输出信号送入FPGA。

由FPGA对信号进行编码、交织、串/并变换、扩频调制及匹配滤波。

FPGA输出两路数字信号,经过双D/A转换器AD9763实现数/模转换,输出两路模拟信号。

这两路信号经过正交调制器AD8346正交调制输出,实现QPSK调制。

因为正交调制器输出的信号功率较小,所以将其经过模拟放大器放大和带通滤波,之后再送到输出。

在整个调制系统中,FPGA模块的软件设计是最为重要的,也是进行系统优化的主要部分,它的优劣会直接影响整个系统的性能。

下面对这部分进行详细的介绍。

2 软件部分实现原理FPGA模块的软件设计部分包括以下几个方面:编码、交织、串并变换、扩频、匹配滤波以及复位和时钟。

2.1 编码和交织数字通信中经常使用信道编码加交织模块来提高数据传输的可靠性和有效性。

为了达到一定的增益要求,选择卷积码中纯编码增益为3.01的(1,1,6)码(在大信噪比下),并对其进行增信删余。

基于FPGA的AM数字调制解调设计验证与分析

图1 AM 调制模型基于FPGA的AM数字调制解调设计验证与分析李国诚,黄明,丁照雨,徐泽琨,曹愿栋(北方工业大学,北京 100144)摘 要: AM和正交调制解调是通信领域应用最广泛的基础技术,由此提出了一种简单基于FPGA数字实现AM和正交调制解调的方法,具有较好的抗噪声性能及较强的抗频偏能力,并推导了所允许的最大载频偏差(Δf max ),为实际应用提供了理论依据;该调制解调方法实现简单,通用性强,并有较好的可靠性、抗噪声性及抗载频适配能力。

利用Matlab仿真软件建立了可视化的AM通信系统模型,介绍了AM系统的工作原理、AM信号的产生和解调方法,设计电路参数和基本数据对实际应用有一定的参考意义。

关键词: AM调制解调;正交解调;Matlab;FPGA中图分类号:TP 311 文献标识码:A 文章编号:2095-8412 (2019) 01-036-07工业技术创新 URL : http: // DOI : 10.14103/j.issn.2095-8412.2019.01.005引言随着移动通信技术的不断发展,通信方式正在从最初的模拟方式朝着数字化方向转变,由于数字信号比模拟信号具有更高的可靠性、抗噪性、灵活性和易于存储等优点,这使得在目前的通信业务中,许多以往的模拟信号处理部分都在模拟转换数字后(模数转换)进行数字信号处理[1]。

本文通过数字方式实现了A M 调制和正交解调,其解调方式相对于包络检波和相干解调有着更好的抗噪声性能和抗载频适配能力,并在Matlab 和FPGA 中验证了这一方法的可行性。

1 AM调制解调原理分析1.1 AM调制原理分析标准调幅就是常规双边带调制,简称调幅(AM ,Amplitude Modulation ),AM调制属于基带调制, 即由调制信号去控制高频载波的幅度,使之随调制信号的幅度线性变化的过程,使得调制信号的信息包含在高频信号之中[2]。

AM 调制是短波和超短波通信中的一种主要的调制方式,它具有电路设备简单、调制所占频带窄,并且与之对应的解调接收设备简单等特点,在日常的通信中得到广泛应用,其调制模型如图1所示。

基于FPGA的DPSK调制解调器的全数字实现

基于FPGA的DPSK调制解调器的全数字实现

基于FPGA的DPSK调制解调器的全数字实现

调制解调技术是通信系统的灵魂,其性能直接影响到整个系统的通信质量.由于数字技术的大量应用,数字调制解调技术得到了广泛的应用.随着软件无线电思想的发展,将整个系统尽可能地集成于一个芯片的设计方法已经呈现出强大的发展潜力,成为系统设计发展的主要方向.基于这种思想,介绍一种在单片FPGA上实现的全数字DPSK调制解调器的设计方法.整个设计基于ALTERA公司的QUARTUS II开发平台,并用单片CYCLONE系列FPGA芯片实现.

作者:赵叶星韦志棉 ZHAO Ye-xing WEI Zhi-mian 作者单位:北京航空航天大学,无人机研究所,北京,100083 刊名:无线电工程英文刊名:RADIO ENGINEERING OF CHINA 年,卷(期):2007 37(10) 分类号:N914.3 关键词:DPSK FPGA 调制解调软件无线电。

基于FPGA的数字正交调制器的研究与设计

I基于FPGA的数字正交调制器的研究与设计2014 年10 月 10日目录1 概述 (1)2 课题功能需求 (1)2.1 课题要求实现的功能 (1)2.2 课题主要技术指标 (1)2.3 课题进度 (2)3 课题技术指标及完成情况 (2)3.1 技术指标的检测 (2)3.2课题要求指标完成情况 (2)4 数字正交调制器原理 (2)5 数字正交调制器软件编程实现 (4)5.1 数字正交算法的matlab仿真 (4)5.1.1 matlab程序释义............................................................. 错误!未定义书签。

5.2 数字正交调制算法的FPGA硬件平台验证 (8)5.2.1 FPGA实现流程 (8)5.2.2 FPGA核心模块介绍 (8)5.2.2 FPGA仿真结果 (9)6 总结 (9)参考文献 (10)1.概述数字正交调制器是雷达干扰中的一项重要技术,通过将截获的雷达信号进行移频并转发形成给雷达造成错误、虚假或者杂乱的速度信息。

它是多普勒调制技术实现的基础,广泛应用于对连续波、脉冲多普勒、合成孔径等具有测速能力雷达的速度波门实施干扰。

传统的雷达干扰设备为进行多普勒调制,通常需要利用混频器、滤波器等实现,大量微波器件的使用使整个干扰系统体积和功耗过大,性能和指标不稳定。

介绍了将数控移相器控制行波管相位实现多普勒调制的方法。

行波管要求调制信号幅度大,控制电路复杂、灵活性差。

70年代发展起来的数字射频存储(DRFM)技术将雷达信号经过高速模数转换后进行数字存储,在适当时刻通过数模转换实现重构和发射。

随着技术的发展,DRFM可以利用多种数字算法实现对信号的调制,本文主要研究单通道采样DRFM的数字多普勒调制方法。

2.课题功能需求2.1 课题要求实现的功能(1)能在输入的雷达脉冲信号上调制递增变化的移频量;(2)能在输入的雷达脉冲信号上调制随机变化的移频量;(3)能在实际硬件电路上调试出上述两项功能;2.2 课题主要技术指标(1)移频范围:1MHz~10MHz;(2)移频步进:1MHz;(3)随机移频范围:1MHz~10MHz;2.3 课题进度(1) 8月20日,了解相关数字储频算法和硬件电路;(2) 9月10号,完成算法设计;(3) 10月1日,完成硬件调试和软件调试;(4) 10月15号,完成资料整理;3. 课题技术指标及完成情况3.1 技术指标的检测根据实现方法和指标的要求,首先用MATLAB 仿真数字正交调制实现单频信号、梳状波等信号的移频,再用FPGA 硬件平台实现算法的功能。

基于FPGA的数字调制系统设计

摘要在科学技术迅速发展尤其是在通信领域以及电子信息方面的发展更为突出的今天,设计者需要一个高速通用硬件平台来实现并验证自己的通信系统和相关算法。

FPGA(现场可编程门阵列)作为一种大规模可编程逻辑器件,体系结构和逻辑单元灵活、集成度高、适用范围宽,并且设计开发周期短、设计制造成本低、开发工具先进并可实时在线检验,广泛应用于产品的原型设计和产品生产。

与传统的DSP(数字信号处理器)或GPP(通用处理器)相比,FPGA在某些信号处理任务中表现出非常强的性能,具有高吞吐率、架构和算法灵活、并行计算、分配存储以及动态配置等优势,因此非常适合用于设计验证高速通信系统的基带处理部分。

基于FPGA的通信系统基带设计验证平台采用大容量、高性能的FPGA器件,为通信系统的基带设计提供了一个有效的硬件实现平台。

基于FPGA的实现和验证与计算机仿真相结合,将大大加速通信系统基带部分的快速原型设计,极大地方便了对实时性和运算量有较高要求的各类算法的验证。

本论文实现了一种基于FPGA的数字信号调制系统的实现方案,由曼彻斯特编码加密后通过频移键控(FSK)数字调制,在QuartusII软件上进行了逻辑编译,以及代码时序仿真,进而验证系统的可行性与可靠性。

关键词:现场可编程门阵列,频移键控调制,曼彻斯特编码AbstractIn science and technology are developing rapidly especially in communication field and the development of electronic information more prominent today, designers need a high-speed general hardware platformto realize and verify their communication system and related algorithm. The FPGA (field programmable gates array) as a large-scale programmable logic devices, the system structure and logic unit, flexible, integration, and wide application scope of short development cycle, design and manufacture of low cost, development tools and on-line inspection can be advanced, the product is widely applied in the prototype design and production.And the tradition of DSP (digital signal processor) or GPP (gm), FPGA processor in some signal processing tasks shows very strong performance, high throughput, architecture and algorithm, parallel computing and storage and distribution of the dynamic configuration advantages, therefore is very suitable for high-speed communication system design verification processing parts. BasebandThe communications system based on FPGA baseband designverification platform using the large capacity and high performance FPGA device for communication system, the baseband design provides an effective realization of hardware platform. Based on FPGA and validation and computer simulation combining communication system will be greatly accelerated, rapid prototyping design part baseband, great place forreal-time computation and show the algorithm has higher requirement of the validation.This paper based on FPGA realizing the digital signal modulation system implementation scheme by Manchester coding encrypted, by FSK digital modulation, and in the QuartusII software on the logical compiled,and reliability of the verification system.Key words:FPGA ,FSK,Manchester coding目录摘要 IAbstract II1 绪论 11.1 课题背景 11.2研究现状 11.3课题研究的目的和意义 22硬件平台概述 32.1 FPGA简介 32.2 FPGA系统设计流程 92.3 QuartusⅡ简介 103系统算法介绍 143.1曼彻斯特编码简介 143.2曼彻斯特编码的原理 143.3数字调制技术概述 153.4 FSK调制原理以及其特点 164系统方案设计 204.1 VHDL硬件描述语言 204.2 功能模块介绍 215总结与展望 285.1 总结 285.2 展望 28致谢 30参考文献 31附录1:英文文献 32附录2:中文文献 40附录3:设计总图 471 绪论1.1 课题背景从1837年莫尔斯发明电报算起,一个世纪以来,通信的发展大致经历了三大阶段:以1837年发明电报(莫尔斯电码)为标志的通信初级阶段;以1948年香农提出的信息论开始的近代通信阶段;以20世纪70年代出现的光纤通信为代表的和以综合业务数字网迅速崛起为标志的现代通信阶段。

FPGA在数字广播调制解调中的应用研究

FPGA在数字广播调制解调中的应用研究数字广播技术是一种现代化的无线通信技术,可以实现多信道、高保真、多样化的音频和数据传输。

然而,数字广播的调制和解调过程中需要高度灵活性和实时性,而传统的软件实现方式受限于计算速度和资源消耗等问题,无法满足复杂的调制解调需求。

而现场可编程门阵列(Field-Programmable Gate Array,FPGA)作为一种灵活可编程的硬件平台,为数字广播调制解调提供了理想的解决方案。

一、FPGA技术概述FPGA是一种可通过编程来实现特定硬件功能的集成电路芯片。

其与固定功能的专用集成电路不同,可以根据需求对逻辑门和触发器的布局进行编程,实现不同的数字逻辑电路。

由于FPGA的逻辑电路可重新编程,因此具有灵活性和可重用性的优势。

二、FPGA在数字广播中的应用1. 调制过程中的FPGA应用调制过程是将音频和数据信号转化为适合传输的模拟或数字信号的过程。

在数字广播中,FPGA可以实现各种调制方式,如幅度调制(AM)、频率调制(FM)和相位调制(PM)。

通过将调制过程中的复杂计算转化为硬件逻辑的运算,FPGA可以提供更高的计算速度和精度。

2. 解调过程中的FPGA应用解调过程是将调制后的信号恢复为原始音频和数据信号的过程。

在数字广播中,FPGA可以实现各种解调方式,如AM解调、FM解调和PM解调。

通过在FPGA中实现解调算法和滤波器等功能模块,可以实现高效、实时的解调过程。

三、FPGA的优势和挑战1. 优势FPGA在数字广播调制解调中具有以下优势:首先,FPGA具有高度可编程性,可以根据不同的调制解调算法进行灵活配置和优化,满足不同数字广播标准和协议的要求。

其次,FPGA具有并行处理能力强的特点,能够同时处理多个信道和多种调制解调方式,提高处理效率和带宽利用率。

最后,FPGA具有低功耗和低成本的特点,可以降低数字广播设备的能耗和生产成本。

2. 挑战然而,FPGA在数字广播调制解调中也面临一些挑战:首先,FPGA的编程和设计需要专业知识和技能,对于广播行业中的专业人士来说,需要具备一定的学习和应用成本。

基于FPGA的CCK调制解调算法的研究与实现的开题报告

基于FPGA的CCK调制解调算法的研究与实现的开题报告摘要频率合成和解调技术是数字通信系统中的核心技术,而CCK调制技术是现代短距离无线通信系统中常用的一种调制方式。

本文针对CCK调制技术,进行了基于FPGA的CCK调制解调算法的研究与实现。

本文首先介绍了CCK调制技术的基本原理和特点,然后详细分析了CCK调制解调算法的具体实现过程,并提出了基于FPGA的CCK调制解调系统的设计方案和实现细节。

最后进行了仿真实验和硬件实现验证,结果表明本文所提出的算法具有良好的实时性和误码率性能,可以满足实际应用需求。

关键词:FPGA,CCK调制,解调算法,仿真实验,硬件实现一、研究背景和意义随着无线通信技术和移动互联网的快速发展,短距离无线通信系统(如Bluetooth、Wi-Fi等)的应用越来越广泛。

在这些系统中,CCK (Complementary Code Keying)调制技术常常被用于实现高速数据传输,其具有距离远、速率高、抗干扰能力强等优点,在数字通信系统中应用广泛。

基于FPGA的数字信号处理系统具有可编程性强、运行速度快、面积小、功耗低等优点,因此被广泛应用于数字通信系统中。

本文旨在通过对CCK调制解调算法的研究和实现,设计一个基于FPGA的CCK调制解调系统,提高其解调效率和可靠性,为无线通信系统的实际应用提供技术支持。

二、研究内容和方法1. CCK调制技术的分析CCK调制技术是利用两种短码(short code)进行交替调制,以达到高速数据传输的目的。

本部分主要分析CCK调制技术的基本原理和特点,为后续的算法研究奠定基础。

K调制解调算法的研究CCK调制解调算法是CCK通信系统中的核心算法,其主要任务是将数字信号经过调制后发送到接收端,并通过解调算法将其还原为原始数字信号。

本部分主要研究CCK调制解调算法,包括短码的生成、频率合成和信号解调等过程。

3.基于FPGA的CCK调制解调系统设计与实现本部分主要设计基于FPGA的CCK调制解调系统,将前两部分研究结果的算法在FPGA芯片上实现。

基于FPGA的数字化调节技术的研究

第29卷第5期 唐山师范学院学报 2007年9月 Vol. 29 No.5 Journal of Tangshan Teachers College Sep. 2007────────── 收稿日期:2007-04-11 作者简介:张铁(1972-),男,河北唐山人,工程师,研究方向为电子学。

- 101 -基于FPGA 的数字化调节技术的研究张 铁1,张 硕2(1.唐山市人事局干部教育培训中心,河北 唐山 063000;2.唐山钢铁集团公司,河北 唐山 063000)摘 要:随着现代移动通讯的发展,软件无线电已经成为3G 标准中重要部分设计的最好的解决方案,而数字调制解调部分是软件无线电系统中至关重要的组成部分。

对基于FPGA 的数字调制解调系统实现进行了研究。

关键词:数字调制解调;FIR 滤波器;VHDL 语言中图分类号:TN949 文献标识码:A 文章编号:1009-9115(2007)05-0101-031 引言自上世纪70年代提出蜂窝概念以来,蜂窝系统蓬勃发展,在全球范围内己经拥有了广泛而庞大的用户群体。

但由于不同标准的各个系统之间一直处于相互独立的发展状态,用户在全球范围的漫游难以实现。

随着全球信息化进程的发展,最终解决这一问题己经提上日程。

在第三代移动通信的标准中,支持全球无缝漫游己经成为移动终端必不可少的功能。

这就意味着第三代移动通信系统的终端设备将是一台多频、多模式、多业务的高性能设备。

软件无线电技术无疑是设计此类型终端的最好解决方案。

用FPGA 器件实现软件无线电系统数字调制解调部分,利用系统级动态仿真软件MAX+plusII 分析并设计软件无线电体系结构中的数字调制解调系统,继而完成了软件无线电数字调制解调系统的时序仿真。

2 数字调制解调器系统分析2.1 数字调制解调器的硬件实现方法及其改进数字无线通信系统中,数字调制是信号变换及系统组成的重要环节。

移动通信的频带资源有限,要求调制信号功率谱占有窄的带宽。

基于fpga的qpsk调制解调原理及实现方法

基于fpga的qpsk调制解调原理及实现方法QPSK(Quadrature Phase Shift Keying)是一种常见的调制解调技术,在许多无线通信系统中广泛应用。

本文将介绍基于FPGA的QPSK调制解调的原理,并给出实现方法。

一、QPSK调制原理QPSK调制是一种相位调制技术,通过调整信号的相位来实现多个比特的传输。

在QPSK调制中,将数字比特流分为两组,每组两位比特,分别称为I和Q。

QPSK调制原理如下:1. 将两位比特I和Q转换为相应的相位值:- 00:相位0°- 01:相位90°- 10:相位180°- 11:相位270°2. 将相位调制的信号进行合并,得到QPSK调制信号。

具体操作是将两路调制信号分别乘以正弦函数和余弦函数,然后相加。

二、QPSK解调原理QPSK解调是将接收到的QPSK调制信号还原为原始的数字比特流。

解调的过程可以分为两步:信号的采样和相位恢复。

1. 信号的采样:使用FPGA时钟信号对收到的QPSK调制信号进行采样,采样频率应与信号的带宽相匹配。

2. 相位恢复:通过采样得到的信号,利用相位锁定环(PLL,Phase-Locked Loop)等技术,恢复原始信号的相位。

三、基于FPGA的QPSK调制解调实现方法基于FPGA的QPSK调制解调可以通过硬件描述语言(如Verilog 或VHDL)实现。

下面给出一种基本的实现方法。

1. QPSK调制实现:a. 采用FPGA的GPIO(通用输入输出)接口输入数字比特流。

b. 将输入的比特流转换为相应的相位值,可以使用查找表(Look-Up Table)实现。

c. 将相位值转换为正弦和余弦函数的乘积,并相加得到调制信号。

d. 输出调制后的信号。

2. QPSK解调实现:a. 使用FPGA的ADC(模数转换器)接口采样接收到的QPSK 调制信号。

b. 对采样信号进行滤波,去除噪声和多径干扰。

基于FPGA的调制解调算法的实时性分析与优化

基于FPGA的调制解调算法的实时性分析与优化随着通信技术的不断发展,调制解调技术在无线通信中起着至关重要的作用。

为了实现高速、高效的数据传输,基于FPGA的调制解调算法成为了一种常见的选择。

本文将重点分析基于FPGA的调制解调算法的实时性,并提出相应的优化方法。

一、调制解调算法概述调制是指将数字信号转换为模拟信号,解调则是将模拟信号转换为数字信号。

在基于FPGA的系统中,调制解调算法主要涉及对数字信号进行采样、调制/解调、滤波等操作。

二、实时性分析基于FPGA的调制解调算法需要在实时性要求较高的场景下工作,因此实时性是评估算法性能的重要指标之一。

实时性分析主要从以下几个方面进行:1. 采样频率:调制解调算法需要对信号进行采样,采样频率过低会导致信息丢失,而过高则会增加处理的复杂性。

因此,需要根据具体应用场景的需求,选择合适的采样频率。

2. 算法复杂度:调制解调算法的复杂度直接影响到实时性。

通过对算法进行合理的优化和设计,可以降低算法复杂度,提升实时性能。

3. 数据传输速率:基于FPGA的系统需要高速地传输数据,因此数据传输速率的要求也会影响调制解调算法的实时性。

保证数据传输速率与算法的处理速度相匹配,是提高实时性的关键。

三、实时性优化方法为了提高基于FPGA的调制解调算法的实时性,可以从以下几个方面进行优化:1. 硬件设计优化:合理设计FPGA的硬件结构,优化资源利用率和时序控制,减少延迟和功耗。

例如,采用流水线技术对算法进行划分,增加并行计算的能力,提高处理速度。

2. 算法优化:对调制解调算法进行优化,降低计算复杂度。

可以考虑使用更简单的算法替代复杂的算法,或者引入近似计算的方法。

同时,充分利用FPGA的并行计算能力,对算法进行并行化处理,提高实时性。

3. 缓存与存储优化:优化数据的存储和传输方式,减少数据的复制和移动。

使用合适的缓存策略,提高数据读写效率,减少延迟。

4. 时钟频率优化:通过合理设计时钟频率,提高系统稳定性和处理速度。

基于FPGA的全数字64QAM调制解调器设计

D 为满 足 系统信 兽 ——诹厂——= — 丽 图 同时 V B 亟亟 蟹 号幅 i

,

度 需 ,多 平 号 电 : 的 要将 电 信 的 :

平值设置为± ± ,1 2V,6V ±OV, 座点 映射关系如表 1 所示 。

图 I 调 制模 块 总体 框 架

6 Q M 全 数 字调 制 解调 。 4A

。

【 关键词 】有线 电视 ;Q M 调制 ;现场可编程 门阵列 ;定 时同步 A 【 中图分类号】T 9 9 N 1 【 文献标识码 】B

Dein o l D gtl6 QA Mo uao n mo uao sd o P sg fA l ii 4 M d ltra d De d ltrBae n F GA - a

・

实 用设计 ・

【 摘 要 】 针对 Q M 调制解调技术在有线 电视领域 的广 泛应用 ,提 出 了 一种 基 于 F G 的全 数 字 6 Q M 调 制 解 调 方 案 ,采 用 A PA 4A

V L 等硬 件 描 述 语 言 进 行 模 块 设 计 ,给 出各 模 块 时序 仿 真 图 , 并对系统中涉及. HD 到的定时同步问题进行阐述 ,最终正确实现

6 Q M m d l i n e o uao ae n F G I g e h ecit n o ah m d l ds nd i V D ,hw t t ig 4 A o uao a dd m d l i b sd o P A. t i sted sr i fec o u ei e n H L so si i n t n tn v po e g s m s ua o eu n ec bste t n rbe ivle n ti ss m.Fnl l dgt 4 A o ua o n e o uao i lin rsl ad dsr e h i gpo l no d i hs yt m t t i mi m v e i l a — i a 6 Q M m d l ina d dm d l i ay l il t t n

基于FPGA的全数字脉宽调制器

基金项目:国家自然科学基金委员会专项基金资助(青年基金项目)(60801047)收稿日期:2008-06-16 修回日期:2008-10-24第26卷 第11期计 算 机 仿 真2009年11月文章编号:1006-9348(2009)11-0347-05基于FPGA 的全数字脉宽调制器张宣妮1,王明军1,鲁 帆2(1.咸阳师范学院物理系,陕西咸阳712000;2.西安测量设备有限公司,陕西西安710089)摘要:为了解决传统的脉宽调制(P WM )信号电路的设计复杂、噪声大及抗干扰能力差等缺点,设计一种全数字脉宽调制器(DP WM ),采用先进的现场可编程逻辑器件(FPGA )和硬件描述语言(V H DL),有效地控制CS 时钟信号的上升沿和下降沿和脉冲宽度,可以很好地解决像增强器的光晕现象,扩大其动态范围;通过仿真实验,验证了全数字脉宽调制器(DP WM )控制系统具有控制灵活精确、设计简单易修改、抗噪抗干扰能力强等特点;FPGA 可重复擦写,当需要实现其它功能时,只需在程序上改动即可,可方便地嵌入需要调节控制的各个系统,加快系统开发和利用。

关键词:全数字脉宽调制器;现场可编程逻辑器件;硬件描述语言;仿真中图分类号:TP13 文献标识码:BA D igitalW i dth M odulator Based on FPGAZ HANG Xuan-n i 1,WANG M ing-jun 1,LU fan2((1.Physics D epa rt m en t ,X ianyang N or m a l Coll ege ,X ianyang Shanx i 712000,Chi na ;2.X i an M easure m en t Equ i p m en t Co m pany ,X i an Shanx i 710089,China)ABSTRACT :In o rder to overcom e the defects of traditiona l pulse w i dth m odulati on (PWM )si gnal circu it ,such as design comp l ex ity ,strong no ise ,poor anti-i nterference capab ility e tc .a d i g ital pulse w i d t h m odulator(DP WM )is de si gned ,w hich adopts the advanced F i e l d P rog ra mm ab l e G ate A rray(FPGA )and V ery H i gh speed i ntegrated circu it H ard w are D escr i pti on L anguage (VHDL ),can e ffectively contro l the risi ng edge and falling edge o f clock signa l and pulse w i dth ,reso l v e the dazi ng o f i m age i ntensifi e r and i m prove its dyna m ic range .T he si m ulati on experi m ents have ver ified tha t the d i g ita l pulse w i dth m odulator can be contro lled prec ise l y and fl ex i b l y ,i s easy to be m od ifi ed ,and has strong an ti-no ise and anti-i nte rerence capability .FPGA can be repea ted ,t hat is t o say ,when needing o t her func tion ,i t needs on l y chang i ng its procedure ,so i t can be easil y embedded i n va rious contro l system s ,thus acce l erati ng syste m development and utili zati on .KEY W ORDS :D i g ita l pu lse w i dth m odulator ;F ield prog ramm ab le ga te a rray (FPGA );H a rd w are desc ri ption lan guage ;S i m u l a ti on1 引言传统的脉宽调制(PWM )信号是通过专用的芯片或是中小规模的数字电路来产生的,在模数转换中,由于模拟信号的抗噪抗干扰能力较差,会使P WM 作用的控制系统产生误动作,又由于PWM 由DSP 定时器来控制,占芯片的一部份资源,因此存在着电路的设计复杂、抗干扰能力差,精度低,实现困难等缺点。

基于FPGA的数字调制解调设计

基于FPGA的数字调制解调设计2016年5月10日目录一、目的 (2)二、原理及实现 (2)2.1 2-ASK (2)2.2 2-FSK (3)2.3 2-PSK (4)三、设备需求 (5)四、硬件电路设计 (5)4.1 设计思路 (5)4.2 顶层设计 (6)4.3 MCU模块设计 (6)4.4 FPGA模块设计 (7)4.5 AD/DA模块设计 (7)4.6 外设部分 (8)五、软件编程 (8)5.1 2-ASK (8)5.2 2-FSK (11)5.3 2-PSK (14)六总结与感想 (16)一、目的1、掌握EDA设计流程和Verilog HDL;2、掌握数字系统调制解调原理,并用Verilog实现的方法;3、掌握Altium Designer绘制原理图和PCB的方法;4、掌握Quartus II的使用方法。

二、原理及实现调制是现代数字通信系统中必不可少的一部分。

在不少通信系统中,基带信号不能直接传输,必须先对基带信号进行变换=,得到适合信道传输信号,这就是调制;二解调就是调制的反变换。

用二进制(多进制)数字信号作为调制信号,去控制载波参量某些的变化以使信号与信道的特性相匹配。

这种用数字基带信号控制载波,把数字基带信号变换为数字贷通信号(已调信号)的过程称为数字调制。

,反之称为数字解调。

用来控制高频载波参数的基带信号称为调制信号,被调制的高频振荡称为载波。

调制的信号通过传输后被接收端接收,把调制信号恢复成原始基带信号。

数字调制有三种基本形式:(1)振幅键控(ASK),(2)频移键控(FSK),(3)相移键控。

ASK属于线性调制,FSK和PSK属于非线性调制。

调制信号是二进制数字基带信号时,这种调制称为二进制数字调制。

在二进制数字调制中,载波的幅度、频率和相位只有两种变化状态。

相应的调制方式有二进制振幅键控(2-ASK)、二进制频移键控(2-FSK)和二进制相移键控(2-PSK)。

2.1 2-ASK1. 调制ASK是利用载波的幅度变化来传递数字信息,而其频率和初始相位保持不变。

FPGA在数字音频调制解调中的应用研究

FPGA在数字音频调制解调中的应用研究随着现代通讯技术的快速发展,数字音频调制解调技术逐渐成为了音频信号处理的主流。

而在数字音频调制解调中,Field Programmable Gate Array(FPGA)作为可重新配置的硬件平台,具有高度的灵活性和性能优势,广泛应用于音频处理和通信系统中。

本文将对FPGA在数字音频调制解调中的应用进行研究,并阐述其优势和挑战。

一、FPGA在数字音频调制中的应用1. 数字音频调制原理数字音频调制是将模拟音频信号转换为数字音频信号的过程。

其中,调制过程包括采样、量化和编码,而解调过程则是将数字音频信号还原为模拟音频信号。

FPGA在这一过程中可以对信号进行高效的处理和计算,提高音频质量和系统性能。

2. FPGA的灵活性和可重构特性FPGA作为可编程硬件平台,可以根据不同的需求进行灵活的配置和重新编程。

由于音频调制解调算法的复杂性和多样性,FPGA能够快速适应不同的算法和信号处理需求,在运行时可以灵活地调整配置和参数。

3. FPGA在数字音频编解码中的优势FPGA具有高速并行计算的能力,能够实时处理大规模的音频数据。

同时,FPGA还具有低延迟和高带宽等特点,能够提供稳定和高效的音频传输。

此外,FPGA还能够进行数据压缩和解压缩,提高音频数据的传输效率和存储容量利用率。

4. FPGA在音频特效处理中的应用FPGA在数字音频调制解调中不仅可以实现基本的信号处理功能,还可以用于音频特效的实时处理。

例如,FPGA可以实现混响、均衡器、声音合成等音频效果,为音频系统提供更多的功能和创造性。

二、FPGA在数字音频调制解调中的挑战1. 复杂性和资源消耗数字音频调制解调算法的复杂性较高,需要大量的计算资源和存储资源。

由于FPGA资源有限,需要对算法进行适当的优化和压缩,以保证在FPGA上的实时运行和高效性能。

2. 时序和时钟同步在数字音频调制解调中,时序和时钟同步是至关重要的。

FPGA系统需要保证各个模块之间的数据同步和时钟同步,以避免数据传输和处理的错误。

基于FPGA的16QAM调制解调系统的研究

基于FPGA的16QAM调制解调系统的研究一、本文概述随着通信技术的飞速发展,对于数据传输速率和频谱效率的要求日益提高。

在这种背景下,正交幅度调制(QAM)技术因其高频谱效率和数据传输能力而受到广泛关注。

其中,16QAM(16级正交幅度调制)作为一种常见的QAM技术,具有适中的复杂度和优秀的性能,被广泛应用于无线通信系统。

然而,传统的16QAM调制解调系统通常基于通用处理器或专用芯片实现,存在功耗高、灵活性差等问题。

为了解决这些问题,本文提出了一种基于FPGA(现场可编程门阵列)的16QAM调制解调系统。

FPGA具有高度的并行处理能力和灵活性,能够实现对16QAM信号的高效处理。

本文首先介绍了16QAM调制解调的基本原理和关键技术,包括信号调制、解调算法以及性能评估等方面。

然后,详细阐述了基于FPGA 的16QAM调制解调系统的设计方案和实现过程。

在此基础上,对系统的性能进行了仿真分析和实验验证,证明了该系统的有效性和优越性。

本文的研究对于提高16QAM调制解调系统的性能、降低功耗和增加灵活性具有重要意义。

也为FPGA在无线通信领域的应用提供了有益的探索和参考。

二、16QAM调制解调原理16QAM(Quadrature Amplitude Modulation,16进制幅度调制)是一种数字调制技术,在数字通信系统中广泛应用。

16QAM将每个符号编码为16个不同的幅度级别,从而每个符号可以携带4位的信息,提高了数据传输的效率。

基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)的16QAM调制解调系统则通过硬件编程的方式实现这一技术,具有高速、灵活和低成本的优点。

在16QAM调制过程中,输入的二进制数据流首先被分为每4位一组的数据块。

然后,每组4位数据被映射到16QAM星座图上的一个点,该点由实部和虚部组成,分别对应I路和Q路信号。

映射完成后,这些星座点通过数字到模拟转换器(DAC)转换为模拟信号,并进一步调制到载波频率上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

分类号密级U D C基于FPGA的全数字调制解调技术的研究艾砾导师姓名(职称)卜祥元(高工)答辩委员会主席 李鸿屺(教授) 申请学科门类工学论文答辩日期 2005年2月28日 申请学位专业通信与信息系统摘要软件无线电是上世纪末新兴的一门学科,它突破了传统的无线电台以硬件为核心的功能单一、可扩展性差的设计局限性,强调以可编程的硬件作为通用平台,尽量地用可升级、可重配置的软件来实现各种无线电功能的设计新思路。

软件无线电的设计思想是将宽带A/D和D/A的变换尽可能地靠近天线,通过对数字化后的信号采用数字信号处理(DSP)技术,在可编程控制的硬件平台上,利用软件来实现无线电台的各部分功能。

由于软件无线电对硬件的依赖程度很小,具有高度的开放性、灵活性和可编程性,使得通信系统的开发将重点放在软件的研究上,因此可以很好的解决通信系统间的通信标准不同的问题,极大缩短通信系统开发的时间和成本。

本文研究了一种基于软件无线电技术的数字发送和接收系统,根据实际需要在FPGA和通用DSP相结合的软件无线电平台上实现AM,FM,PSK等调制解调方式。

在具体实现方面,结合FPGA的特点进行设计。

主要对调制解调算法,成型滤波,锁相环实现载波同步、位同步等各部分进行了详细介绍,整个部分可通过配置参数解调不同的调制信号,具有很强的通用性。

关键词:软件无线电、解调、数字锁相环、FPGAABSTRACTSoftware radio is a new technology which promising in the end of last center. It is very different from those old transmitter-receivers, which tie to hardware and their function was limited. The software radio is based on programmable hardware, all functions realized by software, when you want to update you software, you will find the programmable hardware can be easy reconfigured. The thought way of software radio is to let the A/D and D/A change as near as possible, then realize al kinds of functions by using digital signal processing technology, thus, we can pay more attention to the function of the radio. The problem of different communication protocol between different communication systems will be resolved easy. The research period and cost will be reduced greatly.The thesis is based on the research of digitalized sender and receiver system of software radio. The main responsibility of this thesis is to realize AM、FM、PSK modulation and demodulation on the software radio platform based on DSP and FPGA. According to the characteristics of FPGA, it provides detailed explanations on the carrier synchronization, bit synchronization and other related parts of DPLL, the arithmetic of modulation and demodulation, and match filter. This method may realize demodulation different modulated signals by means of configuring parameters, which has universal application for engineering design.Keyword: Software Radio、demodulation、DPLL、FPGA目录摘要 (1)ABSTRACT (II)第一章绪论 (1)1.1引言 (1)1.1.1 软件无线电简介 (1)1.1.2 软件无线电实现关键技术 (2)1.2课题背景与研究现状 (3)1.2.1 FPGA背景知识 (3)1.2.2 数字调制解调背景知识 (4)1.2.3历史及现状 (4)1.3本文研究的主要内容 (5)1.4 本课题的研究意义及主要工作 (6)1.5本论文的结构 (6)第二章调制解调算法原理 (8)2.1 模拟调制解调的数字实现 (9)2.1.1 AM调制解调 (9)2.1.2 FM调制解调 (10)2.2 MPSK调制解调算法 (12)2.2.1 MPSK调制算法[1] (12)2.2.2 MPSK解调算法 (14)2.2.3 MPSK调制解调结构 (17)2.3 成型滤波实现 (18)2.3.1 成型滤波器原理 (18)2.3.2 码间串扰量的分析 (19)2.3.3 成型滤波器实现 (20)2.4 锁相环理论实现[4] (21)2.4.1 锁相环结构 (22)2.4.2 锁相环参数分析 (22)第三章数字调制解调的算法实现 (26)3.1 调制解调的整体设计 (26)3.1.1 整体结构优化 (26)3.1.2 控制寄存器与接口定义 (30)3.2 载波同步环路实现 (31)3.2.1 载波相位差错检测(鉴相) (31)3.2.2 载波环路滤波 (33)3.3 符号同步环路实现 (34)3.3.1 定时偏差检测器 (34)3.3.2 环路滤波与重采样 (35)3.4 自动增益控制(AGC)环路实现 (36)3.5 锁定检测控制实现 (38)第四章基于FPGA实现的优化设计 (40)4.1 利用CORDIC计算特殊函数 (41)4.1.1 CORDIC算法原理 (42)4.1.2 CORDIC实现混频 (43)4.1.3 CORDIC实现直角坐标到极坐标转换 (45)4.2 滤波器的设计实现 (46)4.2.1 FIR滤波器的基本设计 (46)4.2.2 分布算术式FIR滤波器 (49)第五章系统的调试及性能指标分析 (54)5.1 系统硬件结构 (54)5.2 系统调试 (56)5.3 调制解调性能测试 (59)第六章结束语 (63)致谢 (64)附录一调制解调电路板实物图 (65)附录二程序模块清单 (66)参考文献 (67)第一章绪论1.1引言为了使信号便于在带通信道中传输,必须对信号进行调制解调。

传统的数字调制解调技术已经相当成熟,但是传统的数字调制解调中上变频、滤波器、下变频、锁相环等高速器件大多用模拟器件实现。

这给后继的数字信号处理带来了很大的制约性,严重影响了数字通信的精确性,像并行多通道处理就更加困难了。

随着软件无线电技术快速发展的条件下,数字信号处理芯片的处理能力的不断提高,全数字的调制解调才逐渐浮出水面。

全数字调制解调与传统的解调相比,具有频率分辨率高、相位噪声小、稳定度高、易于调整及控制灵活等特点,随着软件无线电技术的发展,全数字调制解调实现了多种调制方式和多通道解调,本文正是采用软件无线电技术,研究基于FPGA的多种调制方式全数字调制解调技术的实现。

1.1.1 软件无线电简介软件无线电(Software Radio)是二十世纪末提出的一种新的设计思想,其完整的概念和结构体系是由美国MITRE公司的科学家Joseph Mitola 于1992年5月在国家远程系统会议(National Telesystems Conference)上明确提出[3]。

以现代通信理论为基础,以数字信号处理为核心,以微电子技术为支撑的软件无线电又称为软件可定义的无线电(Soft-Defined Radio),它突破了传统的无线电台以功能单一、可扩展性差的硬件为核心的设计局限性,强调以可编程的硬件作为通用平台,尽量地用可升级、可重配置的软件来实现各种无线电功能的设计新思路。

软件无线电的设计思想是将宽带A/D和D/A的变换尽可能地靠近天线,对数字化后的信号采用数字信号处理(DSP)技术,在可编程控制的硬件平台上,利用软件来实现无线电台的各部分功能,即整个无线电台从高频、中频、基带直到控制协议部分全由软件编程来实现。

由于软件无线电对硬件的依赖程度很小,具有高度的开放性、灵活性和可编程性,使得通信系统的开发将重点放在软件的研究上,因此可以很好的解决通信系统的标准问题,极大缩短通信系统开发的时间和成本,这也正是软件无线电与各种通信系统越来越紧密结合的重要原因。

它已经成为继固定通信到移动通信之后的无线通信领域的又一突破。

理想的软件无线电结构如下图所示,应该在天线之后就进行数字化,并使所有的过程软件化和可编程化,如图1.1。

声音图象数据传真图 1.1 理想软件无线电电台基本结构框图显然,理想的软件无线电台是对天线接收的模拟信号经过放大后直接采样,实现完全的可编程性,其后所有的信号处理包括下变频、带通滤波、载波提取、I/Q解调、低通滤波、位同步提取、信道编解码、信源编解码、加密解密等全部由ADC变换器之后的可编程芯片处理,可见理想的软件无线电台可以实现完全的可编程性,因此可以实现通信中的各种调制方式。

1.1.2 软件无线电实现关键技术实现软件无线电的关键技术主要有:射频天线、宽带ADC转换、高速数字信号处理和高性能的总线结构等方面。

z软件无线电的射频段应具备接入多个波段甚至覆盖全波段的功能,它具有频率高、带宽宽的两大特点。

我们可以采用多频段组合式天线和智能天线来实现。

多频段组合式天线是在全频段甚至每个频段使用几付天线组合起来以形成宽带天线。

智能天线的思想是:天线以多个高增益的动态窄波束分别跟踪多个用户,窄波束对准期望用户,波瓣零点对准期望信号以外的干扰信号,以达到信干比最大。