datasheet

CAP200DG Datasheet说明书

版本B 05/152CAP200DGwww.power .com图3. 引脚配置引脚功能描述图3所示的引脚配置可确保SO-8封装的宽度用于提供超过4 mm 的爬电距离和电气间隙。

虽然仅对引脚2、3、6和7进行电气连接,但仍建议在电路板上将引脚1-4和引脚5-8进行耦合 – 参见“应用”部分。

PI-5608-020515D Package (SO-8)NC D1D1NC12348765NC D2D2NC图4. MOV 和C EXT 的放置选项主要应用指南击穿电压选择该系统配置变量包括系统MOV 和X 电容的放置,以及具体应用的差模浪涌电压规格。

如表1所示,CAP200DG 的击穿电压为1000 V 。

对于MOV 放置于位置1(图4中的MOV POS1)的应用,CAP200DG 将提供足够的耐压性,满足高达3 kV 或更高的抗浪涌要求。

当MOV 未直接与X 电容1跨接时(如图4中的MOV POS2),可使用1000 V CAP200DG 器件来满足1.5 kV 的抗浪涌要求。

如果差模浪涌电压规格>1.5 kV ,建议始终将MOV POS1放置于图4所示的位置。

建议在进行最终系统浪涌测试时,始终测量CAP200DG 的D1和D2端子之间的峰值电压。

在浪涌测试期间测量CAP200DG 的峰值电压时,应使用具有适当电压额定值的示波器探针,并使用隔离电源对示波器供电, 以避免接地电流影响测量结果。

进行此类测量时,建议对峰值电压留出低于击穿电压规定值50 V 的工程裕量(例如使用1000 V CAP200DG 时峰值电压为950 V )。

PI-7508-012015X Capacitor1C EXTACX Capacitor2MOV POS1MOV POS2Other EMI Filter ComponentsD1R1R2CAP200DGD2版本B 05/153CAP200DGwww.power .com如果测得的峰值漏极电压超出950 V ,还可以在D1和D2端子之间放置一个最大电容值为47 pF 的1 kV 外部陶瓷电容,以便在浪涌期间对CAP200DG 端子之间的电压进行衰减。

datasheet 表

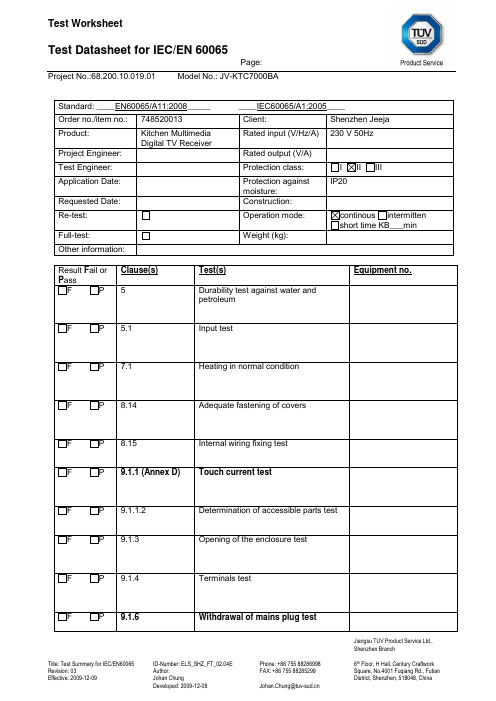

Project No.:68.200.10.019.01 Model No.: JV-KTC7000BAJiangsu TUV Product Service Ltd., Shenzhen BranchProject No.:68.200.10.019.01 Model No.: JV-KTC7000BAJiangsu TUV Product Service Ltd., Shenzhen BranchProject No.:68.200.10.019.01 Model No.: JV-KTC7000BAJiangsu TUV Product Service Ltd., Shenzhen BranchTested by :_____________________, checked by : _____________________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Input test and measurement of other electrical parametersStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause: 5.1 Sample No.: Rated voltage and frequency: Input: output:Load[ √ ] Max. normal load[ ] pink noise signal (1KHz sine wave) input, adjust volume to 1/8 max. non-clipped output power. [ ] Adjust to display max. color, brightness, contrastness.Remark:Input current measurement (0.9, 1.0, 1.1 times of rated input voltage)[ ] AV mode, TV mode and standby mode need considered.[ ] measured consumption (power /input current) not exceed the marked value by more than 10%Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Heating testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause:7 ............... Sample No.: ................. Operation mode / Test conditions: [ √ ] Max. normal load in TV mode[ ] pink noise signal (1KHz sine wave) input, adjust volume to max. output power.[ ] Adjust to display max. color, brightness, contrastness[ ]USB loading________AInstallation: [ ] put in test box according to clause 4.1.4Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkRemarks / Result: Run for thermal equilibrium.( ) No hazard. ( ) Duration: (__________ )Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Heating testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause:7 ............... Sample No.: ................. Operation mode / Test conditions: [ √ ] Max. normal load in TV mode[ ] pink noise signal (1KHz sine wave) input, adjust volume to max. non-clipped output power.[ ] Adjust to display max. color, brightness, contrastness.[ ]USB loading________AInstallation: [ ] put in test box according to clause 4.1.4Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkRemarks / Result: Run for thermal equilibrium.( ) No hazard. ( ) Duration: (__________ )Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: abnormal testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause:11 ............ Sample No.: Operation mode / Test conditions: Transformer output overloadInstallation: [ ] put in test box according to clause 4.1.4*Note: For windings temperatures measured with thermocouple method add 10 K !Remarks / Result:______________________________________________________________________ ( ) run for thermal equilibrium, no damaged, no hazard( ) component ____________ damaged after short/open circuit/after ____ minutes( ) others ______________________________________Duration: __________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: abnormal testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause:11 ............ Sample No.: Operation mode / Test conditions: USB overloading others same as normalInstallation: [ ] put in test box according to clause 4.1.4*Note: For windings temperatures measured with thermocouple method add 10 K !Remarks / Result:______________________________________________________________________ ( ) run for thermal equilibrium, no damaged, no hazard( ) component ____________ damaged after short/open circuit/after ____ minutes( ) others ______________________________________Duration: __________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: abnormal testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause:11 ............ Sample No.: Operation mode / Test conditions: Left speaker short circuit[ ] pink noise signal (1KHz sine wave) input, adjust volume to 1/8 max. non-clipped output power Installation: [ ] put in test box according to clause 4.1.4*Note: For windings temperatures measured with thermocouple method add 10 K !Remarks / Result:______________________________________________________________________ ( ) run for thermal equilibrium, no damaged, no hazard( ) component ____________ damaged after short/open circuit/after ____ minutes( ) others ______________________________________Duration: __________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: abnormal testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause:11 ............ Sample No.: Operation mode / Test conditions: Vent blockedInstallation: [ ] put in test box according to clause 4.1.4*Note: For windings temperatures measured with thermocouple method add 10 K !Remarks / Result:______________________________________________________________________ ( ) run for thermal equilibrium, no damaged, no hazard( ) component ____________ damaged after short/open circuit/after ____ minutes( ) others ______________________________________Duration: __________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkCOMPONENT FAULT SIMULATION:Standard: EN60065/A11:2008, IEC60065/A1:2005, Clause:11 ............ Sample No.: Input: ____230______V, ____50____HzOperation mode / Test conditions:[ √ ] Max. normal load[ ] pink noise signal (1KHz sine wave) input, adjust volume to 1/8 max. non-clipped output power. [ ] Adjust to display max. color, brightness, contrastness.Installation: [ ] put in test box according to clause 4.1.4Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkRemarks/Result: ___________________________________________________________________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BA Test by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065ID-Number: ELS_SHZ_FT_02.04EPhone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Leakage current test / Dielectric strength testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause 10,2 Sample No.: Humidity treatmentRelative humidity: 93 %RH Temperature : _40_ C Duration : 120___ h Leakage current testStandard:EN60065/A11:2008, IEC60065/A1:2005, Clause: 9.1.1 Sample No.: Input: _____253_____V, _50_______Hz; Operation mode / Test conditions: [ ] Max. normal load[ ] pink noise signal (1KHz sine wave) input, adjust volume to 1/8 max. non-clipped output power.Dielectric strength testStandard:EN60065/A11:2008, IEC60065/A1:2005, Clause: 10.3 Sample No.: .................Performed after: (1) Reaching steady state, normal operation Cut-off current: 10.0 mA* measured value : a.c. ; peakI = U 2 / 500Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065ID-Number: ELS_SHZ_FT_02.04EPhone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Surge test / Insulation resistance testStandard:EN60065/A11:2008, IEC60065/A1:2005, Clause: ...10,3 Sample No.: .................Insulation resistance testPerformed after: Humidity treatmentTest voltage: 500V d.c.Surge testStandard: EN60065/A11:2008, IEC60065/A1:2005, Clause: 10,1 Sample No.:IR measurement after 50 times surge test :Test voltage: 500V d.c.Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkProject No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkProject No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkProject No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkProject No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkProject No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Torque TestStandard: EN60065/A11:2008, IEC60065/A1:2005 Clause: ...............17.1 Sample No.: ................................[ ] The non-captive screw, 10 times their nominal diameter ( ____x 10= _______ mm)couldn’t reduce clearance and creepage.Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Working voltageStandard: EN60065/A11:2008, IEC60065/A1:2005 Clause: 13 Sample No.: ................. Input: _____240_____V, _50_______HzOutput: Maximum loading conditionRemark/Result: __________________________________________________________________Project No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065 ID-Number: ELS_SHZ_FT_02.04E Phone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkData sheet: Clearances, creepages and distances through insulationStandard: EN60065/A11:2008, IEC60065/A1:2005 Clause: .............13 Sample No.: .................(*) BI: basic insulation; SI: supplementary insulation; DI: double insulation; RI: reinforced insulation; DP: different polarityProject No.:68.200.10.019.01 Model No.: JV-KTC7000BATest by :_____________________, Date :_________________________Title: Test Summary for IEC/EN60065ID-Number: ELS_SHZ_FT_02.04EPhone: +86 755 88286998 Jiangsu TUV Product Service Ltd., Shenzhen Branch6th Floor, H Hall, Century CraftworkStandard: EN60065/A11:2008, IEC60065/A1:2005 Clause: 13 Model No.:Sample No.:(Clause: ) Sample No.: Date of test:Winding : ___ (Pri / Sec ) Winding : ___ (Pri / Sec ) Winding : ___ (Pri / Sec ) Winding : ___ (Pri / Sec ) Winding : ___ (Pri / Sec ) Winding : ___ (Pri / Sec )。

技术参数datasheet

技术参数datasheet随着科技的不断进步,各种电子设备的技术参数也越来越复杂。

为了让用户更好地了解和选择产品,厂商通常会提供一份技术参数datasheet。

本文将介绍技术参数datasheet的概念、内容以及如何理解和使用它。

一、技术参数datasheet的概念和作用技术参数datasheet是一份详细的技术规格表,通常由产品的制造商提供。

它包含了该产品的各种技术参数、性能指标以及其他相关的信息。

通过阅读和理解技术参数datasheet,用户可以更好地了解产品的功能、性能和适用范围,从而做出更准确的选择和购买决策。

二、技术参数datasheet的内容技术参数datasheet的内容通常包括以下几个方面:1. 产品基本信息:包括产品名称、型号、尺寸、重量等基本信息,帮助用户快速了解产品的基本特征。

2. 电气参数:包括电压、电流、功率等电气性能指标,帮助用户了解产品在电气方面的性能。

3. 机械参数:包括尺寸、重量、材质等机械特性,帮助用户了解产品在机械方面的性能。

4. 环境参数:包括工作温度、储存温度、湿度等环境要求,帮助用户了解产品在不同环境条件下的适用性。

5. 性能指标:包括产品的性能特点、技术指标、测试结果等,帮助用户了解产品在各方面的性能表现。

6. 功能特点:包括产品的功能特点、应用范围、优势等,帮助用户了解产品的实际应用场景和优势。

7. 接口和接线方式:包括产品的接口类型、接线方式等,帮助用户了解产品的接口兼容性和使用方式。

8. 认证和符合性:包括产品的认证标准、符合性要求等,帮助用户了解产品是否符合相关的国际和行业标准。

9. 附件和配件:包括产品的附件和配件清单,帮助用户了解产品的配套资源和可扩展性。

三、如何理解和使用技术参数datasheet为了更好地理解和使用技术参数datasheet,用户可以采取以下几个步骤:1. 阅读整个技术参数datasheet,了解产品的基本信息和各项技术参数。

看datasheet常用词汇

multiply/division,乘法/除法

-----------------------------

N

nand gate,与非门

navigate,浏览

negation,取反

nesting,嵌套

newly,

* T3 n( `/ I4 l8 l6 P8 F+ w最新的

literal,字面的

loads/unloads,装载/卸载

-----------------------------

M

majority,多数

manner,方式

manual trigger,手动触发

mass erase/page erase,整体擦除/页擦除

matrix,矩阵

denote,表示

derivatives,派生品

desired,期望的

difference,差分

differential mode,微分模式

discussion,讨论

distinguish,区别

distortion,失真

divide/remainder,整除/取余

divider,分频器

division factor,分频系数

divisor and dividend,除数和被除数

double-click,双击

drag,拖动

drift,飘移

Dual Universal Synchronous Asynchronous Receiver Transmitter,DUSART,双路同步/异步收发器

comment,注释

common-mode,共模

comparison,比较

SWCG9723A 锂离子电池充电器 Datasheet说明书

and Reliable Chargering General DescriptionThe SWCG9723A is a compact and efficient Lithium ion(Li+) or Lithium ion polymer (Li+/polymer) battery charger. It can provide power and charge the signle cell battery of a system typically found in compact portable device. An internal switching buck converter regulates the supply input for charging the battery and powering the system even if the battery is absent. The converter can also operate as a simple pass-through switch with no switching if the load and input voltages are close.A typical application circuit is shown in Figure 2. The SWCG9723A features resistor programmable constant current and constant voltage charging capability plus a charge limiting timer and operates in compliance with the BAJ/JEITA safety guide. An NTC (β=3950K) can be used for battery temperature sensing on top of the internal junction temperature sensing on top of the internal junction temperature monitoring. The IND status output pin can be connected to LEDs to indicate the operating conditions,such as power input ok(POK), in charging(CHG), VIN over-voltage(POK and CHG alternate blinking) and no power/disabled (OFF). Voltage fold-back on the output is provided to power the system from the input while retaining battery charge and prventing overcharge. Input under-voltage regulation is implemented by reducing the load current such that VIN stays above a minimum when the source is weak. Similarly,the die temperature can be regulated and limited by reducing output power to avoid device or the circuit SWCG9723ACompact Switch Li+/Poly Battery Charger Safe board being overheated.These features simplify the system design and ensure safe and reliable operation as well as improved user experience.The SWCG9723A is delivered in a Green TDFN-2X3-8BL package. The device operates in -40'C to +85'C two two thermal regulation options for +55'C or for +115'C.Features Applications˙Constant Current, Constant Voltage(CCCV)˙Powering and Charge Control ofCharging with Floating Time-Out TimerSystems with 500mAh to 6000mAh ˙Maximum 2.3A Charging for 4.2V to 4.5V Battery Li+/Polymer Batteries˙1.34MHz Switching Frequency˙Programmable Charge Voltage and Current˙4.15V input Voltage Regulation Package˙Output Voltage Fold-Back Charge Retaining ˙TDFN-2X3-8BL˙Thermal Regulation Optins˙Typical Peak Efficiency of 92% at 1.5A, V IN =5V ˙-40'C to +85'C Operating Temperature RangeTDFN-2X3-8BLFigure 1. Package Type of SWCG9723AStar-wingPin ConfigurationFigure 2. Pin Configuration of SWCG9723A (Top View )Pin Function TableTDFN2X3-8BL Pin Name TYPE1SW O 2IND O 3CVICharge current Programming/Charge-Inhibit Input Pin. Connect a resistor between this pin and GND to program the constant chargeSWCG9723APin FunctionBuck Converter Switching Node. Connect to the output inductor Status Indication Output. It can source or sink constant current when powered (Charging or not charging). It can only sink current if no power is applied.Charge Voltage Programming Input Pin. Connect a resistor between this pin and ground to select one of the 7 charging voltages.4CC I5VBAT I 6NTC I 7VIN P 8GND G Exposed PadEPICFunctional Block Diagramcurrent I CC . (R CCSET =K/I CC ). Pull up this pin to a voltage higher than V INH to inhibit and stop charging.Battery Voltage Sense Input.NTC Temperature Sensing Input. Connect to an NTC thermistor (β=3950K) with other end grounded and biased to VIN by a 1.5XR NTC25'C resistor. Ground thois pin if NTC is not used.Power Input Pin.Ground Reference Pin.Exposed Pad. Thermal pad is internally grounded and must be connected to the PCB GND plane.Figure 3. Pin Configuration of SWCG9723A (Top View )Star-wingOrdering InformationOrdering CodeMarking IDnote ACBAXXnote A: XX = Date Code and Vendor Code.Absolute Maximum Ratings Note 1Unit V V TDFN2X3-8BLmW SWCG9723AParameterSymbol Value Input Supply Voltage(V VBAT =4V)V IN 6BAT Pin Voltage (V IN Open)V BAT 6450Maximum Power Dissipation P D SWCG9723A-4V2TDN3BLTR-40'C to +85'CTDFN2X3-8BL3000pcs/TRSWCG9723APart NumberTemperature Range Package Quantity per Reel Circuit TypeTR : Tape and Reel Package Types:TDN3BL: TDFN2X3-8BL Voltage: 4V2: 4.2V'C 'C 'C TDFN2X3-8BL 'C/W V V V VRecommend Operating Conditions note1V A 'C 'CNote 1: the "Absolute maximum Ratings" is rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.2: This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection.Supply Voltage Range 3.5 to 5.5V MAX 100090Package Thermal ResistanceQ JA CDM Surge TestESD SusceptibilityHMB, Any Pin to Ground and Power CDMHBM 4000Operating Junction Temperature T J +150Lead Temperature (Soldering, 10s)T LEAD 260Storage Temperature Range T STG -65 to +150Environmental Temperature RangeT OPR-40 to +85Operating Junction Temperature Range T OJT Charge Current Setting RangeI BAT 0.3 to 2.3-40 to +125V ISD Input Over-Voltage Clamp (50mA, 24 hours)Input Surge DischargeV OVC811Electrical Characteristics( V IN =5V, V VBAT =3.8V Full=-40'C to +85'C typical values at T J =25' unless otherwise specified )Symbol Min Type MaxUnitV OVP5.51 5.67 5.84V V CHGm 3.90 4.04 4.17V I Q -1520uA I LKGFLD -0.1 1.5uA I LKG-0.11.5uAV CHG 4.175 4.20 4.225V V STEP -50-mV V DROPm 2.02040mV V DROPM 120170230mV V DEG -50-mV I DEG 273033%DT1616366%DT2555860%DT3202325%DT4151719%V FLT 96.498.099.5%FR 96.797.197.7%V RR 93.995.597.1%I PRE 6597130mA V PRE 566065%I LPCG -300-mA t LPCG 4.055.005.83mS K 91501000010800V V INH - 1.5-V ICC0.9151.001.08ANote 2. Parameters guaranteed by product characterization.ParameterTest Condition Over-Voltage Protection Threshold Minimum Input Operation Voltage V BAT open, V VIN =5V to 6VV BAT open, V VIN =5V to 4V VIN Supply CurrentIND open, fold-back mode,R CV =1KΩ, set V VBAT =4.17V, no switchingR CC =10KΩ, K=I CC XR CCSETFast Charge CurrentR CC =10KΩ, V VBAT =3.8V, V VIN =5V Charge Inhibition Voltage Threshold Charge Current Setting Ratio Voltage forcing on the CC pin to inhibit chargingLoad Pre-charge Period 10'C Threshold note2As percentage of V CHG 45'C Threshold note2Floating Charge Timer Start Threshold Load Pre-charge Current When power-up at V VBAT <60%XV CHGV IN =5V, V VBAT <60%XV CHG Recharge ThresholdBattery Precondition Charge Current Battery Precondition Threshold Voltage Charge Voltage Fold-Back when NTC Temperature is out of 10'C to 45'C Range As percentage of V CHG As percentage of V CHG As percentage of V IN As percentage of V CHG As percentage of V IN As percentage of V IN Compare with V CHG in 10'C to 45'C NTC temperature range Charge Current Decrease at NTC Temperature Regulation note2As percentage of I CC in 10'C to 45'C NTC temperature range 5'C Threshold note2As percentage of V IN 55'C Threshold note2Float-Back Retaining Output Voltage Fold-back mode, R CV =1KΩ, set V VBAT =4.17V, no switching VIN open, V VBAT =3V to 4.5VLeakage Current into the V BATnote2Charg LoopSwitch charge mode, input voltage is greater than V CHGm The Minimum Voltage Drop between V IN and V BAT Required for Switch ChargingLDO charge mode, input voltage is greater than V CHGmCV pin connected to GND-Charge Output Regulation Voltage Charge Voltage StepElectrical Characteristics(Con.)( V IN =5V, V VBAT =3.8V Full=-40'C to +85'C typical values at T J =25' unless otherwise specified )Symbol Min Type MaxUnitI RES 85140190mA t FCOT 7492108min V INREG 3.98 4.15 4.32V T OTR -115-'C T SHUT-155-'C T SHUT_HYST -20-'C t MON155192224msR DS(ON)-H -140200mΩR DS(ON)-L -120180mΩI PEAK - 3.2-A f S1.081.341.56MHzI INDSNK 0.4 1.3 2.5mA I INDSRC 0.4 1.3 2.5mA I BLINK155192224mSNote 2. Parameters guaranteed by product characterization.IND Source Current note2V VIN =5V IND Blink Period note2Input OVP statePWM Switching Frequency-IND Sink Current note2V VIN =5V Indication DrivingHigh-side Switch MOSFET On-Resistance between VIN and SW -Low-side Switch MOSFET On-Resistance between SW and GND -Peak Current Limit -Thermal Shutdown Temperature Temperature increasingThermal Shutdown Hysteresis -BAT Voltage Monitoring Period before Turning into Fold-Back Switch Operation-Input Voltage Regulation Threshold V VBAT =3.8V, V IN for making charge current to 0Thermal Regulation Threshold note2-ParameterTest ConditionCharge Termination Current Threshold -Floating Charge Termination Time -Typical Performance Characteristics(V VIN=5V, V VBAT=3.8V, T J=25'C, unless otherwise noted.)Typical Performance Characteristics (Con.) (V VIN=5V, V VBAT=3.8V, T J=25'C, unless otherwise noted.)Essential SequenceStar-wingTypical Application CircuitsProgrammed for charge Current of I CC =1.47A and Voltage of V CHG =4.2VFigure 6. Typical Application CircuitSWCG9723ATable 1. Bill of Materials for Typical Application CircuitQuantitySizeMaker1TDFN-2X3-8BL Star-wing 1 5.0X5.0X2.0mm iWAS20603SAMSUMG 10603Uniohm 10603Uniohm 20603Uniohm 10603Uniohm10603SunlordFigure 7. Programmed for charge Current of I CC =1.47A and Voltage of V CHG =4.2VDesignatorPart NumberDescriptionU1L1C1, C2R1R2R3, R4R5R6Ind, 2.2uH, Irms=5.0A, Isat=6.5A,DCR=30mΩCap, Cerm, 10uF, 10V, X5R Res, 0Ω, 1%Res, 6.8KΩ, 1%Res, 3.3KΩ, 1%Res, 15KΩ, 1%NTC, 10KΩ, 1%, β=3950K SWCG9723AiSAB0518-2R2M SDNT1608X103F3950FTFSwitch Li+/Poly Battery Charger20603NationstarLED1, LED2Chip Light Emitting Diode, BlueFC-DA1608BK-470H10Function Description and ApplicationFunction Description and Application(Con.)Star-wing Mechanical DimensionsSWCG9723A PKG: TDFN2X3-8BL ( TDN3BL )。

datasheet

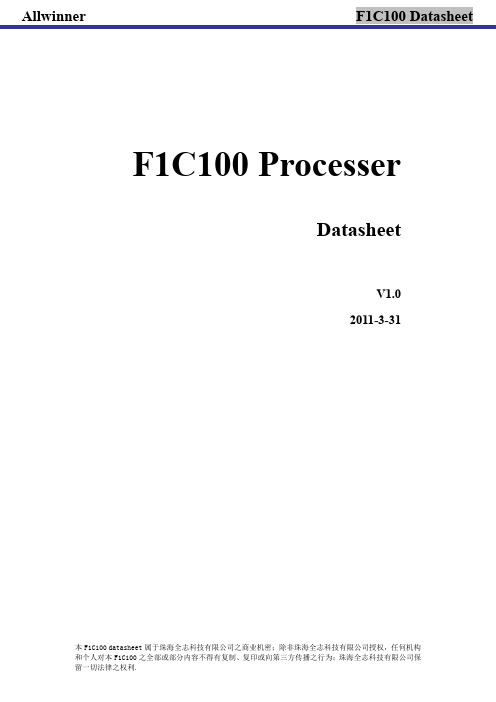

F1C100 ProcesserDatasheetV1.02011-3-31本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.1 Revision History本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.Table of Contents1REVISION HISTORY .................................................................................................................. I I2DESCRIPTION ......................................................................................................................... - 5 -3FEATURE .................................................................................................................................. - 5 -4FUNCTIONAL BLOCK DIAGRAM ...................................................................................... - 7 -5PIN ASSIGNMENT .................................................................................................................. - 8 -6PIN DESCRIPTION ................................................................................................................. - 8 -6.1SDR I NTERFACE P IN (8)6.2NAND F LASH I NTERFACE P IN (10)6.3LCD I NTERFACE P IN (10)6.4USB I NTERFACE P IN (11)6.5T OUCH P ANEL I NTERFACE P IN (11)6.6A UDIO C ODEC I NTERFACE P IN (11)6.7TV-O UT I NTERFACE P IN (12)6.8C LOCK P IN (12)6.9G ENERAL P URPOSE IO P IN (12)6.10M ISCELLANEOUS S IGNAL P IN (12)6.11P OWER AND G ROUND P IN (13)7POWER DOMAIN .................................................................................................................. - 13 -8MODULE DESCRIPTION .................................................................................................... - 13 -8.1C LOCK C ONTROL M ODULE (13)8.1.1CCM Overview............................................................................................................. - 13 -8.1.2CCM Diagram .............................................................................................................. - 15 -8.2I NTERRUPT C ONTROLLER (16)8.2.1Interrupt Overview ....................................................................................................... - 16 -8.2.2Interrupt Diagram ......................................................................................................... - 17 -8.3T IMER (17)8.3.1Timer Overview ............................................................................................................ - 17 -8.3.2Timer Diagram .............................................................................................................. - 18 -8.4P ULSE W IDTH M ODULATOR (18)8.4.1PWM Overview ............................................................................................................ - 18 -8.5DMA . (19)8.5.1DMA Overview ............................................................................................................ - 19 -8.6SDRAM I NTERFACE.. (19)8.6.1DRAM Controller Description ..................................................................................... - 19 -8.7NAND F LASH I NTERFACE .. (20)8.8SD C ARD I NTERFACE (21)8.8.1SD Card Overview ........................................................................................................ - 21 -8.9USB I NTERFACE .. (21)8.9.1USB Overview .............................................................................................................. - 21 -本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.8.10T WO W IRE I NTERFACE (23)8.10.1TWI Controller Description ...................................................................................... - 23 -8.10.2TWI Controller Timing Diagram .............................................................................. - 23 -8.11SPI I NTERFACE . (24)8.11.1SPI Description ......................................................................................................... - 24 -8.11.2SPI Timing Diagram ................................................................................................. - 24 -8.12UART I NTERFACE .. (26)8.12.1UART Overview ....................................................................................................... - 26 -8.12.2UART Timing Diagram ............................................................................................ - 27 -8.13IR I NTERFACE (27)8.13.1IR Overview ............................................................................................................. - 27 -8.13.2IR Timing Diagram................................................................................................... - 29 -8.14A UDIO C ODEC .. (30)8.14.1Description ............................................................................................................... - 30 -8.14.2Feature ...................................................................................................................... - 30 -8.14.3Audio Codec Block Diagram ................................................................................... - 30 -8.15LRADC (31)8.15.1Description ............................................................................................................... - 31 -8.15.2Feature ...................................................................................................................... - 31 -8.16T OUCH P ANEL (31)8.16.1Description ............................................................................................................... - 31 -8.17GPIO I NTERFACE. (32)8.17.1Port Description ........................................................................................................ - 32 -8.17.2Port Configuration Table .......................................................................................... - 32 -8.18TV E NCODER. (34)8.18.1Feature ...................................................................................................................... - 34 -8.18.2Block diagram .......................................................................................................... - 35 -8.19U NIVERSAL LCD/TV T IMING C ONTROLLER.. (35)8.19.1Feature ...................................................................................................................... - 35 -8.20V IDEO D ECODER E NGINE (35)8.20.1Video Decoder Engine Overview ............................................................................. - 35 -9PACKAGE SPECIFICATIONS ............................................................................................. - 38 -本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.2 DescriptionThe F1C100 processor is a highly integrated programmable platform for Media Application. The F1C100 processor contains a rich set of peripherals connected to the ARM926-EJS via several high bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance. The general-purpose peripherals include functions such as USB HS/FS DRD, UART, SPI, TWI, LCD controller, TV encoder, SD/MMC I/F, SDRAM I/F, a watchdog timer. This set of functions satisfies a wide variety of typical system support needs and is augmented by the system expansion capabilities of the part. In addition to these general-purpose peripherals, the processor contains high speed serial and parallel ports for interfacing to a variety of audio and video function.3 FeatureThe systems include the following feature:⏹ARM926-EJS 16KB I-Cache/16KB D-Cache⏹Support 16 bits SDR⏹Two 32-bit Programmed Timers⏹Enhanced 8-CH Direct-Memory-Access Controller⏹Built in Pulse Width Modulator⏹Built in USB 2.0 HS⏹Built in Touch Panel Interface⏹Built in Low Resolution A/D convertor⏹On-chip Sigma-Delta A/D with SNR up to 95dB(A-Weight)⏹On-chip Sigma-Delta D/A and PA with SNR up to 100dB(A-Weight)⏹On-Chip ROM Boot loader⏹Built in HDTV encoder⏹Built in LCD controller⏹Built in IrDA for remote control⏹Built in audio codec for headphone and microphone application⏹Support SLC/MLC NAND flash up to 64bits ECC⏹Support SD/TF/MMC card⏹Fully support PMU application⏹Video Decoder Engine(all format up to 1280*720@30fps)◆H.264Fully compatible with ISO-14496-10 in BP/MP/HPSupports CABAC/CA VLCSupports frame/field/MAFF structureVariable block size(16x16, 16x8, 8x16, 8x8, 8x4, 4x8 and 4x4)◆MPEG-1Fully compatible with ISO/IEC 11172-2 Mpeg1 specification本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.Support I, P, B, D pictures◆MPEG-2Fully compatible with ISO/IEC 13818-2 Mpeg2 specification in Main profileSupport I, P, B picturesSupport field coded picture and frame coded picture◆MPEG-4Fully compatible with ISO-14496-2 SP/ASPSupports GMC up to three wrapping pointsSupports H.264 baseline profileSupports Xvid⏹Package-LQFP128⏹ 3.3V for I/O, and 1.2V for Internal digital circuit本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.4 Functional Block Diagram本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.本F1C100 datasheet 属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.5 Pin AssignmentF1C100 Package Diagram6 Pin Description6.1 SDR Interface Pin本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.6.2 NAND Flash Interface Pin6.3 LCD Interface Pin本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和个人对本F1C100之全部或部分内容不得有复制、复印或向第三方传播之行为;珠海全志科技有限公司保留一切法律之权利.6.4 USB Interface Pin6.5 Touch Panel Interface Pin6.6 Audio Codec Interface Pin本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和6.7 TV-Out Interface Pin6.8 Clock Pin6.9 General Purpose IO Pin6.10 Miscellaneous Signal Pin6.11 Power and Ground Pin7 Power Domain8 Module Description8.1 Clock Control Module8.1.1 CCM OverviewIn the Soc, 6 PLL are built in.本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和●CPU PLL●Display PLL(27MHz~330MHz)●DRAM PLL(60MHz~400MHz)●Audio PLL(24.576MHz or 22.5792MHz)●Video Engine PLL(range: 30MHz~276MHz)●USB PLL(fixed to 480MHz)Only one external 24mhz oscillator is needed for SOC clock.8.1.2 CCM Diagram本F1C100 datasheet属于珠海全志科技有限公司之商业机密;除非珠海全志科技有限公司授权,任何机构和8.2 Interrupt Controller8.2.1 Interrupt OverviewThe interrupt controller has the following feature:●Controls the nIRQ and FIQ of the Processor●Sixty-three individually maskable interrupt sources●One external NMI interrupt source●4-Level Priority Controller● 4 External Sources of Edge-sensitive or Level-sensitive●Fast ForcingIt provides handling of up to sixty-four interrupt sources. The 4-level Priority Controller allows the user to define the priority for each interrupt source, thus permitting higher priority interrupts to be serviced even if a lower priority interrupt is being treated. The fast forcing feature redirects any internal or external source to provide a fast interrupt rather than a normal interrupt.8.2.2 Interrupt Diagram8.3 Timer8.3.1 Timer Overviewhe SOC implements 2 timers.Timer 0 can take their inputs from OSC24M crystal or CLK32K。

AD9850 datasheet 数据手册

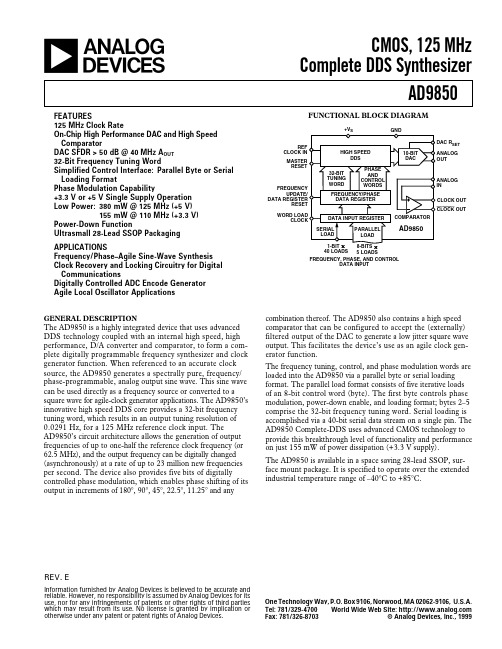

REV.EInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aCMOS, 125 MHzComplete DDS SynthesizerAD9850FUNCTIONAL BLOCK DIAGRAMCLOCK OUTOUTSETREF CLOCK IN MASTER RESETFREQUENCY, PHASE, AND CONTROLDATA INPUTGENERAL DESCRIPTIONThe AD9850 is a highly integrated device that uses advanced DDS technology coupled with an internal high speed, high performance, D/A converter and comparator, to form a com-plete digitally programmable frequency synthesizer and clock generator function. When referenced to an accurate clock source, the AD9850 generates a spectrally pure, frequency/phase-programmable, analog output sine wave. This sine wave can be used directly as a frequency source or converted to a square wave for agile-clock generator applications. The AD9850’s innovative high speed DDS core provides a 32-bit frequency tuning word, which results in an output tuning resolution of 0.0291 Hz, for a 125 MHz reference clock input. TheAD9850’s circuit architecture allows the generation of output frequencies of up to one-half the reference clock frequency (or 62.5 MHz), and the output frequency can be digitally changed (asynchronously) at a rate of up to 23 million new frequencies per second. The device also provides five bits of digitallycontrolled phase modulation, which enables phase shifting of its output in increments of 180°, 90°, 45°, 22.5°, 11.25° and anycombination thereof. The AD9850 also contains a high speed comparator that can be configured to accept the (externally)filtered output of the DAC to generate a low jitter square wave output. This facilitates the device’s use as an agile clock gen-erator function.The frequency tuning, control, and phase modulation words are loaded into the AD9850 via a parallel byte or serial loading format. The parallel load format consists of five iterative loads of an 8-bit control word (byte). The first byte controls phase modulation, power-down enable, and loading format; bytes 2–5comprise the 32-bit frequency tuning word. Serial loading is accomplished via a 40-bit serial data stream on a single pin. The AD9850 Complete-DDS uses advanced CMOS technology to provide this breakthrough level of functionality and performance on just 155 mW of power dissipation (+3.3 V supply).The AD9850 is available in a space saving 28-lead SSOP, sur-face mount package. It is specified to operate over the extended industrial temperature range of –40°C to +85°C.FEATURES125 MHz Clock RateOn-Chip High Performance DAC and High Speed ComparatorDAC SFDR > 50 dB @ 40MHz A OUT 32-Bit Frequency Tuning WordSimplified Control Interface:Parallel Byte or Serial Loading FormatPhase Modulation Capability+3.3 V or +5 V Single Supply Operation Low Power:380 mW @ 125 MHz (+5 V)155 mW @ 110 MHz (+3.3 V)Power-Down FunctionUltrasmall 28-Lead SSOP PackagingAPPLICATIONSFrequency/Phase–Agile Sine-Wave Synthesis Clock Recovery and Locking Circuitry for Digital CommunicationsDigitally Controlled ADC Encode Generator Agile Local Oscillator ApplicationsOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 1999AD9850BRS ParameterTemp Test LevelMin Typ MaxUnitsCLOCK INPUT CHARACTERISTICS Frequency Range +5 V Supply FullIV 1125MHz +3.3 V SupplyFull IV 1110MHz Pulsewidth High/Low +5 V Supply +25°C IV 3.2ns +3.3 V Supply +25°CIV4.1nsDAC OUTPUT CHARACTERISTICS Full-Scale Output Current R SET = 3.9 k Ω+25°C V 10.24mA R SET = 1.95 k Ω+25°C V 20.48mA Gain Error+25°C I –10+10% FS Gain Temperature Coefficient Full V 150ppm/°C Output Offset+25°C I 10µA Output Offset Temperature Coefficient Full V 50nA/°C Differential Nonlinearity +25°C I 0.50.75LSB Integral Nonlinearity+25°C I 0.51LSB Output Slew Rate (50Ω, 2 pF Load)+25°C V 400V/µs Output Impedance +25°C IV 50120k ΩOutput Capacitance +25°C IV 8pF Voltage Compliance+25°C I 1.5V Spurious-Free Dynamic Range (SFDR):Wideband (Nyquist Bandwidth)1 MHz Analog Out +25°C IV 6372dBc 20 MHz Analog Out +25°C IV 5058dBc 40 MHz Analog Out +25°C IV 4654dBc Narrowband40.13579 MHz ± 50 kHz +25°C IV 80dBc 40.13579 MHz ± 200 kHz+25°C IV 77dBc 4.513579 MHz ± 50 kHz/20.5 MHz CLK +25°C IV 84dBc 4.513579 MHz ± 200 kHz/20.5 MHz CLK +25°C IV 84dBc COMPARATOR INPUT CHARACTERISTICS Input Capacitance +25°C V 3pF Input Resistance +25°C IV 500k ΩInput Current+25°C I –12+12µA Input Voltage Range +25°C IV 0V DD V Comparator Offset*Full VI 3030mV COMPARATOR OUTPUT CHARACTERISTICS Logic “1” Voltage +5 V Supply Full VI +4.8V Logic “1” Voltage +3.3 V Supply Full VI +3.1V Logic “0” VoltageFull VI +0.4V Propagation Delay, +5 V Supply (15 pF Load)+25°C V 5.5ns Propagation Delay, +3.3 V Supply (15 pF Load)+25°C V 7ns Rise/Fall Time, +5 V Supply (15 pF Load)+25°C V 3ns Rise/Fall Time, +3.3 V Supply (15 pF Load)+25°C V 3.5ns Output Jitter (p-p)+25°C V 80ps CLOCK OUTPUT CHARACTERISTICS Clock Output Duty Cycle (Clk Gen. Config.)+25°CIV50 ± 10%REV. E–2–(V S= +5 V ؎ 5% except as noted, RSET = 3.9 k ⍀)AD9850–SPECIFICATIONSAD9850AD9850BRSParameter Temp Test Level Min Typ Max Units CMOS LOGIC INPUTS (Including CLKIN)Logic “1” Voltage, +5 V Supply+25°C I 3.5V Logic “1” Voltage, +3.3 V Supply+25°C I 3.0V Logic “0” Voltage+25°C I0.4V Logic “1” Current+25°C I12µA Logic “0” Current+25°C I12µA Input Capacitance+25°C V3pF POWER SUPPLY (A OUT = 1/3 CLKIN)+V S Current @:62.5 MHz Clock, +3.3 V Supply Full VI3048mA110 MHz Clock, +3.3 V Supply Full VI4760mA62.5 MHz Clock, +5 V Supply Full VI4464mA125 MHz Clock, +5 V Supply Full VI7696mAP DISS @:62.5 MHz Clock, +3.3 V Supply Full VI100160mW110 MHz Clock, +3.3 V Supply Full VI155200mW62.5 MHz Clock, +5 V Supply Full VI220320mW125 MHz Clock, +5 V Supply Full VI380480mWP DISS Power-Down Mode+5 V Supply Full V30mW +3.3 V Supply Full V10mW NOTES*Tested by measuring output duty cycle variation.Specifications subject to change without notice.TIMING CHARACTERISTICS*(V S = +5 V ؎ 5% except as noted, R SET = 3.9 k⍀)AD9850BRSParameter Temp Test Level Min Typ Max Unitst DS(Data Setup Time)Full IV 3.5nst DH(Data Hold Time)Full IV 3.5nst WH(W_CLK min. Pulsewidth High)Full IV 3.5nst WL(W_CLK min. Pulsewidth Low)Full IV 3.5nst WD(W_CLK Delay After FQ_UD)Full IV7.0nst CD(CLKIN Delay After FQ_UD)Full IV 3.5nst FH(FQ_UD High)Full IV7.0nst FL(FQ_UD Low)Full IV7.0nst CF(Output Latency from FQ_UD)Frequency Change Full IV18CLKIN Cycles Phase Change Full IV13CLKIN Cycles t FD(FQ_UD Min. Delay After W_CLK)Full IV7.0nst RH(CLKIN Delay After RESET Rising Edge)Full IV 3.5nst RL(RESET Falling Edge After CLKIN)Full IV 3.5nst RS(Minimum RESET Width)Full IV5CLKIN Cycles t OL(RESET Output Latency)Full IV13CLKIN Cycles t RR(Recovery from RESET)Full IV2CLKIN Cycles Wake-Up Time from Power-Down Mode+25°C V5µsNOTES*Control functions are asynchronous with CLKIN.Specifications subject to change without notice.REV. E–3–AD9850–4–REV. EABSOLUTE MAXIMUM RATINGS*Maximum Junction Temperature . . . . . . . . . . . . . . . +165°C V DD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6 V Digital Inputs . . . . . . . . . . . . . . . . . . . . . . . . . –0.7 V to +V S Digital Output Continuous Current . . . . . . . . . . . . . . . 5 mA DAC Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 30 mA Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C Operating Temperature . . . . . . . . . . . . . . . . .–40°C to +85°C Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . +300°C SSOP θJA Thermal Impedance . . . . . . . . . . . . . . . . . . 82°C/W*Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure of absolute maximum rating conditions for extended periods of time may affect device reliability.EXPLANATION OF TEST LEVELSTest Level I –100% Production Tested.III –Sample Tested Only.IV –Parameter is guaranteed by design and characterizationtesting.V –Parameter is a typical value only.VI –All devices are 100% production tested at +25°C.100% production tested at temperature extremes for military temperature devices; guaranteed by design and characterization testing for industrial devices.CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the AD9850 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper E SD precautions are recommended to avoid performance degradation or loss of functionality.Application Note : Users are cautioned not to apply digital input signals prior to power-up of this device. Doing so may r esult in a latch-up condition.ORDERING GUIDEModel Temperature Range Package Description Package Option AD9850BRS–40°C to +85°CShrink Small Outline (SSOP)RS-28AD9850–5–REV. ETable I.Lead Function DescriptionsPin No.Mnemonic Function4–1,D0–D78-Bit Data Input. This is the 8-bit data port for iteratively loading the 32-bit frequency and 8-bit phase/28–25control word. D7 = MSB; D0 = LSB. D7 (Pin 25) also serves as the input pin for the 40-bit serial data word.5, 24DGND Digital Ground. These are the ground return leads for the digital circuitry.6, 23DVDD Supply Voltage Leads for digital circuitry.7W_CLK Word Load Clock. This clock is used to load the parallel or serial frequency/phase/control words.8FQ_UD Frequency Update. On the rising edge of this clock, the DDS will update to the frequency (or phase)loaded in the data input register, it then resets the pointer to Word 0.9CLKIN Reference Clock Input. This may be a continuous CMOS-level pulse train or sine input biased at 1/2V supply. The rising edge of this clock initiates operation.10, 19AGND Analog Ground. These leads are the ground return for the analog circuitry (DAC and comparator).11, 18AVDD Supply Voltage for the analog circuitry (DAC and comparator).12R SETThis is the DAC’s external R SET connection. This resistor value sets the DAC full-scale output current. For normal applications (F S I OUT = 10 mA ), the value for R SET is 3.9 k Ω connected to ground. The R SET /I OUT relationship is: I OUT = 32 (1.248 V/R SET ).13QOUTB Output Complement. This is the comparator’s complement output.14QOUT Output True. This is the comparator’s true output.15VINN Inverting Voltage Input. This is the comparator’s negative input.16VINPNoninverting Voltage Input. This is the comparator’s positive input.17DACBL (NC)DAC Baseline. This is the DAC baseline voltage reference; this lead is internally bypassed and shouldnormally be considered a “no connect” for optimum performance.20IOUTB The Complementary Analog Output of the DAC.21IOUT Analog Current Output of the DAC.22RESETReset. This is the master reset function; when set high it clears all registers (except the input register) and the DAC output will go to Cosine 0 after additional clock cycles—see Figure 19.PIN CONFIGURATIONSD3D7 MSB/SERIAL LOAD D6D5D4D2D1LSB D0RESETDVDDDGND DGND DVDD W CLK FQ UD CLKINAGND AGND IOUTB IOUTAVDD R SET QOUTB QOUT AVDD VINNVINP DACBL (NC)NC = NO CONNECTRBW # 100Hz START 0HzVBW 100HzATN # 30dB SWP 762 secSTOP 62.5MHz Figure 1.SFDR, CLKIN = 125 MHz/f OUT = 1 MHzRBW # 300Hz START 0HzVBW 300Hz ATN # 30dBSWP 182.6 sec STOP 62.5MHzFigure 2.SFDR, CLKIN = 125 MHz/f OUT= 41 MHzCh 1 500mV ⍀M 20.0ns Ch 1 1.58V D 500ps Runs AfterFigure 3.Typical Comparator Output Jitter, AD9850Configured as Clock Generator w/42 MHz LP Filter (40 MHz A OUT /125 MHz CLKIN)AD9850–Typical Performance Characteristics–6–REV. ERBW # 300Hz START 0HzVBW 300HzATN # 30dB SWP 182.6 secSTOP 62.5MHzFigure 4.SFDR, CLKIN = 125 MHz/f OUT = 20 MHzRBW # 3Hz CENTER 4.513579MHzVBW 3Hz ATN # 20dBSWP 399.5 sec SPAN 400kHzFigure 5.SFDR, CLKIN = 20.5 MHz/f OUT = 4.5 MHzOFFSET FROM 5MHz CARRIER – Hz–––––––––––100100k1kd B c10k Figure 6. Output Residual Phase Noise (5 MHz A OUT /125 MHz CLKIN)AD9850–7–REV. ECh1 1.00V ⍀ M 1.00ns Ch 1 1.74V Figure parator Output Rise Time (5 V Supply/15 pF Load)CLKIN – MHz140204060801001206852S F D R – d B66605856546462Figure 8.SFDR vs. CLKIN Frequency (A OUT = 1/3 of CLKIN)FREQUENCY OUT – MHz9080304010S U P P L Y C U R R E N T – m A203070605040Figure 9.Supply Current vs. A OUT Frequency (CLKIN = 125/110 MHz for 5 V/3.3 V Plot)Ch1 1.00V ⍀ M 1.00ns Ch 1 1.74VFigure parator Output Fall Time (5 V Supply/15 pF Load)CLOCK FREQUENCY – MHz0140204060801001209010S U P P L Y C U R R E N T –m A80504030207060Figure 11.Supply Current vs. CLKIN Frequency (A OUT = 1/3 of CLKIN)DAC I OUT – mA205S F D R – d B1015Figure 12.SFDR vs. DAC I OUT (A OUT = 1/3 of CLKIN)AD9850–8–REV. E5-POLE ELLIPTICALFigure 13.Basic AD9850 Clock Generator Application with Low-Pass FilterFigure 14.AD9850 Clock Generator Application in a Spread-Spectrum Receivera.Frequency/Phase –Agile Local Oscillatorb.Frequency/Phase –Agile Reference for PLLREFRFc.Digitally-Programmable ”Divide-by-N “ Function in PLLFigure 15.AD9850 Complete-DDS Synthesizer in Frequency Up-Conversion ApplicationsTHEORY OF OPERATION AND APPLICATIONThe AD9850 uses direct digital synthesis (DDS) technology, in the form of a numerically controlled oscillator, to generate a frequency/phase-agile sine wave. The digital sine wave is con-verted to analog form via an internal 10-bit high speed D/Aconverter, and an onboard high speed comparator is provided to translate the analog sine wave into a low jitter TTL/CMOS-compatible output square wave. DDS technology is an innova-tive circuit architecture that allows fast and precise manipulation of its output frequency under full digital control. DDS also enables very high resolution in the incremental selection of output frequency; the AD9850 allows an output frequency resolution of 0.0291 Hz with a 125 MHz reference clock ap-plied. The AD9850’s output waveform is phase-continuous when changed.The basic functional block diagram and signal flow of theAD9850 configured as a clock generator is shown in Figure 16.The DDS circuitry is basically a digital frequency divider function whose incremental resolution is determined by the frequency of the reference clock divided by the 2N number of bits in the tuning word. The phase accumulator is a variable-modulus counter that increments the number stored in it each time itreceives a clock pulse. When the counter overflows it wraps around, making the phase accumulator’s output contiguous.The frequency tuning word sets the modulus of the counter that effectively determines the size of the increment (∆ Phase) that gets added to the value in the phase accumulator on the next clock pulse. The larger the added increment, the faster the ac-cumulator overflows, which results in a higher output fre-quency. The AD9850 uses an innovative and proprietary algorithm that mathematically converts the 14-bit truncated value of the phase accumulator to the appropriate COS value.This unique algorithm uses a much reduced ROM look-up table and DSP techniques to perform this function, which contributes to the small size and low power dissipation of the AD9850. The relationship of the output frequency, reference clock, and tuning word of the AD9850 is determined by the formula:f OUT = (∆ Phase × CLKIN )/232where:∆ Phase =value of 32-bit tuning wordCLKIN =input reference clock frequency in MHz f OUT =frequency of the output signal in MHz The digital sine wave output of the DDS block drives the inter-nal high speed 10-bit D/A converter that reconstructs the sineAD9850–9–REV. EFigure 16.Basic DDS Block Diagram and Signal Flow of AD9850The reference clock frequency of the AD9850 has a minimum limitation of 1 MHz. The device has internal circuitry that senses when the minimum clock rate threshold has been exceeded and automatically places itself in the power-down mode. When in this state, if the clock frequency again exceeds the threshold,the device resumes normal operation. This shutdown mode prevents excessive current leakage in the dynamic registers of the device.The D/A converter output and comparator inputs are available as differential signals that can be flexibly configured in anymanner desired to achieve the objectives of the end-system. The typical application of the AD9850 is with single-ended output/input analog signals, a single low-pass filter, and generating the comparator reference midpoint from the differential DAC out-put as shown in Figure 13.Programming the AD9850The AD9850 contains a 40-bit register that is used to program the 32-bit frequency control word, the 5-bit phase modulation word and the power-down function. This register can be loaded in a parallel or serial mode.In the parallel load mode, the register is loaded via an 8-bit bus;the full 40-bit word requires five iterations of the 8-bit word.The W_CLK and FQ_UD signals are used to address and load the registers. The rising edge of FQ_UD loads the (up to) 40-bit control data word into the device and resets the address pointer to the first register. Subsequent W_CLK rising edges load the 8-bit data on words [7:0] and move the pointer to the next register. After five loads, W_CLK edges are ignored until either a reset or an FQ_UD rising edge resets the address pointer to the first register.In serial load mode, subsequent rising edges of W_CLK shift the 1-bit data on Lead 25 (D7) through the 40 bits of program-ming information. After 40 bits are shifted through, an FQ_UD pulse is required to update the output frequency (or phase).The function assignments of the data and control words are shown in Table III; the detailed timing sequence for updating the output frequency and/or phase, resetting the device, and powering-up/down, are shown in the timing diagrams of Figures 18–24.Note:There are specific control codes, used for factory test purposes, that render the AD9850 temporarily inoperable. The user must take deliberate precaution to avoid inputting the codes listed in Table II.wave in analog form. This DAC has been optimized for dynamic performance and low glitch energy as manifested in the low jitter performance of the AD9850. Since the output of the AD9850 is a sampled signal, its output spectrum follows the Nyquist sampling theorem. Specifically, its output spectrum contains the fundamental plus aliased signals (images) that occur at multiples of the Reference Clock Frequency ± the selected output frequency. A graphical representation of the sampled spectrum, with aliased images, is shown in Figure 17.REFERENCE CLOCKFREQUENCYFigure 17. Output Spectrum of a Sampled SignalIn this example, the reference clock is 100 MHz and the output frequency is set to 20 MHz. As can be seen, the aliased images are very prominent and of a relatively high energy level as deter-mined by the sin(x)/x roll-off of the quantized D/A converter output. In fact, depending on the fo/Ref Clk relationship, the first aliased image can be on the order of –3dB below the fun-damental. A low-pass filter is generally placed between the out-put of the D/A converter and the input of the comparator to further suppress the effects of aliased images. Obviously, con-sideration must be given to the relationship of the selected output frequency and the Reference Clock frequency to avoid unwanted (and unexpected) output anomalies.A good rule-of-thumb for applying the AD9850 as a clock generator is to limit the selected output frequency to <33% of Reference Clock frequency, thereby avoiding generating aliased signals that fall within, or close to, the output band of interest (generally dc-selected output frequency). This practice will ease the complexity (and cost) of the external filter requirement for the clock generator application.AD9850–10–REV. ETable II.Factory-Reserved Internal Test Control CodesLoading Format Factory-Reserved Codes Parallel 1) W0 = XXXXXX102) W0 = XXXXXX01Serial1) W32 = 1; W33 = 02) W32 = 0; W33 = 13) W32 = 1; W33 = 1Table III.8-Bit Parallel-Load Data/Control Word Functional AssignmentWord data[7]data[6]data[5]data[4]data[3]data[2]data[1]data[0]W0Phase-b4Phase-b3Phase-b2Phase-b1Phase-b0Power-Down Control Control (MSB) (LSB)W1Freq-b31Freq-b30Freq-b29Freq-b28Freq-b27Freq-b26Freq-b25Freq-b24(MSB)W2Freq-b23Freq-b22Freq-b21Freq-b20Freq-b19Freq-b18Freq-b17Freq-b16W3Freq-b15Freq-b14Freq-b13Freq-b12Freq-b11Freq-b10Freq-b9Freq-b8W4Freq-b7Freq-b6Freq-b5Freq-b4Freq-b3Freq-b2Freq-b1Freq-b0(LSB)OLD FREQ (PHASE)NEW FREQ (PHASE)*OUTPUT UPDATE CAN OCCUR AFTER ANY WORD LOAD AND IS ASYNCHRONOUS WITH THE REFERENCE CLOCKDATAW CLKREF CLKCOS OUTFQ UDFigure 18.Parallel-Load Frequency/Phase Update Timing SequenceAD9850COS OUTRESETt RH CLK DELAY AFTER RESET RISING EDGE3.5ns t RLRESET FALLING EDGE AFTER CLK 3.5nst RRRECOVERY FROM RESET 2 CLK CYCLES tRSMINIMUM RESET WIDTH 5 CLK CYCLES t OLRESET OUTPUT LATENCY 13 CLK CYCLESSYMBOL DEFINITION MIN SPECRESULTS OF RESET:– FREQUENCY/PHASE REGISTER SET TO 0– ADDRESS POINTER RESET TO W0– POWER-DOWN BIT RESET TO “0”– DATA INPUT REGISTER UNEFFECTEDFigure 19. Master Reset Timing SequenceDATA (W0)W CLKFQ UDREF CLKDAC STROBEFigure 20.Parallel-Load Power-Down Sequence/Internal OperationDATA (W0)W CLKFQ UDREF CLKFigure 21.Parallel-Load Power-Up Sequence/Internal OperationAD9850DATA (W0)(PARALLEL)W CLK FQ UDARE REQUIRED TO SHIFT IN REQUIRED W32–W34 DATA DATA (SERIAL)REQUIRED TO RESET CONTROL REGISTERSNOTE: FOR DEVICE START-UP IN SERIAL MODE, HARD-WIRE LEAD 2 AT “0”, LEAD 3 AT “1”, AND LEAD 4 AT “1”(SEE FIGURE 23).Figure 22.Serial-Load Enable SequenceFigure 23.Leads 2–4 Connection for Default Serial-Mode OperationDATA–W CLKFQ UDFigure 24.Serial-Load Frequency/Phase Update Sequence Table IV.40-Bit Serial-Load Word Function AssignmentW0Freq-b0 (LSB) W1Freq-b1W2Freq-b2W3Freq-b3W4Freq-b4W5Freq-b5W6Freq-b6W7Freq-b7W8Freq-b8W9Freq-b9W10Freq-b10W11Freq-b11W12Freq-b12W13Freq-b13W28Freq-b28W29Freq-b29W30Freq-b30W31Freq-b31 (MSB)W32ControlW33ControlW34Power-DownW35Phase-b0 (LSB)W36Phase-b1W37Phase-b2W38Phase-b3W39Phase-b4 (MSB) W14Freq-b14W15Freq-b15W16Freq-b16W17Freq-b17W18Freq-b18W19Freq-b19W20Freq-b20W21Freq-b21W22Freq-b22W23Freq-b23W24Freq-b24W25Freq-b25W26Freq-b26W27Freq-b27AD9850DATA (7) –W CLKFQUDFigure 25.Serial-Load Power-Down SequenceDIGITALINV DAC Output Comparator Output Comparator Input Digital InputsFigure 26.AD9850 I/O Equivalent CircuitsPCB LAYOUT INFORMATIONThe AD9850/CGPCB and AD9850/FSPCB evaluation boards (Figures 27–30) represent typical implementations of the AD9850 and exemplify the use of high frequency/high resolu-tion design and layout practices. The printed circuit board that contains the AD9850 should be a multilayer board that allows dedicated power and ground planes. The power and ground planes should be free of etched traces that cause discontinuities in the planes. It is recommended that the top layer of the multi-layer board also contain interspatial ground plane, which makes ground available for surface-mount devices. If separate analog and digital system ground planes exist, they should be con-nected together at the AD9850 for optimum results.Avoid running digital lines under the device as these will couple noise onto the die. The power supply lines to the AD9850should use as large a track as possible to provide a low-impedance path and reduce the effects of glitches on the power supply line.Fast switching signals like clocks should be shielded withground to avoid radiating noise to other sections of the board.Avoid crossover of digital and analog signal paths. Traces on opposite sides of the board should run at right angles to each other. This will reduce the effects of feedthrough through the circuit board. Use microstrip techniques where possible.Good decoupling is also an important consideration. The analog (AVDD) and digital (DVDD) supplies to the AD9850 are independent and separately pinned out to minimize coupling between analog and digital sections of the device. All analog and digital supplies should be decoupled to AGND and DGND,respectively, with high quality ceramic capacitors. To achieve best performance from the decoupling capacitors, they should be placed as close as possible to the device, ideally right upagainst the device. In systems where a common supply is used to drive both the AVDD and DVDD supplies of the AD9850, it is recommended that the system’s AVDD supply be used.Analog Devices, Inc., applications engineering support is avail-able to answer additional questions on grounding and PCB layout. Call 1-800-ANALOGD.Evaluation BoardsTwo versions of evaluation boards are available for the AD9850,which facilitate the implementation of the device for bench-top analysis, and serve as a reference for PCB layout. The AD9850/FSPCB is intended for applications where the device will primarily be used as frequency synthesizer. This version facilitates connection of the AD9850’s internal D/A converter output to a 50Ω spectrum analyzer input; the internal com-parator on the AD9850 DUT is not enabled (see Figure 28 for electrical schematic of AD9850/FSPCB). The AD9850/CGPCB is intended for applications using the device in the clock genera-tor mode. It connects the AD9850’s DAC output to the internal comparator input via a single-ended, 42 MHz low-pass, 5-pole Elliptical filter. This model facilitates the access of the AD9850’s comparator output for evaluation of the device as a frequency- and phase-agile clock source (see Figure 29 for electrical schematic of AD9850/CGPCB).Both versions of the AD9850 evaluation boards are designed to interface to the parallel printer port of a PC. The operating software runs under Microsoft ® Windows and provides a user-friendly and intuitive format for controlling the functionality and observing the performance of the device. The 3.5" floppy provided with the evaluation board contains an executable file that loads and displays the AD9850 function-selection screen.The evaluation board may be operated with +3.3 V or +5 V supplies. The evaluation boards are configured at the factory for an external reference clock input; if the onboard crystal clock source is used, remove R2.All trademarks are the property of their respective holders.。

型号后缀含义和datasheet

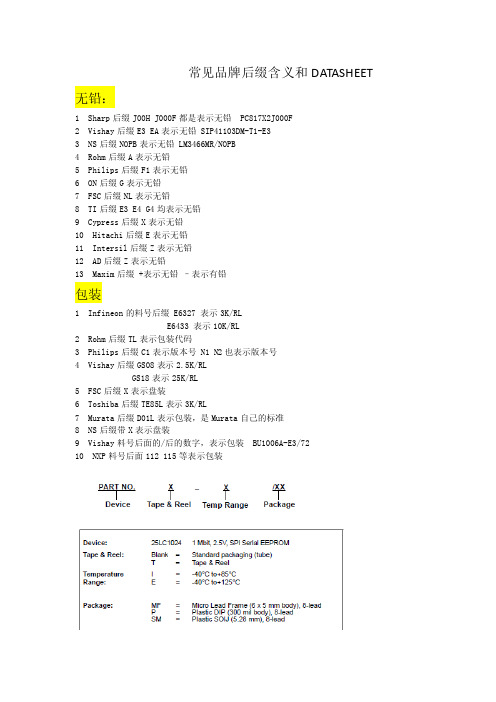

常见品牌后缀含义和DATASHEET 无铅:1 Sharp后缀J00H J000F都是表示无铅 PC817X2J000F2 Vishay后缀E3 EA表示无铅 SIP41103DM-T1-E33 NS后缀NOPB表示无铅 LM3466MR/NOPB4 Rohm后缀A表示无铅5 Philips后缀F1表示无铅6 ON后缀G表示无铅7 FSC后缀NL表示无铅8 TI后缀E3 E4 G4均表示无铅9 Cypress后缀X表示无铅10 Hitachi后缀E表示无铅11 Intersil后缀Z表示无铅12 AD后缀Z表示无铅13 Maxim后缀 +表示无铅–表示有铅包装1 Infineon的料号后缀 E6327 表示3K/RLE6433 表示10K/RL2 Rohm后缀TL表示包装代码3 Philips后缀C1表示版本号 N1 N2也表示版本号4 Vishay后缀GS08表示2.5K/RLGS18表示25K/RL5 FSC后缀X表示盘装6 Toshiba后缀TE85L表示3K/RL7 Murata后缀D01L表示包装,是Murata自己的标准8 NS后缀带X表示盘装9 Vishay料号后面的/后的数字,表示包装 BU1006A-E3/7210 NXP料号后面112 115等表示包装MICROCHIPCommercialIndustrialAutomobileMAXIMMils密耳:晶片布局的长度单位1 mil = 千分之一英寸STTI《简爱》是一本具有多年历史的文学着作。

至今已152年的历史了。

它的成功在于它详细的内容,精彩的片段。

在译序中,它还详细地介绍了《简爱》的作者一些背景故事。

从中我了解到了作者夏洛蒂.勃郎特的许多事。

她出生在一个年经济困顿、多灾多难的家庭;居住在一个远离尘器的穷乡僻壤;生活在革命势头正健,国家由农民向工业国过渡,新兴资产阶级日益壮大的时代,这些都给她的小说创作上打上了可见的烙印。

datasheet什么意思

datasheet什么意思标题:datasheet什么意思引言:在现代科技发达的时代,我们接触到了各种各样的电子产品和设备。

在使用这些设备之前,我们通常需要阅读提供的文档,以了解其功能、规格和使用方法。

其中一种常见的文档类型就是datasheet (数据表)。

那么,datasheet到底是什么意思呢?本文将对datasheet的定义、内容和重要性进行详细介绍。

一、定义:Datasheet一词源于英文单词“data”(数据)和“sheet”(表),可以理解为数据表或资料表。

它是一种包含有关特定产品或设备的详细信息的文档。

通常,datasheet由产品制造商或供应商提供,并包含有关产品性能、规格、接口、功能等方面的详细描述。

二、内容:1. 产品概述:Datasheet的第一部分通常包含对产品的整体概述。

这个部分描述了产品的用途、主要特点和目标用户群体等信息。

2. 规格参数:规格参数是datasheet中最重要的部分之一。

它包含了产品的尺寸、重量、功耗、工作温度等物理规格,而且还包括了电气特性,如输入/输出电压、电流、频率等。

3. 接口和功能:这个部分列举了产品的各个接口和按钮,并对它们的功能进行了详细说明。

比如,一个手机的datasheet可能会说明它的屏幕类型、分辨率、摄像头像素以及各种传感器的功能等。

4. 性能评估:一些datasheet会包含产品的性能评估数据,这些数据可以帮助用户了解产品的性能水平。

例如,一款处理器的datasheet可能包含产品的速度、内存容量和图形性能等方面的评估数据。

5. 安装和使用指南:这个部分提供了有关安装和使用产品的详细说明。

它可能包括产品的装配图、软件安装指南以及使用方法和注意事项等。

三、重要性:1. 了解产品:datasheet是了解产品功能和性能的重要途径。

通过仔细阅读datasheet,我们可以对产品的特点有更深入的了解,从而能够更好地选择和使用适合自己需求的产品。

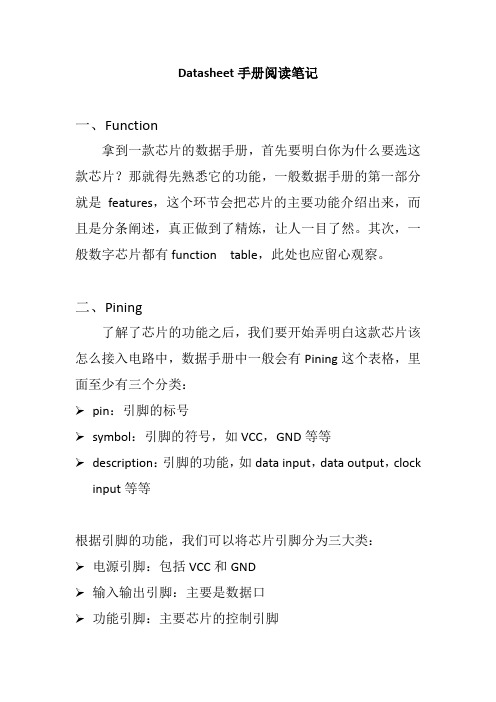

Datasheet手册阅读笔记

Datasheet手册阅读笔记一、Function拿到一款芯片的数据手册,首先要明白你为什么要选这款芯片?那就得先熟悉它的功能,一般数据手册的第一部分就是features,这个环节会把芯片的主要功能介绍出来,而且是分条阐述,真正做到了精炼,让人一目了然。

其次,一般数字芯片都有function table,此处也应留心观察。

二、Pining了解了芯片的功能之后,我们要开始弄明白这款芯片该怎么接入电路中,数据手册中一般会有Pining这个表格,里面至少有三个分类:pin:引脚的标号symbol:引脚的符号,如VCC,GND等等description:引脚的功能,如data input,data output,clock input等等根据引脚的功能,我们可以将芯片引脚分为三大类:电源引脚:包括VCC和GND输入输出引脚:主要是数据口功能引脚:主要芯片的控制引脚三、Recommended operating conditions这个选项会告诉你芯片的一些参数,推荐的使用范围,如果芯片中没有,则留意absolute maximum ratings,将AMR 乘以90%,通常也可作为Recommended值。

四、输入、输出条件注意在什么温度,什么输入电压下,会得到什么输出,留意limiting values,还有DC characters & AC characters,这几个部分,会说明一些输入、输出情况,会告诉你,测试这个芯片的某些值要在什么情况下测才能得到,一般会指明厂家测出这些值时测试芯片的容量,但不是所有的芯片都这样。

五、封装正规芯片都会有封装尺寸,有利于画PCB,通常在画PCB 时,使用这些尺寸时要视情况而定,不一定非得要拿到实物才能开始画,但是一定要留有余地,不能刚刚和那个尺寸一样。

也有些芯片没有这个环节。

一些英文单词:t PHL:从高电平到低电平的传输时间t PLH:从高电平到低电平的传输时间V IK:反向工作电压NOT:非门;AND:与门;OR:或门NAND:与非门;XOR:异或;XNOR:同或;Book:订房间;renew:续借图书;ambient:周围的;T=300℃,Lead Temperature(soldering ,10s):意思是在300℃的温度下焊接,芯片能够承受10s。

datasheet常用词汇

Aabsolute error/relative error,绝对误差/相对误差absolute value,绝对值accidental,意外的active/passive,主动/被动addition/subtraction,加法/减法address, absolute 绝对地址address, base 基底地址addressing modes,寻址模式address strobe 地址选通address transfer 地址传送adjacent,邻近的aims,目的algorithm,运算法则alignment,队列amplitude,振幅and so on,等等approximately,近似的array,数组arbitration,仲裁architecture,体系结构arrangement,排列ascertain,探知assign,指派assignment,分配assume,假设attempt,试图avalanche,雪崩-----------------------------Bbank/segment,(物理/逻辑)段baud rates,波特率bandwidth,带宽behaviour,行为bi-directional,双向big endian/little endian,用来表述一组有序的字节数存放在计算机内存中时的顺序的术语。

big endian是指低地址存放最高有效字节(MSB),也就是将高位字节(序列中最重要的值)先存放在低地址处的顺序;而little endian则是低地址存放最低有效字节(LSB),也就是将低位字节(序列中最不重要的值)先存放在低地址处。

bipolar,双极型bit synchroniser,位同步block mass erase procedure,块擦除程序boundary,边界broaden,变宽buffer,缓冲器be use for,用来做...be used to,习惯于byte accesses/word accesses,字节寻址/字寻址-----------------------------Ccalibrate,校准capability,性能carry out,执行CAS/RAS,Column Address Strobe,列地址控制器/Row Address Strobe,行地址控制器combined,组合comment,注释common-mode,共模comparison,比较compatible,兼容的complement,补码compliant,兼容compensate,补偿compilation,编辑compression,压缩conditional assembly,条件汇编consecutive,连续的consequence,结果constant/variants,常量/变量consumption,消耗convention,协定conversion,转换correctly/incorrectly,正确的/错误的Cyclic Redundancy Check,CRC,循环冗余校验-----------------------------Ddeclares,声明decoupling,退耦decoupling capacitors,退藕电容DC resistance,直流阻抗default state,默认状态demodulate,使解调demonstrate,论证denote,表示derivatives,派生品desired,期望的difference,差分differential mode,微分模式discussion,讨论distinguish,区别distortion,失真divide/remainder,整除/取余divider,分频器division factor,分频系数divisor and dividend,除数和被除数double-click,双击drag,拖动drift,飘移Dual Universal Synchronous Asynchronous Receiver Transmitter,DUSART,双路同步/异步收发器due to,由于dummy,哑元duty cycle,占空比dynamic performance,动态性能-----------------------------EElementary Time Unit,etu,基本时间单元eliminate,消除emulation,仿真enumerations,枚举equality/inequality,相等/不等execute,执行event,事件every other,每隔exceed,超过expression,表达式extend/extension,扩展(名)External Host Interface,EHI,外部主控接口-----------------------------Llatch,锁存latency,延迟lead-in/lead-out,导入/导出leading/trailing,前导/拖尾leakage inductance,漏感limitation,限制linearity,线性literal,字面的loads/unloads,装载/卸载-----------------------------Mmajority,多数manner,方式manual trigger,手动触发mass erase/page erase,整体擦除/页擦除matrix,矩阵Memory Management Unit,MMU,存储器管理单元memory mapped peripherals,MMP,存储器映射外设metastable,亚稳态的Miller effect,密勒效应mimic,模拟minus,负数modulate/demodulate,调制/解调modulate/unmodulate,调制/未调制most significant bit(MSB)/least significant bit(LSB),最高有效位/最低有效位multiplexed,多路复用multi-drop,多从multi-master,多主multiplexer,多路复用器multiply/division,乘法/除法-----------------------------Nnand gate,与非门navigate,浏览negation,取反nesting,嵌套newly,* T3 n( `/ I4 l8 l6 P8 F+ w最新的non-volatile,非易失性-----------------------------Oobtain,获得odd/even,奇/偶operand,操作数organisation,结构-----------------------------Ppacket,信息包pad out,拉长page erase procedure,页擦除程序pane,长方块parallel,并行parenthese,圆括号parity,奇偶pattern,模型pending,未决的photovoltaic generators,光藕pipeline,管道pointer,指针polarity,极性polling,轮流查询potentially,潜在的power down,节电power-on reset,上电复位prefix/suffix,前缀/后缀preload/load/reload,预装载/装载/重装载preprocessor,预处理程序prevent,防止prevent from,阻止primary/sencondary,初级/次级procedure,手续proceed,进程program counter (PC),程序计数器progress,进行propagate,传播properties,道具proportional,均衡的protocol,协议provisionally,临时的pull-up/pull-down,上拉/下拉-----------------------------Qquartz crystal oscillator,石英晶体振荡器queue,队列quotient and remainder,商和余数-----------------------------RRead Strobe/Write Strobe,读选通/写选通reallocation,再分配recognition,识别recoverable,可重获的recursion,递归reentrant,重入refresh,刷新relative,相关的rely on,依赖replace,替换representation,表示法resident,常驻的resource,资源respective,分别response,回应responsibility,职责retention,保持reuse,重新使用reversed,翻转rise/fall,上升/下降ripple,纹波row/column,行/列-----------------------------Ssample/oversample,采样/过采样saturation,饱和状态scheme,计划semi-automate,半自动化Serial Peripheral Interface (SPI),串行外围接口series impedance,串联阻抗Signal to Noise Ratio,信噪比simulator and emulator,模拟器和仿真器simultaneous,同时发生的。

datasheet

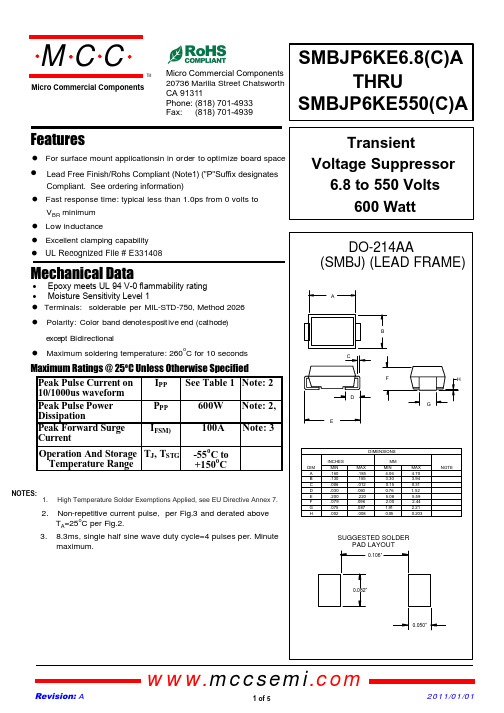

FeaturesFor surface mount applicationsin in order to optimize board spaceFast response time: typical less than 1.0ps from 0 volts toV BR minimum Low inductanceMechanical DataTerminals: solderable per MIL-STD-750, Method 2026Polarity: Color band denotes p ositive end (cathode)e xce pt BidirectionalMaximum soldering temperature: 260oC for 10 secondsMaximum Ratings @ 25o C Unless Otherwise Specified Peak Pulse Current on 10/1000us waveform I PP See Table 1 Note:2Peak Pulse Power DissipationP PP 600W Note:2, Peak Forward Surge CurrentI FSM) 100A Note: 3Operation And Storage Temperature RangeT J , T STG -55o C to +150o CNOTES:2. Non-repetitive current pulse, per Fig.3 and derated aboveT A =25o C per Fig.2. Excellent clamping capability omp onents 20736 Marilla Street Chatsworth! "# $ % ! "#UL Recognized File # E 331408TMMicro Commercial Componentswww.mccsemi .com1 of 5Revision: A 2011/01/01• Lead Free Finish/Rohs Compliant (Note1) ("P"Suffix designatesCompliant. See ordering information)3. 8.3ms, single half sine wave duty cycle=4 pulses per. Minute maximum.1. High Temperature Solder Exemptions Applied, see EU Directive Annex 7.• Epoxy meets UL 94 V-0 flammability rating • Moisture Sensitivity Level 1ELECTRICAL CHARACTERISTICS @25°CMCC PART NUMBERREVERSESTAND-OFFVOLTAGEV WMBREAKDOWN VOLTAGEV(BR) @ I T(VOLTS)MAXIMUMCLAMPINGVOLTAGE @I PPPEAK PULSECURRENTI PPMAXIMUMREVERSELEAKAGE@V WMI DMARKINGCODE(VOLTS)MINMAXI T (mA) (VOLTS) (AMPS) (µA)SMBJP6KE6.8A 5.80 6.457.1410 10.5 58.1 1000 6V8ASMBJP6KE7.5A 6.40 7.137.8810 11.3 54.0 500 7V5ASMBJP6KE8.2A7.02 7.798.6110 12.1 50.4 200 8V2ASMBJP6KE9.1A7.78 8.659.55 1 13.4 45.5 50 9V1ASMBJP6KE10A8.55 9.5010.50114.5 42.1 10 10ASMBJP6KE11A9.40 10.5011.60115.6 39.1 5 11A SMBJP6KE12A10.20 11.4012.60116.7 36.5 512ASMBJP6KE13A11.10 12.4013.70118.2 33.5 513ASMBJP6KE15A12.80 14.3015.80121.2 28.8 515ASMBJP6KE16A13.60 15.2016.80122.5 27.1 516ASMBJP6KE18A15.30 17.1018.90125.5 24.2 518ASMBJP6KE20A17.10 19.0021.00127.7 22.0 520ASMBJP6KE22A18.80 20.9023.10130.6 19.9 522ASMBJP6KE24A20.50 22.8025.20133.2 18.4 524ASMBJP6KE27A23.10 25.7028.40137.5 16.3 527ASMBJP6KE30A25.60 28.5031.50141.4 14.7 530ASMBJP6KE33A28.20 31.4034.70145.7 13.3 533ASMBJP6KE36A30.80 34.2037.80149.9 12.2 536ASMBJP6KE39A33.30 37.1041.00153.9 11.3 539ASMBJP6KE43A36.80 40.9045.20159.3 10.3 543ASMBJP6KE47A40.20 44.7049.40164.8 9.4 547ASMBJP6KE51A43.60 48.5053.60170.1 8.7 551ASMBJP6KE56A47.80 53.2058.80177.0 7.9 556ASMBJP6KE62A53.00 58.9065.10185.0 7.2 562ASMBJP6KE68A58.10 64.6071.40192.0 6.6 568ASMBJP6KE75A64.10 71.3078.801103.0 5.9 575ASMBJP6KE82A70.10 77.9086.101113.0 5.4 582ASMBJP6KE91A77.80 86.5095.501125.0 4.9 591ASMBJP6KE100A85.50 95.00105.001137.0 4.5 5100ASMBJP6KE110A94.00 105.00116.001152.0 4.0 5110ASMBJP6KE120A102.00 114.00126.001165.0 3.7 5120ASMBJP6KE130A111.00 124.00137.001179.0 3.4 5130ASMBJP6KE150A128.00 143.00158.001207.0 2.9 5150ASMBJP6KE160A136.00 152.00168.001219.0 2.8 5160ASMBJP6KE170A145.00 162.00179.001234.0 2.6 5170ASMBJP6KE180A154.00 171.00189.001246.0 2.5 5180ASMBJP6KE200A171.00 190.00210.001274.0 2.2 5200ASMBJP6KE220A185.00 209.00231.001328.0 1.9 5220ASMBJP6KE250A214.00 237.00263.001344.0 1.9 5250ASMBJP6KE300A256.00 285.00315.001414.0 1.5 5300ASMBJP6KE350A300.00 332.00368.001482.0 1.3 5350ASMBJP6KE400A342.00 380.00420.001548.0 1.1 5400ASMBJP6KE440A376.00 418.00462.001602.0 1.0 5440ASMBJP6KE480A408.00 456.00504.001658.0 0.9 5480ASMBJP6KE510A434.00 485.00535.001698.0 0.9 5510ASMBJP6KE530A477.00 503.50556.501725.0 0.8 5530ASMBJP6KE540A459.00 513.00567.001740.0 0.8 5540ASMBJP6KE550A495.00 522.50577.501760.0 0.8 5550AFor bi-directional type having V rwm of 10 volts and less, the I R limit is double.The available parts are “A” type only, the parts without A (V BR is f10%) is not available.Micro Commercial Components2 of 5Revision: A 2011/01/01ELECTRICAL CHARACTERISTICS @25°CMCC PART NUMBERREVERSESTAND-OFFVOLTAGEV WMBREAKDOWN VOLTAGEV(BR) @ I T(VOLTS)MAXIMUMCLAMPINGVOLTAGE @I PPPEAK PULSECURRENTI PPMAXIMUMREVERSELEAKAGE@V WMI DMARKINGCODE(VOLTS)MINMAXI T (mA) (VOLTS) (AMPS) (µA)SMBJP6KE6.8CA 5.80 6.457.1410 10.5 58.1 1000 6V8CSMBJP6KE7.5CA 6.40 7.137.8810 11.3 54.0 500 7V5CSMBJP6KE8.2CA7.02 7.798.6110 12.1 50.4 200 8V2CSMBJP6KE9.1CA7.78 8.659.55 1 13.4 45.5 50 9V1CSMBJP6KE10CA8.55 9.5010.50114.5 42.1 10 10CSMBJP6KE11CA9.40 10.5011.60115.6 39.1 5 11C SMBJP6KE12CA10.20 11.4012.60116.7 36.5 512CSMBJP6KE13CA11.10 12.4013.70118.2 33.5 513CSMBJP6KE15CA12.80 14.3015.80121.2 28.8 515CSMBJP6KE16CA13.60 15.2016.80122.5 27.1 516CSMBJP6KE18CA15.30 17.1018.90125.5 24.2 518CSMBJP6KE20CA17.10 19.0021.00127.7 22.0 520CSMBJP6KE22CA18.80 20.9023.10130.6 19.9 522CSMBJP6KE24CA20.50 22.8025.20133.2 18.4 524CSMBJP6KE27CA23.10 25.7028.40137.5 16.3 527CSMBJP6KE30CA25.60 28.5031.50141.4 14.7 530CSMBJP6KE33CA28.20 31.4034.70145.7 13.3 533CSMBJP6KE36CA30.80 34.2037.80149.9 12.2 536CSMBJP6KE39CA33.30 37.1041.00153.9 11.3 539CSMBJP6KE43CA36.80 40.9045.20159.3 10.3 543CSMBJP6KE47CA40.20 44.7049.40164.8 9.4 547CSMBJP6KE51CA43.60 48.5053.60170.1 8.7 551CSMBJP6KE56CA47.80 53.2058.80177.0 7.9 556CSMBJP6KE62CA53.00 58.9065.10185.0 7.2 562CSMBJP6KE68CA58.10 64.6071.40192.0 6.6 568CSMBJP6KE75CA64.10 71.3078.801103.0 5.9 575CSMBJP6KE82CA70.10 77.9086.101113.0 5.4 582CSMBJP6KE91CA77.80 86.5095.501125.0 4.9 591CSMBJP6KE100CA85.50 95.00105.001137.0 4.5 5100C SMBJP6KE110CA94.00 105.00116.001152.0 4.0 5110C SMBJP6KE120CA102.00 114.00126.001165.0 3.7 5120C SMBJP6KE130CA111.00 124.00137.001179.0 3.4 5130C SMBJP6KE150CA128.00 143.00158.001207.0 2.9 5150C SMBJP6KE160CA136.00 152.00168.001219.0 2.8 5160C SMBJP6KE170CA145.00 162.00179.001234.0 2.6 5170C SMBJP6KE180CA154.00 171.00189.001246.0 2.5 5180C SMBJP6KE200CA171.00 190.00210.001274.0 2.2 5200C SMBJP6KE220CA185.00 209.00231.001328.0 1.9 5220C SMBJP6KE250CA214.00 237.00263.001344.0 1.9 5250C SMBJP6KE300CA256.00 285.00315.001414.0 1.5 5300C SMBJP6KE350CA300.00 332.00368.001482.0 1.3 5350C SMBJP6KE400CA342.00 380.00420.001548.0 1.1 5400C SMBJP6KE440CA376.00 418.00462.001602.0 1.0 5440C SMBJP6KE480CA408.00 456.00504.001658.0 0.9 5480C SMBJP6KE510CA434.00 485.00535.001698.0 0.9 5510C SMBJP6KE530CA477.00 503.50556.501725.0 0.8 5530C SMBJP6KE540CA459.00 513.00567.001740.0 0.8 5540C SMBJP6KE550CA495.00 522.50577.501760.0 0.8 5550CFor bi-directional type having V rwm of 10 volts and less, the I R limit is double.The available parts are “A” type only, the parts without A (V BR is f10%) is not available.Micro Commercial Components3 of 5Revision: A 2011/01/01Micro Commercial Components RATINGS AND CHARACTERISTIC CURVESRevision: A 2011/01/014 of 5Micro Commercial Componentswww.mccsemi .com5 of 5Revision: A 2011/01/013DevicePackingPart Number-TP Tape&Reel: 3Kpcs/ReelOrdering Information :***IMPORTANT NOTICE***Micro Commercial Components Corp. reserve s the right to make changes without further notice to any product herein to make corrections, modifications , enhancements , improvements , or other changes . Micro Commercial Components Corp . does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights ,nor the rights of others . The user of products in such applications shall assume all risks of such use and will agree to hold Micro Commercial Components Corp . and all the companies whose products are represented on our website, harmless against all damages.***LIFE SUPPORT***MCC's products are not authorized for use as critical components in life support devices or systems without the express writtenapproval of Micro Commercial Components Corporation.***CUSTOMER AWARENESS***Counterfeiting of semiconductor parts is a growing problem in the industry. Micro Commercial Components (MCC) is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. MCC strongly encourages customers to purchase MCC parts either directly from MCC or from Authorized MCC Distributors who are listed by country on our web page cited below . Products customers buy either from MCC directly or from Authorized MCC Distributors are genuine parts, have full traceability, meet MCC's quality standards for handling and storage. MCC will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. MCC is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.。

运算放大器datasheet参数详细中文解析

运算放大器datasheet参数详细中文解析

前言输入失调电压V os:输入失调电压的温度漂移(简称输入失调电压温漂)ΔV os/ΔT:输入偏置电流输入失调电流的温度漂移(简称输入失调电流温漂)Δios/ΔT:最大共模输入电压Vcm:共模抑制比CMRR:电源电压抑制比PSRR:输出峰-峰值电压V out:输入阻抗Rin:输出阻抗Rout:开环增益Av:开环带宽:压摆率(转换速率)SR:全功率带宽:

在额定的负载时,运放的闭环增益为1倍条件下,将一个恒幅正弦大信号输入到运放的输入端,使运放输出幅度达到最大(允许一定失真)的信号频率。

这个频率受到运放转换速率的限制。

近似地,全功率带宽=转换速率/2πV op(V op是运放的峰值输出幅度)。

全功率带宽是一个很重要的指标,用于大信号处理中运放选型。

常用运费选型表

下面为从其它地方转载过来的常用运放选型表:

器件名称制造商简介

μA741 TI 单路通用运放

μA747 TI 双路通用运放

AD515A ADI 低功耗FET输入运放

AD605 ADI 低噪声,单电源,可变增益双运放

AD644 ADI 高速,注入BiFET双运放

AD648 ADI 精密的,低功耗BiFET双运放

AD704 ADI 输入微微安培电流双极性四运放

AD705 ADI 输入微微安培电流双极性运放

AD706 ADI 输入微微安培电流双极性双运放

AD707 ADI 超低漂移运放

AD708 ADI 超低偏移电压双运放

AD711 ADI 精密,低成本,高速BiFET运放。

Datasheet中常用英语词汇翻译

106 107 108 地电位 trimmed bandgap 平衡带隙 dropout voltage 压差 large bulk capacitance 大容量电容 circuit breaker 断路器 charge pump 电荷泵