Linear optical setups for active and passive quantum error correction in polarization encod

ZEISS PRESBYOND 激光混合视力矫正手册说明书

Customized. All distances. Immediate.* I n r e f e r e n c e t o c l i n i c a l o u t c o m e s a s c o m p a r e d t o m o n o v i s i o n . D a t a o n f i l e .Blending vision into better outcomes *.ZEISS PRESBYOND Laser Blended VisionZEISS PRESBYOND Laser Blended Vision A clear choice for patients with presbyopiaPRESBYOND ® Laser Blended Vision from ZEISS is an advanced method for treatingpatients with age-related loss of accommodation, also known as presbyopia. It offers the opportunity to achieve freedom from glasses by combining the simplicity and accuracy of corneal refractive surgery with the benefits of increased depth of field in retaining visual quality. As a surgical solution based on the naturally occurring spherical aberrations of the eye, this ZEISS software extends the scope of customized ablation beyond the limits of conventional monovision laser methods in several ways.Whether for its customized treatment profiles, its visual acuity at all distances, its indications range or its immediate impact, ZEISS PRESBYOND Laser Blended Vision is a clear treatment choice for the fast growing demographic of patients with presbyopia.ZEISS PRESBYOND Laser Blended Vision Customized. All distances. Immediate.ZEISS PRESBYOND Laser Blended Vision lets you greatly expand your ZEISS MEL ® 80 or MEL 90 excimer laser treatmentrepertoire and your patient base354Conventional monovisionWith conventional monovision treatment methods, the dominant eye is corrected for distance vision to almost plano while the non-dominant eye is corrected for near vision, usually up to -3.0 D. Optimal vision is achieved at distance and near range, requiring the brain to contend with two separate images at different levels of correction which not all patients cantolerate.Patients that do tolerate the method are left with an uncorrected gap in the intermediate range, the so-called “Blur Zone.” In addition to the fuzzy image, it can also cause other side effects such as reduced contrast sensitivity and stereoacuity.ZEISS PRESBYOND Laser Blended Vision As a physiologically optimized laser treatment method for patients with presbyopia, ZEISS PRESBYOND Laser Blended Vision represents the next stage in eye care excellence. Similar to conventional monovision, the dominant eye is corrected for distance vision to almost plano, whereas the non-dominant eye is corrected to be slightly myopic for near vision to -1.5 D. This micro-monovision strategy is further enhanced by a decisive difference: an increase in the depth of field of each eye using a wavefront-optimized ablation profile to create a continuous refractive power gradient for the whole optical zone of the cornea. This ZEISS software is an absolutely individualized treatment plan based on the preoperative spherical aberrations and the functional age of the eye. As a result, a customized fusion of the two images for near and distance vision is created for each patient – the so-called “Blend Zone.”Although similar to conventional monovision laser methods in terms of the workflow, ZEISS PRESBYOND ® Laser Blended Vision takes customized vision correction a step beyond, particularly with respect to the outcomes.Next-level vision correction beyond conventional monovisionThe unique Blend ZoneEssentially, the Blend Zone makes it easier for the brain to merge the images of both eyes, thereby achieving true binocular vision. In addition to excellent near and far vision, ZEISS PRESBYOND Laser Blended Vision patients also experience very good visual acuity and contrast sensitivity in the intermediate range.No increase in depth of fieldDominant eye±0.0 DNon-dominant eyeup to -3.0 DDISTANCEIncrease in depth of fieldIncrease in depth of fieldDominant eye±0.0 DNon-dominant eye-1.5 DNEARDISTANCENEAR67All distancesCustomizedImmediateOptimizing outcomes for patients with presbyopiaZEISS PRESBYOND Laser Blended VisionIndividualized ablationsZEISS PRESBYOND ® Laser Blended Vision is a truly customized solution for treating presbyopic patients. It incorporates preoperative wavefront data to fine-tune the depth of field for each eye individually. The functional age of the eye is also factored in. As a result, a personalized ablation profile is created per eye for optimized target refraction. The monovision component can be pre-adjusted for the patient’s tolerance level. Also, different optical zone sizes can be selected to account for the patient’s pupil size.Ideal for a growing demographic As an optimized laser method for age-related accommodation loss, ZEISS PRESBYOND Laser Blended Vision is ideally suited for serving the needs of patients 40-60 years of age – a fast-growing demographic group interested in sophisticated options. It is also one of the least invasive methods for addressing this target group.Familiar procedureFollowing the same workflow as conventional LASIK procedures, ZEISS PRESBYOND Laser Blended Vision combines the convenient binocular treatment planning of the CRS-Master ® with the proven comfort and workflow of the MEL ® 80 or MEL 90 excimer laser, all from ZEISS.Outstanding visual acuityBy customizing each eye individually,ZEISS PRESBYOND Laser Blended Vision provides excellent visual acuity for near and distance vision. Unlike traditional monovision methods, PRESBYOND Laser Blended Vision also offers good intermediate vision in the Blend Zone. According to clinical studies, there is virtually no loss of contrast sensitivity while stereoacuity is maintained. Also, side effects such as multiple images in one eye are almost eliminated.An all-natural approachZEISS PRESBYOND Laser Blended Vision is a physiologically optimized solution and a true binocular method for treating patients with presbyopia.Wide indication rangeZEISS PRESBYOND Laser Blended Vision is a proven and effective method for treating indications ranging from -8.0 D to +2.0 D, includingemmetropic and astigmatic patients (up to +2.0 cyl).Appropriate for most patientsA key advantage of ZEISS PRESBYOND Laser Blended Vision is that it is proven to be tolerated by more patients than conventional monovision. It is effective for treating up to 97% of all presbyopia-related forms of impairment as compared to only 59–67% for conventional monovision. Even patients with presbyopia also affected by emmetropia and astigmatism can be treated. In fact, it has the potential to achieve a far greater success rate than any comparable treatment along with giving patients the wow effect of being able to read without glasses the very same day. Thus, it positively impacts patients and refractive surgeons alike – visually for the former, economically for the latter.1-5 A competitive edgeZEISS PRESBYOND Laser Blended Vision allows practices already using a MEL 80 or MEL 90 excimer laser and CRS-Master from ZEISS to significantly expand their LASIK repertoire and increase the patient base. As such, this ZEISS software offers a decisive competitive advantage over other LASIK practices only specializing in monovision treatment methods.MEL 80 and MEL 90 from ZEISSType ArF excimer laser Wavelength 193 nmFrequency MEL 80: 250 HzMEL 90: FLEXIQUENCE ® 250 Hz / 500 Hz Dimensions (W x D x H)MEL 80:1550 mm x 800 mm x 1490 mmMEL 80 with patient supporting system: 3140 mm x 1800 mm x 1490 mm MEL 90:1360 mm x 730 mm x 1480 - 1700 mm MEL 90 with patient supporting system: 3230 mm x 2380 mm x 1700 mmSurgical microscope OPMI ® pico from ZEISS with integratedHD video camera Active eye trackerInfrared, pupil and limbus tracking, 1050 frames per second (fps), manual ablation center selection, automatic Pupil Center Shift Correction Beam dimensions0.7 mm FWHM (full width at half maximum), Gaussian beam profileVisuMax from ZEISSSystem components Patient supporting system, including platformIntegrated uninterruptible power supply (UPS)Surgical microscope with additional slit illumination Video camera with integrated recording Femtosecond laser parametersWavelength 1043 nm Laser pulse rate 500 kHzRecommended space requirements 180° setup with MEL 80 / MEL 90:4500 x 3800 mm90° setup with MEL 80 / MEL 90:4000 x 4000 mm89A perfect combination:The refractive system landscape of ZEISSTechnical dataDimensions (W x D x H)Max. 1060 x 420 x 1510 mmData transfer USB flash memory drive (USB memory stick)Data printoutVia network connection with Ethernet cable and optional network isolatorReferencesClaims made in this document are supported by information provided in the following publications:1. Reinstein DZ, Couch DG, Archer TJ. LASIK for Hyperopic Astigmatism and Presbyopia Using Micro-monovision With the Carl Zeiss Meditec MEL 80. J Refract Surg. 2009;25(1):37-58.2. Reinstein DZ, Archer TJ, Gobbe M. LASIK for Myopic Astigmatism and Presbyopia Using Non-Linear Aspheric Micro-Monovision with the Carl Zeiss Meditec MEL 80 Platform. J Refract Surg. 2011;27(1):23-37.3. Reinstein DZ, Carp GI, Archer TJ, Gobbe M. LASIK for the correction of presbyopia in emmetropic patients using aspheric ablation profiles and a micro-monovision protocol with the Carl Zeiss Meditec MEL 80 and VisuMax. J Refract Surg. 2012 [In Press].4. Reinstein DZ, Archer TJ, Gobbe M. Stereoacuity after Corneal Presbyopic LASIK in Myopic, Hyperopic and Emmetropic Patients. ESCRS Annual Meeting, Vienna, September 2011.5. Evans BJ. Monovision: a review. Ophthalmic Physiol Opt. 2007;27(5):417-439.CRS-Master from ZEISSSimple upgradePRESBYOND ® Laser Blended Vision is an optional software upgrade for the CRS-Master ® from ZEISS. It forms a perfect fit with the ZEISS MEL ® 80 or MEL 90 excimer laser, expanding the repertoire of customized refractive laser corrections far beyond the limits of conventional monovision methods.PRESBYOND Laser Blended Vision and CRS-Master from ZEISS are not intended for sale in the United States.Laser warning sign MEL 80/90Laser warning sign VisuMaxPrecise flapsThe ZEISS VisuMax ® creates flaps of a highly predictable thickness and of adjustable geometries for Femto-LASIK and ZEISS PRESBYOND Laser Blended Vision – the recommended treatment option for patients with presbyopia.Carl Zeiss Meditec AG Goeschwitzer Strasse 51–52 07745 JenaGermany/contacts /presbyond EN_34_1_3IIIPrintedinGermanyCZ-IX/217Thecontentsofthebrochuremaydifferfromthecurrentstatusofapprovaloftheproductorserviceofferinginyourcountry.Pleasecontactourregionalrepresentativesformoreinformation.Subjecttochangesindesignandscopeofdeliveryandduetoongoingtechnicaldevelopment.PRESBYOND,CRS-Master,MELandVisuMaxareeithertrademarksorregisteredtrademarksofCarlZeissMeditecAGorothercompaniesoftheZEISSGroup.©CarlZeissMeditecAG,217.Allrightsreserved.0297。

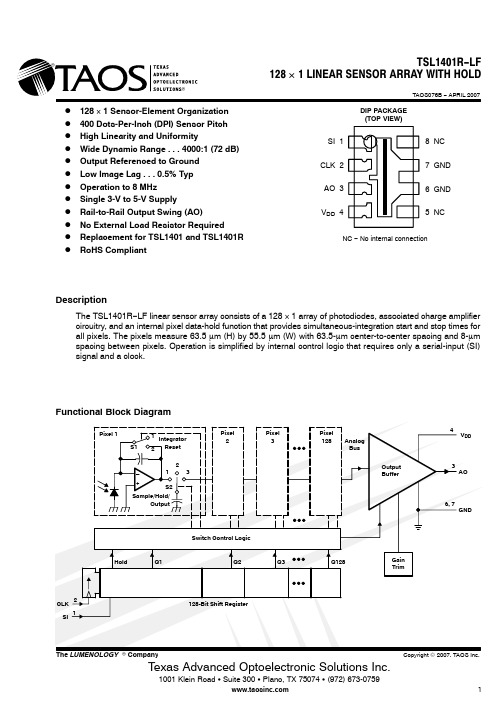

TSL1401R-LF资料

D 128 × 1 Sensor-Element Organization D 400 Dots-Per-Inch (DPI) Sensor Pitch D High Linearity and UniformityD Wide Dynamic Range ...4000:1 (72 dB)D Output Referenced to Ground D Low Image Lag ...0.5% Typ D Operation to 8 MHzD Single 3-V to 5-V SupplyD Rail-to-Rail Output Swing (AO)D No External Load Resistor RequiredD Replacement for TSL1401 and TSL1401R DRoHS CompliantDescriptionThe TSL1401R −LF linear sensor array consists of a 128 × 1 array of photodiodes, associated charge amplifier circuitry, and an internal pixel data-hold function that provides simultaneous-integration start and stop times for all pixels. The pixels measure 63.5 μm (H) by 55.5 μm (W) with 63.5-μm center-to-center spacing and 8-μm spacing between pixels. Operation is simplified by internal control logic that requires only a serial-input (SI)signal and a clock.Functional Block DiagramNC − No internal connection8 NC 7 GND 6 GND 5 NCDIP PACKAGE (TOP VIEW)SI 1CLK 2AO 3V DD 4TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTerminal FunctionsTERMINAL NAME NO.DESCRIPTIONAO 3Analog output.CLK 2Clock. The clock controls charge transfer, pixel output, and reset.GND 6, 7Ground (substrate). All voltages are referenced to the substrate.NC 5, 8No internal connection.SI 1Serial input. SI defines the start of the data-out sequence.V DD4Supply voltage. Supply voltage for both analog and digital circuits.Detailed DescriptionThe sensor consists of 128 photodiodes arranged in a linear array. Light energy impinging on a photodiode generates photocurrent, which is integrated by the active integration circuitry associated with that pixel.During the integration period, a sampling capacitor connects to the output of the integrator through an analog switch. The amount of charge accumulated at each pixel is directly proportional to the light intensity and the integration time.The output and reset of the integrators is controlled by a 128-bit shift register and reset logic. An output cycle is initiated by clocking in a logic 1 on SI. For proper operation, after meeting the minimum hold time condition,SI must go low before the next rising edge of the clock. An internal signal, called Hold, is generated from the rising edge of SI and transmitted to analog switches in the pixel circuit. This causes all 128 sampling capacitors to be disconnected from their respective integrators and starts an integrator reset period. As the SI pulse is clocked through the shift register, the charge stored on the sampling capacitors is sequentially connected to a charge-coupled output amplifier that generates a voltage on analog output AO. Simultaneously, during the first 18 clock cycles, all pixel integrators are reset, and the next integration cycle begins on the 19th clock. On the 129th clock rising edge, the SI pulse is clocked out of the shift register and the analog output AO assumes a high impedance state. Note that this 129th clock pulse is required to terminate the output of the 128th pixel, and return the internal logic to a known state. If a minimum integration time is desired, the next SI pulse may be presented after a minimum delay of t qt (pixel charge transfer time) after the 129th clock pulse.AO is an op amp-type output that does not require an external pull-down resistor. This design allows a rail-to-rail output voltage swing. With V DD = 5 V, the output is nominally 0 V for no light input, 2 V for normal white level, and 4.8 V for saturation light level. When the device is not in the output phase, AO is in a high-impedance state.The voltage developed at analog output (AO) is given by:V out = V drk + (R e ) (E e )(t int )where:V out is the analog output voltage for white condition V drk is the analog output voltage for dark conditionR e is the device responsivity for a given wavelength of light given in V/(μJ/cm 2)E e is the incident irradiance in μW/cm 2t intis integration time in secondsA 0.1 μF bypass capacitor should be connected between V DD and ground as close as possible to the device.The TSL1401R −LF is intended for use in a wide variety of applications, including: image scanning, mark and code reading, optical character recognition (OCR) and contact imaging, edge detection and positioning, and optical linear and rotary encoding.TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007Absolute Maximum Ratings †Supply voltage range, V DD −0.3 V to 6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input voltage range, V I −0.3 V to V DD + 0.3V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input clamp current, I IK (V I < 0) or (V I > V DD ) −20 mA to 20 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Output clamp current, I OK (V O < 0 or V O > V DD ) −25 mA to 25 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Voltage range applied to any output in the high impedance or power-off state, V O −0.3 V to V DD + 0.3 V . . . Continuous output current, I O (V O = 0 to V DD ) −25 mA to 25 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Continuous current through V DD or GND −40 mA to 40 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Analog output current range, I O −25 mA to 25 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum light exposure at 638 nm 5 mJ/cm 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Operating free-air temperature range, T A −25°C to 85°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Storage temperature range, T stg −25°C to 85°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds ‡ 260°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ESD tolerance, human body model 2000 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . †Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “Recommended Operating Conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.‡Not recommended for solder reflow.Recommended Operating Conditions (see Figure 1 and Figure 2)MINNOMMAX UNIT Supply voltage, V DD 355.5V Input voltage, V I0V DD V High-level input voltage, V IH 2V DD V Low-level input voltage, V IL 00.8V Wavelength of light source, λ4001000nm Clock frequency, f clock58000kHz Sensor integration time, t int (see Note 1)0.03375100ms Setup time, serial input, t su(SI)20ns Hold time, serial input, t h(SI) (see Note 2)0ns Operating free-air temperature, T A70°CNOTES: 1.Integration time is calculated as follows:t int(min) = (128 − 18) y clock period + 20 m swhere 128 is the number of pixels in series, 18 is the required logic setup clocks, and 20 m s is the pixel charge transfer time (t qt )2.SI must go low before the rising edge of the next clock pulse.TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007Electrical Characteristics at f clock = 1 MHz, V DD = 5 V, T A = 25°C, λp = 640 nm, t int = 5 ms,R L = 330 Ω, E e = 11 μW/cm 2 (unless otherwise noted) (see Note 3)PARAMETERTEST CONDITIONS MIN TYP MAX UNIT V out Analog output voltage (white, average over 128 pixels)See Note 4 1.62 2.4V V drk Analog output voltage (dark, average over 128 pixels)E e = 000.10.2VPRNUPixel response nonuniformity See Note 5±4%±7.5%Nonlinearity of analog output voltage See Note 6±0.4%FS Output noise voltageSee Note 71mVrms R e ResponsivitySee Note 8253545V/(μJ/cm 2)V DD = 5 V, R L = 330 Ω 4.5 4.8V sat Analog output saturation voltage V DD = 3 V, R L = 330 Ω 2.5 2.8V V DD = 5 V, See Note 9136nJ/cm SE Saturation exposure V DD = 3 V, See Note 9782DSNU Dark signal nonuniformity All pixels, E e = 0, See Note 100.020.05V IL Image lag See Note 110.5%V DD = 5 V, E e = 0 2.8 4.5I DD Supply current V DD = 3 V, E e = 0 2.64.5mA I IH High-level input current V I = V DD 1μA I IL Low-level input current V I = 01μA C iInput capacitance5pFNOTES: 3.All measurements made with a 0.1 μF capacitor connected between V DD and ground.4.The array is uniformly illuminated with a diffused LED source having a peak wavelength of 640 nm.5.PRNU is the maximum difference between the voltage from any single pixel and the average output voltage from all pixels of thedevice under test when the array is uniformly illuminated at the white irradiance level. PRNU includes DSNU.6.Nonlinearity is defined as the maximum deviation from a best-fit straight line over the dark-to-white irradiance levels, as a percentof analog output voltage (white).7.RMS noise is the standard deviation of a single-pixel output under constant illumination as observed over a 5-second period.8.R e(min) = [V out(min) − V drk(max)] ÷ (E e × t int )9.SE(min) = [V sat(min) − V drk(min)] × 〈E e × t int ) ÷ [V out(max) − V drk(min)]10.DSNU is the difference between the maximum and minimum output voltage for all pixels in the absence of illumination.11.Image lag is a residual signal left in a pixel from a previous exposure. It is defined as a percent of white-level signal remaining aftera pixel is exposed to a white condition followed by a dark condition:IL +V out (IL)*V drkV out (white)*V drk100Timing Requirements (see Figure 1 and Figure 2)MINNOMMAXUNIT t su(SI)Setup time, serial input (see Note 12)20ns t h(SI)Hold time, serial input (see Note 12 and Note 13)0ns t w Pulse duration, clock high or low 50ns t r , t f Input transition (rise and fall) time 0500ns t qtPixel charge transfer time20μsNOTES:12.Input pulses have the following characteristics: t r = 6 ns, t f = 6 ns.13.SI must go low before the rising edge of the next clock pulse.Dynamic Characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figures 7 and 8)PARAMETERTEST CONDITIONS MINTYP MAXUNIT t sAnalog output settling time to ±1%R L = 330 Ω,C L = 10 pF120nsTSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007TYPICAL CHARACTERISTICSCLKSIAOInternal ResetIntegrationFigure 1. Timing WaveformsAOCLKt Figure 2. Operational WaveformsTSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007TYPICAL CHARACTERISTICSFigure 3PHOTODIODE SPECTRAL RESPONSIVITYλ − Wavelength − nm4005006007008009001000110030000.20.40.60.81R e l a t i v e R e s p o n s i v i t yFigure 4NORMALIZED IDLE SUPPLY CURRENTvsFREE-AIR TEMPERATURET A − Free-Air Temperature − °C1030407060I D D — N o r m a l i z e d I d l e S u p p l y C u r r e n t00.511.522050Figure 5WHITE OUTPUT VOLTAGEvsFREE-AIR TEMPERATURET A − Free-Air Temperature − °C00.511.52V o u t — O u t p u t V o l t a g e — V10304070602050Figure 6DARK OUTPUT VOLTAGEvsFREE-AIR TEMPERATURET A − Free-Air Temperature − °C0.060.080.10V o u t — O u t p u t V o l t a g e103040706020500.070.09TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007TYPICAL CHARACTERISTICSFigure 7SETTLING TIMEvs.LOADR L — Load Resistance − WS e tt l i n g T i m e t o 1% — n s100200300400500600Figure 8SETTLING TIMEvs.LOADR L — Load Resistance − WS e tt l i n g T i m e t o 1% — n s2004006008001000100200300400500600TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007APPLICATION INFORMATIONIntegration TimeThe integration time of the linear array is the period during which light is sampled and charge accumulates on each pixel’s integrating capacitor. The flexibility to adjust the integration period is a powerful and useful feature of the TAOS TSL14xx linear array family. By changing the integration time, a desired output voltage can be obtained on the output pin while avoiding saturation for a wide range of light levels.The integration time is the time between the SI (Start Integration) positive pulse and the HOLD positive pulse minus the 18 setup clocks. The TSL14xx linear array is normally configured with the SI and HOLD pins tied together. This configuration will be assumed unless otherwise noted. Sending a high pulse to SI (observing timing rules for setup and hold to clock edge) starts a new cycle of pixel output and integration setup. However,a minimum of (n +1) clocks, where n is the number of pixels, must occur before the next high pulse is applied to SI. It is not necessary to send SI immediately on/after the (n +1) clocks. A wait time adding up to a maximum total of 100 ms between SI pulses can be added to increase the integration time creating a higher output voltage in low light applications.Each pixel of the linear array consists of a light-sensitive photodiode. The photodiode converts light intensity to a voltage. The voltage is sampled on the Sampling Capacitor by closing switch S2 (position 1) (see the Functional Block Diagram on page 1). Logic controls the resetting of the Integrating Capacitor to zero by closing switch S1 (position 2).At SI input, all of the pixel voltages are simultaneously scanned and held by moving S2 to position 2 for all pixels.During this event, S2 for pixel 1 is in position 3. This makes the voltage of pixel 1 available on the analog output.On the next clock, S2 for pixel 1 is put into position 2 and S2 for pixel 2 is put into position 3 so that the voltage of pixel 2 is available on the output.Following the SI pulse and the next 17 clocks after the SI pulse is applied, the S1 switch for all pixels remains in position 2 to reset (zero out) the integrating capacitor so that it is ready to begin the next integration cycle.On the rising edge of the 19th clock, the S1 switch for all the pixels is put into position 1 and all of the pixels begin a new integration cycle.The first 18 pixel voltages are output during the time the integrating capacitor is being reset. On the 19th clock following an SI pulse, pixels 1 through 18 have switch S2 in position 1 so that the sampling capacitor can begin storing charge. For the period from the 19th clock through the n th clock, S2 is put into position 3 to read the output voltage during the n th clock. On the next clock the previous pixel S2 switch is put into position 1 to start sampling the integrating capacitor voltage. For example, S2 for pixel 19 moves to position 1 on the 20th clock. On the n +1clock, the S2 switch for the last (n th ) pixel is put into position 1 and the output goes to a high-impedance state.If a SI was initiated on the n +1 clock, there would be no time for the sampling capacitor of pixel n to charge to the voltage level of the integrating capacitor. The minimum time needed to guarantee the sampling capacitor for pixel n will charge to the voltage level of the integrating capacitor is the charge transfer time of 20 μs.Therefore, after n +1 clocks, an extra 20 μs wait must occur before the next SI pulse to start a new integration and output cycle.The minimum integration time for any given array is determined by time required to clock out all the pixels in the array and the time to discharge the pixels. The time required to discharge the pixels is a constant.Therefore, the minimum integration period is simply a function of the clock frequency and the number of pixels in the array. A slower clock speed increases the minimum integration time and reduces the maximum light level for saturation on the output. The minimum integration time shown in this data sheet is based on the maximum clock frequency of 8 MHz.TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007APPLICATION INFORMATIONThe minimum integration time can be calculated from the equation: T int(min)+ǒ1maximum clock frequency Ǔ (n *18) pixels )20m swhere:nis the number of pixelsIn the case of the TSL1401R −LF with the maximum clock frequency of 8 MHz, the minimum integration timewould be:T int(min)+0.125 m s (128*18))20 m s +33.75 m sIt is good practice on initial power up to run the clock (n +1) times after the first SI pulse to clock out indeterminate data from power up. After that, the SI pulse is valid from the time following (n +1) clocks. The output will go into a high-impedance state after the n +1 high clock edge. It is good practice to leave the clock in a low state when inactive because the SI pulse required to start a new cycle is a low-to-high transition.The integration time chosen is valid as long as it falls in the range between the minimum and maximum limits for integration time. If the amount of light incident on the array during a given integration period produces a saturated output (Max Voltage output), then the data is not accurate. If this occurs, the integration period should be reduced until the analog output voltage for each pixel falls below the saturation level. The goal of reducing the period of time the light sampling window is active is to lower the output voltage level to prevent saturation.However, the integration time must still be greater than or equal to the minimum integration period.If the light intensity produces an output below desired signal levels, the output voltage level can be increased by increasing the integration period provided that the maximum integration time is not exceeded. The maximum integration time is limited by the length of time the integrating capacitors on the pixels can hold their accumulated charge. The maximum integration time should not exceed 100 ms for accurate measurements.It should be noted that the data from the light sampled during one integration period is made available on the analog output during the next integration period and is clocked out sequentially at a rate of one pixel per clock period. In other words, at any given time, two groups of data are being handled by the linear array: the previous measured light data is clocked out as the next light sample is being integrated.Although the linear array is capable of running over a wide range of operating frequencies up to a maximum of 8 MHz, the speed of the A/D converter used in the application is likely to be the limiter for the maximum clock frequency. The voltage output is available for the whole period of the clock, so the setup and hold times required for the analog-to-digital conversion must be less than the clock period.TSL1401R−LF128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007MECHANICAL INFORMATIONThis dual-in-line package consists of an integrated circuit mounted on a lead frame and encapsulated in an electrically nonconductive clear plastic compound.0.040 (1,02)0.015 (0,38)0.125 (3,18)0.053 (1,35)0.043 (1,09)0.175 (4,45)0.155 (3,94)Pixel Coverage (Note C)L PackagePbNOTES: A.All linear dimensions are in inches and (millimeters).B.Index of refraction of clear plastic is 1.55.C.Center of pixel active areas typically located under this line.D.Lead finish is NiPd.E.This drawing is subject to change without notice.Figure 9. Packaging ConfigurationTSL1401R−LF 128 × 1 LINEAR SENSOR ARRAY WITH HOLDTAOS076B − APRIL 2007PRODUCTION DATA — information in this document is current at publication date. Products conform to specifications in accordance with the terms of Texas Advanced Optoelectronic Solutions, Inc. standard warranty. Production processing does not necessarily include testing of all parameters.LEAD-FREE (Pb-FREE) and GREEN STATEMENTPb-Free (RoHS) TAOS’ terms Lead-Free or Pb-Free mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TAOS Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS & no Sb/Br) TAOS defines Green to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).Important Information and Disclaimer The information provided in this statement represents TAOS’ knowledge and belief as of the date that it is provided. TAOS bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TAOS has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TAOS and TAOS suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.NOTICETexas Advanced Optoelectronic Solutions, Inc. (TAOS) reserves the right to make changes to the products contained in this document to improve performance or for any other purpose, or to discontinue them without notice. Customers are advised to contact TAOS to obtain the latest product information before placing orders or designing TAOS products into systems.TAOS assumes no responsibility for the use of any products or circuits described in this document or customer product design, conveys no license, either expressed or implied, under any patent or other right, and makes no representation that the circuits are free of patent infringement. TAOS further makes no claim as to the suitability of its products for any particular purpose, nor does TAOS assume any liability arising out of the use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.TEXAS ADVANCED OPTOELECTRONIC SOLUTIONS, INC. PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN CRITICAL APPLICATIONS IN WHICH THE FAILURE OR MALFUNCTION OF THE TAOS PRODUCT MAY RESULT IN PERSONAL INJURY OR DEATH. USE OF TAOS PRODUCTS IN LIFE SUPPORT SYSTEMS IS EXPRESSLY UNAUTHORIZED AND ANY SUCH USE BY A CUSTOMER IS COMPLETELY AT THE CUSTOMER’S RISK.LUMENOLOGY, TAOS, the TAOS logo, and Texas Advanced Optoelectronic Solutions are registered trademarks of Texas Advanced Optoelectronic Solutions Incorporated.TSL1401R−LF128 ×1 LINEAR SENSOR ARRAY WITH HOLD TAOS076B − APRIL 2007。

NAD 306 Amplifier Service Manual

Ultimate NAD Repair Schematics & Service manual 230 PDF manuals on DVD. C $24.95, Buy It Now, Free Shipping. Only 3 left! 38 Sold. 28d 18h left (10/7. SERVICING TO QUALIFIED. SERVICE PERSONNEL. JP101. JP102. 2. 3. 4. JP 201. JP 202. JP103. JP104. NAD. Stereo Power Amplifier 2200. OVERLOAD.

Audio manuals and audio service pdf instructions. Find the NAD Electronics Stereo Pre-Amplifier DataSheet NAD Stereo Amplifier 306. Original NAD AV316 Amplifier Service Manual NAD dealer catalog 1000 106 214 215 208 310 306 302 304 701 705 800 802 804.

Nad 306 Amplifier Service Manual ===> Download Here

Audiophile vintage NAD 306 integrated stereo amplifier including the original manual. The NAD 306 amplifier delivers 50 watts per channel (8 ohm). Owner's Manual. C 375BEE The primary method of isolating the amplifier from 19 Damage Requiring Service - Unplug this product from the wall outlet.

lis2dh12tr

This is information on a product in full production. May 2017DocID025056 Rev 61/53MEMS digital output motion sensor:ultra-low-power high-performance 3-axis "femto" accelerometerDatasheet - production dataFeatures∙Wide supply voltage, 1.71 V to 3.6 V∙Independent IO supply (1.8 V) and supplyvoltage compatible∙Ultra-low power consumption down to 2 μA∙±2g /±4g /±8g /±16g selectable full scales∙I 2C/SPI digital output interface∙ 2 independent programmable interruptgenerators for free-fall and motion detection∙6D/4D orientation detection∙“Sleep-to-wake” and “return-to-sleep” functions∙Free-fall detection∙Motion detection∙Embedded temperature sensor∙Embedded FIFO∙ECOPACK ®, RoHS and “Green” compliant Applications∙Motion-activated functions∙Display orientation∙Shake control∙Pedometer∙Gaming and virtual reality input devices∙Impact recognition and loggingDescriptionThe LIS2DH12 is an ultra-low-power high-performance three-axis linear accelerometerbelonging to the “femto” family with digital I 2C/SPIserial interface standard output.The LIS2DH12 has user-selectable full scales of ±2g /±4g /±8g /±16g and is capable of measuring accelerations with output data rates from 1 Hz to 5.3 kHz.The self-test capability allows the user to check the functionality of the sensor in the final application.The device may be configured to generate interrupt signals by detecting two independent inertial wake-up/free-fall events as well as by the position of the device itself. The LIS2DH12 is available in a small thin plastic land grid array package (LGA) and is guaranteed to operate over an extended temperature range from -40 °C to +85 °C.找Memory 、FPGA 、二三极管、连接器、模块、光耦、电容电阻、单片机、处理器、晶振、传感器、 滤波器上美光存储技术LIS2DH12List of figures List of figuresFigure 1.Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Figure 2.Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Figure 3.SPI slave timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Figure 4.I2C slave timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Figure 5.LIS2DH12 electrical connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20 Figure 6.Read and write protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Figure 7.SPI read protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Figure 8.Multiple byte SPI read protocol (2-byte example). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Figure 9.SPI write protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 Figure 10.Multiple byte SPI write protocol (2-byte example). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 Figure 11.SPI read protocol in 3-wire mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Figure 12.LGA-12: package outline and mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49 Figure 13.Carrier tape information for LGA-12 package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 Figure 14.LGA-12 package orientation in carrier tape . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 Figure 15.Reel information for carrier tape of LGA-12 package. . . . . . . . . . . . . . . . . . . . . . . . . . . . .51DocID025056 Rev 67/53Block diagram and pin description LIS2DH128/53DocID025056 Rev 61 Block diagram and pin description1.1 Block diagram1.2 Pin descriptionLIS2DH12IMPORTANT NOTICE – PLEASE READ CAREFULLYSTMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers’ products.No license, express or implied, to any intellectual property right is granted by ST herein.Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.Information in this document supersedes and replaces information previously supplied in any prior versions of this document.© 2017 STMicroelectronics – All rights reservedDocID025056 Rev 653/53。

u-blox F9 HPS 1.30产品介绍说明书

u-blox F9 HPS 1.30u-blox F9 high precision sensor fusion GNSS receiver Protocol version 33.30Interface descriptionAbstractThis document describes the interface (version 33.30) of the u-bloxF9 firmware HPS 1.30 platform.UBX-22010984 - R01C1-PublicDocument informationTitle u-blox F9 HPS 1.30Subtitle u-blox F9 high precision sensor fusion GNSS receiver Document type Interface descriptionDocument number UBX-22010984Revision and date R0116-Sep-2022 Disclosure restriction C1-Publicu-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this document. Copying, reproduction, or modification of this document or any part thereof is only permitted with the express written permission of u-blox. Disclosure to third parties is permitted for clearly public documents only.The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit .Copyright © 2022, u-blox AG.Contents1 General information (14)1.1 Document overview (14)1.2 Firmware and protocol versions (14)1.3 Receiver configuration (16)1.4 Message naming (17)1.5 GNSS, satellite, and signal identifiers (17)1.5.1 Overview (17)1.5.2 GNSS identifiers (18)1.5.3 Satellite identifiers (18)1.5.4 Signal identifiers (19)1.6 Message types (20)2 NMEA protocol (21)2.1 NMEA frame structure (21)2.2 NMEA protocol configuration (21)2.3 NMEA-proprietary messages (22)2.4 NMEA multi-GNSS operation (23)2.5 NMEA data fields (23)2.5.1 NMEA Talker ID (23)2.5.2 NMEA extra fields (23)2.5.3 NMEA latitude and longitude format (24)2.5.4 NMEA GNSS, satellite, and signal numbering (24)2.5.5 NMEA position fix flags (24)2.5.6 NMEA output of invalid or unknown data (25)2.6 NMEA messages overview (26)2.7 Standard messages (26)2.7.1 DTM (26)2.7.1.1 Datum reference (27)2.7.2 GAQ (27)2.7.2.1 Poll a standard message (Talker ID GA) (27)2.7.3 GBQ (28)2.7.3.1 Poll a standard message (Talker ID GB) (28)2.7.4 GBS (28)2.7.4.1 GNSS satellite fault detection (28)2.7.5 GGA (29)2.7.5.1 Global positioning system fix data (29)2.7.6 GLL (30)2.7.6.1 Latitude and longitude, with time of position fix and status (30)2.7.7 GLQ (30)2.7.7.1 Poll a standard message (Talker ID GL) (30)2.7.8 GNQ (31)2.7.8.1 Poll a standard message (Talker ID GN) (31)2.7.9 GNS (31)2.7.9.1 GNSS fix data (31)2.7.10 GPQ (32)2.7.10.1 Poll a standard message (Talker ID GP) (32)2.7.11 GQQ (32)2.7.11.1 Poll a standard message (Talker ID GQ) (33)2.7.12 GRS (33)2.7.12.1 GNSS range residuals (33)2.7.13 GSA (34)2.7.13.1 GNSS DOP and active satellites (34)2.7.14 GST (34)2.7.14.1 GNSS pseudorange error statistics (34)2.7.15 GSV (35)2.7.15.1 GNSS satellites in view (35)2.7.16 RLM (36)2.7.16.1 Return link message (RLM) (36)2.7.17 RMC (36)2.7.17.1 Recommended minimum data (36)2.7.18 THS (37)2.7.18.1 True heading and status (37)2.7.19 TXT (38)2.7.19.1 Text transmission (38)2.7.20 VTG (38)2.7.20.1 Course over ground and ground speed (38)2.7.21 ZDA (39)2.7.21.1 Time and date (39)2.8 Secondary output messages (40)2.8.1 GGA (40)2.8.1.1 Global positioning system fix data (40)2.8.2 GLL (41)2.8.2.1 Latitude and longitude, with time of position fix and status (41)2.8.3 GNS (41)2.8.3.1 GNSS fix data (42)2.8.4 GSA (43)2.8.4.1 GNSS DOP and active satellites (43)2.8.5 RMC (44)2.8.5.1 Recommended minimum data (44)2.8.6 VTG (45)2.8.6.1 Course over ground and ground speed (45)2.8.7 ZDA (45)2.8.7.1 Time and date (45)2.9 PUBX messages (46)2.9.1 CONFIG (PUBX,41) (46)2.9.1.1 Set protocols and baud rate (46)2.9.2 POSITION (PUBX,00) (47)2.9.2.1 Poll a PUBX,00 message (47)2.9.2.2 Lat/Long position data (47)2.9.3 RATE (PUBX,40) (48)2.9.3.1 Set NMEA message output rate (48)2.9.4 SVSTATUS (PUBX,03) (49)2.9.4.1 Poll a PUBX,03 message (49)2.9.5 TIME (PUBX,04) (49)2.9.5.1 Poll a PUBX,04 message (50)3 UBX protocol (51)3.1 UBX protocol key features (51)3.2 UBX frame structure (51)3.3 UBX payload definition rules (52)3.3.1 UBX structure packing (52)3.3.2 UBX reserved elements (52)3.3.3 UBX undefined values (52)3.3.4 UBX conditional values (52)3.3.5 UBX data types (52)3.3.6 UBX fields scale and unit (53)3.3.7 UBX repeated fields (53)3.3.8 UBX payload decoding (54)3.4 UBX checksum (54)3.5 UBX message flow (54)3.5.1 UBX acknowledgement (54)3.5.2 UBX polling mechanism (54)3.6 GNSS, satellite, and signal numbering (55)3.7 UBX message example (55)3.8 UBX messages overview (56)3.9 UBX-ACK (0x05) (59)3.9.1 UBX-ACK-ACK (0x05 0x01) (59)3.9.1.1 Message acknowledged (60)3.9.2 UBX-ACK-NAK (0x05 0x00) (60)3.9.2.1 Message not acknowledged (60)3.10 UBX-CFG (0x06) (60)3.10.1 UBX-CFG-CFG (0x06 0x09) (60)3.10.1.1 Clear, save and load configurations (60)3.10.2 UBX-CFG-RST (0x06 0x04) (61)3.10.2.1 Reset receiver / Clear backup data structures (61)3.10.3 UBX-CFG-SPT (0x06 0x64) (62)3.10.3.1 Configure and start a sensor production test (62)3.10.4 UBX-CFG-VALDEL (0x06 0x8c) (63)3.10.4.1 Delete configuration item values (63)3.10.4.2 Delete configuration item values (with transaction) (63)3.10.5 UBX-CFG-VALGET (0x06 0x8b) (64)3.10.5.1 Get configuration items (65)3.10.5.2 Configuration items (65)3.10.6 UBX-CFG-VALSET (0x06 0x8a) (66)3.10.6.1 Set configuration item values (66)3.10.6.2 Set configuration item values (with transaction) (67)3.11 UBX-ESF (0x10) (68)3.11.1 UBX-ESF-ALG (0x10 0x14) (68)3.11.1.1 IMU alignment information (68)3.11.2 UBX-ESF-INS (0x10 0x15) (69)3.11.2.1 Vehicle dynamics information (69)3.11.3 UBX-ESF-MEAS (0x10 0x02) (70)3.11.3.1 External sensor fusion measurements (70)3.11.4 UBX-ESF-RAW (0x10 0x03) (70)3.11.4.1 Raw sensor measurements (70)3.11.5 UBX-ESF-STATUS (0x10 0x10) (71)3.11.5.1 External sensor fusion status (71)3.12 UBX-INF (0x04) (72)3.12.1 UBX-INF-DEBUG (0x04 0x04) (72)3.12.1.1 ASCII output with debug contents (72)3.12.2 UBX-INF-ERROR (0x04 0x00) (73)3.12.2.1 ASCII output with error contents (73)3.12.3 UBX-INF-NOTICE (0x04 0x02) (73)3.12.3.1 ASCII output with informational contents (73)3.12.4 UBX-INF-TEST (0x04 0x03) (73)3.12.4.1 ASCII output with test contents (73)3.12.5 UBX-INF-WARNING (0x04 0x01) (74)3.12.5.1 ASCII output with warning contents (74)3.13 UBX-MGA (0x13) (74)3.13.1 UBX-MGA-ACK (0x13 0x60) (74)3.13.1.1 Multiple GNSS acknowledge message (74)3.13.2 UBX-MGA-BDS (0x13 0x03) (75)3.13.2.1 BeiDou ephemeris assistance (75)3.13.2.2 BeiDou almanac assistance (76)3.13.2.3 BeiDou health assistance (77)3.13.2.4 BeiDou UTC assistance (77)3.13.2.5 BeiDou ionosphere assistance (78)3.13.3 UBX-MGA-DBD (0x13 0x80) (78)3.13.3.1 Poll the navigation database (78)3.13.3.2 Navigation database dump entry (79)3.13.4 UBX-MGA-GAL (0x13 0x02) (79)3.13.4.1 Galileo ephemeris assistance (79)3.13.4.2 Galileo almanac assistance (80)3.13.4.3 Galileo GPS time offset assistance (81)3.13.4.4 Galileo UTC assistance (82)3.13.5 UBX-MGA-GLO (0x13 0x06) (82)3.13.5.1 GLONASS ephemeris assistance (82)3.13.5.2 GLONASS almanac assistance (83)3.13.5.3 GLONASS auxiliary time offset assistance (84)3.13.6 UBX-MGA-GPS (0x13 0x00) (84)3.13.6.1 GPS ephemeris assistance (84)3.13.6.2 GPS almanac assistance (86)3.13.6.3 GPS health assistance (86)3.13.6.4 GPS UTC assistance (87)3.13.6.5 GPS ionosphere assistance (87)3.13.7 UBX-MGA-INI (0x13 0x40) (88)3.13.7.1 Initial position assistance (88)3.13.7.2 Initial position assistance (88)3.13.7.3 Initial time assistance (89)3.13.7.4 Initial time assistance (90)3.13.7.5 Initial clock drift assistance (91)3.13.7.6 Initial frequency assistance (91)3.13.8 UBX-MGA-QZSS (0x13 0x05) (91)3.13.8.1 QZSS ephemeris assistance (92)3.13.8.2 QZSS almanac assistance (93)3.13.8.3 QZSS health assistance (93)3.13.9 UBX-MGA-SF (0x13 0x10) (94)3.13.9.1 Sensor fusion initialization data (94)3.13.9.2 Sensor fusion initialization data (94)3.14 UBX-MON (0x0a) (95)3.14.1 UBX-MON-COMMS (0x0a 0x36) (95)3.14.1.1 Communication port information (95)3.14.2 UBX-MON-GNSS (0x0a 0x28) (96)3.14.2.1 Information message major GNSS selection (96)3.14.3 UBX-MON-HW (0x0a 0x09) (96)3.14.3.1 Hardware status (97)3.14.4 UBX-MON-HW2 (0x0a 0x0b) (97)3.14.4.1 Extended hardware status (98)3.14.5 UBX-MON-HW3 (0x0a 0x37) (98)3.14.5.1 I/O pin status (98)3.14.6 UBX-MON-IO (0x0a 0x02) (99)3.14.6.1 I/O system status (99)3.14.7 UBX-MON-MSGPP (0x0a 0x06) (100)3.14.7.1 Message parse and process status (100)3.14.8 UBX-MON-PATCH (0x0a 0x27) (100)3.14.8.1 Installed patches (100)3.14.9 UBX-MON-RF (0x0a 0x38) (101)3.14.9.1 RF information (101)3.14.10 UBX-MON-RXBUF (0x0a 0x07) (102)3.14.10.1 Receiver buffer status (102)3.14.11 UBX-MON-RXR (0x0a 0x21) (102)3.14.11.1 Receiver status information (102)3.14.12 UBX-MON-SPAN (0x0a 0x31) (102)3.14.12.1 Signal characteristics (103)3.14.13 UBX-MON-SPT (0x0a 0x2f) (103)3.14.13.1 Sensor production test (103)3.14.14 UBX-MON-SYS (0x0a 0x39) (105)3.14.14.1 Current system performance information (105)3.14.15 UBX-MON-TXBUF (0x0a 0x08) (106)3.14.15.1 Transmitter buffer status (106)3.14.16 UBX-MON-VER (0x0a 0x04) (107)3.14.16.1 Receiver and software version (107)3.15 UBX-NAV (0x01) (107)3.15.1 UBX-NAV-ATT (0x01 0x05) (108)3.15.1.1 Attitude solution (108)3.15.2 UBX-NAV-CLOCK (0x01 0x22) (108)3.15.2.1 Clock solution (108)3.15.3 UBX-NAV-COV (0x01 0x36) (109)3.15.3.1 Covariance matrices (109)3.15.4 UBX-NAV-DOP (0x01 0x04) (109)3.15.4.1 Dilution of precision (109)3.15.5 UBX-NAV-EELL (0x01 0x3d) (110)3.15.5.1 Position error ellipse parameters (110)3.15.6 UBX-NAV-EOE (0x01 0x61) (110)3.15.6.1 End of epoch (110)3.15.7 UBX-NAV-GEOFENCE (0x01 0x39) (111)3.15.7.1 Geofencing status (111)3.15.8 UBX-NAV-HPPOSECEF (0x01 0x13) (111)3.15.8.1 High precision position solution in ECEF (111)3.15.9 UBX-NAV-HPPOSLLH (0x01 0x14) (112)3.15.9.1 High precision geodetic position solution (112)3.15.10 UBX-NAV-ORB (0x01 0x34) (113)3.15.10.1 GNSS orbit database info (113)3.15.11 UBX-NAV-PL (0x01 0x62) (114)3.15.11.1 Protection level information (114)3.15.12 UBX-NAV-POSECEF (0x01 0x01) (116)3.15.12.1 Position solution in ECEF (116)3.15.13 UBX-NAV-POSLLH (0x01 0x02) (116)3.15.13.1 Geodetic position solution (117)3.15.14 UBX-NAV-PVAT (0x01 0x17) (117)3.15.14.1 Navigation position velocity attitude time solution (117)3.15.15 UBX-NAV-PVT (0x01 0x07) (119)3.15.15.1 Navigation position velocity time solution (119)3.15.16 UBX-NAV-RELPOSNED (0x01 0x3c) (121)3.15.16.1 Relative positioning information in NED frame (122)3.15.17 UBX-NAV-SAT (0x01 0x35) (123)3.15.17.1 Satellite information (123)3.15.18 UBX-NAV-SBAS (0x01 0x32) (125)3.15.18.1 SBAS status data (125)3.15.19 UBX-NAV-SIG (0x01 0x43) (126)3.15.19.1 Signal information (126)3.15.20 UBX-NAV-SLAS (0x01 0x42) (127)3.15.20.1 QZSS L1S SLAS status data (127)3.15.21 UBX-NAV-STATUS (0x01 0x03) (128)3.15.21.1 Receiver navigation status (128)3.15.22 UBX-NAV-TIMEBDS (0x01 0x24) (130)3.15.22.1 BeiDou time solution (130)3.15.23 UBX-NAV-TIMEGAL (0x01 0x25) (130)3.15.23.1 Galileo time solution (130)3.15.24 UBX-NAV-TIMEGLO (0x01 0x23) (131)3.15.24.1 GLONASS time solution (131)3.15.25 UBX-NAV-TIMEGPS (0x01 0x20) (132)3.15.25.1 GPS time solution (132)3.15.26 UBX-NAV-TIMELS (0x01 0x26) (132)3.15.26.1 Leap second event information (132)3.15.27 UBX-NAV-TIMEQZSS (0x01 0x27) (133)3.15.27.1 QZSS time solution (134)3.15.28 UBX-NAV-TIMEUTC (0x01 0x21) (134)3.15.28.1 UTC time solution (134)3.15.29 UBX-NAV-VELECEF (0x01 0x11) (135)3.15.29.1 Velocity solution in ECEF (135)3.15.30 UBX-NAV-VELNED (0x01 0x12) (135)3.15.30.1 Velocity solution in NED frame (136)3.16 UBX-NAV2 (0x29) (136)3.16.1 UBX-NAV2-CLOCK (0x29 0x22) (136)3.16.1.1 Clock solution (136)3.16.2 UBX-NAV2-COV (0x29 0x36) (137)3.16.2.1 Covariance matrices (137)3.16.3 UBX-NAV2-DOP (0x29 0x04) (137)3.16.3.1 Dilution of precision (137)3.16.4 UBX-NAV2-EELL (0x29 0x3d) (138)3.16.4.1 Position error ellipse parameters (138)3.16.5 UBX-NAV2-EOE (0x29 0x61) (138)3.16.5.1 End of epoch (138)3.16.6 UBX-NAV2-POSECEF (0x29 0x01) (139)3.16.6.1 Position solution in ECEF (139)3.16.7 UBX-NAV2-POSLLH (0x29 0x02) (139)3.16.7.1 Geodetic position solution (139)3.16.8 UBX-NAV2-PVAT (0x29 0x17) (140)3.16.8.1 Navigation position velocity attitude time solution (140)3.16.9 UBX-NAV2-PVT (0x29 0x07) (142)3.16.9.1 Navigation position velocity time solution (142)3.16.10 UBX-NAV2-SAT (0x29 0x35) (144)3.16.10.1 Satellite information (144)3.16.11 UBX-NAV2-SBAS (0x29 0x32) (146)3.16.11.1 SBAS status data (146)3.16.12 UBX-NAV2-SIG (0x29 0x43) (147)3.16.12.1 Signal information (147)3.16.13 UBX-NAV2-SLAS (0x29 0x42) (148)3.16.13.1 QZSS L1S SLAS status data (148)3.16.14 UBX-NAV2-STATUS (0x29 0x03) (149)3.16.14.1 Receiver navigation status (149)3.16.15 UBX-NAV2-TIMEBDS (0x29 0x24) (151)3.16.15.1 BeiDou time solution (151)3.16.16 UBX-NAV2-TIMEGAL (0x29 0x25) (151)3.16.16.1 Galileo time solution (151)3.16.17 UBX-NAV2-TIMEGLO (0x29 0x23) (152)3.16.17.1 GLONASS time solution (152)3.16.18 UBX-NAV2-TIMEGPS (0x29 0x20) (153)3.16.18.1 GPS time solution (153)3.16.19 UBX-NAV2-TIMELS (0x29 0x26) (153)3.16.19.1 Leap second event information (153)3.16.20 UBX-NAV2-TIMEQZSS (0x29 0x27) (154)3.16.20.1 QZSS time solution (155)3.16.21 UBX-NAV2-TIMEUTC (0x29 0x21) (155)3.16.21.1 UTC time solution (155)3.16.22 UBX-NAV2-VELECEF (0x29 0x11) (156)3.16.22.1 Velocity solution in ECEF (156)3.16.23 UBX-NAV2-VELNED (0x29 0x12) (156)3.16.23.1 Velocity solution in NED frame (157)3.17 UBX-RXM (0x02) (157)3.17.1 UBX-RXM-COR (0x02 0x34) (157)3.17.1.1 Differential correction input status (157)3.17.2 UBX-RXM-MEASX (0x02 0x14) (158)3.17.2.1 Satellite measurements for RRLP (158)3.17.3 UBX-RXM-PMP (0x02 0x72) (160)3.17.3.1 PMP (LBAND) message (160)3.17.4 UBX-RXM-PMREQ (0x02 0x41) (160)3.17.4.1 Power management request (160)3.17.4.2 Power management request (161)3.17.5 UBX-RXM-QZSSL6 (0x02 0x73) (161)3.17.5.1 QZSS L6 message (161)3.17.6 UBX-RXM-RAWX (0x02 0x15) (162)3.17.6.1 Multi-GNSS raw measurements (162)3.17.7 UBX-RXM-RLM (0x02 0x59) (164)3.17.7.1 Galileo SAR short-RLM report (164)3.17.7.2 Galileo SAR long-RLM report (164)3.17.8 UBX-RXM-RTCM (0x02 0x32) (165)3.17.8.1 RTCM input status (165)3.17.9 UBX-RXM-SPARTN (0x02 0x33) (165)3.17.9.1 SPARTN input status (165)3.17.10 UBX-RXM-SPARTNKEY (0x02 0x36) (166)3.17.10.1 Poll installed keys (166)3.17.10.2 Transfer dynamic SPARTN keys (166)3.18 UBX-SEC (0x27) (167)3.18.1 UBX-SEC-SIG (0x27 0x09) (167)3.18.1.1 Signal security information (167)3.18.2 UBX-SEC-SIGLOG (0x27 0x10) (168)3.18.2.1 Signal security log (168)3.18.3 UBX-SEC-UNIQID (0x27 0x03) (168)3.18.3.1 Unique chip ID (169)3.19 UBX-TIM (0x0d) (169)3.19.1 UBX-TIM-TM2 (0x0d 0x03) (169)3.19.1.1 Time mark data (169)3.19.2 UBX-TIM-TP (0x0d 0x01) (170)3.19.2.1 Time pulse time data (170)3.19.3 UBX-TIM-VRFY (0x0d 0x06) (171)3.19.3.1 Sourced time verification (171)3.20 UBX-UPD (0x09) (171)3.20.1 UBX-UPD-SOS (0x09 0x14) (171)3.20.1.1 Poll backup restore status (172)3.20.1.2 Create backup in flash (172)3.20.1.3 Clear backup in flash (172)3.20.1.4 Backup creation acknowledge (172)3.20.1.5 System restored from backup (173)4 RTCM protocol (174)4.1 RTCM introduction (174)4.2 RTCM 3.x configuration (174)4.3 RTCM messages overview (174)4.4 RTCM 3.3 messages (175)4.4.1 Message type 1001 (175)4.4.1.1 L1-only GPS RTK observables (175)4.4.2 Message type 1002 (176)4.4.2.1 Extended L1-only GPS RTK observables (176)4.4.3 Message type 1003 (176)4.4.3.1 L1/L2 GPS RTK observables (176)4.4.4 Message type 1004 (177)4.4.4.1 Extended L1/L2 GPS RTK observables (177)4.4.5 Message type 1005 (177)4.4.5.1 Stationary RTK reference station ARP (177)4.4.6 Message type 1006 (178)4.4.6.1 Stationary RTK reference station ARP with antenna height (178)4.4.7 Message type 1007 (178)4.4.7.1 Antenna descriptor (179)4.4.8 Message type 1009 (179)4.4.8.1 L1-only GLONASS RTK observables (179)4.4.9 Message type 1010 (180)4.4.9.1 Extended L1-Only GLONASS RTK observables (180)4.4.10 Message type 1011 (180)4.4.10.1 L1&L2 GLONASS RTK observables (180)4.4.11 Message type 1012 (181)4.4.11.1 Extended L1&L2 GLONASS RTK observables (181)4.4.12 Message type 1033 (181)4.4.12.1 Receiver and antenna descriptors (181)4.4.13 Message type 1074 (182)4.4.13.1 GPS MSM4 (182)4.4.14 Message type 1075 (182)4.4.14.1 GPS MSM5 (182)4.4.15 Message type 1077 (183)4.4.15.1 GPS MSM7 (183)4.4.16 Message type 1084 (184)4.4.16.1 GLONASS MSM4 (184)4.4.17 Message type 1085 (184)4.4.17.1 GLONASS MSM5 (184)4.4.18 Message type 1087 (185)4.4.18.1 GLONASS MSM7 (185)4.4.19 Message type 1094 (185)4.4.19.1 Galileo MSM4 (185)4.4.20 Message type 1095 (186)4.4.20.1 Galileo MSM5 (186)4.4.21 Message type 1097 (186)4.4.21.1 Galileo MSM7 (187)4.4.22 Message type 1124 (187)4.4.22.1 BeiDou MSM4 (187)4.4.23 Message type 1125 (188)4.4.23.1 BeiDou MSM5 (188)4.4.24 Message type 1127 (188)4.4.24.1 BeiDou MSM7 (188)4.4.25 Message type 1230 (189)4.4.25.1 GLONASS L1 and L2 code-phase biases (189)5 SPARTN protocol (190)5.1 SPARTN introduction (190)5.2 SPARTN configuration (190)5.3 SPARTN messages overview (190)5.4 SPARTN messages (191)5.4.1 Message type 0, sub-type 0 (191)5.4.1.1 GPS orbit, clock, bias (OCB) (191)5.4.2 Message type 0, sub-type 1 (191)5.4.2.1 GLONASS orbit, clock, bias (OCB) (192)5.4.3 Message type 0, sub-type 2 (192)5.4.3.1 Galileo orbit, clock, bias (OCB) (192)5.4.4 Message type 0, sub-type 3 (193)5.4.4.1 BeiDou orbit, clock, bias (OCB) (193)5.4.5 Message type 0, sub-type 4 (194)5.4.5.1 QZSS orbit, clock, bias (OCB) (194)5.4.6 Message type 1, sub-type 0 (195)5.4.6.1 GPS high-precision atmosphere correction (HPAC) (195)5.4.7 Message type 1, sub-type 1 (195)5.4.7.1 GLONASS high-precision atmosphere correction (HPAC) (195)5.4.8 Message type 1, sub-type 2 (196)5.4.8.1 Galileo high-precision atmosphere correction (HPAC) (196)5.4.9 Message type 1, sub-type 3 (197)5.4.9.1 BeiDou high-precision atmosphere correction (HPAC) (197)5.4.10 Message type 1, sub-type 4 (198)5.4.10.1 QZSS high-precision atmosphere correction (HPAC) (198)5.4.11 Message type 2, sub-type 0 (199)5.4.11.1 Geographic area definition (GAD) (199)5.4.12 Message type 3, sub-type 0 (199)5.4.12.1 Basic-precision atmosphere correction (BPAC) (199)6 Configuration interface (201)6.1 Configuration database (201)6.2 Configuration items (201)6.3 Configuration layers (202)6.4 Configuration interface access (203)6.4.1 UBX protocol interface (203)6.5 Configuration data (203)6.6 Configuration transactions (204)6.7 Configuration reset behavior (205)6.8 Configuration overview (205)6.9 Configuration reference (206)6.9.1 CFG-BDS: BeiDou system configuration (206)6.9.2 CFG-GEOFENCE: Geofencing configuration (206)6.9.3 CFG-HW: Hardware configuration (207)6.9.4 CFG-I2C: Configuration of the I2C interface (209)6.9.5 CFG-I2CINPROT: Input protocol configuration of the I2C interface (209)6.9.6 CFG-I2COUTPROT: Output protocol configuration of the I2C interface (209)6.9.7 CFG-INFMSG: Information message configuration (209)6.9.8 CFG-MOT: Motion detector configuration (210)6.9.9 CFG-MSGOUT: Message output configuration (211)6.9.10 CFG-NAV2: Secondary output configuration (231)6.9.11 CFG-NAVHPG: High precision navigation configuration (231)6.9.12 CFG-NAVSPG: Standard precision navigation configuration (232)6.9.13 CFG-NMEA: NMEA protocol configuration (236)6.9.14 CFG-QZSS: QZSS system configuration (238)6.9.15 CFG-RATE: Navigation and measurement rate configuration (238)6.9.16 CFG-RINV: Remote inventory (239)6.9.17 CFG-RTCM: RTCM protocol configuration (239)6.9.18 CFG-SBAS: SBAS configuration (240)6.9.19 CFG-SEC: Security configuration (241)6.9.20 CFG-SFCORE: Sensor fusion (SF) core configuration (242)6.9.21 CFG-SFIMU: Sensor fusion (SF) inertial measurement unit (IMU) configuration (242)6.9.22 CFG-SFODO: Sensor fusion (SF) odometer configuration (243)6.9.23 CFG-SIGNAL: Satellite systems (GNSS) signal configuration (244)6.9.24 CFG-SPARTN: SPARTN configuration (245)6.9.25 CFG-SPI: Configuration of the SPI interface (245)6.9.26 CFG-SPIINPROT: Input protocol configuration of the SPI interface (246)6.9.27 CFG-SPIOUTPROT: Output protocol configuration of the SPI interface (246)6.9.28 CFG-TP: Time pulse configuration (246)6.9.29 CFG-TXREADY: TX ready configuration (248)6.9.30 CFG-UART1: Configuration of the UART1 interface (248)6.9.31 CFG-UART1INPROT: Input protocol configuration of the UART1 interface (249)6.9.32 CFG-UART1OUTPROT: Output protocol configuration of the UART1 interface (249)6.9.33 CFG-UART2: Configuration of the UART2 interface (250)6.9.34 CFG-UART2INPROT: Input protocol configuration of the UART2 interface (250)6.9.35 CFG-UART2OUTPROT: Output protocol configuration of the UART2 interface (251)6.9.36 CFG-USB: Configuration of the USB interface (251)6.9.37 CFG-USBINPROT: Input protocol configuration of the USB interface (251)6.9.38 CFG-USBOUTPROT: Output protocol configuration of the USB interface (252)6.10 Legacy UBX message fields reference (252)Configuration defaults (258)Related documents (281)Revision history (282)1 General information1.1 Document overviewThis document describes the interface of the u-blox F9 high precision sensor fusion GNSS receiver. The interface consists of the following parts:•NMEA protocol•UBX protocol•RTCM protocol•SPARTN protocol•Configuration interfaceSome of the features described here may not be available in the receiver, and some mayrequire specific configurations to be enabled. See the applicable data sheet for availability of the features and the integration manual for instructions for enabling them.Previous versions of u-blox receiver documentation combined general receiver description and interface specification. In the current documentation the receiver description isincluded in the integration manual.See also Related documents.1.2 Firmware and protocol versionsu-blox generation 9 receivers execute firmware from internal ROM or from internal code-RAM. If the firmware image is stored in a flash it is loaded into the code-RAM before execution. It is also possible to store the firmware image in the host system. The firmware is then loaded into the code-RAM from the host processor. (Loading the firmware from the host processor is not supported in all products.) If there is no external firmware image, then the firmware is executed from the ROM.The location and the version of the boot loader and the currently running firmware can be found in the boot screen and in the UBX-MON-VER message. If the firmware has been loaded from a connected flash or from the host processor, it is indicated by text "EXT". When the receiver is started, the boot screen is output automatically in UBX-INF-NOTICE or NMEA-Standard-TXT messages if configured using CFG-INFMSG. The UBX-MON-VER message can be polled using the UBX polling mechanism.The following u-center screenshots show an example of a u-blox receiver running firmware loaded from flash:The following information is available (✓) from the boot screen (B) and the UBX-MON-VER message (M):B M Example Information✓u-blox AG - Start of the boot screen.✓HW UBX 9 00190000Hardware version of the u-blox receiver.✓00190000✓✓EXT CORE 1.00 (61b2dd)Base (CORE) firmware version and revision number, loaded from externalmemory (EXT).EXT LAP 1.00 (12a3bc)Product firmware version and revision number, loaded from external memory(EXT). Available only in some firmware versions. See below for a list of productacronyms.✓✓ROM BASE 0x118B2060Revision number of the underlying boot loader firmware in ROM.✓✓FWVER=HPG 1.12Product firmware version number, where:•SPG = Standard precision GNSS product•HPG = High precision GNSS product•ADR = Automotive dead reckoning product•TIM = Time sync product•LAP = Lane accurate positioning product•HPS = High precision sensor fusion product•DBS = Dual band standard precision•MDR = Multi-mode dead reckoning product•PMP = L-Band Inmarsat point-to-multipoint receiver•QZS = QZSS L6 centimeter level augmentation service (CLAS) messagereceiver•DBD = Dual band dead reckoning product•LDR = ROM bootloader, no GNSS functionality✓✓PROTVER=34.00Supported protocol version.✓✓MOD=ZED-F9P Module name (if available).✓✓GPS;GLO;GAL;BDS List of supported major GNSS (see GNSS identifiers).✓✓SBAS;QZSS List of supported augmentation systems (see GNSS identifiers).B M Example Information✓ANTSUPERV=AC SD PDoS SR Configuration of the antenna supervisor (if available), where:•AC = Active antenna control enabled•SD = Short circuit detection enabled•OD = Open circuit detection enabled•PDoS = Short circuit power down logic enabled•SR = Automatic recovery from short state enabled✓PF=FFF79Product configuration.✓BD=E01C GNSS band configuration.The "FWVER" product firmware version indicates which firmware is currently running. This is referred to as "firmware version" in this and other documents.The revision numbers should only be used to identify a known firmware version. They arenot necessarily numeric nor are they guaranteed to increase with newer firmware versions.Similarly, firmware version numbers can have additional non-numeric informationappended, such as in "5.00B03".Not every entry is output by all u-blox receivers. The availability of some of the information depends on the product, the firmware location and the firmware version.The product firmware version and the base firmware version relate to the protocol version:Product firmware version Base firmware version Protocol versionHPS 1.00EXT CORE 1.00 (500086)33.00HPS 1.20EXT CORE 1.00 (a669b8)33.20HPS 1.21EXT CORE 1.00 (e2b374)33.21HPS 1.30EXT CORE 1.00 (a59682)33.301.3 Receiver configurationu-blox positioning receivers are fully configurable with UBX protocol messages. The configuration used by the receiver during normal operation is called the "current configuration". The current configuration can be changed during normal operation by sending UBX-CFG-VALSET messages over any I/O port. The receiver will change its current configuration immediately after receiving a configuration message. The receiver will always use the current configuration only.The current configuration is loaded from permanent configuration hard-coded in the receiver firmware (the defaults) and from non-volatile memory (user configuration) on startup of the receiver. Changes made to the current configuration at run-time will be lost when there is a power cycle, a hardware reset or a (complete) controlled software reset (see Configuration reset behavior).See Configuration interface for a detailed description of the receiver configuration system, the explanation of the configuration concept and its principles and interfaces.The configuration interface has changed from earlier u-blox positioning receivers. Thereis some backwards compatibility provided in UBX-CFG configuration messages. Users are strongly advised to only use the Configuration interface. See also Legacy UBX messagefields reference.See the integration manual for a basic receiver configuration most commonly used.。

LTR-553ALS-WA_DS_V1.0(1)

Property of Lite-On Only1. DescriptionThe LTR-553ALS-WA is an integrated low voltage I2C digital light sensor [ALS] and proximity sensor [PS] with built-in emitter, in a single miniature chipled lead-free surface mount package. This sensor converts light intensity to a digital output signal capable of direct I2C interface. It provides a linear response over a wide dynamic range from 0.01 lux to 64k lux and is well suited to applications under high ambient brightness. With built-in proximity sensor (emitter and detector), LTR-553ALS-WA offers the feature to detect object at a user configurable distance.The sensor supports an interrupt feature that removes the need to poll the sensor for a reading which improves system efficiency. The sensor also supports several features that help to minimize the occurrence of false triggering. This CMOS design and factory-set one time trimming capability ensure minimal sensor-to-sensor variations for ease of manufacturability to the end customers.2. Features∙I2C interface (Fast Mode @ 400kbit/s)∙Ultra-small ChipLED package∙Built-in temperature compensation circuit∙Low active power consumption with standby mode∙Supply voltage range from 2.4V to 3.6V capable of 1.7V logic voltage∙Operating temperature range from -30︒C to +70︒C∙RoHS and Halogen free compliant∙Light SensorClose to human eye spectral responseImmunity to IR / UV Light SourceAutomatically rejects 50 / 60 Hz lightings flicker6 dynamic range from 0.01 lux to 64k lux16-bit effective resolution∙Proximity SensorBuilt-in LED driver, emitter and detectorProgrammable LED drive settings11-bit effective resolutionHigh ambient light suppressionPart No.:LTR-553ALS-WA DATA SHEET Page: 1 of 41Property of Lite-On OnlyProperty of Lite-On Only5. Outline DimensionsNotes:1. All dimensions are in millimetersPart No.:LTR-553ALS-WA DATA SHEET Page: 3 of 41Property of Lite-On Only 6. Functional Block DiagramLTR-553ALSProperty of Lite-On Only LTR-553ALSProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On Only2Property of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On Only11. Pseudo Codes ExamplesControl Registers// The Control Registers define the operating modes and gain settings of the ALS and PS of LTR-553.// Default settings are 0x00 for both registers (both in Standby mode).Slave_Addr = 0x23 // Slave address of LTR-553 device// Enable ALSRegister_Addr = 0x80 // ALS_CONTR registerCommand = 0x01 // For Gain X1// For Gain X2, Command = 0x05// For Gain X4, Command = 0x09// For Gain X8, Command = 0x0D// For Gain X48, Command = 0x19// For Gain X96, Command = 0x1DWriteByte(Slave_Addr, Register_Addr, Command)// Enable PSRegister_Addr = 0x81 // PS_CONTR registerCommand = 0x03 // Gain = 16// For Gain = 32, Command = 0x0B// For Gain = 64, Command = 0x0FWriteByte(Slave_Addr, Register_Addr, Command)PS LED Registers// The PS LED Registers define the LED pulse modulation frequency, duty cycle and peak current.// Default setting is 0x7F (60kHz, 100%, 100mA).Slave_Addr = 0x23 // Slave address of LTR-553 device// Set LED Pulse Freq 30kHz (duty cycle 100%, peak curr 100mA)Register_Addr = 0x82 // PS_LED registerCommand = 0x1F // Pulse Freq = 30kHz, (duty cyc 100%, peak curr 100mA)// For Pulse Freq = 40kHz, (100%, 100mA), Command = 0x3F// For Pulse Freq = 50kHz, (100%, 100mA), Command = 0x5F// For Pulse Freq = 60kHz, (100%, 100mA), Command = 0x7F// For Pulse Freq = 70kHz, (100%, 100mA), Command = 0x9F// For Pulse Freq = 80kHz, (100%, 100mA), Command = 0xBF// For Pulse Freq = 90kHz, (100%, 100mA), Command = 0xDF// For Pulse Freq = 100kHz, (100%, 100mA), Command = 0xFF WriteByte(Slave_Addr, Register_Addr, Command)// Set LED Duty Cycle 25% (pulse freq 60kHz, peak curr 100mA)Register_Addr = 0x82 // PS_LED registerCommand = 0x67 // Duty Cycle = 25%, (pulse freq 60kHz, peak curr 100mA)// For Duty Cycle = 50%, (60kHz, 100mA), Command = 0x6F// For Duty Cycle = 75%, (60kHz, 100mA), Command = 0x77// For Duty Cycle = 100%, (60kHz, 100mA), Command = 0x7F WriteByte(Slave_Addr, Register_Addr, Command)Part No.:LTR-553ALS-WA DATA SHEET Page: 33 of 41Property of Lite-On Only// Set LED Peak Current 5mA (pulse freq 60kHz, duty cycle 100%)Register_Addr = 0x82 // PS_LED registerCommand = 0x78 // Peak Current = 5mA, (pulse freq 60kHz, duty cyc 100%)// For Peak Current = 10mA, (60kHz, 100%), Command = 0x79// For Peak Current = 20mA, (60kHz, 100%), Command = 0x7A// For Peak Current = 50mA, (60kHz, 100%), Command = 0x7B WriteByte(Slave_Addr, Register_Addr, Command)PS Measurement Rate// The PS_MEAS_RATE register controls the PS measurement rate.// Default setting of the register is 0x02 (repeat rate 100ms)Slave_Addr = 0x23 // Slave address of LTR-553 device// Set PS Repeat Rate 50msRegister_Addr = 0x84 // PS_MEAS_RATE registerCommand = 0x00 // Meas rate = 50ms// For Meas rate = 500ms, Command = 0x04WriteByte(Slave_Addr, Register_Addr, Command)ALS Measurement Rate// The ALS_MEAS_RATE register controls the ALS integration time and measurement rate.// Default setting of the register is 0x03 (integration time 100ms, repeat rate 500ms)Slave_Addr = 0x23 // Slave address of LTR-553 device// Set ALS Integration Time 200ms, Repeat Rate 200msRegister_Addr = 0x85 // ALS_MEAS_RATE registerCommand = 0x12 // Int time = 200ms, Meas rate = 200ms// For Int time = 400ms, Meas rate = 500ms, Command = 0x1B WriteByte(Slave_Addr, Register_Addr, Command)ALS Data Registers (Read Only)// The ALS Data Registers contain the ADC output data for the respective channel.// These registers should be read as a group, with the lower address being read first.Slave_Addr = 0x23 // Slave address of LTR-553 device// Read back ALS_DATA_CH1Register_Addr = 0x88 // ALS_DATA_CH1 low byte addressReadByte(Slave_Addr, Register_Addr, Data0)Register_Addr = 0x89 // ALS_DATA_CH1 high byte addressReadByte(Slave_Addr, Register_Addr, Data1)// Read back ALS_DATA_CH0Register_Addr = 0x8A // ALS_DATA_CH0 low byte addressReadByte(Slave_Addr, Register_Addr, Data2)Register_Addr = 0x8B // ALS_DATA_CH0 high byte addressReadByte(Slave_Addr, Register_Addr, Data3)ALS_CH1_ADC_Data = (Data1 << 8) | Data0 // Combining lower and upper bytes to give 16-bit Ch1 dataALS_CH0_ADC_Data = (Data3 << 8) | Data2 // Combining lower and upper bytes to give 16-bit Ch0 dataPart No.:LTR-553ALS-WA DATA SHEET Page: 34 of 41Property of Lite-On OnlyALS / PS Status Register (Read Only)// The ALS_PS_STATUS Register contains the information on Interrupt, ALS and PS data availability status.// This register is read only.Slave_Addr = 0x23 // Slave address of LTR-553 device// Read back RegisterRegister_Addr = 0x8C // ALS_PS_STATUS register addressReadByte(Slave_Addr, Register_Addr, Data)Interrupt_Status = Data & 0x0A // Interrupt_Status = 8(decimal) → ALS Interrupt// Interrupt_Status = 2(decimal) → PS Interrupt// Interrupt_Status = 10(decimal) → Both InterruptNewData_Status = Data & 0x05 // NewData_Status = 4(decimal) → ALS New Data// NewData_Status = 1(decimal) → PS New Data// NewData_Status = 5(decimal) → Both New DataALS_Data_Valid = Data & 0x80 // ALS_Data_Valid = 0x00 → ALS New Data is valid (usable)// ALS_Data_Valid = 0x80 → ALS New Data is invalid, discard andwait for new ALS dataPS Data Registers (Read Only)// The PS Data Registers contain the ADC output data.// These registers should be read as a group, with the lower address being read first.Slave_Addr = 0x23 // Slave address of LTR-553 device// Read back PS_DATA registersRegister_Addr = 0x8D // PS_DATA low byte addressReadByte(Slave_Addr, Register_Addr, Data0)Register_Addr = 0x8E // PS_DATA high byte addressReadByte(Slave_Addr, Register_Addr, Data1)PS_ADC_Data = (Data1 << 8) | Data0 // Combining lower and upper bytes to give 16-bit PS data Interrupt Registers// The Interrupt register controls the operation of the interrupt pins and function.// The default value for this register is 0x08 (Interrupt inactive)Slave_Addr = 0x23 // Slave address of LTR-553 device// Set Interrupt Polarity for Active Low, both ALS and PS triggerRegister_Addr = 0x8F // Interrupt Register addressCommand = 0x03 // Interrupt is Active Low and both ALS and PS can trigger// For Active High Interrupt, both trigger, Command = 0x07// For Active High Interrupt, ONLY ALS trigger, Command = 0x06// For Active High Interrupt, ONLY PS trigger, Command = 0x05 WriteByte(Slave_Addr, Register_Addr, Command)Part No.:LTR-553ALS-WA DATA SHEET Page: 35 of 41Property of Lite-On OnlyALS Threshold Registers// The ALS_THRES_UP and ALS_THRES_LOW registers determines the upper and// lower limit of the interrupt threshold value.// Following example illustrates the setting of the ALS threshold window of// decimal values of 200 (lower threshold) and 1000 (upper threshold)Slave_Addr = 0x23 // Slave address of LTR-553 device// Upper Threshold Setting (decimal 1000)ALS_Upp_Threshold_Reg_0 = 0x97 // ALS Upper Threshold Low Byte Register addressALS_Upp_Threshold_Reg_1 = 0x98 // ALS Upper Threshold High Byte Register addressData1 = 1000 >> 8 // To convert decimal 1000 into two eight bytes register values Data0 = 1000 & 0xFFWriteByte(Slave_Addr, ALS_Upp_Threshold_Reg_0, Data0)WriteByte(Slave_Addr, ALS_Upp_Threshold_Reg_1, Data1)// Lower Threshold Setting (decimal 200)ALS_Low_Threshold_Reg_0 = 0x99 // ALS Lower Threshold Low Byte Register addressALS_Low_Threshold_Reg_1 = 0x9A // ALS Lower Threshold High Byte Register addressData1 = 200 >> 8 // To convert decimal 200 into two eight bytes register values Data0 = 200 & 0xFFWriteByte(Slave_Addr, ALS_Low_Threshold_Reg_0, Data0)WriteByte(Slave_Addr, ALS_Low_Threshold_Reg_1, Data1)PS Threshold Registers// The PS_THRES_UP and PS_THRES_LOW registers determines the upper and// lower limit of the interrupt threshold value.// Following example illustrates the setting of the PS threshold window of// decimal values of 200 (lower threshold) and 1000 (upper threshold)Slave_Addr = 0x23 // Slave address of LTR-553 device// Upper Threshold Setting (decimal 1000)PS_Upp_Threshold_Reg_0 = 0x90 // PS Upper Threshold Low Byte Register addressPS_Upp_Threshold_Reg_1 = 0x91 // PS Upper Threshold High Byte Register addressData1 = 1000 >> 8 // To convert decimal 1000 into two eight bytes register values Data0 = 1000 & 0xFFWriteByte(Slave_Addr, PS_Upp_Threshold_Reg_0, Data0)WriteByte(Slave_Addr, PS_Upp_Threshold_Reg_1, Data1)// Lower Threshold Setting (decimal 200)PS_Low_Threshold_Reg_0 = 0x92 // PS Lower Threshold Low Byte Register addressPS_Low_Threshold_Reg_1 = 0x93 // PS Lower Threshold High Byte Register addressData1 = 200 >> 8 // To convert decimal 200 into two eight bytes register values Data0 = 200 & 0xFFWriteByte(Slave_Addr, PS_Low_Threshold_Reg_0, Data0)WriteByte(Slave_Addr, PS_Low_Threshold_Reg_1, Data1)Part No.:LTR-553ALS-WA DATA SHEET Page: 36 of 41Property of Lite-On OnlyProperty of Lite-On OnlyProperty of Lite-On Only Recommended Land PatternProperty of Lite-On OnlyProperty of Lite-On OnlyPart No.: LTR-553ALS-WA DATA SHEETPage: 41 of 41BNS-OD-C131/A4 - Rev 1.0 – 22 May 201315. Package Dimension for Tape and ReelNote:1. All dimensions are in millimetersNotes:1. All dimensions are in millimeters (inches)2. Empty component pockets sealed with top cover tape3. 7 inch reel - 2500 pieces per reel4. In accordance with ANSI/EIA 481-1-A-1994 specifications。

克伊利·7002开关系统数据手册说明书