VDI_6022_MSA_XSA_EN

华三路由器软件升级指南

Moxa ABC-02-USB自动备份配置器说明书

P/N: 1802000021022*1802000021022*ABC-02-USB Quick Installation GuideAutomatic Backup ConfiguratorEdition 2.1, July 2019Technical Support Contact Information/support Moxa Americas:Toll-free: 1-888-669-2872Tel: 1-714-528-6777Fax: 1-714-528-6778 Moxa China (Shanghai office): Toll-free: 800-820-5036 Tel: +86-21-5258-9955 Fax: +86-21-5258-5505 Moxa Europe:Tel: +49-89-3 70 03 99-0Fax: +49-89-3 70 03 99-99 Moxa Asia-Pacific: Tel: +886-2-8919-1230 Fax: +886-2-8919-1231 Moxa India:Tel: +91-80-4172-9088Fax: +91-80-4132-10452019 Moxa Inc. All rights reserved.OverviewThe ABC-02-USB Automatic Backup Configurator is a device that can save and load configuration files, backup event logs, and load firmware of Moxa’s managed switch via the USB (universal serial bus) interface. The ABC-02-USB is able to be accessed directly like a standard USB flash drive from a computer.The ABC-02-USB makes it easier to manage the backup of system parameters or perform configuration during the replacement of a switch. With the ABC-02-USB, users can quickly re-install a substitute switch (of the same model) without the need of a laptop computer. The ABC-02 can be used to recover the entire system configuration, including the IP address, if a switch failure occurs.Switches can load firmware from the ABC-02-USB and backup event logs to the ABC-02-USB. It is also an easy and fast diagnostics tool for automation engineers to retrieve configuration files and event logs in the field immediately, without the need for laptop computers. Package ChecklistThe ABC-02-USB is shipped with the following items. If any of these items is missing or damaged, please contact your customer service representative for assistance.• 1 x ABC-02-USB•Quick installation guide (printed)•Warranty cardFeatures•Widely used USB 2.0 interface•Click the switch rest button to back up the configuration file and event log to ABC-02•Automatic loading of system configuration after system reboot •Manual upgrade firmware from ABC-02 and backup event logs to ABC-02•Manual and saving system configuration through web console •Extend switch event log storage capability•Portable low-power design that requires no power supply•CE, FCC approvalHardware DescriptionProduct InstallationThe ABC-02-USB is designed for use with an USB 2.0 port. Plug the ABC-02 into the USB port of your Moxa managed switch. Securing the ABC-02 on the wall with an M4 screw is suggested.Avoid hanging the ABC-02 configurator from the switch without securing it onto the wall.Please refer to the Product Operation section for instructions on how to save and load the configuration, firmware, and event logs. Product OperationConfiguration Backup and Restore•Backup switch configuration on the ABC-02Use the switch web console to save the configuration file to theABC-02. This function is found under “System/System Files/Configuration Backup and Restore “. Then select “Auto BackupConfigurator (ABC-02)” in the web console. Click “Backup” to save the configuration file to the ABC-02. The file will be saved in the“:\Moxa” folder of the ABC-02. The file name is “Sys.ini”. •Restore the configuration file from the ABC-02 to the switchA. Manually operate in web consoleUse the switch web console to load configuration files from theABC-02 to the switch. This function is found under“System/System Files/ Configuration Backup and Restore”.Then select “Auto Backup Configurator (ABC-02)” in the webconsole. Click “Browse” to select the file you need. Then click“Restore” to start loading into your switch.B. Auto-load the configuration file from the ABC-02 to the systemwhen the switch boots upPower off your switch first, and then plug in the ABC-02. Thenpower on your switch, the system will detect the configurationfile on the ABC-02 automatically. The switch will recognize thefile name with following sequence priority:1. ”MAC address last 6 digits.ini*”2. “Sys.ini”. If no matching configuration file is found, the faultLED light will turn on. The switch will boot up normally.NOTE Please save your configuration files in the “:\Moxa” folder of the ABC-02. Auto-load will detect the configuration file using thispath only.Firmware UpgradeUpgrade the firmware from the ABC-02 to the switch. You can download the firmware file from /support/. Save the firmware file in the “:\Moxa” folder of the ABC-02.Plug in the ABC-02 into your switch. Use the switch web console to load the switch firmware file from the ABC-02. This function is found under “System/System Files/ Firmware Upgrade “. Then select “Auto Backup Configurator (ABC-02)” in the web console. Click “Browse” to select the file you need. Then click “Upgrade” to start loading the file into your switch.Log File BackupBackup the switch log file to the ABC-02Use the switch web console to save the configuration file to the ABC-02. This function is found under “System/System Files/ Log File Backup “. Then select “Auto Backup Configurator (ABC-02)” in the web console. Click “Backup” to save the configuration file to the ABC-02. The log file will be saved in the “:\Moxa” folder of the ABC-02. The file will be named “Sys.log”.One-click backupThe ABC-02 can backup configuration and log files from the switch. When the ABC-02 is plugged into the switch, “STATE” LEDs on the switch will start to blink slowly, and the reset function will be disabled automatically. Press the “reset” button once and the switch will start backing up configuration files and system logs to the ABC-02.The “RESET” button is located on the front panel of rackmount type switches and on the top panel of DIN-rail type switches.Auto backup to the ABC-02 when configurations changeThe ABC-02 is capable of backing up switch configuration files automatically. This function is found under “System/System Files/ Configuration Backup and Restore”. While the ABC-02 is plugged into the switch, enable the “Auto backup to ABC-02 when configuration change” option. Then click “Apply”. Once this configuration is modified, the switch will back up the current configuration under the “/His_ini” folder in the ABC-02. The file name will be the system date/time (MMDDHHmm.ini).Auto backup of the earliest 100 log entries to prevent overwritingThis function is designed to maintain a long-term record the switch log files. Moxa Ethernet switches are capable of saving 1000 entries of event logs. When the 1000-entry storage limit is reached, the switch will delete the oldest saved event log. The ABC-02 can help to backup these event logs. When switch log entries reach 1000, the ABC-02 will back up the earliest 100 entries of the switch.The function is found under “System/System Files/ Log File Backup”. Enable the “Auto backup the earliest 100 log entries to prevent overwriting”. Then click “Apply”. After that, when the ABC-02 is plugged into the switch, the event logs will always be saved to the ABC-02 automatically.NOTE For further details on the ABC-02 operation through the switch web console, please refer to the switch user manual.NOTE The status of the ABC-02 may be checked on the switch web console or by observing the switch front panel LEDs.Operation Switch LED statusThe switch detects ABC-02-USB plugged in STATE blinking slowly (1 time/ 2 seconds),Import/Export in progress* FAULT, MASTER, COUPLER LEDs Blink sequentially and circularlyImport/Export successful FAULT, MASTER, COUPLER LEDs light offSave/Load failed FAULT LED light on until ABC-02 isremoved or system rebootOperation ABC-02 LED status Power on ABC-02 STATE LED green light on Reading /Writing ABC-02 STATE LED blinking*Does not include “Auto backup to the ABC-02 when configuration change” and ”Auto backup the earliest 100 log entries to prevent overwritingSpecificationsOperating Temperature 0 to 60°C (32 to 140°F)Storage Temperature -40 to 85°C (-40 to 185°F) Connectors RS-232 RJ45 portPower Requirement 3 to 5 VDC, power input via RS-232 RTS Configuration via Moxa managed switch’s web console Casing PVC molding, IP40Weight 50 gInstallation M4 screw (> 4 mm)Dimension (W × D × H) 32.5 × 97 × 12 mmCable Length 35 cm, including connectors Operating Temperature 0 to 60°C (32 to 140°F)Storage Temperature -20 to 70°C (-4 to 158°F)Ambient Relative5 % to 95 % (non-condensing) HumidityEMI FCC Part 15, CISPR (EN55032) Class A EMS EN61000-4-2 (ESD), level 3EN61000-4-3 (RS), level 3EN61000-4-4 (EFT), level 3EN61000-4-5 (Surge), level 3EN61000-4-6 (CS), level 3Warranty 5 years。

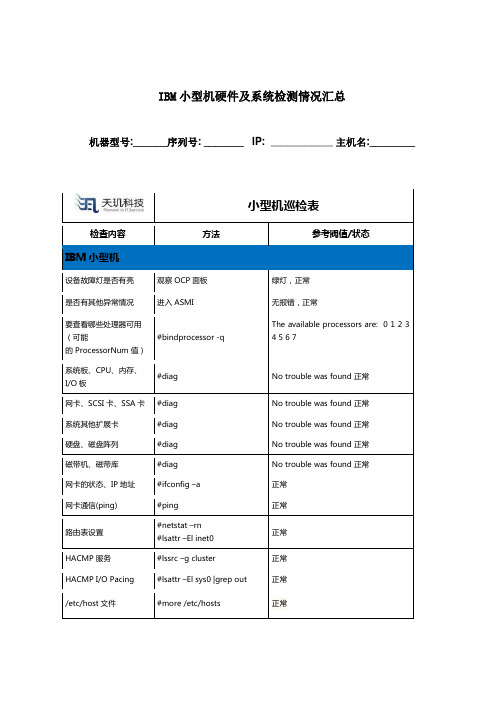

IBM小型机硬件及系统检测情况汇总

正常

HACMP 服务

#lssrc –g cluster

正常

HACMP I/O Pacing

#lsattr –El sys0 |grep out

正常

/etc/host文件

#more /etc/hosts

正常

HACMP 日志

#tail –f /tmp/hacmp.out

# sysdumpdev –l

正常

系统备份检查

做vg配置信息的备份

已备份

询问客户有否在系统变更后或每半年做系统备份

询问客户数据库及应用、应用数据是否定期有效

进行备份

系统性能检查

CPU

#topas

正常

Disk

#vmstat

正常

应用程序磁盘

#iostat

正常

交换区

#lsps -a

正常

#bindprocessor -q

The available processors are: 0 1 2 3 4 5 6 7

系统板、CPU、内存、I/O板

#diag

No trouble was found 正常

网卡、SCSI卡、SSA卡

#diag

No trouble was found 正常

系统其他扩展卡

#diag

No trouble was found 正常

硬盘、磁盘阵列

#diag

No trouble was found 正常

磁带机、磁带库

#diag

No trouble was found 正常

网卡的状态、IP地址

#ifconfig –a

正常

网卡通信(ping)

MLC 9000+ 说明书

保修

我们可以担保这些产品在出厂之前,在材料和工艺方面无任何功能缺陷,并且可以担保此类 产品在三年内符合相关说明手册资料中所提到的技术规范。 除此处及上述所提及的保修条例外,无任何其他明示或暗示保修。WEST 不会因任何特殊原 因对该产品的适销性和适用性做任何担保。

限制

对于任何意外损坏、后续损坏、特殊损坏或任何其他损坏,或者除上述所提及的任何维修或 更换之外的成本或费用,供应商概不承担责任。用户必须按照说明安装和维护产品。对于因 腐蚀性而造成的产品损坏,供应商没有保修责任。用户自己对于这些产品与其应用程序的适 用性负责。对于一个有效的保修声明,产品在保修期内进行返修必须向供应商支付运费。产 品必须进行适当包装,以免在运输过程中因静电放电或其他形式的危害导致产品受损。

MLC 9000+ 用户指南

MLC 9000+ 用户指南

59371-1

价格:

£11.00 €15.00 $15.00

ii

59327,第 1 期 – 2003 年 5 月 4 日

本安装、接线和操作手册中的信息可能会有所变动,恕不另行通知。 Copyright © 2004 年 5 月,Danaher ICG,保留所有权利。未经厂商书面许可,不得以任何 形式或通过任何方式在检索系统中复制、传播、改写或存储本出版物的任何部分,或者将本 出版物的任何部分翻译成任何其他语言。 注意:

ii

59327,第 1 期 – 2003 年 5 月 4 日

MLC 9000+ 用户指南

目录

目录

1 2 MLC 9000+ 系统概述 ................................................................................

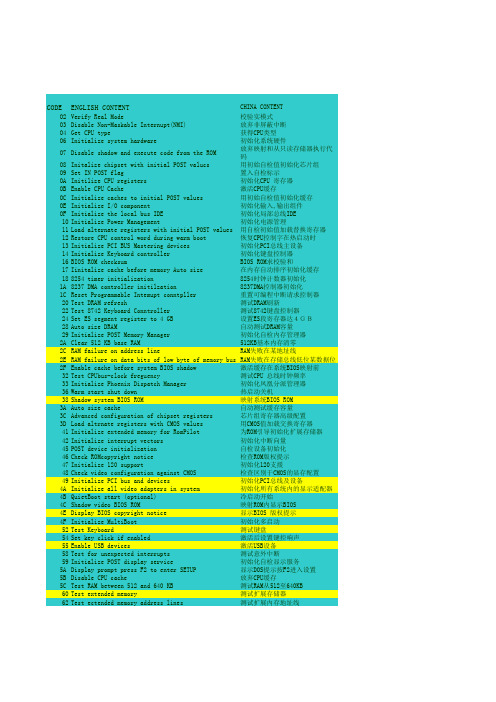

跑马灯代码表

CODE ENGLISH CONTENT CHINA CONTENTO2Verify Real Mode校验实模式O3Disable Non-Maskable Internupt(NMI)放弃非屏蔽中断O4Get CPU type获得CPU类型O6Initialize system hardware 初始化系统硬件O7Disable shadow and execute code from the ROM放弃映射和从只读存储器执行代码 O8Initalize chipset with initial POST valucs用初始自检值初始化芯片组O9Set IN POST flag置入自检标示OA Initilize CPU registers初始化CPU 寄存器OB Enable CPU Cache激活CPU缓存OC Initialize caches to initial POST values用初始自检值初始化缓存OE Initialize I/O component初始化输入,输出组件OF Initialize the local bus IDE初始化局部总线IDE 10Initialize Power Management初始化电源管理11Load alternate registers with initial POST values用自检初始值加载替换寄存器12Restore CPU control word during warm boot恢复CPU控制字在热启动时13Initialize PCI BUS Mastering devices初始化PCI总线主设备14Initialize Keyboard controller初始化键盘控制器16BIOS ROM checksum BIOS ROM求校验和17Iinitalize cache before memory Auto size在内存自动排序初始化缓存188254 timer initialization8254时钟计数器初始化1A8237 DMA controller initilzation8237DMA控制器初始化1C Reset Programmable Intemupt conntpller重置可编程中断请求控制器20Test DRAM refresh测试DRAM刷新22Test 8742 Keyboard Conntroller测试8742键盘控制器24Set ES segment register to 4 GB设置ES段寄存器达4GB28Auto size DRAM自动测试DRAM容量29Initialize POST Memory Manager初始化自检内存管理器2A Clear 512 KB base RAM512KB基本内存清零2C RAM failure on address line RAM失败在某地址线2E RAM failure on data bits of low byte of memory bus RAM失败在存储总线低位某数据位 2F Enable cache before system BIOS shadow激活缓存在系统BIOS映射前32Test CPUbus-clock freguency测试CPU 总线时钟频率33Initialize Phoenix Dispatch Manager初始化凤凰分派管理器36Warm start shut down热启动关机38Shadow system BIOS ROM映射系统BIOS ROM3A Auto size cache自动测试缓存容量3C Advanced configuration of chipset registers芯片组寄存器高级配置3D Load altrnate registers with CMOS values用CMOS值加载交换寄存器41Initialize extended memory for RomPilot为ROM引导初始化扩展存储器42Initialize interrupt vectors初始化中断向量45POST device initialization自检设备初始化46Check ROMcopyright notice检查ROM版权提示47Initialize 120 support初始化120支援48Check video configuration against CMOS检查区别于CMOS的显存配置49Initialize PCI bus and devices初始化PCI总线及设备4A Initialize all video adapters in system初始化所有系统内的显示适配器 4B QuietBoot start (optional)冷启动开始4C Shadow video BIOS ROM映射ROM内显示BIOS4E Display BIOS copyright notice显示BIOS 版权提示4F Initialize MultiBoot初始化多启动52Test Keyboard测试键盘54Set key click if enabled激活后设置键控响声55Enable USB devices激活USB设备58Test for unexpected interrupts测试意外中断59Initialize POST display service初始化自检显示服务5A Display prompt press F2 to enter SETUP显示DOS提示按F2进入设置5B Disable CPU cache放弃CPU缓存5C Test RAM between 512 and 640 KB测试RAM从512至640KB 60Test extended memory测试扩展存储器62Test ectended memory address lines测试扩展内存地址线64Jump to UserPatch1跳至用户补丁区166Configure advanced cache registers配置高级缓存寄存器67Initialize Multi Processor APIC初始化多处理器APIC68Enable external and CPU caches激活外接和CPU缓存69Display system Management Mode (SMM)area显示系统管理模式区6A Display external L2 cache size 显示外接L2缓存容量6B Load custom defaults(optional)加载用户默认值6C Dislay shadow-area message显示映射区信息6E Display possible high address for UMB recover显示可能的高端地址为UMB恢复使用70Display error messages显示错误信息72Check for configuation errors检测配置偏差76Check for keyboard errors检测键盘错误7C Set up tard ware interrupt vectors设置硬件中断向量7D Initialize Intelligent System Monitoring初始化智能系统跟踪7E Initialize coprocessor if present如果存在,初始化协处理器80Disable onboard Super I/O ports and IRQS放弃板上的超级输入输出端口及IRQS 81Late POST device initialization最后自检设备的初始化82Detect and install extemal RS232 ports侦测安装外接RS232端口83Configure non-MCD IDE controllers配置NON-MCD IDE控制器84Detect and installextermal parallel ports侦测安装外接并行端口85Initialize PC-compatible PnP ISA devices初始化兼容PC即插即用ISA设备86Re-initialize onblard I/O Ports重初始化板上的输入输出端口87Configure Motherboard Configurable Devices(optional)配置M/B可配置设备88Initializ BIOS Data area BOIS数据区初始化89Enable mon-maskable inteerupts[NMIS]激活非屏蔽中断请求8A Initializ Extended Bios Data Area扩展BIOS数据区初始化8b Test and initialize PS/2 mouse测试和初始化PS/2端口8C Initialize floppy controller初始化软驱控制器8F Determine number of ATA drives (optional)测试ATA驱动器数量90Initialize hard-disk controllers初始化硬盘驱控制器91Initialize local-bus bard-disk countrollers初始化局部总线上的硬盘控制器92Jump to Userpatch2跳至用户补丁区93Build MPTABLE for multi-processor boards为多处理器板建立多处理器列表95Install CD-ROM for boot为启动安装CD-ROM96Clear hUge ES segment register清空大量ES段寄存器97Fix up Multi Procssor table设置多处理器列表98Scarch for option ROMs,One long,授索可选只读存储器,一长,二two short beeps on checksum failure短嗡鸣声,在校验失败时99Check for SMART Drive(optional)检查SMART驱动器9A Shadow option ROMs映射选定的只读存储器9C Set up power Management设置电源管理9D Initialize security engine(oprional)初始化安防措施9E Enable bardware interrupts激活硬件中断9F Determine number of ATA and SCDI drives 检测A/A和SCDI设备数量A0Set time or day设置时间和日期A2Check key lock检查锁定键A4Initialize typebatic rateA8Erase F2 prompt清除F2提示AA Scan for F2 key stroke扫描有无F2键按下AC Enter SETUP进入设置AE clear boot flag清除启动标志B0Check for errors检查错误B1Inform Rom pilot about the end of POST通知只读存储器在自检结束后引导系统 B2POST done-prepare to boot operating system自检结束准备起动系统B4One short beep before boot起动前一个短嗡鸣声B5Terminate QuietBoot(optional)结束冷启动B6Check passwont(potional)检验密码B7Initialize ACPIBIOS初始化ACPIBIOSB9Prepare Boot准备启动BA Initialize SMBIOS初始化SMBIOSBB Initialize PuP Option ROMs初 始化即插即用只读存储器BC Clear parity checkers清零奇偶校验检测BD Display MultiBoot menu显示多启动菜单BE Clear screen (Optional)清空显示屏BF Check virus and backup reminders检查病毒备份提示C0Try to boot with INT 19试用INT 19启动C1Initialize POST Error Manager初始化自检管理C2Initialize error logging初始化错误日志C3Initialize error display function初始化错误显示功能C4Initialize system error bandler初始化系统错误处理C5PnPnd dual CMOS(optional)C6Initialize note disk (optional)C7Initialize note dock lateC8Force check(optional)强行检查CC Redirect Int 10h to ENable remote serial video重指示INT 10去激活远程窜行显示 CD Re_map I/O and memory for PCMCIA重定位I/O和内存为PCMCIA卡CE Initialize digitize and display message初始化数字的显示信息D2Unknowm interrupt不明中断The followIng are for boot block in Flash ROME0Initialize the chipset初始化芯片组E1Initialize the bridge初始化桥E2Iinitalize the CPU初始化CPUE3Initialize system timer初始化系统时钟E4Initialize system I/0初始化系统输入输出口E5Check force reCovery boot检查强行恢复启动E6Checksum BIOSROM BIOS ROM求校验和E7Go to BIOS转向BIOSE8Set Hune Segment设置大量段寄存器E9Initialize Multi procssor初始化多处理器EA Initialize OEMspectal code初始化OEM专用代码EB Initialize PIC and DMA初始化PIC 和DMAEC Initialize Memory type初始化存储类型ED Initialize Memory size初始化存储容量EE Shadow Boot Block映射启动模块EF System memory test系统存储器测试F0Initilize intemupt vectors初始化中断向量F1Initilize Run Time Clock初始化运行时钟F2Initilize video初始化显示F3Initilize System Management Manager初始化系统管理的管理器F4Output one beep输出一个嗡鸣声F5Clear Huge Seginent清空大量段寄存器F6Boot to Mini DOS最小化DOS启动F7Boot to Full DOS完整DOS启动。

技嘉GA-Z270X-Gaming SOC主板使用手册说明书

Dec. 30, 2016Motherboard GA-Z270X-Gaming SOC目录清点配件 (6)选购配件 (6)GA-Z270X-Gaming SOC主板配置图 (7)第一章硬件安装 (9)1-1 安装前的注意事项 (9)1-2 产品规格 (10)1-3 安装中央处理器及散热风扇 (14)1-3-1 安装中央处理器(CPU) (14)1-3-2 安装散热风扇 (16)1-4 安装内存条 (17)1-4-1 双通道内存技术 (17)1-4-2 安装内存条 (18)1-5 安装扩展卡 (19)1-6 构建AMD CrossFire™/NVIDIA® SLI™系统 (20)1-7 后方设备插座介绍 (21)1-8 内建灯号、按钮及切换器 (23)1-9 更换音频放大器 (25)1-10 插座及跳线介绍 (26)第二章 BIOS 程序设置 (41)2-1 开机画面 (42)2-2 BIOS设定程序主画面 (43)2-3 M.I.T. (频率/电压控制) (45)2-4 System (系统信息) (57)2-5 BIOS (BIOS功能设定) (58)2-6 Peripherals (集成外设) (61)2-7 Chipset (芯片组设定) (64)2-8 Power (省电功能设定) (65)2-9 Save & Exit (储存设定值并结束设定程序) (67)第三章构建磁盘阵列 (69)3-1 设定SATA控制器模式 (69)3-2 安装SATA RAID/AHCI驱动程序及操作系统 (83)3-3 启动Intel® Optane™技术 (86)第四章驱动程序安装 (87)4-1 Drivers & Software (驱动程序及应用软件) (87)4-2 Application Software (软件应用程序) (88)4-3 Information (信息清单) (88)- 4 -第五章独特功能介绍 (89)5-1 BIOS更新方法介绍 (89)5-1-1 如何使用Q-Flash更新BIOS (89)5-1-2 如何使用@BIOS更新BIOS (92)5-2 APP Center (93)5-2-1 3D OSD (94)5-2-2 AutoGreen (95)5-2-3 BIOS Setup (96)5-2-4 Color Temperature (97)5-2-5 Cloud Station (98)5-2-6 EasyTune (103)5-2-7 Easy RAID (104)5-2-8 Fast Boot (107)5-2-9 Game Boost (108)5-2-10 Platform Power Management (109)5-2-11 RGB Fusion (110)5-2-12 Smart TimeLock (111)5-2-13 Smart Keyboard (112)5-2-14 Smart Backup (113)5-2-15 System Information Viewer (115)5-2-16 USB Blocker (116)5-2-17 USB DAC-UP 2 (117)5-2-18 V-Tuner (118)第六章附录 (119)6-1 音频输入/输出设定介绍 (119)6-1-1 2 / 4 / 5.1 / 7.1声道介绍 (119)6-1-2 S/PDIF输出设定 (121)6-1-3 麦克风录音设定 (122)6-1-4 语音录音机使用介绍 (124)6-2 疑难排解 (125)6-2-1 问题集 (125)6-2-2 故障排除 (126)6-3 除错灯号代码说明 (128)管理声明 (132)技嘉主板售后服务及质量保证卡 (134)技嘉科技全球服务网 (135)- 5 -清点配件5GA-Z270X-Gaming SOC主板- 1片5驱动程序光盘- 1片5使用手册- 1本5硬件安装指南- 1张5SATA排线- 4条5后方I/O设备挡板铁片- 1个5G Connector- 1个5后方I/O设备防尘盖- 1包5GC-SLI2P连接器- 1个上述附带配件仅供参考,实际配件请以实物为准,技嘉科技保留修改的权利。

cisco_ASA防火墙恢复初始化

cisco_ASA防火墙恢复初始化ASA 防火墙flash 被删防火墙不断启动Use BREAK or ESC to interrupt boot.Use SPACE to begin boot immediately.按下ESC进入监控模式监控模式下的显示和交换机路由器没有什么区别。

命令格式也大同小异只要大家变通一下就不难恢复。

rommon #1> ?Variables: Use "sync" to store in NVRAMADDRESS= local IP addressCONFIG= config file path/nameGATEWAY= gateway IP addressIMAGE= image file path/nameLINKTIMEOUT= Link UP timeout (seconds)PKTTIMEOUT= packet timeout (seconds)PORT= ethernet interface portRETRY= Packet Retry Count (Ping/TFTP)SERVER= server IP addressVLAN= enable/disable DOT1Q tagging on the selected portrommon #2> ADDRESS=192.168.0.2 (因为是TFFP上传,所以防火墙设置为客户机)rommon #3> GATEWAY=192.168.0.1 (网关)rommon #4> IMAGE=asa802-k8.bin (导入IOS的名称)rommon #5> SERVER=192.168.0.1 (服务器IP,也就是你的PC)rommon #6> sync (保存)Updating NVRAM Parameters...rommon #7> ping 192.168.0.1Sending 20, 100-byte ICMP Echoes to 192.168.0.1, timeout is 4 seconds:Success rate is 95 percent (19/20)确认线路是否连通,开启TFTP软件(这里说明下我测试是ASA5505 所以接的E0/0口。

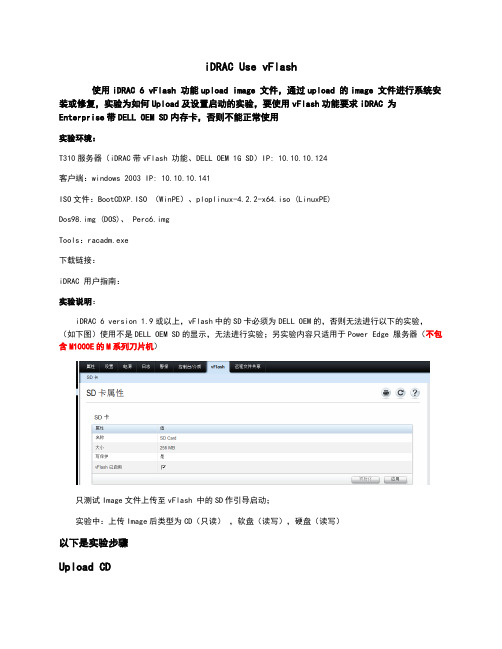

DELL服务器通过sd卡安装系统(iDRAC-Use-vFlash-)

iDRAC Use vFlash使用iDRAC 6 vFlash 功能upload image 文件,通过upload 的image 文件进行系统安装或修复,实验为如何Upload及设置启动的实验,要使用vFlash功能要求iDRAC 为Enterprise带DELL OEM SD内存卡,否则不能正常使用实验环境:T310服务器(iDRAC带vFlash 功能、DELL OEM 1G SD)IP: 10.10.10.124客户端:windows 2003 IP: 10.10.10.141ISO文件:BootCDXP.ISO (WinPE)、ploplinux-4.2.2-x64.iso (LinuxPE)Dos98.img (DOS)、 Perc6.imgTools:racadm.exe下载链接:iDRAC 用户指南:实验说明:iDRAC 6 version 1.9或以上,vFlash中的SD卡必须为DELL OEM的,否则无法进行以下的实验,(如下图)使用不是DELL OEM SD的显示,无法进行实验;另实验内容只适用于Power Edge 服务器(不包含M1000E的M系列刀片机)只测试Image文件上传至vFlash 中的SD作引导启动;实验中:上传Image后类型为CD(只读),软盘(读写),硬盘(读写)以下是实验步骤Upload CD1.首先要登入 iDRAC Web 页面,默认用户名:root, 密码:calvin ;2.进入vFlash 界面,如第一次使用请在SD卡中初始化及启用vFlash功能;如下图3.完成以上步骤后,点击“从映像创建”进行Image文件上传;如下图4.点击上图的“应用”上传文件进程开始运行,并请等待至提示“已完成创建分区”的提示出现;如下图5.完成创建分区后点击“管理”,选中已附加并应用;如下图6.在完成应用后,可进行使用已上传的Image 文件进行启动,可以选择在iDRAC中的设置,设置为第一引导设备,选择一次性引导;如下图或开机时按F11,通过BIOS Boot Manager 的文件启动Image文件;如下图以下启动后的将以ISO文件启动;如下图7.附加后如正常进入操作系统,可在直接中以光驱形式显示,要取消则在iDRAC中取消附加;参考步骤5Upload Fopply1.Upload Fopply first boot;注:上传为软盘只能使用于First Boot ,不能用于安装操作系统过程中加载驱动,如加载阵列控制卡驱动;2.从“映像创建”文件为dos98.img,标签为DOS;如下图3.请确保上传完成100%;如下图4.将文件附加;如下图5.如显示如下断开提示,新附加的介质,iDRAC会中断所有已附加的介质并重新加载,故选择确定即可;如下图6.参考步骤6方式以附加的文件方式启动;7.启动后的显示;如下图8.在系统中的显示为可移设备而不是为A盘;如下图Upload HDD1.上传Image文件作为磁盘分区,标签为HDD,类型为硬盘;如下图2.上传完成;3.附加,新附加的介质,iDRAC会中断所有已附加的介质并重新加载,故选择确定即可;如下图4.在系统的显示为可移动磁盘,而不是本地磁盘;如下图命令模式上传ISO1.以命令模式上传ISO 到vFlash中;工具:racadm.exe命令参数:vflashpartition 子命令(create | delete | status | list)-i (索引1-16的数字)-o (卷标,六个字母或数字,不能带空格)-e (类型:Floppy、cddvd、HDD)-t(类型:empty 创建空白分区,image:使用上传的image创建分区)empty - 创建空白分区。

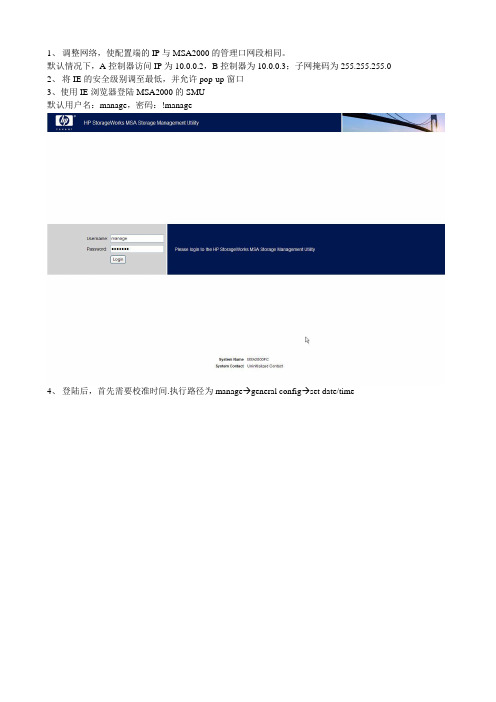

MSA2000简单配置方法

1、调整网络,使配置端的IP与MSA2000的管理口网段相同。

默认情况下,A控制器访问IP为10.0.0.2,B控制器为10.0.0.3;子网掩码为255.255.255.02、将IE的安全级别调至最低,并允许pop-up窗口3、使用IE浏览器登陆MSA2000的SMU默认用户名:manage,密码:!manage4、登陆后,首先需要校准时间.执行路径为manage→general config→set date/timemanage→general config→host port configuration6、建立Vdisk和volume执行路径:manage→virtual disk config→creat a vdisk选择需要加入阵列的磁盘,点击继续此处的选择需要注意第三项“expose volumes to all hosts”(基本意图为是否所有用户都可见)。

如果用户需要配置双机,那么此处可以选择“yes”;如果是不同机器使用不同volume,此时一定要选择“no”。

由于该选项是无法在建立vdisk后进行修改的,所以一定要注意。

否则需要删掉vdisk重新建立。

7、建立好volume后,进行volume mapping。

执行路径:manage→volume management→volume mapping→map hosts to volume在assign host access privileges选项下的host WWN-name下拉菜单中找到对应server上光纤卡的WWN,填写LUN号码(0-127),点击“map it”进行对应。

此时有可能需要加载光纤卡和MSA2000的驱动。

如果涉及到多条链路,需要另行加载多链路软件。

RTL8212

INTEGRATED 10/100/1000 SINGLE/DUALGIGABIT ETHERNET TRANSCEIVERDATASHEETRev. 1.2 15 November 2005 Track ID: JATR-1076-21Realtek Semiconductor Corp.No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, TaiwanTel.: +886-3-578-0211. Fax: +886-3-577-6047 RTL8212-GR RTL8212N-GR RTL8211N-GRIntegrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver ii Track ID: JATR-1076-21 Rev. 1.2COPYRIGHT©2005 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.DISCLAIMERRealtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.TRADEMARKSRealtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.USING THIS DOCUMENTThis document is intended for the hardware and software engineer’s general information on the Realtek RTL8212/RTL8212N/RTL8211N Integrated Circuits.Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.REVISION HISTORY Revision Release Date Summary1.0 2005/08/10 First release.1.1 2005/09/09 1. Add RTL8211N-GR single PHYceiver.2. Correct typo for page 20 P0RXDV description.1.2 2005/11/15 1. Update datasheet and product name to RTL8212, RTL8212N andRTL8211N.2. Remove RSGMII interface from RTL8212 (QFP-128).Table of Contents1.General Description (9)2.Features (10)3.System Applications (10)4.System Application Diagrams (11)5.Block Diagram (13)6.Pin Assignments (14)6.1. RTL8212EDHS QFP-128P ACKAGE (14)6.2. P ACKAGE I DENTIFICATION (RTL8212EDHS QFP-128) (14)6.3. RTL8212N QFN-76P ACKAGE (15)6.4. P ACKAGE I DENTIFICATION (RTL8212N QFN-76) (15)6.5. RTL8211N QFN-76P ACKAGE (16)6.6. P ACKAGE I DENTIFICATION (RTL8211N QFN-76) (16)7.Pin Descriptions (17)7.1. M EDIA D EPENDENT I NTERFACE P INS (17)7.2. GMII/MII T RANSMIT I NTERFACE P INS (18)7.3. GMII/MII R ECEIVE I NTERFACE P INS (19)7.4. RGMII T RANSMIT I NTERFACE P INS (20)7.5. RGMII R ECEIVE I NTERFACE P INS (21)7.6. RSGMII I NTERFACE P INS (21)7.7. S ERIAL M ANAGEMENT I NTERFACE P INS (22)7.8. S ERIAL LED I NTERFACE P INS (22)7.9. S YSTEM C LOCK I NTERFACE P INS (23)7.10. C ONFIGURATION AND C ONTROL P INS (24)7.11. M ISCELLANEOUS P INS (25)7.12. P OWER AND G ROUND P INS (26)Integrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver iii Track ID: JATR-1076-21 Rev. 1.28.1. MDI I NTERFACE (27)8.1.1.Crossover Detection and Auto Correction (27)8.1.2.Polarity Correction (28)8.1.3.MAC Interface (29)8.2. G IGABIT M EDIA I NDEPENDENT I NTERFACE (GMII/MII) (30)8.2.1.Reduced GMII (RGMII) (32)8.2.2.10/100 Functionality (33)8.2.3.TX_CTL and RX_CTL Coding (34)8.2.4.In-Band Status (36)8.2.5.Four RGMII Modes (36)8.3. R EDUCED S ERIAL GMII(RSGMII) (37)8.3.1.RSGMII Data Transfer (39)8.4. MDC/MDIO M ANAGEMENT I NTERFACE (40)8.4.1.Preamble Suppression (41)8.5. H ARDWARE C ONFIGURATION I NTERFACE (42)8.6. LED C ONFIGURATION (43)8.6.1.LED System Application Examples (43)8.6.2.Serial Stream Order (44)8.7. S YSTEM C LOCK I NTERFACE (44)8.8. R EGISTER D ESCRIPTIONS (45)8.8.1.Register Symbols (45)8.8.2.MII Specification Defined Registers (45)8.8.3.Register0: Control (46)8.8.4.Register1: Status (47)8.8.5.Register2: PHY Identifier 1 Register (48)8.8.6.Register3: PHY Identifier 2 Register (48)8.8.7.Register4: Auto-Negotiation Advertisement (49)8.8.8.Register5: Auto-Negotiation Link Partner Ability (50)8.8.9.Register6: Auto-Negotiation Expansion (51)8.8.10.Register7: Auto-Negotiation Page Transmit Register (51)8.8.11.Register8: Auto-Negotiation Link Partner Next Page Register (52)8.8.12.Register9: 1000Base-T Control Register (52)8.8.13.Register10: 1000Base-T Status Register (53)8.8.14.Register15: Extended Status (53)Integrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver iv Track ID: JATR-1076-21 Rev. 1.29.1. A BSOLUTE M AXIMUM R ATINGS (54)9.2. O PERATING R ANGE (54)9.3. DC C HARACTERISTICS (55)9.4. AC C HARACTERISTICS (57)10.Design and Layout Guide (59)10.1. G ENERAL G UIDELINES (59)10.2. MII/GMII/RGMII S IGNAL L AYOUT G UIDELINES (59)10.3. RSGMII S IGNAL L AYOUT G UIDELINES (60)10.4. E THERNET MDI D IFFERENTIAL S IGNAL L AYOUT G UIDELINES (60)10.5. C LOCK C IRCUIT (60)10.6. P OWER P LANES (60)10.7. G ROUND P LANE (61)10.8. T RANSFORMER O PTIONS (61)11.Mechanical Dimensions (62)11.1. EDHS-QFP-128D IMENSIONS (RTL8212) (62)11.2. N OTES FOR EDHS-QFP-128D IMENSIONS (RTL8212) (63)11.3. QFN-76D IMENSIONS (RTL8211N&RTL8212N) (64)11.4. N OTES FOR QFN-76D IMENSIONS (RTL8211N&RTL8212N) (65)12.Ordering Information (66)Integrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver v Track ID: JATR-1076-21 Rev. 1.2List of TablesTable 1. Pin Type Abbreviations (17)Table 2. Media Dependent Interface Pins (17)Table 3. GMII/MII Transmit Interface Pins (18)Table 4. GMII/MII Receive Interface Pins (19)Table 5. RGMII Transmit Interface Pins (20)Table 6. RGMII Receive Interface Pins (21)Table 7. RSGMII Interface Pins (21)Table 8. Serial Management Interface Pins (22)Table 9. Serial LED Interface Pins (22)Table 10. System Clock Interface Pins (23)Table 11. Configuration and Control Pins (24)Table 12. Miscellaneous Pins (25)Table 13. Power and Ground Pins (26)Table 14. Mapping of Twisted-Pair Outputs to RJ-45 Connectors (27)Table 15. Media Dependent Interface Pin Mapping (27)Table 16. Data Rates Supported Through Each Interface (29)Table 17. MAC Interface Modes of Operation (29)Table 18. Gigabit Media Independent Interface (30)Table 19. MAC Interface Modes of Operation (32)Table 20. TX_ER and TX_EN Encoding (34)Table 21. RX_ER and RX_DV Encoding (35)Table 22. RGMII Timing Modes (36)Table 23. Configuration Pin Definitions (42)Table 24. LED Mode (43)Table 25. LED Status (43)Table 26. Serial Stream Order (Mode 0) (44)Table 27. Serial Stream Order (Mode 1) (44)Table 28. MII Specification Defined Registers (45)Table 29. Register0: Control (46)Table 30. Register1: Status (47)Table 31. Register2: PHY Identifier 1 Register (48)Table 32. Register3: PHY Identifier 2 Register (48)Table 33. Register4: Auto-Negotiation Advertisement (49)Integrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver vi Track ID: JATR-1076-21 Rev. 1.2Table 34. Register5: Auto-Negotiation Link Partner Ability (50)Table 35. Register6: Auto-Negotiation Expansion (51)Table 36. Register7: Auto-Negotiation Page Transmit Register (51)Table 37. Register8: Auto-Negotiation Link Partner Next Page Register (52)Table 38. Register9: 1000Base-T Control Register (52)Table 39. Register10: 1000Base-T Status Register (53)Table 40. Register15: Extended Status (53)Table 41. Absolute Maximum Ratings (54)Table 42. Operating Range (54)Table 43. DC Characteristics (55)Table 44. Digital Timing Characteristics (58)Table 45. Ordering Information (66)Integrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver vii Track ID: JATR-1076-21 Rev. 1.2List of FiguresFigure 1. RTL8212N with 8-Port Gigabit MAC (RTL8369) (11)Figure 2. RTL8212 with 24+2G MAC (RTL8326) (12)Figure 3. Block Diagram (13)Figure 4. Pin Assignments (RTL8212 EDHS QFP-128) (14)Figure 5. Pin Assignments (RTL8212N QFN-76) (15)Figure 6. Pin Assignments (RTL8211N QFN-76) (16)Figure 7. Conceptual Example of Polarity Correction (28)Figure 8. GMII Signal Diagram (30)Figure 9. MII Signal Diagram (31)Figure 10. RGMII Signal Diagram (33)Figure 11. RGMII Data Transmission (34)Figure 12. RGMII Data Reception Without Error (35)Figure 13. RGMII Data Reception With Error (35)Figure 14. RSGMII Interconnection Diagram (37)Figure 15. Realtek 8G Switch Application with RSGMII (38)Figure 16. RSGMII Functional Block Diagram at Ethernet PHY Side (39)Figure 17. RSGMII Functional Block Diagram at Ethernet MAC Side (40)Figure 18. MDIO Read Frame Format (41)Figure 19. MDIO Write Frame Format (41)Figure 20. Clock Generated from MAC (RSGMII Mode) (44)Figure 21. MII Interface Reception Data Timing (57)Figure 22. MII Interface Transmission Data Timing (57)Integrated 10/100/1000 Single/ Dual Gigabit Ethernet Transceiver viii Track ID: JATR-1076-21 Rev. 1.21.General DescriptionThe RTL8212/RTL8212N/8211N integrate dual/single independent Gigabit Ethernet transceivers into a single IC and performs all the physical layer (PHY) functions for 10Base-T, 100Base-TX, and 1000Base-T Ethernet on category 3 (10Base-T) or category 5 UTP cable (except 1000Base-T half duplex operation).The device includes the PCS, PMA, and PMD sub-layers. They perform encoding/decoding, clock/data recovery, digital adaptive equalization, echo cancellers, cross-talk elimination, line driver, as well as all other required support circuit functions. The device also integrates an internal hybrid that allows the use of inexpensive 1:1 transformer modules.Each of the two independent transceivers features an industrial standard GMII, MII, and RGMII (Reduced Gigabit Media Independent Interface). To further reduce PCB trace complexity, the RTL8211N/8212N also provides an innovative 2.5Gbps serial interface – the Reduced Serial Gigabit Media Independent Interface (RSGMII). Both dual transceivers can simultaneously communicate with the MAC through the same RSGMII interface.The RTL8212/RTL8212N/8211N adopts mixed mode 0.13µm CMOS technology and analog line driver architecture that offers lower power consumption than DAC architecture.Two package types are available; a thermally-enhanced 128-pin EDHS-QFP (Exposed Drop-in Heat Sink QFP) package, and a QFN (Quad Flat No-Lead) 76-pin package. Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver9Track ID: JATR-1076-21 Rev. 1.22.FeaturesSingle/Dual integrated 10/100/1000Base-T Gigabit Ethernet transceiverSupports full duplex at 10/100/1000Mbps, and half duplex at 10/100MbpsSupports 2.5V I/O (3.3V input tolerance) GMII and RGMII interfaces in 10/100/1000 mode for RTL8212 (QFP-128 Package)Supports RSGMII (2.5Gbps serial high speed interface) in 10/100/1000 mode for RTL8212N and RTL8211N (QFN-76 Package)Crossover detection and auto correction at all 3 speedsAutomatic detection and correction of wiring pair swaps, pair skew, and pair polarity Supports serial LED modeLine driver architecture with low power dissipation PAVE= 0.78W/port3.3V, 1.8V, and 1.2V power supply (2.5V is generated by internal linear regulator forDigital I/O pads)Packages:EDHS QFP-128, 14x20mm, 0.5mm lead pitch packageQFN-76, 9x9mm, 0.4mm pitch package0.13µm CMOS process3.System ApplicationsHigh-density Gigabit Ethernet switches and routersIntegrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver10Track ID: JATR-1076-21 Rev. 1.24.System Application DiagramsFigure 1. RTL8212N with 8-Port Gigabit MAC (RTL8369)Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver11Track ID: JATR-1076-21 Rev. 1.2Figure 2. RTL8212 with 24+2G MAC (RTL8326)Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver12Track ID: JATR-1076-21 Rev. 1.2Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 13 Track ID: JATR-1076-21 Rev. 1.25. Block DiagramXTAL2XTAL1CLK25M-IN CLK25M-OUT LEDCK LEDDAMDI_REFPAIR APAIR BPAIR CPAIR DMDC MDIOPHYADD[4..1]MODE[2..0]INTF_SEL[2..0]PnTXD[7..0]PnGTXC PnTXEN PnTXC PnCOL PnCRS PnRXD[7..0]PnRXC PnRXDV PnRXERSTXP STXN SRXP SRXN SDS_REFRESETBFigure 3. Block DiagramIntegrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver14 Track ID: JATR-1076-21 Rev. 1.26. Pin Assignments6.1. RTL8212 EDHS QFP-128 PackageV D D 12P 0R X D 5/P H Y A D R [4]V S S 12P 1T X D 7P 0R X D 7/I N T F _S E L [1]P 0R X D 6/I N T F _S E L [0]V S S 12P 0G T X C P 0R X D 2/P H Y A D R [1]P 0R X D 1V D D I O P 0M D I B P 0M D I B P 0M D I A P 0M D I A A V D D 33A V D D 18A V D D 1P 1M D I A P 1M D I A A V D D 3A V D D 1P 0M D I D A V S P 0M D I C P 0M D I C P 1M D I B M D I _R E P 1M D I D P 1M D I C P 1M D I C A V D D 1A V D D P L A V S S X TA L2A V S S P L P 0TX D 7A V S P 1M D I B P 1M D I D M D IOL E D D P 0TX D 1M D P 0TX D 6P 0TX D 4P 0TX D 3P 0TX D 2V D D 12V S S 12P 0TX D 5X TA L1A V D D 33A V D D 12A V S S P 0M O D E [0]/ P 0C R SV S S IO V D D IO P 0TX E N P 0TX C R T T L E D C R T T 2P 0TX D 0P 0M D I D A V S A V S A V D D 1A V D D 3N C A V S S N C A V S S N C N C S V D D 18S V D D 12C L K I N A T E S V D D IO P 1T X D 5V D D 12P 1T X D 0P 1T X D 3P 1T X D 4V S S 12P 1T X D 1P 1T X D 2P 1T X D 6V D D I O P 1C R S /P 1M O D E [0]P 0R X D 4/P H Y A D R [3]P 0R X D 3/P H Y A D R [2]V D D 12P 1T X C P 1G T X C P 1T X E N V D D 12D IS _A U T O X O VE R / P 0R X D 0P 0M O D E [3]/ P 0R X D VP 0M O D E [2]/ P 0R X E RP 0M O D E [1]/ P 0C O L P 0R X CV S S 12R V D D 33R V D D 33V D D 12V S S 12V D D IO P 1R X D 1P 1R X D 2 /R X D LY V S S 12P 1R X D 7P 1R X D 5P 1R X D 6P 1R X D 4/LE D M O D E V S S IO V D D 12P 1R X D 3 /TX D LY P 1R X C P 1R X E R /P 1M O D E [2]P 1C O L /P 1M O D E [1]V S S 12P 1R X D V /P 1M O D E [3]P 1R X D 0V D D 12V D D IO R E S E TBFigure 4. Pin Assignments (RTL8212 EDHS QFP-128)6.2. Package Identification (RTL8212 EDHS QFP-128)Green package is indicated by a ‘G’ in the location marked ‘T’ in Figure 4.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver15 Track ID: JATR-1076-21 Rev. 1.26.3. RTL8212N QFN-76 PackageP 1M D I A P A V D D 18P 0M D I D N P 0M D I C P 0M D I B P P 0M D I C P P 1M D I A N P 1M D I D P P 1M D I D P 1M D I C N A V D D 18P 1M D I B P P 1M D I B N P 0M D I D P P 0M D I B N P 0M D I A P P 0M D I A N P 1M D I C P A V D D 18RVDD33RESETB AVDD12AVDD33MDIREF RTT2VDD12VDD12P1MODE[1]P1MODE[2]P1MODE[0]VDDIO NC VDDIO AVDDPLL AVDD18AVDD33P1MODE[3]RTT1VDDIO P0MODE[1]RVDD33VDD12DIS_AUTOXOVERP0MODE[3]MDC AVDD18AVDD33LEDCK LEDDA MDIO P0MODE[0]VDDIO PHYADR[1]NC P0MODE[2]S V D D 12S T X N C L K I N S R X N S R X P V D D I O V D D 12P H Y A D R [3]P H Y A D R [4]V D D 12S T X P V D D 12V D D 12N C P H Y A D R [2]S V D D 18NCS V S S 12S V S S 18V D D I O VDD12Figure 5. Pin Assignments (RTL8212N QFN-76)6.4. Package Identification (RTL8212N QFN-76)Green package is indicated by a ‘G’ in the location marked ‘T’ in Figure 5.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 16Track ID: JATR-1076-21Rev. 1.26.5.RTL8211N QFN-76 PackageFigure 6. Pin Assignments (RTL8211N QFN-76)6.6. Package Identification (RTL8211N QFN-76)Green package is indicated by a ‘G’ in the location marked ‘T’ in Figure 6.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 17 Track ID: JATR-1076-21 Rev. 1.27. Pin DescriptionsTable 1. Pin Type Abbreviations Pin Type Definition I Input O OutputI/O Bi-directional B Bias PU Internal pull-up PD Internal pull-down PWR Power GND GroundNote: The RTL8212/RTL8212N/RTL8211N is a dual-port/single Gigabit Ethernet transceiver. Each port, defined as Port0 and Port1 (Port 0 for RTL8211N), is independent of the other, and is identical in performance and functionality. In this document, these pins for each port are specified by the port number, pin name, and signal number, respectively.For example, GMII transmit data pin 7 for port0 is shown as: P0TXD77.1. Media Dependent Interface PinsTable 2. Media Dependent Interface PinsQFN76 Pin# QFP128 Pin# Pin Name Type Description1, 2 3, 4 6, 7 8, 9 11, 12 13, 14 16, 17 18, 197, 8 10, 11 13, 14 16, 17 20, 21 23, 24 26, 27 29, 30P0MDIAP/N P0MDIBP/N P0MDICP/N P0MDIDP/N P1MDIAP/N P1MDIBP/N P1MDICP/N P1MDIDP/NI/OMedia Dependent Interface A~D. For 1000Base-T operation, differential data from the media is transmitted and received on all four pairs. For 100Base-Tx and 10Base-T operation, only MDIAP/N and MDIBP/N are used. Auto MDIX can reverse the pairs MDIAP/N and MDIBP/N.Each of the differential pairs has an internal 100ohm termination resister.Pins 11, 12, 13, 14, 16, 17, 18, and 19 of the QFN-76 package are N.C pins for the RTL8211N-GR.TheRTL8211N-GR is available in a QFN-76 package only.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 18 Track ID: JATR-1076-21 Rev. 1.27.2. GMII/MII Transmit Interface PinsTable 3. GMII/MII Transmit Interface PinsQFN76 Pin# QFP128 Pin#Pin Name Type Description117 69 P0GTXCP1GTXC I GMII Transmit Clock. 125MHz input clock. All transmit inputs must be synchronized to this clock during 1000Base-Toperation. This clock can be stopped in 10/100Base-T modes, and also during Auto-Negotiation.116 68P0TXC P1TXC OMII Transmit Clock. All transmit inputs must be synchronized to this clock during 10/100 operation. It provides a 25MHz clock reference in 100Base-TX mode, and 2.5MHz clock reference in 10Base-T.The 25MHz clock is the default rate.118 70 P0TXENP1TXENIGMII/MII Transmit Enable. The synchronous input indicates that valid data is being driven on the TXD bus. As the RTL8212 does not support 1000Base-T half-duplex mode, thecarrier-extension symbol is not transmitted onto the cable.TXEN is synchronous to GTXC in 1000Base-T mode and synchronous to TXC in 10/100Base-TX mode.127 126 125 124 123 122 121 120 91 80 79 78 76 75 73 72 P0TXD7 P0TXD6 P0TXD5 P0TXD4 P0TXD3 P0TXD2 P0TXD1 P0TXD0 P1TXD7 P1TXD6 P1TXD5 P1TXD4 P1TXD3 P1TXD2 P1TXD1 P1TXD0I PDGMII/MII Transmit Data Bus. The width of this synchronous input bus varies with the speed mode: 1000: TXD[7:0] are used.10/100: TXD[3:0] are used; TXD[7:4] are ignored.TXD[7:0] is synchronous to GTXC in 1000Base-T mode and synchronous to TXC in 10/100Base-TX mode.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 19 Track ID: JATR-1076-21 Rev. 1.27.3. GMII/MII Receive Interface PinsTable 4. GMII/MII Receive Interface PinsQFN76 Pin# QFP128 Pin#Pin Name Type Description109 62 P0RXCP1RXCO PDGMII/MII Receive Clock. The GMII/MII Receive output clock is used to synchronize received signals. Its frequency depends upon the link speed: 1000: 125MHz 100: 25MHz 10: 2.5MHz107 60 P0RXDVP1RXDVO PDGMII/MII Receive Data valid. This synchronous output is asserted when valid data is driven on RXD.RXDV is synchronous to RXC.115 65 P0CRS P1CRSO PDGMII/MII Carrier Sense. This asynchronous output is asserted when a non-idle condition is detected at the twisted-pair interface, and de-asserted when idle or a valid end of stream delimiter is detected. In 10/100Base-T half duplex, CRS is also asserted during transmission.CRS is asynchronous to TXC and RXC.114 64 P0COL P1COLO PDGMII/MII Collision. This asynchronous output is asserted when a collision is detected in half-duplex modes. In full duplex mode, this out is forced low.COL is asynchronous to TXC, and RXC.110 63 P0RXER P1RXERO PDGMII/MII Receive Error. When RXER and RXDV are both asserted, the symbol indicates an error symbol is detected on the cable. Since RTL8212 don’t support 1000Base-T half-duplex mode, carrier-extension receive symbol (RXER is asserted with RXDV deasserted) is not valid.RXDV is synchronous to RXC.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 20 Track ID: JATR-1076-21 Rev. 1.2QFN76 Pin# QFP128 Pin#Pin Name Type Description93949697981011021064849515254555659P0RXD7 P0RXD6 P0RXD5 P0RXD4 P0RXD3 P0RXD2 P0RXD1 P0RXD0 P1RXD7 P1RXD6 P1RXD5 P1RXD4 P1RXD3 P1RXD2 P1RXD1 P1RXD0 O PDGMII/MII Receive Data Bus. The width of this synchronousoutput bus varies with the speed mode: 1000: RXD[7:0] are used.10/100: RXD[3:0] are used; RXD[7:4] are ignored.RXD[7:0] is synchronous to RXC.7.4. RGMII Transmit Interface PinsTable 5. RGMII Transmit Interface PinsQFN76 Pin# QFP128 Pin#Pin Name Type Description117 69 P0GTXCP1GTXCIRGMII Transmit Clock. All transmit inputs must besynchronized to this clock. Its frequency, with +/- 50ppm tolerance, depends upon the link speed: 1000: 125MHz 100: 25MHz 10: 2.5MHz123 122 121 120 76 75 73 72 P0TXD3P0TXD2 P0TXD1 P0TXD0 P1TXD3 P1TXD2 P1TXD1 P1TXD0I PDRGMII Transmit Data Bus. In RGMII 1000Base-T mode,TXD[3..0] runs at a double data rate with bits[3..0] presented on the rising edge of the GTXC, and bits[7..4] presented on the falling edge of the GTXC. TXD[7..4] are ignored in this mode.In RGMII 10/100Base-T modes, the transmitted data nibble is presented on TXD[3..0] on the rising edge of GTXC and duplicated on the falling edge of GTXC.118 70 P0TXEN/P0TXCTL P1TXEN/P1TXCTLI PDRGMII Transmit Control. In RGMII mode, TXEN is used as TXCTL. TXEN is presented on the rising edge of GTXC.A logical derivative of TXEN and TXER is presented on the falling edge of GTXC.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 21 Track ID: JATR-1076-21 Rev. 1.27.5. RGMII Receive Interface PinsTable 6. RGMII Receive Interface Pins QFN76 Pin# QFP128 Pin#Pin NameType Description 109 62 P0RXCP1RXCO RGMII Receive Clock. All RGMII receive outputs must be synchronized to this clock. Its frequency, with +/- 50ppm tolerance, depends upon the link speed:1000: 125MHz100: 25MHz10: 2.5MHz98 101 102 106 54 55 56 59 P0RXD3 P0RXD2 P0RXD1 P0RXD0 P1RXD3 P1RXD2 P1RXD1 P1RXD0 O PD RGMII Receive Data Bus. In RGMII 1000Base-T mode,RXD[3..0] runs at a double data rate with bits[3..0] presented onthe rising edge of the RXC and bits[7..4] presented on thefalling edge of the RXC. RXD[7..4] are ignored in this mode.In RGMII 10/100Base_T modes, the received data nibble ispresented on RXD[3..0] on the rising edge of RXC and duplicated on the falling edge of RXC.107 60 P0RXCTL/ P0RXDV P1RXCTL/ P1RXDV O PDRGMII Receive Control. In RGMII mode, RXDV is used asRXCTL. RXDV is presented on the rising edge of RXC.A logical derivative of RXDV and RXER is presented on thefalling edge of RXC.7.6. RSGMII Interface PinsTable 7. RSGMII Interface PinsQFN76Pin#QFP128 Pin# Pin Name Type Description 4445N/A SRXP SRXN O RSGMII Receive Pair. 2.5GHz differential serial output. The differential pair has an internal 100ohm termination resister.4950 N/A STXP STXNI RSGMII Transmit Pair. 2.5GHz differential serial input. The differential pair has an internal 100ohm termination resister.Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 22 Track ID: JATR-1076-21 Rev. 1.27.7. Serial Management Interface PinsTable 8. Serial Management Interface Pins QFN76 Pin# QFP128 Pin#Pin Name Type Description71 1 MDC I Management Data Clock. The clock reference for the serialmanagement interface.70 128 MDIO I/O PU Management Data Input/Output. MDIO transfer managementdata; in and out of the device synchronous to the rising edge ofMDC.54 55 56 58 96 97 98 101 PHYADR[4]/P0RXD5 PHYADR[3]/ P0RXD4 PHYADR[2]/ P0RXD3 PHYADR[1]/P0RXD2O PD PHY Address Select. These pins are the four uppermost bits of the 5-bit IEEE-specified PHY address. The states of these four pins are latched during power-up or reset. The lowest bit of the 5-bit PHY address is hard-wired to each of the dual ports within the device. ‘0’ represents Port0, and ‘1’ represents Port1.7.8. Serial LED Interface PinsTable 9. Serial LED Interface PinsQFN76 Pin# QFP128 Pin#Pin Name Type Description72 2 LEDCK O Serial LED Clock. Reference output clock for serial LEDinterface.The 12.5MHz clock outputs periodically. Data is latched on therising edge of LEDCK.73 3 LEDDA O Serial LED Data Output. Serial bit stream of link statusinformation.32 52 LEDMODE/ P1RXD4 O PD Serial LED Mode Select. These pins are used to configure LEDoperation mode. The state of this pin is latched during power-up or reset. There are two LED display modes:0: Mode 01: Mode 1Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 23 Track ID: JATR-1076-21 Rev. 1.27.9. System Clock Interface PinsTable 10. System Clock Interface Pins QFN76 Pin# QFP128 Pin#Pin Name Type Description42 XTAL1 I PHY Reference Clock Input. 25MHz +/- 50ppm tolerance crystalreference or oscillator input. When using a crystal, connect aloading capacitor from each pad to ground.When CLKIN is used this pin is not valid and should bepulled-low.The maximum XTAL1 input voltage is 1.8 V .41 XTAL2 O PHY Reference Clock Output. 25MHz +/- 50ppm tolerance crystalreference or oscillator output.When CLKIN is used this pin is not valid and should be floating.47 CLKIN I 25MHz Clock Input. 25MHz +/- 50ppm tolerance clock input.When RSGMII is used this pin is able to accept a 25MHz clocksignal generated from the MAC device (RTL8212N/RTL8211Nonly).The maximum CLKIN input voltage is 1.8V .Integrated 10/100/1000 Single/Dual Gigabit Ethernet Transceiver 24 Track ID: JATR-1076-21 Rev. 1.27.10. Configuration and Control PinsTable 11. Configuration and Control Pins QFN76 Pin# QFP128 Pin#Pin NameType Description 93 94 INTF_SEL[1]/P0RXD7INTF_SEL[0]/P0RXD6 O PD MAC Interface mode select. INTF_SEL[1:0] determines the MAC interface configuration for both port0 and port1: 00: RSGMII (default mode) 01: GMII10: RGMII11: Reserved6364 67 68 35 36 37 38 107 110 114 115 60 63 64 65 P0MODE[3]/ P0RXDV P0MODE[2]/ P0RXER P0MODE[1]/ P0COL P0MODE[0]/ P0CRS P1MODE[3]/ P1RXDV P1MODE[2]/ P1RXER P1MODE[1]/ P1COL P1MODE[0]/ P1CRS O PD Auto-Negotiation Configuration. PxMODE[3:0] presets each port’s advertise link ability (speed, duplex, and master/slave). The states of this pin is latched during power-up or reset. PxMODE[3:0] defined as: 0000=Auto-negotiation, advertise all capabilities, prefer MASTER. 0001=Auto-negotiation, advertise all capabilities, prefer SLA VE. 0010=Auto-negotiation, advertise only 100Base-TX half duplex. 0011=Auto-negotiation, advertise only 100Base-TX full duplex. 0100=Reserved. 0101=Reserved. 0110=Reserved. 0111=Reserved. 1000=Auto-negotiation, advertise only 1000Base-T full duplex, force MASTER. 1001=Auto-negotiation, advertise only 1000Base-T full duplex, force SLA VE. 1010=Auto-negotiation, advertise only 1000Base-T full duplex, prefer MASTER.1011=Auto-negotiation, advertise only 1000Base-T full duplex,prefer SLA VE.1100=Auto-negotiation, advertise all capabilities, force MASTER.1101=Auto-negotiation, advertise all capabilities, force SLA VE.1110=Auto-negotiation, advertise only 10Base-T half duplex.1111=Auto-negotiation, advertise only 10Base-T full duplex.54 TXDLY/ P1RXD3O PD GTXC Clock Delay Select. This pin enables GTXC input delay inRGMII mode (see Table 22 for detailed configuration). 55 RXDLY/ P1RXD2O PD RXC Clock Delay Select. This pin enables RXC output delay inRGMII mode (see Table 22 for detailed configuration). 62 106 DIS_AUTOXOVER/ P0RXD0O PD 1: Disable auto crossover detection 0: Enable auto crossover detection。

配置HP_MSA2312

配置HP MSA 2000MSA2000默认控制器IP即Management Port IP Address:10.0.0.2 (controller A), 10.0.0.3 (controller B)IP Subnet Mask: 255.255.255.0Gateway IP Address: 10.0.0.11、通过IE输入要配置的控制器的地址,配置基本信息。

Msa 2000控制器的默认用户名密码:user name :managepassword :!manage(首先配置服务器上的网卡使之与控制器的IP地址在同一网段,游览器需支持JAVA)2、建立虚拟磁盘---配置磁盘阵列选择要配置在一个Vdisk 的物理硬盘。

选择在此vdisk上建立卷的数量输入卷的大小和卷名(只是对于这个卷的标注)后选择添加卷。

Vdisk 建立后可通过“视图”--“概况”查看现有vdisk 的建立状态。

初始化完成后操作系统才可以识别到存储空间,但初始化程度不会影响分配vdisk。

初始化时vdisk的状态是Critical,(初始化时间视磁盘数量,会很漫长)。

3、分配卷给服务器首先给光纤卡和所对应的控制器端口起一个别名,然后将卷分配给相应的服务器。

(主机映射)光纤卡的WWN可通过Home及光纤卡背部看到,弄清楚光纤卡WWN与控制器端口的对应关系后给相应端口起一个别名(Nickname)。

在操作系统下识别光纤卡的WWN请看本人的另作《几种系统下查看FC HBA卡信息的方法》。

完成以上操作后,服务器即可识别存储空间,如一台服务器安装了两块HBA,还需要下载/安装双HBA绑定程序将两块H BA卡绑带为一条链路以实现链路冗余。

HP MSA 2312 Storage Management Utility UI。

博世FlexiDomeDN IP网络摄像头操作指南说明书

55

7.7.1

iSCSI IP address (iSCSI IP 地址)

55

7.7.2

iSCSI LUN map (iSCSI LUN 映射)

55

7.7.3

Target IP address (目标 IP 地址)

56

7.7.4

Target node (目标节点)

56

7.7.5

Target LUN (目标 LUN)

56

7.7.6

Target password (目标密码)

56

7.7.7

Initiator name (启动程序名称)

56

7.7.8

Initiator extension (启动程序扩展)

56

7.7.9

Decoupling the drive used (断开使用的驱动器)

57

7.7.10 Storage information (存储信息)

4

摄像机设置

4.1

摄像机定位

4.2

焦距和焦点

4.3

基本设置

博世安保有限公司

操作指南

| 中文 3

13 14 14 15 15 15 16 16 16 16 16 16 16 17 17 17 17 17 17

18

19 20 20 20 21 21

22 22 23 23

V 1.0 | 2006.12

4 中文 |

74

7.13.6 Send e-mail for testing (发送电子邮件进行测试)

74

7.14

Service Settings (服务设置)

74

7.14.1 Network (网络)

VDX6740基础配置文档

博科VDX交换机快速配置手册一、登录交换机1.1串口线连接Windows平台:传输速率:9600bit/sec数据位:8校验位:None停止位:1流控制:None1.2登录交换机➢用户级别VDX Switch > enable ------只能使用?、ping 和 show命令VDX Switch # ------查看交换机详细信息➢全局配置模式VDX Switch # configure terminalVDX Switch (config) # ------配置模式二、升级交换机固件1、给交换机配一个管理地址:VDX Switch # conf tVDX Switch # interface Management 1/0VDX Switch # ip address 10.77.77.76/242、使用FTP服务器升级固件VDX switch# firmware download interactivefirmware download interactiveServer name or IP address: 10.31.2.25File name:/users/home40/Builds/NOS_v5.0.0Protocol (ftp, scp, sftp): ftpUser:fvtPassword:**********Do manual download [y/n]:nSystem sanity check passed.Do you want to continue? [y/n]:y使用USB升级固件VDX Switch # usb onVDX Switch # usb dirVDX Switch # firmware download usb directory nos6.0.0 coldbootPerforming system sanity check...This command will cause a cold/disruptive reboot and will require that existing telnet, secure telnet or SSH sessions be restarted.Do you want to continue? [y/n]:yChecking conditions for downloading to 6.0.0System settings check passed (0).检查升级后的版本VDX Switch # show version三、调整时区+设置本地时间VDX Switch # clock timezone Asia/Shanghai (修改时区)VDX Switch # clock set 2015-05-21T16:10:00(设置本地时间)VDX Switch # show clockrbridge-id 1: 2015-05-21 15:56:10 Asia/Shanghai四、设置timeoutVDX Switch (config)# line vty exec-timeout 5 (设置超时时间为5分钟)VDX Switch (config-line-vty)# do show running-config line vtyline vtyexec-timeout 5!五、添加/移除license添加license:VDX Switch # license add licStr “*B H**********#“ (添加license)移除license:VDX Switch # license remove licStr “FCOE_BASE“ (移除license)六、设置登录密码VDX Switch(config)# username admin role admin password password enable true七、修改设备名称VDX Switch # conf tVDX Switch (config)# switch-attributes 1 host-name VDX6740 chassis-name VDX6740 八、关闭telnet:Switch(config)# telnet server shutdown在VCS模式中关闭telnet:Switch(config)#rbridge-id 3Switch (config-rbridge-id-3)# telnet server shutdown启用telnet:Switch (config)# no telnet server shutdown九、组建VCS逻辑机箱同一个VCS 中每台VDX具有不同的RB-id和相同的VCSID:VDX Switch # vcs rbridge-id 1 vcsid 12 logical-chassis enableVDX Switch # show fabric islports all十、修改principle switchVDX switch# configureVDX switch(config)# rbridge-id 5VDX switch(config-rbridge-id-5)# logical-chassis principal-priority 1VDX switch(config-rbridge-id-5)# endVDX switch# logical-chassis principal-switchover十一、创建VLANVDX Switch (config)# interface vlan 10VDX Switch (config)# interface TenGigabitEthernet 1/0/1-4VDX Switch (conf-if-te-1/0/1-4)# switchportVDX Switch (conf-if-te-1/0/1-4)# switchport mode accessVDX Switch(conf-if-te-1/0/1-4)# switchport access vlan 10十二、给VLAN配置IP地址VDX Switch (config)# rb 1VDX Switch (config-rbridge-id-1)# interface ve 10VDX Switch (config-rbridge-Ve-30)# ip address 172.168.2.19/24VDX Switch (config-rbridge-Ve-30)# no shutdown十三、配置生成树协议(STP/RSTP)VDX Switch (config)# protocol spanning-tree stp/rstpVDX Switch (config-stp)# bridge-priority 4096十四、配置多生成树(MSTP)VDX Switch (config)# protocol spanning-tree mstpVDX Switch (config-mstp)# instance 10 vlan 10-19VDX Switch (config-mstp)# instance 20 vlan 20-29VDX Switch (config-mstp)# instance 10 priority 4096VDX Switch (config)# interface TenGigabitEthernet 1/0/1-4VDX Switch (conf-if-te-1/0/1-4)# switchport mode trunkVDX Switch (conf-if-te-1/0/1-4)# switchport trunk allowed vlan allVDX Switch (conf-if-te-1/0/1-4)# int te 2/0/1-4VDX Switch (conf-if-te-2/0/1-4)# switchport mode trunkVDX Switch (conf-if-te-2/0/1-4)# switchport trunk allowed vlan all十五、配置vLAGVDX Switch (config)# interface Port-channel 10VDX Switch (config-Port-channel-10)# vlag ignore-splitVDX Switch (config-Port-channel-10)# switchportVDX Switch (config-Port-channel-10)# switchport mode trunkVDX Switch (config-Port-channel-10)# switchport trunk allowed vlan all VDX Switch (config-Port-channel-10)# no shutdownVDX Switch_1 (config)# int te 1/0/1VDX Switch (conf-if-te-1/0/1)# channel-group 10 mode active type standard VDX Switch_2 (conf-if-te-1/0/1)# int te 2/0/1VDX Switch (conf-if-te-2/0/1)# channel-group 10 mode active type standard 十六、配置静态路由静态路由不是全局参数,需要进入到每台设备上配置:VDX SWITCH (config)# rb 1VDX SWITCH (config-rbridge-id-1)# ip route x.x.x.x/x x.x.x.xVDX SWITCH (config)# rb 2VDX SWITCH (config-rbridge-id-2)# ip route x.x.x.x/x x.x.x.x十七、配置OSPFOSPF不是全局参数,需要进入到每台设备上配置:VDX SWITCH (conf)# rb 1VDX SWITCH (config-rbridge-id-1)# router ospfVDX SWITCH (config-router-ospf-vrf-default-vrf)# area 0VDX SWITCH (config-rbridge-id-1)# int ve 30VDX SWITCH (config-rbridge-Ve-30)# ip ospf area 0VDX SWITCH (config)# rb 2VDX SWITCH (config-rbridge-id-2)# router ospfVDX SWITCH (config-router-ospf-vrf-default-vrf)# area 0VDX SWITCH (config-router-ospf-vrf-default-vrf)# int ve 30 VDX SWITCH (config-rbridge-Ve-30)# ip ospf area 0十八、配置VRRP/VRRP-ERB1:VDX SWITCH (config)#rbridge 1VDX SWITCH (config)#protocol vrrp-extendedVDX SWITCH (config)#interface ve 30VDX SWITCH (config)#vrrp-extended-group 30VDX SWITCH (config)#priority 125VDX SWITCH (config)#advertise-backup enableVDX SWITCH (config)#preempt-mode enableVDX SWITCH (config)# short-path-forwarding revert-priority 90 VDX SWITCH (config)#vritual-ip 172.168.2.100VDX SWITCH (config)#track ten 1/0/6 priority 20VDX SWITCH (config)#enableRB2:VDX SWITCH (config)#rbridge 2VDX SWITCH (config)#protocol vrrp-extendedVDX SWITCH (config)#interface ve 30VDX SWITCH (config)#vrrp-extended-group 30VDX SWITCH (config)#priority 120VDX SWITCH (config)#advertise-backup enableVDX SWITCH (config)#preempt-mode enableVDX SWITCH (config)# short-path-forwarding revert-priority 90 VDX SWITCH (config)#vritual-ip 172.168.2.100VDX SWITCH (config)#track ten 2/0/6 priority 10VDX SWITCH (config)#enable十九、配置FlexportVDX SWITCH (config)# hardwareVDX SWITCH (config-hardware)# flexport 2/0/45VDX SWITCH (config-flexport-2/0/45)# flexport 2/0/46VDX SWITCH (config-flexport-2/0/46)# flexport 2/0/47VDX SWITCH (config-flexport-2/0/47)# flexport 2/0/48VDX SWITCH (config-hardware)# flexport 2/0/45VDX SWITCH (config-flexport-2/0/45)# type fibre-channelVDX SWITCH (config-flexport-2/0/45)# flexport 2/0/46VDX SWITCH (config-flexport-2/0/46)# type fibre-channel VDX SWITCH (config-flexport-2/0/46)# flexport 2/0/47 VDX SWITCH (config-flexport-2/0/47)# type fibre-channel VDX SWITCH (config-flexport-2/0/47)# flexport 2/0/48 VDX SWITCH (config-flexport-2/0/48)# type fibre-channel二十、QSFP breakout 配置VDX SWITCH (config)#interface fortygigabitethernet 1/0/49 VDX SWITCH (conf-if-fo-1/0/49)# shutdownVDX SWITCH (conf-if-fo-1/0/49)#exitVDX SWITCH (config)#hardwareVDX SWITCH (config-hardware)#connector 1/0/49VDX SWITCH (conf-if-fo-1/0/49)#sfp breakoutVDX SWITCH (conf-if-fo-1/0/49)#do reload二十一、设置syslog服务器VDX SWITCH (config)# logging syslog-server x.x.x.x二十、收集supportsave存放到到FTP服务器:VDX SWITCH (config)# copy support-interactiveServer Name or IP Address: 172.168.2.25Protocol (ftp, scp): ftpUser: adminPassword: *****Directory:/home/admin/supportVCS support [y/n]? (y): y存放到到USB:switch# usb onUSB storage enabledswitch# usb dirfirmwarekey\ 0B 2010 Aug 15 15:13support\ 106MB 2010 Aug 24 05:36support1034\ 105MB 2010 Aug 23 06:11config\ 0B 2010 Aug 15 15:13firmware\ 380MB 2010 Aug 15 15:13Available space on usbstorage 74%switch# copy support usb directory support。

浪潮存储DCS02系统产品安装指导书V1.1版(本指导书适用于AS500G,AS500E存储安装)

涉密第1页/共41页IT service management | 2013 INSPUR ™Copyright and Confidentiality StatementAny information contained in this document, whether it is related to Inspur or its partners, including but not limited to functional description, policies, processes, decisions, employee information, agent and customer information, and all financial data, shall be kept in strict confidence.Copyright© Inspur Group Limited 2014文档信息文档修改记录版权及保密性声明本文档中包含的所有信息,无论涉及到浪潮还是其合作伙伴(包括但不限于功能描述、政策、流程、决定、雇员信息、代理及客户信息以及所有的财务信息),都必须绝对保密。

本文件中出现的任何文字叙述、文档格式、插图、照片、方法、过程等内容,除另有特别注明,版权均属浪潮信息所有,受到有关产权及版权法保护。

任何单位和个人未经浪潮信息的书面授权许可,不得复制或引用本文件的任何片断,无论通过电子形式或非电子形式。

浪潮集团版权所有© 2013目录1.产品介绍 (5)1.1.产品参数 (5)2.调试过程 (5)2.1.硬件安装 (5)2.1.1.硬盘安装 (5)2.1.2.连接扩展柜 (6)2.2.系统授权码申请及注册 (7)2.2.1.获取机器码 (7)2.2.2.授权码注册 (8)重要说明 (8)2.3.存储配置 (8)2.3.1.磁盘信息 (9)2.3.2.卷组管理 (11)2.3.3.逻辑卷管理 (12)3.映射主机 (14)3.1.FC-SAN (14)3.1.1.FC主机组管理 (14)3.1.2.增加FC主机 (15)3.2.IP-SAN (18)3.2.1.主机组信息 (18)3.2.2.新建主机组 (19)3.2.3.增加主机 (19)3.2.4.映射磁盘 (19)4.IP-SAN环境ISCSI启动器的安装与配置 (20)4.1.WINDOWS系统ISCSI启动器安装与配置 (20)4.2.Linux 上启动器的安装和使用 (26)5.多路径软件的安装 (28)5.1.Windows多路径功能 (28)5.1.1.Windows 2003 MPIO安装设置 (28)5.1.2.Windows 2008 MPIO 安装设置 (28)5.1.3.Linux多路径安装配置 (36)6.其他 (40)1.产品介绍1.1. 产品参数2.调试过程2.1. 硬件安装2.1.1.硬盘安装将硬盘从硬盘包装袋中取出,按从右到左的顺序逐一安装硬盘,硬盘安装到位后,应扣紧卡扣,使硬盘面板齐平,如下图2.1.2.连接扩展柜AS500G/AS500E的扩展柜为AS500GJ或者AS500EJ扩展柜示意图如下:连接一个扩展柜方法连接多个扩展柜方法2.2. 系统授权码申请及注册2.2.1.获取机器码通过控制器的IP地址登陆每个控制器,获取两个控制器的机器码2.2.2.授权码注册将两个控制器的系统机器码、购买的功能选择等信息发送给浪潮客户服务部为您产生产品授权码,并发送邮件或致电给您。

博科BrocadeSAN交换机常用命令

博科Brocade SAN交换机常用命令1.查看IP地址命令 (2)2.查看firmware版本 (2)3.查看交换机状态 (2)4.查看交换机license-id (3)5.配置ZONE (3)6.查看zone配置文件 (4)7.查看ZONE (5)8.查看系统日志信息 (6)9.关机 (6)10.设置博科Brocade交换机IP地址 (6)11.博科brocade交换机查看OS版本信息 (6)12.博科brocade交换机添加license授权信息 (7)13.查看博科brocade交换机license授权信息 (7)14.博科Brocade Slikworm 300交换机license (7)15.博科Brocade交换机修改密码命令 (7)16.博科 brocade SAN交换机密码重置 (8)17.登陆后是用passwddefault命令恢复出厂密码 (9)18.交换机升级 (9)19.帮助信息 (13)1.查看IP地址命令swd77:admin> ipaddrshowSWITCHEthernet IP Address: 10.77.77.77Ethernet Subnetmask: 255.255.255.0Fibre Channel IP Address: noneFibre Channel Subnetmask: noneGateway IP Address: noneDHCP: Offswd77:admin>2.查看firmware版本swd211:admin>swd211:admin> firmwareshowAppl Primary/Secondary Versions------------------------------------------FOS v6.2.1v6.2.13.查看交换机状态swd211:admin> switchoshowrbash: switchoshow: command not foundswd211:admin> switchshowswitchName: swd211switchType: 34.0switchState: OnlineswitchMode: NativeswitchRole: PrincipalswitchDomain: 1switchId: fffc01switchWwn: 10:00:00:05:1e:02:a2:10zoning: ON (FC01)switchBeacon: OFFArea Port Media Speed State Proto=====================================0 0 id N2 Online F-Port 50:08:05:f3:00:1b:4e:911 1 id N4 Online F-Port 10:00:00:00:c9:53:b2:8d2 2 id N4 Online F-Port 10:00:00:00:c9:53:b3:c13 3 id N4 Online F-Port 10:00:00:00:c9:53:b3:c24 4 id N4 Online F-Port 50:06:0b:00:00:66:00:c45 5 id N4 Online F-Port 50:06:0b:00:00:66:01:1e6 6 id N2 Online F-Port 50:05:08:b3:00:93:b2:817 7 -- N4 No_Module8 8 id N4 Online F-Port 50:01:43:80:04:c7:87:d89 9 id N4 Online F-Port 50:01:43:80:04:c7:87:dc10 10 id N4 Online F-Port 50:01:43:80:06:31:cf:7c11 11 -- N4 No_Module12 12 -- N4 No_Module13 13 -- N4 No_Module14 14 -- N4 No_Module15 15 -- N4 No_Moduleswd211:admin>4.查看交换机license-idswd211:admin>swd211:admin> licenseidshow10:00:00:05:1e:02:a2:10swd211:admin>5.配置ZONE案例:1) Create Aliases>alicreate “Eng_Host”,“1,0”>alicreate “Eng_Stor”,“1,4; 1,5”>alicreate “Mkt_Host”,“Mktwwn”>alicreate “Mkt_Stor”,“s3wwn; s4wwn; s5wwn”2) Create Zones>zonecreate “Zone_Eng”,“Eng_Host; Eng_Stor”>zonecreate “Zone_Mkt”,“Mkt_Host; Mkt_Stor”3) Create Configuration>cfgcreate “Cfg_EngMkt”,“Zone_Eng; Zone_Mkt”sw4100:admin> cfgshowDefined configuration:cfg: Cfg_EngMktZone_Eng; Zone_Mktzone: Zone_Eng Eng_Host; Eng_Storzone: Zone_Mkt Mkt_Host; Mkt_Storalias: Eng_Stor 1,4; 1,5alias: Eng_Host 1,0alias: Mkt_Stor 21:00:00:20:37:87:49:29; 21:00:00:20:37:87:e5:20; 21:00:00:20:37:87:20:c5alias: Mkt_Host 21:00:00:20:37:87:23:e2Effective configuration:no configuration in effect4) Enable Configuration>cfgenable “Cfg_EngMkt”sw4100:admin> cfgshowDefined configuration:cfg: Cfg_EngMktone_Eng; Zone_Mktzone: Zone_Eng Eng_Host; Eng_Storzone: Zone_Mkt Mkt_Host; Mkt_Storalias: Eng_Stor 1,4; 1,5alias: Eng_Host 1,0alias: Mkt_Stor 21:00:00:20:37:87:49:29; 21:00:00:20:37:87:e5:20; 21:00:00:20:37:87:20:c5alias: Mkt_Host 21:00:00:20:37:87:23:e2Effective configuration:cfg: Cfg_EngMktzone: Zone_Eng 1,0; 1,4; 1,5zone: Zone_Mkt 21:00:00:20:37:87:23:e2; 21:00:00:20:37:87:e5:20; 21:00:00:20:37:87:49:29; 21:00:00:20:37:87:20:c56.查看zone配置文件swd211:admin>swd211:admin> cfgshowDefined configuration:cfg: FC01 OADB_ML6030; SPC_MSA1000; SFDB_EVA4400; SFDB04_MSA1500; SFEVA4400_SMAzone: OADB_ML60301,7; 1,14; 1,15zone: SFDB04_MSA15001,10; 1,6zone: SFDB_EVA44001,3; 1,4; 1,5; 1,7; 1,8; 1,9zone: SFEVA4400_SMA1,8; 1,9; 1,11zone: SPC_MSA10001,0; 1,1; 1,2; 1,7Effective configuration:cfg: FC01zone: OADB_ML60301,71,141,15zone: SFDB04_MSA15001,101,6zone: SFDB_EVA44001,31,41,51,71,81,9zone: SFEVA4400_SMA1,81,91,11zone: SPC_MSA10001,01,11,21,7swd211:admin>swd211:admin>7.查看ZONEswd211:admin> zoneshowDefined configuration:cfg: FC01 OADB_ML6030; SPC_MSA1000; SFDB_EVA4400; SFDB04_MSA1500; SFEVA4400_SMAzone: OADB_ML60301,7; 1,14; 1,15zone: SFDB04_MSA15001,10; 1,6zone: SFDB_EVA44001,3; 1,4; 1,5; 1,7; 1,8; 1,9zone: SFEVA4400_SMA1,8; 1,9; 1,11zone: SPC_MSA10001,0; 1,1; 1,2; 1,7Effective configuration:cfg: FC01zone: OADB_ML60301,71,141,15zone: SFDB04_MSA15001,101,6zone: SFDB_EVA44001,31,41,51,71,81,9zone: SFEVA4400_SMA1,81,91,11zone: SPC_MSA10001,01,11,21,7swd211:admin>8.查看系统日志信息swd211:admin> supportshow日志比较多,建议log出来查看.9.关机swd211:admin> sysshutdown10.设置博科Brocade交换机IP地址博科交换机的默认IP地址是10.77.77.77,在命令行模式下可以通过ipaddrset命令对交换机的IP地址进行设置和修改swd77:admin> ipaddrsetEthernet IP Address [10.77.77.77]: #输入交换机需要设置的IP地址Ethernet Subnetmask [255.255.255.0]: #输入掩码Fibre Channel IP Address [none]:Fibre Channel Subnetmask [none]:Gateway IP Address [none]: # 输入网关DHCP [Off]: #是否开启DHCPswd77:admin>11.博科brocade交换机查看OS版本信息swd77:admin> versionKernel: 2.6.14.2 //linux内核版本Fabric OS: v6.1.0a // 交换机OS版本Made on: Thu Apr 17 21:45:31 2008 // 生产日期Flash: Tue Jan 13 23:33:44 2009BootProm: 4.6.6swd77:admin>12.博科brocade交换机添加license授权信息swd77:admin> licenseadd XXXXXXXX(博科的激活号)13.查看博科brocade交换机license授权信息在命令行模式下使用licenseshow命令可以查看博科交换机的授权情况,使用licenseadd 命令可以添加授权。

MSA2012配置VDISK文档

MSA2012FC快速配置指南MSA2012FC是惠普MSA2000系列产品中的一款光纤接口存储产品,标配支持12块SAS或SATA接口磁盘,最大可扩展到48块,最大存储扩展能力为48T。

编写本文的目的是指导用户对MSA2012FC进行快速配置,以使存储设备在最短时间内上线使用;因此,本文不会包含全部技术细节,欲了解更多内容的用户,可以参考配置界面中的在线帮助以及用户手册。

MSA2000系列的产品可以采用浏览器或命令行(CLI)两种方式进行,本文中介绍采用浏览器的方式,如果希望使用命令行的方式,可以参考用户手册中的相关内容。

1. 建立连接如下图所示,图示中为MSA2012FC的后视图,图中部为两个控制器,每个控制器都有一个以太网口,用于对设备进行管理。

将管理工作站的网口与第一个(上方)控制器的网口相连,并设置管理工作站该网口的IP地址为:10.0.0.4/255.555.255.0注:控制器的默认IP为10.0.0.2(Controller A)及10.0.0.3(Controller B)。

且控制器管理IP默认支持DHCP,建议在配置时,将DHCP改为手工指定。

打开管理工作站上的浏览器,并输入地址http://10.0.0.2,如管理工作站配置正确,则可见如下图所示的管理界面。

使用默认用户名/密码登录(manage/!manage)注:出于安全考虑,建议在正式使用的环境中,更改该密码。

点击Login登入系统,正常返回界面如下图所示点击左侧的Manage按钮,进入管理部分。

点击create a vdisk,选择Manual Virtual Disk Creation(Detail-based),输入Virtual Disk的名字,本例中为Vdisk1,选择Vdisk的Raid级别,点击Continue继续。

请参考下图选择组成Virtual Disk的物理磁盘,在图示中直接选择标记为绿色的未使用磁盘。

SFF-8472MSA数字诊断功能

SFF-8472MSA数字诊断功能数字诊断功能在SFF-8472 MSA中,规范了数字诊断功能及有关SFF-8472的详细内容。

该规范规定,在模块内部的电路板上侦测和数字化参数信号。

然后,提供经过标定的结果或提供数字化的测量结果及标定参量。

这些信息被存贮在标准的内存结构中,以便通过双缆串行接口读取。

SFF-8472保留了原来SFP/GBIC在地址A0h处的地址映射,并在地址A2h处又新增了一个256字节的存贮单元。

这个存贮单元除了提供参数侦测信息外,还定义了报警标志或告警条件,各个管脚的状态镜像,有限的数字控制能力和用户可写的存储单元。

以下是地址空间中保存的部分信息:1)实时测量参数--发射光功率Tx_power,接收光功率Rx_power,温度temp,工作电压Vcc,激光器偏压Laser Bias;2)报警或告警--Tx_faul,LOS测量参数的报警和告警的标志位;3)控制标志位--Tx_disable,Rate_select。

数字诊断功能的应用光纤收发模块中的故障诊断功能为系统提供一种性能监测手段,可以帮助系统管理预测收发模块的寿命、隔离系统故障并在现场安装中验证模块的兼容性。

模块寿命预测这种故障预测可以使网络管理人员在系统性能受到影响之前找到潜在的链路故障。

通过故障预告,系统管理员可以将业务切换到备份链路上或者替换可疑器件,从而在不间断业务的情况下修复系统。

智能SFP提供了一种预测激光器劣化的实时的参数监测手段。

光模块内部的光功率反馈控制单元会将输出功率控制在一个稳定的水平上,但是,随着激光器的老化,激光器的量子效率会降低。

功率的控制是通过提高激光的偏置电流(Tx_Bias)来实现的。

因此,我们可以通过监测激光的偏置电流来预测激光器的寿命。

这种方法可粗略的估计激光器的使用寿命是否接近终了。

因为激光的偏置电流与模块的工作温度及工作电压都有关系,所以在设定偏置电流极限时需要考虑Temp和Vcc的影响。