08_Logic

在PADS LOGIC里画原理图符号中的填充多边形箭头的方法

在PADS LOGIC里画原理图符号中的填充多边形箭头的方法譬如,要画如下图中二极管和三极管的箭头,则方法如下:

1.在LOGIC中点击创建2D线工具

在绘图区右击,弹出菜单中选择多边形和任意角度

依次如图中点A、B、C,在C处双击鼠标后,C点与A点就会自动连接起来。

2.框选刚才画的三角形,在任意位置右击,在弹出菜单中点击特性:

弹出绘图特性窗口里勾选“已填充”,点击确定退出:

此时三角形区域已被填充,在空白区域点击一下鼠标左键,三角形就被取消选中状态,效果如下图:

3.在LOGIC工具栏中点击修改2D线工具:

点击该三角形,则鼠标光标与该点粘连,移动鼠标则图形呈可拉伸状态,依点击的地方端点不同而如下图:

拉伸或压缩各点,达到自己想要的效果:

4.选中该填充图形,右击,在弹出菜单中点击保存到库中:

在弹出窗口中指定保存的库及图形的名字,点确定关闭窗口。

5.在库管理器中加载原图形所在的库,并在筛选条件中选择“线”,键入通配符点应用,

就可以找到刚才做好的图形。

20150715。

苹果iPhone4拆机图解教程

苹果iPhone4拆机图解教程投递:iFixit 发布时间:2011年04月15日点击数: 3878 【字体:小大】苹果iPhone 4智能手机非常受欢迎,那你是否对这款手机内部很好奇呢,下面就让我们来看下国外知名维修网站iFixit 的iPhone 4完全拆解图,让我们能够更全面的了解iPhone 4到底在那些方面做了改变。

本次拆解的主角新版iPhone 4 A1332手机- iPhone 4的设计与过去的铝制和塑料材质的iPhone完全不同- 四周的不锈钢边框不仅起到固定的作用,还有一个重要的功能:iPhone天线和我们观察到的结果一样,先从iPhone 4底部两颗螺丝开始下手然后将iPhone 4后盖向前与主机错开将后盖彻底超级从机身上卸下来卸下后盖后的iPhone 4手机,我们看到电池和主板占据了整个机身的大部分面积投递:iFixit 发布时间:2011年04月15日点击数: 3879 【字体:小大】iPhone 4的电池容量为3.7v 1420mAh卸下机身顶部的屏蔽层卸下主板固定板投递:iFixit 发布时间:2011年04月15日点击数: 3880 【字体:小大】机身震动马达支持720p高清视频拍摄的500万像素模组卸下底部天线和扬声器屏蔽罩卸下iPhone 4的核心——主板主板采用全屏蔽金属罩保护取下金属屏蔽层,我们看到iPhone 4的确采用和iPad一样的1GHz ARM Cortex A8核心的A4处理器采用Skyworks SKY77542双频信号接收芯片、Skyworks SKY77541终端模组和STMicro STM33DH三维加速器等芯片iPhone4采用512MB三星K9PFG08闪存芯片、Cirrus Logic 338S0589音频解码、AKM8975磁场定位芯片、德仪343S0499触摸控制芯片等。

支持802.11n、Bluetooth 2.1 + EDR 和FM接收的Broadcom BCM4329FKUBG 芯片投递:iFixit 发布时间:2011年04月15日点击数: 3880 【字体:小大】Broadcom的GPS单芯片BCM4750IUB8将金属边框和屏幕分离投递:iFixit 发布时间:2011年04月15日点击数: 3880 【字体:小大】取下底部的Home按键取下30pin数据连接口在底部集成双mic阵列,有效降低通话中的外接噪音全部拆卸完毕的iPhone 4至此全部拆机完成,相信通过这篇专业维修网站iFixit的iPhone 4拆机图解教程,不管你是拆机除尘,还是给iPhone4自己换电池或者拆机维修等等,都是大有帮助的。

introduction to logic

Application ReportSLVA700–April 2015Introduction to LogicRyanLandABSTRACTLogic circuits are the building blocks of the digital puters and electronics use 1s and 0s (bits)to transfer data.In the physical world,the 1s and 0s are represented by voltages on a wire,on microscopic traces within an integrated circuit,or on a copper printed circuit board (PCB)puters perform calculations and store data by using combinational and sequential logic circuits.There are many different types of logic circuits that will be described in this report,including logic gates,registers,flip-flops,and more.These devices receive the 1s and 0s as voltages on their inputs,and they perform specific operations on those signals to produce an output.When used in the proper sequence,these devices can manipulate the signals in such a way that can result in anything from a simple adding circuit to a fully-functional supercomputer.TI makes microcontroller units,which contain millions of small logic circuits used to perform complex operations.However,TI also makes the individual building blocks as integrated circuits (ICs)that engineers can use to build smaller-scale digital logic into their own systems.These individual building blocks can also be used for voltage translation or signal conditioning.Contents1Combinational Logic Gates .................................................................................................12Sequential Logic .............................................................................................................33What are 1and 0in the Real World?.....................................................................................54Logic Families . (65)Additional Technical Reading ..............................................................................................7List of Figures1Combinational Logic Gates and their Functions .........................................................................22D-Type Flip-Flop .............................................................................................................33J-K Flip-Flop ..................................................................................................................44Common Switching Input and Output Levels . (5)5Typical V OH /I OH Relationship for Logic Circuits...........................................................................66Typical V OL /I OL Relationship for Logic Circuits ............................................................................6List of Tables1Combinational Logic GatesCombinational logic gates,or simply "logic gates",are the simplest type of logic circuits.They produce an output that is either 1(high)or 0(low)depending in the states of one or more of their inputs.In other words,they perform the basic functions of Boolean algebra.Logic gates are the building blocks for more complicated logic.Figure 1describes each type of logic gate.1SLVA700–April 2015Introduction to LogicSubmit Documentation FeedbackCopyright ©2015,Texas Instruments IncorporatedCombinational Logic Gates binational Logic Gates and their Functions1.Gate name and symbol:The name and standard symbol associated with the gate,including a standardequation used to describe the function it performs.2.Function description:A verbal description of what the gate does.3.Truth table:A table describing what happens to the output at every possible combination of the inputs.In general,inputs are designated"A,B,C,..."while the output is designated with"Y".In truth tables,sometimes there is an"X"instead of0or1listed as an input state.This"X"refers to"Don't Care",and means that particular input has no effect on the output.The OR,AND,NOR,NAND,XOR,and XNOR gates are not limited to2inputs.For example,a3-input AND gate,like the SN74LVC1G11,requires that inputs A,B,and C are all high before output Y will be high.2Introduction to Logic SLVA700–April2015Submit Documentation FeedbackCopyright©2015,Texas Instruments IncorporatedDQQQ Q 0110Q 0DQCLK QD CLK'0101X XQ 0Q 0Q 0'Symbol Truth Table Functional Block DiagramThe D-type flip-flop passes the value of D to the Q output, and the inverse of D to the Q 0 output, when a clock edge occurs. Most devices function on the positive clock edge. Sequential LogicMany TI devices contain multiple independent logic gates.For example,the SN74LVC2G08contains 2separate AND gates,and the SN74LVC32244contains 32buffers.2Sequential LogicOther logic circuits are designed for moving and storage of 1s and 0s.Often,but not always,these devices will have what is known as a "Clock"input.Most commonly,the clock input is a square-shaped waveform that runs at a constant frequency and controls when the device performs a certain action.For example,a device may be designed to output a specific value or move a bit of information when the rising edge of the clock input occurs.2.1Flip-FlopsFlip-flops are sequential logic circuits that can store one or more bits.While their data inputs can change constantly,their outputs will change only when a "clock edge"occurs.A clock edge is defined as a change in state of the "Clock"input pin on the ually,any device function will be triggered by the positive (0to 1)clock edge.There are several types of flip-flops,but the D-type and JK-type are the most common in TI's portfolio.2.1.1D-type Flip-FlopThe D-type flip-flop takes the D input and pushes its value to the Q output on the next clock edge.It also pushes the inverse of D to the Q output.D-type flip-flops can be used for temporary data storage;for example,8D-type flip-flops connected to the same clock line will be able to store one byte of data on each clock edge.The SN74AUC1G79is an example of a TI 1-bit D-type flip-flop.Figure 2.D-Type Flip-Flop3SLVA700–April 2015Introduction to LogicSubmit Documentation FeedbackCopyright ©2015,Texas Instruments IncorporatedJQQQ Q 101J QCLKQ K CLK901010Q 0Q 09Symbol Truth Table Functional Block DiagramThe Q output of the J-K flip-flop output takes the value of J if J and K are different. If J and K are both 0, the output stays the same. If J and K are both 1, the output toggles.K J 001199X Q 0Q 0X XQ 0Q 0X01Q 0Q 0Sequential Logic 2.1.2J-K Flip-FlopThe J-K flip-flop function is slightly more complicated than the D-type flip-flop.However,it can beconverted to a D flip-flop by placing an inverter in front of the K input and tying the input of that inverter to the J input.The SN74LVC112A is an example of a TI dual J-K flip-flop that is triggered on the negative edge of the clock pulse.Figure 3.J-K Flip-Flop2.2Shift RegistersShift registers are chains of flip-flops (usually D-type)that propagate data through the device after each valid clock edge.For example,for an 8-bit shift register,if the data input is a 1and the clock is pulsed 8times,then a 1will be stored in all registers.If the input is 1for 4clock pulses,then 0for another 4clock pulses,then the final 4bits of the shift register will be 1s and the first 4bits of the shift register will be 0.These devices can be used in many different applications,including driving a string of flashing LEDs or scanning a keyboard for key press activity.The SN74LV164A is an example of a TI shift register.2.3CountersCounters are devices that count in binary,starting with 0,1,10,11,100,and so on.Each time a clock edge occurs,the value stored inside increments by 1.There are also counters that start at the maximum value and decrement during each clock cycle.Some even have specific flags for when a count has been finished.Counters are generally used to divide the frequency of a clock signal.The SN74HC393is an example of a dual 4-bit binary counter from TI.4Introduction to LogicSLVA700–April 2015Submit Documentation FeedbackCopyright ©2015,Texas Instruments IncorporatedV CCV CCV CCV CCV CC V CC V OHV IHV TV IL V OL GND5V 4.44 V0.7V CC 0.5V CC 0.3V CC 0.5 V 0 VV IH V IL GNDV OH V IH V T V ILV ILV OL GND5 V2.4 V 2 V1.5 V0.8 V0.4 V 0 VV OH V IH V T V OL GND3.3 V2.4 V 2 V 1.5 V 0.8 V0.4 V 0 V 2.5 V 2.0 V 1.7 V0.7 V0.4 V0 V V OH V IH V IL V OL GND1.8 V V CC-0.45V0.65V CC 0.35V CC 0.45V0 VV OHV IH V IL V OL GND1.2 V 0.65V CC0.35V CC0 V V CC 1.5 V 0.65VCC 0.35V CC0 VV IH V ILGND5V CMOS 5V TTL 3.3V LVTTL 2.5V CMOS 1.8V CMOS 1.5V CMOS 1.2V CMOS What are 1and 0in the Real World?3What are 1and 0in the Real World?So far in this document,we have discussed inputs and outputs of logic circuits as being "high"(1)or "low"(0).But what does this mean exactly?In reality,different families of discrete logic ICs treat "high"and "low"differently.For example,somedevices will register 0.7V at the input as a "high",while on other devices,0.7V is not enough to reach the switching threshold and is still considered a "low".The application report Understanding and Interpreting Standard-Logic Data Sheets has lots of useful information on every specification in logic datasheets,but we will discuss the relevant specifications for input and output voltage levels here.The most common input/output level standards are CMOS and TTL,which can have different voltage levels and are described by the levels in Figure 4.Figure mon Switching Input and Output Levels•V CC :The supply voltage of the device•V OH :The minimum allowed "high"output voltage for a device using that particular logic level standard.For example,a 5-V CMOS device only has a valid output "high"if that output is at least 4.44V.•V IH :The minimum allowed input voltage for an input to be considered "high"•V T :The actual point where the switching occurs from low to high.This is typically not specified in TI datasheets.In reality,there is some variance here,and therefore TI specifies V IH and V IL as maximum and minimum margins for this switching threshold to occur.•VIL:The maximum allowed input voltage for an input to be considered "low"•VOL:The maximum allowed "low"output voltage for a device using that particular logic level standard.For example,a 5-V CMOS device only has a valid output "low"if the output is 0.5V or less.Therefore,when designing a system,it is critical that the designer should choose parts whose outputs are compatible with the receiver's inputs.For example,5-V CMOS outputs are compatible with 5-V TTL inputs because the V IL for 5-V CMOS is 4.44V,which is greater than the 2-V V IH required for a 5-V TTL input to be considered "high".In addition,the 0.5-V V OL for 5-V CMOS is less than the minimum 0.8-V V IL of the 5-V TTL standard.However,a 5-V TTL output should not go into a 5-V CMOS input because the 5-V TTL V OL is allowed to be as low as 2.4V,which is not high enough to guarantee a "high"on the CMOS device;the V IH for 5-V CMOS is 0.7×5V =3.5V.3.1Output Current,V OH ,and V OLMost logic circuits can be thought of as having the same types of output characteristics.That is,for any logic circuit,the output section of the device (regarding its performance with voltage,current,and speed)behaves similarly to a buffer in the same logic family.5SLVA700–April 2015Introduction to LogicSubmit Documentation FeedbackCopyright ©2015,Texas Instruments IncorporatedINOLV OL = 0V RAILV CCIN+²V OHOHV OH = V CCLogic Families TI datasheets usually specify VOHand VOLat different values of VCCand different input/output currentvalues.When a logic circuit outputs a"high",current is flowing out(IOH)of the device into a load.That load can be a resistor,LED,other logic circuit,or any other type of circuit element.However,the more current that flows out of the device,the lower its output voltage will be.This is due to voltage drops within theoutput stage of the device itself.TI datasheets recommend a safe operating current that does not drop theVOHbelow the standard that the device falls under(5-V TTL,1.8-V CMOS,and so forth).At extremelysmall output current values,most logic circuits will output a voltage equal to or very close to VCC.See Figure5.Figure5.Typical VOH/IOHRelationship for Logic CircuitsSimilarly,when the device outputs a"low",current flows into the device.In this case,more current flowinginto the device can increase the VOL,which should ideally be0V at low currents.Figure6.Typical VOL/IOLRelationship for Logic CircuitsMost logic circuits have"push-pull"outputs,meaning that they can provide current and sink current.Some logic circuits have"open-collector"or"open-drain"outputs,which means that they can only sink current and rely on an external pullup resistor to provide the"high"logic level.For an"open-collector"or"open-drain"device,there are no VOHor IOHspecifications.4Logic FamiliesYou may notice different nomenclature in TI part numbers.For example,TI produces many different types of single-bit buffers,including the SN74AUC1G34and SN74LVC1G34.We classify these devices asbeing from two different"families".While they perform the same function,their specifications may bedifferent.For example,the AUC device is characterized to operate at0.8-V VCC,but the LVC device is not.Additionally,the LVC device is characterized to provide up to24mA of output current while retaining its valid CMOS output levels,while the AUC device cannot provide as much current.Family selection isimportant when considering which logic circuit you pick for your design.A list of families and a shortdescription of each can be found in Understanding and Interpreting Standard-Logic Data Sheets.6Introduction to Logic SLVA700–April2015Submit Documentation FeedbackCopyright©2015,Texas Instruments Incorporated Additional Technical Reading 5Additional Technical ReadingThis document is intended to give a brief overview of TI logic and introduce the reader to specific devices and documentation.TI has a wide variety of application reports targeted at different applications andissues engineers may encounter.The following is a brief list of application reports.The full list of logicdocuments is found here.•Understanding and Interpreting Standard-Logic Data Sheets is the most comprehensive overview of datasheet parameters and specifications for TI logic circuits.•Voltage-Level Translation with the LSF Family explains how to use TI's LSF0x0x family of devices to translate between different voltage levels in applications where different logic signaling standards areused.•Power-Up Behavior of Clocked Devices describes dangers of assuming certain output states when using flip-flops and registers-and what to do about it.•Use of the CMOS Unbuffered Inverter in Oscillator Circuits describes a low-cost way to generate a clock signal.•Power-up3-State Circuits in TI Standard Logic Devices describes levels of isolation in TI logic circuits.This is especially useful in systems where not all devices are powered on at the same time.•Implications of Slow or Floating CMOS Inputs describes the unwanted effects of leaving a logic input floating(unconnected)and elaborates on the"Input Transition Rise or Fall Rate"specification required of many devices.•Implications of Slow or Floating CMOS Inputs describes the equations used to calculate the typical power consumption of a logic circuit in your design.•Design Considerations for Logic Products contains a collection of application reports targeted at TI's legacy logic,including proper PCB layout,characterization information,and application-specific design circuits.•How to Select Little Logic describes selection and design guidelines for TI's Little Logic circuits.Little Logic includes TI's smallest-package,1-to-3gate parts.7 SLVA700–April2015Introduction to Logic Submit Documentation FeedbackCopyright©2015,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46,latest issue,and to discontinue any product or service per JESD48,latest issue.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components as meeting ISO/TS16949requirements,mainly for automotive use.In any case of use of non-designated products,TI will not be responsible for any failure to meet ISO/TS16949.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Applications Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2015,Texas Instruments Incorporated。

74ls08

74LS08介绍74LS08 是一种逻辑门芯片,属于 TTL(Transistor-Transistor Logic)系列。

它由四个 2 输入 AND 门组成,是一种四输入 AND 门。

特点74LS08 具有以下特点:•输入端电压范围:0V 到 5V•输出端电压范围:0V 到 5V•输入端的阻抗为10kΩ•输出能力为 8mA•工作温度范围为 -55°C 到 125°C•供电电压为 5V引脚说明74LS08 具有 14 个引脚,它们的功能如下:•Pin 1: 输入 A1•Pin 2: 输入 B1•Pin 3: 输出 Y1•Pin 4: 输入 A2•Pin 5: 输入 B2•Pin 6: 输出 Y2•Pin 7: GND(地)•Pin 8: 输入 A3•Pin 9: 输入 B3•Pin 10: 输出 Y3•Pin 11: 输入 A4•Pin 12: 输入 B4•Pin 13: 输出 Y4•Pin 14: VCC(电源)使用示例以下是一个使用 74LS08 的简单逻辑电路示例,它通过将两个 AND 门的输出连接到第三个 AND 门的输入上,实现了一个 4 个逻辑输入的 AND 逻辑。

+---|B1| +---|B3|| +---|B2| |+-|-+--+ 74LS08| |+-|-+--+ 74LS08| |+---|A1| +---|A3|| +---|B4| |+-|-+--+ 74LS08| |+-|-+--+| |+---|A4| +---|A2|+-|-+–+ 74LS08 | | +—|Y1 | +—|Y3| +—|Y2```•输入 A1、A2、A3、A4 分别连接到逻辑电路的四个逻辑输入•输入 B1、B2、B3、B4 分别连接到逻辑电路的四个逻辑输入•输出 Y1、Y2、Y3、Y4 分别作为逻辑电路的输出以上逻辑电路即为一个 4 个输入的 AND 逻辑电路,只有当所有输入均为高电平(5V)时,输出才会为高电平(5V),否则输出为低电平(0V)。

08模块功能

模拟量输入端子

电压输入

CH0 (输入)

②

V0 I0 COM0

电流输入

CH0 (输入) V0 I0 COM0

⑤

④

⑥

③

②

电流输入时,短接 V 和 I 端子 输入跳线

输入选择

CHO CH1

③

⑦

右边的是 1 通道 左边的是 0 通道

①

模拟输出端子

电压输出

电压输入

电流输入

通过跳线连接 上部分

通过跳线连接 下部分

7-43

第七章 各种功能的应用

4) 接线

(1) 接线注意 确认 AC 混合模块的外部输入信号和模拟量输入/输出不被其它的 AC 电缆感应产生的噪音信号干扰。 接线要考虑外围温度和电流的允许范围,最好线的尺寸比 AWG22 (0.3)粗一些。 如果电线长期靠近高温、辐射和浸在油中,会引起漏电,造成断线或误操作。 在连接外部的 24VDC 电源时,确认正确的极性。 一旦和高压线或感应线连接,就会因感应造成误操作和乱序。

95mA ㎃

重量

240g

180g

备注:

1) 补偿/增益不能修改,它们是固定的 2) 模拟量输入出厂设定为电流输入 3) 最大能使用 3 块扩展模块。

7-40

第七章 各种功能的应用 2) 各部分和功能和名称 各部分和功能的名称的解释

(1) G7F-ADHA

No

说明

① 运行灯 指示 G7F-ADHA 运行状态

4000

4000

0 0mA

20mA

Resolution : 20mA /4000 = 5mA

800

0

-1000 4mA

20mA

Logic IC 选型技巧

Logic 產品的分類及應用料號定義---TI &NXPTISN74AUP 1G 08DCKNXP74AUP 1G 08GWVS1G = Single Gate; 2G = Dual Gate; 3G = Logic FunctionPackage Type Standard Prefix :74= Commercial; 54=MilitaryProduct Families: AHC, AHCT, AUC, AUP , CBT, CBTLV, LVCTriple Gate; 1T=Single Gate Translation; 2T= Dual Gate TranslationTI & NXP 為業界領導廠商,料號命名比較有規則,其它廠商如TOSHIBA, ON, FAIRCHILD 的命名與其不同如何尋找Standard Logic的替代料1.首先確認料件的產品族,找到其它廠商與其對應的產品族;2.確認此料件的邏輯功能(OR Gate/ AND Gate);3.通過主料尾綴確認封裝,找到與其對應的封裝尾綴。

方法一:通過主料號來確認替代料的料號。

主料TI SN74LVC1G08DCK替代料NXP74LVC1G08GWON NL17SZ08DFFairchild NC7SZ08P5TOSHIBA TC7SZ08FU主料TI SN74AHC1G04DBV替代料NXP74AHC1G04GVON MC74VHC1G04DTFairchild NC7S04M5TOSHIBA TC7SH04F如何尋找標準邏輯器件的替代料方法二:通過廠商的官網尋找。

ON, TI, Fairchild, TOSHIBA, NXP這些Logic 廠商的官網上都有競爭對手料件的替代料尋找的功能。

NXPONFairchildTOSHIBATI主要廠商料號前綴比較TI NXP Toshiba Fairchild ON SN74AHC1G74AHC1G TC7SH NC7S MC74VHC1G SN74AHCT1G74AHCT1G TC7SET NC7ST MC74VHC1GT SN74LVC1G74LVC1G TC7SZ NC7SZ NL17SZSN74LVC2G74LVC2G TC7WZ NC7WZ NL27WZSN74LVC3G74LVC3G TC7WZ NC7NZ NL37WZSN74AUC1G74AUC1G TC7SA/PA NC7SV NL17SVSN74AUC2G/TC7PA NC7WV/SN74AUP1G74AUP1G TC7SG NC7SP/各家料號的封裝尾綴對照Package Pins TI FAIRCHILD NXP ON TOSHIBALFBGA 96GKE/ZKE/EC// 114GKF/ZKF/EC/FKDIP8P N/N P 14,16,20N N N N PSOIC8,14,16D M D/T D FN 16,20,24,28DW SC,WM D/T DW FWSOP5,6DBV M5,M6GW DF F 3,5,6DCK P5,P6GW DF FU 4DCY S/ST/SSOP 14,16,20,24,28,30DBMSA,MSCDB/TS SD,DB FS 3KCS//T WTSSOP 8,14,16,20,24,28PW MTC DP/PW DT FS,FT 48,56,64DGG MTD DGG DT FTuQFN6DRY L6GM// WCSP5,6,8,10,20YZP AA/C WBGTape &R X T T1 / T3 / T4ELTI NXP TOSHIBAFamily name VCC(V)TPD(MAX)(ns)Optimized voltage(V)Outputdrive(mA)FamilynameVCC(V)TPD(MAX)(ns)Optimizedvoltage(V)Outputdrive(mA)FamilynameVCC(V)TPD(MAX)(ns)Optimized voltage(V)Outputdrive(mA)AUC0.8 to2.71.3 1.88N/A N/A 0.8 to 0.8 to 0.9主要廠商產品族電性參數比較AUP3.62.4 3.34AUP3.62.23.34LVPto3.63.5 3.34LVC1.65to 5.53.3 3.324LVC1.65 to5.54.5 3.324LCX1.8to5.54.7 3.324AHC 2.0 to5.55.5 5.08AHC 2 to 5.5 5.5 5.08VHC2 to5.55.5 5.08AHCT 4.5 to5.56.9 5.08AHCT4.5 to5.56.2 5.08VHCT4.5 to5.56.2 5.08驱动电流和典型工作电压一般都是一样的 TOSIBA 廠商的產品族電壓範圍較窄一些主要廠商小封裝命名及所遵循的標準JEDECEIAJPin CountPin Pitch (mm)NXP TI Toshiba ON Semi Fairchild Name料號尾綴Name料號尾綴Name料號尾綴Name料號尾綴Name料號尾綴MO-203SC-88A 50.65SC-88A GW SC-70DCK USV FUSOT-353/SC70-5/SC-88ADF SC-70P5SOT-363MO-203SC-8860.65SC-88GW SC-70DCK US6FU/SC70-6/SC-88DF SC-70P6MO-178SC-7460.95SC-74GV SOT-23DBV SM6F TSOP-6DT --MO-178SC-74A50.95SC-74AGVSOT-23DBVSMVFSOT23-5/TSOP-5/SC59-5DTSOT-23M5小封裝命名遵循的標準 NXP 遵循EIAJ 標準;TI & Fairchild 遵循Industry StandardTOSHIBA 遵循自家命名方式ON 封裝命名會整合大小一樣各個標準的封裝名參數比較Vendors NXP TICondition Remark Parameters74AHC1GU04GW SN74AHC1GU04DCKOperatingVoltage2-5.5V2-5.5VOperationtemperature-40-125°C-40-85°C範圍越大越好ESD HBM 2000V HBM 2000V越大越好VIH(min) 2.4V 2.4V Vcc=3.0越小越好VIL(max)0.6V0.6V Vcc=3.0越大越好VOH(min) 2.48V 2.48V(-40-85°C),Vcc=3.0,IOH=-4mA,越大越好2.4V(-20-125°C)VOL(max)0.44V 0.44V(-40-85°C),Vcc=3.0,IOL=4mA,越小越好0.55V(-20-125°C)TPLH1nS MIN1nS MINVcc=3.3,CL=50pF越小越好7.5nS Typical 4.9nS typical12nS MAX12nS MAXTPHL1nS MIN1nS MINVcc=3.3,CL=50pF越小越好7.5nS Typical 4.9nS typical12nS MAX12nS MAX。

PAC8000 8851-LC-MT SafetyNet Logic Controller 说明书

PAC80008851-LC-MT GFK-2569B SafetyNet Logic Controller December 2010The 8851-LC-MT PAC8000 SafetyNet Logic Controller is used for logic control applications in an SIL2 environment. It provides:▪Subset of IEC 61131-3 languages▪Redundancy with bumpless transfer for higher availability▪Dual-redundant high-speed Ethernet connections▪Peer to peer communications between controllers▪On-line configurationProduct DocumentationPAC8000 Safety Manual 3.38000 System Specification Data SheetPAC8000 SafetyNet Data Sheet8000 I/O – 2/2 I/O Modules, General Purpose and 2/2 Applications Including SafetyNet,Instruction Manual - INM81008000 I/O – 2x I/O Modules (2/1 applications) Instruction Manual – INM8200System Specifier’s Guide – SSG8002Product documentation can be downloaded from /supportRelease InformationPAC8000 8851 firmware release 1.26 for PAC8000 8851-LC-MT SafetyNet Controller adds the following features:Update for Modbus read load balancingUpdate for the Register Protection TableFor details, see “Problems Resolved by Release 1.26” on page 2.UpdatesExisting versions of the 8851-LC-MT Controller can be upgraded to version 1.26 using upgrade kit82A1744-MS10-000-A0.Upgrade kits can be downloaded from the Support website, /support.The upgrade kit is published as a SIM for the PAC8000 Workbench programming package. After installing the SIM, firmware upgrades can be done through the Firmware Downloader utility launched from PAC8000 Workbench from PAC8000 SafetyNet controllers.GFK-2569BCompatibilityThis release replaces all previous versions of the 8851-LC-MT Controller firmware.Subject Description PAC8000 WorkbenchVersion RequirementsTo support all features of 01.26, Workbench 8.3.0 SP1 or later is required.Upgrading From PreviousFirmware VersionsVersion 1.x PAC8000 SafetyNet controllers can be upgraded to release 1.26.Downgrade To Previous Firmware Versions Downgrading from release 1.26 to previous releases of 1.x is supported for PAC8000 SafetyNet controllers.Problems Resolved by Release 1.26Subject Configuration DescriptionA Clean Flash command cleared only the Master Duplex A Clean Flash command was processed only by the master controller. This had no impact on operation.Modbus read load balancing on Duplex SafetyNet Duplex In previous releases, large numbers of Modbus reads couldcause the master to abort or the standby to refresh in duplexsystems. This could exhibit in multiple ways:The master would abort and record an “Abort by otherprocessor” log event. The standby would record an “Abortmaster, rendezvous timeout xx ms at <xxxxxx>” event.The master would record multiple Inter AXE Link Eventssuch as “IAL incomplete Rx standby diag [3] size 2 bytes”and “Inter AXE Link failed: retries Tx 0, Rx 1”. Finally a“Force standby, Inter AXE Link failed” event would berecorded and the standby would refresh.The master would record a “Forced other, railbus mismatch”event and the standby would refresh.This issue is corrected in this release.Handling of differences between RTC and CPU date/time Simplex,DuplexIn previous releases under heavy communication load or, rarelyunder normal load, a controller could abort with a log eventindicating “TmrPIT FIT Interrupt rate.” This was due to anincorrect diagnostic check in the controller and has now beencorrected.RTOS did not manage the rollover of time-sliceup-counter correctly Simplex,DuplexIn previous releases a rollover of an internal clock could result ina controller aborting. The event log would indicate, “Abort due toSpvTaskTimeout” for either a UDP or TCP task.The clock rollover occurs at approximately 13 months from thelast reset or power cycle.Strategy download caused Task Timeout Projects containing Safe ISaGRAF strategies and with several thousand tags mapped into the Discrete Control Interface were failing during the Strategy download due to task timeouts. The building of the Register Protection Table (RPT) was changed to better handle these projects.The following error message appeared in the controller event log: “Abort due to SpvTaskTimeout”ISaGRAF debugger sometimes failed to start correctly Simplex,DuplexThe ISaGRAF debugger did not reliably connect to the controller.In these cases, no log message was generated in the controllerlog, and the ISaGRAF debugger indicated a failure or aconnection was not obtained.GFK-2569B Restrictions and Open IssuesSubject Configuration Description8811 Module driver Simplex, Duplex For channels configured to output single pulses, multiple outputpulses can be seen if the pulse length is set below the time ofthe execution cycle of the controller.RECOVERY: None.The pulse duration should normally be substantially longer thanthe execution cycle. A technical note that recommendsappropriate values is available on the Support website,/support.SpvTaskTimeout during sporadic Peer to Peer communications Duplex The SpvTask Timeout may occur on a duplex controller withpeer-to-peer communications starting and stopping, and whilecreating ISaGRAF TCP socket after firmware download andclean flash.The controller event log may contain errors such as thefollowing:00349 0000464.329 00 B ! !Abort due to SpvTaskTimeouttask !EXEC 0x27RECOVERY: Controller returns to healthy master after thereset due to the abort.Debugger locking up Simplex, Duplex The ISaGRAF debugger locks up under certain conditions. Toavoid this problem, only use the ISaGRAF debugger in Configmode. Stop the ISaGRAF debugger when going to Safe modeand do not attempt a connection while the controller is in safemode.RECOVERY: Power cycle the controller(s).Controller aborts during Register Mapping Table download Simplex, Duplex While downloading the Register Mapping Table or the Reg Init Values, the controller aborts with message:"Abort due to RtosAlloc NU_Allocate_MemoryNU_INVALID_MEMORY"RECOVERY: Controller successfully resets after the abort andreturns to healthy master or request standby depending on itspartner controller's state.Downloaded rejected with a CSC_CORRUPT error on peer to peer table Simplex, Duplex Strategy download may be abandoned while downloading the Peer-to-Peer Table with both master and standby offline.PAC8000 Workbench logs the following error in the MicrosoftEvent Log: "Download Failure: Request to AXE timed out -Download failed for the following reason: Load RIT: CRC doesnot match". The controller log also contains the message"Download Peer to Peer Table CSC_CORRUPT."RECOVERY: Re-download the strategyGFK-2569BSubject Configuration DescriptionInvalid data when using packed discrete points in Modbus master Simplex, Duplex When the PAC8000 controller is used as a Modbus Master and an option other than “No Packing” is selected from theWorkBench, the controller could return erroneous Modbusvalues to the slave. The issue occurs only for discrete Modbusregisters.This issue occurs on the standard controller withfirmware v2.x, RTU with firmware v2.11, and safety controllerwith firmware 1.1x and above.RECOVERY: To avoid this issue select the “No Packing”option on the “Map Remote Device Points” dialog in theWorkBench. This would ensure that the issue is notencountered.For complete information on this issue refer to Field ServiceBulletin 100929.Insertion of standby controller causes master abort Duplex On rare occasions, inserting an unpowered standby controllerinto a carrier with an operating master may cause the master toabort and go into failsafe. If this occurs, the master will recordan "Abort due to SpvTaskTimeout task" in the event log.RECOVERY: If this occurs, power cycle the controller to causethe master to exit failsafe and resume normal operation. Themaster can also be commanded to exit failsafe via softwaretools such as the IO or Network Configurator. After the masteris healthy, power can be applied to the standby controller.Removing power to one controller may cause the second controller to abort Duplex On rare occasions, in duplex systems removing power to either the master or standby controller may cause the master to abortand go into failsafe. If this occurs, the controller in failsafe willrecord an “Abort due to PiReadStateFlags Unstable” in theevent log.This issue occurs on units with a date code of 11/3/10 orlater.RECOVERY: If this occurs, power cycle the controller to causethe master to exit failsafe and resume normal operation. Themaster can also be commanded to exit failsafe via softwaretools such as the IO or Network Configurator. .GFK-2569BOperational NotesSubject Configuration DescriptionAbort after strategy download Simplex, Duplex Abort due to SpvTaskTimeout task may occur after strategydownload of a project with a long execution cycle time.The controller event log may contain errors such as thefollowing:01835 0000507.070 00 B !08:14:53~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~01836 0000507.070 00 B ! !Abort due to SpvTaskTimeouttask !EXEC 0x2701837 0000507.070 00 B !08:14:53~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~01838 0000507.070 00 B ! Exec: 1st control package HISRSYSTEM H01839 0000507.070 00 B ! Active Task !EXECRECOVERY: Download a new strategy with shorter executioncycle time.GFK-2569BCompliance InformationFor detailed installation and operating procedures, refer to the user manual for the module.Hazardous Locations• Factory Mutual, Class 1, Div 2, Groups A, B, C, D hazardous locations with Temperature Code T4 Refer to Control Drawings SCI-701 and SCI-1004 for the PAC8000 8811-IO-DC module.Refer to Control Drawings SCI-701 and SCI-956 for the PAC8000 8851 Controller • ATEX II 3 G, Ex nA nL IIC T4 for the PAC8000 8811-IO-DC moduleATEX II 3 G, Ex nL IIC T4 for the PAC8000 8851 Controller• CSA, Class 1, Div 2, Groups A, B, C, D hazardous locations with Temperature Code T4 Refer to Control Drawings SCI-702 and SCI-1005 for the PAC8000 8811-IO-DC module.Refer to Control Drawings SCI-702 and SCI-957 for the PAC8000 8851 ControllerFunctional Safety• TUV Rheinland Safety Related Programmable Electronic System – suitable for safety related applications up to SIL 2.Applicable Standards• FM Approvals: FM 3600, FM 3611, FM 3810• ATEX Approvals: EN 60079-15:2005• CSA Approvals: C22.2 No. 0-M91, C22.2 No. 142-M1987, C22.2 No. 213-M1987• TUV Rheinland: IEC 61508, IEC 61511, EN 50156-1, NFPA 85, EN 61131-2, EN 61010-1,IEC 61326-1, EN 54-2, NFPA 72。

PROTEUS元件库中英对照

仿真软件里的AD0809有问题,用0808代替定时/计数器的使用方法:CLK:计数和测频状态时,数字波的输入端。

(counter enable) CE:计数使能端;通过属性设置高还是低有效。

无效暂停计数RST:复位端(RESET),可设上升沿(Low-High)或者下降沿(High-Low)有效。

4种工作方式:通过属性Operating Mode来选择。

Default :缺省方式,计数器方式。

Time(secs):100S定时方式,由CE和RST控制暂停和重新开始。

Time(hms):10小时定时方式,同上。

Frequency:测频方式,CE和RST有效时,显示CLK端数字波频率Count:计数方式。

常用元件列表:POT-HG可调电位器7SEG-MPX8-CC-BLUE 8位数码管COMPIM串口SW-开关7SEG-BCD含译码驱动的数显Speaker扬声器2N5771和2N5772,15V对管300MA RES,CAP,BUTTON按钮开关KEYPAD-PHONE 3*4电话键盘KEYPAD-SMALLCALC4*4计算器键盘KEYPAD-CALCULATOR4*6计算器键盘PG160128A128*128液晶++++++++元件库详细分类1.analog ics模拟集成器件8个子类:amplifier放大器comparators比较器display drivers显示驱动器filters滤波器miscellaneous混杂器件regulators三端稳压器timers 555定时器voltage references参考电压2,capacitors CAP电容,23个分类别animated可显示充放电电荷电容audio grade axial音响专用电容axial lead polypropene径向轴引线聚丙烯电容axial lead polystyrene径向轴引线聚苯乙烯电容ceramic disc陶瓷圆片电容decoupling disc解耦圆片电容high temp radial高温径向电容high temp axial electrolytic高温径向电解电容metallised polyester film金属聚酯膜电容metallised polypropene金属聚丙烯电容metallised polypropene film金属聚丙烯膜电容miniture electrolytic微型电解电容multilayer metallised polyester film多层金属聚酯膜电容mylar film聚酯薄膜电容nickel barrier镍栅电容non polarised无极性电容polyester layer聚酯层电容radial electrolytic径向电解电容resin dipped树脂蚀刻电容tantalum bead钽珠电容variable可变电容vx a xial electrolytic VX轴电解电容3,CMOS 4000 series 4000系列数字电路adders加法器buffers & drivers缓冲和驱动器comparators比较器counters计数器decoders译码器encoders编码器flip-flops & latches触发器和锁存器frequency dividers & tiner分频和定时器gates & inverters门电路和反相器memory存储器misc.logic混杂逻辑电路mutiplexers数据选择器multivibrators多谐振荡器phase-locked loops(PLL)锁相环registers寄存器signal switcher信号开关4,connectors接头;8个分类:audio音频接头D-type D型接头DIL双排插座header blocks插头miscellaneous各种接头PCB transfer PCB传输接头SIL单盘插座ribbon cable蛇皮电缆terminal blocks接线端子台5,data converters数据转换器:4个分类:A/D converters模数转换器D/A converters数模转换器sample & hold采样保持器temperature sensors温度传感器6,debugging tools调试工具数据:3个类别:breakpoint triggers断点触发器logic probes逻辑输出探针logic timuli逻辑状态输入7,diodes二极管;8个分类:bridge rectifiers整流桥generic普通二极管rectifiers整流二极管schottky肖特基二极管switching开关二极管tunnel隧道二极管varicap稳压二极管8,inductors电感:3个类别:generic普通电感SMT inductors表面安装技术电感transformers变压器9,laplace primitives拉普拉斯模型:7个类别:1st order一阶模型2nd order二阶模型controllers控制器non-linear非线性模型operators算子poles/zeros极点/零点symbols符号10,memory ICs存储器芯片:7个分类:dynamic RAM动态数据存储器EEPROM电可擦出程序存储器EPROM可擦出程序存储器I2C memories I2C总线存储器memory cards存储卡SPI Memories SPI总线存储器static RAM静态数据存储器11,microprocessor ICs微处理器:13个分类:12,modelling primitivvves建模源:9个分类:13,operational amplifiers运算放大器:7个分类:dual双运放ideal理想运放macromodel大量使用的运放octal8运放quad4运放single单运放triple三运放14,optoelectronics光电器件:11个分类:7-segment displays 7段显示alphanumeric LCDs液晶数码显示bargraph displays条形显示dot matrix displays点阵显示graphical LCDs液晶图形显示lamps灯LCD controllers液晶控制器LCD controllers液晶面板显示LEDs发光二极管optocouplers光电耦合serial LCDs串行液晶显示15,resistors电阻:11个分类:0.6w metal film0.6w金属膜电阻10 watt wirewound10w绕线电阻2w metal film2w金属膜电阻3 watt wirewound 3w绕线电阻7 watt wirewound 7w绕线电阻generix普通电阻high voltage高压电阻NTC负温度系数热敏电阻resistor packs排阻variable滑动变阻器varisitors可变电阻参考试验中采用的可变电阻是:POT-HG16,simulator primitives仿真源:3个类别:flip-flops触发器gates门电路sources电源17,switches and relays开关和继电器:4个类别:key pads键盘relays普通继电器relays(specific)专用继电器switches开关18,switching devices开关器件:4个分类:DIACs两端交流开关generic普通开关元件SCRs可控硅TRIACs三端双向可控硅19,真空管:20,传感器:2个分类:pressure压力传感器temperature温度传感器21,晶体管:8个分类:bipolar双极型晶体管generic普通晶体管(错误)IGBT绝缘栅双极晶体管JFET结型场效应管MOSFET金属氧化物场效应管RF power LDMOS射频功率LDMOS管RF power VDMOS射频功率VDMOS管unijunction单结晶体管Electromechanical电机MOTOR AC交流电机MOTOR SERVO伺服电机双相步进电机motor-bistepper(Bipolar Stepper Motor),四相步进电机motor-stepper(unipolar stepper motor)驱动电路,用ULN2003可以,proteus中推荐的L298和L6201(电子元件-步进电机中有L298资料)+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++ ++++++++++步进电机,可以用MTD2003,UN2916等专用芯片Proteus中图形液晶模块驱动芯片一览表LM3228 LM3229 LM3267 LM3283LM3287 LM4228 LM4265 LM4267LM4283 LM4287 PG12864F PG24064FPG128128A PG160128AAGM1232G EW12A03GLY HDM32GS12-B HDM32GS12Y-B HDG12864F-1 HDS12864F-3 HDG12864L-4 HDG12864L-6 NOKIA7110 TG126410GFSB TG13650FEYAMPIRE128x64 LGM12641BS1RPROTEUS原理图元器件库详细说明Device.lib单双向可控硅、包括电阻、电容、二极管、三极管和PCB的连接器符号、ACTIVE.LIB包括虚拟仪器和有源器件、拨动开关、键盘、可调电位器和开关、DIODE.LIB包括二极管和整流桥、稳压管、变容二极管、大功率二极管、高速二极管、可控硅、DISPLAY.LIB包括LCD、LED、LED阵列BIPOLAR.LIB包括三极管FET.LIB包括场效应管ASIMMDLS.LIB包括模拟元器件AS稳压二极管、全桥、74系列、及其他。

logic英语作文

logic英语作文英文回答:The term "logic" can be interpreted in various contexts, ranging from philosophy to computer science, eachconferring unique meanings and applications. In the realmof philosophy, logic encompasses the study of reasoning, argumentation, and the systematization of thought processes. It delves into the principles of correct reasoning, fallacies, and the construction of valid arguments. Logic forms the foundation for critical thinking, enabling individuals to analyze statements, identify flaws, and form sound conclusions.In computer science, logic serves as a formal language used in programming and artificial intelligence. Itprovides a framework for representing knowledge, automating reasoning processes, and developing intelligent systems. Logic-based programming languages, such as Prolog, leverage logical rules to solve complex problems and facilitateknowledge representation.中文回答:逻辑一词可以从不同的背景来解读,从哲学到计算机科学,每个背景都赋予其独特的含义和应用。

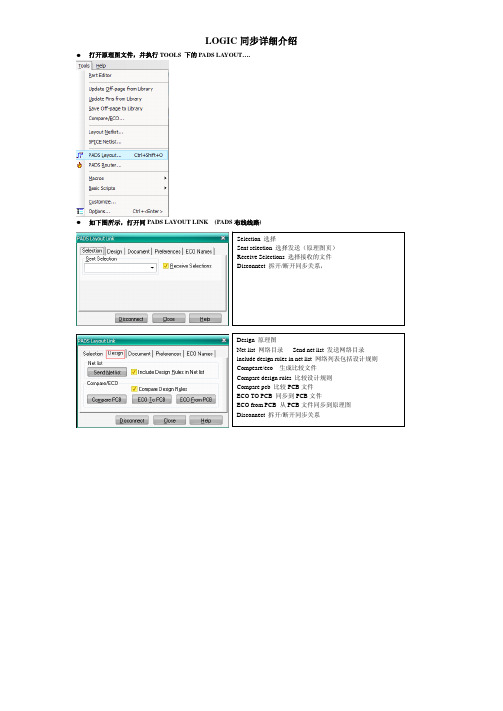

LOGIC同步详细操作

Document 文件 打开要同步/比较的 PCB 文件 NEW 新建 PCB 文件 OPEN 打开 PCB 文件 Disconnect 拆开/断开同步关系

Preferences 优先选择 Lgnore unused pin net 忽略未使用的管脚网络 Name 忽略的网络名称 Lnclude attributes 包括的属性 Parts 元件 Nets 网络 Compare PCB decal assignments 比较 PCB 封装分配

ቤተ መጻሕፍቲ ባይዱ

如下图所示打开同padslayoutlinkpads布线线路selection选择sentselection选择发送原理图页receiveselections选择接收的文件disconnect拆开断开同步关系design原理图netlist网络目录sendnetlist发送网络目录lncludedesignrulesnetlist网络列表包括设计规则compeareeco生成比较文件comparedesignrules比较设计规则comparepcb比较pcb文件ecopcb同步到pcb文件ecofrompcb从pcb文件同步到原理图disconnect拆开断开同步关系document文件打开要同步比较的pcb文件new新建pcb文件open打开pcb文件disconnect拆开断开同步关系preferences优先选择lgnoreunusedpinnet忽略未使用的管脚网络name忽略的网络名称lncludeattributes包括的属性parts元件nets网络comparepcbdecalassignments比较pcb封装分配econameseco名称namecomparisonoptions名称比较选项comparenamesrenamenetsnecessary比较名称和命名网和部分必需的comparenamespreferadddeletepartsrenaming比较名称但优先添加重命名删除部分comparetopologynotnames

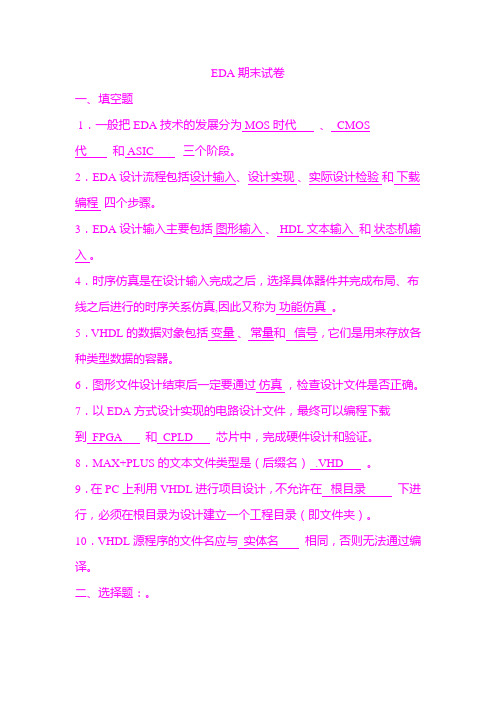

EDA期末试卷及答案

EDA期末试卷一、填空题1.一般把EDA技术的发展分为 MOS时代、 CMOS代和 ASIC 三个阶段。

2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。

3.EDA设计输入主要包括图形输入、 HDL文本输入和状态机输入。

4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。

5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。

6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。

7.以EDA方式设计实现的电路设计文件,最终可以编程下载到 FPGA 和 CPLD 芯片中,完成硬件设计和验证。

8.MAX+PLUS的文本文件类型是(后缀名) .VHD 。

9.在PC上利用VHDL进行项目设计,不允许在根目录下进行,必须在根目录为设计建立一个工程目录(即文件夹)。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。

二、选择题:。

11.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C )A.仿真器B.综合器C.适配器D.下载器12.在执行MAX+PLUSⅡ的(D )命令,可以精确分析设计电路输入与输出波形间的延时量。

A .Create default symbol B. SimulatorC. CompilerD.Timing Analyzer13.VHDL常用的库是(A )A. IEEEB.STDC. WORKD. PACKAGE 14.下面既是并行语句又是串行语句的是( C )A.变量赋值B.信号赋值C.PROCESS语句D.WHEN…ELSE 语句15.在VHDL中,用语句(D )表示clock的下降沿。

A. clock’EVENTB. clock’EVENT AND clock=’1’C. clock=’0’D. clock’EVENT AND clock=’0’16. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL 等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__________。

std_logic_vector用法

std_logic_vector用法==================std_logic_vector 是 Verilog 语言中的一个数据类型,用于表示二进制数据。

它通常用于存储和传输二进制数据,是数字电路设计中的常用数据类型。

一、基本用法------std_logic_vector 类型的数据由一个或多个 std_logic 类型的数据组成,其大小由一个二进制数表示。

它可以表示任意长度的二进制数,从 1 位到 64 位。

在 Verilog 代码中,可以使用 std_logic_vector 类型的变量来存储二进制数据,并进行各种算术运算和逻辑运算。

例如,可以使用“std_logic_vector(bit_vector)” 函数将一个 std_logic 类型的变量转换为 std_logic_vector 类型,并进行位级别的操作。

二、位操作-----std_logic_vector 支持各种位操作,如与、或、非、异或等。

这些操作可以对 std_logic_vector 类型的变量进行位级别的操作,从而实现更精细的控制和优化。

例如,可以使用“&” 运算符进行与运算,将两个std_logic_vector 类型的变量进行逐位比较,只有匹配的位都为 1 时,结果为 1;使用“|” 运算符进行或运算,将两个std_logic_vector 类型的变量进行逐位组合,只要有一个匹配的位为1 时,结果为 1;使用“~” 运算符进行非运算,将一个std_logic_vector 类型的变量逐位取反。

三、存储和传输-------std_logic_vector 类型的数据可以存储在内存中,也可以在数字电路中进行传输。

在 Verilog 代码中,可以使用 assign 语句将std_logic_vector 类型的变量赋值给其他变量,或者将其输出到端口中。

四、注意事项------在使用 std_logic_vector 时,需要注意其大小和数据类型。

OpenCNC_PLC发展工具操作手册V2.5(新代系统plc)

4 PLC 元件說明..................................................................................................37

5 M Code / S Code / T Code ................................................................................38

5.1

M code / S code / T code 功能目的...................................................38

5.2

M Code / S Code / T Code 動作流程 ................................................39

3.1

常開接點(Normal Open Contact).................................................12

3.2

常閉接點(Normal Close Contact) ................................................12

3.21 刀庫旋轉指令(Rotate).................................................................31

3.22 程式跳躍指令(Jump)...................................................................32

3.3

連結線(Connector) ......................................................................12

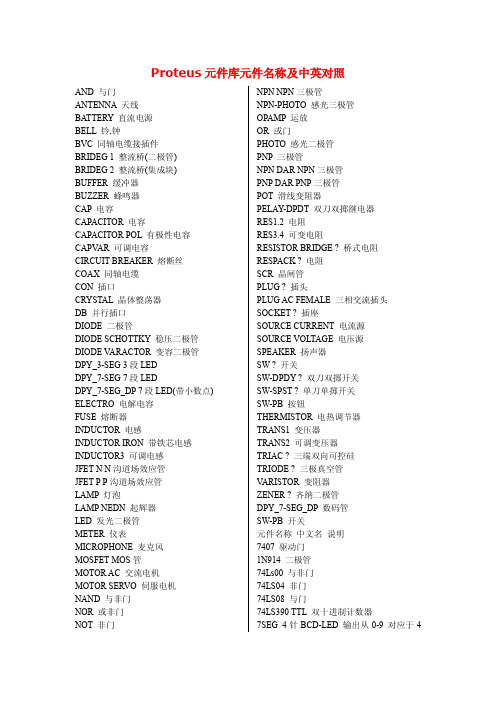

proteus元件库对照表

Proteus元件库元件名称及中英对照AND 与门ANTENNA 天线BA TTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管) BRIDEG 2 整流桥(集成块) BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPV AR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE ? 三极真空管V ARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG转换电路AlterNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BA TTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振Compim 串口D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

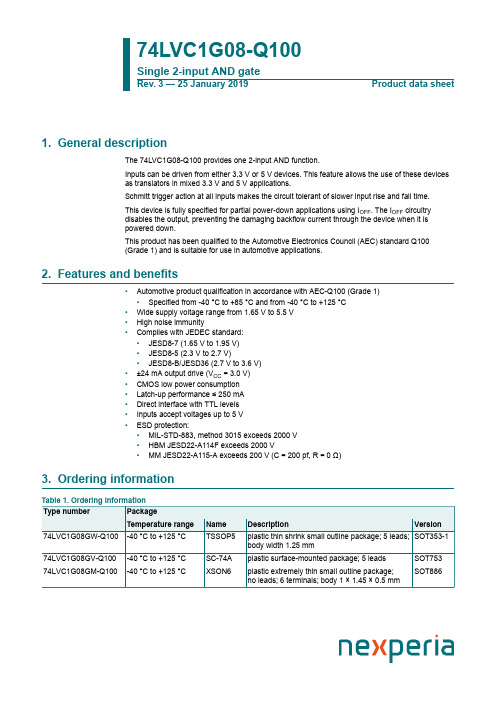

74LVC1G08-Q100 2-输入AND门单片IC数据手册说明书

74LVC1G08-Q100Single 2-input AND gateRev. 3 — 25 January 2019Product data sheet1. General descriptionThe 74LVC1G08-Q100 provides one 2-input AND function.Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of these devicesas translators in mixed 3.3 V and 5 V applications.Schmitt trigger action at all inputs makes the circuit tolerant of slower input rise and fall time.This device is fully specified for partial power-down applications using I OFF. The I OFF circuitrydisables the output, preventing the damaging backflow current through the device when it ispowered down.This product has been qualified to the Automotive Electronics Council (AEC) standard Q100(Grade 1) and is suitable for use in automotive applications.2. Features and benefits•Automotive product qualification in accordance with AEC-Q100 (Grade 1)•Specified from -40 °C to +85 °C and from -40 °C to +125 °C•Wide supply voltage range from 1.65 V to 5.5 V•High noise immunity•Complies with JEDEC standard:•JESD8-7 (1.65 V to 1.95 V)•JESD8-5 (2.3 V to 2.7 V)•JESD8-B/JESD36 (2.7 V to 3.6 V)•±24 mA output drive (V CC = 3.0 V)•CMOS low power consumption•Latch-up performance ≤ 250 mA•Direct interface with TTL levels•Inputs accept voltages up to 5 V•ESD protection:•MIL-STD-883, method 3015 exceeds 2000 V•HBM JESD22-A114F exceeds 2000 V•MM JESD22-A115-A exceeds 200 V (C = 200 pf, R = 0 Ω)3. Ordering information4. Marking[1]The pin 1 indicator is located on the lower left corner of the device, below the marking code.5. Functional diagrammna113B AY214Fig. 1.Logic symbol mna11424&1Fig. 2.IEC logic symbol mna221ABYFig. 3.Logic diagram6. Pinning information6.1. Pinning74LVC1G08B V CCA GNDY001aab63812354Fig. 4.Pin configuration SOT353-1 (TSSOP5)and SOT753 (SC-74A)74LVC1G08A001aab639BGND n.c.V CCYT ransparent top view231546Fig. 5.Pin configuration SOT886 (XSON6)6.2. Pin description7. Functional description[1]H = HIGH voltage level; L = LOW voltage level8. Limiting valuesTable 5. Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]The input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]For TSSOP5 and SC-74A packages: above 87.5 °C the value of P tot derates linearly with 4.0 mW/K.For XSON6 package: above 118 °C the value of P tot derates linearly with 7.8 mW/K.9. Recommended operating conditions10. Static characteristicsTable 7. Static characteristicsAt recommended operating conditions. Voltages are referenced to GND (ground = 0 V).[1]All typical values are measured at V CC = 3.3 V and T amb = 25 °C.11. Dynamic characteristicsTable 8. Dynamic characteristicsVoltages are referenced to GND (ground = 0 V); for test circuit see Fig. 7.[1]Typical values are measured at T amb = 25 °C and V CC = 1.8 V, 2.5 V, 2.7 V, 3.3 V and 5.0 V respectively.[2]t pd is the same as t PLZ and t PZL.[3]C PD is used to determine the dynamic power dissipation (P D in μW).P D = C PD × V CC2 × f i × N + ∑(C L × V CC2 × f o) where:f i = input frequency in MHz;f o = output frequency in MHz;C L = output load capacitance in pF;V CC = supply voltage in V;N = number of inputs switching;∑(C L × V CC2 × f o) = sum of outputs.11.1. Waveforms and test circuit12. Package outlineTSSOP5: plastic thin shrink small outline package; 5 leads; body width 1.25 mm SOT353-1Fig. 8.Package outline SOT353-1 (TSSOP5)Plastic surface-mounted package; 5 leads SOT753Fig. 9.Package outline SOT753 (SC-74A)Fig. 10.Package outline SOT886 (XSON6)13. Abbreviations14. Revision history15. Legal informationData sheet status[1]Please consult the most recently issued document before initiating orcompleting a design.[2]The term 'short data sheet' is explained in section "Definitions".[3]The product status of device(s) described in this document may havechanged since this document was published and may differ in case ofmultiple devices. The latest product status information is available onthe internet at https://.DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information. Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.DisclaimersLimited warranty and liability — Information in this document is believedto be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracyor completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removalor replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to make changesto information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use in automotive applications — This Nexperia product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted tobe suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.Quick reference data — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding. Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitable and fit for the customer’s applications and products planned, as well asfor the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer’s third party customer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above thosegiven in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — Nexperia products aresold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of Nexperia products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.Translations — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.Contents1. General description (1)2. Features and benefits (1)3. Ordering information (1)4. Marking (2)5. Functional diagram (2)6. Pinning information (2)6.1. Pinning (2)6.2. Pin description (2)7. Functional description (3)8. Limiting values (3)9. Recommended operating conditions (3)10. Static characteristics (4)11. Dynamic characteristics (5)11.1. Waveforms and test circuit (5)12. Package outline (7)13. Abbreviations (10)14. Revision history (10)15. Legal information (11)© Nexperia B.V. 2019. All rights reservedFor more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:*************************** Date of release: 25 January 2019Mouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:N experia:74LVC1G08GV-Q100,174LVC1G08GW-Q100,174LVC1G08GM-Q100X。

08.First order logic

15

A common mistake to avoid

Typically, is the main connective with 在需要用全称量词书写一般规则的时候, 的真值 表项是一个理想的选择

Common mistake: using as the main connective with :

First-Order Logic

Chapter 8

Last week

Logical agents apply inference to a knowledge base to derive new information and make decisions

Basic concepts of logic: — syntax(语法): formal structure of sentences — semantics(语义): truth of sentences wrt models — entailment(蕴涵): necessary truth of one sentence given another — inference(推理): deriving sentences from other sentences — soundness(可靠性): derivations produce only entailed sentences — completeness(完备性): derivations can produce all entailed sentences Forward, backward chaining are linear-time, complete for Horn clauses Resolution is complete for propositional logic

水文代码包说明书

Package‘HydroCode’March26,2023Type PackageTitle Hydrological CodesDate2023-03-26Version1.0.3Description Pfafstetter Hydrological Codesas cited in Verdin and Verdin(1999)<doi:10.1016/S0022-1694(99)00011-6>are decoded for upstream or downstream queries.Depends R(>=3.5.0)License GPL-3Encoding UTF-8LazyData trueImports parallel,spRoxygenNote7.2.2NeedsCompilation noAuthor Thorsten Pohlert[aut,cre](<https:///0000-0003-3855-3025>)Maintainer Thorsten Pohlert<***********************>Repository CRANDate/Publication2023-03-2621:50:11UTCR topics documented:is.odd (2)is.upstream (2)rhineCCM2 (5)rhineHYBASlev08 (6)Index81is.odd Number TypeDescriptionis.odd tests whether a number is odd.is.even returns the oppositeUsageis.odd(x)is.even(x)Argumentsx numeric object to be testedValuea vector of type logicalNoteif x contains NA the function returns NAExamplesx<-seq(1,9,2)is.odd(x)y<-seq(2,8,2)is.even(y)#NA valuesx[1]<-NAis.odd(x)is.upstream Comparison of Pfafstetter Coded BasinsDescriptionOne point(river segment or subbasin)with Pfafstetter code a on the water system can be queried for beeing upstream or downstream as compared to one or many points b on the water system.Usageis.upstream(a,b)a%up%bis.downstream(a,b)a%down%bArgumentsa numeric,Pfafstetter coded pointb numeric,one or more Pfaffstetter coded pointsDetailsFor the scientific background of the Pfafstetter coding system see the literature reference.The following option(s)can be set via,e.g.options("hydrocode.X"=XX):hydrocode.parallel:logical.Defaults to FALSE.The runtime may or may not decrease for very large vectors(length>50000)on multi-threading processors.hydrocode.alloddorzero:logical.Defaults to FALSE.This refers to the original Pfafstetter cod-ing system and tests,whether all n numbers are odd,[13579]{n}.Hydrocodes that contain the digit0are interpreted as closed catchments(endorheic basins).This setting works,e.g.with the Pfafstetter coded table riversegments of CCM River and Catchment Database,v2.1 (European Commission-JRC,2007;V ogt et al.,2007).For decoding the Pfafstetter coded tables of the HydroBASIN,v1c dataset(Lehner and Grill,2013),this option should be set to options("hydrocode.alloddorzero"=TRUE).This tests for all n numbers are odd or zero, [013579]{n}.Valuea vector of type logicalReferencesA.L.de Jager and J.V.V ogt,2010,Development and Demonstration of a Structured Hydrologi-cal Feature Coding System for Europe,Hydrological Sciences Journal,55,661–75,doi:10.1080/ 02626667.2010.490786.B.Lehner and G.Grill,2013,Global river hydrography and network routing:baseline data andnew approaches to study the world’s large river systems,Hydrological Processes,27,2171–2186, doi:10.1002/hyp.9740.K.L.Verdin and J.P.Verdin,1999,A topological system for delineation and codification of the Earth’s river basins,Journal of Hydrology,218,1–12,doi:10.1016/S0*******(99)000116.J.V ogt,P.Soille,A.de Jager,E.Rimaviˇc i¯u t˙e,W.Mehl,S.Foisneau,K.Bódis,et al.,2007,A Pan-European River and Catchment Database,Publications Office:Luxembourg,doi:10.2788/35907.Wikipedia contributors,2019,Pfafstetter Coding System,In Wikipedia,The Free Encyclopedia,Re-trieved13:23,November9,2019,https:///w/index.php?title=Pfafstetter_ Coding_System&oldid=907987995See AlsooptionsExamples##example from Wikipedia##8835is upstream of segments8833and8811,##but not segments8832,8821or9135dwn<-c(8833,8811,8832,8821,9135)is.upstream(8835,dwn)##works with operator8835%up%dwn##this will produce errors##Not run:is.upstream("12h",123)is.upstream(12.4,123)##End(Not run)##example from Verdin and Verdin,1999,p.10b<-c(8883,8881,8879,8877,8875,8873,8871,8859,8857,8855,8853,8851,8839,8837,8835,8833,8831,8819,8817,8815,8813,8811,8886,8887,8888,8889)a<-8885a%down%b##example from Vogt et al.(2007),##pollution source at464.##Which subcatchments are##affected?Mixed levels of subdivisions.a<-464b<-c(465,466,467,47,48,49,463,461,41,43,45,452,454)a%up%b##same hydro codes return TRUE per default112%up%112112%down%112rhineCCM25 rhineCCM2CCM2River and Catchment of the Rhine Catchment,Rivers onlyDescriptionThis spatial dataset is a subset of the data layer RIVERSEGMENTS of the tile WGS84_W2003from the CCM River and Catchment Database v2.1(V ogt et al.2007).The original data format was PGeo (ESRI Personal GeoDatabase).The subset consists of rivers within the Rhine basin,i.e.WSO_ID= 291110.In order to save disk space,thefields of the attribute table were shortened.FormatAn Object of class SpatialLinesDataFrame with30343features.The attribute table comprises2fields:WSO1_ID int,unique river segment identifierPFAFSTETTER num,Pfafstetter code according to CCM2The PROJ.4string is+proj=longlat+datum=WGS84+no_defs+ellps=WGS84+towgs84=0,0,0. SourceCCM River and Catchment Database(C)European Commission-JRC,2007.ReferencesJ.V ogt,P.Soille,A.de Jager,E.Rimaviˇc i¯u t˙e,W.Mehl,S.Foisneau,K.Bódis,et al.,2007,A Pan-European River and Catchment Database,Publications Office:Luxembourg,doi:10.2788/35907. Examples##Not run:##get the flowpath from a head catchment to##the sea##Be patient,this might take a while.system.time(fps<-973842223%up%rhineCCM2$PFAFSTETTER)flowpath<-subset(rhineCCM2,subset=fps)sp::plot(flowpath)##does parallel threats increase the speed##and provide the same results?op.old<-options()options("hydrocode.parallel"=TRUE)system.time(fpp<-973842223%up%rhineCCM2$PFAFSTETTER)all.equal(fps,fpp)##reset previous settingsoptions(op.old)##End(Not run)rhineHYBASlev08HydroBASINS Level08Data of the Rhine CatchmentDescriptionThis spatial dataset is a subset of the data layer hybas_eu_lev08_v1c from the HydroBASINS v1.c database(Lehner and Grill,2013).The original data format was SHP(ESRI Shape File).The subset consists of subbasins within the Rhine basin,i.e.MAIN_BAS=2080023010.FormatAn Object of class SpatialPolygonsDataFrame with289features.The attribute table comprises13fields:HYBAS_ID factor,unique basin identifierNEXT_DOWN factor,Hybas_id of the next downstream polygonNEXT_SINK factor,Hybas_id of the next downstream sinkMAIN_BAS factor,Hybas_id of the most downstream sink,i.e.the outlet of the main river basin DIST_SINK numeric,Distance from polygon outlet to the next downstream sink along the river network,in kilometersDIST_MAIN numeric,Distance from polygon outlet to the most downstream sink,i.e.the outlet of the main river basin along the river network,in kilometersSUB_AREA numeric,Area of the individual polygon(i.e.sub-basin),in square kilometersUP_AREA numeric,Total upstream area,in square kilometers,calculated from the headwaters to the polygon location(including the polygon)PFAF_IF int,the Pfafstetter codeENDO int,Indicator for endorheic(inland)basins without surfaceflow connection to the ocean:0 =not part of an endorheic basin;1=part of an endorheic basin;2=sink(i.e.most downstream polygon)of an endorheic basin.COAST int,indicator for lumped coastal basins:0=no;1=yesORDER int,Indicator of river order(classical ordering system):order1represents the main stem river from sink to source;order2represents all tributaries thatflow into a1st order river;order3represents all tributaries thatflow into a2nd order river;etc.;order0is used for conglomerates of small coastal watershedsSORT int,Indicator showing the record number(sequence)in which the original polygons are stored in the shapefile(i.e.counting upwards from1in the original shapefile).The PROJ.4string is+proj=longlat+datum=WGS84+no_defs+ellps=WGS84+towgs84=0,0,0SourceThis product rhineHYBASlev08incorporates data from the HydroSHEDS database which is(C) World Wildlife Fund,Inc.(2006-2013)and has been used herein under license.WWF has not evaluated the data as altered and incorporated within rhineHYBASlev08,and therefore gives no warranty regarding its accuracy,completeness,currency or suitability for any particular purpose.Portions of the HydroSHEDS database incorporate data which are the intellectual property rights of(C)USGS(2006-2008),NASA(2000-2005),ESRI(1992-1998),CIAT(2004-2006),UNEP-WCMC(1993),WWF(2004),Commonwealth of Australia(2007),and Her Royal Majesty and the British Crown and are used under license.The HydroSHEDS database and more information are available at .ReferencesB.Lehner and G.Grill,2013,Global river hydrography and network routing:baseline data andnew approaches to study the world’s large river systems,Hydrological Processes,27,2171–2186, doi:10.1002/hyp.9740.Examples##Not run:##Catchment of gauge Mainz/Rhein##HYBAS uses a modified version of Pfafstetterop.old<-options()options("hydrocode.alloddorzero"=TRUE)ok<-is.downstream(23263070,rhineHYBASlev08$PFAF_ID)MzBas<-subset(rhineHYBASlev08,subset=ok)sp::plot(rhineHYBASlev08)sp::plot(MzBas,add=TRUE,col="red")##get catchment size##AEO:98206km2according to websitesum(MzBas$SUB_AREA)##reset previous settingsoptions(op.old)##End(Not run)Index∗datasetsrhineCCM2,5rhineHYBASlev08,6∗logicis.upstream,2∗mathis.odd,2is.upstream,2%down%(is.upstream),2%up%(is.upstream),2is.downstream(is.upstream),2is.even(is.odd),2is.odd,2is.upstream,2options,4rhineCCM2,5rhineHYBASlev08,68。

proteus中各种元器件的英文名

元件名称中文名说明AND 与门ANTENNA 天线BA TTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管)BRIDEG 2 整流桥(集成块)BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPV AR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点)ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN 三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE ? 三极真空管V ARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关补充:7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BA TTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM 016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

– 绘制逻辑框图 – 在DCS里组态逻辑控制 – 调试

建立逻辑联锁控制回路 • 在工艺生产时为了保护人员或设备的安 全,通常有联锁保护要求。这些联锁保护 可通过建立逻辑联锁控制回路来实现 • 逻辑联锁控制回路的CM包括:

– AI Channel 和DI Channel – 若干个逻辑运算块,完成与、或、非、异或、 比较、延迟、R/S触发器等逻辑运算 – DO Channel或者DEVCTL功能块

– – – – 液位输入信号(AI Channel) 启动按钮输入(DI Channel ,按下时为ON) 停止按钮输入(DI Channel ,按下时为ON) 流量开关输入(DI Channel ,流量大于一个设定值时为 ON,否则为OFF)

GT

Greater Than

LI100 20

START STOP FS100

– 将输入的整数变为16位的二进制,然后向右 循环移动,第1位移到第16位 – 第16位是符号位,0为正,1为负 – 为负数时,为0的位参与计算,为1的位不参 与计算 – 再变为十进制输出 – 移动的位数可以定义

谢谢!

逻辑运算块 • SHR (Shift Output Right)

– 将输入的整数变为16位的二进制,然后向右 移,再变为十进制输出 – 移动的位数可以定义 – 例如输入为10,移动1位 – 输出为5 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1

delaytime

逻辑运算块 • RS (Reset Dominant )

– R主导的触发器 – 2个输入中,1个是S位 (Set),另一个是 R 位 (Reset)

Set 0 0 1 1 Reset 0 1 0 1 Output Not Change 0 1 0

逻辑运算块 • SR (Set Dominant ) • 2个输入中,1个是S位 (Set),另一个 是 R位 (Reset)

建立逻辑联锁控制回路

Rev.01

逻辑控制在DCS中的实现 • 逻辑控制的概念

– 根据某些条件的逻辑关系决定最后措施 和动作的控制 – 包括与、或、非等运算 – 输出逻辑运算的结果来控制设备的运行 或停止 – 保证人员和设备的安全

• 常用的逻辑运算

逻辑控制在DCS中的实现 • 实现逻辑控制的步骤

– 了解逻辑需求

AND

P100

已有的2个输入管脚

选择输入管脚

选择管脚的序号

这是输入管脚

放置在左右侧

新添加的第三个输入管脚

对第三个管脚上的信号取反

LI100 20

GT Greater Than

START STOP FS100

AND

P100

逻辑运算块 • 2OO3

– 3选2表决 – 3个输入中,2个或者2个以上为ON,输出 参数MAJ为ON,2个或者以上为OFF,输 出参数MAJ为OFF – 在延迟一段时间后,如果3个输入的值相 同,输出参数DISCREP为OFF,否则为ON

– 输入的变化延迟一个扫描周期后送到输出

逻辑运算块 • ONDelay

– 当输入从OFF变为ON时,信号被延迟 – 延迟时间可组态

delaytime

delaytime

delaytime

逻辑运算块 • OFFDelay

– 当输入从ON变为OFF时,信号被延迟 – 延迟时间可组态

delaytime

delaytime

pulsewidth

pulsewidth

pulsewidth

逻辑运算块 • MinPulse

– 当输入从OFF变为ON时,有一脉冲输出 – 脉冲的时间宽度与输入为ON的时间相关 – PulseWidth参数定义出最小的脉冲宽度

pulsewidth

pulsewidth

pulsewidth

逻辑运算块 • FTRIG (Falling-edge Trigger)

逻辑运算块 • nOON

– N选n表决,最多可以有20个输入 – N个输入中,n个或者n个以上为ON,输出 参数VOTED为ON,否则为OFF – 有1个或者1个以上输入为ON时,输出参数 ORED为ON,否则为OFF – 当某一个输入从OFF变为ON时,触发一个 报警脉冲,参数ALARM变为ON – 脉冲的时间宽度通过参数PULSEWIDTH设 定,时间单位为秒

• MIN

– 最多有8个输入 – 输出等于输入中的最小值

逻辑运算块 • SHL (Shift Output Left)

– 将输入的整数变为16位的二进制,然后向左 移,再变为十进制输出 – 移动的位数可以定义 – 例如输入为10,移动1位 – 输出为20 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0

Set 0 0 1 1 Reset 0 1 0 1 Output Not Change 0 1 1

逻辑运算块 • LIMIT

– 可设定最大值和最小值 – 当输入在设定范围内,输出等于输入 – 当输入大于最大值,输出等于最大值 – 当输入大于最大值,输出等于最大值

逻辑运算块 • MAX

– 最多有8个输入 – 输出等于输入中的最大值

AND

P100

AI Channel:将液 位测量信号读进来

逻辑运算块

GT: Greater Than 大于比较块

相比较的数值

LI100 20

GT Greater Than

START STOP FS100

AND

P100

LI100 20

GT Greater Than

START ST下:现场有一个泵P100,当操作人 员按下启动按钮时,泵启动;当操作人员 按下停止按钮时,泵停止转动。泵在运行期 间,如果润滑油流量偏低或者液位偏低,为 了保护泵不受磨损,泵强制被停止运转 • 可建立一个逻辑联锁控制回路来实现这个要 求

建立逻辑联锁控制回路

• 建立逻辑联锁控制回路之前应先根据工艺上的逻辑要 求画出逻辑框图 • 在这个例子中,有4个输入变量参与到逻辑运算中

– 下降沿触发脉冲 – 1个输入、1个输出 – 输入从ON变为OFF时,输出变为ON,持续 一个扫描周期后变为OFF

• RTRIG (Rising-edge Trigger)

– 上升沿触发脉冲 – 1个输入、1个输出 – 输入从OFF变为ON时,输出变为ON,持续 一个扫描周期后变为OFF

逻辑运算块 • Delay

逻辑运算块 • Pulse

– 当输入从OFF变为ON时,输出一个固定宽 度的脉冲 – 脉冲的宽度通过PulseWidth参数组态

pulsewidth

pulsewidth

pulsewidth

逻辑运算块 • MaxPulse

– 当输入从OFF变为ON时,产生一脉冲输出 – 脉冲的时间宽度与输入为ON的时间相关 – PulseWidth参数定义出最大的脉冲宽度

逻辑运算块 • ROL (Rotate Output Left)

– 将输入的整数变为16位的二进制,然后向左 循环移动,第16位移到第1位 – 第16位是符号位,0为正,1为负 – 为负数时,为0的位参与计算,为1的位不参 与计算 – 再变为十进制输出 – 移动的位数可以定义

逻辑运算块 • ROR (Rotate Output Right)