TPS65023RSBT;TPS65023RSBR;TPS65023EVM-205;中文规格书,Datasheet资料

TPS65132

L V IN V POSV NEG5.4 V/40 mA–5.4V/40 mAProduct FolderSample &BuyTechnical Documents Tools &SoftwareSupport &CommunityTPS65132ZHCSCH4B –JUNE 2013–REVISED MAY 2014TPS65132单电感器-双输出电源1特性2应用范围•SIMO (单电感器多输出)稳压器技术•薄膜晶体管(TFT)液晶显示器(LCD)智能手机(原文为Smarpthones )•在I OUT 大于10mA 时,效率大于85%•TFT LCD 平板电脑• 2.5V 至5.5V 输入电压范围•有机发光二极管(OLED)显示器•欠压闭锁上升/下降•普通双电源应用•可编程输出电压•正输出电压范围:3说明4V 至6V (步长0.1V )TPS65132被设计用来支持由正/负电压驱动的普通应•负输出电压范围:用。

该器件使用单电感器系统配置,以便为用户提供-4V 至-6V (步长0.1V )尽可能小的解决方案尺寸以及高效率。

借助其2.5V 至•1%的输出电压准确度 5.5V 的输入电压范围,此器件针对由单节电池(锂离•可编程有源放电子、镍锂、锂聚合物)供电的产品进行了优化,并且输•内部EEPROM 类型存储器(1000x 可再编程)出电流高达80mA 。

TPS65132采用15焊球晶圆级芯•出色线路稳压片尺寸(WCSP)封装。

•用于实现轻负载效率的高级节电模式器件信息(1)•热关断产品型号封装封装尺寸(标称值)•15焊球芯片尺寸封装(CSP)TPS65132YFF (15)2.108mm x 1.514mm(1)要了解所有可用封装,请见数据表末尾的可订购产品附录。

典型应用效率与输出电流间的关系TPS65132ZHCSCH4B–JUNE2013–REVISED 目录8.4Device Functional Modes (12)1特性 (1)8.5Programming (12)2应用范围 (1)8.6Register Maps (16)3说明 (1)9Application and Implementation (19)4修订历史记录 (2)9.1Application Information (19)5Device Comparison Table (3)9.2Typical Applications (19)6Pin Configuration and Functions (3)10Power Supply Recommendations (37)7Specifications (4)11Layout (38)7.1Absolute Maximum Ratings (4)11.1Layout Guidelines (38)7.2Handling Ratings (4)11.2Layout Example (38)7.3Recommended Operating Conditions (5)12Device and Documentation Support (39)7.4Thermal Information (5)12.1Device Support (39)7.5Electrical Characteristics (6)12.2Trademarks (39)7.6I2C Interface Timing Requirements/Characteristics12.3Electrostatic Discharge Caution (39) (6)12.4Glossary (39)7.7Typical Characteristics (8)13Mechanical,Packaging,and Orderable 8Detailed Description (9)Information (39)8.1Overview (9)13.1CSP Package Summary (40)8.2Functional Block Diagram (9)8.3Feature Description (9)4修订历史记录NOTE:Page numbers for previous revisions may differ from page numbers in the current version.Changes from Revision A(August2013)to Revision B Page •Added the Handling Ratings table (4)Changes from Original(June2013)to Revision A Page •已将格式更改为全新的数据表标准 (1)•Added TPS65132Bx devices to the Device Comparison table (3)AA 112233BB CC DD EE (bottom view)(top view)SCL CFLY1SDA REGOUTPAGND REG OUTN CFLY2PGNDENP VIN SW PGND ENN TPS65132ZHCSCH4B –JUNE 2013–REVISED MAY 20145Device Comparison TableDEFAULTSTARTUP TIME PART NUMBER I SDOUTPUT VOLTAGESI OUT_MAX ACTIVE DISCHARGEVPOSVNEGV POS =5.4V TPS65132A V NEG =–5.4V 40mAV POS /V NEG0.25ms 0.40ms 30µAV POS =5.0V TPS65132A0V NEG =–5.0V V POS =5.4V TPS65132B V NEG =–5.4V V POS =5.0V TPS65132B040mAV POS /V NEG0.25ms0.40ms130nAV NEG =–5.0V V POS =5.5V TPS65132B5V NEG =–5.5V V POS =5.2V TPS65132B2V NEG =–5.2V 40mAV POS /V NEG0.82ms1.6ms130nAV POS =5.4V TPS65132LV NEG =–5.4V6Pin Configuration and FunctionsYFF PackageTPS65132ZHCSCH4B–JUNE2013–REVISED Pin FunctionsPINI/O DESCRIPTIONNAME YFFAGND D2—Analog groundCFLY1C3I/O Negative charge pump flying capacitor pinCFLY2A3I/O Negative charge pump flying capacitor pinENN A1I Enable pin for V NEG railENP B1I Enable pin for V POS railOUTP E3O Output pin of the LDO(V POS)OUTN A2O Output pin of the negative charge pump(V NEG)B3PGND—Power groundE1D3REG I/O Boost converter output pinE2SCL B2I/O I²C interface clock signal pinSDA C2I/O I²C interface data signal pinSW D1I/O Switch pin of the boost converterVIN C1I Input voltage supply pin7Specifications7.1Absolute Maximum Ratings(1)(2)over operating free-air temperature range(unless otherwise noted)VALUEUNITMIN MAXCFLY1,ENN,ENP,OUTP,REG,SCL,SDA,SW,VIN–0.37V Voltage rangeCFLY2,OUTN–70.3V Continuous total power dissipation See Thermal InformationOperating junction temperature range,T J–40150°C Operating ambient temperature range,T A–4085°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to ground.7.2Handling RatingsMIN MAX UNITT stg Storage temperature range–65150°C Human body model(HBM),per ANSI/ESDA/JEDEC JS-001,all pins(1)–22kVV ESD Charged device model(CDM)per JEDEC specification JESD22-–500500V C101,all pins(2)(1)JEDEC document JEP155states that500-V HBM allows safe manufacturing with a standard ESD control process.(2)JEDEC document JEP157states that250-V CDM allows safe manufacturing with a standard ESD control process.TPS65132 ZHCSCH4B–JUNE2013–REVISED MAY20147.3Recommended Operating ConditionsMIN TYP MAX UNITV IN Input voltage range 2.5 5.5VL Inductor(1) 2.2 4.7µHC IN Input capacitor(1)(2) 4.7µFC FLY Flying capacitor(1)(2) 2.2µFC OUTP,C OUTN,C REG Output capacitors(1)(2) 4.7µFT A Operating ambient temperature–4085°CT J Operating junction temperature–40125°C(1)Please see Detailed Description section for further information.(2)X7R(or better dielectric material)is recommended.7.4Thermal InformationTPS65132THERMAL METRIC(1)YFF UNIT(15)BALLSRθJA Junction-to-ambient thermal resistance76.5RθJCtop Junction-to-case(top)thermal resistance0.2RθJB Junction-to-board thermal resistance44°C/WψJT Junction-to-top characterization parameter 1.6ψJB Junction-to-board characterization parameter43.4RθJCbot Junction-to-case(bottom)thermal resistance N/A(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report,SPRA953.TPS65132ZHCSCH4B–JUNE2013–REVISED 7.5Electrical CharacteristicsV IN=3.7V,ENN=ENP=V IN,V POS=5.4V,V NEG=–5.4V,T A=–40°C to85°C;typical values are at T A=25°C(unless otherwise noted).PARAMETER TEST CONDITIONS MIN TYP MAX UNIT SUPPLY CURRENTV IN Input voltage range 2.5 5.5VV IN rising 2.5V UVLO Undervoltage lockout threshold VV IN falling 2.3I Q Quiescent current0.54mAThermal shutdown140°CThermal shutdown hysteresis5°C LOGIC ENN,ENP,SCL,SDAV IH High level input voltage 1.1V IN=2.5V to5.5V VV IL Low level input voltage0.54R EN ENN,ENP pulldown resistors200kΩBOOST CONVERTERI LIM Boost converter valley current limit0.9 1.2 1.5Af SW Boost converter switching frequency 1.35 1.80 2.25MHz LDO OUTPUT V POSV POS Positive output voltage range 4.0 6.0VV POS_acc Positive output voltage accuracy–1%+1%I POS Positive output current capability200mAV DO Dropout voltage V REG=V POS(NOM)=5.4V,I OUT=150mA160mV Line regulation V IN=2.5V to5.5V,I OUT=40mA 2.7mVLoad regulationΔI OUT=80mA 3.4%/AR D Discharge resistor70ΩNEGATIVE CHARGE PUMP OUTPUT V NEGV NEG Negative output voltage range–4.0–6.0VV NEG_acc Negative output voltage accuracy–1%+1%Smartphone MODE40I NEG Negative output current capability mATablet MODE80Negative charge pump switchingf OSC0.8 1.0 1.2MHzfrequencyLine regulation V IN=2.5V to5.5V,I OUT=40mA 3.3mVLoad regulationΔI OUT=80mA 6.1%/AR D Discharge resistor20Ω7.6I2C Interface Timing Requirements/Characteristics(1)PARAMETER TEST CONDITIONS MIN TYP MAX UNITStandard mode100kHzf SCL SCL clock frequencyFast mode400kHzStandard mode 4.7µst LOW LOW period of the SCL clockFast mode 1.3µsStandard mode 4.0µst HIGH HIGH period of the SCL clockFast mode600nsStandard mode 4.7µst BUF Bus free time between a STOP and START conditionFast mode 1.3µsStandard mode 4.0µst hd;STA Hold time for a repeated START conditionFast mode600ns (1)Industry standard I2C timing characteristics acoording to I2C-Bus Specification,Version2.1,January2000.Not tested in production.SDA SCL TPS65132 ZHCSCH4B–JUNE2013–REVISED MAY2014I2C Interface Timing Requirements/Characteristics(continued)PARAMETER TEST CONDITIONS MIN TYP MAX UNITStandard mode 4.7µst su;STA Setup time for a repeated START conditionFast mode600nsStandard mode250nst su;DAT Data setup timeFast mode100nsStandard mode0.05 3.45µst hd;DAT Data hold timeFast mode0.050.9µsStandard mode20+1000ns0.1C BRise time of SCL signal after a repeated START conditiont RCL1and after an acknowledge bit Fast mode20+1000ns0.1C BStandard mode20+1000ns0.1C Bt RCL Rise time of SCL signalFast mode20+300ns0.1C BStandard mode20+300ns0.1C Bt FCL Fall time of SCL signalFast mode20+300ns0.1C BStandard mode20+1000ns0.1C Bt RDA Rise time of SDA signalFast mode20+300ns0.1C BStandard mode20+300ns0.1C Bt FDA Fall time of SDA signalFast mode20+300ns0.1C BStandard mode 4.0µst su;STO Setup time for STOP conditionFast mode600nsC B Capacitive load for SDA and SCL0.4nFFigure1.Serial Interface Timing For F/S-ModeTPS65132ZHCSCH4B–JUNE2013–REVISED 7.7Typical CharacteristicsV IN=3.7V,V POS=5.4V,V NEG=–5.4V,unless otherwise notedV INV POSV NEG5.4 V/40 mA–5.4V/40 mA TPS65132 ZHCSCH4B–JUNE2013–REVISED MAY2014 8Detailed Description8.1OverviewThe TPS65132,supporting input voltage range from2.5V to5.5V,operates with a single inductor scheme to provide a high efficiency with a small solution size.The synchronous boost converter generates a positive voltage that is regulated down by an integrated LDO,providing the positive supply rail(V POS).The negative supply rail(V NEG)is generated by an integrated negative charge pump(or CPN)driven from the boost converter output pin REG.The operating mode can be selected between Smartphone and Tablet in order to select the necessary output current capability and to get the best efficiency possible based on the application.The device topology allows a100%asymmetry of the output currents.8.2Functional Block Diagram8.3Feature Description8.3.1Undervoltage Lockout(UVLO)The TPS65132integrates an undervoltage lockout block(UVLO)that enables the device once the voltage on the VIN pin exceeds the UVLO threshold(2.5V maximum).No output voltage will however be generated as long as the enable signals are not pulled HIGH.The device,as well as all converters(boost converter,LDO,CPN),will be disabled as soon as the V IN voltage falls below the UVLO threshold.The UVLO threshold is designed in a way that the TPS65132will continue operating as long as V IN stays above2.3V.This guarantees a proper operation even in the event of extensive line transients when the battery gets suddenly heavily loaded.For TPS65132Ax,a40ms delay is starting as soon as the UVLO threshold is reached.This delay prevents the device to be disabled and enabled by an unwanted VIN voltage spike.Once this delay has passed,the output rails can be enabled and disabled as desired with the enable signals without any delay.8.3.2Active DischargeAn active discharge of the positive rail and/or the negative rail can be programmed(DISP and DISN bits respectively-refer to DAC Registers).If programmed to be active,the discharge will occur at power down,when the enable signals go LOW(Figure40and Figure41).TPS65132ZHCSCH4B–JUNE2013–REVISED Feature Description(continued)8.3.3Boost Converter8.3.3.1Boost Converter OperationThe synchronous boost converter uses a current mode topology and operates at a quasi-fixed frequency of typically1.8MHz,allowing chip inductors such as2.2µH or4.7µH to be used.The converter is internally compensated and provides a regulated output voltage automatically adjusted depending on the programmed V POS and V NEG voltages.The boost converter operates either in continuous conduction mode(CCM)or Pulse Frequency Modulation mode(PFM),depending on the load current in order to provide the highest efficiency possible.The switch node waveforms for CCM and DCM operation are shown in Figure6and Figure7.8.3.3.2Power-Up And Soft-Start(Boost Converter)The boost converter starts switching as soon as the enable signal is pulled HIGH and the voltage on VIN pin is above the UVLO threshold.For TPS65132Ax,in the case where the enable signal is already HIGH when V IN reaches the UVLO threshold,the boost converter will only start switching after a40ms delay has passed(see Undervoltage Lockout(UVLO)).The boost converter starts up with an integrated soft-start to avoid drawing excessive inrush current from the supply.The output voltage V REG is slowly ramped up to its target value.Typical startup waveforms are shown in Figure36and Figure38.8.3.3.3Power-Down(Boost Converter)The boost converter stops switching when V IN is below the UVLO threshold or when both output rails are disabled.For example,due to a special sequencing,the LDO might still be operating while the CPN is already disabled,in which case,the boost will continue operating until the LDO has been disabled.Typical power-down waveforms are shown in Figure37and Figure39.8.3.3.4Isolation(Boost Converter)The boost converter output(REG)is isolated from the input supply V IN,provinding a true shutdown.8.3.3.5Output Voltage(Boost Converter)The output voltage of the boost converter is automatically adjusted depending on the programmed V POS and V NEG voltages.8.3.3.6Advanced Power-Save Mode For Light-Load Efficiency And PFMThe TPS65132device integrates a power save mode to improve efficiency at light load.In power save mode the converter stops switching when the inductor current reaches0A.The device resumes its switching activity with one or more pulses once the V REG voltage falls below its regulation level,and goes again into power save mode once the inductor current reaches0A.The pulse duration remains constant,but the frequency of these pulses varies according to the output load.This operating mode is also known as Pulse Frequency Modulation or PFM. Figure6provides plots of the inductor current and the switch node in PFM mode.V SWV REG_AC I LV SWV REG_ACI LFigure 7.Boost Converter —Heavy Load (40mA)Figure 6.Boost Converter -Light Load (1mA)8.3.4LDO Regulator 8.3.4.1LDO OperationThe Low Dropout regulator (or LDO)generates the positive voltage rail V POS by regulating down the output voltage of the boost converter (V REG ).Its inherent power supply rejection helps filtering the output ripple of the boost converter in order to provide on OUTP pin a clean voltage,e.g.to supply the source driver IC of the display.8.3.4.2Power-Up And Soft-Start (LDO)The LDO starts operating as soon as the ENP signal is pulled HIGH,V IN voltage is above the UVLO threshold and the boost converter has reached its Power Good threshold.In the case where the enable signal is already HIGH when V IN exceeds the UVLO threshold,the boost converter will start first and the LDO will only start after the boost converter has reached its target voltage.For TPS65132Ax,the boost will start after the 40ms delay has passed (see Undervoltage Lockout (UVLO)).The LDO integrates a soft-start that slowly ramps up its output voltage V POS regardless of the output capacitor,as long as the LDO current limit is not reached.For TPS65132Ax and TPS65132Bx (except TPS65132B2),the typical startup time is 250µs.For TPS65132B2,TPS65132Lx,the typical ramp-up time is 800µs and the inrush current is also reduced by a factor of 3.3.Typical startup waveforms are shown in Figure 36and Figure 38.8.3.4.3Power-Down And Discharge (LDO)The LDO stops operating when V IN is below the UVLO threshold or when ENP is pulled LOW.The positive rail can be actively discharged to GND during power-down if required.A discharge selection bit is available to enable or disable this function.See DAC Settings for more details,as well as waveforms on Figure 40and Figure 41.8.3.4.4Isolation (LDO)The LDO is isolating the V POS rail from V REG (boost converter output)as long as the rail is not enabled in order to ensure flexible startup like V NEG before V POS .8.3.4.5Setting The Output Voltage (LDO)The output voltage of the LDO is programmable via a I 2C compatible interface,from 4.0V to 6.0V with 100mV steps.For more details,please refer to the DAC Settings section.8.3.5Negative Charge Pump8.3.5.1OperationThe negative charge pump(CPN)generates the negative voltage rail V NEG by inverting and regulating the output voltage of the boost converter(V REG).The charge pump uses4switches and an external flying capacitor to generate the negative rail.Two of the switches are turned on in the first phase to charge the flying capacitor up to V REG,and in the second phase they are turned-off and the two others turn on to pump the energy negatively out of the OUTN capacitor.8.3.5.2Power-Up And Soft-Start(CPN)The CPN starts operating as soon as the ENN signal is pulled HIGH,V IN voltage is above the UVLO threshold and the boost converter has reached its Power Good threshold.In the case where the enable signal is already HIGH when V IN reaches the UVLO threshold,the boost converter will start first and the CPN will only start after the boost converter has reached its target voltage.For TPS65132Ax,the boost will start after the40ms delay has passed(see Undervoltage Lockout(UVLO)).The CPN integrates a soft-start that slowly ramps up its output voltage V NEG within a time defined by the selected mode(Smartphone or Tablet),the output voltage and the output capacitor value.For TPS65132Ax and TPS65132Bx(except TPS65132B2),the startup current charging the output capacitor in Smartphone mode is 50mA,and100mA in Tablet mode typically.For TPS65132B2,TPS65132Lx,the typical ramp-up times are slowed down by a factor of4(i.e12.5mA and25mA output current respectively)and the inrush current is also reduced by a factor of about4.Typical startup waveforms are shown in Figure36and Figure38.8.3.5.3Power-Down And Discharge(CPN)The CPN stops operating when V IN is below the UVLO threshold or when ENN is pulled LOW.The negative rail can be actively discharged to GND during power-down if required.A discharge selection bit is available to enable or disable this function.See DAC Settings for more details,as well as waveforms Figure40 and Figure41.8.3.5.4Isolation(CPN)The CPN isolates the V NEG rail from V REG(boost converter output)as long as the rail is not enabled in order to ensure flexible startup like V POS before V NEG.8.3.5.5Setting The Output Voltage(CPN)The output voltage of the CPN is programmable via a I2C compatible interface,from4.0V to6.0V with100mV steps.For more details,please refer to the DAC Settings section.8.4Device Functional Modes8.4.1Enabling and Disabling the DeviceThe TPS65132is enabled as long as the VIN voltage is above the UVLO and the enable pin for V NEG rail(ENN).8.5Programming8.5.1I2C Serial Interface DescriptionThe TPS65132communicates through an industry standard I2C compatible interface,to receive data in slave mode.I2C is a2-wire serial interface developed by Philips Semiconductor(see I2C-Bus Specification,Version 2.1,January2000).The TPS65132integrates a non-volatile memory(EEPROM)that allows the storage of the DAC values into the registers with a capability of up to1000programming cycles maximum.DATACLKSTART ConditionDATACLKSTOP ConditionProgramming (continued)The bus consists of a data line (SDA)and a clock line (SCL)with pull-up structures.When the bus is idle,both SDA and SCL lines are pulled high.All the I 2C compatible devices connect to the I 2C bus through open drain I/O pins,SDA and SCL.A master device,usually a microcontroller or a digital signal processor,controls the bus.The master is responsible for generating the SCL signal and device addresses.The master also generates specific conditions that indicate the START and STOP of data transfer.A slave device receives and/or transmits data on the bus under control of the master device.The TPS65132works as a slave and supports the following data transfer modes,as defined in the I 2C-Bus specification:standard mode (100kbps)and fast mode (400kbps).The data transfer protocol for standard and fast modes is exactly the same,therefore they are referred to as F/S-mode in this document.The TPS65132supports 7-bit addressing.The device 7-bit address is 3E (see Figure 8),and the LSB enables the write or read function.Figure 8.TPS65132Slave Address ByteMSB TPS65132AddressLSB 011111R/WR/W =R/(W)The device that initiates the communication is called a master,and the devices controlled by the master are slaves.The master generates the serial clock on SCL,controls the bus access,and generates START and STOP conditions (see Figure 9).A START initiates a new data transfer to a slave.Transitioning SDA from high to low while SCL remains high generates a START condition.A STOP condition ends a data transfer to slave.Transitioning SDA from low to high while SCL remains high generates a STOP condition.Figure 9.Start And Stop ConditionsThe master then generates the SCL pulses,and transmits the 7-bit address and the read/write direction bit R/(W)on the SDA line.During all transmissions,the master ensures that the data is valid.A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 10).All devices recognize the address sent by the master and compare it to their internal fixed addresses.Only the slave device with a matching address generates an Acknowledgment,ACK,(see Figure 11)by pulling the SDA line low during the entire high period of the SCL cycle.Upon detecting this Acknowledgment,the master knows that communication link with a slave has been established.Figure 10.Bit Transfer On The Serial InterfaceFigure11.Acknowledge On The IC Bus2The master generates further SCL cycles to either transmit data to the slave(R/(W)bit=0)or receive data from the slave(R/(W)bit=1).In either case,the receiver needs to acknowledge the data sent by the transmitter.So an acknowledge signal can either be generated by the master or by the slave,depending on which one is the receiver.9-bit valid data sequences consisting of8-bit data and1-bit acknowledge can continue as long as necessary.To terminate the data transfer,the master generates a STOP condition by pulling the SDA line from low to high while the SCL line is high(see Figure12).This releases the bus and stops the communication link with the addressed slave.All I2C compatible devices must recognize the stop condition.Upon the receipt of a stop condition,all devices know that the bus is released,and they wait for a start condition followed by a matching address.Figure12.Bus ProtocolNOTEWith TPS65132Bx,TPS65132Lx,the I2C interface is not accessible as long as ENN=ENP=LOW.As soon as one of the enable pins is pulled HIGH,the I2C interface isaccessible.11111“1”Write all DAC data to EEPROM1From Master to SlaveFrom Slave to MasterP =STOPcondition111111From Master to SlaveFrom Slave to MasterP =STOP condition111111From Master to SlaveFrom Slave to MasterP =STOP condition8.5.2I 2C Interface ProtocolFigure 13.“Write"Data To DAC –Transfer Format In F/S-ModeFigure 14."Write"Data To DAC –Transfer Format In F/S-Mode Featuring Register Address Auto-IncrementFigure 15.“Write”Data To EEPROM –Transfer Format In F/S-ModeFrom Master to SlaveFrom Slave to MasterA A ==Acknowledge (SDA LOW)Not Acknowledge (SDA HIGH)S =START conditionSr =REPEATED START condition P =STOPcondition111111111111From Master to SlaveFrom Slave to MasterA A ==Acknowledge (SDA LOW)Not Acknowledge (SDA HIGH)S =START conditionSr =REPEATED START condition P =STOP conditionFigure 16.“Read”Data From DAC/EEPROM –Transfer Format In F/S-ModeFigure 17.“Read”Data From DAC/EEPROM –Transfer Format In F/S-Mode Featuring Register AddressAuto-Increment8.6Register MapsThe TPS65132has one non-volatile memory which contains the initial value of the DAC and one volatile memory which contains the DAC setting.The non-volatile memory is called the Initial Value Register (IVR)and the volatile memory is called DAC Register (DR).The non-volatile IVR and the volatile DR are accessed with the same address.Startup option:At power-up,the value contained in the IVR is loaded into the volatile DR and IVR presets the DAC to the last stored setting within less than 20µs.The programmed factory value of the IVR of each address is described below and,at power-up,these data byte set the output voltage of each rail.Write description:The user has to program all data registers first (0×00~0×03),then set the WED (Write EEPROM Data)bit to 1once all desired data are addressed.A dead time of 50ms is then initiated during which all the register data (0×00~0×03)are stored into the non volatile EEPROM cell.During that time,there should be no data flowing through the I 2C because the I 2C interface is momentarily not responding.After the 50ms have passed,the WED bit is automatically reset to 0,and the user is able to read the values or program again.Register Maps(continued)Slave address:0×3EX=R/W R/W=1→read modeR/W=0→write mode8.6.1DAC RegistersFigure18.VPOS Register–0×00MSB Address0×0011LSB Reserved Reserved Reserved VPOS VPOS VPOS VPOS VPOSFigure19.VNEG Register–0×01:MSB Address0×01LSB Reserved Reserved Reserved VNEG VNEG VNEG VNEG VNEGFigure20.APPS-DISP-DISN Register–0×03:MSB Address0×01LSB Reserved APPS Reserved Reserved Reserved SEQD DISP DISNFigure21.Control Register–0×FF:MSB Address0×01LSB WED Reserved Reserved Reserved Reserved Reserved Reserved EE/(DR)The Reserved bits are ignored when written and return either0or1when read.Attempting to read data from register addresses not listed in the following section will result in0×00being read out.8.6.2DAC SettingsThe following tables show the DAC values and the corresponding voltages of each block address.VPOS—VPOS VNEG—0×01VNEG APPS—0×03APPLICATION 0×00[4:0][4:0]00h 4.0V00h–4.0V0Smartphone 01h 4.1V01h–4.1V1Tablet 02h 4.2V02h–4.2V03h 4.3V03h–4.3V04h 4.4V04h–4.4V05h 4.5V05h–4.5V DISP—0×03ACTIVEDISCHARGE 06h 4.6V06h–4.6V0No discharge 07h 4.7V07h–4.7V1V POS actively 08h 4.8V08h–4.8V discharged 09h 4.9V09h–4.9V0Ah 5.0V0Ah–5.0V DISN—0×03ACTIVEDISCHARGE 0Bh 5.1V0Bh–5.1V0No discharge 0Ch 5.2V0Ch–5.2V1V NEG actively 0Dh 5.3V0Dh–5.3V discharged 0Eh 5.4V0Eh–5.4V0Fh 5.5V0Fh–5.5V10h 5.6V10h–5.6V11h 5.7V11h–5.7V12h 5.8V12h–5.8V13h 5.9V13h–5.9V14h 6.0V14h–6.0V8.6.2.1Factory Default Register ValueRegister addressPart number0×000×010×03TPS65132A0×0E0×0E0×03TPS65132A00×0A0×0A0×03TPS65132B0×0E0×0E0×03TPS65132B00×0A0×0A0×03TPS65132B20×0C0×0C0×03TPS65132B50×0F0×0F0×03TPS65132L0×0E0×0E0×03。

TPS650250RHBT;TPS650250RHBR;TPS650250EVM-447;中文规格书,Datasheet资料

FEATURESAPPLICATIONSDESCRIPTIONTPS650250/2.8V V /1.8V m FF F TPS650250 SLVS843–DECEMBER 2008Power Management IC for Li-Ion Powered SystemsThe TPS650250also integrates two general purpose 200mA LDO voltage regulators,which are enabled •1.6A,97%Efficient Step-Down Converter for with an external input pin.Each LDO operates with System Voltage (VDCDC1)an input voltage range between 1.5V and 6.5V – 3.3V or2.8V or Adjustableallowing them to be supplied from one of the step-down converters or directly from the battery.The •0.8A,up to 95%Efficient Step-Down Converter output voltage of the LDOs can be set with an for Memory Voltage (VDCDC2)external resistor divider for maximum flexibility.– 1.8V or 2.5V or AdjustableAdditionally there is a 30mA LDO typically used to •0.8A,90%Efficient Step-Down Converter for provide power in a processor based system to a Processor Core (VDCDC3)voltage rail that is always on.TPS650250comes in a small 5mm x 5mm 32pin QFN package (RHB).•adjustable output voltage on VDCDC3•30mA LDO for Vdd_aliveFunctional Block Diagram•2×200mA General Purpose LDOs (LDO1and LDO2)•Dynamic Voltage Management for Processor Core•LDO1and LDO2Voltage Externally Adjustable •Separate Enable Pins for Inductive Converters • 2.25MHz Switching Frequency •85µA Quiescent Current•Thermal Shutdown Protection•Cellular/Smart Phone •GPS•Digital Still Camera•Split Supply DSP and µP Solutions •Samsung ARM-Based Processors,etc.The TPS650250is an integrated Power Management IC for applications powered by one Li-Ion or Li-Polymer cell,which require multiple power rails.The TPS650250provides three highly efficient,step-down converters targeted at providing the core voltage,peripheral,I/O and memory rails in a processor based system.All three step-down converters enter a low power mode at light load for maximum efficiency across the widest possible range of load currents.The converters can be forced into fixed frequency PWM mode by pulling the MODE pin high.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright ©2008,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.ht t p ://oABSOLUTE MAXIMUM RATINGSDISSIPATION RATINGSTPS650250SLVS843–DECEMBER These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.ORDERING INFORMATION (1)VOLTAGE ATOUTPUT CURRENT ON VOLTAGE AT T APACKAGE PART NUMBER (2)DCDC3DCDC1/DCDC2/DCDC3VDD_ALIVE32Pin QFN –40°C to 85°C Adjustable1.6A /0.8A /0.8A1VTPS650250RHB(RHB)(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI website at .(2)The RHB package is available in tape and reel.Add R suffix (TPS650250RHBR)to order quantities of 3000parts per reel.Add T suffix (TPS650250RHBT)to order quantities of 250parts per reel.over operating free-air temperature range (unless otherwise noted)(1)VALUEUNIT Input voltage range on all pins except A/PGND pins with respect to AGND –0.3to 7V Voltage range on pins VLDO1,VLDO2,FB_LDO1,FB_LDO2–0.3to 3.6V Current at VINDCDC1,L1,PGND1,VINDCDC2,L2,PGND2,VINDCDC3,L3,PGND32000mA Peak current at all other pins 500mA Continuous total power dissipation See Dissipation Rating TableT A Operating free-air temperature –40to 85°C T J Maximum junction temperature 125°C T st Storage temperature–65to 150°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.T A ≤25°C DERATING FACTOR T A =70°C T A =85°C PACKAGE (1)R θJA POWER RATINGABOVE T A =25°CPOWER RATINGPOWER RATINGRHB35K/W2.85W28mW/K1.57W1.14W(1)The thermal resistance junction to ambient of the RHB package is measured on a high K board.The thermal resistance junction to power pad is 1.5k/W.2Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):TPS650250ht t p ://oRECOMMENDED OPERATING CONDITIONS TPS650250 SLVS843–DECEMBER2008MIN NOM MAX UNIT V CC Input voltage range step-down converters,VINDCDC1,VINDCDC2,VINDCDC3 2.5 6.0V Output voltage range for step-down converter,VDCDC1(1)0.6VINDCDC1V V O Output voltage range for mem step-down converter,VDCDC2(1)0.6VINDCDC2V Output voltage range for core step-down converter,VDCDC30.6VINDCDC3V V I Input voltage range for LDOs,VINLDO1,VINLDO2 1.5 6.5V V O Output voltage range for LDOs1 3.3VI O Output current at L,V1DCDC11600mAL1Inductor at L1(2) 1.5 2.2µHC I Input capacitor at VINDCDC1(2)10µFC O Output capacitor at VDCDC1(2)1022µFI O Output current at L2,VDCDC2800mAL2Inductor at L2(2) 1.5 2.2µHC I Input capacitor at VINDCDC2(2)10µFC O Output capacitor at VDCDC2(2)1022µFI O Output current at L3,VDCDC3800mAL3Inductor at L3(2) 1.5 2.2µHC I Input capacitor at VINDCDC3(2)10µFC O Output capacitor at VDCDC3(2)1022µFC I Input capacitor at VCC(2)1µFC I Input capacitor at VINLDO(2)1µFC O Output capacitor at VLDO1,VLDO2(2) 2.2µFI O Output current at VLDO1,VLDO2200mAC O Output capacitor at Vdd_alive(2) 2.2µFI O Output current at Vdd_alive30mAT A Operating ambient temperature–4085°C T J Operating junction temperature–40125°C R CC Resistor from VINDCDC3,VINDCDC2,VINDCDC1to V CC used for filtering(3)110Ω(1)When using an external resistor divider at DEFDCDC2,DEFDCDC1.(2)See applications section for more information,for V O>2.85V choose3.3µH inductor.(3)Up to2.5mA can flow into V CC when all3converters are running in PWM,this resistor will cause the UVLO threshold to be shiftedaccordingly.Copyright©2008,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):TPS650250h t t p://oELECTRICAL CHARACTERISTICSTPS650250SLVS843–DECEMBER VINDCDC1=VINDCDC2=VINDCDC3=VCC =VINLDO =3.6V,T A =–40°C to 85°C,typical values are at T A =25°C (unless otherwise noted)CONTROL SIGNALS:EN_DCDC1,EN_DCDC2,EN_DCDC3,EN_LDO,MODE,EN_VDD_ALIVEPARAMETERTEST CONDITIONSMIN TYPMAX UNIT High level input V IH 1.45VCC V voltage Low level input V IL 00.4V voltageI HInput bias current0.010.1µASUPPLY PINS:VCC,VINDCDC1,VINDCDC2,VINDCDC3PFM All 3DCDC converters enabled,zero load 135170and no switching,LDOs enabledPFM All 3DCDC converters enabled,zero load and no switching,LDO1,LDO2=OFF,Vdd_alive 75100=ONOperating quiescent I (qPFM)V CC =3.6VµAcurrentPFM DCDC1and DCDC2converters enabled,zero load and no switching,LDO1,LDO2=OFF,5580Vdd_alive =ONPFM DCDC1converter enabled,zero load and no 4060switching,LDO1,LDO2=OFF,Vdd_alive =ON All 3DCDC converters enabled &running in PWM,2LDOs offCurrent into V CC ;PWM DCDC1and DCDC2converters enabled and1.52.5I VCC(PWM)V CC =3.6VmAPWMrunning in PWM,LDOs offPWM DCDC1converter enabled and running in 0.852PWM,LDOs offAll converters disabled,LDO1,LDO2=OFF,16Vdd_alive =OFFI qQuiescent currentV CC =3.6VµAAll converters disabled,LDO1,LDO2=OFF,26Vdd_alive =ON4Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):TPS650250ht t p ://oELECTRICAL CHARACTERISTICS TPS650250 SLVS843–DECEMBER2008 VINDCDC1=VINDCDC2=VINDCDC3=VCC=VINLDO=3.6V,T A=–40°C to85°C,typical values are at T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT VDCDC1STEP-DOWN CONVERTERV I Input voltage range,VINDCDC1 2.56VI O Maximum output current V O=3.3V1600mAI SD Shutdown supply current in VINDCDC1EN_DCDC1=GND0.11µAR DS(on)P-channel MOSFET on-resistance VINDCDC1=VGS=3.6V125261mΩI LP P-channel leakage current VINDCDC1=6V2µAR DS(on)N-channel MOSFET on-resistance VINDCDC1=VGS=3.6V130260mΩI LN N-channel leakage current V DS=6V710µAI LIMF Forward current limit(P-and N-channel) 2.5V<V INMAIN<6V 1.75 1.97 2.15Af S Oscillator frequency 1.95 2.25 2.55MHzFixed output voltage 2.8V–2%2%VINDCDC1=3.3V to6V;MODE=0(PWM/PFM)0mA≤IO ≤1.0A3.3V–2%2% Fixed output voltage 2.8V–1%1%VINDCDC1=3.7V to6V;MODE=1(PWM)0mA≤IO ≤1.0A3.3V–1%1%VDCDC1Adjustable output voltage with resistorVINDCDC1=VDCDC1+0.4V(min2.5V)divider at DEFDCDC1MODE=0–2%2%to6V;0mA≤I O≤1.6A(PWM/PFM)Adjustable output voltage with resistorVINDCDC1=VDCDC1+0.4V(min2.5V)divider at DEFDCDC1;MODE=1–1%1%to6V;0mA≤I O≤1.6A(PWM)VINDCDC1=VDCDC1+0.3V(min.2.5V)Line regulation0%/Vto6V;I O=10mALoad regulation I O=10mA to1.6A0.25%/AVDCDC1ramping from5%to95%oft SS Soft start ramp time750µstarget valueR(L1)Internal resistance from L1to GND1MΩCopyright©2008,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):TPS650250h t t p://oELECTRICAL CHARACTERISTICSTPS650250SLVS843–DECEMBER VINDCDC1=VINDCDC2=VINDCDC3=VCC =VINLDO =3.6V,T A =–40°C to 85°C,typical values are at T A =25°C (unless otherwise noted)PARAMETERTEST CONDITIONSMINTYPMAXUNITVDCDC2STEP-DOWN CONVERTER V I Input voltage range,VINDCDC2 2.56V I O Maximum output currentV O =2.5V800mA I SD Shutdown supply current in VINDCDC2EN_DCDC2=GND 0.11µA R DS(on)P-channel MOSFET on-resistance VINDCDC2=V GS =3.6V 140300m ΩI LP P-channel leakage current VINDCDC2=6.0V 2µA R DS(on)N-channel MOSFET on-resistance VINDCDC2=VGS =3.6V 150297m ΩI LN N-channel leakage current V DS =6V710µA I LIMF Forward current limit (P-and N-channel) 2.5V <VINDCDC2<6V1.05 1.16 1.29A f SOscillator frequency 1.95 2.252.55MHz1.8V VINDCDC2=2.5V to 6V;0mA ≤I O ≤1.6A –2%2%Fixed output voltage MODE =0(PWM/PFM) 2.5V VINDCDC2=3V to 6V;0mA ≤I O ≤1.6A –2%2%1.8V VINDCDC2=2.5V to 6V;0mA ≤I O ≤1.6A –2%2%Fixed output voltage MODE =1(PWM)2.5VVINDCDC2=3V to 6V;0mA ≤I O ≤1.6A –1%1%VDCDC2Adjustable output voltage with resistor VINDCDC2=VDCDC2+0.5V (min 2.5V)divider at DEFDCDC2MODE =0–2%2%to 6V;0mA ≤I O ≤1.6A(PWM)Adjustable output voltage with resistor VINDCDC2=VDCDC2+0.5V (min 2.5V)divider at DEFDCDC2;MODE =1–1%1%to 6V;0mA ≤I O ≤1.6A(PWM)VINDCDC2=VDCDC2+0.3V (min.2.5Line regulation 0.0%/V V)to 6V;I O =10mA Load regulationI O =10mA to 1.6A0.25%/A VDCDC2ramping from 5%to 95%of t SS Soft start ramp time750µs target value R(L2)Internal resistance from L2to GND1M Ω6Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):TPS650250ht t p ://oELECTRICAL CHARACTERISTICS TPS650250 SLVS843–DECEMBER2008 VINDCDC1=VINDCDC2=VINDCDC3=VCC=VINLDO=3.6V,T A=–40°C to85°C,typical values are at T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT VDCDC3STEP-DOWN CONVERTERV I Input voltage range,VINDCDC3 2.5 6.0VI O Maximum output current V O=1.6V800mAShutdown supply current inI SD EN_DCDC3=GND0.11µAVINDCDC3R DS(on)P-channel MOSFET on-resistance V INDCDC3=V GS=3.6V310698mΩI LP P-channel leakage current VINDCDC3=6V0.12µAR DS(on)N-channel MOSFET on-resistance V INDCDC3=V GS=3.6V220503mΩI LN N-channel leakage current V DS=6.0V710µAForward current limit(P-andI LIMF 2.5V<V INDCDC3<6V 1.00 1.20 1.40AN-channel)f S Oscillator frequency 1.95 2.25 2.55MHzAdjustable output voltage with VINDCDC3=VDCDC3+0.5V(min2.5V)to6V;resistor divider at DEFDCDC20mA≤I O≤0.8A–2%2%MODE=0(PWM)VDCDC3Adjustable output voltage with VINDCDC3=VDCDC3+0.5V(min2.5V)to6V;resistor divider at DEFDCDC2;0mA≤I O≤0.8A–1%1%MODE=1(PWM)VINDCDC3=VDCDC3+0.3V(min.2.5V)toLine regulation0.0%/V6V;I O=10mALoad regulation I O=10mA to600mA0.25%/AVDCDC3ramping from5%to95%of targett SS Soft start ramp time750µsvalueR(L3)Internal resistance from L3to GND1MΩCopyright©2008,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):TPS650250h t t p://oELECTRICAL CHARACTERISTICSTPS650250SLVS843–DECEMBER VINDCDC1=VINDCDC2=VINDCDC3=VCC =VINLDO =3.6V,T A =–40°C to 85°C,typical values are at T A =25°C (unless otherwise noted)PARAMETERTEST CONDITIONSMIN TYP MAX UNIT VLDO1and VLDO2Low Dropout Regulators I (q)Operating quiescent current Current per LDO into VINLDO 1630µA I (SD)Shutdown currentTotal current into VINLDO,VLDO =0V0.62µA V I Input voltage range for LDO1,LDO2 1.5 6.5V V O LDO1output voltage range 1 3.3V LDO2output voltage range 13.3V VFB LDO1and LDO2feedback voltage See(1)1.0V I O Maximum output current for LDO1,LDO2V I =1.8V,V O =1.3V 200mA I O Maximum output current for LDO1,LDO2V I =1.5V;V O =1.3V 120mAI SCLDO1and LDO2short circuit current limit V LDO1=GND,V LDO2=GND 400mA Minimum voltage drop at LDO1,LDO2I O =50mA,VINLDO =1.8V 120mV Minimum voltage drop at LDO1,LDO2I O =50mA,VINLDO =1.5V 65150mV Minimum voltage drop at LDO1,LDO2I O =200mA,VINLDO =1.8V 300mVOutput voltage accuracy for LDO1,LDO2I O =10mA–2%1%Line regulation for LDO1,LDO2V INLDO1,2=V LDO1,2+0.5V (min.2.5V)to 6.5V,–1%1%I O =10mALoad regulation for LDO1,LDO2I O =0mA to 200mA–1%1%Regulation time for LDO1,LDO2Load change from 10%to 90%10µsVdd_alive Low Dropout Regulator Vdd_alive Vdd_alive LDO output voltage,TPS6502500to I O =0mA1.0V TPS6502504I O Output current for Vdd_alive 30mA I (SC)Vdd_alive short circuit current limit Vdd_alive =GND 100mAOutput voltage accuracy for Vdd_alive I O =0mA–1%1%Line regulation for Vdd_alive V CC =Vdd_alive +0.5V to 6.5V,I O =0mA –1%1%Regulation time for Vdd_aliveLoad change from 10%to 90%10µs AnaLogic Signals DEFDCDC1,DEFDCDC2,DEFDCDC3V IH High level input voltage 1.3VCC V V IL Low level input voltage 00.1V I H Input bias current 0.0010.05µA THERMAL SHUTDOWNT SDThermal shutdownIncreasing junction temperature 160°C Thermal shudown hysteresisDecreasing junction temperature20°CINTERNAL UNDER VOLTAGE LOCK OUT UVLO Internal UVLOVCC falling–3%2.353%V V UVLO_HYST internal UVLO comparator hysteresis 120mV VOLTAGE DETECTOR COMPARATORPWRFAIL_SNSComparator threshold Falling threshold–2% 1.02%V Hysteresis 405060mV Propagation delay25mV overdrive 10µs V OLPower fail output low voltageI OL =5mA 0.3V(1)If the feedback voltage is forced higher than above 1.2V,a leakage current into the feedback pin may occur.8Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):TPS650250ht t p ://oDEVICE INFORMATION PIN ASSIGNMENTSVDCDC3PGND3L3 VINDCDC3 VINDCDC1L1PGND1 VDCDC1EN_Vdd_aliveMODEDEFDCDC2PWRFAILEN_DCDC1EN_DCDC2EN_DCDC3EN_LDODEFDCDC3AGND1PWRFAIL_SNSVccVINDCDC2L2PGND2VDCDC2DEFDCDC1FB_LDO2FB_LDO1Vdd_aliveAGND2VLDO2VINLDOVLDO1TPS650250 SLVS843–DECEMBER2008TERMINAL FUNCTIONSTERMINALI/O DESCRIPTIONNAME NO.SWITCHING REGULATOR SECTIONAGND131Analog ground connection.All analog ground pins are connected internally on the chip.AGND213Analog ground connection.All analog ground pins are connected internally on the chip.PowerPad–Connect the power pad to analog ground.I Input voltage for VDCDC1step-down converter.This must be connected to the same voltage supply asVINDCDC15VINDCDC2,VINDCDC3and VCC.L16Switch pin of VDCDC1converter.The VDCDC1inductor is connected here.VDCDC18I VDCDC1feedback voltage sense input,connect directly to VDCDC1PGND17Power ground for VDCDC1converterI Input voltage for VDCDC2step-down converter.This must be connected to the same voltage supply asVINDCDC228VINDCDC1,VINDCDC3and VCC.L227Switch pin of VDCDC2converter.The VDCDC2inductor is connected here.VDCDC225I VDCDC2feedback voltage sense input,connect directly to VDCDC2PGND226Power ground for VDCDC2converterI Input voltage for VDCDC3step-down converter.This must be connected to the same voltage supply asVINDCDC34VINDCDC1,VINDCDC2and VCC.L33Switch pin of VDCDC3converter.The VDCDC3inductor is connected here.VDCDC31I VDCDC3feedback voltage sense input,connect directly to VDCDC3PGND32Power ground for VDCDC3converterPower supply for digital and analog circuitry of DCDC1,DCDC2and DCDC3DC-DC converters.This must be Vcc29Iconnected to the same voltage supply as VINDCDC3,VINDCDC1and VINDCDC2.Input signal indicating default VDCDC1voltage,0=2.8V,1=3.3VDEFDCDC19I This pin can also be connected to a resistor divider between VDCDC1and GND.In this case the outputvoltage of the DCDC1converter can be set in a range from0.6V to VINDCDC1Input signal indicating default VDCDC2voltage,0=1.8V,1=2.5VDEFDCDC222I This pin can also be connected to a resistor divider between VDCDC2and GND.In this case the outputvoltage of the DCDC2converter can be set in a range from0.6V to VINDCDC2.Copyright©2008,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):TPS650250h t t p://oh t t p://oTPS650250SLVS843–TERMINAL FUNCTIONS(continued)TERMINALI/O DESCRIPTIONNAME NO.I This pin must be connected to a resistor divider between VDCDC3and GND.The output voltage of theDEFDCDC332DCDC3converter can be set in a range from0.6V to VINDCDC3.EN_DCDC120I VDCDC1enable pin.A logic high enables the regulator,a logic low disables the regulator.EN_DCDC219I VDCDC2enable pin.A logic high enables the regulator,a logic low disables the regulator.EN_DCDC318I VDCDC3enable pin.A logic high enables the regulator,a logic low disables the regulator.LDO REGULATOR SECTIONVINLDO15I Input voltage for LDO1and LDO2VLDO116O Output voltage of LDO1VLDO214O Output voltage of LDO2EN_LDO17I Enable input for LDO1and LDO2.Logic high enables the LDOs,logic low disables the LDOsEN_Vdd_alive24I Enable input for Vdd_alive LDO.Logic high enables the LDO,logic low disables the LDOVdd_alive12O Output voltage for Vdd_aliveFB_LDO111I Feedback pin for LDO1FB_LDO210I Feedback pin for LDO2CONTROL AND I2C SECTIONSelect between Power Safe Mode and forced PWM Mode for DCDC1,DCDC2and DCDC3.In Power Safe MODE23I Mode PFM is used at light loads,PWM for higher loads.If PIN is set to high level,forced PWM Mode isselected.If Pin has low level,then Device operates in Power Safe Mode.PWRFAIL21O Open drain output.Active low when PWRFAIL comparator indicates low VBAT condition.PWRFAIL_SNS30I Input for the comparator driving the/PWRFAIL output10Submit Documentation Feedback Copyright©2008,Texas Instruments IncorporatedProduct Folder Link(s):TPS650250分销商库存信息:TITPS650250RHBT TPS650250RHBR TPS650250EVM-447。

WIFI模块-硬件设计资料

WIFI模块硬件设计规格书版本: 1.0目录1 模块总体介绍(Gerneral introduction) (4)1.1 概述及实物图片(Description) (4)1.2 应用领域(Application) (6)1.3 产品特性 (Main feature) (6)2 模块电气特性(Electric Characteristics) (8)2.1 极限条件(Absolute Maximum Ratings) (8)2.2 工作条件(Recommended Operate Range) (8)2.3 电气特性(General Electric Characteristics)............................... (8)2.4 拼脚定义(Pin Assignment and Description) (9)3 模块应用设计指导(Application note) (14)3.1 功能框图(Function Block description) (14)3.2 工作状态描述(state descriptions) (14)3.3 硬件应用接口概述 (15)3.4 电源和驱动应用接口 (16)3.4.1 电源和驱动管脚定义 (16)3.4.2 主电源供电特性Vbat (17)3.4.3 备用电池RTC................................................................................. ........................... (18)3.4.4 开关机及复位(Power ON/OFF and Reset) (19)3.4.5 充电输入口VCHGIN............................ ................................. .. (20)3.4.6 充电输出口VCHGOUT........................... ................................. . (21)3.4.7 电池检测专用ADC口ADC3/BAT_ID ........................... .. (21)3.4.8 4路LDO输出.................................................... .. (22)3.4.9 LED-驱动 (22)3.4.10 KEY_ LED-驱动 (23)3.4.11电源电路参考设计 (23)3.5 按键接口........................................... . (24)3.6 语音接口........................................... (25)3.6.1模拟音频差分输入主MIC0和辅助MIC1.................................................................................. . (25)3.6.2 模拟音频差分输出受话器REC (26)3.6.3 模拟音频差分输出喇叭SPK (26)3.7 UART 接口 (27)3.8 IIC 接口 (28)3.9 LCD IO驱动为2.8V SPI 接口 (28)3.10 LCD IO驱动为1.8V SPI 接口 (29)3.11 USB 接口..................................... . (30)3.12 SIM 卡接口 (31)3.13 T-F卡接口 (32)3.14 F M 接口 (34)3.15 BT 接口 (34)3.16 通用GPIO接口 (35)3.17 中断口EINT (35)3.18 模拟输入ADC (35)3.19 射频天线接口 (36)4硬件设计指南 (37)4.1 PCB板布局说明 (37)4.2 PCB 关键走线说明......................................................... (37)5 机械特性 (38)5.1 模块机械尺寸 (38)5.2 模块产品 Top-View 视图.......................................... (39)5.3模块供电要求及接法 (41)5.4下载软件 (41)5.5模块开机 (41)5.6 RF测试连接 (41)6 附录 (42)6.1 射频指标 (42)6.2 通信专用术语 (42)1 模块总体介绍1.1 概述及实物图片GW01_GSM&WIFI是一款GSM/GPRS/WIFI无线四频(GSM850/GSM900/DCS1800/PCS1900)工业模块,可以覆盖全球通用GSM频段。

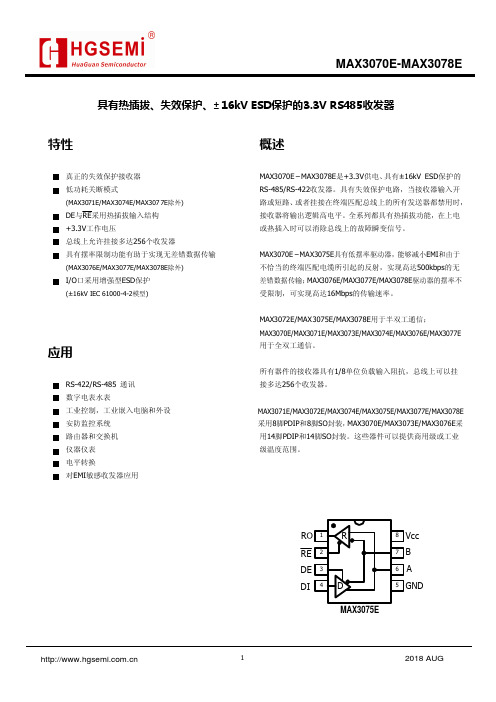

MAX3070E-MAX3078E 及 MAX3075E 型号的 RS-485 RS-422 收发器

具有热插拔、失效保护、±16kV ESD保护的3.3V RS485收发器特性真正的失效保护接收器低功耗关断模式(MAX3071E/MAX3074E/MAX3077E除外)DE与RE采用热插拔输入结构+3.3V工作电压总线上允许挂接多达256个收发器具有摆率限制功能有助于实现无差错数据传输(MAX3076E/MAX3077E/MAX3078E除外)I/O口采用增强型ESD保护(±16kV IEC 61000-4-2模型)应用RS-422/RS-485 通讯数字电表水表工业控制,工业嵌入电脑和外设安防监控系统路由器和交换机仪器仪表电平转换对EMI敏感收发器应用概述MAX3070E –MAX3078E是+3.3V供电、具有±16kV ESD保护的RS-485/RS-422收发器。

具有失效保护电路,当接收器输入开路或短路、或者挂接在终端匹配总线上的所有发送器都禁用时,接收器将输出逻辑高电平。

全系列都具有热插拔功能,在上电或热插入时可以消除总线上的故障瞬变信号。

MAX3070E – MAX3075E具有低摆率驱动器,能够减小EMI和由于不恰当的终端匹配电缆所引起的反射,实现高达500kbps的无差错数据传输;MAX3076E/MAX3077E/MAX3078E驱动器的摆率不受限制,可实现高达16Mbps的传输速率。

MAX3072E/MAX3075E/MAX3078E用于半双工通信;MAX3070E/MAX3071E/MAX3073E/MAX3074E/MAX3076E/MAX3077E 用于全双工通信。

所有器件的接收器具有1/8单位负载输入阻抗,总线上可以挂接多达256个收发器。

MAX3071E/MAX3072E/MAX3074E/MAX3075E/MAX3077E/MAX3078E 采用8脚PDIP和8脚SO封装,MAX3070E/MAX3073E/MAX3076E采用14脚PDIP和14脚SO封装。

MAX774ISDN铃声电源供应器评估套件(EV套件)使用说明书

For free samples & the latest literature: , or phone 1-800-998-8800.For small orders, phone 408-737-7600 ext. 3468._______________General DescriptionThe MAX774 ISDN ring-tone power-supply (IRG) evalua-tion kit (EV kit) provides the high voltages required for implementing a plain old telephone system (POTS) inter-face on ISDN modems and line cards. It is a fully assem-bled and tested board that provides a tightly regulated, -24V output for powering off-hook voice communication and a -70V output for on-hook, ring-tone generation.The EV kit is designed for applications that implement the telephone interface using subscriber line interface circuit (SLIC) ICs, such as the AM79R79 from AMD and comparable products from Lucent, Harris, and other vendors. Its design feeds back the -24V output, achiev-ing tight regulation for clean voice-signal transmission.An economical, off-the-shelf, surface-mount transformer reduces system cost and size. Compact design con-serves board area. High efficiency and reduced quies-cent current make this design the optimal solution for green PC and portable designs.The MAX774 IRG EV kit can also be used to evaluate the MAX775/MAX776. It has a layout that allows modifi-cation for -48V output operation as well as adaptation____________________________Featureso +3V to +16.5V Operating Rangeo Tightly Regulated, -24V Output for Off-Hook Voice Communication o -70V Output Supports a Five-Ringer-Equivalent Load (V IN > 10.5V)o Compact Construction o Proven PC Board Design o Uses Off-the-Shelf Components o Up to 84% Efficiency o 5µA Shutdown Current o Fully Assembled and TestedEvaluates: MAX774/MAX775/MAX776MAX774 ISDN, Ring-Tone, Power-Supply Evaluation Kit________________________________________________________________Maxim Integrated Products119-1287; Rev 0; 9/97______________Ordering InformationE v a l u a t e s : M A X 774/M A X 775/M A X 776MAX774 ISDN, Ring-Tone,Power-Supply Evaluation Kit 2____________________________________________________________________________________________________________________________Quick Start The MAX774 IRG evaluation kit (EV kit) is fully assem-bled and tested. Follow these steps to verify board operation. Do not turn on the power supply until all connections are completed.1)Connect a 12V, 2A power-supply ground terminal to a GND pad on the MAX774 IRG EV kit. 2)Monitor the input current by connecting the power supply's positive terminal to the EV kit’s VIN input through a current meter. 3)Attach a voltmeter across the EV kit’s VIN and GND inputs to monitor input voltage.4)Connect voltmeters to each of the EV kit’s outputs labeled -70V and -24V.5)Connect the SHDN pad to GND.6)Turn on the power supply and slowly increase the voltage to 12V. 7)Monitor the outputs for correct voltage and check the input for typical supply current (20mA at 12V)._______________Detailed DescriptionThe MAX774 IRG EV kit provides the high voltages required for implementing a plain old telephone system (POTS) interface on ISDN modems and other telephone line cards. These boards typically employ ICs such as the AM79R79 Ringing Subscriber Line Interface Circuit (SLIC) from AMD. These ICs generate an analog tele-phone interface by providing both off-hook and on-hook signal transmission, ring-tone generation, and ring-trip detection. Ringing SLIC ICs typically require two high-voltage power-supply inputs. The first is atightly regulated voltage around -24V or -48V for off-hook signal transmission. The second is a loosely regu-lated -70V for ring-tone generation. Servicing a typical five-ringer equivalent load requires a current around 100mA or more from the -70V supply, depending on the SLIC IC and the ring-generation scheme.The MAX774 IRG EV kit can service a SLIC with a five-phone ringer equivalent load (approximately 9W) from a 12V ±10% input. It operates down to 3V, and pro-vides 2.4W from 3.3V and 3.9W from 5V. Use of an inexpensive off-the-shelf transformer, such as the Versa-Pac™ model VP2-0216, provides both high-volt-age outputs from a single inverting DC-DC controller,reducing board area and component costs. Selection of a transformer with multifilar winding enhances cross regulation by improving voltage coupling between the outputs and reducing spiking from leakage inductance.The two outputs are implemented by connecting three pairs of transformer windings in series. The -24V output is obtained by connecting a diode (D1) and output filter capacitor (C9) to the first pair of windings. Feeding back this output achieves tight regulation. The -70V output is derived from the third pair of windings. Loose regulation of this output is obtained by the turns ratio with the -24V output.Circuit OperationThe EV kit schematic (Figure 1) and the MAX774 block diagram in the MAX774/MAX775/MAX776 data sheet show how the circuit works. When the -24V output drops out of regulation, the error comparator in the MAX774 initiates a switching cycle. The P-channel MOSFET (P1) turns on, allowing current to ramp up through the transformer’s lower windings (between the 1/3 tap and ground) and store energy in a magnetic field. When the current through the sense resistor crosses the trip threshold (210mV / 68m Ω= 3.09A), the MOSFET turns off and interrupts the current flow, caus-ing the magnetic field in the transformer to collapse.The transformer forces current through the output diodes, transferring the stored energy to the output fil-ter capacitors. The output filter capacitors smooth the power and voltage delivered to the load. The MAX774waits until it senses the output dropping below the reg-ulation trip point before initiating another cycle. The -24V output is precisely regulated by connecting a volt-age divider, R1 and R2, as shown in Figure 1. The MAX774 regulates the FB pin, keeping it at 0V. The -70V output is regulated using the turns ratios between the -24V and -70V output.Versa-Pac is a trademark of Coiltronics Corp.Output Filter CapacitorsThe positive pin of the filter capacitor for the -70V out-put is connected to the -24V output rather than ground to simplify board layout, enhance stability, allow the use of a lower-cost lower-voltage capacitor, and improve cross-regulation. Ripple on the -24V output is about 200mV and can be reduced further using a capacitor with lower ESR. The Sanyo MV-GX series is recom-mended.__________Applications InformationThis section is intended to aid in transferring the EV kit design to a finished product.Transformer SelectionChoose a transformer with an inductance around 10µH to 15µH per winding, with a saturation-current rating greater than 3A. The MAX774 IRG EV kit uses Coiltronics’ Versa-Pac model VP2-0216. This economi-cal, off-the-shelf transformer uses two trifilar windings for superior coupling and improved regulation of the-70V output. Dale’s LPE6855-100MB and LPE6562-100MB also work, but have different footprints and pinouts and require almost double preloading.If lower output power is desired, increase the current-sense-resistor value and transformer inductance propor-tionally. For example, when reducing power capability to one-half of the current design, double the current-sense resistor to around 130m Ωand the transformer induc-tance per winding to around 20µH to 33µH.Cross RegulationThe -70V output is derived from the -24V output by stacking pairs of windings in an autotransformer config-uration. Cross regulation between the two outputs, how-ever, has limitations. In the on-hook and ringing case,when the -24V output is lightly loaded with the -70V out-put heavily loaded, the -70V output droops. In the off-hook case with the -24V output heavily loaded and the -70V output lightly loaded, the -70V output rises. These effects occur in all transformer-based flyback solutions when the outputs are dissimilarly loaded.Evaluates: MAX774/MAX775/MAX776MAX774 ISDN, Ring-Tone, Power-Supply Evaluation Kit_______________________________________________________________________________________3Figure 1. MAX774 IRG EV Kit SchematicE v a l u a t e s : M A X 774/M A X 775/M A X 776PreloadingUse preloading at the outputs to keep the -70V output in regulation. For designs servicing a five-ringer equiva-lent load, use the following preloads. For the off-hook case, only a couple hundred microamperes are neces-sary to hold down the -70V output. This can be achieved using either a 330k Ωresistor (R4, Figure 1) or zener diode (Figure 2b). For the on-hook case, draw approximately 5.5mA from the -24V output to hold up the -70V output. This 5.5mA can be drawn continuously using two 8.2k Ωresistors (R5 and R6), or intermittently using a transistor to gate the preload while the phone is ringing (Figure 2c). The transistor can be controlled using a microcontroller input/output line, or it can be decoded from the control signals of the AM79R79.To optimize performance or efficiency in applications servicing a different ringer-equivalent load, use the pre-loading curves for guidance (Figure 3 and 4). UseFigure 3 to determine the minimum preloading needed on the -24V output for adequate regulation of the -70V output while the SLIC IC is ringing phones (on-hook case). For example, approximately 50mA is required for a two-phone load. First, follow the vertical line from the -70V output axis up to curve A or B. Next, follow the hor-izontal lines to the corresponding point on the -24V Output Minimum Load axis, in this case 2.5mA using curve A. Preload the -24V output with this current using a resistor R = V / I or 24V / 2.5mA = 9.6k Ω. Round down to the nearest standard value (9.1k Ω). The power rating of the resistor must exceed V 2 / R = 24V 2 / 9.1k Ω=63mW.Use Figure 4 to determine the preloading needed to hold down the -70V output when the -24V output is heavily loaded during off-hook communication. This preloading is intended to protect the AM79R79. The VBAT1 pin of this SLIC IC has a -75V operational range and a -80V absolute maximum rating. If a zener diode is used for preloading, set the zener voltage rating suf-ficiently above the regulation set point to prevent unnecessary current draw.Efficiency, Quiescent Current,and PreloadingThe MAX774 is a pulse-frequency-modulation (PFM)controller designed primarily for use in portable appli-cations. It improves efficiency and reduces quiescent current by switching only as needed to service the load. Prior to preloading, this circuit’s efficiency can be up to 84%, and quiescent current is around 170µA.Resistor preloading reduces efficiency and increasesMAX774 ISDN, Ring-Tone,Power-Supply Evaluation Kit 4_______________________________________________________________________________________Figure 2. Fixed and Switchable Preloading SchemesFigure 3. Cross Regulation for -24V Output Preload Selection (on-hook case)quiescent current. Switchable preloading on the -24V output (Figure 2c), combined with zener clamping of the -70V output (Figure 2b) can be used to reduce cir-cuit current consumption.Current Limiting and Overload ProtectionNeither this EV kit nor competing solutions have a prac-tical level of current protection at the outputs. Use the current-limiting features built into the AM79R79 SLIC IC as described in the data sheet for that product. Using PolySwitch™ resettable fuses at the outputs adds pro-tection to the system at little expense (Figure 5). With a PolySwitch, use faster models such as the surface-mount SMD series.The MAX774 uses an internal current-sense compara-tor that provides pulse-by-pulse input current limiting.However, like competing flyback solutions, this trans-lates to power (and not current) limiting at the output.As the output voltage pulls down during overload, the output current can become high (essentially P IN(MAX)/V OUT ) until inefficiency and parasitic resistance in the circuit dominate. Since the circuit is designed for 9W (min) output to service a five-phone load, short-circuit currents can reach several amperes.Stability and Feedback CompensationThe MAX774 IRG EV kit has been compensated and tested for a full range of loads. When implementing the circuit, ensure stability by following the EV kit board and component list (see PC Board Layout section). Use NPO or COG ceramic capacitors for C1 and C2.Connect the ground terminal of the -70V filter capacitor to the -24V output rather than to ground. (This also improves transient response and simplifies layout.)The MAX774 uses a PFM control scheme that adjusts the pulse rate to regulate power and voltage to the load. Pulse spacing decreases with increasing load. As the pulses begin touching each other, the circuit transi-tions into continuous-conduction mode. Stable transi-tion into continuous conduction occurs through pulse grouping, with gaps less than two cycles wide between groups, and output ripple no larger than the single-cycle voltage ripple at light loads (Figure 6).Poor PC board layout or improper compensation can cause instability by corrupting the feedback signals.Instability is identified by either grouped pulses, large gaps between groups, or output ripple larger than the single-cycle voltage ripple (Figure 7). It can cause increased audio interference. Test for instability with aEvaluates: MAX774/MAX775/MAX776MAX774 ISDN, Ring-Tone, Power-Supply Evaluation Kit_______________________________________________________________________________________5Figure 4. Cross Regulation for -70V Output Preload Selection (off-hook case)Figure 5. Overload Protection Using Raychem PolySwitch Resettable FusesPolySwitch is a trademark of Raychem Corp.M A X 774I R G E V F I G 065µs/divV OUT1 = -23.6V, V OUT2 = -70V, I OUT2 = -30mA, V IN = 9VA: MOSFET DRAIN, 20V/divB: V OUT1, 100mV/div, AC COUPLED C: TRANSFORMER CURRENT, 1A/divFigure 6. Normal Light-Load Switching WaveformsE v a l u a t e s : M A X 774/M A X 775/M A X 7769V input by applying a 5mA to 10mA load on the -24V output and then sweeping the -70V output to full-load. If instability occurs due to errors in the design if a pro-duction board, try removing C7 and C8.If the feedback resistors are changed, adjust the com-pensation capacitors. In general, M x C1 x R1 = C2 x R2with C2 around 1nF provides the best results, where M ranges from 0.5 to 1.PC Board LayoutUse of the tested PC board design is strongly recom-mended. Components can be placed closer together to conserve space. Observe the following guidelines in PC board design:1)Place the current-sense resistor (R3) within 0.2in.(5mm) of the MAX774, directly between the V+ and CS pins. The V+ and reference-bypass capacitors (C3 and C4) must be placed as close as possible to their respective pins. Figure 8 shows the recom-mended layout and routing for these components. 2)Place the voltage-feedback resistors (R1 and R2)and compensation capacitors (C1 and C2) within 0.2in. (5mm) of the MAX774’s FB pin. Keep high-current traces and noisy signals, such as EXT, away from FB. On multilayer boards, if inner ground or power planes are thinly separated from the top-side copper, use small cutouts in the ground plane under the FB node to reduce stray capacitance and capacitive coupling. 3)Make high-power traces, highlighted in the EV kit schematic (Figure 1), as short and as wide as possi-ble. Make the supply-current loop (formed by C5,C6, R3, P1, and L1) and output current loops (L1,D1, and C9 for the -24V output; L1, D2, C9, and C10for the -70V output) as tight as possible to reduce radiated noise. 4)Route transformer L1’s ground pins (C5, C6, and C10) to a common ground point in a star ground configuration using top-side copper fill as a pseudo-ground plane. On multilayer boards, use the star ground as described, and connect it to the inner ground plane using vias. Build up separate star grounds for the power components and controller IC (Figure 9), and then couple them together through the back side of the board using several vias.5)For reduced noise and improved heat dissipation,keep the extra copper on the PC board’s compo-nent and solder sides, rather than etching it away,and connect it to ground for use as a pseudo-ground plane.DC-DC Converter Placementand Audio InterferencePrevent interference through careful board and system design. Place the DC-DC converter and high-speed CMOS logic on a corner of the PC board, away from sensitive analog circuitry such as audio-signal pream-plifier stages (Figure 10). In very compact designs, use localized shielding around sensitive analog stages. Use a separate ground plane for analog circuitry. Where necessary, reduce supply ripple to sensitive analog stages by using LC Pi filters or specialized, low-dropout linear regulators. Tiny, inexpensive linear regulators,such as the SOT23 MAX8863 and µMAX MAX8865, are designed specifically for this purpose. These solutions are commonly used in cellular phones and other portable communications devices.MAX774 ISDN, Ring-Tone,Power-Supply Evaluation Kit 6_______________________________________________________________________________________M A X 774I R G E V F I G 07250µs/divV OUT1 = -23.6V, V OUT2 = -70V, I OUT2 = -30mA, V IN = 9V A: MOSFET DRAIN, 20V/divB: V OUT1, 100mV/div, AC COUPLED C: TRANSFORMER CURRENT, 1A/divC2 REMOVEDFigure 7. Unstable Switching Waveforms from Improper Compensation or Board DesignFigure 8. Recommended Placement and Routing of R3, C3,and C4Modification for -48V and -70V OutputsThe MAX774 IRG EV kit board design allows leeway for adapting the circuit for -48V and -70V outputs. Perform the following steps for implementation:1)Cut the trace from the transformer’s 1/3 tap to theoutput diode, and then solder a wire jumper from the transformer’s 2/3 tap to the diode (D2) (Figure 11).2)Swap output filter capacitors C9 with C10. Be sure toconnect them with the correct polarity. This exchange ensures that the output filter capacitors have voltage ratings exceeding their respective outputs.3)Replace voltage-feedback resistor R2 with a 31.6k Ωresistor.4)Replace compensation capacitor C1 with a 330pFceramic capacitor.5)Change R5 and R6 to 16k Ωresistors.Evaluates: MAX774/MAX775/MAX776MAX774 ISDN, Ring-Tone, Power-Supply Evaluation Kit_______________________________________________________________________________________7SWITCHING DC-DCCONVERTERSSHIELDING (IF NEEDED)DIGITAL LOGIC= LC Pi FILTERS OR LDO LINEAR REGULATORFigure 10. Place the DC-DC converter and CMOS logic away from sensitive analog circuitry.PLACE POWER COMPONENTS CLOSE TOGETHER;MAKE POWER TRACES SHORT AND WIDE.LEAVE THE EXTRA FRONT- AND BACK-SIDE COPPER ON THE BOARD AS A PSEUDO-GROUND PLANE.PLACE GROUND PINS OF POWER COMPONENTS CLOSE TOGETHER AND ORIENT TO CONVERGE, FORMING A STAR GROUND.PLACE VOLTAGE-FEEDBACK COMPONENTS AS CLOSE TO THE FB PIN AS POSSIBLE.PLACE BYPASS CAPACITORS CLOSE TO THE REF AND V+ PINS; ORIENT AS SHOWN.TIE THE IC GROUND AND POWER STAR GROUND TOGETHER USING VIAS AND A WIDE BACK-SIDE GROUND TRACE. ON MULTILAYER BOARDS, TIE INTERIOR GROUND PLANES TO THE POWER STAR GROUND.PLACE CURRENT-SENSE RESISTOR R3 WITHIN 0.2IN. OF CS AND V+ PINS.Figure 9. Key Layout FeaturesE v a l u a t e s : M A X 774/M A X 775/M A X 776MAX774 ISDN, Ring-Tone, Power-Supply Evaluation Kit Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.8_____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©1997 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Modification for European ApplicationsApplications targeted for Europe may require a lower voltage on the -70V output to meet European safety regulations. In such cases, modify the circuit for -48V and -70V outputs as described previously, then change the feedback resistor R2 to reduce output voltages to -43V and -65V. Add a clamping zener to preload the high-voltage output. Since the MAX774 regulates the FB pin to 0V, R2 will be:R2 = (V REF / V OUT ) x R1where V REF = 1.5V.Adjust C1 so that R1C1 = R2C2. Verify correct com-pensation by examining stability over all loading combi-nations, especially with the -43V output lightly loaded and the -65V output moderately and heavily loaded.Suggested values are R1 = 1M Ω, C1 = 330pF, R2 =34.8k Ω, C2 = 1000pF.RECONNECT TRACE HERECUT TRACE HEREFigure 11. PC Board Changes for -48V and -70V OperationFigure 12. MAX774 IRG EV Kit Component Placement Guide (Top Silkscreen)Figure 13. MAX774 IRG EV Kit PC Board Layout—Component SideFigure 14. MAX774 IRG EV Kit PC Board Layout—Solder Side1.0"1.0" 1.0"。

LT3960 I2C至CAN物理收发器评估电路EVAL-LT3960-AZ 说明书

1Rev. 0DESCRIPTIONLT3960I 2C to CAN-PhysicalTransceiverEvaluation circuit EVAL-LT3960-AZ features the L T ®3960, an I 2C to CAN-Physical transceiver in a 10-lead plastic MSOP package. EVAL-LT3960-AZ consists of two ICs configured in the master and slave mode using selectable jumpers, JP1 and JP3. The board is designed to be easily snapped apart at the center , separating two circuitries.The LT3960 I 2C to CAN-Physical transceiver is used to send and receive I 2C data through harsh or noisy envi-ronments at up to 400kb/s using the CAN-Physical layer for differential signaling over twisted pair connections. The SDA and SCL data lines are converted to differential signals and are shared between devices connected to the bus. This allows for the physical separation of the I 2C source and I 2C receiver .All registered trademarks and trademarks are the property of their respective owners.PERFORMANCE SUMMARYThe first LT3960 is connected to the I 2C master (I 2C-compatible microcontroller). The second LT3960 should be connected to the first LT3960 by two twisted pairs. It regenerates the I 2C bus locally for one or more I 2C slave devices. The LT3960 devices transmit the clock signal in only one direction, from master to slave. Bidirectional communication of the data signal is always permitted.The LT3960 data sheet gives a complete description of the parts, their operation, and application information. The data sheet must be read in conjunction with this user guide for the evaluation circuit EVAL-LT3960-AZ. The LT3960EMSE is assembled in a 10-lead MSOP package.Design files for this circuit board are available .Specifications are at T A = 25°CSYMBOL PARAMETER CONDITIONMIN TYP MAX UNIT V IN Input VoltageV IN Tied to V CC , 3.3V Range (Jumper JP2, JP4: V IN = V CC ) V IN Tied to V CC , 5V Range (Jumper JP2, JP4: V IN = V CC ) V CC Regulated Internally from V IN (Jumper JP2, JP4: V IN ≠ V CC )3 4.5 4 3.3 53.6 5.5 60V V V V MSTR , V SLV , V SHDN EN/MODE VoltageMaster Mode (Jumper JP1, JP3: MASTER) Slave Mode(Jumper JP1, JP3: SLAVE) Low Power Shutdown Mode(Jumper JP1, JP3: OFF)2 0.7 05 2 0.7V V V f CLK Clock Frequency400kHz V CMBus Common Mode Voltage V CC = 3.3VV CC = 5V±25 ±36V VQUICK START PROCEDUREEVAL-LT3960-AZ can be powered by a voltage source between 4V and 60V due to the integrated LDO in the LT3960. The LDO regulates the input from the V IN pin between 4V and 60V to 3.3V on the V CC pin from which the transceivers and bus lines are powered. Alternatively, the EVAL-LT3960-AZ can be powered from a supply volt-age of 3.3V or 5V on VIN, bypassing the LDO by shorting VCC to VIN using jumpers JP2 and JP4.One procedure for using the EVAL-LT3960-AZ is described as follows:1. Launch Arduino IDE.2. Connect two Linduinos to the computer via USB.3. Download the Linduino code from the EVAL-LT3960-AZ webpage.4. Upload the code to the master and slave Linduinosaccordingly.5. Break the EVAL-LT3960-AZ into two separate boardsby applying force to the horizontal scoring line. 6. Use 2 twisted pairs of small wires to connect CANSCLx1and CANSCLx2; CANSDAx1 and CANS-DAx2.7. Connect GND1 and GND2 pins on two boards using asmall wire (optional).8. Connect SLC, SDA, GND pins from the master (slave)Linduino to SLC1, SDA1, GND1 (SLC2, SDA2, GND2) of the EVAL-LT3960-AZ, respectively.9. With input power off, connect the first (second) inputpower supply to VIN1 and GND1 (VIN2 and GND2) of the EVAL-LT3960-AZ.10. Turn on input power supplies.11. Open the serial monitor associated with the slaveLinduino and check the received message.2Rev. 0QUICK START PROCEDUREFigure 1. Quick Start Procedure Setup Drawing for EVAL-LT3960-AZ3Rev. 04Rev. 0PARTS LISTTEST RESULTSFigure 2. Linduino COM Terminal Window of the Slave DeviceITEM QTY REFERENCE PART DESCRIPTIONMANUFACTURER/PART NUMBER Required Circuit Components12C1, C5CAP ., 1µF, X7R, 50V, 10%, 0603YAGEO, CC0603KRX7R9BB10524C2, C4, C7, C8CAP ., 4700pF, X7R, 50V, 10%, 0402MURATA, GRM155R71H472KA01D 32C3, C6CAP ., 2.2µF, X7S, 10V, 10%, 0603, AEC-Q200TDK, CGA3E3X7S1A225K080AB 42R1, R8RES., 10k, 1%, 1/10W, 0603, AEC-Q200VISHAY, CRCW060310K0FKEA 58R2, R4, R6, R7, R9, R12, R13, R14RES., 60.4Ω, 1%, 1/8W, 0805, AEC-Q200PANASONIC, ERJ6ENF60R4V 64R3, R5, R10, R11RES., 4.99k, 1%, 1/10W, 0603, AEC-Q200PANASONIC, ERJ3EKF4991V 72U1, U2IC, 12C TO DUAL CAN TRANSCEIVER, MSOP-10ANALOG DEVICES, LT3960EMSE#PBF Hardware: For Demo Board Only18E1-E8TEST POINT , TURRET , 0.064" MTG. HOLE, PCB 0.062" THK MILL-MAX, 2308-2-00-80-00-00-07-022J1, J3CONN., TERM BLOCK, 5 POS, 2.54mm, ST , THT , SIDE ENTRY, GREEN ON-SHORE TECHNOLOGY, OSTVN05A15032J2, J4CONN., HDR, MALE, 1x2, 2.54mm, VERT , ST , THT WURTH ELEKTRONIK, 6130021112142JP1, JP3CONN., HDR, MALE, 2x3, 2mm, VERT , ST , THT WURTH ELEKTRONIK, 6200062112152JP2, JP4CONN., HDR, MALE, 1x3, 2mm, VERT , ST , THTWURTH ELEKTRONIK, 62000311121618TP1-TP18TEST POINT , 1POS, 0.040" MTG. HOLE, 2.54mm DIA x 4.57mm L, THT , BLACKKEYSTONE, 500174XJP1, XJP2, XJP3, XJP4CONN., SHUNT , FEMALE, 2 POS, 2mmWURTH ELEKTRONIK, 608002134215Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.SCHEMATIC DIAGRAMc o m6Rev. 0ANALOG DEVICES, INC. 202103/21ESD CautionESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.Legal Terms and ConditionsBy using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONL Y. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer , assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer , their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer . Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT . ADI SPECIFICALL Y DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT , OR CONSEQUENTIAL DAMAGES RESUL TING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT . Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW . This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.。

双向可控硅及其触发电路精编版

双向可控硅及其触发电路双向可控硅是一种功率半导体器件,也称双向晶闸管,在单片机控制系统中,可作为功率驱动器件,由于双向可控硅没有反向耐压问题,控制电路简单,因此特别适合做交流无触点开关使用。

双向可控硅接通的一般都是一些功率较大的用电器,且连接在强电网络中,其触发电路的抗干扰问题很重要,通常都是通过光电耦合器将单片机控制系统中的触发信号加载到可控硅的控制极。

为减小驱动功率和可控硅触发时产生的干扰,交流电路双向可控硅的触发常采用过零触发电路。

(过零触发是指在电压为零或零附近的瞬间接通,由于采用过零触发,因此需要正弦交流电过零检测电路)双向可控硅分为三象限、四象限可控硅,四象限可控硅其导通条件如下图:总的来说导通的条件就是:G极与T1之间存在一个足够的电压时并能够提供足够的导通电流就可以使可控硅导通,这个电压可以是正、负,和T1、T2之间的电流方向也没有关系。

因为双向可控硅可以双向导通,所以没有正极负极,但是有T1、T2之分再看看BT134-600E的简介:(飞利浦公司的,双向四象限可控硅,最大电流4A)推荐电路:为了提高效率,使触发脉冲与交流电压同步,要求每隔半个交流电的周期输出一个触发脉冲,且触发脉冲电压应大于4V ,脉冲宽度应大于20us.图中BT 为变压器,TPL521 - 2 为光电耦合器,起隔离作用。

当正弦交流电压接近零时,光电耦合器的两个发光二极管截止,三极管T1基极的偏置电阻电位使之导通,产生负脉冲信号,T1的输出端接到单片机80C51 的外部中断0 的输入引脚,以引起中断。

在中断服务子程序中使用定时器累计移相时间,然后发出双向可控硅的同步触发信号。

过零检测电路A、B 两点电压输出波形如图2 所示。

过零触发电路电路如图3 所示,图中MOC3061 为光电耦合双向可控硅驱动器,也属于光电耦合器的一种,用来驱动双向可控硅BCR 并且起到隔离的作用,R6 为触发限流电阻,R7 为BCR 门极电阻,防止误触发,提高抗干扰能力。

TPS65023资料

PRODUCT PREVIEW

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW

ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

VI Input voltage range on all pins except AGND and PGND pins with respect to AGND Current at VINDCDC1, L1, PGND1, VINDCDC2, L2, PGND2, VINDCDC3, L3, PGND3 Peak current at all other pins Continuous total power dissipation

°C

125

°CLeabharlann –65 to 150°C