【通俗易懂】浅谈Delta-Sigma之工作原理

高精度delta-sigmaad转换器的原理及其应用

高精度Delta-Sigma A/D转换器的原理及其应用本次在线座谈主要介绍TI的高精度Delta-Sigma A/D转换器的原理及其应用,Delta-Sigma转换器的特点是将绝大多数的噪声从动态转移到阻态,通常Delta-Sigma转换器被用于对成本与精度有要求的低频场合。

本文首先将对TI的高精度Delta-Sigma A/D转换器进行综述性介绍,而后将介绍噪声的测量及芯片ADS1232等。

Delta-Sigma转换器综述Delta-Sigma转换器是采用超采样的方法将模拟电压转换成数字量的1位转换器,它由1位ADC、1位DAC与一个积分器组成,见图1。

Delta-Sigma转换器的优点表现在低成本与高分辨率,适合用于现在的低电压半导体工业的生产。

Delta-Sigma转换器组成Delta-Sigma转换器由差分放大器、积分器、比较器与1位的DAC组成,输入信号减去来自1位DAC 的信号将结果作为积分器的输入,当系统得到稳定工作状态时,积分器的输出信号是全部误差电压之和,同时积分器可以看作是低通滤波器,对噪声有-6dB的抑制能力。

积分器的输出用1位ADC来转换,而后比较器将输出数字1和0的位流。

DAC将比较级的输出转换为数字波形,回馈给差分放大器。

Delta-Sigma转换器原理详述积分器将量化噪声伸展到整个频带宽度,从而使噪声成型,而滤波器可以过滤掉绝大多数的成型噪声。

有几个误差源会降低整个系统的效果,为了满足ADC的输入范围,很多信号要求一些放大电路和电平偏移电路,有时放大器在ADC的内部,有时使用外部放大器。

无论是哪一种情况,放大器电压、电压漂移、输入偏置电流或采样噪声将引入误差信号。

为了得到精确的ADC转换结果,放大器的误差应该通过调整来消除或减少。

积分器对输入低频或直流信号内置一个低通滤波器,从而极大地降低了通道内的噪声。

典型的半导体放大器的噪声分为两个部分,1/F噪声和对地噪声,Delta-Sigma ADC的主要应用是在低频场合,因此1/F噪声的影响占主要地位。

sigmadeltaadc原理

sigmadeltaadc原理

Σ-Δ模数转换是一种典型的数模转换技术,它利用非线性微分模拟器(Differentiator)把模拟信号转变为进行离散采样的差分脉冲。

Σ-Δ转换技术

有很高的灵敏度,但同时也有一定的复杂性,因为需要大量的计算和设备限制。

Σ-Δ模数转换器中,Σ表示累加器(Accumulator),Δ表示微分器(Differentiator)。

它通常有两个部分,累加(Accumulation)和微分(Differentiation),一般采用了高速積分和微分技术(Sigma-Delta Topology),来完成模拟脉冲的转换。

其中累加(Accumulation)实现的是采样技术,原来的模拟信号在特定的时刻取得一个采样值;累加(Accumulation)把这些采样值累加到心跳的末端;微分(Differentiation)实现的是离散化技术,它使用如

此精密的采样技术,以在心跳的末端释放不同大小的脉冲,从而离散化地表示原始模拟信号。

Σ-Δ模数转换器使得可以使用很少的采样来代表原始模拟信号,但其本质原理却是可以植根于模拟信号的数字信息量的增加,即出现精度的提高。

Σ-Δmodulators的发展为模拟-数字转换技术提供了可靠的仪表精度以及脉冲

转换的灵活性。

deltasigma dac工作原理

deltasigma dac工作原理Delta-Sigma DAC(数字-ΔΣ DAC)是一种数字-to-analog converter (数字到模拟转换器),常用于将数字信号转换为模拟信号。

下面是Delta-Sigma DAC的工作原理的详细解释:Delta-Sigma调制:Delta-Sigma(ΔΣ)调制是一种将低比特的数字信号转换为高比特的数字信号的技术。

它通过过采样和差分编码来实现,将原始的低分辨率信号进行高频率采样,然后通过差分编码提高了信号的有效分辨率。

过采样:Delta-Sigma DAC在输入信号之前对其进行过采样,即以高于Nyquist频率的采样率对输入信号进行采样。

这有助于将信号的噪声推向高频区域,以便后续的滤波可以更有效地去除。

Delta模数调制器:过采样后的信号经过Delta模数调制器,该模块负责将输入信号进行ΔΣ调制。

这意味着模数调制器会在高频率上产生一个ΔΣ调制的数字信号,这个信号在频率域上具有高精度。

数字滤波器:Delta模数调制器的输出被送入数字滤波器,以去除高频噪声。

这个滤波器通常是一个低通滤波器,其目标是保留有效信号并去除噪声。

数模转换:过滤后的信号被送入数模转换器,将数字信号转换为模拟信号。

在Delta-Sigma DAC中,这个过程也被称为Delta-Sigma 解调,它通过反馈回到模数调制器来补偿误差。

滤波:最后,模拟信号通过一个模拟滤波器,以进一步去除高频噪声,并得到最终的模拟输出信号。

总体而言,Delta-Sigma DAC通过过采样、Delta-Sigma调制和数字滤波来提高信号的有效分辨率,从而实现高精度的数字到模拟转换。

这种方法在音频和其他高精度应用中得到广泛应用。

1。

delta-sigma adc原理

delta-sigma adc原理Delta-Sigma ADC是一种常用的模数转换器,其原理基于Δ-Σ调制(Delta-Sigma Modulation)。

它应用广泛,特点是可实现高分辨率、低失真和高动态范围的模数转换。

1.简介Delta-Sigma ADC是将模拟信号转换为数字信号的一种技术。

它使用增量调制技术将输入信号转换为脉冲序列,再通过积分器形成模拟信号。

然后通过数字滤波器对模拟信号进行滤波,最后得到输出数字信号。

2.增量调制增量调制是Delta-Sigma ADC的核心部分。

它通过比较输入信号与量化器输出信号的差值,生成Δ-Σ调制的输出脉冲序列。

在增量调制中,使用一个比较器将输入信号与量化器输出信号进行比较。

当输入信号大于量化器输出信号时,比较器输出1;当输入信号小于量化器输出信号时,比较器输出-1。

这样,通过不断比较输入信号与量化器输出信号,就可以得到Δ-Σ调制的输出脉冲序列。

3.积分器在增量调制过程中,由于比较操作是离散的,会导致增量调制的输出脉冲序列带有高频成分。

为了消除这些高频成分,需要使用积分器将输出脉冲序列转换为模拟信号。

积分器通过对输出脉冲序列进行积分,得到与输入信号相关的模拟信号。

积分器可以使用电容器和运算放大器等元件来实现。

4.数字滤波器模拟信号经过积分器转换为数字信号后,仍然存在一些高频噪声。

为了滤除这些噪声,需要使用数字滤波器对数字信号进行滤波。

最常用的数字滤波器是低通滤波器,可以通过抽取和重插值的方式实现。

5.数据处理通过数字滤波器滤波后得到的输出数字信号可以用于后续的数据处理。

可以对其进行采样、量化和编码等操作,以得到最终的数字输出结果。

6.优势Delta-Sigma ADC具有以下优势:-高分辨率:通过增量调制和数字滤波器,可以实现较高的分辨率。

-低失真:增量调制和数字滤波器的特性可以降低噪声和失真。

-高动态范围:Delta-Sigma ADC可以实现比较大的动态范围,适用于高精度应用场景。

delta-sigma ADC原理

Σ Δ模数转换器基本原理及应用(1)北京服装学院 (100029) 张亮孟庆昌华正权中国科学院长春物理研究所 (130021) 高光天摘要本文从过采样、噪声整形、数字滤波和采样抽取等概念入手, 介绍了Σ Δ模数转换器的工作原理和特性, 并给出了Σ Δ模数转换器与微机接口的应用实例。

关键词Σ ΔADC 过采样噪声整形数字滤波采样抽取随着超大规模集成电路制造水平的提高, 近年来Σ Δ模数转换器(以下简称ADC)正以其分辨率高、线性度好、成本低等特点得到越来越广泛的应用, 特别是在既有模拟又有数字的混合信号处理场合更是如此。

本文将简要介绍Σ Δ ADC的基本原理及应用。

一、Σ Δ ADC基本原理Σ Δ ADC以很低的采样分辨率(1位)和很高的采样速率将模拟信号数字化, 通过使用过采样、噪声整形和数字滤波等方法增加有效分辨率, 然后对ADC输出进行采样抽取处理以降低有效采样速率。

Σ Δ ADC 的电路结构是由非常简单的模拟电路(一个比较器、一个开关、一个或几个积分器及模拟求和电路)和十分复杂的数字信号处理电路构成。

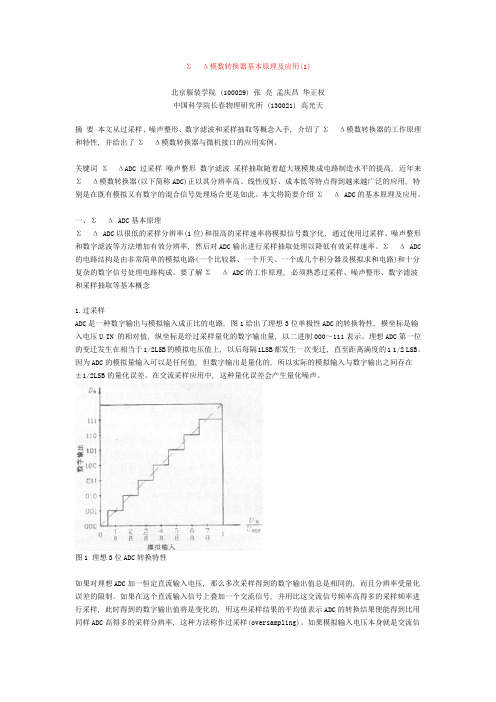

要了解Σ Δ ADC的工作原理, 必须熟悉过采样、噪声整形、数字滤波和采样抽取等基本概念1.过采样ADC是一种数字输出与模拟输入成正比的电路, 图1给出了理想3位单极性ADC的转换特性, 横坐标是输入电压U IN 的相对值, 纵坐标是经过采样量化的数字输出量, 以二进制000~111表示。

理想ADC第一位的变迁发生在相当于1/2LSB的模拟电压值上, 以后每隔1LSB都发生一次变迁, 直至距离满度的1 1/2 LSB。

因为ADC的模拟量输入可以是任何值, 但数字输出是量化的, 所以实际的模拟输入与数字输出之间存在±1/2LSB的量化误差。

在交流采样应用中, 这种量化误差会产生量化噪声。

图1 理想3位ADC转换特性如果对理想ADC加一恒定直流输入电压, 那么多次采样得到的数字输出值总是相同的, 而且分辨率受量化误差的限制。

deltasigma小数分频dither原理

deltasigma小数分频dither原理Delta Sigma 小数分频是一种将高频信号降频为低频信号的数字信号处理技术。

Dither(抖动)则是在数字信号处理过程中加入一定的噪音,以改善信号的量化误差。

本文将详细介绍Delta Sigma 小数分频和dither 的原理和应用。

一、Delta Sigma 小数分频的原理Delta Sigma(ΔΣ)调制是一种高效的数字信号处理技术,通过将高频信号采样、量化和编码,然后再将编码结果通过可变的数字序列进行调制,最终转换为低频信号。

其主要原理可以简单概括为以下几个步骤:1.采样:将待分频的高频信号进行采样,并将采样结果通过一个低通滤波器进行滤波,以去除高频成分形成基带信号。

2.量化:通过一个高分辨率的ADC(模数转换器)将基带信号进行量化,得到一个比特序列。

量化的目标是尽量减小误差,并保持足够的动态范围。

3.利用反馈和比较器:通过一个比较器将量化的结果与反馈信号进行比较,得到一个差值。

4.可变的数字序列:这个差值将作为一个可变的数字序列,控制下一个采样周期中采样的时刻和幅度。

5.重复以上过程:重复以上过程直到最新的差值足够小,或者达到设定的停止条件。

Delta Sigma 小数分频的主要特点是需要较高的过采样率,即采样频率要远高于分频后的输出频率。

这样可以利用高采样率降低量化误差,并通过反馈调制得到准确的分频结果。

二、Dither 的原理Dither 是一种在数字信号处理过程中引入一定程度的噪音的技术,主要用于解决量化误差带来的问题。

在数字信号处理中,由于信号是以离散的方式进行采样和量化,因此可能会出现量化误差。

量化误差是指将连续的模拟信号转换为离散的数字信号时所引入的误差。

这种误差会导致信号失真和动态范围的减小。

Dither 的作用是通过引入一定程度的噪音,将量化误差转化为随机的噪音,从而改善信号的质量。

具体原理如下:1.加入噪音:在量化过程中,将一个随机的、均匀分布的噪音序列加到待量化信号上。

delta-sigma调制原理 通俗易懂讲义

delta-sigma调制原理通俗易懂讲义

Delta-Sigma 调制是一种将模拟信号转换为数字信号的技术。

它的基本思想是通过对输入信号进行过采样和滤波,将其转换为一位数字信号。

下面是一个简单的Delta-Sigma 调制原理的讲义:

1. 过采样:Delta-Sigma 调制的第一步是对输入信号进行过采样。

这意味着我们以比输入信号带宽高得多的频率对其进行采样。

例如,如果输入信号的带宽为10 kHz,我们可能以100 kHz 或更高的频率进行采样。

2. 量化:接下来,我们对采样后的信号进行量化。

在Delta-Sigma 调制中,我们通常使用一位量化,即将信号量化为两个电平之一,例如+1 或-1。

3. 滤波:量化后的信号通过一个低通滤波器。

这个滤波器的作用是平滑量化误差,从而减少数字信号中的噪声。

4. 反馈:滤波后的信号被反馈到量化器。

这个反馈信号与输入信号相减,产生一个误差信号。

5. 调整:误差信号被用来调整量化器的阈值。

如果误差信号为正,量化器的阈值将增加,使更多的采样值被量化为+1。

如果误差信号为负,量化器的阈值将降低,使更多的采样值被量化为-1。

通过这种方式,Delta-Sigma 调制不断调整量化器的阈值,以最小化误差信号。

最终,输出的数字信号非常接近输入信号,并且具有较低的噪声和较高的精度。

Delta-Sigma 调制常用于模数转换器(ADC)中,以将模拟信号转换为数字信号。

它也用于数字信号处理中,例如在音频编码中,以实现高质量的数字音频。

Delta-Sigma(Σ-Δ) AD转换器原理及PSPICE仿真

DeltaSigma AD 转换器原理及 PSPICE 仿真作者:陈拓 2011年1月5日 chentuo@概述DeltaSigma 或ΣΔ模数转换器具有高分辨率、高集成度、成本低和使用方便的特点, 近年来得到广泛的应用。

特别是ΣΔ ADC 易于用 FPGA 实现,逻辑电路可以完全集成在 FPGA内部,只需要很少的外围器件,使 FPGA能直接进行混合信号处理,由于 FPGA可扩 展和可重配置的特性,特别适合做产品研发和需要多个 AD 转换器的场合。

本文通过 PSPICE 仿真介绍ΣΔ模数转换器的工作原理。

为便于理解原理本文中只有 原理性的描述,没有高深的数学推导。

DeltaSigma 即大写的希腊字母ΣΔ。

在数学和物理学中,大写的希腊字母德尔塔 delta (Δ)代表差或变化,大写的希腊字母西格玛 sigma (Σ)代表求和。

有时称其为 SigmaDelta,或 ΣΔ。

在 Δ Σ 转换器中,模拟输入电压信号被连接到一个积分器的输入端。

在输出端对应输 入大小产生一个电压变化率,或者斜坡。

然后用比较器将该斜坡电压与地电位(0V)进行比“高” 较。

比较器的行为就像1 位 AD 转换器,根据积分器的输出是正或负产生1 位的输出( )。

比较器的输出通过一个以很高频率时钟驱动的 D 触发器被锁存,并且反馈到积 或“低”分器的另一个输入通道,向 0V方向趋势驱动积分器。

基本电路如下:最左边的运放是积分器。

积分器馈入的下一个运放是比较器,或 1位 AD 转换器。

接下 来是 D 触发器,在每个时钟脉冲锁存比较器的输出,发送“高”或“低”信号到电路顶部 的下一个比较器。

最后这个比较器用于转换信号极性,将触发器的 0V/5V 逻辑电平输出转 换到+V/V电压信号再反馈到积分器。

工作原理电路的工作原理如下:如果积分器输出是正,第一次比较器将输出一个“高”信号给触发器的 D 输入。

Delta-Sigma原理

分器(sigma)中。然后将积分器的输出馈送到比较器中。比较器的输出同时将反馈

信号(误差信号)传送到差动器,而自身被馈送到数字滤波器中。这种反馈环路

的目的是使反馈信号(误差信号)趋于零。比较器输出的结果就是1/0 流。该流

我的理解应该是通过软件信号变化,然后通过软件积分运算,得出外部信号随

时间变化的基本状况。

40. Delta-Sigma软件测量方式,是什么概念?

答:Delta-Sigma原理一般应用在ADC应用中。具体来说,Delta-Sigma ADC的

工作原理是由差动器、积分器和比较器构成调制器,它们一起构成一个反馈环路。

调制器以大大高于模拟输入信号带宽的速率运行,以便提供过采样。模拟输入与

如果1密度较高,则意味着模拟输入电压较高;反之,0密度较高,则意味着模拟

输入电压较低。接着将1/0流馈送到数字滤波器中,该滤波器通过过采样与抽样,

将1/0流从高速率、低精度位流转换成低速率、高精度数字输出。

简而言之,Delta就是差动,Sigma就是积分的意思。Delta-Sigma软件测试,

delta-sigma adc原理

delta-sigma adc原理Delta-sigma模数转换器(ADC)是一种常用的转换器类型,用于将模拟信号转换为数字信号。

它使用了一种称为delta-sigma调制的技术,可以实现高分辨率和低成本的模数转换。

本文将介绍delta-sigma ADC的工作原理、架构和应用。

一、工作原理1. Delta-sigma调制Delta-sigma调制是一种用于将模拟信号转换为数字信号的技术。

它使用了一个比较器、一个积分器和一个数字滤波器。

比较器用于将模拟信号与一个参考信号进行比较,输出一个脉冲序列。

积分器用于对这个脉冲序列进行积分,得到一个累积量。

数字滤波器则用于对这个累积量进行滤波,以得到最终的数字输出。

2.噪声整形Delta-sigma调制的一个重要特性是噪声整形效应。

由于比较器的不理想性和积分器的存在,信号和噪声会被一起转换为脉冲序列,并紧接着被积分和滤波。

这样,高频噪声被转换成了低频噪声,这使得delta-sigma ADC对噪声更加敏感,可以实现较高的分辨率。

3.过采样Delta-sigma ADC通常会采用过采样的方式进行工作。

过采样是指在采样过程中使用比需要的采样率更高的采样率。

通过对信号进行多次采样,可以提高信号和噪声的比值,进而提高分辨率。

二、架构1.单级和多级Delta-sigma ADC可以分为单级和多级两种类型。

单级delta-sigma ADC一般只包含一个一阶delta-sigma调制器。

多级delta-sigma ADC则包含多个一阶或二阶delta-sigma调制器,并且通常会在不同的频率上进行采样。

多级delta-sigma ADC通常可以实现更高的分辨率和动态范围,但相应地,其复杂度也更高。

2.反馈结构Delta-sigma ADC的基本结构是一个带有反馈的调制器。

这个反馈回路通常以数字形式存在,用于校正系统中的非线性误差和偏移。

反馈结构可以使得delta-sigma ADC的性能更加稳定和准确。

浅谈 Delta Sigma 调制

浅谈 Delta Sigma 调制CMOS工艺发展的要求出于对降低成本的最原始的渴求,现代CMOS集成电路工艺的特征尺寸一直都在按照摩尔定律的速度减小,产生的结果就是集成电路的面积越来越小,密度越来越大,速度越来越快,电压越来越低,功耗越来越小。

这样的结果显然更利于追求高速、高密度的数字电路,而不利于追求精确的模拟电路。

因此关于信号处理的内容正在不断的向数字域内倾斜,射频和模拟电路将只能在偏置电路和接口电路等外围领域中发挥作用,所有的处理工作将全部由数字电路完成。

可以这样说,今后,所有人类思想中对输入和输出之间进行的变换将全部由数字信号处理器完成,剩下的物理实现中不可或缺的工作将由射频和模拟电路完成。

系统设计师进行设计时需要考虑的一个重要权衡就是最大限度的利用价格低廉、功能强大的数字电路,减少射频和模拟电路与芯片整体性能之间的折中。

为了降低成本,片上系统(SOC)也是越来越流行,这就要求射频和模拟电路与数字电路共同集成在同一块芯片上,使用相同的工艺制造。

今天,高速混合信号IC可以将所有电路和元件集成在一起,完成处理工作。

过采样技术由于集成电路的发展趋势不利于追求精度的模拟电路,但是有利于高速率工作,于是过采样技术应运而生,过采样的频率是信号的奈奎斯特频率的N倍,称为过采样率(OSR)。

过采样技术实际上是利用动态变化的数值去等效静态不变的数值,本质是牺牲速度换取精度。

由于过采样频率远大于信号的奈奎斯特频率,所以由采样带来的混叠效应将大大降低,这样可以降低对模拟滤波器的精度的要求,而这正是CMOS工艺发展趋势带来的不利影响。

由于过采样技术实现的是动态等效,所以静态观察任何一个时间点,输出和输入之间总是存在误差的,称为量化误差。

如果将量化误差视为一个随机的变量,那么量化误差的频谱特性就和白噪声的频谱特性相似了,这时量化误差也称为量化噪声。

Delta-Sigma调制和噪声整形表面上看使用过采样技术没有带来任何好处,实际上过采样技术的高速率引入了一个自由度,设计师可以利用这个自由度设计动态等效输出的频谱形状,实现“以快打慢”。

Delta-Sigma A/D转换器

Delta-Sigma A/D转换器陈拓,刘铮中国科学院0 引言Delta-Sigma A/D转换器具有高分辨率、高集成度、成本低和使用方便的特点,近年来,因数字化产品对高分辨率A/D,D/A转换器需求的激增而得到广泛地应用。

Delta-Sigma A/D转换器的构想出现已有很多年了,早期因受集成电路制造技术的限制,未在产品中广泛使用,随着集成电路制造成本不断降低,该技术的应用渐多,目前已成为高精度ADC的主流技术。

随着该技术的趋热,有更多人想了解其工作原理,但目前国内的教材对其涉及还不多,期刊论文多侧重数学演绎,文献中未见有详尽的仿真实例。

除了制造专用ADC,该技术还易于用FPGA实现,逻辑电路可以完全集成在FPGA内部,只需要很少的外围元件,就可以用FPGA直接进行混合信号处理。

由于FPGA可扩展和可重配置的特性,特别适合产品研发和小规模生产的场合,另外用FPGA在单一芯片上实现多路Sigma-Delta A /D转换也很容易。

Delta-Sigma有时称其为Sigma-Delta,或∑-△。

1 Delta-Sigma A/D转换器原理在△-∑A/D转换器中,模拟输入电压信号被连接到一个积分器的输入端。

在输出端对应输入大小产生一个电压变化率,或者斜坡。

然后用比较器将该斜坡电压与地电位(0V)进行比较。

比较器的行为就像1位A/D转换器,根据积分器的输出是正或负产生1位的输出(“高”或“低”)。

比较器的输出通过一个以很高频率时钟驱动的D触发器被锁存,并且反馈到积分器的另一个输入通道,向0V方向趋势驱动积分器。

基本电路如图1所示。

在图1中,最左边的运放是积分器。

积分器馈入的下一个运放是比较器,或1位A /D转换器。

接下来是D触发器,在每个时钟脉冲锁存比较器的输出,发送“高”或“低”信号到电路顶部的下一个比较器。

最后这个比较器用于转换信号极性,将触发器的0 V/5 V逻辑电平输出转换到V+/V-电压信号再反馈到积分器。

delta sigma dac 原理

delta sigma dac 原理Delta-sigmadac(数字模拟转换器)是数字信号处理系统中的重要组成部分,它将数字信号转换为模拟信号,从而实现数字信号与模拟信号之间的转换。

本文将详细介绍deltasigmadac的原理、工作流程、核心技术和应用领域。

一、基本原理Delta-sigmadac是一种高精度、高动态范围、低噪声的模拟转换器。

其基本原理是将输入的数字信号进行量化后,通过高分辨率的采样和量化过程,将数字信号转换为模拟信号。

在转换过程中,采用噪声密度较低的带通滤波器对量化后的模拟信号进行滤波,从而得到高质量的模拟输出。

二、工作流程Delta-sigmadac的工作流程可以分为以下几个步骤:1.数字输入:输入数字信号经过编码和滤波处理后,成为可用于转换的数字信号。

2.采样和量化:通过对数字信号进行采样和量化,将其转换为连续的模拟信号。

3.滤波处理:通过带通滤波器对模拟信号进行滤波处理,消除高频噪声和失真。

4.输出模拟信号:经过滤波处理的模拟信号输出到负载电阻,形成模拟电压输出。

三、核心技术Delta-sigmadac的核心技术包括采样和量化技术、带通滤波器设计和噪声整形技术。

其中,采样和量化技术是影响转换精度和动态范围的关键因素;带通滤波器设计用于滤除不需要的频率成分,提高输出信号的质量;噪声整形技术则通过提高量化噪声的功率谱密度,减小系统噪声对输出质量的影响。

四、应用领域Delta-sigmadac在各个领域都有广泛的应用,包括音频、通信、仪表、医疗等。

在音频领域,delta-sigmadac被广泛应用于音频编码、解码、放大器和音频处理系统中,提供高质量的模拟音频输出。

在通信领域,delta-sigmadac被用于无线通信、光纤传输和数据存储等系统中,实现数字信号与模拟信号之间的转换。

在仪表领域,delta-sigmadac被用于测量各种物理量,如温度、压力、流量等,提供高精度的模拟输出。

delta sigma dac 原理adi

delta sigma dac 原理adiDeltaSigmaDAC是一种常用的数字模拟转换器(DAC),广泛应用于音频、图像处理等领域。

本文将介绍DeltaSigmaDAC的基本原理、技术特点以及应用领域。

一、基本原理DeltaSigmaDAC的核心部件包括一个数字输入、一个积分器以及一个数字控制的可变模拟电阻器。

输入的数字信号经过滤波和反相处理后,作为积分器的输入,实现数字到模拟的转换。

积分器的作用是将数字信号转换成连续的模拟信号,但同时也引入了量化噪声。

为了减小噪声对输出质量的影响,DAC中通常采用相位噪声消除技术。

数字控制的可变电阻器是一个重要的部件,它可以根据输入数字信号的变化而改变电阻值,从而影响输出电压的大小。

此外,数字控制的可变电阻器通常具有较高的精度和稳定性,可以保证输出电压的准确性和稳定性。

二、技术特点1.高精度:由于采用了数字控制的可变电阻器,DeltaSigmaDAC 具有较高的精度和稳定性,可以保证输出电压的准确性和稳定性。

2.噪声抑制:由于采用了积分器和相位噪声消除技术,DeltaSigmaDAC可以有效地抑制量化噪声,提高输出质量。

3.适合于高动态范围应用:由于DeltaSigmaDAC具有较高的转换速度和较低的噪声,因此适合于高动态范围应用,如音频、图像处理等领域。

三、应用领域DeltaSigmaDAC在以下领域得到了广泛应用:1.音频处理:DeltaSigmaDAC被广泛应用于音频处理领域,如音频编码、解码、放大器等。

它可以提供高质量的音频输出,同时具有较低的噪声和较高的动态范围。

2.图像处理:DeltaSigmaDAC也被广泛应用于图像处理领域,如摄像头、显示器等。

它可以提供高清晰度的图像输出,同时具有较低的噪声和较高的色彩还原度。

3.其他领域:DeltaSigmaDAC还可以应用于其他领域,如通信、航空航天、医疗设备等。

总之,DeltaSigmaDAC是一种重要的数字模拟转换器,具有高精度、噪声抑制和适合于高动态范围应用等技术特点。

(完整版)SigmaDeltaADC原理简单理解

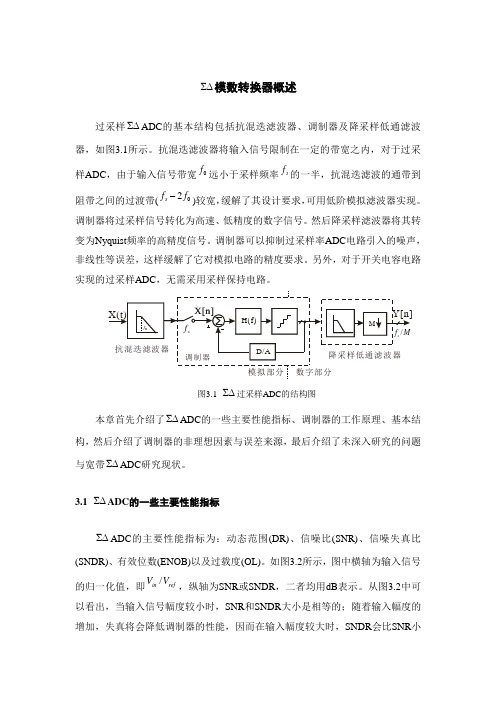

∑∆模数转换器概述过采样∑∆ADC 的基本结构包括抗混迭滤波器、调制器及降采样低通滤波器,如图3.1所示。

抗混迭滤波器将输入信号限制在一定的带宽之内,对于过采样ADC ,由于输入信号带宽0f 远小于采样频率sf 的一半,抗混迭滤波的通带到阻带之间的过渡带(2s f f -)较宽,缓解了其设计要求,可用低阶模拟滤波器实现。

调制器将过采样信号转化为高速、低精度的数字信号。

然后降采样滤波器将其转变为Nyquist 频率的高精度信号。

调制器可以抑制过采样率ADC 电路引入的噪声,非线性等误差,这样缓解了它对模拟电路的精度要求。

另外,对于开关电容电路实现的过采样ADC ,无需采用采样保持电路。

图3.1 ∑∆过采样ADC 的结构图本章首先介绍了∑∆ADC 的一些主要性能指标、调制器的工作原理、基本结构,然后介绍了调制器的非理想因素与误差来源,最后介绍了未深入研究的问题与宽带∑∆ADC 研究现状。

3.1 ∑∆ADC 的一些主要性能指标∑∆ADC 的主要性能指标为:动态范围(DR)、信噪比(SNR)、信噪失真比(SNDR)、有效位数(ENOB)以及过载度(OL)。

如图3.2所示,图中横轴为输入信号的归一化值,即/in refV V ,纵轴为SNR 或SNDR ,二者均用dB 表示。

从图3.2中可以看出,当输入信号幅度较小时,SNR 和SNDR 大小是相等的;随着输入幅度的增加,失真将会降低调制器的性能,因而在输入幅度较大时,SNDR 会比SNR 小一些。

图3.2显示了非理想调制器的性能比理想调制器的性能差一些:一方面是由于实际调制器的有限增益引起性能成呈线性下降;另一方面是由于实际调制器过载而造成的性能下降。

图3.2 典型的∑∆转换器的性能图调制器各相主要性能指标[60]介绍如下:1.信噪比(SNR):是指在一定的输入幅度时,转换器输出信号能量与噪声能量的比值。

转换器能获得的最大信噪比为峰值信噪比(PSNR)。

Delta_Sigma调制原理及性能分析

INFORMA TION SYSTEM AND APPLICATION │信息系统及应用2018年第3期 85Delta_Sigma 调制原理及性能分析周佶昊 钱志华重庆邮电大学,重庆 400000摘要:Delta_Sigma 调制技术以其高分辨率、低功耗、使用方便等特点在传感器等众多领域中被广泛运用。

首先从系统框图、电路模型和z 域模型三个方面详细地阐释了Delta_Sigma 调制的原理,并从过采样技术和噪声整形技术两个方面通俗易懂地分析了Delta_Sigma 调制的性能指标。

最后给出了Delta_Sigma 调制技术的应用场景,让读者对Delta_Sigma 调制技术有更全面的了解。

关键词:Delta_Sigma 调制;系统框图;电路模型;z 域模型;过采样;噪声整形 中图分类号:TN761 文献标识码:APrinciple and Performance Analysis of Delta_Sigma ModulationZhou Jihao Qian ZhiHuaChongqing University of Posts and Telecommunications, Chongqing 400000Abstract: Delta_Sigma modulation technology is widely used in sensors and many other fields due to its high resolution, low power consumption, and convenient use. In the paper, the principle of Delta-Sigma modulation is explained in detail from three aspects, system block diagram, circuit model and z-domain model. The performance of Delta-Sigma modulation is analyzed from two aspects of oversampling and noise shaping. Finally, the application scene of Delta_Sigma modulation technology is given, which gives readers a more complete understanding of Delta_Sigma modulation technology.Keywords: Delta_Sigma modulation; system block diagram; circuit model; z-domain model; oversampling; noise shaping引言Delta_Sigma 调制也称为ΔΣ调制、Sigma_Delta 调制和ΣΔ调制,是一种将模拟信号转化为数字信号的调制方法。

浅谈Delta-Sigma之工作原理

淺談Delta-Sigma之工作原理文/黃克強’95年初老朽準備「EAD-DSP系列之DSP演算法」(詳見高傳真227期)之前,蒲總編曾經向老朽提及Crystal公司的CS4328、CS4330……一系列的IC,希望我能寫一系列的文章來談這一系列廣泛用途之Over Sampling之D/A Converter IC,其實這一系列的IC都是採用了所謂之「分段式Up Sample」的DSP架構搭配△-Σ之D/A Converter而成,由於老朽在『細說EAD-DSP系列之DSP演算法」一支中並末談及△-Σ的工作原理,因此特別請我的好友黃克強博士來撰寫△-Σ的部份。

——何志誠何老朽是我的摯友兼同事,他的辦公桌就在筆者的左手邊。

他是個發燒友,也是音響專家。

而筆者卻是個音響白癡(編者:唉!唉!黃先生實在太謙虛了,如果您是白癡,那我們豈不……)。

他專精信號處理,尤其是Over Sampling。

而筆者擅長數位通訊及一點點適應性控制。

半年前,甚至更久之前,何老朽拿了一些CS4328之類的Data Sheet及他在高傳真發表的文章給我,這時我才在他的調教之下初窺發燒音響之門徑。

誰知黃鼠狼給雞拜年不懷好意,何老朽半哄半騙的要我替他寫一篇有關Delta-Sigma的介紹文章。

礙於多年交情,我勉強答應下來。

事後才發現這種文章真難寫。

為了能在高傳真雜誌上「露臉」,必須避免學院派的數學推導,又必須把東西寫得清清楚楚(要不然就變成低傳真),真是難。

難!難!難!難!不過何老朽畢意沒看走眼,筆者費了九牛二虎之力,終究把它寫出來了。

但由於筆者筆法不夠老練,寫出來的文章可能還是生硬了些,尚請讀老您多多包涵。

有任何批評指教,請找何老朽代轉,包君滿意!圖零是CS4328的方塊圖,第一個方塊8 X Interpolation Filter已經在何老朽以前的一系列高傳真文章中介紹過了。

第二個方塊就是本文所要談的Delta-Sigma(△Σ)。

浅谈Delta-Sigma之工作原理

淺談Delta-Sigma之工作原理文/黃克強’95年初老朽準備「EAD-DSP系列之DSP演算法」(詳見高傳真227期)之前,蒲總編曾經向老朽提及Crystal公司的CS4328、CS4330……一系列的IC,希望我能寫一系列的文章來談這一系列廣泛用途之Over Sampling之D/A Converter IC,其實這一系列的IC都是採用了所謂之「分段式Up Sample」的DSP架構搭配△-Σ之D/A Converter而成,由於老朽在『細說EAD-DSP系列之DSP演算法」一支中並末談及△-Σ的工作原理,因此特別請我的好友黃克強博士來撰寫△-Σ的部份。

——何志誠何老朽是我的摯友兼同事,他的辦公桌就在筆者的左手邊。

他是個發燒友,也是音響專家。

而筆者卻是個音響白癡(編者:唉!唉!黃先生實在太謙虛了,如果您是白癡,那我們豈不……)。

他專精信號處理,尤其是Over Sampling。

而筆者擅長數位通訊及一點點適應性控制。

半年前,甚至更久之前,何老朽拿了一些CS4328之類的Data Sheet及他在高傳真發表的文章給我,這時我才在他的調教之下初窺發燒音響之門徑。

誰知黃鼠狼給雞拜年不懷好意,何老朽半哄半騙的要我替他寫一篇有關Delta-Sigma的介紹文章。

礙於多年交情,我勉強答應下來。

事後才發現這種文章真難寫。

為了能在高傳真雜誌上「露臉」,必須避免學院派的數學推導,又必須把東西寫得清清楚楚(要不然就變成低傳真),真是難。

難!難!難!難!不過何老朽畢意沒看走眼,筆者費了九牛二虎之力,終究把它寫出來了。

但由於筆者筆法不夠老練,寫出來的文章可能還是生硬了些,尚請讀老您多多包涵。

有任何批評指教,請找何老朽代轉,包君滿意!圖零是CS4328的方塊圖,第一個方塊8 X Interpolation Filter已經在何老朽以前的一系列高傳真文章中介紹過了。

第二個方塊就是本文所要談的Delta-Sigma(△Σ)。

delta_sigma ADC 数字滤波器

delta-sigma型ADC的数字滤波器应用事项1、delta-sigma型ADCdelta-sigma型ADC以很低的采样分辨率(1位)和很高的采样速率将模拟信号数字化,通过使用过采样(Oversampling)技术,噪声整形和数字滤波技术增加有效分辨率,然后对滤波器输出进行采样抽取(Decimation)处理得到输出结果。

delta-sigma型ADC采用简单的模拟电路(仅一位量化器和一位数模转换器)和大量的数字信号处理电路,造价低廉却具有高可靠性,能在低频下获得极高的线性度和分辨率。

为了适应不同应用场合对响应时间,噪声滤波等性能的不同要求,delta-sigma型ADC 通常允许用户对滤波器的结构和性能进行一定的编程组态。

2、数字滤波与模拟滤波与传统的模数转换器相比,delta-sigma型ADC具有独特的内置数字滤波器,分为FIR (有限冲击响应)和IIR(无限冲击响应)两种;FIR是非递归型,输出仅依赖于过去至当前的输入,IIR是递归型,输出是过去至当前的输入与输出值的函数。

数字滤波发生在模数转换后,它能消除模数转换过程中产生的噪声(特别是量化噪声);数字滤波比模拟滤波容易实现可编程性,依靠数字滤波器设计,用户可以编程转折频率和输出更新速率,对工频干扰(50Hz,60Hz)很容易取得90~100dB以上的抑制效果。

典型地,delta-sigma型ADC数字滤波器采用一个低通SINC(3)滤波器,它的响应与平均滤波器有相似之处,数字滤波器输出速率对应于第一个陷波频率,陷波位置多次在第一个陷波频率的倍数处重复,并在这些陷波处提供高于100dB的衰减。

下图是输出速率(陷波频率)为60Hz的频响曲线。

具体应用中在ADC前端进行模拟滤波,主要作用是抗混叠。

过采样转换技术使得防止混叠所需要的滤波变得十分简单:只须滤除频率为调制器采样速率(多倍于奈氏频率)整数倍的输入噪声,因为数字滤波器不能抑制该频带的信号;另外在输入接近满标度范围的信号时,模拟滤波可避免有用带宽外的差分噪声叠加,使调制器和数字滤波器饱和――这种情况也可以采用降低输入通道电压的方法,使之为输入通道满标度范围的一半,这样动态范围降低1倍而超范围性能增加1倍。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

浅谈Delta-Sigma之工作原理

文/黄克强’95年初老朽准备「EAD-DSP系列之DSP演算法」(详见高传真227期)之前,蒲总编曾经向老朽提及Crystal公司的CS4328、CS4330……一系列的IC,希望我能写一系列的文章来谈这一系列广泛用途之Over Sampling之D/A Converter IC,其实这一系列的IC都是采用了所谓之「分段式Up Sample」的DSP架构搭配△-Σ之D/A Converter而成,由于老朽在『细说EAD-DSP系列之DSP演算法」一支中并末谈及△-Σ的工作原理,因此特别请我的好友黄克强博士来撰写△-Σ的部份。

——何志诚

何老朽是我的挚友兼同事,他的办公桌就在笔者的左手边。

他是个发烧友,也是音响专家。

而笔者却是个音响白痴(编者:唉!唉!黄先生实在太谦虚了,如果您是白痴,那我们岂不……)。

他专精信号处理,尤其是Over Sampling。

而笔者擅长数位通讯及一点点适应性控制。

半年前,甚至更久之前,何老朽拿了一些CS4328之类的Data Sheet及他在高传真发表的文章给我,这时我才在他的调教之下初窥发烧音响之门径。

谁知黄鼠狼给鸡拜年不怀好意,何老朽半哄半骗的要我替他写一篇有关Delta-Sigma的介绍文章。

碍于多年交情,我勉强答应下来。

事后才发现这种文章真难写。

为了能在高传真杂志上「露脸」,必须避免学院派的数学推导,又必须把东西写得清清楚楚(要不然就变成低传真),真是难。

难!难!难!难!不过何老朽毕意没看走眼,笔者费了九牛二虎之力,终究把它写出来了。

但由于笔者笔法不够老练,写出来的文章可能还是生硬了些,尚请读老您多多包涵。

有任何批评指教,请找何老朽代转,包君满意!

图零是CS4328的方块图,第一个方块8X Interpolation Filter已经在何老朽以前的一系列高传真文章中介绍过了。

第二个方块就是本文所要谈的Delta-Sigma(△Σ)。

现在我们就开始正式进入△-ΣD/A converter之殿堂。

为了使本文雅俗共赏,笔者避开了所有的数学方程式,尽量以图解的方式作观念上的介绍。

要了解△Σ调变,必须先从△调变下手,比较容易进入状况,复杂如CS4328所采用之五阶△Σ调变就是从最原始之△调变一步一步演化而来的。

请详见图一的演化图。

建议读者在K这篇文章时,多看图,至于文字就只是用来说明图例而已。

图二是一个八调变之1Bit DAC。

Xd代表数位波形输入,就数位音响而言,Xd可能是18bit,至于尾巴的d代表digital之意。

Yd为△调变之1Bit输出,值为正1或负1。

△调变之观念很简单,就是要使Yd之积分波形愈接近Xd愈好,如图三所示。

每当Yd之积分值(即Zd)超过Xd,下一个Yd值就设为负1。

如果Yd之积分值Zd低于Xd,下一个Yd值就设为正1。

图二的减法器就是要看看Xd和Zd谁大谁小,Ud=Xd-Zd,若Ud大于零,比较器输出(即Yd)就为正1,若Ud小于零,比较器输出为负1。

如此一来Yd不断的修正使得Yd之积分后波形Zd如影随形般的和Xd同上同下。

现在要做的就是把Zd以类比的方式重现出来。

很容易的,首先利用1Bit的DAC将数位的Yd转成类比的对等信号Ya,(其中a代表analog 之意),然后再用类比积分器将Ya作积分而产生Za。

于是Za和Zd两者之波形是一样的,只不过Zd是数位而Za是类比。

但是由于1Bit DAC,Za会有些不平滑的转折点,所以最后还

需要一个类比低通滤波器以产生平滑的Xa,Xa就是Xd的类比重现。

这样的△调变方式产生了一些问题。

首先是如果数位输入波形Xd的变化太急剧,也就是斜率过大,如图四(a)所示,那幺Zd将会跟不上,而产生严重的失真。

第二个问题是△调变看不见直流或极低频成份。

因为△调变基本上是针对输入波形的时间变化量(类似微分)作1Bit的量化编码(如图三(a)所示),所以直流成分显示不出来。

这样说太模糊,我们看图四(b),如果输入Xd是直流,那幺不管Xd的固定值是多少,Yd的输出永远都一样,那当然不对。

此外,类止积分器在实际工程上也不是那幺讨人喜欢。

要克服上述两个问题,可以将图二之△调变DAC作一些变形,我们将积分器从后面搬移到最前面.如图五所显示的。

如此一来原来的类比积分器就变成数位的积分器。

而且Xd 经过积分之后,原有的急剧变化将会变得平缓得多,于是后面的△调变就不会有斜坡跟不上的问题。

至于Xd中的直流或极低频的成份,经过积分之放大效果后,就不会像图四(a)所示的那样水平固定不动,于是后面的△调变就可以看得到而加以量化编码。

这实在是一本万利。

图五这样的系统可以称呼为△Σ调变(Sigma Delta Modulator),就是在△调变之前加个Σ,Σ

意指积分。

图五所描述的△Σ调变可以再加以简单化。

我们注意到图五之Ud为Xd之积分减去Yd 之积分,是先积分再相减。

所以我们也可以使Xd和Yd先相减,以后它们的差再积分,就如同图六所描绘的,结果Ud不变,但是图六比图五省下一个积分器。

因为图六是先相减再积分,可称之为△Σ调变(Delta-Sigma Modulator)。

由于其中所用之积分器事实上是一个一阶滤波器,所以图六可细称为一阶△Σ调变。

图六只是△Σ调变的基本型,它的效能还可再改进。

例如图七,这是个n阶△Σ调变器,也就是以一个n阶滤波器去取代图六之积分器,这样就

可以大幅提高最后类比输出之S/N比。

如果n=5,就是CS4328所采用的1bit DAC。

经过上面那幺一大段烦闷琐碎的文字解说,我们来点轻松易懂的。

图八(a)是△Σ调变的数位波形输入,经过△Σ调变后1Bit输出为图八(b)。

图八(b)的二值类比波形经过类比低通滤波器之后,又还原成图八(a)一样的波形,不过是类比的。

在时间指标为l0附近,图八(a)小于零,于是1Bit输出大部份是负1。

在时间为30附近,图八(a)大于零,于是1Bit输出大部份

是正1。

在时间为45附近图八(b)大约是零,于是1Bit输出为正负1交错。

看这图八,相信读者对于△Σ一定有了一些较具体的感觉。

现在我们解释一下CS4328的五阶△Σ(图七)优于基本型一阶△Σ(图六)的道理何在。

总归一句话,△Σ就是要产生一串1Bit信号,这串信号和输入波形(audio)在低频部份(20KHz以下)一模一样.而其它量化误差则尽量往高频移过去.这些高频误差就可以用类比低通滤波器轻松地干掉。

图九是一个一阶△Σ调变输出Yd的频谱,20KHz以下低频部份是我们所要的信号,50KHz以上高频部份就是其它误差。

图十是二阶△Σ调变输出的频谱。

两相比较,读者可发现二阶△Σ的量化误差(频谱高频部份)比较多,且比较往高频率挤。

意思就是说,低频信号部份比较精准,S/N比较高。

为什幺?道理很简单,△Σ调变中的比较器是在作信号量化的工作,如同一般的16bit DAC一样,只是它比较极端,只有1bit。

我们自然希望这个比较器只针对低频信号作量化,所以最好是不要让比较器看到高频部份。

图六的一阶数位积分器和图七的n阶数位滤波器就是在扮演这种站在比较器前面阻挡高频的角色。

谁阻挡高频越成功,比较器对低频信号的量子化也就越精准,量化误差也就越往高频挤。

讲到这里大家一定就明白为何二阶△Σ比一阶△Σ的S/N比高,因为二阶数位低通滤波器比一阶的更能阻挡高频。

依此类推,三阶,四阶,五阶,阶数越高越好。

但是阶数越高数位滤波器越复杂,成本越高。

而且阶数太高会引起整个△Σ调变器的稳定性的问题。

基于这些考量,

CS4328采用五阶。

啰嗦了这幺一大段,相信大家只要有一些Digital的基本概念,就一定对CS4328的△Σ调变有了一些观念上的认识。

如果还不清楚,那幺读者未免太对不起笔者牺牲这幺多的宝贵时间,半年!至于CS4328还有Switched Capacitor Filter的部份,读者就把它想成是类比低通滤波器就好了,至于什幺是Switched Capacitor,笔者就暂时不奉陪了。

数位,虽然我们常说那只不过是0与1的变化,然而它的学问却是博大精深的,Delta-Sigma这个名词出现已久,却无人能将它说明清楚。

我们非常感谢黄博士,竟以半年的时间,在不谈理论、不写公式的条件下,把Delta-Sigma 说得这幺明白,并亲绘本文之所有附图,在此本人谨代表高传真及读者向黄博士致最深之谢忱。

蒲鸿庆。