利用FPGA实现UART的设计

基于FPGA的波特率连续可调的UART接口设计

基于FPGA的波特率连续可调的UART接口设计吴志勇;郭元兴;刘雨沁【摘要】在FPGA上设计了一种波特率连续可调的UART接口,该接口符合RS-232C通信协议.将波特率转换为比特持续时间,在固定工作时钟频率下通过改变比特持续时间来实现波特率的连续可调,并将比特持续时间和中断时间间隔作为接口参数,用户可以灵活设置接口速率和中断CPU的频率.在接收端高速采样,采用大数判决的方式确定当前比特值,有效过滤了信号线上的毛刺,提高了UART接口的抗干扰能力.该接口已在实际项目中应用,经验证其工作稳定可靠,数据通信完全正确.%A continuous and adjustable baud-rate UART interface conformable to RS-232C communication protocol is designed on FPGA. Baud rate is converted to bit duration. At constant working clock frequency, the baud rate can be continuously adjusted by changing bit duration, while the bit duration and the interruption interval are used as interface parameters. The rate of interface and the frequency of interrupting the CPU can be set flexibly by users. At the receiver, high-speed sampling is adopted, and the current bit value is determined by the way of majority decision, thus effectively filtering out the burr on the signal line and improving the anti-interference ability of UART interface. The interface is now applied to the actual project. The experiment indicates that this interface is stable and reliable in work and the data communication is completely correct.【期刊名称】《通信技术》【年(卷),期】2018(051)001【总页数】5页(P252-256)【关键词】通用异步收发器;FPGA;波特率可调;大数判决【作者】吴志勇;郭元兴;刘雨沁【作者单位】中国电子科技集团公司第三十研究所,四川成都 610041;中国电子科技集团公司第三十研究所,四川成都 610041;中国电子科技集团公司第三十研究所,四川成都 610041【正文语种】中文【中图分类】TP3360 引言UART(Universal Asynchronous Receiver Transmitter,通用异步收发器)是一种广泛使用的低速串行接口,遵循的协议是RS-232C标准。

基于FPGA的UART电路的设计

UART传 送 一 个 字 符 以 起 始 位 ( tr i) 开 S atBt

始 , 以停 止位 ( tp Bt 结 束 ,字 符 之 间 没 有 固 定 So i )

的 时 间 间 隔 要 求 。每 一 个 字 符 的 前 面 都 有 一 位 起 始 位 ( 电 平 ,逻 辑 值 O ,字 符 本 身 由 5 8位 数 据 位 低 ) ~

波特率发 生模 块 、发送模块和接 收模块 ,并 给 出了仿真 结果 。程序 下载 到 F G 芯 片中 ,通信 数据 完全 正确 。 PA

该设计 不仅实现 了异步通讯 的主要 功能 ,而且 电路 简单 ,工 作稳定 、可靠 ,可 以将 其灵 活地嵌 入到各 个通 信系

统 中。

关 键 词 :F GA;UA P RT;VeigHD ro L l

Ab ta t s r c :Th s p p r d s rb s t e f n t n a d c a a t r tc f U ART. Th e u c i n f FP i a e e c i e h u c i n h r c e i is o o s e k y f n t s o GA , wh c o ih ic u e b u a e p o u e , ta s t e n e ev r we e i lm e t d o G n ld a d r t r d c r r n mitr a d r c i e , r mp e n e n FP Th i l t n r s l i a s e smu a i e u t s lo o

De i n o nd o s g f a ki fUART ic i a e o FPGA c r u tb s d n

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

基于FPGA的UART设计综述

四川师范大学本科毕业设计基于FPGA的UART设计学生姓名院系名称专业名称班级学号指导教师完成时间基于FPGA的UART设计电子信息工程专业摘要:UART(通用异步收发器)是一种应用广泛,协议简单,易于调试的串行传输接口。

FPGA是能高密度,低消耗完成所需要的逻辑功能的一种在线可编程器件,是现在业内提高系统集成度最佳技术之一,其可反复配置,且使用灵活。

VHDL 是描述电路功能或行为的一种硬件语言。

本文首先阐述了运用FPGA实现UART接口的意义。

接着介绍了UART的波特率发生器,发送功能和接收三大核心功能的理论知识。

FPGA的工作原理,配置模式以及VHDL语言实现状态机的相关理论基础。

给出了运用VHDL语言将UART三大功能嵌入在FPGA上的模块化设计方法。

设计包括四大模块:顶层模块,波特率发生器,UART接收器,UART发生器。

在FPGA片上集成UART主要功能,减少了电路板体积,同时电路也增加了可移植和反复配置功能,有效提高了电路的集成度和灵活性。

最后运用Quartus ii 9.1实现了其功能仿真。

关键词:FPGA UART VHDL 有限状态机The Design of Universal Asynchronous Receiver Transmitter Based on FPGAAbstract:UART (Universal Asynchronous Receiver Transmitter) is a widely used, simple protocol, easy to debug serial transmission interface. FPGA is capable of high-density, low-cost needed to complete a line of programmable logic devices, is now one of the industry's best technologies to improve system integration, which can be repeated to configure and use and flexible. VHDL description of the circuit function or behavior is a hardware language. This paper first describes the use of FPGA to realize the significance of the UART interface. Then introduced the theory of knowledge UART baud rate generator, sending and receiving three core functions. FPGA works, configuration mode and the VHDL-based state machine theory. Gives the UART using VHDL language to three functions embedded in the FPGA design. Design includes four modules: the top-level module, baud rate generator, UART receivers, UART generator. Integrated on-chip UART FPGA basic functions, reducing board space, the circuit also increases the portability and repeated configuration capabilities, improve the integration and flexibility of the circuit. Finally, the use of Quartus ii 9.1 implements its functional simulation.Key Words:FPGA ;UART ;VHDL;FSM目录摘要: (I)Abstract: (II)1 绪论 (1)1.1 课题背景 (1)1.2 课题研究现状 (2)1.3 课题研究内容与主要工作 (3)1.4 课题内容结构 (3)2 UART理论基础 (4)2.1 接口技术简介 (4)2.2 UART基本结构 (4)2.3 UART数据帧格式 (5)2.4 涉及到的理论计算 (6)3 设计工具 (7)3.1 课题硬件平台——FPGA (7)3.2 设计工具QuartusII简介与使用 (7)3.3 VHDL语言简介 (7)4 UART实现方案 (8)4.1 系统总体结构 (8)4.2 顶层模块设计 (8)4.3 波特率发生模块设计 (9)4.4 接收模块 (10)4.5 发送模块设计 (12)5 UART设计的仿真与验证 (15)5.1波特率发生模块仿真 (15)5.2 接收模块仿真 (15)5.3 发送模块仿真 (16)6 总结 (17)参考文献 (18)致谢 (19)附录 (20)基于FPGA的UART设计1 绪论在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:(1)速度不匹配。

一种基于FPGA的UART IP核设计

发送数据 , 一帧 由起始位 、 数据位 、 校验位和停止 位组成 。数 据逐位传输 , 帧格式 如图 1 所示 。

1 )起 始 位 。 U R A T空 闲 时 ( 有 数 据 传 输 ) 总 线 为 高 没 ,

6 )波 特率 。由于 U R A T没有 同步时钟 线 , 发双方如 收/ 果需要 进行正 确的数据 传输 , 则要在 收/ 发双方定 义一致 的

数 据位 ( 有 校 验 位 ) 后 发 送 1— 没 之 2位 的“ 辑 1 和 校 验 位 逻 ”

之后 1 位 的“ 辑 1 ( ~2 ” 有校验位 )停止位可 以为 1位和 2 ,

1 U R A T概 述

U R A T是 一 种 异 步 通 信 协 议 。 “ 步 ” 不 需 要 额 外 的 异 指 时 钟 线 进 行数 据 的 同 步 传 输 , 一 种 串 行 总 线 接 口 , 需 占 是 只 用 2根线 就 可 以完 成 数 据 的收 发 ( 根 接 收 数 据 , 根 发 送 一 一

数据 开始传输 前 , 需

要刘‘ 数 化 数 作 一 的定 义 , 则 会 导 致 数 据 的 传 输 舣 致 的 发 送 采』 低 f L B 先 发 送 。 J ( S ) J

议 。它具有 使用 简单 ( 只有 几个 寄存 器 ) 应用广 泛 、 、 接线简 单等优点 , 电平进行转换后 , 对 通信距离较 长 , 但存 在电路复 杂、 成本高 、 可移植性 差等 缺点 。本文采用 F G 现 场逻辑 P A(

进行编程仿真试验 。仿真结果表明 : 该方法减小 了系统休秋 , 降低 rJ 牦 , 『 J 摊 』 ’ r系统 的稳定 和州 稚性 , 增加 了系

统 的灵 活 性 , 高 了可 移 植 性 。 提 ’

基于FPGA实现多路UARTSPI通信系统

基于FPGA实现多路UARTSPI通信系统第一部分设计概述 /Design Introduction本次的设计为多路UART/SPI通信系统,可以实现一对多的通信。

系统可以运行在UART模式,也可以运行在SPI模式。

我选择这一课题的原因主要是目前我所在的实验室需要写基于UART的快速通信。

这一课题既可以帮助我巩固之前学习的知识,又可以为我后面的项目做准备。

在完成课题的过程中,主要用到了FPGA状态机、总线等方面的知识。

这一课题可以应用在需要高速异步串行或同步串行通信的应用场合,如实时控制、监测等。

当系统运行在UART模式下,可以实现一个发送端最多向四个接收端发送信息,且有效信息中包含地址码,接收端可以根据发送端发送的地址码判断该信息是否是发送给自己的,实现信号线复用。

UART 通信简单,仅需要一根信号线,但是其缺点是只能实现单向通信,接收端无法给发送端反向发送数据。

但是这一缺点也可以通过采用两个UART系统来弥补。

当系统运行在SPI模式下,可以实现一个主机与多个从机之间的通信,且在通信过程中,系统是全双工的。

主机通过选择性拉低某一个或者某几个从机的片选信号,实现对于从机的选择。

第二部分系统组成及功能说明 /System Construction & Function Description计划功能程序实现UART和SPI的通信,并可以通过按键的方式在两种模式之间切换。

在UART模式下,发送端给接收端发送一串数据,接收端判断是否和已知数据相符。

如果相符则点亮LED,如果不符则不点亮。

在SPI模式下,主机给从机、从机给主机同时发送数据,若接收到的数据和已知数据相符,则点亮LED,如果不符,则不点亮。

同时,UART和SPI均有寻址功能。

UART的寻址方式是在数据位前面加两位地址位,实现对最多四个接收端的区分;SPI的寻址方式是通过拉低需要选定的从机的SS信号,实现对最多四个接收端的区分。

目前所有的功能均已实现。

FPGA和单片机串行通信接口的实现

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

UART通信的FPGA实现设计

停止位

始位

t

8 位数据

停止位 空闲位

0 I 100 lI Illl I 1l 1 / , 1 11l, 1,I 11 1I 0 1 , 0 0 l 1 1

由D B9的 T D端输 出。 x

接器 ( B2 )实际使用 中多采用 的是一个 9 D ̄ , 5 芯的 D型连接 器 ( B9 , 方案采用了 D -连接器。 D )本 B9

式。本方案采用的是异步通信方式, 其的特点是 : 通信的发 送方和接收方各 自 有独立的时钟, 传输的速率由双方约定。

国际上规定 的一 个 串行 通信 波特 率 标 准系 列是 :1、0 、 10 30 6010 、802O 、80 90 、90 。本 方 案采用 的波 0 、20 10 、40 40、60 120

特率是 9 0 。 60

异 步传输是 一个字符 接一个字符传 输 。 一个字符 的信 息 由起始 位、 数据位 、 偶校 验位和停 止位组 成 。每一个字符 奇

圈 2 A T异步 串行通信硬件接 口电路田 U R

.

本 方案的异步 串行通信的硬件接 口电路 图如图 2 所示 ,

的传送靠起始位来同步, 字符的前面是一位起始位, 用下降

沿通知收方传输 开始 , 紧跟 着起始位 之后 的是数 据位 , 传输

由三部分组成:

串口模块、 X 3 和 D -。MA I MA 22 B9 XM

公司 的 MA 22是 为 满足 EA T A22 X3 I / E - E的标 准 而设 计 3

时低位在前、 高位在后 , 字符本身由 5 8位数据位组成。 ~

基于DSP+FPGA的UART设计与实现

基于DSP+FPGA的UART设计与实现摘要:UART作为RS232协议的控制接口得到广泛的应用,将UART功能集成在DSP和FPGA芯片组成的系统中,可使整个系统更为灵活、紧凑,减小电路体积,提高系统的可靠性和稳定性。

本文提出了一种基于DSP和FPGA 系统的UART 实现方法。

关键词:通用异步收发器;DSP;FPGA1 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,通常称作UART)是一种串行异步收发协议,应用十分广泛。

UART可以和各种标准串行接口,如RS232、RS485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART 由专用芯片来实现,但专用芯片引脚较多,内含许多辅助功能,在实际使用时往往只需要用到UART 的基本功能,使用专用芯片会造成资源浪费和成本提高[1]。

在DSP和FPGA组成的系统中,利用DSP芯片完成UART数据收发控制,FPGA完成UART数据具体的收发时序,二者利用EMIF接口配合,即可实现UART通信功能。

这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

2 UART原理UART是一种串行数据总线,用于全双工异步通信。

工作原理是将数据的二进制位按位进行传输。

基本的UART 只需要两条信号线(收、发)和一条地线就可以完成数据的互通,接收和发送互不干扰。

在UART通信协议中,信号线上的状态位高电平代表“1”,低电平代表“0”。

图1 UART数据传输格式UART 数据传输格式如图1所示,一个字符由起始位、数据位、校验位和停止位组成(其中校验位可选)。

其中各位的含义如下:起始位:一位逻辑“0”信号,表示字符数据传输的开始;数据位:5~8位可选的逻辑“0”或“1”。

数据位的发送顺序为:先发送数据的最低位,最后发送最高位;校验位:包括奇校验或偶校验两种方式,即数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验)。

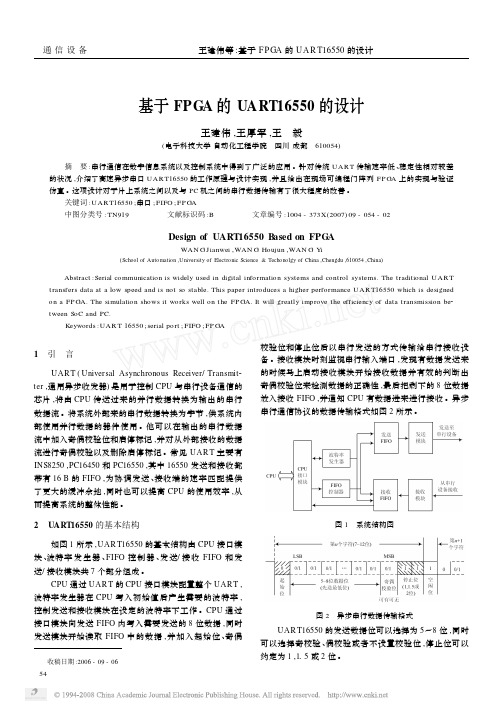

基于FPGA的UART16550的设计

基于FPGA 的UART16550的设计王建伟,王厚军,王 毅(电子科技大学自动化工程学院 四川成都 610054)摘 要:串行通信在数字信息系统以及控制系统中得到了广泛的应用。

针对传统UAR T 传输速率低、稳定性相对较差的状况,介绍了高速异步串口UAR T16550的工作原理与设计实现,并且给出在现场可编程门阵列FP GA 上的实现与验证仿真。

这项设计对于片上系统之间以及与PC 机之间的串行数据传输有了很大程度的改善。

关键词:UAR T16550;串口;FIFO ;FP GA中图分类号:TN919 文献标识码:B 文章编号:1004-373X (2007)09-054-02Design of UART16550B ased on FPG AWAN G Jianwei ,WAN G Houjun ,WAN G Y i(School of Automation ,University of Electronic Science &Techonolgy of China ,Chengdu ,610054,China )Abstract :Serial communication is widely used in digital information systems and control systems.The traditional UAR T transfers data at a low speed and is not so stable.This paper introduces a higher performance UAR T16550which is designed on a FP GA.The simulation shows it works well on the FP GA.It will greatly improve the efficiency of data transmission be 2tween SoC and PC.K eywords :UAR T 16550;serial port ;FIFO ;FP GA收稿日期:2006-09-061 引 言UAR T (Universal Asynchronous Receiver/Transmit 2ter ,通用异步收发器)是用于控制CPU 与串行设备通信的芯片,将由CPU 传送过来的并行数据转换为输出的串行数据流。

基于FPGA的UART设计与应用

Tas ie U R ) r mt r A T是一种短 距离串行通信接 口,主要 用于计 n t, 算机、 处理器与小型通信 网络之 间的短距离通信…。目前, 微

通信接 1技 术已发展 成为硬件 和软件相 结合 的综合性技术 , 3 在嵌入式系统设 计中 ,异步串行通信接 1 3已成为必不可少 的

3 波特率发生器设计

按照 R 一3 通信规则 ,该 U R S22 A T输出 1 6倍波特率 的时 钟信号 ,UA T 在发送数据 时,只需将数据按照一定格式和 R 速率 串行移位发送 。当 U T接收数据 时,在何时采样数据 AR 线 ,即读入 串行数据 的时刻非常关键 。最理想情况是在 串行 数据每一位 的中间时刻 ,对 串行 数据进行采样 。为保证数据 采集 的准确性 ,需要对每一位数据 的时间进行 分段来降低接 收方 出现采样错误 的概率 。本设计是在每 一串行数据位 的持

p o o e T l o i m n l d ss ae m a h n e i n a d l v l e i e h i u s T e ta mis o u t ff l— up e e e v / e d t r p s d. hea g rt h i cu e tt c i e d s g n e e sgn tc n q e . d h r ns s i n f nci o ld lx t r c i e s n sdaa i on u o s r ai e T e f nci a s ic t fUART sas e i e Ex e i n a e u t h w a e d s g a ea v n a e fp o r mm a l i i o e l d. z h u t on l e t r ui o t c i l o d sgn d. p r me t lr s lss o t tt e i n h s d a tg so r g a h h h t bedgt f t e s n /e e v a aa d f n to a x a so t . h e d r c i e d t n u c i n l p n i n e c e ‘

基于FPGACPLD设计与实现UART(VHDL)

基于FPGA/CPLD设计与实现UART(VHDL)1 引言由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。

特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。

可以说EDA 产业已经成为电子信息类产品的支柱产业。

EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(HDL)描述电路系统。

就FPGA和CPLD开发而言,比较流行的HDL主要有Verilog HDL、VHDL、ABEL-HDL和 AHDL 等,其中VHDL 和Verilog HDL因适合标准化的发展方向而最终成为IEEE标准。

下面的设计就是用VHDL来完成实现的。

2 UART设计实例通常设计数字电路大都采用自顶向下将系统按功能逐层分割的层次化设计方法,这比传统自下向上的EDA设计方法有更明显的优势(当时的主要设计文件是电路图)。

因为由自顶向下的设计过程可以看出,从总体行为设计开始到最终逻辑综合,形成网络表为止。

每一步都要进行仿真检查,这样有利于尽早发现系统设计中存在的问题,从而可以大大缩短系统硬件的设计周期。

下面以UART的设计为例具体说明:(本设计只对本设计的总模块做各种基于MAX+PLUS II环境下的各种分析,对于各分模块只是作些必要的说明。

) UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是一种应用广泛的短距离串行传输接口。

UART允许在串行链路上进行全双工的通信。

串行外设用到的RS232-C异步串行接口,一般采用专用的集成电路即UART实现。

如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。

或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。

基于FPGA的UART 16倍频采样的VHDL设计

基于FPGA 的UART 16 倍频采样的VHDL 设计概述随着电子设计自动化(EDA)技术的发展,可编程逻辑器件FPGA/CPLD 已经在许多方面得到了广泛应用,而UART(通用异步收发器) 是在数字通信和控制系统中广泛使用的串行数据传输协议。

因此越来越多用户根据自己的需要,以EDA 技术作为开发手段,用一块FPGA/CPLD 设计出符合自己需要的UART 芯片。

基于FPGA/ CPLD 的UART 设计在诸多文献中都有论述,在此不再对UART 整个功能模块实现做太多的论述。

本文着重分析UART 接收器起始位的检测。

3 倍频采样的缺陷首先,串行异步通信规定了字符数据的传送格式。

每一帧数据由起始位、数据位、奇偶校验位、停止位和线路空闲状态组成,格式如图1 所示。

一般情况起始位为1 位,数据位为5、6、7 或8 位、奇偶校验位为1 位,停止位为1、1.5 或2 位。

其中的起始位和停止位就是用来实现字符的同步。

在空闲状态,传送线为逻辑1 状态。

数据的传送总是以一个起始位开始的,接着是要传送的若干数据位,低位先行,最后是一个1 状态的停止位;那么,当接收器检测到一个1 向0 的跳变时,便视为可能的起始位。

起始位被确认后,就知道发送器已开始发送,当接收了已协议好的位数后并接收到字符帧中停止位就是一帧字符数据已发送完毕。

这样,接收器就知道发送器何时开始发送数据和何时结束发送数据。

要提高接收器的接收准确性,减少误码率,必须要用比数据波特率高n 倍(n≥1)的速率对数据进行采样。

文献2 中采用了非常规的3 倍频采样方法:用3 倍频的波特率对每一位数据进行采样(如图2 所示),然后对3 次采样结果进行判决。

如果3 次采样中至少有2 次为高电平,则接收这一位数据被判决为。

基于FPGA的UART通信接口电路设计

率发 生 器 、IO 接 口 、 A T发 送 子 模 块 、 信 校 验 FF U R 通 模块 , 场试验 表 明 了该 接 口电路 具有 良好 的实用性 现

及可 靠性 。

1 功 能设计

1 1 过 采 样 流 程 .

一

不 够灵 活 , 数据 位数 固定 、 信 的波 特率 一般 限制 在 通 几 个 固定 的数值 , 可扩 展性 较小 。 FG P A是 在传 统 P L、A A G L等 可 编程 器 件 的基 础 上 进一 步发 展 的产 物 , 使 用 非 常 灵 活 , 其 同一 片 F — P G A通 过 不 同 的 编 程 数 据 可 以 产 生 不 同 的 电路 功 能 j 。随着 F G P A技 术 的 突 飞 猛 进 , 在 通 信 系 其

目 , 国的煤矿设备 自动化程度不断提高 , 前 我 井

下作 业对 信号 传 输 的要 求 也 愈 趋 严 格 。本 文 研究 的

通用 串行 收发 器 ( nvra ay crnu eevrad u iesl snho o srci n e

需求 建 立 自己 的 高层 通 信 协 议 。本 文使 用 F G 来 PA 设计 满 足矿 井 通 信 的 R 22接 口电路 。使 用 F G S3 PA

个U R A T一 般 包 括 发 送 器 和 接 收 器 两 部 分 。

UR A T发 送 器 的主要 功能是 读 入并 行 的待 发送 数 据 , 然 后通 过移 位 寄存 器 , 以一 定 的 波特 率 , 数 据 一 位 将 位地 串行移 出 ; 收器的 主要 功能则 是 串行 读人 接 收 接

tnmtrU R ) r s ie, A T 可通 过 串行 线 传输 并 行 数 据 , 本 a t 其 质功 能是 作为控 制 器和 串行设 备 问 的编码转 换装 置 , 在基 于 R 2 2 R 4 5等标 准协 议 的通信 系 统 中广泛 S3 、 S8 应用 ¨ J非常 适 合 矿 井 通 信 系 统 。常 用 的单 片 机 、 , D P控 制器 等一 般都 集成 有专 用 的 U R S A T外 设 , 大 极 地方便 了基于 R 22等 协议 的通 信 系统 设 计 。但 这 S3

基于FPGA的UART模块化设计

几 r 广. 几 厂. 几 . n 几 r ] 弋 门. 弋n 一 ]几 n 几 几 几 几 r n n r ] n

广 1 _

Tas ie) 得 到 了相 当广 泛 的 应 用 , 允 许 串行 链 路 rnmt r t 也 它 广- 1 上 进行 全双 工 通 信 。 一般 使 用 通 用 的 U R A T接 口芯 片 , 但 这 种 芯 片 存 在 电路 复 杂 , 本 高 , 低 了 系统 的 可 靠 成 降 图 2 波 特 率发 生 器 仿 真 结 果 性 和稳定度 , 由于 结 构 和 功 能 的相 对 固 定 , 因而 我 们 不 能 根 据 自 己的 设 计 需 要 去 进 行 剪 裁 和 移 植 。 而 日益成 熟 的 S P 所 以分 频 器 对 晶振 的 分频 数 为 3 6 每 一 计 数 周期 周期 使 输 出 电平 OC 2, (yt nPorm beC i 技 术要 求将 整 个 设 计 功 能 集 成 到 ~ 高 、 变 化 , S s m O rga mal h e p) 低 即可 得 到 9 0 6 0波特 率对 应 的 U R 的时 钟 。 图 2为波 AT 块或几块芯 片中, 文通过对 U R 本 A T功 能 的 分析 , 出 了在 F G 特率 发生 器 的 仿真 波形 。 提 PA 22接 收器 模 块 接 收 模块 从 捕 捉到 数据 串的 第 一 个 0开 始 工 - 上 集成 U R A T功 能模 块 , 强 了设 计 的 灵活 性 , 化 了电 路 , 通 过 增 简 并 有 限状 态 机 来描 述 核 心 功 能控 制 逻 辑 , 而 提 高 了整 个 系统 稳 定 性 作 , 也 就 是 验 证 起 始 位 的 到 从 来 , 证 完 后 , 始 接 收 8位 验 开 数 据 , 进 行 串并 转 换 , 后 并 随 正 UR A T是 异 步 通 信 方 式 , 基 本 的 U R 最 A T通 信 只 需 要 两 条信 号 检测停止 位 , 确则输 出。接 所 线 ( X ,X 就 可 以完 成 数 据 的相 互 通 信 , 收 和 发 送 是 全 双 工 收 器状 态 转换 如 图 3 示 。 R DT D) 接 的 , 接收端, 在 串行 的数 字 信 号 转 化成 并 行 的信 号 , 能进 行 处理 数 才 接 收 器 状 态 机 共 包 含 四 据 , 发送 端 , 行 的 信 号 转 化 成 串行 信 号 才 能被 发送 到 另 一 个 设 个 状 态 : 闲 状 态 ( L 、 在 并 空 I E)检 D 备 中使 用 。 测 起 始 位 ( T R 、 据 采 样 S A T)数 S IT)停 S O U R A T帧 格 式 ( 就 是 发送 数据 的格 式 )是 以 一 个 起始 位 开 始 (H F 、 止 位检 测 (T P o 也 ,

uart驱动电路设计

uart驱动电路设计摘要:一、uart驱动电路设计概述1.uart驱动电路的作用2.uart驱动电路的设计目标二、uart驱动电路设计原理1.uart通信的基本原理2.uart驱动电路的关键组件3.uart驱动电路的工作流程三、uart驱动电路设计步骤1.确定电路拓扑结构2.选择合适的元器件3.设计电路原理图4.布局与布线5.仿真与测试四、uart驱动电路设计实践1.基于FPGA的uart驱动电路设计2.基于ASIC的uart驱动电路设计3.常见问题与解决方案五、uart驱动电路设计展望1.新技术的发展趋势2.应用领域的拓展3.我国在uart驱动电路设计方面的优势与挑战正文:一、uart驱动电路设计概述uart驱动电路,即通用异步接收发送器(Universal Asynchronous Receiver/Transmitter)驱动电路,是一种用于实现串行通信的电路。

在电子设备中,uart驱动电路主要负责数据的接收与发送,其性能直接影响到通信的质量和效率。

因此,设计一个高性能、稳定的uart驱动电路是通信系统设计中的关键环节。

二、uart驱动电路设计原理1.uart通信的基本原理uart通信是一种异步通信方式,数据是按照位(bit)进行传输的。

发送方将数据从并行转换为串行,按位发送给接收方。

接收方收到串行数据后,再将其转换为并行数据。

在通信过程中,双方需要约定一个波特率(baud rate),即每秒传输的位速率。

2.uart驱动电路的关键组件uart驱动电路主要包括以下几个关键组件:(1)uart芯片:作为核心部件,负责数据的接收与发送。

(2)电平转换器:用于将uart芯片与外部逻辑电平进行转换,以保证通信的稳定性。

(3)波特率发生器:产生所需的波特率信号,用于同步数据传输。

(4)其他辅助元件:如电阻、电容、二极管等,用于组成电路的基本组成部分。

3.uart驱动电路的工作流程uart驱动电路的工作流程主要包括以下几个步骤:(1)数据接收:uart芯片接收来自其他设备的串行数据。

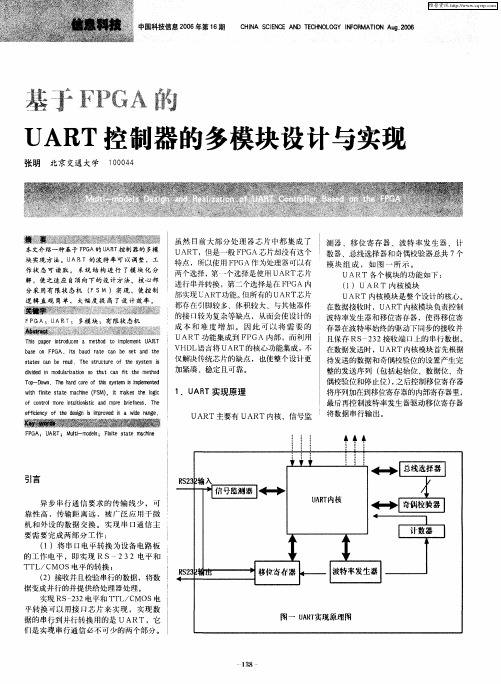

基于FPGA的UART控制器的多模块设计与实现

作 状 态 可 读 取 。 系 统 结 构 进 行 了模 块 化 分

测 器 、移位 寄 存器 、波 特 率发 生器 、计 数 器、总线选择 器和奇偶校验 器总共 7个

模 块 组 成 ,如 图一 所 示 。 UART 各个模块 的功 能如下 :

解 ,使之适应 自顶 向下的设 计方 法。核 心部

、

U R A T实现原 理

UART主要有 UART内核、信号监

F GA; U R P A T; M l -mo e ; Fnt sa e ma h e ut i dl s i e t t c l i n

引言

异步 串行通 信要 求的 传输 线 少 ,可 靠性 高 ,传输 距离远 ,被广 泛应 用于微 机和 外设 的数据 交换 。 实现 串 口通信 主 要需要 完成 两部分 工作 : ( )将 串 口电平 转换 为设备 电路板 1 的 工 作 电 平 ,即 实 现 R S 232 电平 和 TTL CMOS电平的转换 ; / ( )接收并且检验 串行的数据,将数 2 据变成并行的并提供给处理 器处理 。

b s n P A. 1 b u r t c n e e a d h a e o F G t a d a e a b s t n t e S sa e c n e ra . T e tu t r o t e s se i t t s a b e d h s rc ue f h y t m S d ie r m d lr a i S t a a f te me h d i d d i o u i to O h t c n i h t o v l az n t

基于FPGA的UART通信接口电路设计

基于FPGA的UART通信接口电路设计张蕾【摘要】随着煤矿设备自动化程度的不断提高,对信号的传输也提出了越来越高的要求.本文设计了一种基于现场可编程门阵列(field programmable gate array,FPGA)的RS232接口电路.首先,分析了FPGA在设计通用串行收发器(universal asynchronous receiver and transmitter,UART)接口电路中的优势.该接口电路主要分为UART接收子模块、波特率发生器、先进先出(first in first out,FIFO)模块、UART发送子模块、通信校验模块等.然后,基于Xilinx公司的FPGA平台,使用Verilog HDL语言编写并实现了整个系统,给出了完整的电路结构框图及实验结果.实验结果验证了所设计RS232接口电路的有效性.【期刊名称】《山西焦煤科技》【年(卷),期】2011(035)008【总页数】3页(P18-20)【关键词】通用串行收发器(UART);可编程门阵列(FPGA);过采样;先进先出(FIFO)【作者】张蕾【作者单位】山西煤炭进出口集团有限公司,山西太原 030006【正文语种】中文【中图分类】TD65目前,我国的煤矿设备自动化程度不断提高,井下作业对信号传输的要求也愈趋严格。

本文研究的通用串行收发器(universal asynchronous receiver and transmitter,UART)可通过串行线传输并行数据,其本质功能是作为控制器和串行设备间的编码转换装置,在基于RS232、RS485等标准协议的通信系统中广泛应用[1-3],非常适合矿井通信系统。

常用的单片机、DSP控制器等一般都集成有专用的UART外设,极大地方便了基于RS232等协议的通信系统设计。

但这类预先固化好的系统也存在一定的不足,如工作模式不够灵活,数据位数固定、通信的波特率一般限制在几个固定的数值,可扩展性较小。

基于FPGA的UART模块设计及仿真

Q a ul软件进行顶层和 R L级的仿真和观察 , dl ur s t I T Moe —

S 仿真 工 具 仿真 发 送 过 程 以及 应 用 开 发 板 上 L D等辅 i e r E 助显 示 接 收 数据 。结 果 使其 性 能 稳 定 ,并 在 此 设 计 基 础 上 更 容 易 扩 展 为 U A O E, 于 A I 计 的重 复 R TI C R 利 P SC设

Ke wo ds F y r : PGA ; UART; rlg;i l t n Ve i o smu a i o

UART( ie slAs n h o o sRe ev rTr n mi e Unv ra y c r n u c ie / a s t r) t

通 用 异 步 收 发 器 是 各 种 设 备 之 问进 行 通 信 的关 键 模 块 , 当一 个设 备 需 要 和另 一 个 连 接 的设 备 进 行 通信 时 ,通 常 采 用 数 字 信 号 。在 硬 件 方 面 采 用 的 是 基 于 Cc n yl eI o I FG P A系列 的开 发 板 ,时钟 晶振 为 5 z 0 MH 。本 文 在 做 以 FG P A为处理 器 的系 统设 计 时 , 用 V ro 硬件 描 述语 言 采 eig l

设 计 ,在 片 内集 成 了一 款 通用 性 较 强 的 U T模 块 。用 AR

起始位

( tr) s t a

2

奇偶位

( ai ) p r y t

停 止位

(t s p) o

图 1 数 据 传 输 时 序 图

2 U ART控 制器 的 Vei g实现 ro l

21 顶 层 模块 组成 结 构 .

Ab t a tT e s s e , sn P s r c : h y t m u i gF GA h pa ep o e s r p o i e c i s h r c s o , r v d s UART mo u e, h c e in d b rlg h r wa ed s rp i n t a d l w i h i d sg e yVe i a d r e c i t s o o

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第 33卷第 4期

孟志华 :利用 FPGA 实现 UART的设计

·通信技术 ·

使用 VHDL 将 UART的核心功能集成 ,从而使整个设 计更加紧凑 、稳定且可靠 。

下面分别设计 UART的 3个模块 (发送器 、接收器 和波特率产生器 ) ,并给出其仿真结果 。 3. 1 发送器设计

UART串行发送器模块框图如图 2 所示 。D IN 为 8位数据 ,其余为 1位 。

end if;

end if;

end p rocess; b_clk < = clk16x_t; / /输出波特率 ……

波特率功能仿真结果图略 。输入频率为 20 MHz, 波形周期为 50 ns, 20 MHz/ ( 9 600 bit/ s ×16 bit) = 130,由仿真结果可知输出波形的半个周期为 65 倍的 输入时钟周期 ,从而证明了波特率产生器模块的正确 性。

…… elsif ( clk’event and clk = ’1’) then if ( clk_div = clk_div_coef) then clk_div < = (others = > ’0’) ; clk16x_t < = not clk16x_t; / /取反 else clk_div < = clk_div + 1; / /除数加 1

1 总体设计

整个设计包括两部分 :基于 FPGA 的 UART的设 计和基于 VB6. 0的上位机程序设计 。UART的设计采 用模块化的设计思想 ,可分为 3个模块 : FPGA 数据发 送模块 、FPGA 波特率发生器控制模块及数据接收模 块 。上位机程序采用 VB 6. 0的 M scomm 控件 ,可分为 画面设计和功能设计两部分 。串口采用标准的 RS2 232 协议 ,主要参数选择为 :波特率 9 600 bit/ s, 8位有 效位 ,无奇偶校验位 , 1 位停止位 [ 1 ] 。

图 4 UART串行接收器模块框图

本设计只要求实现简单的收发功能 ,故未设计检 错程序 ,程序在侦测到起始位后 ,计 16个时钟周期 ,便 开始接收数据 ,移位输入 RSR ,最后输出数据 DOUT。 还要输出一个数据接收标志信号标志数据接收完 。实 现的部分 VHDL 程序如下 :

…… elsif clk1x’event and clk1x = ’1’then if std_logic_vector( no_bits_ rcvd) > =“0001”and std_ logic_vec2

tor( no_bits_rcvd) < =“1000”then rsr( 0) < = rxd2 ; / /数据帧数据由接收串行数据端移位入

R SR rsr(7 downto 1) < = rsr(6 downto 0) ; elsif std_logic_vector( no_bits_rcvd) =“1001”then rbr < = rsr; / /RSR数据进入 RBR ……

3. 3 波特率发生器的设计 UAR T的接收和发送是按照相同的波特率进行收

发的 。波特率发生器产生的时钟频率不是波特率时钟 频率 ,而是波特率时钟频率的 16 倍 ,目的是为在接收 时进行精确地采样 ,以提出异步的串行数据 [ 1 ] 。根据 给定的晶振时钟和要求的波特率算出波特率分频数 。 实现的部分 VHDL 程序如下 :

end if ; ……

图 3 发送器功能仿真结果

3. 2 接收器设计 UART串行接收器模块框图如图 4 所示 。DOUT

为 8位数据 ,其余为 1位 。接收器包含一个 8位 RBR 和 RSR。RBR 的状态可以通过引脚 DATA _READY来 表示 。当 RBR 中的数据有效时 , DATA _READY变为 高电平 ,向 CPU 表明可以取回数据 。

收稿日期 : 2006210208; 修回日期 : 2007203220。

·14·

UART主要包括接收器和发送器 。从异步接收输 入信号 SIN 接收到的异步信号通过接收器完成串行 / 并行的转换 ,形成异步数据帧 ;发送器将 CPU 发出的 8 位数据进行并行 /串行转换 ,从 SOUT发送出去 。功能 包括微处理器接口 、TBR (发送缓冲器 ) 、TSR (发送移 位寄存器 ) 、帧产生 、并转串 、RBR (接收缓冲器 ) 、RSR (接收移位寄存器 ) 、帧产生 、串转并 。UART的结构如 图 1所示 。

1. 5、2[ 1 ] 。 将 UART的程序编译 、仿真后 , 下载到 FPGA 的

EP1K30TC14423芯片上 。引入 20 MHz的晶振频率 ; 发送使能端和复位端分别接一个开关 ;状态输出标志 TRE和 DATA 2READTY 分别接 一个 二极 管 , 指示 状 态 ;设置波特率为“9 800, N , 8, 1 ”。串行数据帧的格 式为 :起始位 0, 8 位数据位 ,无校验位 , 1 位停止位 。 将 UART的串行发送 、接收端口分别与计算机的 RS2 232的串行接收 、发送端口连接 ,以便与 PC 机进行串 行通信 ;并行输入 D IN 接入并行输出 DOUT; 连好线 后 ,执行发送测试程序 。

关键词 : UART; FPGA;串行通信 ; MSCOMM32. OCX控件 ; VHDL 中图分类号 : TN919. 3

0 引 言

பைடு நூலகம்

2 UA RT的结构和帧格式

随着计算机技术的发展和广泛应用 ,尤其是在工 业控制领域的应用越来越广泛 ,计算机通信显的尤为 重要 。串行通信虽然使设备之间的连线大为减少 ,但 随之带来串 /并转换和位计数等问题 ,这使串行通信技 术比并行通信技术更为复杂 。串 /并转换可用软件实 现 ,也可用硬件实现 。用软件实现串行传送大多采用 循环移位指令将一个字节由高位到低位 (或低位到高 位 )一位一位依次传送 ,这种方法虽然简单但速度慢 , 而且大量占用 CPU 的时间 ,影响系统的性能 。更为方 便的实现方法是用硬件 ,目前微处理器串行接口常用 的 LSI芯片是 UART (通用异步收发器 ) 、USART (通用 同步异步收发器 )和 AC IA (异步通信接口适配器 )等 。 不论是哪一种芯片 ,它们的一种基本功能是实现串 /并 转换 。正是这些串行接口芯片弥补了串行通信较为复 杂这一缺陷 。本文应用 EDA (电子设计自动化 )技术 , 基于 FPGA (现场可编程门阵列 ) /CPLD (复杂可编程 逻辑器件 )设计与实现 UART。

5 结束语

在实现 FPGA 与 PC的串行通信中 ,将程序下载到 芯片中验证设计的正确性 ,目前还没有更好的工具可 以在下载后实时地对 FPGA 的工作情况和数据进行分 析 。通过串行通信 ,可以向 FPGA 发控制命令让其执 行相应的操作 ,同时把需要的数据通过串口发到 PC 上进行相应的数据处理和分析 ,以此来判断 FPGA 是 否按设计要求工作 。本文以 UART为重点讨论了 FP2 GA 与上位机串行通信的实现方法 。采用高级语言 VB 实现了上位机与 FPGA 的通信 。

3 UA RT的设计与实现

UART是广泛使用的串行数据传输协议 。UART 允许在串行链路上进行全双工的通信 。串行外设使用 RS22322C异步串行接口 , 一般采用专用集成电路即 UART实现 。如 8250、8251、NS16450等芯片都是常见 的 UART器件 ,这类芯片已经相当复杂 ,有的含有许多 辅助的模块 (如 F IFO ) ,有时不需要使用完整的 UART 的功能和这些辅助功能 ,或者使用了 FPGA /CPLD ,那 么就可以将所需要的 UART功能集成到 FPGA 内部 。

从图 2的框图可以看出 ,串行发送器中包含有一 个 8 位 THR (发送保持寄存器 )和 TSR (发送移位寄 存 ) 。复位 时 , 引 脚 TRE 为 高电 平 。当 数据 载 入 到 TSR 之后 ,引脚 TRE变为低电平 。发送完毕 , TRE 变 为高电平 。当侦测到输入 WRN 变为低电平时 ,自动 使能串行数据发送过程 。首先传送 1 位的起始位 (逻 辑电平 0 ) , 同时 THR 中 的数 据自 动地 并行 载入 到 TSR中 。然后 ,定长的数据位从 TSR 中移出 ,接着是 校验位 。最后 ,产生停止位 (逻辑电平 1 ) ,标志着一 帧的结束 。串行数据帧将以内部时钟频率的 1 /16 传 送 。如果 THR中内容不空 ,当一个串行数据帧传送结 束后 ,紧接着发送下一个数据帧 。这种自动的流程使 得数据帧以背靠背的方式发送 ,提高了数据传输的带 宽 。当没有数据发送时 , SDO 引脚保持高电平 。

接受器功 能仿 真结 果图 略 。串 行 输 入 RXD 为 0010101101,每一位占 16个时钟周期 ,一旦检测到输 入 RXD 为 0,计数器开始计数 ,开始接收数据 ,接收完 毕 ,标志位变为高电平 。仿真结果证明了接收模块的 正确性 。

·15·

·通信技术 ·

电子工程师

2007年 4月

摘 要 : 采用 VHDL 语言作为硬件功能的描述 ,硬件采用 A ltera公司的 EP1K30TC14423芯片 ,运 用模块化设计方法分别设计了 UART (通用异步收发器 )的发送器 、接收器和波特率发生器 。在 M ax2 p lusII环境下进行设计 、编译和仿真 ,并结合 FPGA (现场可编程门阵列 )的特点 ,实现了一个可编程的 UART模块 。上位机利用 VB6. 0编程实现 PC机与 UART的通信 。

vector( no_bits_sent) < =“1010”then tsr < = tsr(6 downto 0) &’0’; sdo < = tsr(7) ; / /从低位到高位进行移位输出至串行输出

端 elsif std_logic_vector( no_bits_send) =“1011”then sdo < = ’1’; / /停止位输出 tre < = ’1’; / /发送完毕标志置“1”