UART收发器设计实例

基于FPGA的UART电路设计与仿真

基于FPGA的UART电路设计与仿真基于FPGA的UART电路设计与仿真Design and Simulation of UART Circuit Based on FPGA(蚌埠中国⼈民解放军汽车管理学院) 杨⼤柱Yang, Dazhu摘要:⽂章介绍了⼀种采基于FPGA 实现UART电路的⽅法,并对系统结构进⾏了模块化分解以适应⾃顶向下的设计⽅法。

采⽤有限状态机对接收器模块和发送器模块进⾏了设计,所有功能的实现全部采⽤VHDL进⾏描述,并在Modelsim环境下进⾏了仿真,结果表明了该设计的正确性和可靠性。

关键词:UART;FPGA;RS-232;有限状态机中图分类号:TP332 ⽂献标识码:AAbstract:This paper introduces a method to design UART circuit based on FPGA. and the system structure is divided into modularization to fit the design method of Top-Down.The receiver and transfer are designed by FSM (Finite State Machine).All functions are described by VHDL.We stimulate the functions under Modelsim environment,the result proves the validity and reliability of the design.Keywords:UART;FPGA;RS-232;FSMUART(通⽤异步收发器)是⼴泛使⽤的串⾏数据传输协议。

UART允许在串⾏链路上进⾏全双⼯的通信。

专⽤的UART集成电路如8250,8251,NS16450等已经相当复杂,有些含有许多辅助的模块(如FIF0),在实际应⽤中,往往只需要⽤到UART的⼏个基本功能,使⽤专⽤芯⽚会造成资源浪费和成本提⾼,我们可以将所需要的UART功能集成到FPGA内部,从⽽简化了整个系统电路,提⾼了可靠性、稳定性和灵活性。

UART

通用异步收发器(Universal Asynchronous Receiver Transmitter,UART)是数字通信领域流行和广泛使用的一种接口设备,主要用来控制符合RS 232-C协议的计算机与串行设备间的通信。

普通串行外设和计算机间的通信,一般使用通用的串行接口芯片,但是这种接口芯片存在体积较大、接口复杂以及成本较高的缺点,会使得硬件设计更加复杂,并且结构与功能相对固定,无法根据设计的需要对其逻辑控制进行灵活的修改。

而目前日趋成熟的SOC技术则要求将整个设计的功能集成在单片或几块芯片当中,因此,将UART的功能集成在FPGA芯片当中,可以使整个系统更为灵活、紧凑,性能也更加稳定。

本文提出了一种使用VHDL语言开发UAWT的方法,实现了FPGA与计算机之间的数据通信,并将其应用于FPGA芯片开发的功能验证当中,从而衍生出了将UART嵌入到EPGA芯片,与计算机互联的一种直观的FPGA设计的验证和调试方法。

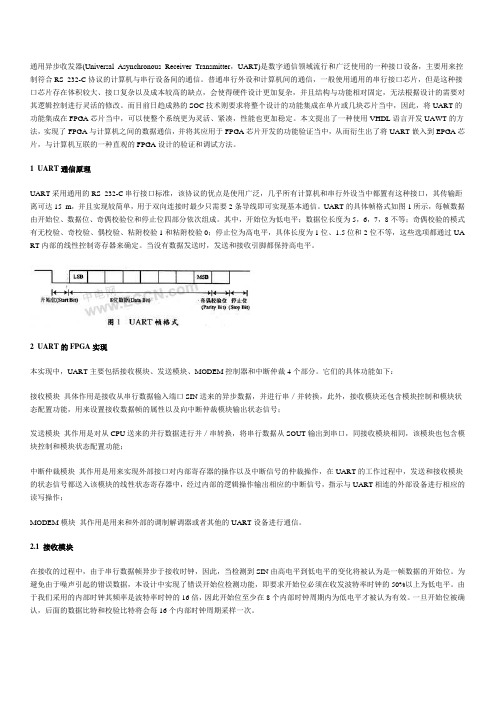

1 UART通信原理UART采用通用的RS 232-C串行接口标准,该协议的优点是使用广泛,几乎所有计算机和串行外设当中都置有这种接口,其传输距离可达15 m,并且实现较简单,用于双向连接时最少只需要2条导线即可实现基本通信。

UART的具体帧格式如图1所示,每帧数据由开始位、数据位、奇偶校验位和停止位四部分依次组成。

其中,开始位为低电平;数据位长度为5,6,7,8不等;奇偶校验的模式有无校验、奇校验、偶校验、粘附校验1和粘附校验0;停止位为高电平,具体长度为1位、1.5位和2位不等,这些选项都通过UA RT内部的线性控制寄存器来确定。

当没有数据发送时,发送和接收引脚都保持高电平。

2 UART的FPGA实现本实现中,UART主要包括接收模块、发送模块、MODEM控制器和中断仲裁4个部分。

它们的具体功能如下:接收模块具体作用是接收从串行数据输入端口SIN送来的异步数据,并进行串/并转换,此外,接收模块还包含模块控制和模块状态配置功能,用来设置接收数据帧的属性以及向中断仲裁模块输出状态信号;发送模块其作用是对从CPU送来的并行数据进行并/串转换,将串行数据从SOUT输出到串口,同接收模块相同,该模块也包含模块控制和模块状态配置功能;中断仲裁模块其作用是用来实现外部接口对内部寄存器的操作以及中断信号的仲裁操作,在UART的工作过程中,发送和接收模块的状态信号都送入该模块的线性状态寄存器中,经过内部的逻辑操作输出相应的中断信号,指示与UART相连的外部设备进行相应的读写操作;MODEM模块其作用是用来和外部的调制解调器或者其他的UART设备进行通信。

单片机UART通信实现

单片机UART通信实现在单片机系统中,UART(通用异步收发器)通信是一种常见的串口通信方式。

通过UART通信,可以实现单片机与外部设备之间的数据传输。

本篇文章将介绍如何使用单片机实现UART通信,并提供相应的代码示例。

一、UART通信原理UART通信是一种串行通信方式,其中数据按照位的形式依次传输。

UART接口包括发送端和接收端,发送端将要传输的数据通过串行方式发送出去,接收端将接收到的数据按位恢复为原始数据。

通信的核心是波特率,即数据传输的速度。

发送端和接收端必须以相同的波特率进行通信,以确保数据的正确传输。

二、单片机UART通信的硬件连接实现单片机UART通信的关键是正确连接相应的硬件。

典型的单片机UART通信硬件连接如下:发送端:- 单片机的TX(发送)引脚连接到外部设备的RX(接收)引脚- 单片机的GND引脚连接到外部设备的GND引脚接收端:- 单片机的RX(接收)引脚连接到外部设备的TX(发送)引脚- 单片机的GND引脚连接到外部设备的GND引脚三、单片机UART通信的软件实现在软件方面,需要编写相应的代码来配置单片机的UART通信模块。

以下是一个示例代码,用于实现基本的UART通信功能。

```c#include <reg51.h>#define BAUDRATE 9600 // 波特率设置为9600bpsvoid uart_init(){TMOD = 0x20; // 设置定时器1为8位自动重装模式TH1 = -(256 - (11059200 / 12 / 32) / BAUDRATE); // 设置波特率TL1 = TH1; // 初始化定时器1的初值TR1 = 1; // 启动定时器1SCON = 0x50; // 标识为8位UART模式EA = 1; // 允许全局中断ES = 1; // 允许串口中断}void uart_send(unsigned char dat)SBUF = dat; // 将数据写入发送寄存器 while (!TI); // 等待发送完毕TI = 0; // 清除发送完成标志}unsigned char uart_receive(){while (!RI); // 等待接收完毕RI = 0; // 清除接收标志return SBUF; // 返回接收到的数据}void main(){unsigned char data;uart_init(); // 初始化UART通信模块 while (1)data = uart_receive(); // 接收数据uart_send(data); // 发送接收到的数据}}```以上代码是基于8051系列单片机的实现示例,具体的单片机型号和编程语言可能有所不同,但基本原理是相同的。

十、UART控制器

TXD:发送数据

原理说明

UART使用标准的TTL/CMOS逻辑电平(0~5V、 0~3.3V、0~2.5V或0~1.8V)来表示数据,高电平 表示1,低电平表示0。为了增强数据的刚干扰能力, 提高传输长度,通常将TTL/CMOS逻辑电平转换为 RS-232逻辑电平,3~12V表示0,-3~-12表示1。 TXD、RXD数据线以“位”为最小的单位传输数 据。帧(frame)由具有完整意义的、不可分割的的若 干“位”组成。包括起始位、数据位、校验位(非必 需)和停止位。发送之前UART之间要约定好数据的 传输速率(即每位所占据的时间,其倒数称之为波 特率)、数据的传输格式。

– 溢出错误表明新数据在读出旧数据前覆盖了旧数据。 – 奇偶校验错误表明接收器检测出一个非预期奇偶校验字 段。 – 帧错误表明接收到的数据没有有效的结束位。

中断请求

•中断请求产生

• S3C2440A 的每个UART 包括7种状态(Tx/Rx/错误)信号: 溢出错误、奇偶校验错误、帧错误、断点、接收缓冲器数 据就绪、发送缓冲器空以及发送移位器空,全部都由相应 UART 状态寄存器(UTRSTATn/UERSTATn)标示。 • 溢出错误,奇偶校验错误、帧错误和断点状态被认为是接 收错误的状态。如果接收错误中断请求使能位在控制寄存 器UCONn中设置为1,则每个都可以引起接收错误中断请 求。当检测到接收错误中断请求,读取UERSTSTn的值识别 该信号引起请求。 • 当接收器在FIFO模式中转移接收移位器的数据到Rx FIFO 寄存器中,并且接收到的数据量达到Rx FIFO触发深度,并 且在控制寄存器 (UCONn)中的接收模式选择为1 (中断 请求或查询模式),则发生接收中断。在非FIFO模式中, 转移接受移位器的数据到接收保持寄存器,将在中断请求和 查询模式下引起Rx中断。

uart驱动电路设计

uart驱动电路设计摘要:1.UART 概述2.UART 驱动电路设计原则3.UART 驱动电路的主要组成部分4.UART 驱动电路设计流程5.设计实例与注意事项正文:一、UART 概述UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)是一种广泛应用于电子设备中的串行通信接口。

它的主要功能是在发送端将数据字符从并行转换为串行,按位发送到接收端,在接收端将串行数据字符转换为并行数据,以便于设备处理。

UART在电子设备中具有重要作用,如计算机外设、通信设备等。

二、UART 驱动电路设计原则1.稳定性:驱动电路应具有良好的稳定性,确保数据传输的可靠性。

2.兼容性:驱动电路应能兼容不同厂商、不同型号的UART 设备。

3.低功耗:驱动电路应在满足性能要求的前提下,尽量降低功耗。

4.简洁性:驱动电路设计应尽量简洁,便于调试和维护。

三、UART 驱动电路的主要组成部分1.电源模块:为驱动电路提供稳定的电源。

2.晶振模块:提供驱动电路的工作时钟。

3.复位模块:为驱动电路提供复位信号。

4.电平转换模块:实现UART 接口的电平转换,如TTL 电平转换为CMOS 电平。

5.串行发送模块:将数据字符从并行转换为串行,按位发送。

6.串行接收模块:将串行数据字符转换为并行数据。

7.缓存模块:缓存发送和接收的数据,以适应不同速率的UART 设备。

四、UART 驱动电路设计流程1.需求分析:明确驱动电路的功能、性能、兼容性等要求。

2.电路设计:根据需求分析,设计驱动电路的各个模块,并选择合适的元器件。

3.电路仿真:使用仿真软件对驱动电路进行仿真测试,验证电路性能。

4.硬件调试:制作驱动电路硬件原型,进行实际硬件调试。

5.软件调试:编写驱动程序,对驱动电路进行功能测试。

6.性能测试:对驱动电路的稳定性、兼容性、功耗等性能进行测试。

7.优化与完善:根据测试结果,对驱动电路进行优化与完善。

基于FPGA的UART16550的设计

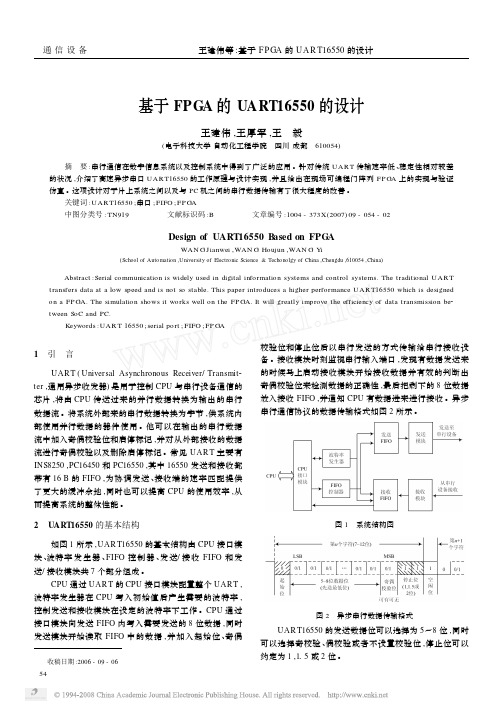

基于FPGA 的UART16550的设计王建伟,王厚军,王 毅(电子科技大学自动化工程学院 四川成都 610054)摘 要:串行通信在数字信息系统以及控制系统中得到了广泛的应用。

针对传统UAR T 传输速率低、稳定性相对较差的状况,介绍了高速异步串口UAR T16550的工作原理与设计实现,并且给出在现场可编程门阵列FP GA 上的实现与验证仿真。

这项设计对于片上系统之间以及与PC 机之间的串行数据传输有了很大程度的改善。

关键词:UAR T16550;串口;FIFO ;FP GA中图分类号:TN919 文献标识码:B 文章编号:1004-373X (2007)09-054-02Design of UART16550B ased on FPG AWAN G Jianwei ,WAN G Houjun ,WAN G Y i(School of Automation ,University of Electronic Science &Techonolgy of China ,Chengdu ,610054,China )Abstract :Serial communication is widely used in digital information systems and control systems.The traditional UAR T transfers data at a low speed and is not so stable.This paper introduces a higher performance UAR T16550which is designed on a FP GA.The simulation shows it works well on the FP GA.It will greatly improve the efficiency of data transmission be 2tween SoC and PC.K eywords :UAR T 16550;serial port ;FIFO ;FP GA收稿日期:2006-09-061 引 言UAR T (Universal Asynchronous Receiver/Transmit 2ter ,通用异步收发器)是用于控制CPU 与串行设备通信的芯片,将由CPU 传送过来的并行数据转换为输出的串行数据流。

linux uart收发原理

linux uart收发原理摘要:一、UART 简介二、Linux UART 驱动框架三、UART 接收原理四、UART 发送原理五、Linux UART 应用实例正文:一、UART 简介UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)是一种串行通信接口,广泛应用于电子设备之间的数据传输。

UART的主要作用是将数据从并行转换为串行,以便在通信线路上进行传输。

在接收端,UART再将串行数据转换为并行数据。

二、Linux UART 驱动框架Linux 内核中,UART 设备的驱动框架主要由以下几个部分组成:1.uart.h:UART 设备的头文件,定义了UART 设备的结构体和相关宏。

2.uart_class:UART 设备的类,包含了UART 设备的共性操作,如初始化、启动、停止等。

3.uart_device:UART 设备的实例,包含了UART 设备的硬件相关操作,如配置、发送、接收等。

4.uart_driver:UART 设备的驱动,包含了UART 设备的驱动程序,用于操作系统和硬件设备之间的通信。

三、UART 接收原理当UART 接收到数据时,首先会对数据进行解串行操作,即将串行数据转换为并行数据。

然后,UART 接收模块将数据传送给处理器进行处理。

在Linux 系统中,UART 接收数据的过程主要由以下步骤组成:1.配置UART 设备:在使用UART 设备之前,需要对其进行配置,包括波特率、数据位、停止位等。

2.开启UART 设备:配置完成后,需要启动UART 设备,使其进入工作状态。

3.读取UART 数据:通过读取UART 设备的数据寄存器,获取接收到的数据。

四、UART 发送原理当UART 需要发送数据时,首先会将数据进行串行操作,即将并行数据转换为串行数据。

然后,UART 发送模块将数据发送给接收设备。

在Linux 系统中,UART 发送数据的过程主要由以下步骤组成:1.配置UART 设备:在使用UART 设备之前,需要对其进行配置,包括波特率、数据位、停止位等。

基于FPGA的UART通信模块设计_20111002

一基于FPGA的UART通信模块设计1. UART简介(1)UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种应用广泛的短距离串行传输接口。

常常用于短距离、低速、低成本的通讯中。

8250、8251、NS16450等芯片都是常见的UART器件。

(2)基本的UART通信只需要两条信号线(RXD、TXD)就可以完成数据的相互通信,接收与发送是全双工形式。

TXD是UART发送端,为输出;RXD是UART接收端,为输入。

2. UART的基本特点是:(1) 在信号线上共有两种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。

在发送器空闲时,数据线应该保持在逻辑高电平状态。

(2) 起始位(Start Bit):发送器是通过发送起始位而开始一个字符传送,起始位使数据线处于逻辑0状态,提示接受器数据传输即将开始。

(3) 数据位(Data Bits):起始位之后就是传送数据位。

数据位一般为8位一个字节的数据(也有6位、7位的情况),低位(LSB)在前,高位(MSB)在后。

(4) 校验位(parity Bit):可以认为是一个特殊的数据位。

校验位一般用来判断接收的数据位有无错误,一般是奇偶校验。

在使用中,该位常常取消。

(5) 停止位:停止位在最后,用以标志一个字符传送的结束,它对应于逻辑1状态。

(6) 位时间:即每个位的时间宽度。

起始位、数据位、校验位的位宽度是一致的,停止位有0.5位、1位、1.5位格式,一般为1位。

(7) 帧:从起始位开始到停止位结束的时间间隔称之为一帧。

(8) 波特率:UART的传送速率,用于说明数据传送的快慢。

在串行通信中,数据是按位进行传送的,因此传送速率用每秒钟传送数据位的数目来表示,称之为波特率。

如波特率9600=9600bps(位/秒)。

3. FPGA UART系统组成FPGA UART由三个子模块组成:波特率发生器;接收模块;发送模块;包含四个模块:顶层模块,波特率发生器,UART接收器,UART发送器(1)顶层模块(1)异步收发器的顶层模块由波特率发生器、UART接收器和UART发送器构成。

基于FPGA的UART通信接口电路设计

率发 生 器 、IO 接 口 、 A T发 送 子 模 块 、 信 校 验 FF U R 通 模块 , 场试验 表 明 了该 接 口电路 具有 良好 的实用性 现

及可 靠性 。

1 功 能设计

1 1 过 采 样 流 程 .

一

不 够灵 活 , 数据 位数 固定 、 信 的波 特率 一般 限制 在 通 几 个 固定 的数值 , 可扩 展性 较小 。 FG P A是 在传 统 P L、A A G L等 可 编程 器 件 的基 础 上 进一 步发 展 的产 物 , 使 用 非 常 灵 活 , 其 同一 片 F — P G A通 过 不 同 的 编 程 数 据 可 以 产 生 不 同 的 电路 功 能 j 。随着 F G P A技 术 的 突 飞 猛 进 , 在 通 信 系 其

目 , 国的煤矿设备 自动化程度不断提高 , 前 我 井

下作 业对 信号 传 输 的要 求 也 愈 趋 严 格 。本 文 研究 的

通用 串行 收发 器 ( nvra ay crnu eevrad u iesl snho o srci n e

需求 建 立 自己 的 高层 通 信 协 议 。本 文使 用 F G 来 PA 设计 满 足矿 井 通 信 的 R 22接 口电路 。使 用 F G S3 PA

个U R A T一 般 包 括 发 送 器 和 接 收 器 两 部 分 。

UR A T发 送 器 的主要 功能是 读 入并 行 的待 发送 数 据 , 然 后通 过移 位 寄存 器 , 以一 定 的 波特 率 , 数 据 一 位 将 位地 串行移 出 ; 收器的 主要 功能则 是 串行 读人 接 收 接

tnmtrU R ) r s ie, A T 可通 过 串行 线 传输 并 行 数 据 , 本 a t 其 质功 能是 作为控 制 器和 串行设 备 问 的编码转 换装 置 , 在基 于 R 2 2 R 4 5等标 准协 议 的通信 系 统 中广泛 S3 、 S8 应用 ¨ J非常 适 合 矿 井 通 信 系 统 。常 用 的单 片 机 、 , D P控 制器 等一 般都 集成 有专 用 的 U R S A T外 设 , 大 极 地方便 了基于 R 22等 协议 的通 信 系统 设 计 。但 这 S3

《单片机原理与实践》 UART模块介绍

《单片机原理与实践》Cortex-M4 TM4C1294XL微处理器UART模块的介绍摘要:数据传输的接线方式大体上就是两种:一种是并行接口,一种是串行接口。

本组就串行接口展开研究,所谓串行接口是指数据在有限的几个IO上按照顺序,一位一位的进行传输。

UART、IIC、SPI、CAN、USB等只要是串行传输的接口,都是串口的一种,本文重点讨论的是其中的UART口。

一.UART定义通用异步收发器(Universal Asynchronous Receiver/ Transmitter, UART)是一个异步的串行通信接口。

UART模块将处理器内部的并行数据转换为串行数据,通过串行总线UnTX以异步通信的方式发送出去;另一方面它也可以接收UnRX 总线上的串行数据,转换为并行数据后返回给处理器进行处理。

异步模式是一种常用的通信方式,相对于同步模式,异步模式不需要一个专门的时钟信号来控制数据的收发,因此发送数据时位与位的间隙可以任意改变。

UART总线采用双向通信,可以实现全双工的发送和接收。

嵌入式设计中,UART用来与计算机或其他设备进行通信。

二.UART的优点这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,但其传输速度比并行传输低。

它很简单并且能够实现远距离通信。

比如IEEE488定义并行通行状态时,规定设备线总长不得超过20米,并且任意两个设备间的长度不得超过2米;而对于串口而言,长度可达1200米。

通信使用3根线完成:(1)地线,(2)发送,(3)接收。

由于串口通信是异步的,端口能够在一根线上发送数据同时在另一根线上接收数据。

串口通信最重要的参数是波特率、数据位、停止位和奇偶校验。

对于两个进行通信的端口,这些参数必须匹配。

三.UART与IIC、SPI的区别1、UART就是两线,一根发送一根接收,可以全双工通信,线数也比较少。

数据是异步传输的,对双方的时序要求比较严格,通信速度也不是很快。

1.通用异步收发器

1.通用异步收发器1.1通用异步收发器概述S5PV210的通用异步收发器(UART )提供四对独立的异步串行输入/输出(I / O)端口。

所有的端口操作基于中断或基于DMA的操作模式。

UART产生一个中断或DMA请求,将数据传输给CPU或者从CPU传输给UART 。

UART支持高达3Mbps比特率。

每个UART通道包含两个FIFO接收和发送数据:在ch0的256个字节,在ch1的64字节和在ch2和ch3 16个字节。

UART包括可编程波特率,红外(IR )发射器/接收器,一个或两个停止位插入, 5位, 6 位, 7位或8位数据宽度和奇偶校验。

每个UART包含一个波特率发生器,发送器,接收器和一个控制单元,如图1-1 。

波特率发生器采用PCLK或SCLK_UART 。

发射器和接收器包含FIFO和数据移位器。

要传输的数据被写入到Tx FIFO ,并复制到发送移位器。

然后,数据由发送数据引脚( TXDn )移出。

所接收的数据从接收数据引脚( RxDn )移位,并且从移位器复制到Rx FIFO。

1.2通用异步收发器的主要特点• RXD0 , TxD0, RXD1 , TXD1 ,RxD2 , TxD2, RXD3和TXD3带有基于DMA或基于中断的操作• UART通道0 ,1 ,2和3 具有IrDA 1.0• UART通道0具有256字节FIFO ,通道1具有64字节FIFO ,通道2和3具有16字节的FIFO• UART通道0 ,1和2具有 nRTS0 , nCTS0 , nRTS1 , nCTS1 , nCTS2和nRTS2的自动流控制功能•支持握手发送/接收。

图1-1UART的框图1.3 UART的说明以下各节描述的UART操作,如数据传输,数据接收,中断产生,波特率发生器,回环模式,红外模式和自动流控制1.3.1数据传输用于传输的数据帧是可编程的。

它由一个起始位,五至八个数据位,一个可选的奇偶性位,和一到两个停止位,由线路控制寄存器( ULCONn )指定。

实验七、UART串行数据通信实验

实验七、UART串行数据通信实验1(查询与中断方式)一、实验目的通过实验,掌握UART查询与中断方式的程序的设计。

二、实验设备●硬件:PC 机一台●LPC2131教学实验开发平台一套●软件:Windows98/XP/2000 系统,ADS 1.2 集成开发环境。

●EasyARM工具软件。

三、实验原理EasyARM2131 开发板上,UART0 的电路图如图8.1 所示,当跳线JP6 分别选择TxD0和RxD0 端时方可进行UART0 通讯实验。

图8.1 UART0 电路原理图四、实验内容实验内容1使用查询方式,通过串口0 接收上位机发送的字符串如“Hello EasyARM2131!”,然后送回上位机显示,主程序以及各子程序流程如图8.2 所示。

(改写发送内容,字符个数不同)。

说明:需要上位机(PC机)串口终端如EasyARM.exe 软件。

使用串口延长线把LPC2131教学实验开发平台的CZ2(UART0)与PC机的COM1 连接。

PC 机运行EasyARM 软件,设置串口为COM1,波特率为115200,然后选择【设置】->【发送数据】,在弹出的发送数据窗口中点击“高级”即可打开接收窗口。

图8.2 串口实验相关程序流程图1.实验预习要求①研读LPC2000 UART工作原理与控制章节,注意FIFO 接收情况的特性。

②了解LPC2131教学实验开发平台的硬件结构,注意串口部分的电路。

2.实验步骤①启动ADS 1.2,使用ARM Executable Image for lpc2131工程模板建立一个工程DataRet_C。

②在user 组中的main.c 中编写主程序代码,在项目中的config.h 文件中加入#include <stdio.h>。

③选用DebugInFlash生成目标,然后编译连接工程。

④将EasyARM2131开发板上的JP6跳线分别选择TxD0和RxD0端时,方可进行UART0通信实验。

UART串行扩展接口应用实例

UART串行扩展接口应用实例UART(Universal Asynchronous Receiver/Transmitter):通用异步收发器,既能同步又能异步通信的硬件电路称为UART。

UART是用于掌握计算机与串行设备的芯片,它供应了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其他使用RS-232C接口的串行设备通信了。

80C51的串行通信口是一个功能强大的通信口,而且是相当好用的通信口。

用于显示驱动电路特别合适,下面我们就依据这种需要用两个串行通信口线加上两根一般I/O口线,设计一个4位LED显示电路。

当然只要再加上两根I/O口线即可轻易实现8位LED显示电路。

例1:如图1所示的电原理图,利用74LS164串行输入并行输出芯片作一个简洁的电子钟,要求四个数码管显示时钟;其中LED1显示小时的十位,LED2显示小时的个位,LED3显示分钟的十位,LED4显示分钟的个位。

图1 串行动态LED扫描电路解:采纳单片机的串行口输出字形码,用74LS164和74LS139作为扩展芯片。

74LS164的功能是将80C51串行通信口输出的串行数据译码并在其并口线上输出,从而驱动LED 数码管。

74LS139是一个双2-4线译码器,它将单片机输出的地址信号译码后动态驱动相应的LED。

因74LS139电流驱动力量较小,故用末级驱动三极管9013作为地址驱动。

将4只LED的字段位都连在一起,它们的公共端则由74LS139分时选通,这样任何一个时刻,都只有一位LED在点亮,也即动态扫描显示方式,其优点使用串行口进行LED通信程序编写相当简洁,用户只需将需显示的数据直接送串口发送缓冲器,等待串行发送完毕标志位即可。

参考程序如下:上面是一个简洁的动态扫描程序,假如再利用上第6章的定时器就可做成一个完整的电子钟,四个数码管显示为00:00这种形式。

在本例中冒号就不显示出来了,分别用20H、21H 、22H、23H地址在放时间的时钟的十位、时钟的个位、分钟的十位、分钟的个位。

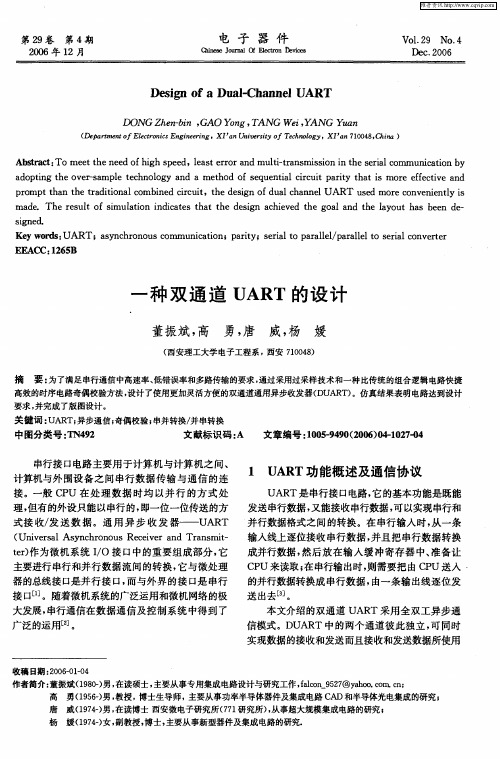

一种双通道UART的设计

大发展, 串行通信在数据通信及控制系统 中得到了

广 泛 的运用 - 。 2 J

本文介绍的双通道 U R A T采用全双工异步通

信模式。D A T中的两个通道彼此独立 , 同时 U R 可

实现数据的接收和发送而且接收和发送数据所使用

收稿 日期 :0 6O 一4 20 一l0

作者简介 : 斌(90) , 董振 18一男 在读硕士 , 主要从事专用集成 电路 设计与研究工作 , l n92@yhoCI c; f c _ 57 ao.O. n ao D .

DONG Zh n bn , e - i GAO o g, Y n TAN G e , A NG u n W iY Ya

( p r no De a t t fElcrnc En iern me eto is g neig,XJa nvri fT cn lg ’nU iest o eh oo y,XJ a 1 0 8 C ia) y ’n7 0 4 ,h n

( ie s lAs n h o o sRe ev r a d Tr n mi— Unv r a y c r n u c ie n a s t

1 U R A T功 能概述及通信协议

U R A T是串行接 口电路 , 的基本功能是既能 它 发送串行数据, 又能接收串行数据 , 以实现串行和 可 输入线上逐位接收 串行数据 , 并且把串行数据转换 成并行数据 , 后放在输入缓 冲寄存器 中、 然 准备 让 C U来读取 ; P 在串行输 出时, 则需要把由 C U送人 P 的并行数据转换成 串行数据 , 由一条输 出线逐位发

E ] = 16 B C: 2 5

一

种 双 通 道 U T的设 计 AR

董振 斌 , 高 勇 , 唐 威 , 杨 媛

基于DSP+FPGA的UART设计与实现

基于DSP+FPGA的UART设计与实现发表时间:2020-07-07T03:20:20.125Z 来源:《学习与科普》2020年4期作者:孙小美[导读] 这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

陕西烽火通信集团有限公司陕西宝鸡 721006摘要:UART作为RS232协议的控制接口得到广泛的应用,将UART功能集成在DSP和FPGA芯片组成的系统中,可使整个系统更为灵活、紧凑,减小电路体积,提高系统的可靠性和稳定性。

本文提出了一种基于DSP和FPGA 系统的UART 实现方法。

关键词:通用异步收发器;DSP;FPGA1 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,通常称作UART)是一种串行异步收发协议,应用十分广泛。

UART可以和各种标准串行接口,如RS232、RS485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART 由专用芯片来实现,但专用芯片引脚较多,内含许多辅助功能,在实际使用时往往只需要用到UART 的基本功能,使用专用芯片会造成资源浪费和成本提高[1]。

在DSP和FPGA组成的系统中,利用DSP芯片完成UART数据收发控制,FPGA完成UART数据具体的收发时序,二者利用EMIF接口配合,即可实现UART通信功能。

这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

2 UART原理UART是一种串行数据总线,用于全双工异步通信。

工作原理是将数据的二进制位按位进行传输。

基本的UART 只需要两条信号线(收、发)和一条地线就可以完成数据的互通,接收和发送互不干扰。

在UART通信协议中,信号线上的状态位高电平代表“1”,低电平代表“0”。

图1 UART数据传输格式UART 数据传输格式如图1所示,一个字符由起始位、数据位、校验位和停止位组成(其中校验位可选)。

gd32 freertos uart例子

gd32 freertos uart例子为了演示如何在GD32微控制器上使用FreeRTOS实现UART通信功能,我们可以按照以下步骤进行操作。

首先,我们需要准备相关的硬件和软件。

确保我们有一台可编程GD32微控制器的开发板,并且已经安装了适当的开发环境,例如MDK-ARM或者GCC。

接下来,我们需要创建一个新的FreeRTOS项目。

通过选择适当的开发环境和目标设备,我们可以设置好项目的配置。

确保我们已经正确地配置了系统时钟和外设。

然后,我们需要在项目中添加FreeRTOS库。

将FreeRTOS源文件和头文件复制到项目的适当目录中。

确保源文件包括任务、队列和定时器等必要组件。

接着,我们可以开始编写代码来实现UART通信功能。

创建一个新的任务函数,在其中初始化UART外设,并设置波特率、数据位和停止位等参数。

然后,通过调用FreeRTOS提供的API函数,在任务函数中实现UART的接收和发送功能。

例如,我们可以使用vTaskDelay函数来模拟接收或发送数据的时间间隔,使用xQueueSend和xQueueReceive函数来操作队列来存储和获取数据。

最后,我们需要在主函数中创建和启动任务。

通过调用xTaskCreate函数,我们可以创建一个新的任务,指定任务函数和任务优先级等参数。

然后,调用vTaskStartScheduler函数来启动FreeRTOS内核,并使任务开始执行。

总结一下,我们可以通过在GD32微控制器上使用FreeRTOS来实现UART通信功能。

通过合理配置项目和编写相应的代码,我们可以实现串口数据的收发。

这个例子将帮助我们更好地理解如何在FreeRTOS环境下进行任务调度和资源管理,以及如何使用UART外设进行通信。

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线(USB)等,这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文详细介绍了嵌入式系统设计的串行总线、驱动器和物理接口的特性,并为总线最优选择提供性能比较和选择建议。

由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。

目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。

微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C)和通用串行总线,以及车用串行总线,包括控制器区域网(CAN)和本地互连网(LIN)。

这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。

为了说明方便起见,本文的阐述是基于微处理器的设计。

串行与并行相比串行相比于并行的主要优点是要求的线数较少。

例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。

较少的线意味着所需要的控制器引脚较少。

集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。

相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。

另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB 板面积更大、更复杂,从而增加了硬件成本。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

11.5U A R T收发器设计实例U A R T(U n i v e r s a l A s y n c h r o n o u s R e c e i v e r T r a n s m i t t e r,通用异步收发器)是广泛使用的异步串行数据通信协议。

下面首先介绍U A R T硬件接口及电平转换电路,分析U A R T的传输时序并利用V e r i l o g H D L语言进行建模与仿真,最后通过开发板与P C相连进行R S-232通信来测试U A R T收发器的正确性。

1.5.111.5.1U A R T界面介绍本节所介绍的U A R T即美国电子工业协会定义的R S-232C,简称R S-232。

R S-232的接口一般有9针的D B9和25针的D B25,这里以9针为例,它的各个引脚的定义如表11-8所示。

表11-8D B9的引脚定义引脚功能缩写1资料载波检测D C D2接收数据R X D3发送数据T X D4数据终端准备就绪D T R5信号地G N D6数据准备就绪D S R7发送请求R T S8清除发送C T S9振铃提示R I由于R S-232的电气特性与F P G A引脚不相同,因此它们之间不能直接相连,对于R S-232的数据线,当为逻辑“1”时,对应电平是-15V~-3V;当为逻辑“0”时,对应电平是15V~3V。

因此,与F P G A相连之前必须进行电平转换,转换原理图如图11-39所示。

图11-39R S-232电平转换原理图1.5.211.5.2U A R T传输时序U A R T传输时序如图11-40所示。

图11-40U A R T传输时序发送数据过程:空闲状态,线路处于高电位;当收到发送数据指令后,拉低线路一个数据位的时间T,接着数据按低位到高位依次发送,数据发送完毕后,接着发送奇偶校验位和停止位(停止位为高电位),一帧资料发送结束。

接收数据过程:空闲状态,线路处于高电位;当检测到线路的下降沿(线路电位由高电位变为低电位)时说明线路有数据传输,按照约定的波特率从低位到高位接收数据,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如果正确则通知后续设备准备接收数据或存入缓存。

由于U A R T是异步传输,没有传输同步时钟。

为了能保证数据传输的正确性,U A R T采用16倍数据波特率的时钟进行采样。

每个数据有16个时钟采样,取中间的采样值,以保证采样不会滑码或误码。

一般U A R T一帧的数据位数为8,这样即使每个数据有一个时钟的误差,接收端也能正确地采样到数据。

U A R T的接收数据时序为:当检测到数据的下降沿时,表明线路上有数据进行传输,这时计数器C N T开始计数,当计数器为24=16+8时,采样的值为第0位数据;当计数器的值为40=24+16时,采样的值为第1位数据,依此类推,进行后面6个数据的采样。

如果需要进行奇偶校验,则当计数器的值为152时,采样的值即为奇偶位;当计数器的值为168时,采样的值为“1”表示停止位,一帧数据接收完成。

本节章将按上面的算法进行V e r i l o g H D L语言建模与仿真。

1.5.311.5.3U A R T分频器假设数据的波特率为p,则所需时钟的频率为16*p。

以波特率p为115200为例,系统时钟为50M H z,则分频系数为50000000/(16*115200)=27.127,取整为27。

分频器V e r i l o g H D L语言代码如下:m o d u l e c l k d i v(c l k,c l k o u t);i n p u t c l k;//系统时钟o u t p u t c l k o u t;//采样时钟输出r e g c l k o u t;r e g[15:0]c n t;a l w a y s@(p o s e d g e c l k)//分频进程b e g i ni f(c n t==16'd12)b e g i nc l k o u t<=1'b1;c n t<=c n t+16'd1;e n de l s e i f(c n t==16'd26)b e g i nc l k o u t<=1'b0;c n t<=16'd0;e n de l s eb e g i nc n t<=c n t+16'd1;e n de n de n d m o d u l e保存文件为c l k d i v.v,单击F i l e s→ C r e a t e/U p d a t e→ C r e a t e S y m b o l F i l e s f o r C u r r e n t F i l e命令,为c l k d i v.v生成原理图模块。

新建一个原理图文件,在原理图空白处双击,在弹出的S y m b o l对话框中选择P r o j e c t→ c l k i d v模块,单击O K按钮退出S y m b o l对话框。

在原理图的适当位置放置c l k d i v模块,并添加输入输出模块。

保存原理图为u a r t r x t x.b d f。

编译工程文件,编译无误后单击P r o c e s s i n g→ G e n e r a t e F u n c t i o n a l S i m u l a t i o n N e t l i s t,产生功能仿真网表。

新建波形仿真文件,加入输入输出信号,设置系统时钟信号c l k 的周期为20n s,保存波形文件为 u a r t r x t x.v w f,单击按钮进行分频器的波形仿真,波形仿真报告如图11-41所示。

图11-41分频器的波形仿真报告波形仿真报告说明:分频时钟输出实现了所需的27分频,分频模块得到正确验证。

1.5.411.5.4U A R T发送模块U A R T发送模块的功能:接收到发送指令后,把数据按U A R T协议输出,先输出一个低电平的起始位,然后从低到高输出8个数据位,接着是可选的奇偶校验位,最后是高电平的停止位。

V e r i l o g H D L语言代码如下:m o d u l e u a r t t x(c l k,d a t a i n,w r s i g,i d l e,t x);i n p u t c l k;//U A R T时钟i n p u t[7:0]d a t a i n;//需要发送的数据i n p u t w r s i g;//发送命令,上升沿有效o u t p u t i d l e;//线路状态指示,高为线路忙,低为线路空闲o u t p u t t x;//发送数据信号r e g i d l e,t x;r e g s e n d;r e g w r s i g b u f,w r s i g r i s e;r e g p r e s u l t;r e g[7:0]c n t;//计数器p a r a m e t e r p a r i t y m o d e=1'b0;//检测发送命令是否有效a l w a y s@(p o s e d g e c l k)b e g i nw r s i g b u f<=w r s i g;w r s i g r i s e<=(~w r s i g b u f)&w r s i g;e n da l w a y s@(p o s e d g e c l k)b e g i ni f(w r s i g r i s e&&(~i d l e))//当发送命令有效且线路为空闲时,启动新的数据发送进程 b e g i ns e n d<=1'b1;e n de l s e i f(c n t==8'd176)//一帧资料发送结束b e g i ns e n d<=1'b0;e n de n da l w a y s@(p o s e d g e c l k)b e g i ni f(s e n d==1'b1)b e g i nc a s e(c n t)//产生起始位8'd0:b e g i nt x<=1'b0;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd16:b e g i nt x<=d a t a i n[0];//发送数据0位 p r e s u l t<=d a t a i n[0]^p a r i t y m o d e;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd32:b e g i nt x<=d a t a i n[1];//发送数据1位 p r e s u l t<=d a t a i n[1]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd48:b e g i nt x<=d a t a i n[2];//发送数据2位 p r e s u l t<=d a t a i n[2]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd64:b e g i nt x<=d a t a i n[3];//发送数据3位 p r e s u l t<=d a t a i n[3]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd80:b e g i nt x<=d a t a i n[4];//发送数据4位 p r e s u l t<=d a t a i n[4]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd96:b e g i nt x<=d a t a i n[5];//发送数据5位 p r e s u l t<=d a t a i n[5]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd112:b e g i nt x<=d a t a i n[6];//发送数据6位 p r e s u l t<=d a t a i n[6]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd128:b e g i nt x<=d a t a i n[7];//发送数据7位 p r e s u l t<=d a t a i n[7]^p r e s u l t;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd144:b e g i nt x<=p r e s u l t;//发送奇偶校验位 p r e s u l t<=d a t a i n[0]^p a r i t y m o d e;i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd160:b e g i nt x<=1'b1;//发送停止位i d l e<=1'b1;c n t<=c n t+8'd1;e n d8'd176:b e g i nt x<=1'b1;i d l e<=1'b0;//一帧资料发送结束 c n t<=c n t+8'd1;e n dd e f a u l t:b e g i nc n t<=c n t+8'd1;e n de n d c a s ee n de l s eb e g i nt x<=1'b1;c n t<=8'd0;i d l e<=1'b0;e n de n de n d m o d u l e保存文件为u a r t t x.v,单击F i l e s→ C r e a t e/U p d a t e→ C r e a t e S y m b o l F i l e s f o r C u r r e n t F i l e命令,为u a r t t x.v生成原理图模块。