MS3106F36-5PY;中文规格书,Datasheet资料

BP3106中文规格书

6 保护功能

IOUT

=

I P_PK 4

×

NP NS

其中,Np 是变压器主级的匝数,Ns 是变压器次级 的匝数,Ip_pk 是主级侧的峰值电流。

3 反馈网络

芯片通过 FB 来反馈输出电流的状态, FB 的阈值 电压设置在 1V,建议 FB 检测的上分压电阻和下分 压电阻比值设计在 4.0 左右。为了提高系统效率, 反馈检测网络的上分压电阻可以设计到 300KΩ~750KΩ。

符号

描述

条件

最小值 典型值 最大值 单位

电源电压 VCC_th VUVLO VOVP

VCC_clamp

芯片启动电压 欠压保护阈值 过压保护阈值 VCC 钳位电压

VCC 升高

13

14

15

V

6.5

V

16

V

19

V

电流采样 VCS_th TLEB TDelay

电流检测阈值 前沿消隐时间 芯片关断延迟

480

500

晶丰明源半导体

BP3106

高精度原边反馈 LED 恒流驱动芯片

概述

特点

BP3106 是一款高精度原边反馈的 LED 恒流控制芯片。 适用于输入电压 85Vac~264Vac 全电压范围 30W 以 内反激式隔离 LED 恒流电源。

BP3106 工作在电感电流断续模式,采用原边反馈模 式,无需次级反馈电路,也无需补偿电路即可实现 恒流,极大的节约系统成本和体积。芯片采用了专 利的恒流控制方式,可以达到优异的线性调整率和 负载调整率。

BP3106 内置多种保护功能。当 Vcc 电压高于 16V 时,芯片关断外部功率管,芯片自动重启直到外 部过压状态解除;Vcc 内部自带 19V 钳位电路,以 防止异常条件下芯片损坏。

DS3106LN+;中文规格书,Datasheet资料

DS3106 Line Card Timing ICGeneral Description The DS3106 is a low-cost timing IC for telecom line cards. The device accepts two reference clocks from dual redundant system timing cards, continually monitors both inputs, and performs manual reference switching if the primary reference fails. The highly programmable DS3106 supports numerous input and output frequencies including frequencies required for SONET/SDH, Synchronous Ethernet (1G, 10G, and 100Mbps), wireless base stations, and CMTS systems. PLL bandwidths from 18Hz to 400Hz are supported, and a wide variety of PLL characteristics and device features can be configured to meet the needs of many different applications.The DS3106 register set is backward compatible with Semtech’s ACS8526 line card timing IC. The DS3106 pinout is similar but not identical to the ACS8526.Applications SONET/SDH, Synchronous Ethernet, PDH, and Other Line Cards in WAN Equipment IncludingMSPPs, Ethernet Switches, Routers, DSLAMs,and Wireless Base StationsSimplified Functional DiagramFeatures ♦Advanced DPLL Technology♦Programmable PLL Bandwidth: 18Hz to 400Hz♦Manual Reference Switching♦Holdover on Loss of All Input References♦Frequency Conversion Among SONET/SDH, PDH, Ethernet, Wireless, and CMTS Rates♦Two Input Clocks♦CMOS/TTL Signal Format (≤ 125MHz)♦Numerous Input Clock Frequencies Supported Ethernet xMII: 2.5, 25, 125, 156.25MHzSONET/SDH: 6.48, N x 19.44, N x 51.84MHzPDH: N x DS1, N x E1, N x DS2, DS3, E3Frame Sync: 2kHz, 4kHz, 8kHzCustom Clock Rates: Any Multiple of 2kHz Upto 125MHz♦Two Output Clocks♦One CMOS/TTL Output (≤ 125MHz)♦One LVDS/LVPECL Output (≤ 312.50MHz)♦Two Optional Frame-Sync Outputs: 2kHz, 8kHz♦Numerous Output Clock Frequencies Supported Ethernet xMII: 2.5, 25, 125, 156.25, 312.5MHzSONET/SDH: 6.48, N x 19.44, N x 51.84MHzPDH: N x DS1, N x E1, N x DS2, DS3, E3Other: 10, 10.24, 13, 30.72MHzFrame Sync: 2kHz, 8kHzCustom Clock Rates: Any Multiple of 2kHz Up to77.76MHz, Any Multiple of 8kHz Up to311.04MHz, Any Multiple of 10kHz Up to388.79MHz♦General♦Suitable Line Card IC for Stratum 3/3E/4, SMC, SEC♦Internal Compensation for Master Clock Oscillator ♦SPI™ Processor Interface♦ 1.8V Operation with 3.3V I/O (5V Tolerant)♦Industrial Operating Temperature RangeOrdering Information PART TEMP RANGE PIN-PACKAGEDS3106LN -40°C to +85°C 64 LQFPDS3106LN+ -40°C to +85°C 64 LQFP+Denotes a lead(Pb)-free/RoHS-compliant package.Data Sheet April 20121.STANDARDS COMPLIANCE (6)2.APPLICATION EXAMPLE (7)3.BLOCK DIAGRAM (7)4.DETAILED DESCRIPTION (8)5.DETAILED FEATURES (9)5.1I NPUT C LOCK F EATURES (9)5.2DPLL F EATURES (9)5.3O UTPUT APLL F EATURES (9)5.4O UTPUT C LOCK F EATURES (9)5.5G ENERAL F EATURES (9)6.PIN DESCRIPTIONS (10)7.FUNCTIONAL DESCRIPTION (14)7.1O VERVIEW (14)7.2D EVICE I DENTIFICATION AND P ROTECTION (14)7.3L OCAL O SCILLATOR AND M ASTER C LOCK C ONFIGURATION (14)7.4I NPUT C LOCK C ONFIGURATION (15)7.4.1Signal Format Configuration (15)7.4.2Frequency Configuration (15)7.5I NPUT C LOCK M ONITORING (16)7.5.1Frequency Monitoring (16)7.5.2Activity Monitoring (16)7.5.3Selected Reference Activity Monitoring (17)7.6I NPUT C LOCK P RIORITY AND S WITCHING (18)7.7DPLL A RCHITECTURE AND C ONFIGURATION (19)7.7.1T0 DPLL State Machine (20)7.7.2Bandwidth (23)7.7.3Damping Factor (23)7.7.4Phase Detectors (23)7.7.5Loss-of-Lock Detection (24)7.7.6Frequency and Phase Measurement (25)7.7.7Input Jitter Tolerance (25)7.7.8Jitter Transfer (25)7.7.9Output Jitter and Wander (25)7.8O UTPUT C LOCK C ONFIGURATION (25)7.8.1Signal Format Configuration (26)7.8.2Frequency Configuration (26)7.9M ICROPROCESSOR I NTERFACE (34)7.10R ESET L OGIC (37)7.11P OWER-S UPPLY C ONSIDERATIONS (37)7.12I NITIALIZATION (37)8.REGISTER DESCRIPTIONS (38)8.1S TATUS B ITS (38)8.2C ONFIGURATION F IELDS (38)8.3M ULTIREGISTER F IELDS (38)8.4R EGISTER D EFINITIONS (39)9.JTAG TEST ACCESS PORT AND BOUNDARY SCAN (74)9.1JTAG D ESCRIPTION (74)9.2JTAG TAP C ONTROLLER S TATE M ACHINE D ESCRIPTION (75)9.3JTAG I NSTRUCTION R EGISTER AND I NSTRUCTIONS (77)9.4JTAG T EST R EGISTERS (78)10.ELECTRICAL CHARACTERISTICS (79)10.1DC C HARACTERISTICS (79)10.2I NPUT C LOCK T IMING (82)10.3O UTPUT C LOCK T IMING (82)10.4SPI I NTERFACE T IMING (83)10.5JTAG I NTERFACE T IMING (85)10.6R ESET P IN T IMING (86)11.PIN ASSIGNMENTS (87)12.PACKAGE INFORMATION (89)13.THERMAL INFORMATION (89)14.ACRONYMS AND ABBREVIATIONS (90)15.DATA SHEET REVISION HISTORY (91)Figure 2-1. Typical Application Example (7)Figure 3-1. Block Diagram (7)Figure 7-1. DPLL Block Diagram (19)Figure 7-2. T0 DPLL State Transition Diagram (21)Figure 7-3. FSYNC 8kHz Options (33)Figure 7-4. SPI Clock Phase Options (36)Figure 7-5. SPI Bus Transactions (36)Figure 9-1. JTAG Block Diagram (74)Figure 9-2. JTAG TAP Controller State Machine (76)Figure 10-1. Recommended Termination for LVDS Output Pins (81)Figure 10-2. Recommended Termination for LVPECL-Compatible Output Pins (81)Figure 10-3. SPI Interface Timing Diagram (84)Figure 10-4. JTAG Timing Diagram (85)Figure 10-5. Reset Pin Timing Diagram (86)Figure 11-1. Pin Assignment Diagram (88)Table 1-1. Applicable Telecom Standards (6)Table 6-1. Input Clock Pin Descriptions (10)Table 6-2. Output Clock Pin Descriptions (10)Table 6-3. Global Pin Descriptions (11)Table 6-4. SPI Bus Mode Pin Descriptions (12)Table 6-5. JTAG Interface Pin Descriptions (12)Table 6-6. Power-Supply Pin Descriptions (13)Table 7-1. Input Clock Capabilities (15)Table 7-2. Input Clock Default Frequency Configuration (15)Table 7-3. Locking Frequency Modes (15)Table 7-4. Damping Factors and Peak Jitter/Wander Gain (23)Table 7-5. Output Clock Capabilities (25)Table 7-6. Digital1 Frequencies (27)Table 7-7. Digital2 Frequencies (27)Table 7-8. APLL Frequency to Output Frequencies (T0 APLL and T4 APLL) (28)Table 7-9. T0 APLL Frequency Configuration (28)Table 7-10. T0 APLL2 Frequency Configuration (28)Table 7-11. T4 APLL Frequency Configuration (29)Table 7-12. OC3 and OC6 Output Frequency Selection (29)Table 7-13. Standard Frequencies for Programmable Outputs (30)Table 7-14. T0FREQ Default Settings (32)Table 7-15. T4FREQ Default Settings (32)Table 7-16. OC6 Default Frequency Configuration (32)Table 7-17. OC3 Default Frequency Configuration (33)Table 8-1. Register Map (39)Table 9-1. JTAG Instruction Codes (77)Table 9-2. JTAG ID Code (78)Table 10-1. Recommended DC Operating Conditions (79)Table 10-2. DC Characteristics (79)Table 10-3. CMOS/TTL Pins (80)Table 10-4. LVDS Output Pins (80)Table 10-5. LVPECL Level-Compatible Output Pins (81)Table 10-6. Input Clock Timing (82)Table 10-7. Input Clock to Output Clock Delay (82)Table 10-8. Output Clock Phase Alignment, Frame-Sync Alignment Mode (82)Table 10-9. SPI Interface Timing (83)Table 10-10. JTAG Interface Timing (85)Table 10-11. Reset Pin Timing (86)Table 11-1. Pin Assignments Sorted by Signal Name (87)Table 13-1. LQFP Package Thermal Properties, Natural Convection (89)Table 13-2. LQFP Theta-JA (θJA) vs. Airflow (89)Table 1-1. Applicable Telecom Standards2. Application ExampleFigure 2-1. Typical Application Example3. Block DiagramFigure 3-1. Block DiagramLocal OscillatorDS31064.Detailed DescriptionFigure 3-1 illustrates the blocks described in this section and how they relate to one another. Section 5 provides a detailed feature list.The DS3106 is a complete line card timing IC. At the core of this device is a digital phase-locked loop (DPLL). DPLL technology makes use of digital-signal processing (DSP) and digital-frequency synthesis (DFS) techniques to implement PLLs that are precise, flexible, and have consistent performance over voltage, temperature, and manufacturing process variations. The DS3106’s T01DPLL is digitally configurable for input and output frequencies, loop bandwidth, damping factor, pull-in/hold-in range, and a variety of other factors. The T0 DPLL can directly lock to many common telecom frequencies and also can lock at 8kHz to any multiple of 8kHz up to 156.25MHz. The DPLL can also tolerate and filter significant amounts of jitter and wander.In typical line card applications, the T0 DPLL takes reference clock signals from two redundant system timing cards, monitors both, selects one, and uses that reference to produce a variety of clocks that are needed to time the outgoing traffic interfaces of the line card (SONET/SDH, Synchronous Ethernet, etc.). To perform this role in a variety of systems with diverse performance requirements, the T0 DPLL has a sophisticated feature set and is highly configurable. T0 can automatically transition among free-run, locked, and holdover states without software intervention. In free-run, T0 generates a stable, low-noise clock with the same frequency accuracy as the external oscillator connected to the REFCLK pin. With software calibration the DS3106 can even improve the accuracy to within ±0.02ppm. When the selected input reference clock has been validated, T0 transitions to the locked state in which its output clock accuracy is equal to the accuracy of the input reference. While in the locked state, T0 acquires an average frequency value to use as the holdover frequency. When its selected reference fails, T0 can very quickly detect the failure and enter the holdover state to avoid affecting its output clock. From holdover it can be manually switched to another input reference. When all input references are lost, T0 stays in the holdover state, in which it generates a stable low-noise clock with initial frequency accuracy equal to its stored holdover value and drift performance determined by the quality of the external oscillator.At the front end of the T0 DPLL is the Input Clock Selector, Divider, and Monitor (ICSDM) block. This block continuously monitors both input clocks for activity and coarse frequency accuracy. In addition, ICSDM can manually select one of the input clocks to be the selected reference for the T0 DPLL. The ICSDM block can also divide the selected clock down to a lower rate as needed by the DPLL.The Output Clock Synthesizer and Selector (OCSS) block shown in Figure 3-1and in more detail in Figure 7-1 contains three output APLLs—T0 APLL, T0 APLL2, and T4 APLL—and their associated DFS engines and output divider logic plus several additional DFS engines. The APLL DFS blocks perform frequency translation, creating clocks of other frequencies that are phase/frequency locked to the output clock of the T0 DPLL. The APLLs multiply the clock rates from the APLL DFS blocks and simultaneously attenuate jitter. Altogether the output blocks of the DS3106 can produce more than 90 different output frequencies including common SONET/SDH, PDH, and Synchronous Ethernet rates plus 2kHz and 8kHz frame-sync pulses.The entire chip is clocked from the external oscillator connected to the REFCLK pin. Thus, the free-run and holdover stability of the DS3106 is entirely a function of the stability of the external oscillator, the performance of which can be selected to match the application: typically XO or TCXO. The 12.8MHz clock from the external oscillator is multiplied by 16 by the Master Clock Generator block to create the 204.8MHz master clock used by the remainder of the device.1The labels T0 and T4 in this document are adapted from output ports of the SETS function specified in ITU-T and ETSI standards such as ETSI EN 300 462-2-1. Although strictly speaking these names are appropriate only for timing card ICs such as the DS3100 that can serve as the SETS function, the names have been carried over to the DS3106 so that all of the products in Maxim’s timing IC product line have consistent nomenclature.5.Detailed Features5.1Input Clock Features•Two programmable-frequency CMOS/TTL input clocks•Input clocks accept any multiple of 2kHz up to 125MHz•All input clocks are constantly monitored by programmable activity monitors5.2DPLL Features•High-resolution DPLL plus three low-jitter output APLLs•Sophisticated state machine automatically transitions between free-run, locked, and holdover states •Programmable bandwidth from 18Hz to 400Hz•Separately configurable acquisition bandwidth and locked bandwidth•Programmable damping factor to balance lock time with peaking: 1.2, 2.5, 5, 10, or 20•Multiple phase detectors: phase/frequency, early/late, and multicycle•Phase/frequency locking (±360° capture) or nearest edge phase locking (±180° capture)•Multicycle phase detection and locking (up to ±8191UI) improves jitter tolerance and lock time•High-resolution frequency and phase measurement•Holdover frequency averaging over 1 second interval•Fast detection of input clock failure and transition to holdover mode•Low-jitter frame sync (8kHz) and multiframe sync (2kHz) aligned with output clocks5.3Output APLL Features•Three separate clock-multiplying, jitter attenuating APLLs can simultaneously produce SONET/SDH rates, Fast/Gigabit Ethernet rates, and 10G Ethernet rates, all locked to a common reference clock •The T0 APLL has frequency options suitable for N x 19.44MHz, N x DS1, N x E1, N x 25MHz, and N x 62.5MHz•The T4 APLL has frequency options suitable for N x 19.44MHz, N x DS1, N x E1, N x DS2, DS3, E3, N x 10MHz, N x 10.24MHz, N x 13MHz, N x 25MHz, and N x 62.5MHz•The T0 APLL2 produces 312.5MHz for 10G Synchronous Ethernet applications5.4Output Clock Features•Two output clocks: one CMOS/TTL (≤ 125MHz) and one LVDS/LVPECL (≤ 312.50MHz)•Output clock rates include 2kHz, 8kHz, N x DS1, N x E1, DS2, DS3, E3, 6.48MHz, 19.44MHz, 38.88MHz,51.84MHz, 77.76MHz, 155.52MHz, 311.04MHz, 2.5MHz, 25MHz, 125MHz, 156.25MHz, 312.50MHz,10MHz, 10.24MHz, 13MHz, 30.72MHz, and various multiples and submultiples of these rates •Custom clock rates also available: any multiple of 2kHz up to 77.76MHz, any multiple of 8kHz up to 311.04MHz, and any multiple of 10kHz up to 388.79MHz•All outputs have < 1ns peak-to-peak output jitter; outputs from APLLs have < 0.5ns peak-to-peak•8kHz frame-sync and 2kHz multiframe-sync outputs have programmable polarity and pulse width, and can be disciplined by a 2kHz or 8kHz sync input5.5General Features•Operates from a single external 12.800MHz local oscillator (XO or TCXO)•SPI serial microprocessor interface•Four general-purpose I/O pins•Register set can be write protected6.Pin DescriptionsTable 6-1. Input Clock Pin DescriptionsPIN NAME(1)TYPE(2)PIN DESCRIPTIONREFCLK I Reference Clock. Connect to a 12.800MHz, high-accuracy, high-stability, low-noise local oscillator (XO or TCXO). See Section 7.3.IC3 I PD Input Clock 3. CMOS/TTL. Programmable frequency. Default frequency selected by IPF[2:0] pins when the RST pin goes high, 8kHz if IPF[2:0] pins left open.IC4 I PD Input Clock 4. CMOS/TTL. Programmable frequency. Default frequency selected by IPF[2:0] pins when the RST pin goes high, 8kHz if IPF[2:0] pins left open.Table 6-2. Output Clock Pin DescriptionsPIN NAME(1)TYPE(2)PIN DESCRIPTIONOC3 O Output Clock 3. CMOS/TTL. Programmable frequency. Default frequency selected byO3F[2:0] pins when the RST pin goes high, 19.44MHz if O3F[2:0] pins left open. See Table 7-17.OC6POS, OC6NEG O DIFFOutput Clock 6. LVDS/LVPECL. Programmable frequency. Default frequency selected byO6F[2:0] pins when the RST pin goes high, 38.88MHz if O6F[2:0] pins left open. The outputmode is selected by MCR8.OC6SF[1:0]. See Table 10-4, Table 10-5, Figure 10-1,and Figure 10-2.FSYNC O38kHz FSYNC. CMOS/TTL. 8kHz frame sync or clock (default 50% duty cycle clock, noninverted). The pulse polarity and width are selectable using FSCR1.8KINV and FSCR1.8KPUL.MFSYNC O32kHz MFSYNC. CMOS/TTL. 2kHz frame sync or clock (default 50% duty cycle clock, noninverted). The pulse polarity and width are selectable using FSCR1.2KINV and FSCR1.2KPUL.分销商库存信息: MAXIMDS3106LN+。

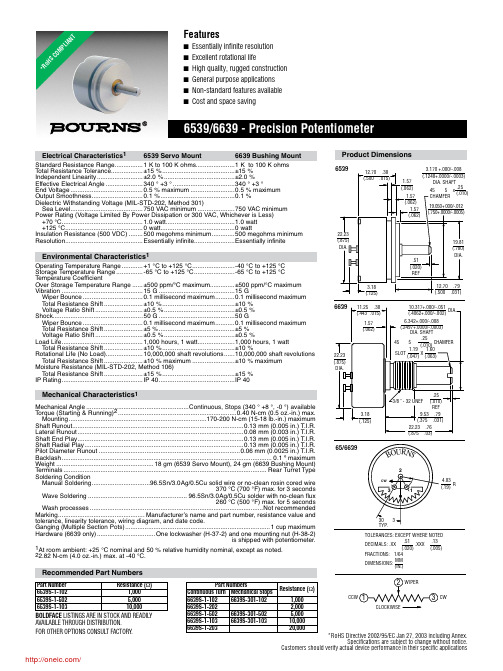

6639S-1-103;6639S-1-102;6639S-1-104;6639S-1-202;6639S-1-203;中文规格书,Datasheet资料

22.23 (.875) DIA.

3.18 (.125)

6639

11.25 .38 (.443 .015)

1.57 (.062)

Байду номын сангаас

22.23 (.875) DIA.

.51 (.020) REF

19.81 (.780) DIA.

12.70 .79 (.500 .031)

10.317+.000/-.051 (.4062+.000/-.002)

DIA.

6.342+.000/-.008

(.2497+.0000/-.0003) DIA. SHAFT .25

45 5 (.010) CHAMFER 1.19 1.60

SLOT (.047) X (.063)

Mechanical Characteristics1

Mechanical Angle ..........................................................Continuous, Stops (340 ° +8 °, -0 °) available Torque (Starting & Running)2 ...................................................................0.40 N-cm (0.5 oz.-in.) max.

Sea Level......................................... 750 VAC minimum .....................750 VAC minimum Power Rating (Voltage Limited By Power Dissipation or 300 VAC, Whichever is Less)

SDS3106(ESOP8) LED驱动芯片规格书说明书

SDS3106(ESOP8)规格书(2014年10月份Version:V2.0)目录一、产品说明 (2)二、产品特性 (2)三、应用领域 (3)四、引脚排列及定义 (4)五、最大额定值及电气特性 (5)六、功能描述 (6)七、封装尺寸 (7)中山芯动力电子科技有限公司杨婷一、产品说明SDS3106是一款高压线性恒流LED驱动芯片。

采用专利主动电容填谷技术,将最高驱动功率提高到18W。

芯片内部集成1.5mA7.5V低压电源,用于驱动红外感应。

芯片集成开关调光功能,可以通过普通墙面开关实现正向/反向三级调光,以及调色温功能。

芯片内部集成DIMM调光功能,通过片外电阻可以实现10%~100%之间任意比例的调光。

二、产品特性⏹输出功率2~18W⏹AC185-265V工作电压⏹PF值>0.6~0.9⏹开关调光和DIMM调光⏹无频闪⏹恒流精度<±3%⏹温度补偿和过压保护中山芯动力电子科技有限公司杨婷三、应用领域⏹LED日光灯T5/T8/T10等规格8w/16w/18w/25w/36w⏹LED吸顶灯、台灯8w/12w/18w/25w/36w⏹LED灯泡3w/5w/7w/8w/9w/10w/11w/12w/14w⏹LED筒灯3w/5w/7w/8w/9w/10w/11w/12w/14w⏹LED路灯、街灯20w/30w/50w⏹LED面板灯15w/22w/36w中山芯动力电子科技有限公司杨婷四、引脚排列及定义a)引脚排列b)引脚定义PinOrderPinNameIn/Out Function Discription 1CAP In/Out开关调光滤波接口,接滤波电容到地2DIMM In/Out DIMM调光接口,接2K~20K电阻到地,实现10%~100%调光功能3VDD Power低压电源输出,驱动能力**********4CS Output采样电阻引脚,接采样电阻到地5DOUT2Input高压恒流源输出,接散热电阻6DOUT1Input高压恒流源输出,接灯串7CB Input填谷电容下极板输入8GATE Output片外填谷MOS管栅极输出9GND Power芯片地中山芯动力电子科技有限公司五、最大额定值及电气特性a)最大额定值项目最小最大单位存储温度-40125℃工作温度-40125℃电流驱动端耐压500--V封装热阻--33℃/W静电耐受度2000--V b)电气特性中山芯动力电子科技有限公司杨婷六、功能描述图1SDS3106系统框图如图1所示,为SDS3106系统框图。

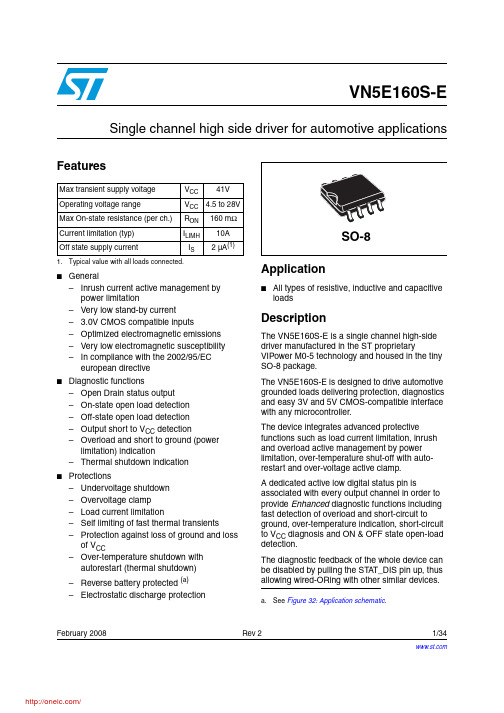

VN5E160S-E;VN5E160STR-E;中文规格书,Datasheet资料

February 2008Rev 21/34VN5E160S-ESingle channel high side driver for automotive applicationsFeatures■General–Inrush current active management by power limitation–Very low stand-by current– 3.0V CMOS compatible inputs–Optimized electromagnetic emissions –Very low electromagnetic susceptibility –In compliance with the 2002/95/EC european directive ■Diagnostic functions–Open Drain status output –On-state open load detection –Off-state open load detection –Output short to V CC detection–Overload and short to ground (power limitation) indication–Thermal shutdown indication■Protections–Undervoltage shutdown –Overvoltage clamp –Load current limitation–Self limiting of fast thermal transients–Protection against loss of ground and loss of V CC–Over-temperature shutdown with autorestart (thermal shutdown)–Reverse battery protected (a)–Electrostatic discharge protectionApplication■All types of resistive, inductive and capacitive loadsDescriptionThe VN5E160S-E is a single channel high-side driver manufactured in the ST proprietaryVIPower M0-5 technology and housed in the tiny SO-8 package.The VN5E160S-E is designed to drive automotive grounded loads delivering protection, diagnostics and easy 3V and 5V CMOS-compatible interface with any microcontroller.The device integrates advanced protectivefunctions such as load current limitation, inrush and overload active management by power limitation, over-temperature shut-off with auto-restart and over-voltage active clamp.A dedicated active low digital status pin isassociated with every output channel in order to provide Enhanced diagnostic functions including fast detection of overload and short-circuit to ground, over-temperature indication, short-circuit to V CC diagnosis and ON & OFF state open-load detection.The diagnostic feedback of the whole device can be disabled by pulling the STAT_DIS pin up, thus allowing wired-ORing with other similar devices.Max transient supply voltage V CC41VOperating voltage rangeV CC 4.5 to 28V Max On-state resistance (per ch.)R ON 160 m ΩCurrent limitation (typ)I LIMH 10A Off state supply currentI S2 µA (1)1.Typical value with all loads connected. a.See Figure 32: Application schematic .Contents VN5E160S-EContents1Block diagram and pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.1Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.2Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.3Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152.4Electrical characteristics curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.1GND protection network against reverse battery . . . . . . . . . . . . . . . . . . . 223.1.1Solution 1: resistor in the ground line (RGND only) . . . . . . . . . . . . . . . . 223.1.2Solution 2: diode (DGND) in the ground line . . . . . . . . . . . . . . . . . . . . . 233.2Load dump protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233.3MCU I/Os protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233.4Open load detection in Off state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243.5Maximum demagnetization energy (VCC=13.5V) . . . . . . . . . . . . . . . . . 254Package and PCB thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264.1SO-8 thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265Package and packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295.1ECOP ACK® packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295.2Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295.3Packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 6Order codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 7Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332/34VN5E160S-E List of tables List of tablesTable 1.Pin function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Table 2.Suggested connections for unused and not connected pins . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 3.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table 4.Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Table 5.Power section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 6.Switching (VCC=13V; Tj=25°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 7.Status pin (V SD=0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 8.Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 9.Open load detection (8V<V CC<18V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 10.Logic input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 11.Truth table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Table 12.Electrical transient requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 13.Thermal parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 14.SO-8 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 15.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Table 16.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333/34List of figures VN5E160S-E List of figuresFigure 1.Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 2.Configuration diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 3.Current and voltage conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4.Status timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 5.Output voltage drop limitation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 6.Switching characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 7.Normal operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 8.Undervoltage shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 9.Overload or Short to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 10.Intermittent Overload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 11.Open Load with external pull-up. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 12.Open Load without external pull-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 13.Short to V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 14.T J evolution in Overload or Short to GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 15.Off state output current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 16.High level input current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 17.Input clamp voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 18.Input high level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 19.Input low level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 20.Low level STAT_DIS current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 21.On state resistance vs T case. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 22.High level STAT_DIS current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 23.On state resistance vs V CC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 24.Low level input current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 25.I LIM vs T case . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 26.Turn-On voltage slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 27.Undervoltage shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 28.Turn-Off voltage slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 29.STAT_DIS clamp voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 30.High level STAT_DIS voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 31.Low level STAT_DIS voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 32.Application schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 33.Open load detection in Off state. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 34.Maximum turn-Off current versus inductance (for each channel). . . . . . . . . . . . . . . . . . . . 25 Figure 35.SO-8 PC board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 36.Rthj-amb Vs. PCB copper area in open box free air condition. . . . . . . . . . . . . . . . . . . . . . 26 Figure 37.SO-8 thermal impedance junction ambient single pulse. . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 38.Thermal fitting model of a single channel HSD in SO-8 . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 39.SO-8 package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Figure 40.SO-8 tube shipment (no suffix). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 41.SO-8 tape and reel shipment (suffix “TR”) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 4/34VN5E160S-E Block diagram and pin configuration5/341 Block diagram and pin configurationTable 1.Pin functionName FunctionV CCBattery connection.OUTPUT Power output.GND Ground connection. Must be reverse battery protected by an external diode/resistor network.INPUT Voltage controlled input pin with hysteresis, CMOS compatible. Controls output switch state.STA TUS Open Drain digital diagnostic pin.ST A T_DISActive high CMOS compatible pin, to disable the ST A TUS pin.Block diagram and pin configuration VN5E160S-E6/34Figure 2.Configuration diagram (top view)Table 2.Suggested connections for unused and not connected pins Connection / pin Status N.C.Output Input STAT_DIS Floating X X X X XT o groundNotallowedXNotallowedThrough 10KΩresistorThrough 10KΩresistorV CCV CCOUTPUTOUTPUTSTAT_DISGNDSTATUSINPUT14586723SO-8VN5E160S-E Electrical specifications7/342 Electrical specificationsNote:V F = V OUT - V CC during reverse battery condition.2.1 Absolute maximum ratingsStressing the device above the ratings listed in the “Absolute maximum ratings” tables maycause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to the conditions in the “Absolute maximum ratings” tables for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and others relevant quality documents.Table 3.Absolute maximum ratingsSymbol ParameterValue Unit V CC DC supply voltage 41V - V CC Reverse DC supply voltage 0.3V - I GND DC reverse ground pin current 200mA I OUT DC output currentInternally limitedA - I OUT Reverse DC output current 6A I IN DC input current +10 / -1mA I STATDC status current+10 / -1mA I STAT_DIS DC status disable current +10 / -1mA E MAXMaximum switching energy (single pulse)(L=8 mH; R L =0Ω; V bat =13.5V; T jstart =150ºC; I OUT = I limL (Typ.) )36mJElectrical specifications VN5E160S-E8/34Symbol Parameter Value Unit V ESDElectrostatic discharge (Human body model: R=1.5KΩ;C=100pF)–INPUT–ST A TUS–ST A T_DIS–OUTPUT–V CC40004000400050005000VVVVV V ESD Charge device model (CDM-AEC-Q100-011)750V T j Junction operating temperature-40 to 150°C T stg Storage temperature- 55 to 150°CTable 4.Thermal dataSymbol Parameter Max. value Unit R thj-pins Thermal resistance junction-pins30°C/W R thj-amb Thermal resistance junction-ambient See Figure 36.°C/W Table 3.Absolute maximum ratings (continued)VN5E160S-E Electrical specifications9/342.2 Electrical characteristicsValues specified in this section are for 8V<V CC <28V; -40°C< Tj <150°C, unless otherwisestated.Table 5.Power sectionSymbol ParameterTest conditionsMin.Typ.Max.Unit V CC Operating supply voltage 4.51328V V USD Undervoltage shutdown 3.5 4.5V V USDhystUndervoltage shutdown hysteresis0.5V R ON On state resistance I OUT =1A; T j =25°C I OUT =1A; T j =150°CI OUT =1A; V CC =5V; T j =25°C 160320210m Ωm Ωm ΩV clampClamp voltageI S =20 mA414652V I SSupply currentOff State; V CC =13V; V IN =V OUT =0V; T j =25°COn State; V IN =5V; V CC =13V; I OUT =0A2(1)1.91.PowerMOS leakage included.5(1)3.5µA mA I L(off1)Off state output current V IN =V OUT =0V; V CC =13V; T j =25°C V IN =V OUT =0V; V CC =13V; T j =125°C 000.0135µA µA V FOutput - V CC diode voltage-I OUT =0.6A; T j =150°C0.7VTable 6.Switching (V CC =13V;T j =25°C)Symbol Parameter Test conditions Min.Typ.Max.Unit t d(on)T urn-On delay time R L =13Ω (see Figure 6.)10µs t d(off)T urn-Off delay timeR L =13Ω (see Figure 6.)15µs dV OUT /dt (on)T urn-On voltage slope R L =13Ω See Figure 26.V/µs dV OUT /dt (off)T urn-Off voltage slopeR L =13Ω See Figure 28.V/µs W ON Switching energy losses during t wonR L =13Ω (see Figure 6.)70µJ W OFFSwitching energy losses during t woffR L =13Ω (see Figure 6.)40µJElectrical specifications VN5E160S-E10/34Table 7.Status pin (V SD=0)Symbol Parameter Test conditions Min.Typ.Max.Unit V STA TStatus low outputvoltageI STA T= 1.6 mA, V SD=0V0.5VI LSTA T Status leakage currentNormal operation or V SD=5V,V STAT= 5V10µAC STA TStatus pin inputcapacitanceNormal operation or V SD=5V,V STAT= 5V100pF V SCL Status clamp voltageI STA T= 1mAI STA T= - 1mA5.5-0.77VV Table 8.Protection (1)1.To ensure long term reliability under heavy overload or short circuit conditions, protection and relateddiagnostic signals must be used together with a proper software strategy. If the device is subjected toabnormal conditions, this software must limit the duration and number of activation cycles.Symbol Parameter Test conditions Min.Typ.Max.UnitI limHDC short circuitcurrentV CC=13V; 5V<V CC<28V7101414AAI limLShort circuit currentduring thermal cyclingV CC=13V; T R<T j<T TSD 2.5A T TSDShutdowntemperature150175200°C T R Reset temperature T RS + 1T RS + 5°C T RSThermal reset ofSTA TUS135°C T HYSTThermal hysteresis(T TSD-T R)7°C t SDLStatus delay inoverload conditionsT j>T TSD (see Figure4)20µs V DEMAGT urn-off output voltageclampI OUT=1A; V IN=0; L=20mH V CC-41V CC-46V CC-52VV ONOutput voltage droplimitationI OUT=0.03A (see Figure 5.)T j= -40°C...+150°C25mV分销商库存信息:STMVN5E160S-E VN5E160STR-E。