CYONS1001L-LBXC中文资料

REX-C100 系列 模拟式温度控制器 说明书

Notes:Make sure that this Instruction Manual is always readily available to personnel who use the REX-C100 series.The contents of the Instruction Manual are subject to change without notice. If you have any questions regarding the manual,contact one of our sales people, our nearest sales office, or the place where you have purchased the controller.1.PRODUCT CHECKCheck whether the delivered product is as specified by referring to the following model code list.OModel codeC100 QQQ - Q ~ QQÎ Ï Ð Ñ Ò ÓÎControl actionÓSecond alarm [ALM2]F : PID action [Reverse action]N : No second alarmD : PID action [ Direct action]A : Deviation high alarm *2B : Deviation low alarm *2ÏInput typeC : Deviation high / low alarm *2See input range table “Model code” page 9D : Band alarmE : Deviation high alarm *3ÐInput rangeF : Deviation low alarm *3See input range table “Model code” page 9G : Deviation high / low alarm *3H : Process high alarm *2ÑControl output [OUT]J : Process low alarm *2M : Relay contact K : Process high alarm *3V : Voltage pulseL : Process low alarm *38 : Current 4 to 20mA DCP : Heater break alarm (CTL-6)G : Trigger (for triac driving) *1S : Heater break alarm (CTL-12)R : Control loop break alarm *4ÒFirst alarm [ALM1]N : No first alarm*1When control output is trigger output A : Deviation high alarm *2for triac driving, only the first alarm isB : Deviation low alarm *2available.C : Deviation high / low alarm *2*2Without hold action.D : Band alarm*3With hold actionE : Deviation high alarm *3*4As control loop break alarm, only eitherF : Deviation low alarm *3the first alarm or second alarm is G : Deviation high / low alarm *3selected.H : Process high alarm *2J : Process low alarm *2CConfirm that power supply voltage is alsoK : Process high alarm *3the same as that specified when ordering.L : Process low alarm *3R : Control loop break alarm *4Accessories C Mounting brackets (2 pcs.)CInstruction manual(1 copy)REX-C100SERIESINSTRUCTION MANUALFig. 1Fig. 22.MOUNTING •DimensionsUnit : mm (inch)* Dimensions in inches are shown for reference•Mounting proceduresThickness of panel board:1 to 5mm or 5 to 9mm (0.04 to 0.20 inch or 0.20 to 0.35 inch)uWhen the controllers are mounted on panel with 1 to 5mm in thickness ÎMake a rectangular cutout corresponding to thenumber of controllers to be mounted on panel by referring to the panel cutout dimensions.ÏSince the mounting brackets are already installed onthe controller, insert the controller into the panel from the panel front without removal of the brackets (Fig. 1).uWhen the controllers are mounted on panel with 5 to 9m in thickness ÎRemove the mounting brackets from the controllerwith a slotted screwdriver.ÏEngage each mounting bracket with holes markedwith “5.9" on the housing (Fig. 2) and then insert the controller into the panel from the panel front.OCautions for mountingMo untingbracketAvoid the following location where the controller is mounted.C Location where ambient temperature is more than 50E C (122E F) or less than 0E C (32E F).C Location where humidity is high.C Location where corrosive gas is generated.C Location where strong vibration and shock exist.C Location where flooding and oil splash exist.C Location where much dust exists.CLocation where inductive disturbance is large and otherlocation where bad influence is exerted on electric instrument.3.WIRING•Rear terminalsNotes1.Terminals which are not used according to the controller type are all removed.2.For thermocouple input, no metal piece is attached to terminal No. 10. Instead, the temperature compensationelement in the internal assembly is projected through a hole at terminal No. 10.Do not damage the above temperature compensation element when the internal assembly is removed from the case.O Cautions for wiring(1)Conduct input signal wiring away from instrument, electric(3)For wiring, use wires conforming to domesticequipment power and load lines as such as possible to avoid standard of each country.noise induction.(4)About 5 to 6 sec. are required as the(2)Conduct instrument power wiring so as not to be influenced preparation time of contact output duringby noise from the electric equipment power.power ON. Use a delay relay whenthe outputIf it is assumed that a noise generation source is located near line, is used for an external interlock circuit.the controller and the controller is influenced by noise, use anoise filter (select the filter by checking instrument power(5)The figures below show the REX-C100 circuit supply voltage.)configuration. When connecting wires, notethat the power, input, MCU and output circuitsC Sufficient effect may not be obtained depending on the are isolated independently, while the inside offilter. Therefore, select the filter by referring to its the input and outputcircuits are not isolated.frequency characteristic, etc.ÎFor instrument power wiring, if it is assumed that noiseexerts a bad influence upon the controller, shorten thedistance between twisted power supply wire pitches.(The shorter the distance between the pitches, the moreeffective for noise reduction).ÏInstall the noise filter on the panel which is alwaysgrounded and minimize the wiring distance between thenoise filter output side and the controller power terminals.Otherwise, the longer the distance between output sideand instrument power terminals, the less effective for REX-C100 circuit configurationnoise.ÐDo not install fuses and / or switches on the filter outputsignal since this may lessen filter effect.WIRING AND NAME OF PARTS•Wiring exampleREX-C100F GG-M*-~2N-HA OF PARTSÑSet-value increment keyC Used when the number needs to be increasedfor set-value change.ÒMeasured-value (PV) display unit [Green]C Displays measured-value (PV)C Displays a parameter symbol in the parametersetting mode.ÓSet-value (SV) display unit [Orange]C Displays set-value (SV)C Displays set-value corresponding to theparameter symbol displayed on the measured-value (PV) display unit.ÎSet (SET) keyC The set-value thus changed is enteredÔControl output (OUT) lamp [Green]C Parameters in the parameter setting mode are C Lights up when the control output is turnedON.selected in due order.C Can select PV / SV display mode, SV settingÕAuto-tuning (AT) lamp [Green]mode, and parameter setting modes.C Flashes during auto-tuning.ÏSetting digit shift keyÖFirst alarm (ALM1) lamp [Red]C Used when the cursor (brightly lit) is moved to C Lights up when the first alarm is turned ON.the digit whose number needs to be changed for C When a control loop break alarm (LBA) is set-value change.selected as the first alarm, this lamp lights up.ÐSet-value decrement key×Second alarm (ALM2) lamp [Red]C Used when the number needs to be decreased C Lights up when second alarm is turned ON.for set-value change.C When either a heater break alarm (HBA) orcontrol loop break alarm (LBA) is selected asthe second alarm, this lamp lights up.5.OPERATION•Calling-up procedure of each mode:Press the key.Input type code / input range displayThis controller, with the power turned ON, displaysautomatically the input type code on the measured-value (PV)display unit and the input range, on the set-value (SV) displayunit, respectively.Example : For a controller with the K thermocouple inputtype and input range from 0 to 1372E C.ÎDisplays the input type code.: Indicates input abbreviation.unit. ( : E F)input type code table).ÏDisplays the input range.< Input type code >Code Input Type Code Input typeRSBW5Re/W26RePLIIPt100JPt100PV / SV display modeC Displays measured-value (PV) on the measured-value(PV) display unit and set-value (SV) on the set-value (SV)display unit. Usually the control is set to this modeexcepting that the set-value (SV) and/or the parameter set-value are changed.PV / SV display modeC Pressing the key lights the least significant digit onvalue (SV).In order to register the value whose setting was changed,always press the key after the value is changed.sec. in the PV / SV display or SV setting mode, thecontroller is set to the parameter setting mode.C Parameters in the parameter setting mode changes in dueorder every time the key is pressed (See page 6).and keys are pressed.C In order to register the value whose setting was changed,press the key after change to shift to the nextsec.•When no key is operated for more than 1 minute.•Parameter typesThe following parameter symbols are displayed one by one every time the key is pressed.Current transformer input (CT)Setting is not possible.Set heater break alarm value byreferring to this value.Display input value from thecurrent transformerCTSecond alarm Set alarm set-value of second alarm.AL2Control loopbreak alarm (LBA)0.0 to 200.0 min.Set control loop break alarmset-value.Cannot be set to “0.0".8.0LbAAuto-tuning (AT)0 : Auto-tuning end or stop1 : Auto-tuning startTurns the auto-tuningON/OFF.ATUIntegral time (I)1 to 3600 sec.Eliminates offset occurringcontrol is performed. I actionturns OFF with I set to “0".240IAnti-reset windup (ARW)1 to 100% of proportional band.Prevents overshoot and/orundershoot caused by integralaction. I action turns OFFwith this action set to “0".100ArSet data lock 0100 : No set data locked (Allparameters changeable)0101 : Set data locked (All parametersnot changeable)0110 : Only the set-value (SV) ischangeable with the set data locked.Performs set data changeenable / disable.0100LCK* The second alarm (or first alarm), heater break alarm, control loop break alarm parameter symbols are not simultaneously displayed. * Heater break alarm is not available on a current output.C Parameter setting procedure Setting set-value (SV)Following is an example of setting the set-value (SV) to 200E C. (PV : 30E C)Î Set to the set modeÏ Shift of the digit brightly litÐ Set-value increase or decrease ÑSet-value entryPress the key to Press the key to shift Press the key to set “2".After finishing the setting,enter the SV setting mode.the digit which lights brightlypress thekey. All ofController returns to the PV/SV display mode.Example : When a temperature of 199E C is changed to 200E C.Set-value increase or decreasePress the key to shift the digit brightly lit to the least significant digit. Press the key to change “9" to “0", therebyobtaining 200E C. The same applies to set-value decrease.Example : For changing 200 to -100.Minus (-) value settingPress the key to shift the digit brightly lit to the hundreds digit. Press the key to decrement figures in order of÷ 0 ÷ -1.Setting parameters other than set-value In the PV/SV display modeIn the parameter setting modeKey operational cautions CFor this controller, the value whose setting was changed is not registered. It is registered for the first time it is shifted to the next parameter by pressing the key.setting mode, set data lock is activated.In this case, change the “” parameter set-value to “0100".the parameter setting mode.Press thekey by the required number of times untilkey after the setting is finished in the parameters).When no parameter setting is required, return the controller to the PV/SV display mode.¬Pay attention to the following when the parameters described below are set.Auto-tuning (AT)C Prior to starting the auto-tuning function, end all the parameter settings other than PID and control loop break alarm(LBA).Heater break alarm (HBA)C Set heater break alarm set-value to a value about 85% current transformer input value. However, when power supplyvariations are large, set the alarm to a slightly smaller value.In addition, when two or more heaters are connected in parallel, set the alarm to a slightly larger value so that it is activated even with only one heater is broken. (However, within the value of a current transformer input value).C When the heater break alarm set-value is set to “0.0" or the current transformer is not connected, the heater breakalarm is turned ON.Control loop break alarm (LBA)C Usually set the set-value of the LBA to a value twice the integral time (I).O Set data locking procedureThis controller is provided with a set data locking function which disables each set-value change by the front key and also the auto-tuning function. Use this function for malfunction prevention at the end of each setting.C Press the key by the required number of(PV) display unit.C Press the , and keys to set the•Display at error occurrence< Heater break alarm >Display CauseMeasure(Lights)C Controlled object trouble (No power supply,incorrect wiring, etc).C Sensor trouble (Sensor disconnected, shorted, etc).C Actuator trouble (Weld relay contact, incorrectwiring, relay contact not closed, etc).C Output circuit trouble (Weld internal relay contact,relay contact not opened or closed, etc).C Input circuit trouble (The measured-value does notchange even if input changes, etc).Control system check(Error cause cannot bespecified)Check whether there is no effectby disturbances (Other heatsource, etc).LBA set time check< Overscale, Underscale >Input type Input display rangeTCK-30 to +1372E C -30 to +2502E F J-30 to +1200E C -30 to +2192E F R, S-30 to +1769E C -30 to +3216E F B-30 to +1820E C -30 to +3308E F E-30 to +1000E C -30 to +1832E F T-199.9 to +400.0E C -199.9 to +752.0E F N-30 to +1300E C -30 to +2372E F PLII-30 to +1390E C -30 to +2534E F L-30 to +800E C -30 to +1600E F U-199.9 to +600.0E C -199.9 to +999.9E F W5Re/W26Re-30 to +2320E C -30 to +4000E FRTDPt100JPT100-199.9 to +649.0E C Pt100-199.9 to +999.9E F。

Olympus 1X71 用户手册说明书

UCL Institute of Child HealthUser guide Olympus 1X71Dr Bertrand VernayLight Microscopy Facility ManagerWellcome building, Office W2.09Tel Office: 42224TelMobile************Email:***************.ukRevised December 2014Table of contentspage 3 ......... O wnershippage 3 ........ Access Rulespage 3 ......... O lympus Customer Support Contactpage 4 ........ General SpecificationsMicroscopy Techniques AvailableObjectivesFilter CubesCameraFluorescence IlluminationPixels to Microns CalibrationConsumables Listpage 5 ......... Quick User GuidesTransmitted LightEpifluorescenceImage Capturepage 6 ......... Halogen Lamp Operationpage 7 .... Kohler Illuminationpage 8 ........ Adjusting the Objective Correction Collar page 9 ........ Prior Lumen200 Metal Halide Lamp Operation page 10 .. Image Capture with HClmagepage 11 ... Selecting the Right Fluorochrome/Filter Setpage 11 DAPIpage 12 Endow GFP/EGFP Bandpasspage 13 DsRed(TRITC/Cy3)page 14 Cy5page 15 Cy7page 16 ....Prior Lumen200 Spectral Outputpage 17 ... Hamamatsu ORCA-R2 Spectral ResponseOwnershipProf. Jane Sowden, Developmental Biology Unit (Purchased in 2011)Access Rules∙No access without prior training by the Light Microscopy Facility Staff ∙Free of hourly charge for Sowden and Ferretti groups, £1 hourly charge for all other users towards the cost of the consumables is expected ∙Prof. Sowden team has priority over other users.∙Users must always record their activity in the Log book∙Problem(s) with the microscope should be reported as soon as they are noticedOlympus customer support service: /microscopy The system is not covered by a maintenance contractOlympus requires a PO number before sending an engineerGeneral specificationsMicroscopy techniques available∙Brightfield∙Phase contrast∙EpitluorescenceObjectives∙O ly mpu s UP l an FL N 10x Ph1 NA0.3 WD10.0 mm∙Olympus LUCPlanFLN 20x Ph1 NA 0.45 WD 6.6-7.8 with correction collar ∙Olympus LUCPlanFLN 40x Ph2 NA 0.6 WD 3.0-4.2 with correction collar ∙Ze is s o bj ec t ive s c an al s o be use dCamera (see p16)Hamamatsu ORCA R2 CCD Camera with HClmage Capture SoftwareFluorescence illumination (see p16)Prior Lumen 200 Metal Halide Light Source (2000 hours/bulb)Pixels to Microns calibration5x objective binning 1x1 1 pixel = 1.88 um10x objective binning 1x1 1 pixel = 1.03 um20x objective binning 1x1 1 pixel = 0.514 um40x objective binning 1x1 1 pixel = 0.256 umCalibration with a micrometer under transmitted white ligh tConsumables listPrice correct as of November 2013∙Prior Lumen 200 bulb LM375 (£550, Prior Scientific Instruments Ltd)∙Prior Lumen 200 light guide LM587 (£400, Prior Scientific Instruments Ltd)∙Halogen bulb 12V/100W (£1.8, Technical Lamp Supplies UK)Quick user guidesUsers must always record their activity in the Log bookTransmitted light1.Halogen Lamp Power Supply Unit TH4 "ON"2.Light Path selector on "Ocular"3.Kohler illumination adjusted4.Correct phase ring in position (10x & 20x Ph1, 40x Ph2)5.Filter cube on po sition #6EpifluorescenceWarnings:Do not shut the unit down within 30 minutes of powering up the unit.∙After shutting down the unit allow 30 minutes before re-powering up ∙After shutting down the unit allow 30 minutes before changing the bulb. Failure to do so is likely to result in damage to the bulb.1.Prior Lumen 200 module on2.Prior Lumen 200 intensity knob >0%3.Light Path selector lever on "Ocular"4.Correct filter cube in position5.Fluorescence shutter openImage Capture1.Start Camera controller (press until LED turns green)puter on (Login: Jane/ Password: Ja*e)3.HClmage software open4.Light Path selector lever on Camera5.Correct transmitted light/epifluorescence set-up6."L i v e"mo de7.Adjust exposure time accordingly. Make use of the Histogram and the Saturatio noptions8."A b o r t"9."C a p t u r e l"10.S a v e a s in M y D o cu me n ts>U s e r N ame_U n i t>Fi le N am e.t i f11.Shut-down: exit HClmage, log out windows session, camera on stand-by (pressuntil LED turns orange)Halogen lamp operation:Turning on the lamp1.Make sure the light intensity control knob (5) is in the MIN (minimum intensity)position on the microscope frame.2.Make sure the light intensity control knob (1) is in the MIN (minimum intensity)position on the TH4 module.3.Set the main switch (2) to "I" (ON) on the TH4 module.4.On the microscope front, press the transmitted light ON-OFF button (6) so thatthe button is illuminated.5.Adjust the brightness with the light intensity control knob (5).6.To turn OFF, set the transmitted light ON-OFF button (6) to OFFHalogen lamp operation:T urning off the lamp1.Set the light intensity control knob (5) to the MIN (minimum intensity) position onthe microscope frame.2.Set the light intensity control knob (1) to the MIN (minimum intensity) position onthe TH4 module.3.Set the main switch (2) to "0" (OFF) on the TH4 module.Kohler illumination:1.Rotate the turret (1) to the "BF" position. (Any of positions 3,4 or 5, position 1=Ph1, 2 = Ph2)2.Slide the aperture iris diaphragm lever (2) to fully open the diaphragm.3.Slide the field iris diaphragm lever (3) to the fully open position.4.Engage the 10x objective and bring the specimen into focu s.ing the field iris diaphragm lever (3), completly close the field iris diaphragm.6.Rotate the condensor height adjustment knob (4) to bring the field iris diaphragmimage into focus.7.Center the field iris diaphragm (3) using the condenser centering kno bs (5).8.Open the field iris diaphragm (3) until its image reach the limits of the field of view,adjust the centering if necessary.9.Open the field iris diaphragm (3) until not visible.Step 6 Step 7 Step 8 Step 9Adjusting the objective correction collarCorrection is possible according to the vessel bottom thickness.1.When the thickness of the vessel bottom is known, match the scale reading of thecorrection collar to the thickness of the vessel in use.or2.If the thickness of the vessel is unknown or diverge from the manufacturerspecifications, the optimum position for the correction collar can be obtained by judging the image resolution and contrast. When a satisfactory image is not obtain after focusing:1. Rotate the correction collar to the left and right, refocus each time andcompare the images.2 Then rotate the collar in the direction yielding a better image, rotate thecorrection collar to the left and right, refocus each time and compare theimages.3 Repeat this cycle until the position with the optimum image is found.20x Correction Collar 40x Correction CollarCorrection Collar Scale0 mm0.17 mm (glass coverslip #1.5)0.5 mm1 mm (most tissue culture plates)1.5 mm2 mmPrior Lumen200 Metal Halide Lamp Operation:Starting Up the Lumen1.Switch the Lumen power switch on.2.Make sure the ventilation vent on the left hand side is unobstructed or the lampwill overheat resulting in automatic shutdown and damage to the module.3.Allow 1-5 minutes for light to reach 70% of output.4.Allow 30 minutes for the Lumen to reach operational temperature.5.Warning: Do not power down the unit within 30 mins of power up. This may re-duce the effective lifetime of the bulb.Shutting down the LumenThe following warnings apply as damage to the bulb may result if instructions not followed:1.Warning: Do not shut the unit down within 30 minutes of powering up the unit.2.Warning: After shutting down the unit allow 30 minutes before re-powering up orchanging the bulb. Failure to do so is likely to result in damage to the bulb.Warning: the airoutlet for heatventilation mustnot but obstructed[Mono: 1 Channel ⏹ Mono: 1 Channel v•[C10600-100 (O R CA-R 2) S IN: 011316 ⏹C10600-106 (CIRCA-R2) SP!: 011316--- — X CaptureXBinning and SubArray Advanced Camera PropertiesBinning and SubArray Advanced Camera PropertiesusL IP r o c e s s i n gIF! 0uL P r oc es s in gD e p t h16 b itBinning and SubArray Binning [1 Sub-Array ResetPreset Sizes[1344 x 1024 ⏹X 0 0 L i e d a g .:Width 1344 Image Capture with HClmage1. Click the Capture pane.2. Click Live for a live image from the camera3. Camera binning or image sub-array can be set in the Binning SubArray panel.4. In the Camera Control panel, adjust exposure/gain manually or automatically by clicking on Auto Expose; view the intensity distribution in the histogram.5. Check Sat. (saturation) in the histogram of the Image Display to guard against image saturation. Saturated pixel are indicated in Red. Yellow indicates pixels ap -proaching saturation.6. Adjust camera exposure and gain settings as necessary7. Click Abort.8. Click Capture1 to acquire an image.9.Click the Save icon to save the image in My Documents>UserName_Unit>file name.tifC a p t u r eMEMCapturelAbort1Capture1iY 2/ C a m e r a C o n t r o l1 Li n 1,1.A.M.Pi n M.,11Auto ExposeAu to Expos eT e m p e r a t u r e [C ] Current100 Camera ControlTemperature [C]OffsetB4UDefault ⏹DefaultGain Exposure 00.10000(OffsetG a i n E x pos u re 0 ! ;0. 10400C 1Ilkstogursr ;401Lopg:• ItE•4 • a-YO 0Height 1024I lb O..^ • la Coorto0wpo•d • ItI P f o r H O V I. M o o n.. t l e f r a89Selecting the right fluorochrome/filter setPosition #149000 - ET - DAPIExciter 350/50xbeamsplitter 400113Emitter ET460/50m550Wavelength (nm)Position #241017 EndowGFP/EGFP Bandpass Emitter ET470/40xBeamsplitter 495LPEmitter ET 525/50mPosition #349005 - ET - DSRed (TRITC/Cy3) Exciter ET545/30xBeamsplitter T570LPXREmitter ET620/60m100Position #4 49006 - ET - Cy5 emitter ET620/60xBeamsplitter T660LPXR Emitter ET700/75n,Position #549007 - ET - Cy7Exciter ET710/75xBeamsplitter T760LPXREmitter ET810/90m700 750 800 850Wavelength (nm)T7601pxrHClmage Live。

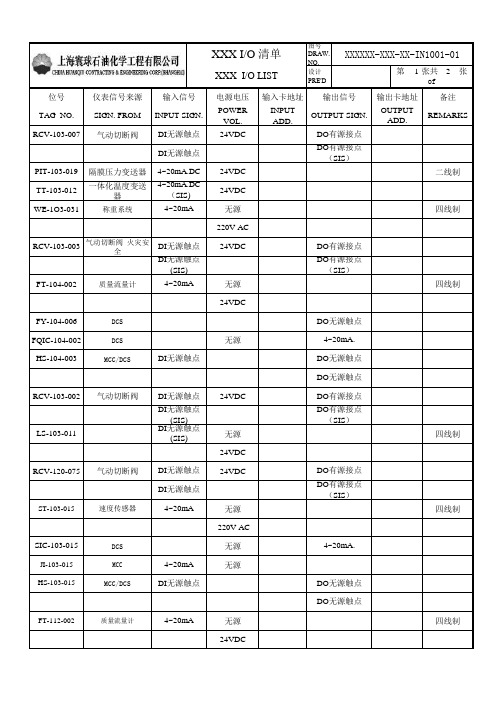

XXXXXX-XXX-XX-IN1001-01 简化版

24VDC

无源 24VDC 24VDC

无源

4~20mA. DO无源触点 DO无源触点 DO有源接点 DO有源接点

(SIS)

DO有源接点制

220V AC

SIC-103-015

DCS

无源

4~20mA.

JI-103-015 HS-103-015

MCC MCC/DCS

4~20mA DI无源触点

称重系统

4~20mA

无源

四线制

HS-121-001 SOLENOID VAVLE

220V AC 24VDC

DO有源接点

TT-120-011 一体化温度变送器

RCV-120-009

气动切断阀 火灾 安全

RCV-120-010 气动三通切断阀

4~20mA.DC

DI无源触点 DI无源触点

(SIS) DI无源触点

第 2 张共 2 张 of

输入信号

电源电压 输入卡地址 输出信号

输出卡地址

备注

INPUT SIGN.

POWER VOL. 无源

INPUT ADD.

OUTPUT SIGN. 4~20mA.

OUTPUT ADD.

REMARKS

MCC/DCS

DI无源触点

DO无源触点

DO无源触点

WE-111-008

称重系统

(SIS)

OUTPUT ADD.

REMARKS 二线制

四线制

RCV-103-003

气动切断阀 全

火灾安

FT-104-002

质量流量计

DI无源触点 DI无源触点

(SIS)

4~20mA

220V AC 24VDC

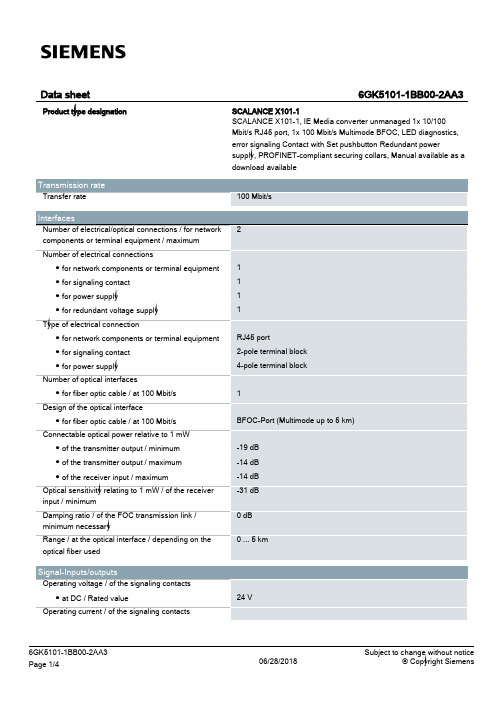

SCALANCE X101-1 商品说明书

24 V

6GK5101-1BB00-2AA3 Page 1/4

06/28/2018

Subject to change without notice © Copyright Siemens

● at DC / maximum

Supply voltage, current consumption, power loss Supply voltage ● external ● external Type of voltage / of the supply voltage Product component / fusing at power supply input Fuse protection type / at input for supply voltage Consumed current ● maximum Power loss [W] ● at DC / at 24 V

Compact 40 mm 125 mm 124 mm 0.55 kg

Yes Yes Yes

No No

FM3611: Class 1, Divison 2, Group A, B, C, D / T.., Class 1, Zone 2, Group IIC, T.. EN 600079-15 II 3 G EEx nA II T.. KEMA 06 ATEX 0021 X

Yes

Yes Yes Yes Yes Yes No 134 y

/snst

/simatic-net https:// /industry/infocenter /bilddb /cax https://

Security information

UL 60950-1, CSA C22.2 No. 60950-1 UL 1604 and UL 2279-15 (Hazardous Location), Class 1 / Division 2 / Group A, B, C, D / T.., Class 1 / Zone 2 / Group IIC / T.. EN 61000-6-3 EN 61000-6-4:2001 EN 61000-6-2:2001, EN 61000-6-4:2001 Yes Yes Yes

ADC1001CCJ-1中文资料

ADC100110-Bit µP Compatible A/D ConverterGeneral DescriptionThe ADC1001is a CMOS,10-bit successive approximation A/D converter.The 20-pin ADC1001is pin compatible with the ADC08018-bit A/D family.The 10-bit data word is read in two 8-bit bytes,formatted left justified and high byte first.The six least significant bits of the second byte are set to zero,as is proper for a 16-bit word.Differential inputs provide low frequency input common mode rejection and allow offsetting the analog range of the converter.In addition,the reference input can be adjusted enabling the conversion of reduced analog ranges with 10-bit resolution.Key Specificationsn Resolution 10bitsn Linearity error ±1LSBn Conversion time200µSFeaturesn ADC1001is pin compatible with ADC0801series 8-bit A/D convertersn Compatible with NSC800and 8080µP derivatives —no interfacing logic neededn Easily interfaced to 6800µP derivatives n Differential analog voltage inputsn Logic inputs and outputs meet both MOS and TTL voltage level specificationsn Works with 2.5V (LM336)voltage reference n On-chip clock generatorn 0V to 5V analog input voltage range with single 5V supplyn Operates ratiometrically or with 5V DC ,2.5V DC ,or analog span adjusted voltage reference n 0.3"standard width 20-pin DIP packageConnection DiagramOrdering InformationTemperature Range 0˚C to +70˚C −40˚C to +85˚C Order Number ADC1001CCJ-1ADC1001CCJPackage OutlineJ20AJ20ATRI-STATE ®is a registered trademark of National Semiconductor Corp.ADC1001Dual-In-Line PackageDS005675-11Top ViewJune 1999ADC100110-Bit µP Compatible A/D Converter©1999National Semiconductor Corporation Absolute Maximum Ratings(Notes1,2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage(V CC)(Note3) 6.5V Logic Control Inputs−0.3V to+18V Voltage at Other Inputs and Outputs−0.3V to(V CC+0.3V) Storage Temperature Range−65˚C to+150˚C Package Dissipation at T A=25˚C875mW Lead Temp.(Soldering,10seconds)300˚C ESD Susceptibility(Note10)800VOperating Conditions(Notes1,2) Temperature Range T MIN≤T A≤T MAX ADC1001CCJ−40˚C≤T A≤+85˚C ADC1001CCJ-10˚C≤T A≤+70˚C Range of V CC 4.5V DC to6.3V DCConverter CharacteristicsConverter Specifications:V CC=5V DC,V REF/2=2.500V DC,T MIN≤T A≤T MAX and f CLK=410kHz unless otherwise specified.Parameter Conditions MIn Typ Max Units Linearity Error±1LSB Zero Error±2LSB Full-Scale Error±2LSB Total Ladder Resistance(Note9)Input Resistance at Pin9 2.2 4.8KΩAnalog Input Voltage Range(Note4)V(+)or V(−)GND−0.05V CC+0.05V DC DC Common-Mode Error Over Analog Input Voltage Range±1⁄8LSB Power Supply Sensitivity V CC=5V DC±5%Over±1⁄8LSBAllowed V IN(+)and V IN(−)Voltage Range(Note4)AC Electrical CharacteristicsTiming Specifications:V CC=5V DC and T A=25˚C unless otherwise specified.Symbol Parameter Conditions MIn Typ Max Units T c Conversion Time(Note5)80901/f CLKf CLK=410kHz195220µsf CLK Clock Frequency(Note8)1001260kHzClock Duty Cycle4060% CR Conversion Rate In Free-Running INTR tied to WR with4600conv/s Mode CS=0V DC,f CLK=410kHzt W(WR)L Width of WR Input(Start Pulse CS=0V DC(Note6)150ns Width)t ACC Access Time(Delay from C L=100pF170300ns Falling Edge of RD to OutputData Valid)t1H,t0H TRI-STATE®Control(Delay C L=10pF,R L=10k125200ns from Rising Edge of RD to(See TRI-STATE TestHi-Z State)Circuits)t WI,t RI Delay from Falling Edge300450ns of WR or RD to Reset of INTRt1rs INTR to1st Read Set-Up Time550400nsC IN Input Capacitance of Logic57.5pFControl InputsC OUT TRI-STATE Output57.5pFCapacitance(Data Buffers)2DC Electrical CharacteristicsThe following specifications apply for V CC=5V DC and T MIN≤T A≤T MAX,unless otherwise specified.Symbol Parameter Conditions MIn Typ Max Units CONTROL INPUTS[Note:CLK IN is the input of a Schmitt trigger circuit and is therefore specified separately]V IN(1)Logical“1”Input Voltage V CC=5.25V DC 2.015V DC (Except CLK IN)V IN(0)Logical“0”Input Voltage V CC=4.75V DC0.8V DC (Except CLK IN)I IN(1)Logical“1”Input Current V IN=5V DC0.0051µA DC(All Inputs)I IN(0)Logical“0”input Current V IN=0V DC−1−0.005µA DC(All Inputs)CLOCK INV T+CLK IN Positive Going 2.7 3.1 3.5V DC Threshold VoltageV T−CLK IN Negative Going 1.5 1.8 2.1V DC Threshold VoltageV H CLK IN Hysteresis0.6 1.3 2.0V DC (V T+)−(V T−)OUTPUTS AND INTRV OUT(0)Logical“0”Output Voltage I OUT=1.6mA,V CC=4.75V DC0.4V DCV OUT(1)Logical“1”Output Voltage I O=−360µA,V CC=4.75V DC 2.4V DCI O=−10µA,V CC=4.75V DC 4.5V DCI OUT TRI-STATE Disabled Output V OUT=0.4V DC0.1−100µA DCLeakage(All Data Buffers)V OUT=5V DC0.13µA DCI SOURCE V OUT Short to GND,T A=25˚C 4.56mA DCI SINK V OUT Short to V CC,T A=25˚C9.016mA DC POWER SUPPLYI CC Supply Current(Includes f CLK=410kHz,Ladder Current)V REF/2=NC,T A=25˚Cand CS=1 2.5 5.0mANote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do not apply when operatingthe device beyond its specified operating conditions.Note2:All voltages are measured with respect to GND,unless otherwise specified.The separate A GND point should always be wired to the D GND.Note3:A zener diode exists,internally,from V CC to GND and has a typical breakdown voltage of7V DC.Note4:For V IN(−)≥V IN(+)the digital output code will be all zeros.Two on-chip diodes are tied to each analog input(see Block Diagram)which will forward conductfor analog input voltages one diode drop below ground or one diode drop greater than the V CC supply.Be careful,during testing at low V CC levels(4.5V),as high level analog inputs(5V)can cause this input diode to conduct—especially at elevated temperatures,and cause errors for analog inputs near fullscale.The spec al-lows50mV forward bias of either diode.This means that as long as the analog V IN does not exceed the supply voltage by more than50mV,the output code willbe correct.To achieve an absolute0V DC to5V DC input voltage range will therefore require a minimum supply voltage of4.950V DC over temperature variations,initial tolerance and loading.Note5:With an asynchronous start pulse,up to8clock periods may be required before the internal clock phases are proper to start the conversion process.The start request is internally latched,see Figure3.Note6:The CS input is assumed to bracket the WR strobe input and therefore timing is dependent on the WR pulse width.An arbitrarily wide pulse width will holdthe converter in a reset mode and the start of conversion is initiated by the low to high transition of the WR pulse(see Timing Diagrams).Note7:All typical values are for T A=25˚C.Note8:Accuracy is guaranteed at f CLK=410kHz.At higher clock frequencies accuracy can degrade.Note9:The V REF/2pin is the center point of a two resistor divider(each resistor is2.4kΩ)connected from V CC to ground.Total ladder input resistance is the sumof these two equal resistors.Note10:Human body model,100pF discharged through a1.5kΩresistor.3Typical Performance CharacteristicsTRI-STATE Test Circuits and WaveformsLogic Input Threshold Voltage vs Supply VoltageDS005675-14Delay From Falling Edge of RD to Output Data Valid vs Load CapacitanceDS005675-15CLK IN Schmitt Trip Levels vs Supply VoltageDS005675-16Output Current vs TemperatureDS005675-17DS005675-3t 1H ,C L =10pFDS005675-4t r =20nsDS005675-5t 0H ,C L =10pFDS005675-6t r =20ns 4TRI-STATE Test Circuits and Waveforms(Continued)Timing DiagramsDS005675-7Output Enable and Reset INTRDS005675-8*All timing is measured from the50%voltage points.5Timing Diagrams(Continued)Byte Sequencing For The20-Pin ADC1001Byte8-Bit Data Bus ConnectionOrder DB7DB6DB5DB4DB3DB2DB1DB0 MSB1st Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2LSB2nd Bit1Bit0000000 Functional DescriptionThe ADC1001uses an advanced potentiometric resistive ladder network.The analog inputs,as well as the taps of this ladder network,are switched into a weighted capacitor array. The output of this capacitor array is the input to a sampled data comparator.This comparator allows the successive ap-proximation logic to match the analog difference input volt-age[V IN(+)−V IN(−)]to taps on the R network.The most sig-nificant bit is tested first and after10comparisons(80clock cycles)a digital10-bit binary code(all“1”s=full-scale)is transferred to an output latch and then an interrupt is as-serted(INTR makes a high-to-low transition).The device may be operated in the free-running mode by connecting INTR to the WR input with CS=0.To ensure start-up under all possible conditions,an external WR pulse is required dur-ing the first power-up cycle.A conversion in process can be interrupted by issuing a second start command.On the high-to-low transition of the WR input the internal SAR latches and the shift register stages are reset.As long as the CS input and WR input remain low,the A/D will remain in a reset state.Conversion will start from1to8clock peri-ods after at least one of these inputs makes a low-to-high transition.A functional diagram of the A/D converter is shown in Figure3.All of the inputs and outputs are shown and the major logic control paths are drawn in heavier weight lines.The conversion is initialized by taking CS and WR simulta-neously low.This sets the start flip-flop(F/F)and the result-ing“1”level resets the8-bit shift register,resets the Interrupt (INTR)F/F and inputs a“1”to the D flop,F/F1,which is at the input end of the10-bit shift register.Internal clock signals then transfer this“1”to the Q output of F/F1.The AND gate, G1,combines this“1”output with a clock signal to provide a reset signal to the start F/F.If the set signal is no longer present(either WR or CS is a“1”)the start F/F is reset and the10-bit shift register then can have the“1”clocked in, which allows the conversion process to continue.If the set signal were to still be present,this reset pulse would have no effect and the10-bit shift register would continue to be held in the reset mode.This logic therefore allows for wide CS and WR signals and the converter will start after at least one of these signals returns high and the internal clocks again provide a reset signal for the start F/F.After the“1”is clocked through the10-bit shift register(which completes the SAR search)it causes the new digital word to transfer to the TRI-STATE output latches.When this XFER signal makes a high-to-low transition the one shot fires,set-ting the INTR F/F.An inverting buffer then supplies the INTR output signal.Note that this SET control of the INTR F/F remains low for aproximately400ns.If the data output is continuously en-abled(CS and RD both held low),the INTR output will still signal the end of the conversion(by a high-to-low transition),because the SET input can control the Q output of the INTR F/F even though the RESET input is constantly at a“1”level. This INTR output will therefore stay low for the duration of the SET signal.When data is to be read,the combination of both CS and RD being low will cause the INTR F/F to be reset and the TRI-STATE output latches will be enabled.Zero and Full-Scale AdjustmentZero error can be adjusted as shown in Figure1.V IN(+)is forced to+2.5mV(+1⁄2LSB)and the potentiometer is ad-justed until the digital output code changes from000000 0000to0000000001.Full-scale is adjusted as shown in Figure2,with the V REF/2 input.With V IN(+)forced to the desired full-scale voltage less11⁄2LSBs(V FS−11⁄2LSBs),V REF/2is adjusted until the digital output code changes from1111111110to111111 1111.6Functional Description(Continued)Typical Application DS005675-9Note11:V IN(−)should be biased so that V IN(−)≥−0.05V when potentiom-eter wiper is set at most negative voltage position.FIGURE1.Zero Adjust CircuitDS005675-10FIGURE2.Full-Scale AdjustDS005675-1 7Block DiagramDS005675-13 Note12:CS shown twice for clarity.Note13:SAR=Successive Approximation Register.FIGURE3.8Physical Dimensions inches(millimeters)unless otherwise notedLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implantinto the body,or(b)support or sustain life,andwhose failure to perform when properly used inaccordance with instructions for use provided in thelabeling,can be reasonably expected to result in asignificant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to performcan be reasonably expected to cause the failure ofthe life support device or system,or to affect itssafety or effectiveness.National SemiconductorCorporationAmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National SemiconductorEuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National SemiconductorAsia Pacific CustomerResponse GroupTel:65-2544466Fax:65-2504466Email:sea.support@National SemiconductorJapan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507 Cavity Dual-In-Line Package(J)(Side Brazed)Order Number ADC1001CCJ or ADC1001CCJ-1NS Package Number J20AADC100110-BitµPCompatibleA/DConverter National does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

Celmi s.r.l. S1D模型分析力量传输器商业说明书

ANALOG WEIGHT TRANSMITTER MODEL S1DCELMI s.r.l. Tel: +39 024******* Largo Brugnatelli 13/16 Page 1 of 3 Fax: +39 024******* 20090 Buccinasco (MI) ************** Italy Applications:The analog weight transmitter model S1D has been designed for electronic weighing systems with strain-gages load cells and is suitable for installation in any industrial or residential plant.Typical applications are:- Overload control for cranes - Silo level measurement - PLC weight inputMain features:- Suitable for max 4 strain-gage load cells - Load cell supply short circuit protection - Standard analog signal output- Zero and span adjustment by step switches + 20 turn pot.- Wiring and load cell failure control - DIN bracket mounting- 24 V a.c. supply or 24 V d.c. - Optional isolated analog outputSpecification:Power supply: 24 V a.c., ±10%, 50/60 Hz, 4 VA Option : 24 V d.c.Load cell supply : 10 V cc, max 120 mA Load cell number : max 4 - 350 ohm load cells Measuring range : From 0,25 to 3 mV/V Tare compensation : ± 80% of measuring range Analog output : Standard 4-20 mA, 400 ohm max Combined error : 0,1 % o of measuring range Zero / span thermal drift : 2,0 µV/°C max / 0,01 % reading/°C Operating/stocking temp. : -20 + 50 °C / -40 + 80 °C Wiring : Terminal board for 2,5 mm 2 wire max Protection : IP00 Weight / packing volume : 0,3 kg / 0,9 dm 3ANALOG WEIGHT TRANSMITTER MODEL S1DCELMI s.r.l. Tel: +39 024******* Largo Brugnatelli 13/16 Page 2 of 3 Fax: +39 024******* 20090 Buccinasco (MI) ************** Italy Description:Model S1D weight transmitter is an analog instrument specifically designed for industrial electronic weighing.The instrument generates the load cell stabilized voltage supply and converts the low voltage signal delivered by the load cells, into a standard 4-20 mA analog signal usable by any normal control and supervisor equipment (display, PLC, PC, ecc.).The load cell supply is short circuit protected with autoreset by power supply on/off switching.Analog output is a standard 4-20 mA non isolated suitable for connection to any conventional equipment. The circuit includes the control of any failure (open or short circuit) inside the load cell or relevant wiring and alarms the failure condition by driving the output signal over 20,8 mA or below 3,2 mA.Zero and span adjustments are performed trough 20 turn potentiometers plus coarse dip-switch adjustment.Options:Output signal: Standard availabilty is 4-20 mA.Analog output optoisolation: The mA analog output does not normally requires to be isolated; however, some specific applications (such as interconnection with motor drive controls) may require the use of this option.Model options:Specify the complete model number, together with the required functions; to allow correction of misunderstanding or writing errors.Base model S1D- X X X Output signal 4 - 20 mA 0 Analog output optoisolation NO 0 YES 1 Supply 24 V a.c. 0 24 V d.c. 1 110 V a.c. 2InstallationThe unit have to be installed on DIN bracket (EN50022) at an height suitable for easy operation in environments with temperature within spec. limits and without humidity condensation, aggressive or explosive vapours.The supporting structure must not have high vibrations; eventually vibration smoothers should be provided. Distance between load cells and the instrument should be kept to the minimum; possibly connect the load cell cable directly to the instrument; long distance connections may be carefully checked against required accuracy and installation conditions.ANALOG WEIGHT TRANSMITTER MODEL S1DCELMI s.r.l. Tel: +39 024******* Largo Brugnatelli 13/16 Page 3 of 3 Fax: +39 024******* 20090 Buccinasco (MI) ************** Italy WiringWiring have to be done on the basis of terminal board connection diagram and according to local standard and regulations.Always use needle type wire terminator and install an external switch with fuse on power supply connection (eventually common to other instruments).WARNING:Load cell, analog output and serial signal cables must run separate from power cables.。

自由系列NEMA接触器——产品概述说明书

Freedom Series NEMA Contactors – Overview• Market leader in NEMA power control • Most complete line in the industry• Ideal for project construction, HVAC, pump and industrial applications • Open and enclosed versionsType CN15/CN55 NEMA Contactors – Model SelectionNEMA Size Continuous Ampere Rating Maximum UL Horsepower 3-Pole Non-Reversing 3-Pole Reversing 1-Phase 3-Phase 115V 230V 208V 240V 480V 600V Catalog Number 1Catalog Number 10091/311-1/21-1/222CN15AN3_B CN55AN3_B 018123355CN15BN3_B CN55BN3_B 127237-1/27-1/21010CN15DN3_B CN55DN3_B 24537-1/210152525CN15GN3_B CN55GN3_B 390––25305050CN15KN3_CN55KN3_4135––4050100100CN15NN3_CN55NN3_5270––75100200200CN15SN3_CN55SN3_6540––150200400400CN15TN3_B CN55TN3_B 7810––200300600600CN15UN3_CN55UN3_821215––400450900900CN15VN3_CN55VN3_1 When ordering, replace magnet coil alpha designation in catalog number (_) with proper code suffi x from table below.2Common control. For separate 120V control, insert letter D in seventh position of listed catalog number (ex. CN15VND3C).Magnet Coils (AC and DC) – Model SelectionCoil Volts and Hertz Code Suffi x Coil Volts and Hertz Code Suffi x 120/60, 110/50240/60, 220/50480/60, 440/50600/60, 550/50A B C D 380-415/50550/5024/60, 24/50 424/50L N T U 208/60277/60208-240/60 3240/50E H J K32/5048/6048/50V W Y3 NEMA Sizes 00 and 0 only.4NEMA Sizes 00 and 0 only. Sizes 1 through 8 are 24/60 only.NEMA Contactors forthe Construction MarketNEMA Size 1 ContactorAuxiliary Contacts – Model SelectionSide-Mounted, NEMA Sizes 00 to 2, IEC Sizes A to K Description Contact Confi guration Code 5Catalog Number 1NO 1NC1001C320KGS1C320KGS21NO-1NC 2NO 2NC1NO-1NCI1NO (EC) - 1NC (LO)1NCI112002N/A N/A N/AC320KGS3C320KGS4C320KGS5C320KGS6C320KGS7C320KGS85This two-digit code is found on the auxiliary contact to assist in identifying the specifi c contact confi guration. The fi rst digit indicates the quantity of NO contacts and the second indicates the quantity of NC contacts.Additional Freedom Series auxiliary contacts are available. For a complete listing of theseaccessories, see the Control Products & Services Catalog (CA08102001E), Tab 33.Eaton Corporation Electrical Group1000 Cherrington Parkway Moon Township, PA 15108United States877-ETN-CARE (877-386-2273)© 2009 Eaton Corporation All Rights ReservedPublication No. TD03301007EApril 2009PowerChain Management is a registered trademark of Eaton Corporation. All other trademarks are property of their respective owners.Quick Selector TD03301007EApril 2009NEMA Contactors for the Construction MarketFreedom Series NEMA Starters – Overview• Three-phase, full voltage magnetic starters most commonly used to switch ACmotor loads • Bimetallic ambient compensated overload relays • These overload relays feature:• Interchangeable heater packs adjustable ±24% to match motor FLA • Selectable manual or automatic reset operation• Single-phase protection, Class 20 or Class 10 trip time • Overload trip indication•Electrically isolated NO-NC contacts (pull RESET button to test)• Also available with solid-state overload relays (see T ab 33 of the Control Products & Services Catalog, CA08102001E)Type AN16/An56 NEMA Starters – Model SelectionNEMA Size Continuous Ampere Rating Service-Limit Current Ratings 2Maximum UL Horsepower3-Pole Non-Reversing 3-Pole Reversing Vertical Reversing 1-Phase 3-Phase 115V 230V 208V 240V 480V 600V Catalog Number 1Catalog Number 1Catalog Number 1009111/311-1/21-1/222AN16AN0_C AN56AN0_C –01821123355AN16BN0_C An56BN0_C AN56BNV0_12732237-1/27-1/21010AN16DN0_B AN56DN0_B AN56DNV0_2455237-1/210152525AN16GN0_B AN56GN0_B AN56GNV0_390104––25305050AN16KN0_AN56KN0_AN56KNV0_4135156––4050100100AN16NN0_AN56NN0_AN56NNV0_5270311––75100200200AN16SN0_B AN56SN0_B –6540621––150200400400AN16TN0_C AN56TN0_B –7810932––200300600600AN16UN0_B AN56UN0_B –8312151400––400450900900AN16VN0_BAN56VN0_B–1 When ordering, replace magnet coil alpha designation in catalog number (_) with proper code suffi x from table below.2The service-limit current ratings represent the maximum RMS current, in amperes, which the controller shall be permitted to carry for protracted periods in normal service. At service-limit current ratings, termperature rises shall be permitted to exceed those obtained by testing the controller at its continuous current rating. The current rating of overload relays or trip current of other motor protective devices used shall not exceed the service-limit current rating of the controller.3Common control. For separate 120V control, insert letter D in seventh position of listed catalog number (ex. CN15VND3C).Magnet Coils (AC and DC) – Model SelectionCoil Volts and Hertz Code Suffi x Coil Volts and Hertz Code Suffi x 120/60, 110/50240/60, 220/50480/60, 440/50600/60, 550/50A B C D 380-415/50550/5024/60, 24/50 524/50L N T U 208/60277/60208-240/60 4240/50E H J K32/5048/6048/50V W Y4 NEMA Sizes 00 and 0 only.5NEMA Sizes 00 and 0 only. Sizes 1 through 8 are 24/60 only.Freedom Series Non-Reversing StarterNEMA Size 1Freedom Series Reversing StarterNEMA Size 1Freedom Series Auxiliary ContactsAuxiliary Contacts – Model SelectionSide-Mounted, NEMA Sizes 00 to 2, IEC Sizes A to K Description Contact Confi guration Code 6Catalog Number 1NO 1NC1001C320KGS1C320KGS21NO-1NC 2NO 2NC1NO-1NCI1NO (EC) - 1NC (LO)1NCI112002N/A N/A N/AC320KGS3C320KGS4C320KGS5C320KGS6C320KGS7C320KGS86This two-digit code is found on the auxiliary contact to assist in identifying the specifi c contact confi guration. The fi rst digit indicates the quantity of NO contacts and the second indicates the quantity of NC contacts.Additional Freedom Series auxiliary contacts are available inNEMA sizes 3 to 8 and IEC sizes L to Z. For a complete listing of these accessories, see the Control Products & Services Catalog (CA08102001E), Tab 33.。

GBS-92120F-CXX0G资料

Optoway GBS-92120F-CXX0G********************************************************************************************************************************************************************************************************************************************************************************************************************************************OPTOWAY TECHNOLOGY INC. No .38, Kuang Fu S. Road, Hu Kou, Hsin Chu Industrial Park, Hsin Chu, Taiwan 3031GBS-92120F-CXX0G (RoHS Compliant)5V / CWDM / 2.125 Gb/s Single-Mode Gigabit Interface Converter (GBIC)**********************************************************************************************************************************************************************FEATURESl 18-Wavelength CWDM GBIC Transceivers l Up to 2. 5 Gbps Bi-directional Data Linksl Compliant with 1X / 2X Fibre Channel FC-PI 13.0 l Compliant with Gigabit Interface Converter (GBIC) Specification Rev. 5.5l CWDM DFB Laser Transmitter l APD High Sensitivity Receiverl Multi-rate Operation for 2.5 / 2.125 / 1.062 / 1.25 Gbps l Duplex SC Connectorl 30 dB Power Budget At Least l SCA-2 Host Connector l Single +5 V Power Supplyl RoHS Compliantl Differential PECL Inputs and Outputs l TTL RX-LOS Output l Hot Pluggablel Class 1 Laser International Safety Standard IEC-60825 CompliantAPPLICATIONSl Switch to Switch Interfacel High Speed Interface for File Servers l Bus Extension Application l Data Storagel Dual Rate 1.06 / 2.125 Gb/s Fibre ChannelDESCRIPTIONThe GBS-92120F-CXX0G series optical transceivers meet the Gigabit Interface Converter (GBIC) specification Rev. 5.5. It satisfies the optical interface specifications defined in IEEE 802.3z Drift 5.0 1000 BASE-SX for Gigabit Ethernet and 1x/2x Fiber Channel FC-PI13.0. This module is designed for single-mode fiber and operates at a nominal wavelength of CWDM. There are eighteen center wavelengths availablefrom 1270 nm to 1610 nm, each step 20 nm. A guaranteed minimum optical link budget of 30 dB is offered. The transmission distance is depended on the wavelength and loss of fiber. The transmitter section uses a multiple quantumwell CWDM DFB laser and is a class 1 laser compliant according to International Safety Standard IEC-60825. The receiver section uses an integrated InGaAs detector preamplifier (IDP) mounted in an optical header and a limiting post-amplifier IC. A PECL input / output logic interface is used. TTL RX-LOS output simplifies interface to external circuitry. A 20-pin SCA-2 host connector is used to connect the converter to the host system.LASER SAFETYThis single mode transceiver is a Class 1 laser product. It complies with IEC-60825 and FDA 21 CFR 1040.10 and 1040.11. The transceiver must be operated within the specified temperature and voltage limits. The optical ports of the module shall be terminated with an optical connector or with a dust plug.ORDER INFORMATIONP/No.Bit Rate (Gb/s)FC-PIPower Budget (dB) Wavelength (nm) Package Temp.(o C) TX Power (dBm) RX Sens. (dBm) RoHS Compliant GBS-92120F-CXX0G 2.125/1.063 200/100> 30 CWDM * SC GBIC0 to 705 to 0-30YesCWDM Wavelength (0 to 70oC)Central Wavelength Min. (nm) Typ. (nm) Max. (nm) Central Wavelength Min. (nm) Typ. (nm) Max. (nm) -C270 1264.5 1270 1277.5 -C450 1444.5 1450 1457.5 -C290 1284.5 1290 1297.5 -C470 1464.5 1470 1477.5 -C310 1304.5 1310 1317.5 -C490 1484.5 1490 1497.5 -C330 1324.5 1330 1337.5 -C510 1504.5 1510 1517.5 -C350 1344.5 1350 1357.5 -C530 1524.5 1530 1537.5 -C370 1364.5 1370 1377.5 -C550 1544.5 1550 1557.5 -C390 1384.5 1390 1397.5 -C570 1564.5 1570 1577.5 -C410 1404.5 1410 1417.5 -C590 1584.5 1590 1597.5 -C430 1424.5 1430 1437.5 -C610 1604.5 1610 1617.5CWDM *: 18 Wavelengths from 1270 nm to 1610 nm, each step 20 nm.***********************************************************************************************************************************************************************OPTOWAY TECHNOLOGY INC. No .38, Kuang Fu S. Road, Hu Kou, Hsin Chu Industrial Park, Hsin Chu, Taiwan 303Absolute Maximum RatingsParameterSymbol Min Max Units NotesStorage Temperature Tstg -40 85 o COperating Temperature Topr -5 70 o C Air flow 1m/sec Power Supply Voltage Vcc -0.5 6 V Input Voltage----0.5VccVRecommended Operating ConditionsParameterSymbol Min Typ Max Units ConditionsPower Supply Voltage Vcc 4.75 5 5.25 V Reference to GND.Power Supply Current I TX + I RX 200 300 mAOperating Temperature Topr 070 oC Air flow 1m/secData Rate1.0625 / 1.252.125 / 2.52.5Gb/sTransmitter Specifications (0o C < Topr < 70o C, 4.75V < Vcc < 5.25V)ParameterSymbol Min Typ Max Units NotesOpticalOptical Transmit Power Po 0 --- 5 dBm 1 Output Center Wavelength λ λ-5.5 λ λ+7.5 nm 2Output Spectrum Width∆λ --- 1 nm -20 dB Width Side Mode Suppression Ratio SMSR 30 dB Extinction Ratio E R 9 --- dBOptical Rise Time t r 150 ps 20% to 80% value Optical Fall Time t f 150 ps 20% to 80% valueElectricalDifferential Input Voltage V IH - V IL 0.65 2.0 Vp-p Transmit Fault LoadTX-FAULT LOAD 4.7 10 k Ω 3Transmit Fault Output-Low V TX-FAULT -L 0.0 0.5 V Transmit Fault Output-High V TX-FAULT-H Vcc – 0.5Vcc + 0.3 V TX-Disable Input - Low V TX-DISABLE -L 0 0.8 V TX-Disable Input - High V TX-DISABLE-H2.0 Vcc + 0.3 V TX-Disable Assert Time t_off 10 µsTX-Disable Negate Timet-on 1 ms Time to initialize, includes reset of TX-FAULTt-int300 ms TX FAULT from fault to assertiont-fault 100 µsTX-Disable time to start resett-reset10µs1. Output power is power coupled into a 9/125 µm SM fiber.2. ITU-T G.694.2 CWDM wavelength from 1270 nm to 1610 nm, each step 20 nm.3. Pull-up resistor on host Vcc.Receiver Specifications(0o C < Topr < 70o C, 4.75 V < Vcc < 5.25V)Parameter Symbol Min Typ Max Units NotesOpticalSensitivity @2.125Gb/s @BER=10-12SENS --- --- -30 dBm 4 Maximum Input Power Pin -9 --- dBm 4Signal detect – Hysteresis 1.0 --- dBWavelength of Operation 1260 --- 1620 nmRX-LOS – Asserted Pa --- --- -30 dBm Transition: low to high RX-LOS – Deasserted Pd -40 --- --- dBm Transition: high to low ElectricalDifferential Output Voltage ±RX-DAT 0.37 2.0 Vp-pData Output Rise Time Tr RX-DAT0.35 nsData Output Fall Time Tf RX-DAT0.35 nsReceiver Loss of Light Load RX-LOS LOAD 4.7 10 kΩ 5Loss of Signal Output Voltage --- Low RX-LOS L0 0.5 VLoss of Signal Output Voltage --- High RX-LOS H 2.4 Vcc VLoss of Signal Assert Time (off to on) T A,RX-LOS100 µsLoss of Signal Deassert Time (on to off) T D,RX-LOS100 µs4.Minimum sensitivity and saturation levels at BER=1E-12 for a 27-1 PRBS.5.Pull-up resistor on host Vcc.*********************************************************************************************************************************************************************** OPTOWAY TECHNOLOGY INC. No.38, Kuang Fu S. Road, Hu Kou, Hsin Chu Industrial Park, Hsin Chu, Taiwan 303***********************************************************************************************************************************************************************OPTOWAY TECHNOLOGY INC. No .38, Kuang Fu S. Road, Hu Kou, Hsin Chu Industrial Park, Hsin Chu, Taiwan 303A sequence value of 1 indicates that the signal is in the first group to engage during plugging of a module. A sequence value of 2 indicates that the signal is the second and last group. The two guide pins on the connector are electrically connected to the transceiver circuit ground. These two guide pins make contact with circuit prior to sequence 1 signals.Module Definition Module DefinitionMOD-DEF(0) PIN 4MOD-DEF (1) PIN 5MOD-DEF (2) PIN 6Interpretation byHost4TTL LowSCLSDASerial module definitionprotocolModule Definition 4 specifies a serial definition protocol. For this definition, upon power up, MOD-DEF(1:2) appear as no connector (NC) and MOD-DEF(0) is TTL LOW. When the host system detects this condition, it activates the serial protocol. The protocol uses the 2-wire serial CMOS E 2PROM protocol of the ATMEL AT24C01A/02/04 family of components.*********************************************************************************************************************************************************************** OPTOWAY TECHNOLOGY INC. No.38, Kuang Fu S. Road, Hu Kou, Hsin Chu Industrial Park, Hsin Chu, Taiwan 303。

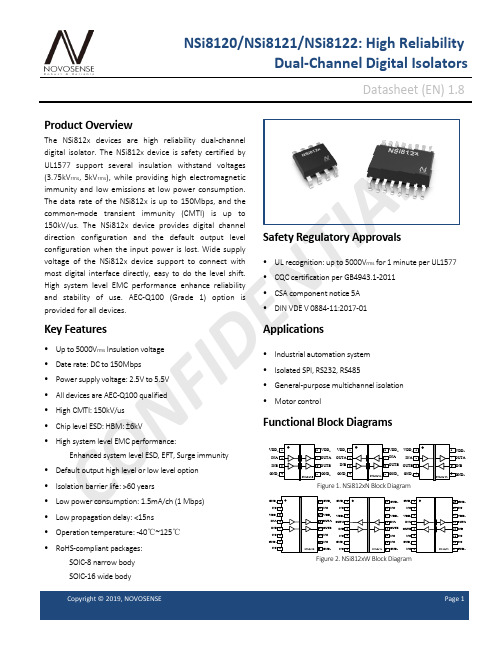

NSi812x高可靠双通道数字隔离器数据手册说明书

C O NF ID EN T IA LNSi8120/NSi8121/NSi8122: High ReliabilityDual-Channel Digital IsolatorsDatasheet (EN) 1.8Product OverviewThe NSi812x devices are high reliability dual-channel digital isolator. The NSi812x device is safety certified by UL1577 support several insulation withstand voltages (3.75kV rms , 5kV rms ), while providing high electromagnetic immunity and low emissions at low power consumption. The data rate of the NSi812x is up to 150Mbps, and the common-mode transient immunity (CMTI) is up to 150kV/us. The NSi812x device provides digital channel direction configuration and the default output level configuration when the input power is lost. Wide supply voltage of the NSi812x device support to connect with most digital interface directly, easy to do the level shift. High system level EMC performance enhance reliability and stability of use. AEC-Q100 (Grade 1) option is provided for all devices.Key Features• Up to 5000V rms Insulation voltage• Date rate: DC to 150Mbps• Power supply voltage: 2.5V to 5.5V • All devices are AEC-Q100 qualified • High CMTI: 150kV/us • Chip level ESD: HBM: ±6kV• High system level EMC performance:Enhanced system level ESD, EFT, Surge immunity• Default output high level or low level option • Isolation barrier life: >60 years• Low power consumption: 1.5mA/ch (1 Mbps) • Low propagation delay: <15ns • Operation temperature: -40℃~125℃ • RoHS-compliant packages:SOIC-8 narrow body SOIC-16 wide bodySafety Regulatory Approvals• UL recognition: up to 5000V rms for 1 minute per UL1577• CQC certification per GB4943.1-2011• CSA component notice 5A • DIN VDE V 0884-11:2017-01Applications• Industrial automation system • Isolated SPI, RS232, RS485• General-purpose multichannel isolation • Motor controlFunctional Block DiagramsC O NF ID EN T IA LIndex1.0 ABSOLUTE MAXIMUM RATINGS .............................................................................................................................. 3 2.0 SPECIFICATIONS ........................................................................................................................................................... 3 2.1. E LECTRICAL CHARACTERISTICS .................................................................................................................................................. 3 2.2. TYPICAL PERFORMANCE CHARACTERISTICS ........................................................................................................................... 7 2.3. P ARAMETER M EASUREMENT I NFORMATION . (8)3.0 HIGH VOLTAGE FEATURE DESCRIPTION (9)3.1. INSULATION AND SAFETY RELATED SPECIFICATIONS (9)3.2. DIN VDE V 0884-11(VDE V 0884-11):2017-01 INSULATION CHARATERISTICS ....................................................................... 9 3.3. R EGULATORY INFORMATION ................................................................................................................................................... 11 4.0 FUNCTION DESCRIPTION ..........................................................................................................................................11 5.0 APPLICATION NOTE ................................................................................................................................................... 12 5.1. PCB L AYOUT ...................................................................................................................................................................... 12 5.2. H IGH SPEED PERFORMANCE ................................................................................................................................................... 12 5.3. T YPICAL S UPPLY C URRENT E QUATIONS ..................................................................................................................................... 13 6.0 PACKAGE INFORMATION ......................................................................................................................................... 13 7.0 TAPE AND REEL INFORMATION ............................................................................................................................. 17 8.0 ORDER INFORMATION .............................................................................................................................................. 20 9.0 REVISION HISTORY . (21)C O NF ID EN T IA L1.0 ABSOLUTE MAXIMUM RATINGSPower Supply Voltage VDD1, VDD2 -0.5 6.5 V Maximum Input Voltage VINA, VINB -0.4 VDD+0.41 V Maximum Output Voltage V OUTA , V OUTB -0.4 VDD+0.41 VMaximum Input/Output Pulse VoltageVINA, VINB, V OUTA , V OUTB-0.8VDD+0.8VPulse width should be less than 100ns, and the duty cycle should be less than 10%Common-Mode Transients CMTI ±150 kV/us Output currentIo -15 15mAMaximum Surge Isolation VoltageV IOSM5.3kVOperating Temperature Topr -40125 ℃Storage Temperature Tstg -40150℃Electrostatic dischargeHBM±6000VCDM±2000V1 The maximum voltage must not exceed 6.5V.2.0 SPECIFICATIONS2.1. ELECTRICAL CHARACTERISTICS(VDD1=2.5V~5.5V, VDD2=2.5V~5.5V, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 5V, VDD2 = 5V, Ta =25℃)Power on ResetVDD POR2.2 V POR threshold as during power-upVDD HYS 0.1 V POR threshold Hysteresis Input ThresholdV IT1.6 V Input Threshold at rising edge V IT_HYS 0.4 V Input Threshold Hysteresis High Level Input Voltage V IH 2 V Low Level Input Voltage V IL 0.8 V High Level Output Voltage V OH VDD-0.3 V I OH ≤ 4mA Low Level Output VoltageV OL0.3VI OL ≤ 4mAC O NF ID EN T IA LOutput Impedance R out 50 ohm Input Pull high or low CurrentI pull 8 15 uA Start Up Time after POR trbs 40 usec Common Mode Transient ImmunityCMTI±100±150kV/us(VDD1=5V± 10%, VDD2=5V± 10%, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 5V, VDD2 = 5V, Ta = 25℃)Supply currentNSi8120 I DD1(Q0) 0.58 0.87 mAAll Input 0V for NSi8120x0 Or All Input at supply for NSi8120x1 I DD2(Q0) 1.18 1.77 mA I DD1(Q1) 2.92 4.38 mA All Input at supply for NSi8120x0 Or All Input 0V for NSi8120x1I DD2(Q1) 1.241.86mAI DD1(1M) 1.71 2.56 mA All Input with 1Mbps, C L =15pFI DD2(1M)1.382.07mAI DD1(10M) 1.78 2.67 mA All Input with 10Mbps, C L =15pF I DD2(10M)3.24.8mA I DD1(100M)2.103.15 mA All Input with 100Mbps, C L =15pFI DD2(100M)21.031.5mANSi8121/ NSi8122 I DD1(Q0) 1.031.55 mA All Input 0V for NSi812xx0 Or All Input at supply for NSi812xx1 I DD2(Q0) 1.00 1.5 mA I DD1(Q1)2.203.3 mA All Input at supply for NSi812xx0Or All Input 0V for NSi812xx1 I DD2(Q1)2.133.2 mA I DD1(1M) 1.72 2.58 mA All Input with 1Mbps, C L =15pFI DD2(1M) 1.68 2.52 mA I DD1(10M) 2.62 3.93 mA All Input with 10Mbps, C L =15pFI DD2(10M) 2.71 4.06 mA I DD1(100M) 11.01 16.5 mA All Input with 100Mbps, C L = 15pF I DD2(100M)12.8 19.2 mA Data RateDR 0 150 MbpsC O NF ID EN T IA LPropagation Delayt PLH 5 8.20 15 ns See Figure 2.7 , C L = 15pF t PHL 5 10.56 15 ns See Figure 2.7, C L = 15pF Pulse Width Distortion |t PHL – t PLH | PWD5.0nsSee Figure 2.7 , C L = 15pFRising Time t r 5.0 ns See Figure 2.7 , C L = 15pF Falling Timet f 5.0 ns See Figure 2.7 , C L = 15pFPeak Eye Diagram Jitter t JIT (PK) 350 ps Channel-to-Channel Delay Skewt SK (c2c) 2.5 nsPart-to-Part Delay Skewt SK (p2p)5.0ns(VDD1=3.3V± 10%, VDD2=3.3V± 10%, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 3.3V, VDD2 = 3.3V, Ta =25℃)Supply currentNSi8120 I DD1(Q0) 0.550.83mA All Input 0V for NSi8120x0 Or All Input at supply for NSi8120x1 I DD2(Q0) 1.12 1.68 mA I DD1(Q1) 2.87 4.3 mA All Input at supply for NSi8120x0 Or All Input 0V for NSi8120x1 I DD2(Q1)1.18 1.77mA I DD1(1M)1.72.55mA All Input with 1Mbps, C L = 15pFI DD2(1M)1.271.91 mA I DD1(10M) 1.732.6 mA All Input with 10Mbps, C L = 15pF I DD2(10M)2.413.6 mA I DD1(100M) 2.05 3.08 mA All Input with 100Mbps, C L = 15pF I DD2(100M)14.0521.08mANSi8121/ NSi8122 I DD1(Q0) 0.98 1.47 mA All Input 0V for NSi812xx0 Or All Input at supply for NSi812xx1 I DD2(Q0) 0.95 1.43 mA I DD1(Q1) 2.14 3.21 mA All Input at supply for NSi812xx0 Or All Input 0V for NSi812xx1 I DD2(Q1) 2.08 3.12 mA I DD1(1M) 1.63 2.45 mA All Input with 1Mbps, C L = 15pFI DD2(1M) 1.59 2.39 mA I (10M)2.223.33mAAll Input with 10Mbps,C O NF I D EN T IA LI DD2(10M) 2.25 3.38 mA C L = 15pFI DD1(100M) 7.57 11.36 mA All Input with 100Mbps, C L = 15pF I DD2(100M)8.5 12.75 mA Data RateDR 0 150 Mbps Minimum Pulse Width PW 5.0 nsPropagation Delayt PLH 5 9.20 15 ns See Figure 2.7 , C L = 15pF t PHL5 10.40 15 ns See Figure 2.7, C L = 15pF Pulse Width Distortion |t PHL – t PLH | PWD5.0nsSee Figure 2.7 , C L = 15pFRising Time t r 5.0 ns See Figure 2.7 , C L = 15pF Falling Timet f5.0 nsSee Figure 2.7 , C L = 15pFPeak Eye Diagram Jitter t JIT (PK) 350psChannel-to-Channel Delay Skewt SK (c2c)2.5nsPart-to-Part Delay Skew t SK (p2p)5.0ns(VDD1=2.5V± 10%, VDD2=2.5V± 10%, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 2.5V, VDD2 = 2.5V, Ta =25℃)Supply currentNSi8120I DD1(Q0) 0.53 0.8 mA All Input 0V for NSi8120x0 Or All Input at supply for NSi8120x1 I DD2(Q0) 1.11.65 mA I DD1(Q1)2.85 4.28 mA All Input at supply for NSi8120x0 Or All Input 0V for NSi8120x1 I DD2(Q1)1.15 1.73 mA I DD1(1M) 1.632.45 mA All Input with 1Mbps, C L = 15pFI DD2(1M) 1.21 1.82 mA I DD1(10M) 1.68 2.52 mA All Input with 10Mbps, C L = 15pFI DD2(10M) 2.05 3.08 mA I DD1(100M) 1.95 2.93 mA All Input with 100Mbps, C L = 15pFI DD2(100M)10.415.6mANSi8121/ NSi8122I DD1(Q0) 0.96 1.44 mA All Input 0V for NSi812xx0 Or All Input at supply for NSi812xx1I (Q0)0.931.395mAF ID EN T IA LI DD1(Q1) 2.11 3.165 mA All Input at supply for NSi812xx0Or All Input 0V for NSi812xx1 I DD2(Q1) 2.05 3.075 mA I DD1(1M) 1.58 2.37 mA All Input with 1Mbps, C L = 15pFI DD2(1M) 1.54 2.31 mA I DD1(10M) 2.02 3.03 mA All Input with 10Mbps, C L = 15pFI DD2(10M) 2.04 3.06 mA I DD1(100M) 6.03 9.045 mA All Input with 100Mbps, C L = 15pF I DD2(100M)6 9 mAData RateDR 0 150 Mbps Minimum Pulse Width PW 5.0 nsPropagation Delayt PLH 5 10 15 nsSee Figure 2.7 , C L = 15pF t PHL5 10 15nsSee Figure 2.7, C L = 15pFPulse Width Distortion |t PHL – t PLH | PWD5.0nsSee Figure 2.7 , C L = 15pFRising Time t r5.0ns See Figure 2.7 , C L = 15pF Falling Timet f5.0 ns See Figure 2.7 , C L = 15pFPeak Eye Diagram Jitter t JIT (PK)350ps Channel-to-Channel Delay Skewt SK (c2c)2.5ns Part-to-Part Delay Skew t SK (p2p)5.0ns2.2. TYPICAL PERFORMANCE CHARACTERISTICSFigure 2.1 NSi8120 VDD1 Supply Current vs Data Rate Figure 2.2 NSi8120 VDD2 Supply Current vs Data RateC OE2.3. PARAMETER MEASUREMENT INFORMATIONC LFigure 2.7 Switching Characteristics Test Circuit and WaveformFigure 2.8 Common-Mode Transient Immunity Test CircuitC O NF ID EN T IA L3.0 HIGH VOLTAGE FEATURE DESCRIPTION3.1. INSULATION AND SAFETY RELATED SPECIFICATIONSMinimum External Air Gap (Clearance)L(I01) 4.0 8.0 mm Shortest terminal-to-terminal distance through air Minimum External Tracking (Creepage)L(I02)4.08.0mmShortest terminal-to-terminal distance across the package surfaceMinimum internal gap DTI 20 um Distance through insulationTrackingResistance(Comparative Tracking Index) CTI>400VDIN EN 60112 (VDE 0303-11); IEC 60112Material GroupⅡ3.2. DIN VDE V 0884-11(VDE V 0884-11):2017-01 INSULATION CHARATERISTICSSOIC-8 SOIC-16 Installation Classification per DIN VDE 0110For Rated Mains Voltage ≤ 150V rms Ⅰto Ⅳ Ⅰto Ⅳ For Rated Mains Voltage ≤ 300V rms Ⅰto Ⅲ Ⅰto Ⅳ For Rated Mains Voltage ≤ 400V rms Ⅰto Ⅲ Ⅰto Ⅳ Climatic Classification10/105/2110/105/21 Pollution Degree per DIN VDE 0110, Table 122Maximum repetitive isolation voltageVIORM 565 849 Vpeak Input to Output Test Voltage, Method B1V IORM × 1.5 = V pd (m) , 100%production test, t ini = t m = 1 sec, partial discharge < 5 pCV pd (m)8471273VpeakInput to Output Test Voltage, Method AAfter Environmental Tests Subgroup 1V IORM × 1.2= V pd (m) , t ini = 60 sec, t m = 10 sec, partial V pd (m)6781018VpeakC O N T IA LAfter Input and /or Safety Test Subgroup 2 and Subgroup 3 V IORM × 1.2= V pd (m) , t ini = 60 sec, t m = 10 sec, partialdischarge < 5 pC V pd (m)6781018VpeakMaximum transient isolation voltage t = 60 sec VIOTM 5300 7000 Vpeak Maximum Surge Isolation VoltageTest method per IEC60065,1.2/50uswaveform, VTEST=VIOSM×1.3VIOSM53845384VpeakIsolation resistance VIO =500V RIO >109 >109 Ω Isolation capacitance f = 1MHzCIO 0.6 0.6pFInput capacitanceCI22pF Total Power Dissipation at 25℃Ps1499 mW Safety input, output, or supply currentθJA = 140 °C/W, V I = 5.5 V, T J = 150 °C, T A = 25 °C Is160mAθJA = 84 °C/W, V I = 5.5 V, T J = 150 °C, T A = 25 °C237 mA Case TemperatureTs150150℃Figure 3.2 NSi8120W/NSi8121W/NSi8122W Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN VDE V 0884-11C O NF ID EN T IA L3.3. REGULATORY INFORMATIONThe NSi8120N/NSi8121N/NSi8122N are approved by the organizations listed in table.UL 1577 Component Recognition Program 1Approved under CSA ComponentAcceptance Notice 5ADIN VDE V 0884-11:2017-012Certified by CQC11-471543-2012 GB4943.1-2011Single Protection, 3750V rms Isolation voltageSingle Protection, 3750V rms IsolationvoltageBasic Insulation 565Vpeak, V IOSM =5384VpeakBasic insulation at 400V rms (565Vpeak)File (E500602)File (E500602)File (5024579-4880-0001)File (pending)1 In accordance with UL 1577, each NSi8120N/NSi8121N/NSi8122N is proof tested by applying an insulation test voltage ≥ 4500 Vrms for 1 sec.2 In accordance with DIN VDE V 0884-11, each NSi8120N/NSi8121N/NSi8122N is proof tested by applying an insulation test voltage ≥ 847 V peak for 1 sec(partial discharge detection limit = 5 pC). The * marking branded on the component designates DIN VDE V 0884-11 approval.The NSi8120W/NSi8121W/NSi8122W are approved by the organizations listed in table.UL 1577 Component Recognition Program 1Approved under CSAComponent Acceptance Notice5ADIN VDE V 0884-11(VDE V 0884-11):2017-012 Certified by CQC11-471543-2012 GB4943.1-2011Single Protection, 5000V rms Isolation voltageSingle Protection, 5000V rmsIsolation voltageBasic Insulation 849Vpeak, V IOSM =5384Vpeak Basic insulation at 800V rms (1131Vpeak) Reinforced insulation at 400V rms (565Vpeak)File (E500602)File (E500602)File (5024579-4880-0001)File (pending)1 In accordance with UL 1577, each NSi8120W/NSi8121W/NSi8122W is proof tested by applying an insulation test voltage ≥ 6000 V rms for 1 sec.2 In accordance with DIN VDE V 0884-11, each NSi8120W/NSi8121W/NSi8122W is proof tested by applying an insulation test voltage ≥ 1273 V peak for 1 sec(partial discharge detection limit = 5 pC). The * marking branded on the component designates DIN VDE V 0884-11 approval.4.0 FUNCTION DESCRIPTIONThe NSi812x is a Dual-channel digital isolator based on a capacitive isolation barrier technique. The digital signal is modulated with RF carrier generated by the internal oscillator at the Transmitter side. Then it is transferred through the capacitive isolation barrier and demodulated at the Receiver side.The NSi812x devices are high reliability dual-channel digital isolator with AEC-Q100 qualified. The NSi812x device is safety certified by UL1577 support several insulation withstand voltages (3.75kV rms , 5kV rms ), while providing high electromagnetic immunity and low emissions at low power consumption. The data rate of the NSi812x is up to 150Mbps, and the common-mode transient immunity (CMTI) is up to 150kV/us. The NSi812x device provides digital channel direction configuration and the default output level configuration when the input power is lost. Wide supply voltage of the NSi812x device support to connect with most digital interface directly, easy to do the level shift. High system level EMC performance enhance reliability and stability of use.The NSi812x has a default output status when VDDIN is unready and VDDOUT is ready as shown in Table 4.1, which helps for diagnosis when power is missing at the transmitter side. The output B follows the same status with the input A within 1us after powering up.C O NF ID EN T IA LCopyright © 2019, NOVOSENSEPage 12 Table 4.1 Output status vs. power statusH Ready Ready H Normal operation.L Ready Ready L XUnreadyReadyL HThe output follows the same status with the input within 60us after input side VDD1 is powered on.X Ready Unready XThe output follows the same status with the input within 60us after output side VDD2 is powered on.5.0 APPLICATION NOTE5.1. PCB LAYOUTThe NSi812x requires a 0.1 µF bypass capacitor between VDD1 and GND1, VDD2 and GND2. The capacitor should beplaced as close as possible to the package. Figure 5.1 to Figure 5.4 show the recommended PCB layout, make sure the space under the chip should keep free from planes, traces, pads and via. To enhance the robustness of a design, the user may also include resistors (50–300 Ω ) in series with the inputs and outputs if the system is excessively noisy. The series resistors also improve the system reliability such as latch-up immunity.The typical output impedance of an isolator driver channel is approximately 50 Ω, ±40%. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.Figure5.1 Recommended PCB Layout — Top Layer Figure5.2 Recommended PCB Layout — Bottom LayerFigure5.3 Recommended PCB Layout — Top Layer Figure5.4 Recommended PCB Layout — Bottom Layer5.2. HIGH SPEED PERFORMANCEFigure 5.5 shows the eye diagram of NSi812x at 200Mbps data rate output. The result shows a typical measurement on the NSi812x with 350ps p-p jitter.C O NF ID EN T IA LFigure5.5 NSi812x Eye Diagram5.3. TYPICAL SUPPLY CURRENT EQUATIONSThe typical supply current of NSi812x can be calculated using below equations. I DD1 and I DD2 are typical supply currents measured in mA, f is data rate measured in Mbps, C L is the capacitive load measured in pFNSi8120:I DD1 = 0.19 *a1+1.45*b1+0.82*c1. I DD2 = 1.36+ VDD1*f* C L *c1*10-9When a1 is the channel number of low input at side 1, b1 is the channel number of high input at side 1, c1 is the channel number of switch signal input at side 1.NSi8121/ NSi8122:I DD1 = 0.87 +1.26*b1+0.63*c1+ VDD1*f* C L *c2*10-9I DD2 = 0.87 +1.26*b2+0.63*c2+ VDD1*f* C L *c1*10-9When b1 is the channel number of high input at side 1, c1 is the channel number of switch signal input at side 1, b2 is the channel number of high input at side 2, c2 is the channel number of switch signal input at side 2.6.0 PACKAGE INFORMATIONVDD GND 22VDD INA GND 2VDD 2Figure 6.1 NSi8120N Package Figure 6.2 NSi8121N PackageC O NF ID EN T IA LVDD INBGND 22Figure 6.3 NSi8122N PackageFigure 6.4 SOIC8 Package Shape and Dimension in millimeters (inches)Table6.1 NSi8120N/ NSi8121N/ NSi8122N Pin Configuration and DescriptionNSi8121N PIN NO.NSi8122N PIN NO.SYMBOL FUNCTION1 1 1 VDD1 Power Supply for Isolator Side 12 7 2 INA Logic Input A3 3 6 INB Logic Input B4 4 4 GND1 Ground 1, the ground reference for Isolator Side 15 5 5 GND2 Ground 2, the ground reference for Isolator Side 26 6 3 OUTB Logic Output B7 2 7 OUTA Logic Output A888VDD2Power Supply for Isolator Side 2C O NFVDD GND GND 2VDD 2GND 2GND NC NCNC VDD GND GND 2VDD 22GND NC NC NCFigure 6.5 NSi8120W Package Figure 6.6 NSi8121W PackageVDD INB GND GND 2VDD 2GND 2GND NC NC NCFigure 6.7 NSi8122W PackageFigure 6.8 WB SOIC16 Package Shape and Dimension in millimeters and (inches)C O NF ID EN T IA LTable 6.2 NSi8120W/ NSi8121W/ NSi8122W Pin Configuration and Description1 1 1 GND1 Ground 1, the ground reference for Isolator Side 12 2 2 NC No Connection.3 3 3 VDD1 Power Supply for Isolator Side 14 13 4 INA Logic Input A5 5 12 INB Logic Input B6 6 6 NC No Connection.7 7 7 GND1 Ground 1, the ground reference for Isolator Side 18 8 8 NC No Connection. 9 9 9 GND2 Ground 2, the ground reference for Isolator Side 210 10 10 NC No Connection. 11 11 11 NC No Connection. 12 12 5OUTB Logic Output A 13 4 13OUTALogic Output B 14 14 14 VDD2 Power Supply for Isolator Side 215 15 15 NC No Connection.161616GND2Ground 2, the ground reference for Isolator Side 27.0TAPE AND REEL INFORMATIONLAITNEDIFNOCC O NF ID EN T IA LFigure 7.1 Tape and Reel Information of SOIC8LAITNEDIFNOCFigure 7.2 Tape and Reel Information of WB SOIC16NF ID EN T IA L8.0 ORDER INFORMATIONNSi8120N0 3.75 2 0 150 Low -40 to 125℃ NO SOIC8 NSi8120N1 3.75 2 0 150 High -40 to 125℃ NO SOIC8 NSi8121N0 3.75 1 1 150 Low -40 to 125℃ NO SOIC8 NSi8121N1 3.75 1 1 150 High -40 to 125℃ NO SOIC8 NSi8122N0 3.75 1 1 150 Low -40 to 125℃ NO SOIC8 NSi8122N1 3.75 1 1 150 High -40 to 125℃ NO SOIC8 NSi8120W0 5 2 0 150 Low -40 to 125℃ NO WB SOIC16 NSi8120W1 5 2 0 150 High -40 to 125℃ NO WB SOIC16 NSi8121W0 5 1 1 150 Low -40 to 125℃ NO WB SOIC16 NSi8121W1 5 1 1 150 High -40 to 125℃ NO WB SOIC16 NSi8122W0 5 1 1 150 Low -40 to 125℃ NO WB SOIC16 NSi8122W1 5 1 1 150 High -40 to 125℃ NO WB SOIC16 NSi8120N0Q 3.75 2 0 150 Low -40 to 125℃ YES SOIC8 NSi8120N1Q 3.75 2 0 150 High -40 to 125℃ YES SOIC8 NSi8121N0Q 3.75 1 1 150 Low -40 to 125℃ YES SOIC8 NSi8121N1Q 3.75 1 1 150 High -40 to 125℃ YES SOIC8 NSi8122N0Q 3.75 1 1 150 Low -40 to 125℃ YES SOIC8 NSi8122N1Q 3.75 1 1 150 High -40 to 125℃ YES SOIC8 NSi8120W0Q 5 2 0 150 Low -40 to 125℃ YES WB SOIC16 NSi8120W1Q 5 2 0 150 High -40 to 125℃ YES WB SOIC16 NSi8121W0Q 5 1 1 150 Low -40 to 125℃ YES WB SOIC16 NSi8121W1Q 5 1 1 150 High -40 to 125℃ YES WB SOIC16 NSi8122W0Q 5 1 1 150 Low -40 to 125℃ YES WB SOIC16 NSi8122W1Q 5 1 1 150 High -40 to 125℃YES WB SOIC16 NOTE: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures. All devices are AEC-Q100 qualified.Part Number Rule:NSi(81)(2)(1)(N)(1)(Q)C O NF ID EN T IA LNSi8120/NSi8121/NSi81229.0 REVISION HISTORY1.0 Original2017/11/15 1.1 Change to Ordering information2018/3/26 1.2 Add maximum operation current specification. 2018/6/20 1.3 Change block diagram 2018/7/28 1.4 Correct Table 6.2 Pin No.2018/8/20 1.5 Add specification “Input Pull high or low Current” 2018/9/10 1.6 Add “Maximum Input/Output Pulse Voltage” 2018/10/91.7 Change to Ordering information 2018/12/20 1.8 Change Certification Information2019/06/17。

SLB_C

0°C 到+70°C(32°F 到 158°F) - 25°C 到+70°C(-13°F 到 158°F) - 25°C 到+70C(-13°F 到 158°F)

♦ 只有在必要时才接触电子板。 ♦ 在接触电子板之前,先将身体所带的静电释放。 ♦ 电子板不要接触绝缘体,如塑料、绝缘桌面及由人造纤维制成的布料或衣物等。 ♦ 电子板放于良导体表面上。 ♦ 电子板或元件只允许储存、装运在导电的包装盒内(如导电的塑料盒或金属容器

等)。

♦ 如果包装材料不导电,电子板必须包上一层导电材料,如导电的泡沫橡胶或铝箔 等。

地运行。

0-2

6SE7085-0NX84-0FJ0 Siemens Electrical Drives Ltd.

使用说明书 SIMOVERT MASTERDRIVES

SLB-SIMOLINK 板

定义和警告

! 当心

小心静电放电(ESD)击穿元件

电路板中包含有静电敏感元件,如处理不当,这些元件极易损坏。当您接触电子板时, 应注意以下事项:

5

显 示 ......................................................................................................................................... 5-1

6

启 动 ......................................................................................................................................... 6-1

Emaux SSC Mini盐水氯化器快速用户指南说明书