DC综合全过程及使用的命令

Tcl与DesignCompiler(三)——DC综合的流程

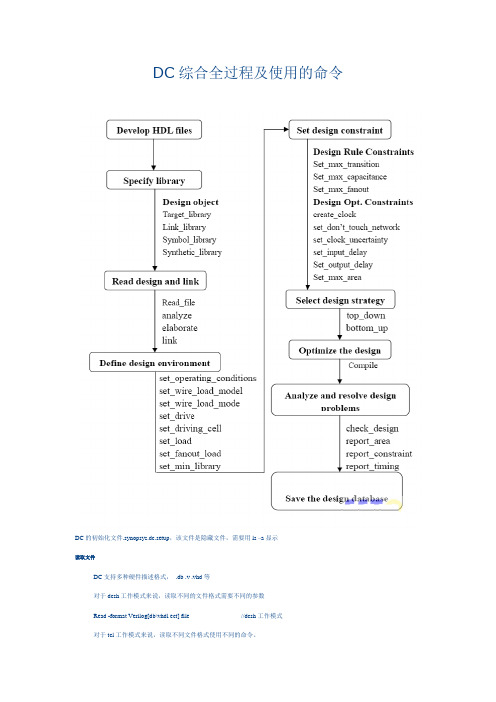

Tcl与DesignCompiler(三)——DC综合的流程1、基本流程概述⾸先给三个图,⼀个图是⾼层次设计的流程图:下⾯是我对这张图的理解: ①设计之前,准备好库、HDL代码的思想、约束⽣成;然后根据设计思想⽤ RTL 源码详细地、完整地为设计建⽴模型、定义设计中寄存器结构和数⽬、定义设计中的组合电路功能、定义设计中寄存器时钟等等的设计规格和实现。

②完成 RTL 源码设计之后,应让设计开发与功能仿真并⾏进⾏: ·在设计开发阶段,我们使⽤ DC 来实现特定的设计⽬标(设计规则和优化约束),以及执⾏默认选项的初步综合. ·如果设计开发结果未能在 10%的偏差范围内满⾜时序⽬标,则需要修正 HDL 代码,然后重复设计开发和功能验证的过程. ·在功能仿真中,通过特定的⼯具来确定设计是否能按如所需的功能⼯作. ·如果设计未能满⾜功能要求, 我们必须修改设计代码以及重复设计开发和功能仿真. 继续设计开发和功能仿真直⾄设计功能正确及满⾜⼩于 10%偏差的时序⽬标. ③使⽤ DC 完成设计的综合并满⾜设计⽬标.这个过程包括三个步骤,即综合=转化+逻辑优化+映射,⾸先将 RTL 源代码转化为通⽤的布尔等式,然后设计的约束对电路进⾏逻辑综合和优化,使电路能满⾜设计的⽬标或者约束,最后使⽤⽬标⼯艺库的逻辑单元映射成门级⽹表,在将设计综合成门级⽹表之后,要验证此时的设计是否满⾜设计⽬标.如果不能满⾜设计⽬标,此时需要产⽣及分析报告确定问题及解决问题 ④当设计满⾜功能、时序以及其他的设计⽬标的时候,需要执⾏物理层设计最后分析物理层设计的性能,也就是使⽤DC的拓扑模式,加⼊floorplan的物理信息后进⾏综合分析设计的性能。

如果结果未能满⾜设计⽬标,应返回第三步.如果满⾜设计⽬标,则本部分设计周期完成. ⼀个图是DC在设计流程中的位置: 这个图将上⾯的流程图细化,着重与DC的部分,描述了使⽤DC进⾏逻辑综合时要做的事,同时,也是对前⾯的流程图解说的图形概述。

DC综合

DC综合归纳总结Author:WJDate:Dec 11 2014 概述:●综合是将RTL源代码转换成门级网表的过程。

●电路的逻辑综合一般由三个步骤组成,即综合=转化+逻辑优化+映射(Synthesis=Translation+Logic Optimization+Mapping)●在综合过程中,优化进程尝试完成库单元的组合,使组合成的电路能最好地满足设计的功能、时序和面积的要求●综合是约束驱动(constraint driven)的,给定的约束是综合的目标。

约束一般是在对整个系统进行时序分析得到的,综合工具会对电路进行优化以满足约束的要求。

●综合以时序路径为基础进行优化。

(注意:电路中的cell,对于前一级是load,其电容越大负载能力越大;对于后一级是drive,其电阻越小驱动能力越大。

有:大器件大电容小电阻,小器件小电容大电阻)启动文件:1. search_path指定了综合工具的搜索路径。

2. target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

3.synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

4. link_library是链接库,它是DC在解释综合后网表时用来参考的库。

一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

5. symbol_library为指定的符号库。

6. synlib_wait_for_design_license用来获得DesignWare-Foudation的许可(license)。

7. alias语句与UNIX相似,它定义了命令的简称。

8. 另外,在启动文件中用符号“/*” 和“*/” 进行注释。

DC使用说明

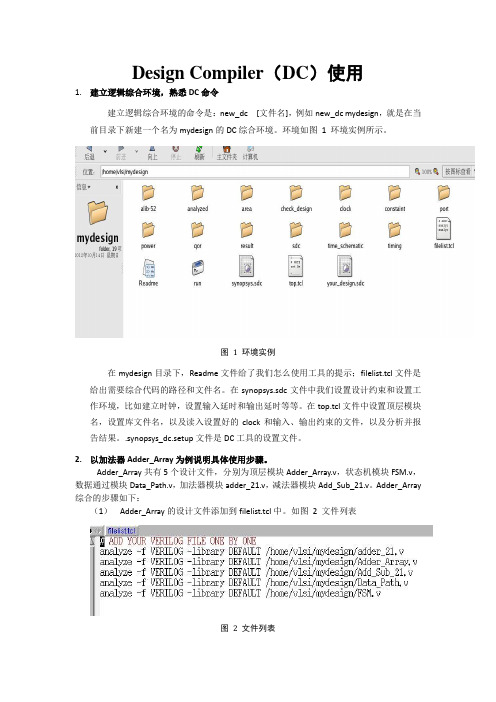

Design Compiler(DC)使用1.建立逻辑综合环境,熟悉DC命令建立逻辑综合环境的命令是:new_dc [文件名],例如new_dc mydesign,就是在当前目录下新建一个名为mydesign的DC综合环境。

环境如图1 环境实例所示。

图1 环境实例在mydesign目录下,Readme文件给了我们怎么使用工具的提示;filelist.tcl文件是给出需要综合代码的路径和文件名。

在synopsys.sdc文件中我们设置设计约束和设置工作环境,比如建立时钟,设置输入延时和输出延时等等。

在top.tcl文件中设置顶层模块名,设置库文件名,以及读入设置好的clock和输入、输出约束的文件,以及分析并报告结果。

.synopsys_dc.setup文件是DC工具的设置文件。

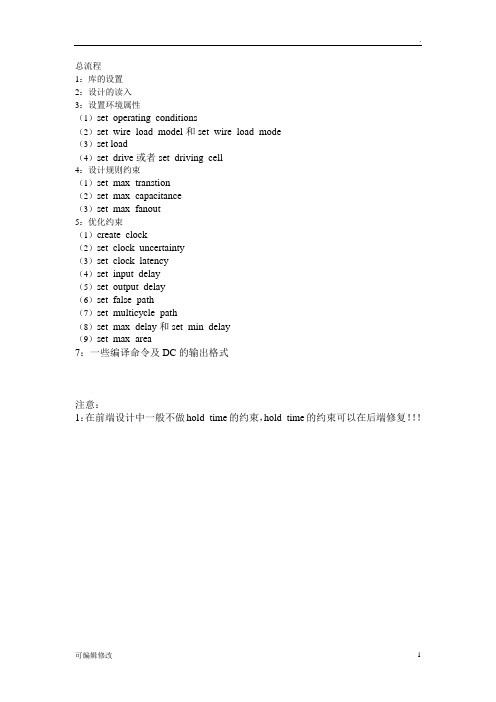

2.以加法器Adder_Array为例说明具体使用步骤。

Adder_Array共有5个设计文件,分别为顶层模块Adder_Array.v,状态机模块FSM.v,数据通过模块Data_Path.v,加法器模块adder_21.v,减法器模块Add_Sub_21.v。

Adder_Array 综合的步骤如下:(1)Adder_Array的设计文件添加到filelist.tcl中。

如图2 文件列表图2 文件列表(2)在top.tcl中将顶层模块设置为Adder_Array。

如图3修改顶层模块名图3 修改顶层模块名(3)修改synopsys.sdc实现以下设计约束:时钟周期1.2ns,input_delay设置为0.5ns,output_delay设置为0.5ns。

如果使用者想增加其他的设计约束可以在此文件中增添。

(4)进入刚才建好的综合环境,在终端中执行run命令,调用Design Compiler执行逻辑综合。

打开终端:cd [建好的环境路径],进入后输入run,即可。

(5)等逻辑综合执行完毕后,查看123.log,对其中的error和warning进行确认,如果有问题修改设计或综合脚本后重新综合,直至没有问题。

DC综合操作流程_设置流程

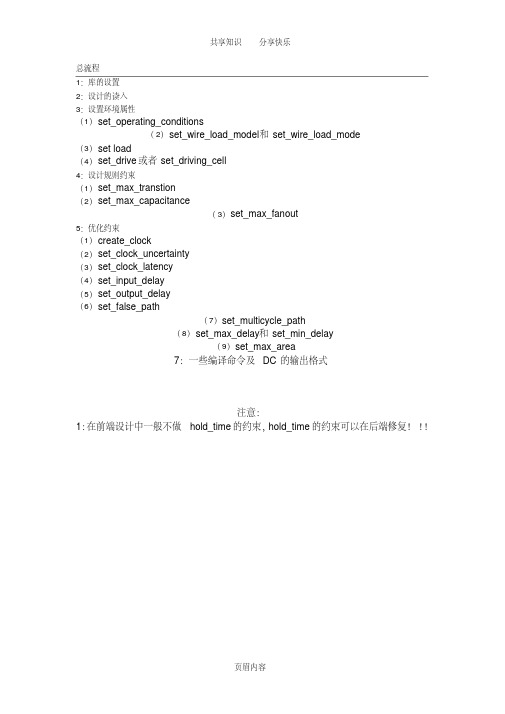

总流程1:库的设置2:设计的读入3:设置环境属性(1)set_operating_conditions(2)set_wire_load_model和set_wire_load_mode(3)set load(4)set_drive或者set_driving_cell4:设计规则约束(1)set_max_transtion(2)set_max_capacitance(3)set_max_fanout5:优化约束(1)create_clock(2)set_clock_uncertainty(3)set_clock_latency(4)set_input_delay(5)set_output_delay(6)set_false_path(7)set_multicycle_path(8)set_max_delay和set_min_delay(9)set_max_area7:一些编译命令及DC的输出格式注意:1:在前端设计中一般不做hold_time的约束,hold_time的约束可以在后端修复!!!总流程:1:对库进行基本设置,如下:设置完成后应该查看.synopsys_dc.setup里面库的设置和软件application setup处的设置是否一样!DC的初始化文件.synopsys.dc.setup 需要用ls –a显示,命令:more .synopsys.dc.setup查看文件内容!2:读入设计,两种方法:read和analyze+elaborateAnalyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件3:设置环境定义:如果不指定operating_conditions,DC自动搜索link_library 中的第一个库的工作环境作为优化时使用的工作环境。

DC综合过程,Design Compiler

Design Compiler 使用简要说明Design Compiler可以针对层次化的组合电路或者时序电路的速度、面积和可布性进行优化。

按照所定义的电路的测量特征所要达到的目标,Design Compiler综合一个电路并将其放入目标库中,这样可以生成适用于你的计算机辅助设计工程(CAE)工具的原理图或网表。

综合的过程如下图:•读入设计及其子设计。

•设置顶层的设计特性参数•设置实际时序和面积目标参数•执行check_design验证设计,识别并且更正错误•进行Design Compiler优化在db、verilog、vhdl文件夹下设计内容都是一样的,只是形式不一样。

Db文件夹:ALARM_BLOCK.db ALARM_COUNTER.db ALARM_SM.dbALARM_STATE_MACHINE.db COMPARATOR.dbHOURS_FILTER.db MUX.db TIME_BLOCK.dbTIME_COUNTER.dbTIME_STATE_MACHINE.db CONVERTOR.pla CONVERTOR_CKT.db TOP.dbVerilog文件夹:ALARM_BLOCK.v ALARM_COUNTER.v ALARM_SM.vALARM_STATE_MACHINE.v COMPARATOR.vHOURS_FILTER.v MUX.vTIME_BLOCK.vTIME_COUNTER.vTIME_STATE_MACHINE.v CONVERTOR.pla CONVERTOR_CKT.v TOP.vVhdl文件夹:ALARM_BLOCK.vhd ALARM_BLOCK.vhd ALARM_SM.vhdALARM_STATE_MACHINE.vhd COMPARATOR.vhdHOURS_FILTER.vhd MUX.vhd TIME_BLOCK.vhdTIME_COUNTER.vhdTIME_STATE_MACHINE.vhd CONVERTOR.pla CONVERTOR_CKT.vhd TOP.vhd设置path参数将 Synopsys_installroot/arch/syn/bin加到.cshrc文件中。

DC综合操作流程设置流程

总流程1:库的设置2:设计的读入3:设置环境属性(1)set_operating_conditions(2)set_wire_load_model和set_wire_load_mode(3)set load(4)set_drive或者set_driving_cell4:设计规则约束(1)set_max_transtion(2)set_max_capacitance(3)set_max_fanout5:优化约束(1)create_clock(2)set_clock_uncertainty(3)set_clock_latency(4)set_input_delay(5)set_output_delay(6)set_false_path(7)set_multicycle_path(8)set_max_delay和set_min_delay(9)set_max_area7:一些编译命令及DC的输出格式注意:1:在前端设计中一般不做hold_time的约束,hold_time的约束可以在后端修复!!!总流程:1:对库进行基本设置,如下:设置完成后应该查看.synopsys_dc.setup里面库的设置和软件application setup处的设置是否一样!DC的初始化文件.synopsys.dc.setup 需要用ls –a显示,命令:more .synopsys.dc.setup查看文件内容!2:读入设计,两种方法:read和analyze+elaborateAnalyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件中的第一个库的工作环境作为优化时使用的工作环境。

(1)set_operating_conditions:工作条件包括三方面—温度、电压以及工艺;工作条件一般分三种情况:best case, typical case, worst case图形界面:#1:先进入the symbol view of the top界面,选择top模块#2:attributes—operating environment—operating conditions命令方式:#1:可通过report_lib libraryname命令来查看,如下图查看的是slow.db 库的工作条件,则使用命令:report_lib slow,右边是report_lib fast。

DC逻辑综合使用流程

DC逻辑综合使用流程1、启动软件:新开一个terminal窗口,输入命令:design_vision,回车即可开启图形界面,进入图形界面后可通过菜单、对话框等来实现DC的功能,相关的命令操作同样可以使用。

2、指定相关库文件及路径“File > Setup”打开下图所示对话框Search_path指定了搜索路径,点击右侧按钮进入如图所示对话框点击add添加库文件所在路径。

Target_library为逻辑综合的目标库,由代工厂提供的 * .db 文件,用相似的方法添加所需库文件。

Link_library是链接库,一般和目标库相同注:“*”这一项要保留,否则链接时会出错,该项指示DC在链接时首先搜索内存中的内容。

Symble_library为指定的符号库,一般为 *.sdb 文件,与单元的库文件对应。

3、设计读入“File > Read”读入设计文件,用此方式读入时在此处不用指定顶层文件,但读入后应马上指明设计的顶层名。

通过左侧的窗口可以观察设计的层次4、链接“File > Link Design”在弹出对话框中点击“ok”即可完成链接。

其执行的相关信息可从命令框中可查看5、实例唯一化当设计中有某个子模块被多次调用时就需要进行实例唯一化,实例唯一化就是将同一个子模块的多个实例生成为多个不同的子设计的过程。

之所以要进行实例唯一化是因为DC在逻辑综合时可能使用不同的电路形式来实现同一个子模块的不同实例,从而这些实例在DC看来是不同的设计(尽管其调用的子模块代码和功能完全相同)。

实现方法:“Hierarchy > Uniquify > Hierarchy ”在弹出对话框中默认点击“ok”即可,命令框中将显示“design_vision-t> uniquify”。

若选中“instances to be renamed even if unique or assigned don’t_touch”则会强制将所调用的模块从新命名,此时命令框中显示“design_vision-t> uniquify –force”。

DC综合操作流程_设置流程

总流程1:库的设置2:设计的读入3:设置环境属性(1)set_operating_conditions(2)set_wire_load_model和set_wire_load_mode (3)set load(4)set_drive或者set_driving_cell4:设计规则约束(1)set_max_transtion(2)set_max_capacitance(3)set_max_fanout5:优化约束(1)create_clock(2)set_clock_uncertainty(3)set_clock_latency(4)set_input_delay(5)set_output_delay(6)set_false_path(7)set_multicycle_path(8)set_max_delay和set_min_delay(9)set_max_area7:一些编译命令及DC的输出格式注意:1:在前端设计中一般不做hold_time的约束,hold_time的约束可以在后端修复!!!总流程:1:对库进行基本设置,如下:设置完成后应该查看.synopsys_dc.setup里面库的设置和软件application setup处的设置是否一样!DC的初始化文件.synopsys.dc.setup需要用ls –a显示,命令:more .synopsys.dc.setup查看文件内容!2:读入设计,两种方法:read和analyze+elaborateAnalyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件3:设置环境定义:如果不指定operating_conditions,DC自动搜索link_library 中的第一个库的工作环境作为优化时使用的工作环境。

dc综合约束指令

dc综合约束指令

dc 是一个Linux和Unix系统中的逆波兰计算器命令行程序,用于进行数字计算和数学表达式求值。

dc 提供了一组指令进行数字操作、函数计算和控制流程控制等操作。

关于综合约束指令,dc 并没有直接支持该功能。

然而,可以使用 dc 提供的基本指令和计算规则构建综合约束的求解器。

综合约束指的是一组不等式和等式的集合,求解这些约束需要找到满足所有约束的变量的取值。

这通常涉及到线性规划、整数规划、非线性规划等高级优化算法。

要使用 dc 进行基本的计算和约束求解,可以使用以下指令和方法:

1.dc 提供了基本的算术操作指令,如 +、-、*、/ 等,用于

进行数字计算。

2.使用 d1 <value> 这样的指令将一个常量值压入 dc 的堆栈中。

3.使用 ? 指令打印堆栈的值。

4.利用条件和循环控制指令,如 if、else、while 等,可以实

现简单的控制流程控制。

但是,对于复杂的综合约束求解,建议使用专门的优化软件包或库,如GLPK、CVXOPT、Gurobi等,它们提供了丰富的功能和高效的算法来处理约束求解问题。

总而言之,尽管dc在基本数字计算中很有用,但对于复杂的综合约束求解,建议考虑使用更专业的优化软件或库。

DC综合操作流程_设置流程

DC综合操作流程_设置流程

一、前期筹备

1、制定DC流程

1.1、根据项目管理体系的要求,结合实际情况,制定DC流程,特别是文件的内容,保证DC流程的合规性和充分性;

1.2、确定主要责任人:DC流程的主要责任人应该是项目经理,他负责统筹协调和审批DC流程的执行,以及DC的报告审批

2、组织DC文件

2.1、设计DC文档模板:,确定DC文件的内容、结构、分类、要素等;

2.2、根据DC文档模板,准备DC文档,以及表格、图形的完善;

2.3、收集相关资料:搜集有关服务器的资料,包括存储容量、备份内容、网络性能等。

3、准备相关报告

3.1、搜集相关资料:搜集有关服务器、网络、存储的资料,分析服务器的历史情况;

3.2、准备报告:根据项目要求,根据搜集的信息,准备DC报告,详细分析DC状态,以及优化、风险管理等;

3.3、提交报告:提交内容报告,经项目经理审批后,正式实施DC流程。

二、系统实施

1、部署DC流程

1.1、确定DC系统功能:根据实际情况,确定DC系统的功能,包括存储、备份、网络、安全等;

1.2、搭建DC系统:根据DC功能,搭建DC系统,准备对各个系统的设置,如,通过网络连接,安装备份系统,设置权限等;。

DC综合操作流程_设置流程

总流程1:库的设置2:设计的读入3:设置环境属性(1)set_operating_conditions(2)set_wire_load_model和set_wire_load_mode(3)set load(4)set_drive或者set_driving_cell4:设计规则约束(1)set_max_transtion(2)set_max_capacitance(3)set_max_fanout5:优化约束(1)create_clock(2)set_clock_uncertainty(3)set_clock_latency(4)set_input_delay(5)set_output_delay(6)set_false_path(7)set_multicycle_path(8)set_max_delay和set_min_delay(9)set_max_area7:一些编译命令及DC的输出格式注意:1:在前端设计中一般不做hold_time的约束,hold_time的约束可以在后端修复!!!总流程:1:对库进行基本设置,如下:设置完成后应该查看.synopsys_dc.setup里面库的设置和软件application setup处的设置是否一样!DC的初始化文件.synopsys.dc.setup 需要用ls –a显示,命令:more .synopsys.dc.setup查看文件内容!2:读入设计,两种方法:read和analyze+elaborateAnalyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件3:设置环境定义:如果不指定operating_conditions,DC自动搜索link_library 中的第一个库的工作环境作为优化时使用的工作环境。

DC参考流程

一、工作环境的建立及仿真环境的启动:1)建立工作目录:mkdir project(建立属于自己的文件夹)2)进入工作目录:cd project(希望大家别忘了这步!要不然服务器上就太乱了)3)敲入dv即可进入DC的开发环境可以看到如下的图形界面:二、工程建立:1. 定义路径:File setup1)设置查找路径(search path):主要是为DC综合提供调用文件的路径工艺库路径分别为:/home/studentxx/Versilicon_SMIC18_v2.7/FEView_STDIO/STD/sysnopsys/home/ studentxx / Versilicon_SMIC18_v2.7/FEView_STDIO/IO/sysnopsys/home/ studentxx / Versilicon_SMIC18_v2.7/FEView_STDIO/STD/symbol/sysnopsys/home/ studentxx / Versilicon_SMIC18_v2.7/FEView_STDIO/IO/symbol/sysnopsys2)定义目标库和链接库,这两个库是用来将Verilog模型综合时所用的库文件,其中存放各种标准单元和Macro模型的综合模型,用来产生最后的综合的门级网单。

(以下省去了路径。

考虑最坏情况,因此使用ss工艺拐角)Link library 设为* smic18io_line_ss_1p62v_2p97v_125c.dbsmic18_ss_1p62v_125c.dbTarget library 设为smic18io_line_ss_1p62v_2p97v_125c.dbsmic18_ss_1p62v_125c.db3)定义符号库,用来绘制相应的模块的图形以便对系统的结构得到形象而直观的认识。

Symbol library 设为smic18io.sdb smic18.sdb。

dc使用教程

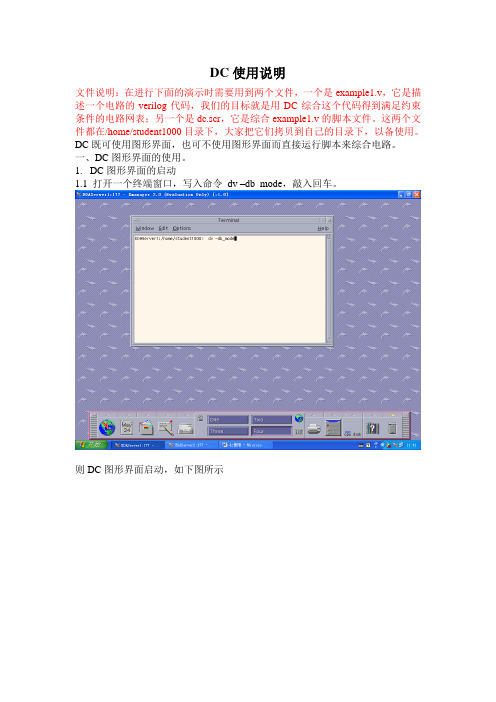

DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是example1.v,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是dc.scr,它是综合example1.v的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动1.1 打开一个终端窗口,写入命令dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help----- Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File---- Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \/tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys] set target_library { smic25_ff.db }set link_library { smic25_ff.db smic25_ss.db }set symbol_library { smic25.sdb }点OK,设置完成。

3.读入verilog文件选择File--- Read在打开文件对话框中选中要打开的文件,在这里我们选中example1.v文件。

在Log框中出现successfully字样表明读入文件成功。

DC综合全过程及使用的命令

DC综合全过程及使用的命令DC的初始化文件.synopsys.dc.setup,该文件是隐藏文件,需要用ls –a显示读取文件DC支持多种硬件描述格式,.db .v .vhd等对于dcsh工作模式来说,读取不同的文件格式需要不同的参数Read -format Verilog[db\vhdl ect] file //dcsh工作模式对于tcl工作模式来说,读取不同文件格式使用不同的命令。

Read_db file.db //tcl工作模式读取db格式Read_verilog file.v //tcl工作模式读取verilog格式Read_vhdl file.v //tcl工作模式读取vhdl格式读取源程序的另外一种方式是配合使用analyzer命令和elaborate命令;Analyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件当读取完所要综合的模块后,需要使用link命令将读到DC存储区中的模块或实体连接起来注意:如果在使用link命令后,出现unresolved design reference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录Link命令执行后,DC就将模块按照RTL级或者门级的描述将电路连接起来,之后的各种限制条件就可以对该电路的顶层模块施加DC限制条件施加的对象针对以下电路成分:输入输出端口、模块、子模块的实例化、单元电路、连线及电路的引脚。

在使用DC命令的时候,不要使用模糊的对象,例如,如下面的电路:Set_load 3 Clk由于在电路中含有名称为CLK的pin、port和net,因此,DC无法知道该处的load是施加在哪个对象上,注意到一般连线会驱动负载,该命令就改为:Set_load 3 [get_nets Clk] TCL modeSet_load 3 find(net,”Clk”)dc_shell mode路径的划分与合法路径DC综合的时候是基于路径的优化,对于DC来说,合法的路径必须满足以下条件路径的起点为输入端口或者是触发器的数据端路径终点为输出端口或者是触发器的时钟端DC设定的限制条件的值都是无单位的,这些单位都是由工艺库中给定的可以用report_lib lib_name来查看所有在工艺库中设定的各个参数的单位定义电路的工作环境和综合环境1.Set_operating_conditions不同的工作环境对应的单元电路的延迟不相同温度升高、电压降低、电路的特征线宽增大都会使得单元电路的延迟增大电路的工作环境一般在工艺库中都有给定命令格式:set_operating_conditions [–min min_condition] [–max max_condition] [-min_library min_lib] [–max_library max_lib]命令使用说明指定DC进行优化时使用的工作环境,其中工作环境的指定必须在库中指定,或者在link_library中的其中一个库中指定,如果不指定operating_conditions,DC自动搜索link_library中的第一个库的工作环境作为优化时使用的工作环境可以用get_attributes语句取得库中缺省的工作环境-max选项指定电路最大延迟分析(分析电路是否满足触发器建立时间set up的要求)的工作环境-min选项用于指定电路最小延迟分析(分析电路是否满足触发器保持时间hold time的要求)的工作环境,该选项不能单独使用,必须与-max同时使用如果不指定用于分析最小延迟的库,则只使用-max中指定的库用于电路的延迟分析-min_library选项指定用于电路最大延迟分析的工艺库-max_library选项指定用于电路最小延迟分析的工艺库2.set_min_libraryVendor可能提供多个不同的工艺库,用于分析电路的时序,不同工艺库定义了不同的工作环境、不同的线负载模型、不同的单元延迟时间,这是可以将这些苦都指定用于分析电路的延迟命令格式:set_min_library max_library –min_version min_library | -none命令的使用说明:该命令指定max_library用于分析电路的最大延迟,min_library用于分析电路的最小延迟。

DC综合全过程及使用的命令

DC综合全过程及使用的命令DC(Direct Current,直流)综合全过程是一个用于仿真电路和系统的软件工具。

它允许用户分析和设计包含电源电压、电阻、电容和电感等元件的电路。

DC的命令形式为命令行输入,命令行通常包含两个部分:命令和选项。

命令用于指定要执行的操作,而选项通常用于自定义和细化命令。

以下是DC综合全过程的使用的命令:1. help:显示DC的所有命令和选项的列表。

示例:help2. source:指定要仿真的电路文件。

示例:source example.cir3. op:执行直流分析操作,计算电路的直流状态。

示例:op4. tran:执行时间域分析操作,模拟电路随时间变化的行为。

示例:tran 0.1ms 10ms5. print:打印指定的节点或变量的值。

示例:print V(1)6. plot:绘制指定的波形图。

示例:plot V(1)7. temp:设置电路中的温度。

示例:temp 258. model:指定电子元件的模型。

示例:model res 1 109. option:设置DC综合全过程的选项。

示例:option reltol=0.00110. save:保存当前仿真结果。

示例:save example.out11. quit:退出DC综合全过程。

示例:quit以上命令只是DC综合全过程中的一部分,还有许多其他命令和选项可供使用。

用户可以根据自己的需求来选择和使用这些命令。

1.准备电路文件:用户需要创建一个文本文件,其中包含要仿真的电路的描述。

该文件应按照DC综合全过程的语法规则编写。

2. 指定源文件:在DC综合全过程中使用source命令指定要仿真的电路文件。

3. 执行直流分析:使用op命令执行直流分析操作,计算电路的直流状态。

4. 执行时间域分析:使用tran命令执行时间域分析操作,模拟电路随时间变化的行为。

5. 打印和绘制结果:使用print命令打印指定的节点或变量的值,使用plot命令绘制指定的波形图。

DC综合操作流程_设置流程.

总流程1:库的设置2:设计的读入3:设置环境属性(1)set_operating_conditions(2)set_wire_load_model和set_wire_load_mode(3)set load(4)set_drive或者set_driving_cell4:设计规则约束(1)set_max_transtion(2)set_max_capacitance(3)set_max_fanout5:优化约束(1)create_clock(2)set_clock_uncertainty(3)set_clock_latency(4)set_input_delay(5)set_output_delay(6)set_false_path(7)set_multicycle_path(8)set_max_delay和set_min_delay(9)set_max_area7:一些编译命令及DC的输出格式注意:1:在前端设计中一般不做hold_time的约束,hold_time的约束可以在后端修复!!!总流程:1:对库进行基本设置,如下:设置完成后应该查看.synopsys_dc.setup里面库的设置和软件application setup处的设置是否一样!DC的初始化文件.synopsys.dc.setup 需要用ls –a显示,命令:more .synopsys.dc.setup查看文件内容!2:读入设计,两种方法:read和analyze+elaborateAnalyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件中的第一个库的工作环境作为优化时使用的工作环境。

(1)set_operating_conditions:工作条件包括三方面—温度、电压以及工艺;工作条件一般分三种情况:best case, typical case, worst case图形界面:#1:先进入the symbol view of the top界面,选择top模块#2:attributes—operating environment—operating conditions命令方式:#1:可通过report_lib libraryname命令来查看,如下图查看的是slow.db 库的工作条件,则使用命令:report_lib slow,右边是report_lib fast。

DC详细命令

Design Compiler FAQPart1 DC Basics1.1 什么是DC?DC(Design Compiler)是Synopsys的逻辑综合优化工具,它根据设计描述和约束条件自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高读者设计性能。

1.2 DC能接受多少种输入格式?支持.db, .v, .vhd , edif等等。

1.3 DC提供多少种输出格式?1.4 DC的主要功能或者主要作用是什么?DC是把HDL描述的电路综合为跟工艺相关的、门级电路。

并且根据用户的设计要求,在时序和面积,时序和功耗上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证1.5 如何寻找帮助?帮助可以分为3种求助方式:1.使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档?SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令 which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,即重要参数:工艺库,目标库,标志库等等。

要在.synopsys_dc.setup上设置好这些参数。

而.synopsys_dc.setup要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

由后一个设置覆盖前一个文件。

参数包括:search_path, target_library, link_library, symbol_library1.8 target_library 是指什么?target_library是综合是在map时需要的实际的工艺库1.9 link_library如何指定?链接时需要的库,通常与library相同,设置时,需要加“*”,表示内存中的所有库。

DC综合流程

综合步骤8:分析修改设计

通常Design Compiler根据设计综合和优化的结果生成众多的报告。根据诸如面积、 约束和时序报告来分析和解决任何设计问题,或者改进综合结果。

需要的报告: report_design:报告用户的综合环境,包括operating condition、wire load report_constraint:用户定义的constraint report_timing -nworts num :所有路径中最差的路径。

DC综合流程

提纲

• 综合概述

• 技术库概述

• 综合基本步骤

综合概念

● 逻辑综合:决定设计电路逻辑门的相互连接。

● 逻辑综合的目的:决定电路门级结构、寻求时序和与面积的平衡、寻求功 耗与时序的平衡、增强电路的测试性。

● 逻辑综合的过程:Translation 、map 、optimization Translation是指把设计的HDL描述转化为GTECH库元件组成的逻辑电路

综合步骤4:design environment

1、operating condition

operating condition包括工作温度、工作电压、制造工艺,通过命令 set_operating_condition来设定

命令set_operating_conditions –min BEST –max WORST用于指示DC对WORST 和BEST条件,同时优化。WORST用于对setup-time进行优化,BEST用于对holdtime进行优化,当BEST和WORST都满足时,TYPICAL也就可以满足。

综合步骤7:优化设计

使用dc进行逻辑综合的基本步骤

使用dc进行逻辑综合的基本步骤该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

该使用dc进行逻辑综合的基本步骤该文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注。

文档下载说明Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document 使用dc进行逻辑综合的基本步骤can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!DC综合是数字电路设计过程中非常重要的一步,它将逻辑功能描述转换为对应的门级电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DC综合全过程及使用的命令DC的初始化文件.synopsys.dc.setup,该文件是隐藏文件,需要用ls –a显示读取文件DC支持多种硬件描述格式,.db .v .vhd等对于dcsh工作模式来说,读取不同的文件格式需要不同的参数Read -format Verilog[db\vhdl ect] file //dcsh工作模式对于tcl工作模式来说,读取不同文件格式使用不同的命令。

Read_db file.db //tcl工作模式读取db格式Read_verilog file.v //tcl工作模式读取verilog格式Read_vhdl file.v //tcl工作模式读取vhdl格式读取源程序的另外一种方式是配合使用analyzer命令和elaborate命令;Analyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件当读取完所要综合的模块后,需要使用link命令将读到DC存储区中的模块或实体连接起来注意:如果在使用link命令后,出现unresolved design reference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录Link命令执行后,DC就将模块按照RTL级或者门级的描述将电路连接起来,之后的各种限制条件就可以对该电路的顶层模块施加DC限制条件施加的对象针对以下电路成分:输入输出端口、模块、子模块的实例化、单元电路、连线及电路的引脚。

在使用DC命令的时候,不要使用模糊的对象,例如,如下面的电路:Set_load 3 Clk由于在电路中含有名称为CLK的pin、port和net,因此,DC无法知道该处的load是施加在哪个对象上,注意到一般连线会驱动负载,该命令就改为:Set_load 3 [get_nets Clk] TCL modeSet_load 3 find(net,”Clk”)dc_shell mode路径的划分与合法路径DC综合的时候是基于路径的优化,对于DC来说,合法的路径必须满足以下条件路径的起点为输入端口或者是触发器的数据端路径终点为输出端口或者是触发器的时钟端DC设定的限制条件的值都是无单位的,这些单位都是由工艺库中给定的可以用report_lib lib_name来查看所有在工艺库中设定的各个参数的单位定义电路的工作环境和综合环境1.Set_operating_conditions不同的工作环境对应的单元电路的延迟不相同温度升高、电压降低、电路的特征线宽增大都会使得单元电路的延迟增大电路的工作环境一般在工艺库中都有给定命令格式:set_operating_conditions [–min min_condition] [–max max_condition] [-min_library min_lib] [–max_library max_lib]命令使用说明指定DC进行优化时使用的工作环境,其中工作环境的指定必须在库中指定,或者在link_library中的其中一个库中指定,如果不指定operating_conditions,DC自动搜索link_library中的第一个库的工作环境作为优化时使用的工作环境可以用get_attributes语句取得库中缺省的工作环境-max选项指定电路最大延迟分析(分析电路是否满足触发器建立时间set up的要求)的工作环境-min选项用于指定电路最小延迟分析(分析电路是否满足触发器保持时间hold time的要求)的工作环境,该选项不能单独使用,必须与-max同时使用如果不指定用于分析最小延迟的库,则只使用-max中指定的库用于电路的延迟分析-min_library选项指定用于电路最大延迟分析的工艺库-max_library选项指定用于电路最小延迟分析的工艺库2.set_min_libraryVendor可能提供多个不同的工艺库,用于分析电路的时序,不同工艺库定义了不同的工作环境、不同的线负载模型、不同的单元延迟时间,这是可以将这些苦都指定用于分析电路的延迟命令格式:set_min_library max_library –min_version min_library | -none命令的使用说明:该命令指定max_library用于分析电路的最大延迟,min_library用于分析电路的最小延迟。

当DC需要计算路径的最小延迟时,首先在max_library中找到单元电路,如果在min_library中有和该单元电路有相同名称、相同的引脚名、相同的时序弧时,则使用min_library中给出的时序信息用于计算电路中路径的延迟使用-none选项可以取消设定min_library不要在target library中设置min_library对应的库该命令只有当vendor提供两个库时才使用3.set_wire_load_model在DC计算路径的延迟时,工具会估计连线的延迟,该命令是设置一个连线延迟估计的模型。

但是在综合完成后,用report_timing –nets一般看到的连线延迟都是0,这是因为在做综合之前,工具使用的线负载模型是比较粗糙的,所以连线延迟比较小。

另外,不仅互连线本身有延迟,互连线的寄生电容、寄生电阻会影响到单元电路的延迟注意:在深亚微米、超级亚微米阶段互连线的延迟在整个路径的延迟中占一半左右。

因此,现在一般在综合之前会做一次floorplan,然后提取出线负载模型来供综合工具使用,以便更加准确的估计连线延迟。

Synopsys的另外一个工具physical compiler 就可以将floorplan跟综合放在一起做命令的格式为:set_wire_load_model –name model_name –lib_name library –max –min设置综合时使用的线负载模型,用于估计电路的连线延迟。

由于布线之前没有准确的电路走线。

因此,即使设置该模型,也不能准确估计电路的互连线延迟。

如果没有wire_load_model,可以将auto_wire_load_selection参数设置为true,则DC自动根据综合之后的面积来选择一个统计的线负载模型用于估计连线延迟Set auto_wire_load_selection true-max –min选项同上,分别指定该模型用于估计最大路径延迟和最小路径延迟。

-lib_name指定包含该线负载模型的工艺库一个线负载模型的例子:1: Name : 320KGATES 模块名称,用于引用该模块2: Location : ssc_core_slow 该模块库的位置3: Resistance : 0.000271 单位长度的连线电阻4: Capacitance : 0.00017 单位长度的连线电容5: Area : 0 连线所占面积6: Slope : 55.6653 外推计算连线长度的斜率7: Fanout Length Points Average Cap Std Deviation8: --------------------------------------------------------------9: 1 34.79 按照连线的扇出估计连线长度,从而估计连线延迟10: 2 90.4611: 3 146.1212: 4 201.7913: 5 257.45set_wire_load_mode如果只是在子模块综合中设置了线负载模型,那么跨模块边界的连线延迟如何估计,该命令就是用于设置模块互连线延迟估计所使用的模块该模式有三种选择:Top 指定模块互连线延迟的估计使用顶层模块的线负载模型Enclosed 指定模块互连线延迟的估计使用包含该连线的最小模块的线负载模型Segmented 将连线按模型边界分段,各段的延迟分别按照各自模块的线负载模型估计延迟,然后把估计结果相加得到该连线的延迟命令的格式为:set_wire_load_mode mode其中mode 为top、enclosed、segmented4.set_drive为了更加准确的估计输入电路的延迟,DC需要知道信号到达输入端口的过渡时间(transition time)。

Set_drive使用确定的值来估计输入端的输入电阻,从而得到输入端口的延迟;而set_driving_cell是假定一个实际的外部驱动单元来估计输入的transition time该命令用于设置输入端口或者双向端口上的电阻值,该电阻值是用于驱动输入端口的单元的输入电阻,因此,该值越大,就说明输入端口的驱动能力越弱,连线的延迟也就越大。

更常用的是set_driving_cell命令,以库中某个单元电路的引脚驱动能力为基准来模拟输入端口的驱动能力。

命令的格式:set_drive resistance_value –max –min –rise –fall命令使用要点缺省情况下,该值为0,即输入具有无限大的驱动能力电路的优化阶段,输入端口的驱动能力用于计算输入端口到门电路延迟,一般来说,输入端口的驱动能力可以按照以下公式影响延迟Time = arrive_time + drive*net_load + connect_delay5.set_driving_cell该命令实现的功能和set_drive命令基本相同,set_driving_cell是指定使用库中某一个单元来驱动输入端口。

该命令是在输入端口之前假想一个驱动单元,然后按照该单元的输出电阻来计算transition time,从而计算输入端口到门单元电路的延迟,如:set_driving_cell –lib_cell buf1a3 –pin Y Reset即设置Reset端口的驱动能力与单元bufla3的Y引脚驱动能力相同用set_driving_cell命令后,会出现很多警告,因为加上driving_cell约束之后,相当于人为的给很多引脚加上设计规则的限制条件6.set_load由于外部电路的负载将会影响到接到端口上单元电路的延迟,因此需要对端口的带负载能力做限制。

为了比较精确地计算输出电路的延迟,DC需要知道输出电路驱动的所有负载。

命令的格式:set_load load_of(ssc_core_slow/buf1a2/A) [all_outputs]即使用ssc_core_slow库中bufla2单元A引脚的电容负载来计算所有输出端口延迟。