ADM8839中文资料

ADN8830中文资料

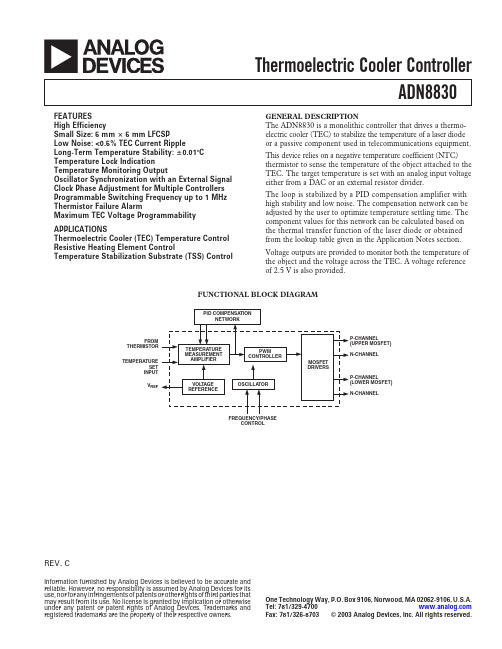

The ADN8830 is a monolithic controller that drives a thermoelectric cooler (TEC) to stabilize the temperature of a laser diode or a passive component used in telecommunications equipment. This device relies re coefficient (NTC) thermistor to sense the temperature of the object attached to the TEC. The target temperature is set with an analog input voltage either from a DAC or an external resistor divider. The loop is stabilized by a PID compensation amplifier with high stability and low noise. The compensation network can be adjusted by the user to optimize temperature settling time. The component values for this network can be calculated based on the thermal transfer function of the laser diode or obtained from the lookup table given in the Application Notes section. Voltage outputs are provided to monitor both the temperature of the object and the voltage across the TEC. A voltage reference of 2.5 V is also provided.

美军标883的对应国内标准-概述说明以及解释

美军标883的对应国内标准-概述说明以及解释1.引言1.1 概述概述部分的内容可以包括以下几个方面:引言部分主要是对该篇文章的背景和意义进行简要介绍,可以提及以下内容:- 美军标883,也即美国军方的标准MIL-STD-883,是一份关于电子元器件可靠性测试方法的标准。

这份标准对于确保电子元器件的可靠性和性能至关重要,不仅在军事领域具有重要意义,也在民用领域有广泛应用。

- 近年来,我国的电子元器件产业迅速发展,国内对于电子元器件的测试与认证标准也日益重要。

为了满足国内市场对高质量电子元器件的需求,有必要对照美军标883制定国内对应的标准,以确保产品的质量与性能。

- 本文将对比分析美军标883与国内对应标准的内容和要求,探讨其差异与相似之处,并对其对国内电子元器件产业的影响与建议进行讨论。

通过对这两个标准的比较,可以为我国电子元器件产业的发展提供一定的借鉴和指导。

引言部分的概述应该简洁明了,能够准确介绍该文章的主题和研究方法,同时能够激发读者的兴趣,引导读者进一步阅读后续内容。

1.2文章结构文章结构部分的内容可以包括以下内容:文章结构部分的主要目的是介绍本文的组织结构和各个章节的内容,以便读者能够更好地理解和阅读文章。

本文分为引言、正文和结论三个部分。

第一部分是引言部分。

在引言部分,首先要对文章的主题进行概述,简要介绍美军标883以及国内对应的标准的背景和重要性。

其次,说明文章结构,即介绍各个章节的内容和安排。

最后,阐明本文的目的,即通过对比分析美军标883和国内对应标准的内容,探讨其差异和影响,并给出相关建议。

第二部分是正文部分。

在正文部分,首先要详细介绍美军标883的内容,包括其主要内容和要求。

可以列举一些关键点和具体规定,以帮助读者更好地理解。

然后,介绍国内对应的标准,包括其起草背景、内容和适用范围等方面。

可以结合实际案例和数据进行说明,以论证国内对应标准的有效性和实用性。

第三部分是结论部分。

J1939中文资料3

(SAE1939-15:2003 MOD )国家标准化管理委员会ICSGB/T XXXX.3-XXXX商用车控制系统局域网络(CAN )通信协议第3分:物理层—非屏蔽双绞线(250K 比特/秒)(征求意见稿)20xx-xx-xx 发布20xx-xx-xx 实施GB/T XXXX.3-XXXX前言GB/T××××《商用车控制系统局域网络(CAN 总线)通信协议》包括10个部分:—第1部分:物理层—屏蔽双绞线(250K比特/秒)—第2部分:物理层—非车载诊断连接器—第3部分:物理层—非屏蔽双绞线(250K比特/秒)—第4部分:数据链路层—第5部分:应用层—车辆—第6部分:应用层—诊断—第7部分:网络管理—第8部分:参数组分配—第9部分:地址和标识分配—第10部分:可疑参数编号(SPN)—第11部分:网络层本部分为GB/T××××的第3部分,对应于SAE 1939-15:2003《物理层,非屏蔽双绞线》,本部分与SAE1939-15的一致性程度为修改采用(技术内容完全等同),主要差异如下:—按1.1规定增加了”前言”、“范围”。

—进行了编辑性修改。

本部分由全国汽车标准化技术委员会提出。

本部分由全国汽车标准化技术委员会归口。

本部分由负责起草。

本部分主要起草人:GB/T XXXX.3-XXXX 汽车控制系统局域网络(CAN 总线)通信协议第3部分:物理层—非屏蔽双绞线(250千比特/秒)1 范围本部分规定了CAN 总线的物理层—非屏蔽双绞线(250K比特/秒)的电气性能参数等。

本部分适用于M2、M3、N及L类车辆,其他车辆可参考。

2 规范性引用文件下列文件中的条款通过本部分的引用而成为本部分的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本部分,然而鼓励根据本部分达成协议的各方研究是否可使用这些文件的最新版本。

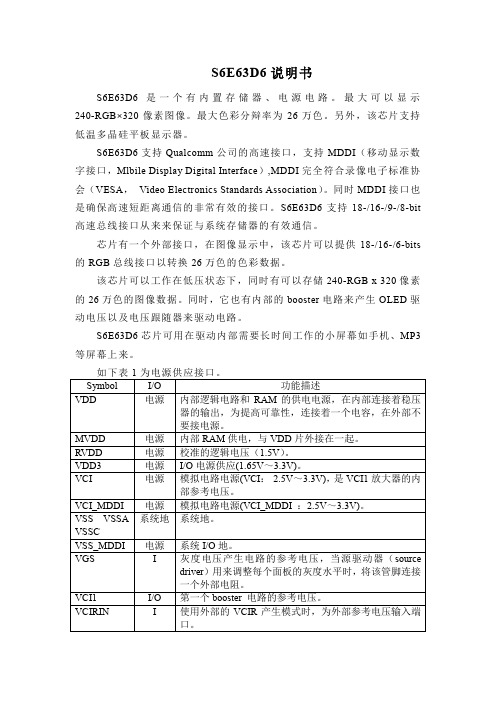

三星AMOLED驱动芯片中文版说明书

表 5 所示为其他端口。 Symbol I/O 功能描述 DUMMYR[3:1] 电阻测量管脚,正常情况下悬空。 DUMMYL[3:1] DUMMY 无用管脚,悬空即可。 V0/V63 O 伽玛电压镜像管脚。 VDD3DUM O 内部与 VDD3 接在一起。

VSSDUM FUSE_EN RTEST EN_EXCLK EN_CLK TEST_MODE[1:0] TEST_IN[6:0] TE TEST_OUT[2:0]

表 2 系统接口

表3为 Symbol MDP MDN MSP MSN GPIO[9:0] (DB[17:8]) S_CSB(DB [7])

MDDI 管脚作用。 I/O 功能描述 I/O MDDI 数据输入/输出正端,如果 MDDI 不用,该端口悬空。 I/O MDDI 数据输入/输出负端,如果 MDDI 不用,该端口悬空。 I MDDI 数据选通输入正端,如果 MDDI 不用,该端口悬空。 I MDDI 数据选通输入负端,如果 MDDI 不用,该端口悬空。 I/O 总体输入输出,如果在 MDDI 中没有用 GPIO 的话,这些管 脚应该置地。 O 子屏幕驱动 IC 片选信号。 低电平时说明子屏幕驱动 IC 可用,高电平时说明子屏幕驱动

表 1 电源接口

如表 2 所示为系统接口。 Symbol I/O 功能描述 S_PB I 选择 CPU 接口模式,低电平时为并行接口,高电平时为串行 接口。 MDDI_E I 选择 MDDI 接口,低电平时 MDDI 接口不可用,高电平时 N MDDI 接口可用。 ID_MIB I 选择 CPU 种类, 低电平为 intel 80 系列 CPU, 高电平为 motorola 68 系列 CPU,如果 S_PB 是高电平,该端口为 ID 设置端口。 CSB I 片选信号,低电平芯片可用,高电平芯片不可用。 RS I 寄存器选择管脚。 低电平时,指令/状态,高电平时为指令参数/RAM 数据。 不用时需与 VDD3 接在一起。 RW_WR I 管脚作用 CPU 种类 管脚说明 B/SCL RW 68 系列 读写选择,低电平写,高电平读。 WRB 80 系列 写选通作用,在上升沿捕获数据。 SCL 串行接口 时钟同步信号。 E_RDB I 管脚作用 CPU 种类 管脚说明 E 68 系列 读写操作使能端。 RDB 80 系列 读选通作用,低电平时读出数据。 选择串行模式时,将此端口接在 VDD3 上。 SDI I 串行接口的数据输入接口,在 SCL 上升沿捕捉到输入数据,

Cavium_OCTEON31xx30xx_Chinese_v16

Cavium Networks Contact: Cavium NetworksAngel Atondo 805 East Middlefield RoadTel: (650) 623-7033 Mountain View, CA 94043 Email: angel.atondo@ Phone: (650) 623-7000Cavium Networks 发布业界最全的基于单核与双核 MIPS64®面向下一代智能网络的 OCTEON™ 处理器新的 OCTEON SOC 处理器为网络、无线、控制和存储应用提供处理器为网络、无线、控制和存储应用提供了了高度集成高度集成和和有成本效益有成本效益的的 64 位计算的解决方案2006 年 1 月 30 日,美国加州日,美国加州山景城山景城 —— 安全、网络服务和嵌入式处理器解决方案的世界领导者 Cavium Networks 今天发布 10 款新的价格从 $20 以下开始基于单核和双核 MIPS64 高度集成的处理器。

为了突破下一代网络、无线、控制和存储应用对特性、性价比和功耗的需求,新的 SOC (System on Chip )集成了定制的 MIPS64 处理器和业界最先进的多层应用(multi-layer applications )加速和安全处理硬件,以及丰富的可配置的网络接口。

新的 OCTEON CN31XX 和 CN30XX 系列处理器与目前市场上领先的多核处理器家族 CN38XX 系列保持软件兼容。

OCTEON 产品家族目前提供从单核到 16 核的业界最具可扩展性和兼容的 MIPS64 处理器产品线,这样 OEM 厂商可以使用同一套通用的软件开发不同性能和价格点的设备,大量的降低了开发成本和缩短了产品面市时间。

OCTEON 处理器被广泛的设计进了各种网络设备,包括路由器、交换机、统一威胁管理(UTM ,Unified Threat Management )设备、应用认知(Application-aware )网关、三网合一(Triple-play )网关、无线局域网(WLAN )、3G 接入和聚合设备以及网络存储设备等。

华硕主板

数字家庭主板M2NDH-支持AMD®SocketAM2Athlon64FX/Athlo64X2/Athlon64/Sempron -AMDLive!™Ready-强大扩充能力:1xPCI-Ex16、2xPCI-E、3xPCI-华硕WiFi-APSolo-华硕DHRemote™-华硕MP3-In™-华硕Q-Connector-高保真音频中央处理器支持AMD®SocketAM2Athlon64FX/Athlo64X2/Athlon64/Sempron 支持AMDCool'n'Quiet™技术AMD64架构,同时兼容32位和64位计算AMDLive!™Ready芯片组NVIDIAnForce®430MCP前端总线2000/1600MT/s内存双通道内存架构4x240-pinDIMM内存插槽,支持最大容量高达8GB的DDR2800/667/533ECC和non-ECC、un-buffered内存扩充插槽1xPCI-Expressx16插槽2xPCI-Expressx1插槽3xPCI2.2插槽存储装置/RAID-1xUltraDMA133/100/66/33-4xSerialATA3.0Gb/s-NVIDIAMediaShield™RAID通过SerialA TA设备支持RAID0、1、0+1、5和JBOD网络功能NVIDIAnForce®430内建GigabitMAC,支持externalAttansicPHY无线局域网:54MbpsIEEE802.11b/g(华硕WiFi-APSolo)音频功能ADI6声道高保真音频CODEC背板S/PDIF数字音频输出USB高达8个USB2.0/1.1接口M2N-VMDH-AMDSocketAM2-NVIDIAGeForce6100/nForce430-双通道DDR2800/667/533-1xPCIExpressx16+1xPCIExpressx1+2xPCI-双VGA:DVI-D和D-Sub-8声道高保真音频-2x1394a接口中央处理器支持AMD®SocketAM2Athlon64X2/Athlon64FX/Athlon64/Sempro nAMDCool'n'Quiet™技术AMD64架构,兼容32位和64位计算AMDLive!™Ready芯片组NVIDIAGeForce6100/nForce430前端总线2000/1600MT/s 内存双通道内存架构4x240-pinDIMM插槽,支持最大容量为8GB的DDR2800/667/533non-ECC,un-buffered内存显卡集成GeForce6100GPU高清晰视频处理,最高分辨率可达1920x1440(@75Hz)支持RGB显示;UXGA1600x1200(@60Hz)支持DVI-D显示支持双VGA输出:DVI-D和RGB注意:DVI-D不能用来输出RGB信号至CRT。

adm芯片

adm芯片ADM芯片是一种数字集成电路,可用于各种应用领域。

ADM 芯片的全称为Analog Devices(ADI)的高精度模拟数字转换器(ADC)与数字模拟转换器(DAC)芯片。

ADM芯片主要由模拟部分和数字部分组成,能够将模拟信号转换为数字信号或将数字信号转换为模拟信号。

ADM芯片采用高精度的模拟电路和先进的数字技术,具有高速、高精度和低功耗等特点。

它可以处理各种类型的信号,如声音、图像和传感器信号等。

ADM芯片的广泛应用包括通信设备、工业自动化、医疗器械、汽车电子等领域。

ADM芯片的核心技术是模拟数字转换器(ADC)和数字模拟转换器(DAC)。

ADC能够将模拟信号转换为数字信号,DAC能够将数字信号转换为模拟信号。

ADM芯片的ADC和DAC具有高分辨率、高采样率和低失真等优点,可以实现高质量的信号转换。

ADM芯片还集成了数字信号处理器(DSP),可以对数字信号进行复杂的算法处理。

DSP可以实现滤波、解调、编解码等功能,提高了ADM芯片的灵活性和性能。

ADM芯片的设计和制造需要专业的技术和设备。

ADI是一家拥有多年经验和先进工艺的半导体公司,可以提供高质量的ADM芯片和解决方案。

对于使用ADM芯片的应用,开发人员需要了解其性能参数和接口规范。

ADM芯片的性能参数包括分辨率、采样率、信噪比和动态范围等,接口规范包括电源电压、通信协议和引脚定义等。

总之,ADM芯片是一种功能强大、性能优异的数字集成电路,广泛应用于各种领域。

它能够实现模拟信号与数字信号的转换,并具有高速、高精度和低功耗等特点。

ADM芯片的设计和制造需要专业的技术和设备,开发人员需要了解其性能参数和接口规范。

有了ADM芯片的支持,各种应用系统可以实现更高的功能和性能。

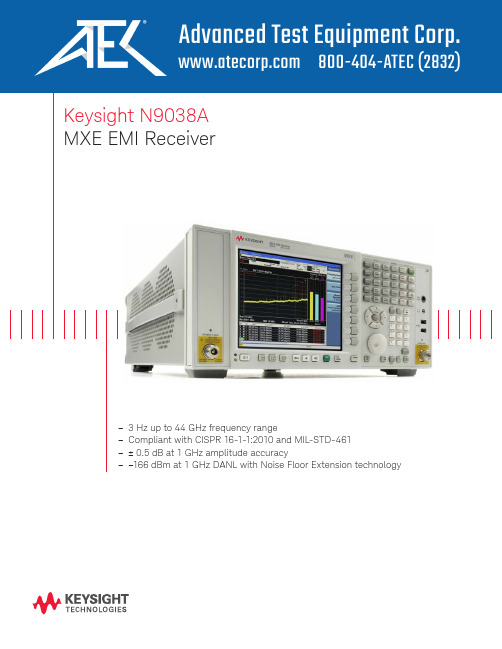

Keysight N9038A MXE EMI接收器产品简介说明书

Keysight N9038AMXE EMI Receiver–3 Hz up to 44 GHz frequency range–Compliant with CISPR 16-1-1:2010 and MIL-STD-461–± 0.5 dB at 1 GHz amplitude accuracySummary of Key SpecificationsThe X-Series difference Future-readyOptimize your investment and extend instrument longevity with upgradeable processor, memory, connectivity, and more to keep your test assets current today and tomorrow.Consistent measurement frameworkAchieve measurement integrity across your organization and drive more productivity in less time by leveraging a proven foundation for signal analysis and identical operation across the X-Series instruments.Broadest set of applicationsAddress the changing demands of technology with additionalmeasurement applications, the ability to run software inside the openWindows operating system, and a first-to-market track record in emerging standards.Stay ready, stay in sync, and arrive ahead —with the Keysight X-Series./find/X-SeriesKeep the Test Queue FlowingIn EMC testing, success depends on tools that can help you do more in less time—today and tomorrow. That’s why we created the MXE: it’s a standards-compliant EMI receiver and diagnostic signal analyzer built on an upgradeable platform. In the lab and on the bench, it provides the accuracy, repeatability,and reliability you need to test with confidence.The MXE makes it easy to test in accordance with CISPR 16-1-1:2010 and MIL-STD-461. Choose the frequency coverage you need—up to 3.6, 8.4, 26.5, or44 GHz—and fully test devices with outstanding accuracy and excellent sensitivity across the required ranges.Through the front panel or remotely with software, you can evaluate emissions and identify suspect signals using EMC measurements and a variety of intuitive displays. The extensive set of built-in analysis tools helps you diagnose the causes of noncompliant emissions.With all these capabilities and more, the MXE enables you and your team to keep the test queue flowing.Extend instrument longevity with easy upgradabilityTo keep your instrument current and extend its longevity, the MXE offers easy upgradability of hardware and software capabilities. For example, you can enhance platform performance through CPU and memory upgrades, and add functionality with a simple license key.Leverage the proven reliability of a mature hardware platform Uptime is essential in a test lab and that’s why we built the MXE on the robust Keysight X-Series signal analyzer platform. In addition, the MXE carries the benefits of Keysight’s standard three-year warranty and responsive service and support team.The MXE is ideally suited for high-performance EMC testing in commercial and military applications. The instrument offers a range of CISPR- and MIL-STD-compliant capabilities—detectors, bandwidths, and more—as well as features that further enhance the accuracy and throughput of EMC testing and data analysis.Simplify setupThe MXE contains a number of features that simplify the setup process for compliance measurements. For example, you can use setup tables to create specific measurement configurations for a variety of frequency ranges and antennas. You can also reduce overall setup time by saving and recallingfrequently used custom instrument settings. In addition, the MXE can remotely control switching functions in external LISNs.To accelerate identification of suspect emissions, access the built-in library of limit lines and activate the relevant regulatory limits. You can also define custom limit lines with the easy-to-use editor. To ensure appropriate limit testing, the MXE can automatically correct measured amplitudes for specific transducers, antennas, cabling, and external preamplifiers using customer-configured amplitude correction files.Accelerate data collectionThe MXE is designed to help you see signal activity—quickly and easily—from multiple perspectives. The comprehensive user display allows you to see both a broad overview of the emissions environment and a detailed view of the signal amplitude at a single frequency.Easily capture emissions data using built-in automated scan, search, and measure functions that mirror recommended commercial and military testing procedures. The multi-trace and max hold capabilities let you view emissions from the current position of the device under test (DUT) along with themaximum emissions from all DUT positions. During monitoring, the three color-coded detectors are updated simultaneously to ensure accurate results.The MXE receiver display provides a simplified view into the emissions performance of the DUT.Maximize Throughput in Compliance TestingChoose from traditional frequency or rapid time domain scanning.Easily identify suspect signalsWith built-in measurement and analysis functions, the MXE makes it easy to identify suspect emissions. For example, the unique color-coded trace display capability clearly identifies signals that exceed the selected limit lines and margins.When creating suspect lists, you can choose between traditional frequency scanning and rapid time domain scanning. Time domain scans significantly reduce the time needed to create a list of suspect emissions prior to making final measurements.Built-in limit testing makes it easy to create emission suspect lists. The receiver can automatically move out-of-limit signals to the signal list, where you can perform measurements with the touch of a button.Simplify final measurementsThe list function in the MXE makes it easy to perform final emissionsmeasurements for all supported standards. When you need to control tower or turntable position, internal frequency lists can be passed to automationsoftware. When orientation optimization isn’t required, built-in capabilities help you complete final measurements with ease.When final measurements are complete, you can conveniently create reports in HTML or PDF format with customized content that includes amplitude corrections, limits, scan tables, trace data, signal lists, and screen shots.All-digital IF architectureA digital intermediate frequency (IF) receiver architecture improvesmeasurement accuracy. By comparison, an analog IF architecture implements gain blocks, log amps, resolution bandwidths, and detectors with analog hardware. Even the best of these designs exhibit performance differences when receiver settings are changed from the settings used for calibration. These differences are then exacerbated over temperature.The all-digital IF architectureincludes digital realizations of the key components, which operate on the signal after it has been digitized. Digital IF can improve EMC measurement throughput by minimizing the need for users to bring the signal being measured to the top of the reference level. Analog receivers require this step for every measurement to minimize the effects of analog hardware errors.In addition, digital IF architecturereduces the occurrence of IF overload, even if signals are above the reference level.As an EMI receiver and diagnostic signal analyzer, the MXE puts a wealth of capabilities at yourfingertips. New receiver technology reduces measurement time and ensures you are prepared for future requirements.Go faster with time domain scanningThe MXE offers three types offrequency scanning: swept, stepped, and time domain. Time domain scan decreases total test time by reducing overall prescan collection times when longer measurement dwell times are required.Time domain scan speedsmeasurements by using high-overlap fast Fourier transforms (FFTs) tocollect emissions data simultaneously over an acquisition bandwidth that is multiple resolution bandwidths wide. This is in contrast to frequency-domain measurements, whichcollect data in individual resolution bandwidths.With time domain testing, you can collect suspect lists rapidly, greatly improving overall test time and throughput.Automate click measurementsUse the MXE's built-in disturbance analyzer to easily make discontinuous disturbance, or click, measurements as specified in CISPR 14-1. Simplify and automate data collection, analysis, and report generation for these commonly tested emissions for more efficient testing.Enhance Your Lab with the Latest CapabilitiesComparison of resolution and FFT acquisition bandwidths.FrequencyA m p l i t u d eFFT acquisition bandwidthA m p l i t u d eFrequencyReceiver resolution bandwidthSwept or stepped frequency domain scanTime domain scanDwell for each resolution bandwidthDwell for each FFT bandwidth (multiple resolution bandwidth)Simplify and automate data collection, analysis, and report generation for click measurements.Be ready for APD measurementsThe MXE helps future-proof your lab by offering the amplitude probability distribution (APD) function that is being considered by CISPR foremissions testing of microwave ovens. To characterize slowly-varyingemissions, the APD function displays the probability of an emissionreaching or exceeding a given level. To facilitate use of this new function, the MXE also offers specific limit-line types that can be used with built-in evaluation capabilities to simplify DUT testing.Find the maximum with monitor spectrumIn EMC testing, capturing the maximum value of each emissionfrequency is crucial. Doing so enables accurate characterization of the DUT.To ensure that you have identified the frequencies of maximum emissions in your suspect list, the MXE offers a new feature called monitor spectrum. This feature offers both live-spectrum and meter displays that make it easy to see emission levels and find the maximum while adjusting the center frequency. Ultimately, monitor spectrum improves overall measurement time by reducing the time it takes to prepare your signal list for final measurements.Monitor spectrum identifies frequency of peak emissions.Be ready for future applications with the APD function.The global center frequency feature lets you easily track signals in both the receiver and spectrum analyzer.Gain Insight with Extensive Diagnostic CapabilitiesVerifying product compliance is just one facet of EMI testing. Solving emissions problems can present a wide range of challenges, and the MXE offers a number of tools that will help you see and understand what’s happening.Leverage powerful spectrum analysisInvestigate out-of-compliance emissions with the MXE’s built-in X-Series spectrum analysis capabilities, which include a rich set of resolution and video analysis bandwidths, detectors, and marker functions. In addition, the MXE includes the X-Series PowerSuite measurements for characterization of transmitted signals.Switching between receiver and spectrum analyzer modes is greatlysimplified with the global center frequency function, which links the viewed frequencies. When analyzing an emission, any modification of its frequency will be automatically updated in the MXE’s suspect list, simplifying the final measurement process.Enhance precompliance measurementsYou can leverage the power and usability of the MXE when making precompliance measurements. The Keysight EMI measurement applications (N6141A and W6141A) put the functionality of the MXE inside any of our X-Series signalanalyzers: PXA, MXA, EXA, or CXA. The excellent sensitivity of the X-Series signal analyzers translates into highly accurate emissions measurements.For PXA, MXA or EXA:/find/N6141A For CXA:/find/W6141AStrip Chart mode provides a unique, gap-free view that is useful fortracking DUT performance as a function of turntable or antenna position.Spectrogram displays and the signal-marker capability help you understand the amplitude–and time-varying nature of emissions.RTSA lets you see and understand high-speed transient signals that aredifficult to capture.See amplitude variation vs time with Strip ChartCharacterize the variation of signal amplitude versus time using Strip Chart, a Keysight-exclusive feature which plots data for up to three detectors. All collected data isgapless, with a two-hour time record. This feature is especially useful for capturing the azimuthal emissions characteristics of a DUT when testing on a turntable.The frequency used for the Strip Chart display is coupled to the suspect list, making it easy to view each signal in the suspect list.View varying emissions with spectrograph displaysObserve how emissions spanning a broad spectral range change over time using the built-in spectrograph display. Tracking any variations in spectral data can provide clues about the origins of out-of-compliance emissions.Capture transient signals with real-time spectrum analysisDiagnose high-speed transient signals using real-time spectrum analysis (RTSA) with frequencymask trigger capability. Preselected microwave RTSA enables image-free, over-the-air signal analysis so you can more quickly and easily analyze sources of radiated emissions.Build a Complete EMI Test SolutionProtect Your Investment with an Upgradable PlatformOur qualified Keysight Solution Partners provide a single point of contact to purchase complete EMI measurement solutions that meet commercial and military specifications. In addition to the MXE EMI receiver, they can provide equipment including chambers, probes, towers and antennas, and services such as integration, installation, training, and support. To further simplify testing, they also offer automation software that can meet your specific needs.If you need to go beyond emission and immunity, our solution partners can provide ESD, line harmonics, droop testing, and more.To keep your instrument current and extend its longevity, the MXE offers easy upgradability of hardware and software. When needed, you can enhanceplatform performance through upgradable CPU, memory, disk drives, and I/O ports. Internally, the mechanical assembly has three expansion slots that can accommodate future enhancements.On the software side, simple license-key upgrades are all it takes to add functionality or measurement applications. For example, the external source control option lets the MXE interface with a variety of Keysight signalgenerators, enabling stimulus/response testing up to 20 GHz. For detailed signal analysis, the library of available measurement applications includes analog demodulation, phase noise, and noise figure.Upgrade frequencyThrough return-to-Keysight upgrades, you can extend the frequency range of MXE EMI receivers up to 44 GHz. The receiver maintains its options, applications, and serial number.While the receiver is at the service center for a frequency extension, it is a convenient time to add functionality such as time domain scan for fast FFT-based frequency scanning.For precompliance testing, Keysight also offers frequency upgrades on PXA, MXA, or EXA signal /find/frequencyup11 | Keysight | MXE EMI Receiver N9038A - BrochureMXE Front and Rear PanelsView up to threedifferent prehensive display provides view of spectrum, meters, and suspect list.Second inputpulse-protected to 2 kW.Removable CPU enables processor, memory, and I/O upgrades.Auxiliary/IO port for LISN control.Send and receive SCPI commands over the GPIB interface.Identify signals and view information easily on the 21.4-cm, high-resolution XGA display.Acquire IQ waveform data quickly or control the MXE remotely from an external PC over the USB 2.0 (type-B port) interface.Synchronize other test equipment with the analyzer using the external trigger output signals.Get answers quickly with the comprehensive, context-sensitive embedded help system.Connect external peripherals and transfer data via the USB 2.0 (type-A port) interface.Navigate the interface and help system using the front-panel keys, or a mouse and keyboard.Test devices up to 44 GHz.View the display on an external monitor by connecting to the VGA video output.Two USB 2.0 ports conveniently located on the front of the instrument.Control the MXE remotely over1000Base-T LAN.Removable solid-state drive.Additional solid-state driveavailable for instrument security.Save files fast with the quick-save feature.12 | Keysight | MXE EMI Receiver N9038A - BrochureThis information is subject to change without notice.© Keysight Technologies, 2013 - 2018Published in USA, March 27, 20185990-7422ENRelated LiteratureKeysight MXE EMI receiverPublication title Publication number Data Sheet5990-7421EN Configuration Guide5990-7419EN X-Series Measurement Application Brochure5989-8019EN/find/mxeEvolving Since 1939Our unique combination of hardware, software, services, and people can help you reach your next breakthrough. We are unlocking the future of technology.From Hewlett-Packard to Agilent to Keysight.myKeysight/find/mykeysightA personalized view into the information most relevant to you. /find/emt_product_registrationRegister your products to get up-to-date product information and find warranty information.Keysight Services/find/serviceKeysight Services can help from acquisition to renewal across your instrument’s lifecycle. Our comprehensive service offerings—one-stop calibration, repair, asset management, technology refresh, consulting, training and more—helps you improve product qualityand lower costs.Keysight Assurance Plans/find/AssurancePlansUp to ten years of protection and no budgetary surprises to ensure your instruments are operating to specification, so you can rely on accurate measurements.Keysight Channel Partners/find/channelpartnersGet the best of both worlds: Keysight’s measurement expertise and product breadth, combined with channel partner convenience.For more information on KeysightTechnologies’ products, applications or services, please contact your local Keysight office. The complete list is available at:/find/contactus Americas Canada (877) 894 4414Brazil 55 11 3351 7010Mexico001 800 254 2440United States (800) 829 4444Asia Pacific Australia 1 800 629 485China800 810 0189Hong Kong 800 938 693India 1 800 11 2626Japan 0120 (421) 345Korea 080 769 0800Malaysia 1 800 888 848Singapore 180****8100Taiwan0800 047 866Other AP Countries (65) 6375 8100Europe & Middle East Austria 0800 001122Belgium 0800 58580Finland 0800 523252France 0805 980333Germany ***********Ireland 1800 832700Israel 1 809 343051Italy800 599100Luxembourg +32 800 58580Netherlands 0800 0233200Russia 8800 5009286Spain 800 000154Sweden 0200 882255Switzerland0800 805353Opt. 1 (DE)Opt. 2 (FR)Opt. 3 (IT)United Kingdom0800 0260637For other unlisted countries:/find/contactus(BP-9-7-17)/go/quality Keysight Technologies, Inc.DEKRA Certified ISO 9001:2015Quality Management System。

LM883AWG中文资料

LM124A/LM124QMLLow Power Quad Operational AmplifiersGeneral DescriptionThe LM124/124A consists of four independent,high gain,internally frequency compensated operational amplifiers which were designed specifically to operate from a single power supply over a wide range of voltages.Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage.Application areas include transducer amplifiers,DC gain blocks and all the conventional op amp circuits which now can be more easily implemented in single power supply systems.For example,the LM124/124A can be directly op-erated off of the standard +5Vdc power supply voltage which is used in digital systems and will easily provide the required interface electronics without requiring the additional +15Vdc power supplies.Unique Characteristicsn In the linear mode the input common-mode voltage range includes ground and the output voltage can also swing to ground,even though operated from only a single power supply voltagen The unity gain cross frequency is temperature compensatedn The input bias current is also temperature compensatedAdvantagesn Eliminates need for dual suppliesn Four internally compensated op amps in a single packagen Allows directly sensing near GND and V OUT also goes to GNDn Compatible with all forms of logicn Power drain suitable for battery operationFeaturesn Internally frequency compensated for unity gain n Large DC voltage gain 100dBn Wide bandwidth (unity gain)1MHz (temperature compensated)n Wide power supply range:Single supply 3V to 32Vor dual supplies ±1.5V to ±16Vn Very low supply current drain (700µA)—essentially independent of supply voltage n Low input biasing current 45nA (temperature compensated)n Low input offset voltage 2mV and offset current:5nAn Input common-mode voltage range includes ground n Differential input voltage range equal to the power supply voltagen Large output voltage swing 0V to V +−1.5VOrdering InformationNS PART NUMBER SMD PART NUMBERNS PACKAGE NUMBERPACKAGE DISCRIPTION LM124J/8837704301CA J14A 14LD CERDIPLM124AE/88377043022A E20A 20LD LEADLESS CHIP CARRIER LM124AJ/8837704302CAJ14A 14LD CERDIP LM124AW/883W14B 14LD CERPACK LM124AWG/8837704302XA WG14A 14LD CERAMIC SOIC LM124AJLQMLV 5962L9950401VCA,50k rd(Si)J14A 14LD CERDIP LM124AJRQMLV 5962R9950401VCA,100k rd(Si)J14A 14LD CERDIP LM124AWGLQMLV 5962L9950401VZA,50k rd(Si)WG14A 14LD CERAMIC SOIC LM124AWGRQMLV 5962R9950401VZA,100k rd(Si)WG14A 14LD CERAMIC SOIC LM124AWLQMLV 5962L9950401VDA,50k rd(Si)W14B 14LD CERPACK LM124AWRQMLV5962R9950401VDA,100k rd(Si)W14B14LD CERPACKJanuary 2005LM124A/LM124QML Low Power Quad Operational Amplifiers©2005National Semiconductor Corporation Connection DiagramsLeadless Chip Carrier20108055See NS Package Number E20ADual-In-Line Package20108001Top ViewSee NS Package Number J14A20108033See NS Package Number W14B or WG14AL M 124A /L M 124Q M L 2LM124A/LM124QML Schematic Diagram(Each Amplifier)3Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage,V +32Vdc or +16VdcDifferential Input Voltage 32VdcInput Voltage −0.3Vdc to +32VdcInput Current(V IN <−0.3Vdc)(Note 4)50mAPower Dissipation (Note 2)CERDIP 1260mW CERPACK 700mW LCC1350mW CERAMIC SOIC700mW Output Short-Circuit to GND (One Amplifier)(Note 3)V +≤15Vdc and T A =25˚C ContinuousOperating Temperature Range −55˚C ≤T A ≤+125˚CMaximum Junction Temperature 150˚CStorage Temperature Range−65˚C ≤T A ≤+150˚CLead Temperature (Soldering,10seconds)260˚C Thermal Resistance ThetaJA CERDIP (Still Air)103C/W (500LF/Min Air flow)51C/W CERPACK (Still Air)176C/W (500LF/Min Air flow)116C/W LCC (Still Air)91C/W (500LF/Min Air flow)66C/W CERAMIC SOIC (Still Air)176C/W (500LF/Min Air flow)116C/W ThetaJC CERDIP 19C/W CERPACK 18C/W LCC24C/W CERAMIC SOIC 18C/W Package Weight (Typical)CERDIP TBD CERPACK TBD LCCTBD CERAMIC SOIC 410mg ESD Tolerance (Note 5)250V Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:The maximum power dissipation must be derated at elevated temperatures and is dictated by Tjmax (maximum junction temperature),ThetaJA (package junction to ambient thermal resistance),and TA (ambient temperature).The maximum allowable power dissipation at any temperature is Pdmax =(Tjmax -TA)/ThetaJA or the number given in the Absolute Maximum Ratings,whichever is lower.Note 3:Short circuits from the output to V+can cause excessive heating and eventual destruction.When considering short circuits to ground,the maximum output current is approximately 40mA independent of the magnitude of V+.At values of supply voltage in excess of +15Vdc,continuous short-circuits can exceed the power dissipation ratings and cause eventual destruction.Destructive dissipation can result from simultaneous shorts on all amplifiers.Note 4:This input current will only exist when the voltage at any of the input leads is driven negative.It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps.In addition to this diode action,there is also lateral NPN parasitic transistor action on the IC chip.This transistor action can cause the output voltages of the op amps to go to the V+voltage level (or to ground for a large overdrive)for the time duration that an input is driven negative.This is not destructive and normal output states will re-establish when the input voltage,which was negative,again returns to a value greater than -0.3Vdc (at 25C).Note 5:Human body model,1.5k Ωin series with 100pF.L M 124A /L M 124Q M L 4LM124A/LM124QML Quality Conformance InspectionMIL-STD-883,Method5005—Group ASubgroup Description Temp(˚C)1Static tests at+252Static tests at+1253Static tests at-554Dynamic tests at+255Dynamic tests at+1256Dynamic tests at-557Functional tests at+258A Functional tests at+1258B Functional tests at-559Switching tests at+2510Switching tests at+12511Switching tests at-555LM124A 883DC Electrical Characteristics(The following conditions apply to all the following parameters,unless otherwise specified.)All voltages referenced to device ground.SYMBOL PARAMETERCONDITIONSNOTESMINMAX UNIT SUB-GROUPS IccPower Supply Current V+=5V1.2mA 1,2,3V+=30V3.0mA 14.0mA 2,3IsinkOutput Sink CurrentV+=15V,Vout =200mV,+Vin =0mV,-Vin =+65mV 12uA 1V+=15V,Vout =2V,+Vin =0mV,-Vin =+65mV10mA 15mA 2,3Isource Output Source CurrentV+=15V,Vout =2V,+Vin =0mV,-Vin =-65mV -20mA 1-10mA 2,3Ios Short Circuit Current V+=5V,Vout =0V -60mA 1VioInput Offset VoltageV+=30V,Vcm =0V -22mV 1-44mV 2,3V+=30V,Vcm =28.5V -22mV 1V+=30V,Vcm =28V -44mV 2,3V+=5V,Vcm =0V-22mV 1-44mV 2,3CMRRCommon Mode Rejection Ratio V+=30V,Vin =0V to 28.5V 70dB 1±IibInput Bias Current V+=5V,Vcm =0V -5010nA 1-10010nA 2,3Iio Input Offset Current V+=5V,Vcm =0V -1010nA 1-3030nA 2,3PSRR Power Supply Rejection Ratio V+=5V to 30V,Vcm =0V 65dB 1Vcm Common Mode Voltage Range V+=30V(Note 6)28.5V 1(Note 6)28V 2,3Avs Large Signal Gain V+=15V,Rl =2K Ohms,Vo =1V to 11V(Note 7)50V/mV 4(Note 7)25V/mV 5,6VohOutput Voltage High V+=30V,Rl =2K Ohms 26V 4,5,6V+=30V,Rl =10K Ohms27V 4,5,6VolOutput Voltage LowV+=30V,Rl =10K Ohms 40mV 4,5,6V+=30V,Isink =1uA 40mV 4100mV 5,6V+=5V,Rl =10K Ohms20mV 4,5,6Channel Separation Amp to Amp Coupling1KHz,20KHz (Note 8)80dB4L M 124A /L M 124Q M L 6LM124883DC Electrical Characteristics(The following conditions apply to all the following parameters,unless otherwise specified.)All voltages referenced to device ground.SYMBOL PARAMETER CONDITIONS NOTES MIN MAX UNIT SUB-GROUPS Icc Power Supply Current V+=5V 1.2mA1,2,3V+=30V 3.0mA14.0mA2,3Isink Output Sink Current V+=15V,Vout=200mV,+Vin=0mV,-Vin=+65mV12uA1V+=15V,Vout=2V,+Vin=0mV,-Vin=+65mV 10mA15mA2,3Isource Output SourceCurrent V+=15V,Vout=2V,+Vin=0mV,-Vin=-65mV-20mA1-10mA2,3Ios Short Circuit Current V+=5V,Vout=0V-60mA1 Vio Input Offset Voltage V+=30V,Vcm=0V-55mV1-77mV2,3V+=30V,Vcm=28V-55mV1-77mV2,3V+=5V,Vcm=0V-55mV1-77mV2,3V+=30V,Vcm=28.5V-55mV1 CMRR Common ModeRejection RatioV+=30V,Vin=0V to28.5V70dB1 +Iib Input Bias Current V+=5V,Vcm=0V-15010nA1-30010nA2,3 Iio Input Offset Current V+=5V,Vcm=0V-3030nA1-100100nA2,3 PSRR Power SupplyRejection RatioV+=5V to30V,Vcm=0V65dB1Vcm Common ModeVoltage Range V+=30V(Note6)28.5V1(Note6)28V2,3Avs Large Signal Gain V+=15V,Rl=2K Ohms,Vo=1V to11V 50V/mV4 25V/mV5,6Voh Output Voltage High V+=30V,Rl=2K Ohms26V4,5,6V+=30V,Rl=10K Ohms27V4,5,6 Vol Output Voltage Low V+=30V,Rl=10K Ohms40mV4,5,6V+=30V,Isink=1uA40mV4100mV5,6V+=5V,Rl=10K Ohms20mV4,5,6Channel Separation (Amp to Amp Coupling)1KHz,20KHz(Note8)80dB4LM124A/LM124QML7LM124A RAD HARD DC Electrical Characteristics(Note 10)(The following conditions apply to all the following parameters,unless otherwise specified.)All voltages referenced to device ground.SYMBOL PARAMETER CONDITIONSNOTESMIN MAX UNIT SUB-GROUPS VioInput Offset VoltageVcc+=30V,Vcc-=Gnd,Vcm =-15V-22mV 1-44mV 2,3Vcc+=2V,Vcc-=-28V,Vcm =13V-22mV 1-44mV 2,3Vcc+=5V,Vcc-=Gnd,Vcm =-1.4V-22mV 1-44mV 2,3Vcc+=2.5V,Vcc-=-2.5,Vcm =1.1V-22mV 1-44mV 2,3IioInput Offset CurrentVcc+=30V,Vcc-=Gnd,Vcm =-15V-1010nA 1,2-3030nA 3Vcc+=2V,Vcc-=-28V,Vcm =13V-1010nA 1,2-3030nA 3Vcc+=5V,Vcc-=Gnd,Vcm =-1.4V-1010nA 1,2-3030nA 3Vcc+=2.5V,Vcc-=-2.5,Vcm =1.1V-1010nA 1,2-3030nA 3±IibInput Bias CurrentVcc+=30V,Vcc-=Gnd,Vcm =-15V-50+0.1nA 1,2-100+0.1nA 3Vcc+=2V,Vcc-=-28V,Vcm =13V-50+0.1nA 1,2-100+0.1nA 3Vcc+=5V,Vcc-=Gnd,Vcm =-1.4V-50+0.1nA 1,2-100+0.1nA 3Vcc+=2.5V,Vcc-=-2.5,Vcm =1.1V-50+0.1nA 1,2-100+0.1nA 3+PSRR Power Supply Rejection Ratio Vcc-=Gnd,Vcm =-1.4V,5V ≤Vcc ≤30V-100100uV/V 1,2,3CMRR Common Mode Rejection Ratio 76dB 1,2,3Ios+Output Short Circiut CurrentVcc+=30V,Vcc-=Gnd,Vo =25V-70mA 1,2,3IccPower Supply Current Vcc+=30V,Vcc-=Gnd3mA 1,24mA 3Delta Vio/Delta TInput Offset Voltage Temperature Sensitivity+25˚C ≤TA ≤+125˚C,+Vcc =5V,-Vcc =0V,Vcm =-1.4V(Note 9)-3030uV/˚C2-55˚C ≤TA ≤+25˚C,+Vcc =5V,-Vcc =0V,Vcm =-1.4V(Note 9)-3030uV/˚C 3Delta Iio/Delta TInput Offset Current Temperature Sensitivity+25˚C ≤TA ≤+125˚C,+Vcc =5V,-Vcc =0V,Vcm =-1.4V(Note 9)-400400pA/˚C2-55˚C ≤TA ≤+25˚C,+Vcc =5V,-Vcc =0V,Vcm =-1.4V(Note 9)-700700pA/˚C 3L M 124A /L M 124Q M L 8LM124A RAD HARD AC/DC Electrical Characteristics(Note10)(The following conditions apply to all the following parameters,unless otherwise specified.)All voltages referenced to device ground.SYMBOL PARAMETER CONDITIONS NOTES MIN MAX UNIT SUB-GROUPSVol Logical"0"OutputVoltage Vcc+=30V,Vcc-=Gnd,Rl=10K Ohms35mV4,5,6Vcc+=30V,Vcc-=Gnd,Iol=5mA1.5V4,5,6Vcc+=4.5V,Vcc-=Gnd,Iol=2uA0.4V4,5,6Voh Logical"1"OutputVoltage Vcc+=30V,Vcc-=Gnd,Ioh=-10mA27V4,5,6Vcc+=4.5V,Vcc-=Gnd,Ioh=-10mA2.4V4,5,6Avs+Voltage Gain Vcc+=30V,Vcc-=Gnd,1V≤Vo≤26V,Rl=10K Ohms50V/mV425V/mV5,6 Vcc+=30V,Vcc-=Gnd,5V≤Vo≤20V,Rl=2K Ohms50V/mV425V/mV5,6Avs Voltage Gain Vcc+=5V,Vcc-=Gnd,1V≤Vo≤2.5V,Rl=10K Ohms10V/mV4,5,6Vcc+=5V,Vcc-=Gnd,1V≤Vo≤2.5V,Rl=2K Ohms10V/mV4,5,6+Vop Maximum OutputVoltage Swing Vcc+=30V,Vcc-=Gnd,Vo=+30V,Rl=10K Ohms27V4,5,6Vcc+=30V,Vcc-=Gnd,Vo=+30V,Rl=2K Ohms26V4,5,6TR(tr)Transient Response:Rise TimeVcc+=30V,Vcc-=Gnd1uS7,8A,8BTR(os)Transient Response:OvershootVcc+=30V,Vcc-=Gnd50%7,8A,8B±Sr Slew Rate:Rise Vcc+=30V,Vcc-=Gnd0.1V/uS7,8A,8B Slew Rate:Fall Vcc+=30V,Vcc-=Gnd0.1V/uS7,8A,8BLM124A/LM124QML9LM124A RAD HARD —AC Electrical Characteristics(Note 10)(The following conditions apply to all the following parameters,unless otherwise specified.)AC:+Vcc =30V,-Vcc =0VSYMBOL PARAMETER CONDITIONSNOTESMINMAX UNIT SUB-GROUPS NI(BB)Noise Broadband +Vcc =15V,-Vcc =-15V,BW =10Hz to 5KHz 15uVrm s 7NI(PC)Noise Popcorn+Vcc =15V,-Vcc =-15V,Rs =20K Ohms,BW =10Hz to 5KHz 50uVpK7Cs Channel Separation +Vcc =30V,-Vcc =Gnd,Rl =2K Ohms80dB 7Rl =2K Ohms,Vin =1V and 16V,A to B 80dB 7Rl =2K Ohms,Vin =1V and 16V,A to C 80dB 7Rl =2K Ohms,Vin =1V and 16V,A to D 80dB 7Rl =2K Ohms,Vin =1V and 16V,B to A 80dB 7Rl =2K Ohms,Vin =1V and 16V,B to C 80dB 7Rl =2K Ohms,Vin =1V and 16V,B to D 80dB 7Rl =2K Ohms,Vin =1V and 16V,C to A 80dB 7Rl =2K Ohms,Vin =1V and 16V,C to B 80dB 7Rl =2K Ohms,Vin =1V and 16V,C to D 80dB 7Rl =2K Ohms,Vin =1V and 16V,D to A 80dB 7Rl =2K Ohms,Vin =1V and 16V,D to B 80dB 7Rl =2K Ohms,Vin =1V and 16V,D to C80dB7L M 124A /L M 124Q M L 10LM124A/LM124QML LM124A RAD HARD—DC Drift Values(Note10)(The following conditions apply to all the following parameters,unless otherwise specified.)DC:"Delta calculationsperformedon QMLV devices at group B,subgroup5only"SYMBOL PARAMETER CONDITIONS NOTES MIN MAX UNIT SUB-GROUPSVio Input Offset Voltage Vcc+=30V,Vcc-=Gnd,-0.50.5mV1Vcm=-15V±Iib Input Bias Current Vcc+=30V,Vcc-=Gnd,-1010nA1Vcm=-15VElectrical Characteristics—POST RADIATION LIMITS+25˚C(Note10)(The following conditions apply to all the following parameters,unless otherwise specified.)All voltages referenced to device ground.SYMBOL PARAMETER CONDITIONS NOTES MIN MAX UNIT SUB-GROUPS(Note10)-2.5 2.5mV1Vio Input Offset Voltage Vcc+=30V,Vcc-=Gnd,Vcm=-15VVcc+=2V,Vcc-=-28V,(Note10)-2.5 2.5mV1Vcm=13V(Note10)-2.5 2.5mV1Vcc+=5V,Vcc-=GND,Vcm=-1.4V(Note10)-2.5 2.5mV1Vcc+=2.5V,Vcc-=-2.5,Vcm=1.1VIio Input Offset Current Vcc+=30V,Vcc-=GND,(Note10)-1515nA1Vcm=-15V(Note10)-1515nA1Vcc+=2V,Vcc-=-28V,Vcm=13VVcc+=5V,Vcc-=GND,(Note10)-1515nA1Vcm=-1.4V(Note10)-1515nA1Vcc+=2.5V,Vcc-=-2.5V,Vcm=1.1V±Iib Input Bias Current Vcc+=30V,Vcc-=GND,(Note10)-75+0.1nA1Vcm=-15V(Note10)-75+0.1nA1Vcc+=2V,Vcc-=-28V,Vcm=13VVcc+=5V,Vcc-=GND,(Note10)-75+0.1nA1Vcm=-1.4V(Note10)-75+0.1nA1Vcc+=2.5V,Vcc-=-2.5V,Vcm=1.1VAvs+Voltage Gain Vcc+=30V,Vcc-=GND,(Note10)40V/mV41V≤Vo≤26V,Rl=10K Ohms(Note10)40V/mV4Vcc+=30V,Vcc-=GND,5V≤Vo≤20V,Rl=2K OhmsNote6:Guaranteed by Vio tests.Note7:Datalog reading in K=V/mVNote8:Guaranteed,not testedNote9:Calculated parametersNote10:Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics except as listed in the Post Radiation Limits Table.These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect.Radiation end point limits for the noted parameters are guaranteed only for the conditions as specified in MIL-STD-883,Method1019Typical Performance CharacteristicsInput Voltage RangeInput Current2010803420108035Supply Current Voltage Gain2010803620108037Open Loop FrequencyResponse Common Mode RejectionRatio2010803820108039L M 124A /L M 124Q M LTypical Performance Characteristics(Continued)Voltage Follower PulseResponseVoltage Follower PulseResponse(Small Signal) 2010804020108041Large Signal FrequencyResponseOutput CharacteristicsCurrent Sourcing 2010804220108043Output CharacteristicsCurrent Sinking Current Limiting2010804420108045LM124A/LM124QMLApplication HintsThe LM124series are op amps which operate with only a single power supply voltage,have true-differential inputs,and remain in the linear mode with an input common-mode voltage of 0V DC .These amplifiers operate over a wide range of power supply voltage with little change in performance characteristics.At 25˚C amplifier operation is possible down to a minimum supply voltage of 2.3V DC .The pinouts of the package have been designed to simplify PC board layouts.Inverting inputs are adjacent to outputs for all of the amplifiers and the outputs have also been placed at the corners of the package (pins 1,7,8,and 14).Precautions should be taken to insure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a test socket as an unlimited current surge through the result-ing forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.Large differential input voltages can be easily accommo-dated and,as input differential voltage protection diodes are not needed,no large input currents result from large differ-ential input voltages.The differential input voltage may be larger than V +without damaging the device.Protection should be provided to prevent the input voltages from going negative more than −0.3V DC (at 25˚C).An input clamp diode with a resistor to the IC input terminal can be used.To reduce the power supply drain,the amplifiers have a class A output stage for small signal levels which converts to class B in a large signal mode.This allows the amplifiers to both source and sink large output currents.Therefore both NPN and PNP external current boost transistors can be used to extend the power capability of the basic amplifiers.The output voltage needs to raise approximately 1diode drop above ground to bias the on-chip vertical PNP transistor for output current sinking applications.For ac applications,where the load is capacitively coupled to the output of the amplifier,a resistor should be used,from the output of the amplifier to ground to increase the class A bias current and prevent crossover distortion.Where the load is directly coupled,as in dc applications,there is no crossover distortion.Capacitive loads which are applied directly to the output of the amplifier reduce the loop stability margin.Values of 50pF can be accommodated using the worst-case non-inverting unity gain rge closed loop gains or resistive isolation should be used if larger load capacitance must be driven by the amplifier.The bias network of the LM124establishes a drain current which is independent of the magnitude of the power supply voltage over the range of from 3V DC to 30V DC .Output short circuits either to ground or to the positive power supply should be of short time duration.Units can be de-stroyed,not as a result of the short circuit current causing metal fusing,but rather due to the large increase in IC chip dissipation which will cause eventual failure due to exces-sive junction temperatures.Putting direct short-circuits on more than one amplifier at a time will increase the total IC power dissipation to destructive levels,if not properly pro-tected with external dissipation limiting resistors in series with the output leads of the amplifiers.The larger value of output source current which is available at 25˚C provides a larger output current capability at elevated temperatures (see typical performance characteristics)than a standard IC op amp.The circuits presented in the section on typical applications emphasize operation on only a single power supply voltage.If complementary power supplies are available,all of the standard op amp circuits can be used.In general,introduc-ing a pseudo-ground (a bias voltage reference of V +/2)will allow operation above and below this value in single power supply systems.Many application circuits are shown which take advantage of the wide input common-mode voltage range which includes ground.In most cases,input biasing is not required and input voltages which range to ground can easily be accommodated.L M 124A /L M 124Q M LTypical Single-Supply Applications(V+=5.0V DC)Non-Inverting DC Gain(0V Input=0V Output)20108005 *R not needed due to temperature independent I INDC Summing Amplifier(V IN’S≥0V DC and V O≥V DC)Power Amplifier20108006 Where:V0=V1+V2−V3−V4(V1+V2)≥(V3+V4)to keep V O>0V DC20108007V0=0V DC for V IN=0V DCA V=10LM124A/LM124QMLTypical Single-Supply Applications (V +=5.0V DC )(Continued)LED Driver“BI-QUAD”RC Active Bandpass Filter2010800820108009f o =1kHz Q =50A V =100(40dB)Fixed Current Sources Lamp Driver2010801020108011L M 124A /L M 124Q M LTypical Single-Supply Applications(V+=5.0V DC)(Continued)Current Monitor20108012*(Increase R1for I L small)Driving TTL20108013Voltage Follower20108014Pulse Generator20108015Squarewave Oscillator20108016Pulse Generator20108017LM124A/LM124QMLTypical Single-Supply Applications (V +=5.0V DC )(Continued)High Compliance Current Sink20108018I O =1amp/volt V IN (Increase R E for I o small)Low Drift Peak Detector20108019L M 124A /L M 124Q M LTypical Single-Supply Applications (V +=5.0V DC )(Continued)Comparator with HysteresisGround Referencing a Differential Input Signal2010802020108021V O =V RVoltage Controlled Oscillator Circuit20108022*Wide control voltage range:0V DC ≤V C ≤2(V +−1.5V DC )Photo Voltaic-Cell Amplifier20108023LM124A/LM124QMLTypical Single-Supply Applications (V +=5.0V DC )(Continued)AC Coupled Inverting Amplifier20108024AC Coupled Non-Inverting Amplifier20108025L M 124A /L M 124Q M LTypical Single-Supply Applications (V +=5.0V DC )(Continued)DC Coupled Low-Pass RC Active Filter20108026f O =1kHz Q =1A V =2High Input Z,DC Differential Amplifier20108027LM124A/LM124QML21Typical Single-Supply Applications (V +=5.0V DC )(Continued)High Input Z Adjustable-Gain DC Instrumentation Amplifier20108028Using Symmetrical Amplifiers to Reduce Input Current (General Concept)20108029Bridge Current Amplifier20108030L M 124A /L M 124Q M L 22LM124A/LM124QMLTypical Single-Supply Applications(V+=5.0V)(Continued)DCBandpass Active Filter Array20108031f O=1kHzQ=2523Revision History SectionDateReleased RevisionSectionOriginator Changes9–2–04ANew Release,Corporate formatR.Malone3MDS data sheets converted into one Corp.data sheet format.MNLM124-X,Rev.1A2,MNLM124A-X,Rev.1A3and MRLM124A-X-RH,Rev.5A0.MDS data sheets will be archived.01/27/05BConnection Diagrams,Quality Conformance Inspection Section,and Physical Dimensions drawingsR.MaloneAdded E package Connection Diagram.Changed verbiage under Quality Conformance Title,and UpdatedRevisions for the Marketing Drawings.L M 124A /L M 124Q M L 24Physical Dimensionsinches (millimeters)unless otherwise notedSAMPLE TEXT Ceramic Dual-In-Line Package (J)NS Package Number J14ASAMPLE TEXT 20Pin Leadless Chip Carrier,Type C (E)NS Package Number E20ALM124A/LM124QML25Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)SAMPLE TEXT Ceramic Flatpak PackageNS Package Number W14BSAMPLE TEXT 14-Pin Ceramic Package (WG)NS Package Number WG14AL M 124A /L M 124Q M L 26NotesNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.For the most current product information visit us at .LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systemswhich,(a)are intended for surgical implant into the body,or(b)support or sustain life,and whose failure to perform whenproperly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life supportdevice or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification(CSP-9-111C2)and the Banned Substances and Materials of Interest Specification(CSP-9-111S2)and contain no‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas CustomerSupport CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerSupport CenterEmail:ap.support@National SemiconductorJapan Customer Support CenterFax:81-3-5639-7507Email:jpn.feedback@Tel:81-3-5639-7560 LM124A/LM124QML Low Power Quad Operational Amplifiers。

将整合进行到底

将整合进行到底作者:阿龙来源:《电脑知识与技术·经验技巧》2010年第05期对应DIY玩家来说,为了发挥CPU的性能极限,往往需要选配一款出色的主板,而在主板整合时代,高清应用、节能环保被放在主要位置,AMD在这个方面表现优越,自AMD2009年推出785G/790GX整合主板后,又于2010年3月推出功能更强大的整合主板:AMD 890GX芯片组,对于AMD一族,这款主板无疑是更好的选择。

一、AMD 890GX主板特点作为AMD最新一代整合主板,890GX芯片组拥有令人称道的应用优势,首先它整合了Radeon HD4290显卡,板载128MB DDR3显存,内置40个流处理器、8个纹理寻址单元、4个纹理过滤单元和4个光栅化单元,支持DirextX 10.1及UVD2.0高清解码引擎,对于高清解码、3D 游戏处理表现不俗,用户无需额外买显卡也能体验高清娱乐。

在图形扩展能力上,890GX主板在外接PCI-E X16显卡情况下,可实现混合交火、3路或4路交火,大大提升了游戏玩家的扩展能力,由于PCI-E提升到了2.0版本,可最大限度满足USB3.0接口的数据传输需要,此外,890GX主板搭配了SB850南桥,原生支持SATA 6GB/s,且很多主板也通过板载第三方芯片来支持USB3.0接口。

在兼容性方面,890GX主板支持目前所有的AM3系列处理器,且可兼容AMD即将推出的Thuban Phenom II X6六核处理器,由于采用VGA/DVI/HDMI全接口设计,为此890GX主板非常容易搭建家庭娱乐PC或HTPC,对应影音娱乐或游戏玩家,如果你钟情AMD平台,890GX主板是不错的选择。

二、890GX主板选购须知从产品行情来看,目前890GX主板的价格在699元到千元不等,除了用料工艺和特殊功能有区别外,例如10相供电设计、双BIOS设计或智能超频能力等,几乎所有的890GX主板在规格上都没太多差距,为此,如果不是有特别需要,建议选择价格在700元左右的890GX主板,但值得注意,为了节省成本,部分890GX主板只搭配了SB750南桥,这会限制SATA接口和USB接口的数据传输能力。

黑莓8830-入门进阶全攻略

开篇前言黑莓8830在这个价位上不是不二的王者,非常强大,想想吧200块,也只能买个最低端的诺基亚蓝屏手机!由于特殊的国情,黑莓8830C网无法使用,我们也不提供这方面的技术支持,diy高手请自行参阅各论坛写号教程,请理解。

入门篇一、认识你的Blackberry8830无线手持设备电源键-机顶左侧,长按电源键可实现开/关手机。

静音键-机顶右侧,长按可进入待机状态;播放音频、视频中可暂停;可中断电话铃声。

快捷键-机身左侧,可通过设置获取快捷功能,默认声控拨号。

音量调节键-机身右侧,可调节音量大小,包括通话音量,音频、视频音量。

主键盘区(暂且这么称呼)-如下图首排键位:拨号键/菜单键/轨迹球/返回键/挂机键(注:不是退出键)字母键不多赘言。

符号的实现:1、键盘上显示的符号:数字键7左侧-ALT键+对应键位2、特殊符号:space键右侧SYM键3、大写锁定:键盘最下排标有aA符号的键粒(shift键)+对应字母键进阶篇二、基础设置及操作基本功能的实现开机后信号的选择:主菜单-manage connections-mobile networkoptions-network mode-GSM 这样你的8830才有G网的信号。

1、电话- 1.按绿色拨号键2.按菜单键3.进入选项(按轨迹球或者按回车键)4.智能拨号5.看到国家地区代码是+多少了对么6.按下alt 出现列表然后上拨轨迹球选择未知7.保存退出关于8830 4.5ROM状态下,修改国家区域码后仍然提示未开通国际漫游业务的解决办法:选项-安全选项-一般设置-按黑莓键-擦除手持设备按提示输入blackberry 等待重启-重新设置国家区域那为未知,OK了,可以接打电话了。

2、SIM卡电话本导入- 1.进入通讯录看到一片空白2.如果是4.6 4.7等ROM会提示你了。

早先的不会。

3.按黑莓键进入sim地址簿4.看到你卡上的电话本了吧5.再来一次按黑莓键选择全部复制到地址簿6.还做啥等待等待完成。

ad9850中文资料

海纳电子资讯网:www.fpga-arm.com目录摘要 —————————————————————————2 创新之处 ———————————————————————2 关键词 ————————————————————————2 引言 —————————————————————————2 系统工作原理 —————————————————————3 直接数字频率合成 ———————————————————4 DDS 基本原理及性能特点 —————————————————5 采用 DDS 的 AD9851 ———————————————————6 AD9851 的原理 —————————————————————7 AD9851 在信号源中的应用 ————————————————8 AD9851 在本系统的应用电路 ———————————————9 低通滤波器(LPF) ——————————————————10 锁相环频率合成 ———————————————————11 锁相环频率合成 MC145151 在本电路中的应用 ————————12 压控振荡器(VCO) ———————————————————12 缓冲放大器 ——————————————————————13 单片机控制的整体电路 —————————————————14 功率放大 ———————————————————————15 本系统的软件设计 ———————————————————15 总调试 ————————————————————————25 结束语 ————————————————————————25 DDS 短波信号发生器技术指标 ——————————————26 所采用的仪器设备 ———————————————————26 所用软件 ———————————————————————26 参考文献 ———————————————————————26 参考网站 ———————————————————————27www.fpga-ar m1.海纳电子资讯网:www.fpga-arm.comDDS 短波信号发生器摘要: 本文主要介绍的是采用直接数字频率合成的短波信号发生器, 它 主要以微电脑控制部分、直接数字频率合成(DDS)部分、数字锁相 环频率合成部分、背光液晶显示部分、功率放大部分等组成。

AO8830;中文规格书,Datasheet资料

SymbolTyp Max 6483115140R θJL 7085Absolute Maximum Ratings T °C/W Maximum Junction-to-Ambient A Steady-State °C/W Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-Ambient A t ≤ 10s R θJA AO8830SymbolMin TypMaxUnits BV DSS 20V1T J =55°C5I GSS 10BV GSO ±12V V GS(th)0.50.61V I D(ON)30A 162227T J =125°C31192530m Ω223037253241m Ω324255m Ωg FS 21S V SD 0.751V I S2.5A C iss 290pF C oss 120pF C rss 40pF R g1.6k ΩQ g 5.2nC Q gs 2.1nC Q gd 1.9nC t D(on)280ns t r 972ns t D(off) 2.35µs t f 2.2µs t rr 25ns Q rr8nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Maximum Body-Diode Continuous CurrentInput Capacitance Output Capacitance Gate-Source Breakdown Voltage V DS =0V, I G =±250uA Gate Threshold Voltage V DS =V GS I D =1mA Diode Forward VoltageTurn-On DelayTime DYNAMIC PARAMETERS V GS =0V, V DS =10V, f=1MHz Gate Drain Charge Turn-On Rise Time Turn-Off DelayTime V GS =4.5V, V DS =10V, R L =1.7Ω, R GEN =3ΩGate resistanceV GS =0V, V DS =0V, f=1MHzTurn-Off Fall TimeSWITCHING PARAMETERS Total Gate Charge V GS =4.5V, V DS =10V, I D =6AGate Source Charge m ΩV GS =2.5V, I D =4A I S =1A,V GS =0V V DS =5V, I D =6AV GS =1.8V, I D =2AV GS =4.5V, I D =5A V GS =3.1V, I D =4A Gate-Body leakage current R DS(ON)Static Drain-Source On-ResistanceForward TransconductanceµAElectrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions I DSS V DS =16V, V GS =0VZero Gate Voltage Drain Current V DS =0V, V GS =±10V Body Diode Reverse Recovery TimeBody Diode Reverse Recovery Charge I F =6A, dI/dt=100A/µs, V GS =-9VDrain-Source Breakdown Voltage On state drain currentI D =250µA, V GS =0V V GS =4.5V, V DS =5V V GS =10V, I D =6AReverse Transfer Capacitance I F =6A, dI/dt=100A/µs, V GS =-9VA: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The currentand power rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6,12,14 are obtained using <300 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev 5: July 2010VdsCharge Gate Charge Test Circuit & WaveformVddVddVR esistive S w itching Test C ircuit & W aveform s分销商库存信息: AOSAO8830。

5833中文资料

5833中⽂资料Designed to reduce logic supply current, chip size, and system cost, the UCN5833A/EP integrated circuits offer high-speed operation for thermal printers. These devices can also be used to drive multi-plexed LED displays or incandescent lamps within their 125 mA peak output current rating. The combination of bipolar and MOS technolo-gies gives BiMOS II smart power ICs an interface flexibility beyond the reach of standard buffers and power driver circuits.These 32-bit drivers have bipolar open-collector npn Darlington outputs, a CMOS data latch for each of the drivers, a 32-bit CMOS shift register, and CMOS control circuitry. The high-speed CMOS shift registers and latches allow operation with most microprocessor-based systems at data input rates above 3.3 MHz. Use of these drivers with TTL may require input pull-up resistors to ensure an input logic high.The UCN5833A is supplied in a 40-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. At an ambient temperature of +75°C, all outputs of the DlP-packaged device will sustain 50 mA continuously. For high-density applications, the UCN5833EP is available. This 44-lead plastic chip carrier (quad pack) is intended for surface-mounting on solder lands with 0.050" (1.27 mm) centers.CMOS serial data outputs permit cascading for applications requiring additional drive lines.FEATURESI To 3.3 MHz Data Input Rate I 30 V Minimum Output Breakdown I Darlington Current-Sink Outputs I Low-Power CMOS Logic and LatchesBiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERAlways order by complete part number:Part Number Package UCN5833A 40-Pin DIP UCN5833EP 44-Lead PLCCData Sheet 26185.16A*58335833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000SERIAL DATA IN POWER STROBE OUT OUT OUT OUT OUT OUT 123456OUT7OUT 8OUT 9OUTOUT OUTOUT OUTLOGIC SUPPLY OUT OUT Dwg. No. A-13,051TYPICAL OUTPUT DRIVERSUBOUT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright ? 1986, 1995, Allegro MicroSystems, Inc.5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERTRUTH TABLEL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 5 V (unless otherwise noted).Limits CharacteristicSymbol Test Conditions Min.Max.Units Output Leakage Current I CEX V OUT = 30 V, T A = 70°C —10µA Collector-Emitter V CE(SAT)l OUT = 50 mA — 1.2V l OUT = 100 mA— 1.7V Input VoltageV IN(1) 3.5 5.3V V IN(0)-0.3+0.8V Input Currentl IN(1)V IN = 5.0 V — 1.0µA l IN(0)V IN = 0 V —-1.0µA Serial Output VoltageV OUT(1)I OUT = -200 µA 4.5—V V OUT(0)I OUT = 200 µA—0.3V Supply Currentl DD One output ON, l OUT = 100 mA — 1.0mA All outputs OFF—50µA Output Rise Time t r l OUT = 100 mA, 10% to 90%—500ns Output Fall Timet fl OUT = 100 mA, 90% to 10%—500nsNOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.Saturation Voltage5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TIMING CONDITIONS(V DD = 5.0 V, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time)..........................................................................75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time).............................................................................75 ns C.Minimum Data Pulse Width ................................................................150 ns D.Minimum Clock Pulse Width...............................................................150 nsE.Minimum Time Between Clock Activation and Strobe.......................300 nsF.Minimum Strobe Pulse Width .............................................................100 nsG.Typical Time Between Strobe Activation andOutput Transition ...........................................................................500 nsDwg. No. A-12,276ASerial Data present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the OUTPUT ENABLE input be low during serial data entry.When the OUTPUT ENABLE input is low, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the OUTPUT ENABLE input high, the outputs are controlled by the state of the latches.CLOCK DATA INSTROBE NOUTPUT ENABLEOUT5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.UCN5833ADimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)123Dwg. MA-003-40 mm20421123Dwg. MA-003-40 in2045833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000UCN5833EPDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)Dwg. MA-005-44A mm0.53340Dwg. MA-005-44A in0.021740NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.5833BiMOS II 32-BITSERIAL-INPUT,LATCHED DRIVERThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use. 5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number ?SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V?58958-Bit 350 mA 50 V 58218-Bit 350 mA 80 V 58228-Bit 350 mA 50 V?58418-Bit 350 mA 80 V?58428-Bit (constant-current LED driver)75 mA 17 V 62758-Bit (DMOS drivers)250 mA 50 V 65958-Bit (DMOS drivers)350 mA 50 V?6A5958-Bit (DMOS drivers)100 mA 50 V 6B59510-Bit (active pull-downs)-25 mA 60 V 5810-F and 6809/1012-Bit (active pull-downs)-25 mA 60 V 5811 and 681116-Bit (constant-current LED driver)75 mA 17 V 627620-Bit (active pull-downs)-25 mA 60 V 5812-F and 681232-Bit (active pull-downs)-25 mA 60 V 5818-F and 681832-Bit100 mA 30 V 583332-Bit (saturated drivers)100 mA 40 V 5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V?58008-Bit -25 mA 60 V 58158-Bit350 mA 50 V?58018-Bit (DMOS drivers)100 mA 50 V 6B2738-Bit (DMOS drivers)250 mA 50 V 6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V?5804Addressable 8-Bit Decoder/DMOS Driver 250 mA 50 V6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V?6A259Addressable 8-Bit Decoder/DMOS Driver 100 mA 50 V 6B259Addressable 28-Line Decoder/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltagelimits.Negative current is defined as coming out of (sourcing) the output.Complete part number includes additional characters to indicate operating temperature range and package style. Internal transient-suppression diodes included for inductive-load protection.。

芯片

声卡芯片:AC97只是一个规范,不是芯片.如AD1881,AD1885,CS4299,ALC100才是声卡芯片,太多了cmi8738,cmi9739,cmi9738,alc6XX一般的cmi8738,创新,黑金,德国坦克是独立的。

其他为板载。

realtek 台湾瑞昱公司,主要生产ALC系列AC'97声卡For所有的芯片组Analog Devices 美国模拟器件,主要生产AD18XX、AD19XX系列FOR所有的芯片组Cmedia 台湾骅迅公司,主要制作CMI97系列FOR所有的芯片组VIA 台湾威胜公司,制作VT系列FOR VIA芯片组SiS 台湾矽统公司,FOR SIS芯片组Sigmatel 美国集成声讯公司,笔记本和早期主板上常见的AC'97芯片声卡很容易找到的一般再板子的左侧就是接近机箱后面扩展接口的位置有一个方形或长方形的小手指尖大小的新片为声卡新片显卡新片是看不到的一般集成再南桥里面就算是独立的上面也有散热片很难看到网卡新片一般和声卡的相隔不愿稍大一些有大手指肚大小具体型号厂家实在是太多了声卡一般为alc hd 的较多显卡跟主板芯片组有关网卡多为8139的居多网卡芯片;常用网卡芯片简介网卡芯片厂商主要有六家,Intel、Realtek、Broadcom、Atheros、VIA、SIS。

其中Intel、Realtek、Broadcom、Atheros的芯片是最为常见的。

让我们来分别了解一下。

IntelIntel是个老品牌了,早期的台式机有很多都采用Intel的入门级网卡产品——lntel Pro/100VE。

在AMD还没与Intel形成明显的竞争关系之前,这个网卡在市场中很常见,后来Intel又推出了Pro 10/100、Pro 100/1000,后两个产品现在大多集成到Intel自主品牌的主板中,DIY市场已经不多见了。

除此之外,Intel还有很多网卡芯片,例如:8257X系列,隶属于高端千兆网卡产品。

MEMORY存储芯片ADM3483EARZ中文规格书

POWER SUPPLY Voltage Range Supply Current

FUNCTIONAL BLOCK DIAGRAMS

VCC

ADM3483E/ ADM3486E

RO

R

RE

A

DE

B

DI

D

06284-001

GND

Figure 1.

VCC

ADM3488E/ ADM3490E

A

RO

R

B

06284-002

Z

DI

D

Y

GND

Figure 2.

VCC

ADM3491E

A

RO

R

B

RE

DE

Common-Mode O for Complementary Output States1 ∆VOC

Short-Circuit Output Current

IOSD

−250

Output Leakage (Y, Z) (ADM3491E Only) IO Normal Mode

Table 2. ADM3483E/ADM3486E/ADM3488E/ADM3490E/ADM3491E

Parameter

Symbol Min

Typ

DRIVER

Differential Outputs

Differential Output Voltage

VOD

2.0

MB90F883S资料