基于Nios_自定制Avalon设备的设计与实现

基于NiosⅡ的嵌入式智能网络家居系统的设计

执

行 — — —

被

控 器

供的网页进行远程浏览 , 对网页上显示 的家 电状态 进行 查 询并按 照用 户 的新 的要 求进 行

重 新设 置 . 收 到远 程客户 的设 置请 求 后 , 在 服 务 器端 通过 一个 C IC mm nG t a ne一 G ( o o ae yItr w

网络七层协议栈 中的传输层 和 M C层 A 的功能 , 它还 具有 1/ 0 自适应 、 0 10 M 双 ]/ [ 半工 自适应 等功 能. 存储 器部 分有

个 8MB S R M、 个 4 MB Fah D A 一 l s R M和有一个 52 BS A O 1 R M用来提供 K

用户可以通过客户端浏览器访问嵌入式 B A服务器对远程家居中的电器进行状态查询和控制. O 由于采用了

先进的 S P 技术 , OC 本系统具有设计效率高和灵活性好等优 . J

1 系统功能

系统功能如图 1 所示. 整个 系统由都接入 了 I e t n me 网络 的客户端访问设备 和一个功能强大的嵌入式 t We 服务以及一个执行机构构成. b 嵌入式 We b服务器通过执行机构和被控家 电连接. 服务器通过查询方式 获得被控电器的当前状况 , 并将该信息显示在服务器的主页上. 远程用户使用带有浏览器软件的设备 ( 个人

2 系统 的硬 件设计

嵌入式智能家居控制器的硬件 由 F G 存储器和外围模块等三个部分构 成, P A、 结构如图 2 所示.

收稿 日期 :0 6—1 —2 . 20 1 O 基金项 目: 湖北省教育厅重点资助项 目( o 3 o 8 . 2oA o ) 作者简介 : 袁海林 (9 2一 ) 男 , 16 , 硕士 , 副教授 , 主要从事嵌入式技术和 E A技术的应用和研究 D

基于NiosⅡ的数据采集系统设计与实现

萍 凌

力。

203) 043

上海

2 0 3 )2 复旦大学信息科学 与工程学 院通信科学与工程系 上海 0 4 4 (.

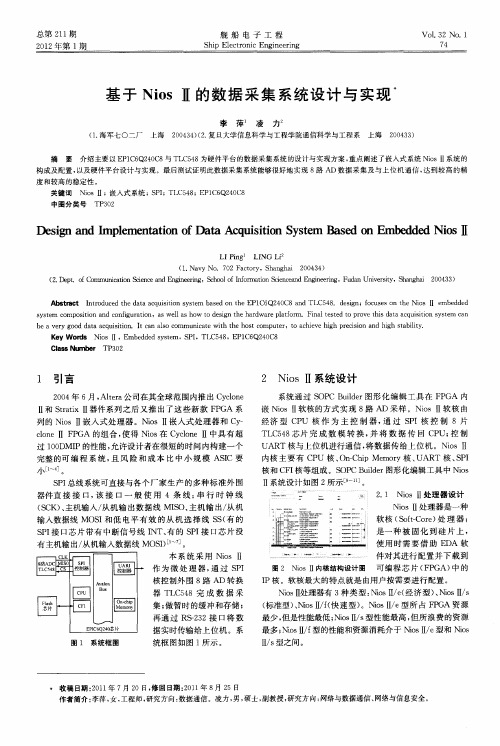

介绍主要 以E 1 6 4 C P C Q2 0 8与 TI 5 8为硬件平 台的数据采集系统 的设计与实现方案 , 4 C 重点阐述 了嵌入式系统 NisI系统 的 o I

构成及配置 , 以及硬件平台设计 与实现 。最后测试证明此数据采集系统能够很好地实 现 8路 AD数 据采集及与上位机通 信, 达到较高 的精

度 和较 高 的稳 定 性 。 关键词 Nis1 嵌 入 式 系 统 ; P ;T 5 8 P C6 4 C o 1; S I I 4 ;E I Q2 0 8 C T 32 P 0 中 图分 类 号

K yWod Nis1 e rs o I,E e ddsse , P , C 4 , P1 6 4 C mb d e ytm S I TL 5 8 E C Q2 O 8

Cls m b TP3 a s Nu er 02

1 引言

2 0 年 6 , tr 公司在其全球范围 内推 出 C c n 04 月 Al a e yl e o Ⅱ和 Srt 器 件系列之后 又推 出了这些 新款 F GA 系 tai 1 x1 P

( . p o mmu iainSc nc n n iern ,S h o fIf mmt n S in en gn eig,Fu a iest ,S a g a 2 0 3 2 De L fCo ncto i ea d E gn eig c o l n o e o i e ca dEn ie r o c n dn Unvriy h n h i 0 4 3)

小 ~ 。

核和C I F 核等组成 。S CB i e 图形化编辑工具 中 Nis OP ul r d o Ⅱ系统设计如 图 2所示[ 1 。 9 1  ̄]

基于NiosⅡ自定制Avalon设备的设计与实现

( 西南交通大学电气工程学 院, 四川 成都 6 03 ) 10 1

摘 要 : Nol系统的构建过程 中,O C B i e 开发环境集成 了许多常用类型 的设备模型, 在 is I S P udr l 供开发者调用 。而对 于其 他的一些设备可 以按照 A a n总线规范将设备驱动程序集成到 S P u d r vo l O C B i e 的硬件抽象层中 , l 同样可以加载 使用 , 方便 了用户开发一个 自定制 的片上 系统 。本文通 过在 Nol系统 内部集成一个 F i I s - C总线 控制器详细说明了 自 定制 A a n设备 的设计方法 , vl o 并通过行为仿真和系统测试验证 了方法的可行性。

c n e in l .T i p p r e p u d d h e o v ne t y b s a e x o n e t me o f d s n n a h t d o e i i g Us r De n d v o e ie hr u h n e r t g a g e - f e A a n d vc t o s i tg ai i l n

维普资讯

第 0 7年 7 3 3 20卷第 H O DG HN E S R M N E N 【 Y U E E TTC

V 13 N . 03 o4 .

J l.0 7 uy2 0

基 于 No 自定 制 A a n设备的设计与实现 isI 1 vl o

fr d v lp r o s .Bu f r 0l r d vc s te r e h u d e n e r td no ad a e b t c l y r f he o e eo e t u e t o t e e ie . h d v r s o l b i tg ae i t h r w r a s a t a e o t l i r S C Bul e c o d n t ao u n r .I s a b o d d n ma e e eo i g a ¥ r De n d S OP i r a c r i g o Av n b s o ms t a o C d l l n e l a e a d k d v l p n U e — f e OC i

Avalon总线规范

Avalon总线规范1 A valon总线基本从端口读传输时序2 A valon总线基本从端口写传输时序3 A valon总线上的基本主端口读传输时序4 A valon总线上的基本主端口写传输时序Nios采用的Avalon总线是一种相对简单的总线结构,主要用于连接片内处理器和外设,以构成可编程单芯片上系统。

它描述了主从构件间的端口连接关系,以及构件间通信的时序关系。

Avalon总线拥有多种传输模式,以适应不同外设的要求。

它的基本传输模式是在一个主外设和一个从外设之间进行单字节、半字或字(8、16或32位)的传输,每次只传送一个单元的数据。

当一次传输结束后,不论新的传输过程是否还在同样的外设间进行,Avalon总线总是可以在下一个时钟周期立即开始另一次传输。

所有Avalon从传输的信号时序都源自从端口的基本传输模式,同样,主端口的基本传输模式是所有Avalon主传输的基础。

Avalon总线的端口分为主端口和从端口。

主端口是主外设用于在Avalon总线上发起传输的一组信号。

从端口是用于接受来自另一个Avalon外设主端口的总线传输的一组信号,主端口和从端口都直接连接到Avalon总线模块上。

Avalon总线规范定义了主端口和从端口之间通过Avalon总线模块传输数据所需的信号和时序。

构成Avalon总线模块和外设之间接口的信号随着传输模式的不同而不同。

Avalon总线规范提供了各种选项来剪裁总线信号和时序,以满足不同类型外设的需要。

1 Avalon总线基本从端口读传输时序基本从端口传输模式是所有Avalon从端口传输的基础。

所有其他的从端口传输使用的信号都包含了基本从端口传输的信号,并扩展了基本从端口的操作时序。

基本从端口传输由Avalon总线模块发起,然后从端口向Avalon总线模块传输一个单元的数据。

基本从端口读传输没有延迟。

在clk的第一个上升沿,Avalon总线向目标外设传递address、byteenable_n 和read_n信号。

第四讲NIOS微处理器与Avalon总线

§4.5 Avalon总线简介

Avalon 总线

Avalon总线由ALTERA公司提出,用于在基于 FPGA的片上系统中连接片内处理器和片内外设的总 线结构。 连接到Avalon总线的设备分为主从设备, 并各有其工作模式。

Avalon 总 线 本 身 是 一 个 数 字 逻 辑 系 统 , 它 在 实 现 “信号线汇接”这一传统总线功能的同时,增加了 许多内部功能模块,引用了很多新的方法,比如从 端仲裁模式,多主端工作方式,延时数据传输,这 些功能使得在可编程逻辑器件中可以灵活的实现系 统增减和IP复用。

§4.4 SOPC Builder的设计流程

§4.4 SOPC Builder的设计流程

(c)配置JTAG调试模块

JTAG调试模块可以完成系统的下载,程序的调试, 还可以当成一个普通的UART设备使用。在开发阶段 是必不可少的模块。JTAG调试模块分为4级,第4级 需要第三方公司的硬件调试器支持。

对每个设备,系统会自动分配设备名称,地址和中断,用户也可以自己指定设备名称, 地址和中断优先级。对于存储设备,用户还可以锁定地址。

§4.4 SOPC Builder的设计流程

§4.4 SOPC Builder的设计流程

(e)配置reset地址和exception地址

reset地址一般设为非易失性存储器地址,exception地址一般设为主存储器设备的地址。

(3)简而言之,可以这样认为,总线就是一种通信规 范以及规范的实现方法,不论是计算机系统还是通信 领域。

§4.5 Avalon总线简介

计算机总线的分类:

(1)按相对于CPU或其它芯片的位置可分为:片内总线、片外总线 ; (2)按总线的功能可分为:地址总线、数据总线、控制总线 ; (3)按总线的层次结构可分为:

一种基于AVALON总线的VGA控制器的设计与实现

G、 B各用 一个 bt 本 系统 每 色 4 bt 来 控 制 , i( i) 即只 有 0 1两种 电平 , 、 则所 能形成 的颜 色种 类 只有 8种 。

若每 一种颜 色 能 用 多 个 bt 分 出不 同 的 电 流 值 , i来

1 A A O V L N总线概述

A a n 换 式 总线 并 立 于 A A、 vl 交 o MB WB等 三

片上 系统 ) A T R 是 L E A公 司提 出 的一 种 灵 活 、 高效 的 S C解 决 方 案 。 在 N O O I S开 发 的 过 程 中 , 现 发

SP O C中 的 V A I G P核不适 合 项 目应 用 , 故根 据 需要

设计 了一 个 V A控制 器 。基 本 原理 是 用 系统 R M G A 作 为 V A控制 器 的显 存 , P G C U只要 把数 据按 位 图的 格 式放 到指定 的 R AM 区域就 能在 V A显示 器上显 G 示 出来 。一般 的 V A控 制器要 使用 D A 和 中断控 G M 制, 或者采 用流模 式 , 由 C U协 调管 理 , 并 P 占用 硬件

Байду номын сангаас

⑥

2 1 S i eh E gg 0 0 c T c. nn . .

一

种基于 A A O V L N总 线 的 V A G 控 制 器 的设 计 与 实 现

郭 小清 谢 忠红

( 京 农 业 大 学 计算 机 科 学 与 技 术 系 , 京 20 9 ) 南 南 10 5

摘

要

描述 了一个基于 A A O V L N片上 总线 的 V A控制器的设计与实现, G 着重介绍 了设计与调试过程。此控制器基于 A a v.

一种多核远程重构控制器的设计与实现

一种多核远程重构控制器的设计与实现朱丹;王家宁;朱玙骅【摘要】利用可编程片上系统构建多任务远程可重构控制器.控制器运用非对称多核架构、片上双RAM通信区、多任务相互监控、扩展TFTP服务器等方法,保证控制任务的实时性,实现硬软件的远程重构和故障的自主恢复.基于NIOS Ⅱ,论述系统设计的总体思路和实现方法,在实际的控制系统中进行验证,取得了良好的结果.%This paper constitutes a multi-task remote reconfigurable field controller based on SOPC technology.By using the methods of asymmetric multi-core architecture, on-chip dual RAM communications areas, mutual monitor between multi-tasks and extended TFTP server, the controller ensures the operation of real-time tasks.The controller also achieves remote reconfiguration of hardware and software and failure self-recovery.It describes the overall design and implementaOon method of this multi-core reconfigurable controller based on NIOS II.It has been verified in the actual control system and very good results are obtained.【期刊名称】《计算机工程》【年(卷),期】2011(037)009【总页数】3页(P254-256)【关键词】可编程片上系统;NIOSⅡ软核;多核控制器;故障恢复【作者】朱丹;王家宁;朱玙骅【作者单位】南京邮电大学计算机学院,南京,210003;中国科学院国家天文台南京天文光学技术研究所,南京,210042;南京邮电大学通信与信息工程学院,南京,210003【正文语种】中文【中图分类】TP3911 概述在控制点多、分布范围广的大型控制系统中,主控计算机加现场控制器的分布式控制方案已被广泛应用。

NIOS软件设计流程和方法

NIOS软件设计流程和方法1软件开发包NIOS嵌入式处理器是经过专门优化过的软核CPU,以便于在可编程逻辑器件上实现SOPC设计。

Altera。

公司提供SOPC Buildei。

系统开发工具,来帮助用户创建采用NIOS处理器的软硬件系统:硬件设计师利用SOPC Builder构建软硬件开发的基础,SOPC Builder的生成结果将作为特定用户设计的开发软件的起点。

当SOPC Builder生成一个NIOS处理器设计时,会完成以下工作:1.系统存储器映像的一致性检查。

对外设地址和中断优先级进行惟一性验证,检查其是否在CPU的有效访问范围之内。

如果不是,报告相应的错误,并在继续下一步以前修正。

2.为NIOS系统生成一个定制的软件开发包(Soflw~e Development Kit,SDK)。

3.生成NIOS处理器系统的硬件设计文件。

硬件设计师可以用这些文件来创建NIOS系统硬件。

1.1软件开发流程在进行NIOS软件开发时,通常按照下面的过程进行。

步骤1:获得目标N10S系统的SDK从SOPC Builder创建的工程目录中(或从负责NIOS处理器硬件系统的设计师那里)得到目标NIOS处理器系统的SD K。

软件开发环境的基础是由SOPC Builder生成的SDK目录。

SDK中包含的头文件和库文件,提供了硬件映像地址和一些基本的硬件访问子程序,有效地减少了原有分工模式下的软硬件衔接工作。

步骤2:建立和编译应用软件首先使用文本编辑器,用C/C++或汇编语言编写应用程序的源代码(.c或.s);然后使用nios-build命令或Makef ile将源代码编译成可执行代码。

编译产生的二进制码以S-record的格式(.sere)存储。

对于一个小型或中型的软件项目,使用nios-build就可以编译生成可执行代码:对于一个大型项目,则必须参照由SOPC Builder生成的示例Makefi le编写自己的Makefile,来编译生成可执行代码。

基于AVALON总线的光电编码器计数模块的定制

G E L AI P D等可 编程 器 件 的 基础 上 进 一 步 发展 的 、 产物 。F GA 的使 用 非 常灵 活 , P 同一 片 F GA 通过 P 不 同的编程 数据可 以产 生不 同的 电路功 能 , 通信 、 在 数据处理 、 网络 、 器 、 仪 工业 控制 、 事和航 空航 天等 军

众多领域 得 到了广 泛应用 。

ln Me r Ma p d n efc (简 称 Av ln o moy p e I trae ao - MM ) Av ln MM 是 内存 映 射 系统 下 的用 于主 从 , ao —

设 备之 间的读写 接 口。

Av lnMM 接 口有 很 多特点 , 中最大 的特 点 a — o 其

W a g Yo g n ,Li mig,L u Ya b ,S n Ya mig n n mi g i Jn n i n o u n n

( a g h nRee rh I siuef rMe h n c lS in eC . Ch n c u sa c n tt t o c a ia ce c o ,Lt .C a g’u 3 0 2 d h n ( n 1 0 1 ,Jii ,C i a h ln h n )

元 件 。光 电 编 码 器 是 工 业 控 制 常 用 的 部 件 , 来 位 用 置测 量和控 制 , 的数 据 采集 电路 包 括鉴 向 、 频 、 它 倍 计 数 部 分 。 本 文 介 绍 基 于 NI OSI I的 AVAI ON 总 线 的光电编码 器模 块 的定 制 过程 , 模 块 能 够很 方 该

就 是 根 据 自己 的需 求 自 由选 择 信 号 线 。

NI 是一 个建 立在 F G 上 的嵌入 式 软核 OS 1 P A

Avalon总线SHT11的自定义IP核的开发

术 。 S C 是 可 编 程 逻 辑 器 件 技 术 和 S C( y tm n OP o S se o

C i) 术 发 展 与融 合 的产 物 。 hp 技 S C的 关 键 技 术 之 一 就 是 I OP P核 , 就 是 知 识 产 权 也 核 。所 谓 的 I P核 就 是 指 将 一 些 比较 复 杂 的 功 能 模 块 , 如

d c d. Thi P c e a op s t e t d s a e m a hi c o dng t h vc o r l rs e iia i n h i ig r qu s ,t n a m ue s I or d t he n s e t t c ne a c r i ot e de iec ntole p cfc ton a d t e tm n e e t he n e

Absr c :T h sa tce b ify d s rbe h ta t i ril re l e c i st e SOPC nd A v l a aon bus The d v l m e o e soft . e eop ntpr c s he SH T 1 usom ie P o e i nto c t l z d I c r s i r —

个 典 型 从 端 口包 含 的 信 号 如 表 1所 列 。

表 1 Av ln从 端 口 信 号 ao

信 号 类 型 宽

c

音 频 编 / 码 、 DRAM 等 , 计 成 可 以 修 改 参 数 的模 块 , 解 S 设

b d d s s e o hi as d o o l s bul. CPU e dsa ie e de y t m n c p b e n Ni s Ii it r a nd wrt sSH T1】 t r u h P o e I hegr e ou eofa iulu e,t h o gh t e I c r . n t e nh s grc t r he s s e a c a y i e iid Thec t ie P or c n s r e t e d v l pme c l nd e c he wor oa y t m c ur c s v rfe . usom z d I c e a ho t n h e e o nt yce a r du e t kl d whe t r us r u e n o he e s s

基于Niosll步进电机控制器IP核的设计与实现

性进行 S C设计 , O 其最突出优点是在提供丰富 I P库的 情况下 , 用户可以利用 I P库中的组件按需求来搭建系 统, 有较 大 的灵 活性 。但 是 在供应 商 提供 的 I 中没 P库 有 用户 所需 的 I P核 时 , 户 只 能 根 据 需 要 自定 义 I 用 P

核 。另 外 ,P A 的传统 应用 是 在 通 信 、 业 控 制等 领 FG 工 域 。鉴 于此 , 设计 了一 款 步 进 电机 控 制 器 I P核 , 具 它 有 对步 进 电机 的转 速 、 向及 运 转节 拍 数 进 行 控制 的 转

摘 要

22 5 ) 5 09

根 据 N o I 处理 器 的 A a n总 线规 范 ,设 计 了 一款 面 向 步 进 电机 的 控 制 器 I 。 该 定制 I 采 用软 、 i I s vl o P核 P核

硬件协 同设计 的方法,功 能符合 A a n总线的读 写传输 时序 ,具有 完备的 步进 电机驱 动能 力。仿 真结果 表明 ,该 I vo l P

叶技 21 第2卷 1期 0 年 4 第0 1

Elcr n c S i & Te h /Oc . 5. 201 e to i c . c. t1 1

基 于 No 步 进 电机 控 制 器 I 的 设 计 与 实 现 i l sl P核

刘 洪朋 ,葛广 英

( 聊城大学 物理科学与信息工程学 院,山东 聊城

功能。

2 步 进 电机 控 制器 J 设 is I I P核 包

设备 I P核和主设备 I P核两大类。文中设计 的步进 电 机控制器 I P核是一个受控对象 , 属于从设备 。No I i sI

处理 器通过 A a n总线 对 步 进 电机 控 制 器 I 的 寄 vl o P核 存器 进行 参 数 设 置 , 现 对 步 进 电 机 的 一 系 列 操 作 。 实

nios2移植uClinux硬件架构

niosII 硬件架构在开始之前,我总是想多说点,因为看了很多的教程,中间也很辛酸,要达到无师自通的境界,在这种领域有些困难,每每遇到问题,总是喜欢百度一下,当找不到符合自己的情况的时候才是最头疼的时候,我们有点懒,有点想走捷径~~~做做笔记,同时也做做教程,在摩尔定律走不下去的时候,我们就会想起FPGA,我们乐此不疲,因为前途无量,当我们轻车熟路,请不要忘了给我们经验的前辈,同时有好的经验的时候,写写教程,小则帮助一二像我们一样的人,大则为中国的科技兴国做做贡献,无所求,只为心里踏实。

这个教程分两部分,一个是硬件架构,另一个是软件架构,不免会有错误,希望指正,所需硬件要求:cpu包含硬件乘法器,timer,串口,至少8M SDRAMusb blaster , pc一台所需软件要求:此番硬件架构大体分为以下内容:1.建立quartusII 工程。

2.利用sopc 工具搭建niosII软核处理器。

3.建立锁相环。

4.编译工程,分配引脚,重新编译。

5.提取所需的ptf文件。

1.建立工程:选择File -> New Project Wizard...会点英文的,或者是用过别的软件的都会知道,wizard是向导的意思,我们就喜欢向导,因为它会给我们剩下很多工作。

这个不用管它,点next,向下。

这个对话框就有用啦,看第一行,翻译过来就是你要把工程放到哪个文件夹下,然后点"..."选吧,选择你要放的位置,但是我要提醒一点就是,因为这是个外国人用的软件,它的路径里不能有中文,否则当你用niosII IDE软件的时候会有莫名奇妙的错误,这个就是我的经验,免费告诉大家啦。

我设置的路径是D:\quartus_pro\uclinux_nios2,然后点击:打开。

看第二个框。

工程名字,这次的有点特殊了,我们要同时看看第三个框了,第三个是顶层实体的名字,如果知道硬件描述语言,那么肯定会明白我说的意思,这里的工程名字必须和顶层实体的名字相同,我在工程名字填上uclinux_nios2。

基于NiosII的片上可编程系统_SOPC_实现的直流电机的PWM调速系统

基于Nios II的片上可编程系统(SOPC)实现的直流电机的PWM调速系统朱科星,郁建平(东南大学机械工程学院,江苏南京211189)摘 要:介绍了一种基于Nios II软核处理器的直流电机PWM调速系统,并以此说明了SOPC思想及其实现途径。

该系统以一片PF G A为核心,结构紧凑,体现了SOPC系统集成度高、灵活性强、扩展性好的特点。

并且能大大缩短产品的开发周期。

关键词:现场可编程逻辑门阵列(FPG A);片上可编程系统(SOPC);Nios II;脉宽调制(PWM);直流电机中图分类号:TM33;TP273+5 文献标识码:B 文章编号:167125276(2007)0120113203PWM R egulating Speed System of DC Motor B ased on SOPC of Nios IIZHU K e2xing,YU Jian2ping(College of Mechenical Engineering,S outheast University,Nanjing211189,China)Abstract:This paper introduces a kind of s peed regulation for DC mortor based on the soft CPU core named Nios II,and then il2 luminates the thinking and method of SOPC.A piece of FPG A is the core of the system,simple and compact,showsing high in2 tegration,flexibility,expandability of SOPC and reduction of the time of develo pment of product.K ey w ords:SOPC;Nios II;PWM;DC motor0 引言SOPC是电子设计自动化EDA(electronics design au2tomation)技术和大规模集成电路技术高度发展的产物。

niosii课程设计

niosii课程设计一、教学目标本课程旨在通过NIOS II软核处理器的教学,让学生掌握嵌入式系统的基本概念、软硬件协同设计的方法,以及基于NIOS II处理器的设计和实现。

具体目标如下:1.理解嵌入式系统的基本概念、特点和应用。

2.掌握NIOS II处理器的基本结构、工作原理和指令系统。

3.熟悉软硬件协同设计的基本方法,包括硬件描述语言(HDL)和软件编程。

4.能够使用NIOS II处理器进行简单的嵌入式系统设计和实现。

5.能够独立完成NIOS II处理器的硬件设计和软件编程。

6.能够对NIOS II处理器的设计进行优化和调试。

情感态度价值观目标:1.培养学生的创新意识和团队协作精神。

2.增强学生对嵌入式系统领域的兴趣和热情。

3.培养学生对我国嵌入式产业发展的关注和支持。

二、教学内容本课程的教学内容主要包括以下几个部分:1.嵌入式系统概述:嵌入式系统的定义、特点、应用和发展趋势。

2.NIOS II处理器:基本结构、工作原理、指令系统、寄存器文件和数据通路。

3.软硬件协同设计:硬件描述语言(HDL)的基本概念和应用,软件编程基础。

4.NIOS II处理器设计:硬件设计和软件编程,设计优化和调试方法。

5.案例分析:分析实际应用中的嵌入式系统设计,了解行业动态和发展趋势。

三、教学方法本课程采用多种教学方法,以激发学生的学习兴趣和主动性:1.讲授法:讲解基本概念、原理和方法,确保学生掌握基础知识。

2.案例分析法:分析实际应用案例,让学生了解嵌入式系统的实际应用和发展趋势。

3.讨论法:学生进行小组讨论,培养学生的团队协作能力和创新意识。

4.实验法:动手实践,让学生亲自设计并实现NIOS II处理器 based的嵌入式系统。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:《NIOS II嵌入式系统设计与实践》。

2.参考书:提供相关领域的经典教材和论文,以便学生深入研究。

3.多媒体资料:制作课件、视频等教学资料,以便学生更好地理解和掌握知识。

基于NIOSⅡ的嵌入式云发生器电路设计

成拟人控制 的智能控制 方法 , 在三级倒立摆的控制 I数据挖掘 、 、 数字水印技术等研究方向得 到重要应用 。 I

通过 云 模 型 建 立某 个 定 性 概 念 与 其定 量表 示 之 间 的不 确 定 性

转换关 系, 而这种不确定性关系可以仅用三个数来表示 , 使一条语 言描述 的定性规则 可以通过云发生器输 出定量 的控制参数,以实 现拟人化 的智能控制。先验知识与逆向云发生器是获得云模型参 数的必要条件和方式,正 向云发生器则是规则转化为控制 参数 的

1 引 言

隶 属 云 和 隶 属 云发 生器 ” 提供 了一 种 以语 言 值 构成 规则 . I 形

和超 熵 所 示 。 望 期

三个 是云

数值 表示 , 如 图 1 滴 在 论 域 空 间 分 布 的 期 望 , 是 最 能 够 代 表 定 性 概 念 的

点 , 反 映 了 云 的重

维普资讯

《 气自 化 2 7 第2卷第3 电 动 } 0年 9 0 期

应 用 电路 设 计

垒 巳皇 ! ! 皇 ! 巳 !g ! 曼 璺 旦

基于 N l l的嵌入式 云发 生器 电路设计 I OS

Ci utDe in o r i c sg fEmb d e o d Ge e a o s d on NI IPr c s o e d d Clu n r t rBa e OS I o e s r

摘

要: 提出基 于 N O I ISI处理器系统 在 目标 电路板的 F G P A中实现嵌入式云发生器的设计方法 。 将定制处理器 系统加入硬件设计实体, 生成硬件配置文件, 编写调试云发生器代码, 生成软件配置文件 , 再利用二者生成最终 的配置文件 并下载到 F G P A配置芯片中, 实现嵌入式云发生器, 具有接 口灵活, 扩展性强, 低功耗, 高性 能, 低成本 等优点 。

基于NiosⅡ多核智能交通车载终端的设计与实现

( 1 . 西安 邮 电 大 学 计 算 机 学 院 ,陕西 西 安 7 1 0 1 2 1 ; 2 . 西 安 邮 电大 学 电 子 工程 学 院 ,陕 西 西安 7 1 0 1 2 1 ;

3 . 广 州 致远 电子 有 限公 司 广 东 广 州 5 1 0 6 6 0 ) 摘 要 :利 用 N i o s l I多核 处 理 器 , 提 出 了基 于 I n t e r n e t 的 实 时路 况 查 询 系统 和 智 能 车 栽 终 端 。通 过 配 置 双 N i o s l l 软核 ,

3 . G u ng a z h o u Z h i Y u n a E l e c t r o n c i s C o m p ny a L i m i t e d , G u a n g z h o u 5 1 0 6 6 0 , C h i n a )

Ab s t r a c t :Us i n g Ni o s I I mu l t i - c o r e p r o c e s s o r , b a s e d o n t h e I n t e r n e t r e a l - t i me t r a f f i c q u e r y s y s t e m a n d i n t e l l i g e n t t e r mi n a 1 . T h r o u g h t h e c o n f i g u r a t i o n o f d o u b l e N i o s I I c o r e , MC U i mp r o v e d t h e p r o c e s s i n g s p e e d i s n o t h i g h ,l i mi t e d r e s o u r c e s , p e i r p h e r a l i n t e r f a c e c o n i f g u r a t i o n i s c o mp l i c a t e d ,h a r d wa r e d e s i g n a n d s o f t w a r e p r o g r a mmi n g o f c o mp l e x i s s u e s , a c o n t r o l a n d a v a i r e t y o f p e ip r h e r a l a c c e s s wo r k a l l o c a t i o n . No t o n l y h a s t h e o r d i n a r y n a v i g a t i o n e q u i p me n t i s c o n v e n i e n t a n d p r a c t i c a l ,b u t a l s o t h r o u g h t h e wi r e l e s s c o mmu n i c a t i o n a n d I n t e r n e t a n d b a c k ro g u n d s e r v e r ,a c c e s s r o a d c o n g e s t i o n ,p a r k i n g a n d r e a l — t i me d y n a mi c i n f o ma r t i o n ,a t t h e s a me t i me a s t h e i n t e l l i g e n t t r a f i c v e h i c l e f r o n t e n d . Ke y wo r d s :i n t e l l i g e n t t e mi r n a l ;d o u b l e Ni o s I I s o f t c o r e ;r o a d c o n g e s t i o n;i n t e l l i g e n t t r a n s p o r t a t i o n

Avalon总线与自定义外设

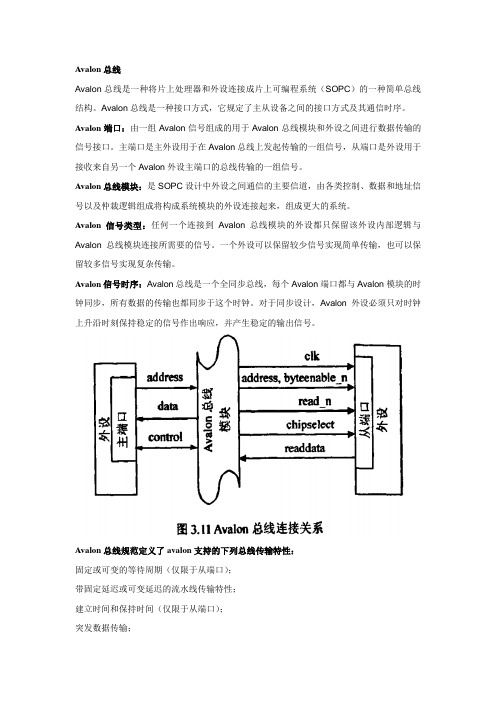

Avalon 总线是一种将片上处理器和外设连接成片上可编程系统(SOPC)的一种简单总线结构。

Avalon总线是一种接口方式,它规定了主从设备之间的接口方式及其通信时序。

Avalon端口:由一组Avalon信号组成的用于Avalon总线模块和外设之间进行数据传输的信号接口。

主端口是主外设用于在Avalon总线上发起传输的一组信号,从端口是外设用于接收来自另一个Avalon外设主端口的总线传输的一组信号。

Avalon总线模块:是SOPC设计中外设之间通信的主要信道,由各类控制、数据和地址信号以及仲裁逻辑组成将构成系统模块的外设连接起来,组成更大的系统。

Avalon信号类型:任何一个连接到Avalon总线模块的外设都只保留该外设内部逻辑与Avalon总线模块连接所需要的信号。

一个外设可以保留较少信号实现简单传输,也可以保留较多信号实现复杂传输。

Avalon信号时序:Avalon总线是一个全同步总线,每个Avalon端口都与Avalon模块的时钟同步,所有数据的传输也都同步于这个时钟。

对于同步设计,Avalon外设必须只对时钟上升沿时刻保持稳定的信号作出响应,并产生稳定的输出信号。

Avalon总线规范定义了avalon支持的下列总线传输特性:固定或可变的等待周期(仅限于从端口);带固定延迟或可变延迟的流水线传输特性;建立时间和保持时间(仅限于从端口);突发数据传输;三态。

Avalon基本传输:对于从端口基本传输:(1)无等待周期的基本从端口读传输只适用于完全异步的从外设,从外设必须在被选中或者地址变化时立即向Avalon总线模块提供数据。

锁存输入或输出端口的同步外设不能用无等待周期的基本从端口读传输。

(2)理想情况下,基本从端口传输的最大数据吞吐量是每个总线时钟周期传送一个数据单元,插入n个等待周期后,变为每n 个周期传输一个数据单元。

具有单个等待周期的读传输一般用于片上的同步外设,使外设具有至少一个完整总线周期向Avalon模块提供返回数据。

Avalon总线规范(中文版)

Avalon总线规范参考手册(Avalon从端口传输与流模式从端口传输部分)Avalon 总线是一种将片上处理器和外设连接成片上可编程系统(SOPC)的一种简单总线结构。

Avalon总线是一种接口方式,它规定了主从设备之间的接口方式及其通信时序。

Avalon 总线的设计目的在于:■简便:提供了简单易学的协议;■优化总线逻辑的资源利用:节约了可编程器件(PLD)内部的逻辑单元(LE);■同步操作:将PLD 上的其他用户逻辑很好的集成在一起,从而避免了复杂的时序分析;基本的Avalon 总线事务可以在主﹑从设备之间传送一个字节,半字或字(8,16 或32 位)。

当一次事务处理完成,总线可以迅速的在下一个时钟到来的时候在相同的主从设备之间或其他的主从设备间开始新的事务。

Avalon 总线也支持一些高级功能,如“延迟型(latency-aware)外设”,“流(streaming)外设”及多总线主设备。

这些高级的功能使其允许在一个总线事务中进行外设间的多数据单元的传输。

Avalon 总线支持多个总线主设备。

多主设备的结构为SOPC 系统及高带宽外设提供了很大程度上的稳定性。

例如,一个主外设可以进行直接存储器访问(DMA),而不需要处理器在数据传输路径上从外设将数据读入存储器。

Avalon 总线上,主设备和从设备之间的相互作用是基于一种被称为“从设备(slave-side)仲裁”的技术。

从设备仲裁决定了当多主设备在同一时刻尝试连接同一个从设备的时候,哪个主设备获得从设备控制权。

从设备仲裁具有两个优势:1.仲裁细节内嵌于Avalon 总线内部。

所以,主设备和从设备的接口具有一致性,不考虑总线上的主设备和从设备的数量。

在每一个和Avalon 总线相连接的主设备看来,它都是总线上唯一的主设备。

2.多个主设备可以同时完成总线事务,就像他们并不是在同一个总线周期连接到同一个从设备一样。

Avalon总线的设计是为了配合片上可编程系统(SOPC)的。

A200805-1035

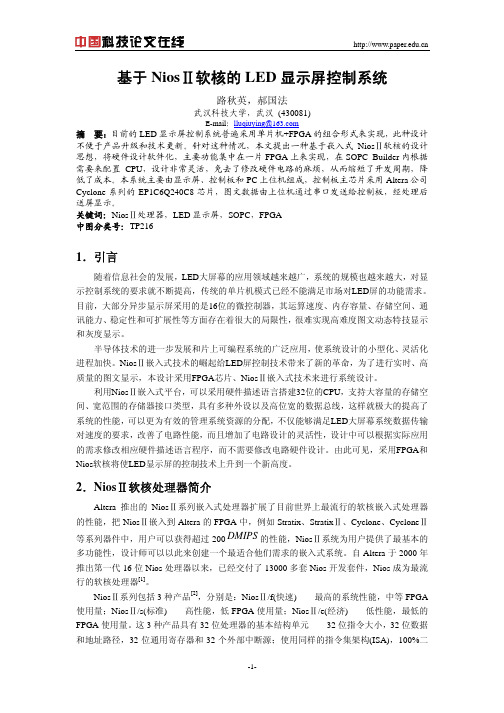

基于NiosⅡ软核的LED显示屏控制系统路秋英,郝国法武汉科技大学,武汉 (430081)E-mail:lluqiuying@摘要:目前的LED显示屏控制系统普遍采用单片机+FPGA的组合形式来实现,此种设计不便于产品升级和技术更新。

针对这种情况,本文提出一种基于嵌入式NiosⅡ软核的设计思想,将硬件设计软件化,主要功能集中在一片FPGA上来实现,在SOPC Builder内根据需要来配置CPU,设计非常灵活,免去了修改硬件电路的麻烦,从而缩短了开发周期,降低了成本。

本系统主要由显示屏、控制板和PC上位机组成,控制板主芯片采用Altera公司Cyclone系列的EP1C6Q240C8芯片,图文数据由上位机通过串口发送给控制板,经处理后送屏显示。

关键词:NiosⅡ处理器,LED显示屏,SOPC,FPGA中图分类号:TP2161.引言随着信息社会的发展,LED大屏幕的应用领域越来越广,系统的规模也越来越大,对显示控制系统的要求就不断提高,传统的单片机模式已经不能满足市场对LED屏的功能需求。

目前,大部分异步显示屏采用的是16位的微控制器,其运算速度、内存容量、存储空间、通讯能力、稳定性和可扩展性等方面存在着很大的局限性,很难实现高难度图文动态特技显示和灰度显示。

半导体技术的进一步发展和片上可编程系统的广泛应用,使系统设计的小型化、灵活化进程加快。

NiosⅡ嵌入式技术的崛起给LED屏控制技术带来了新的革命,为了进行实时、高质量的图文显示,本设计采用FPGA芯片、NiosⅡ嵌入式技术来进行系统设计。

利用NiosⅡ嵌入式平台,可以采用硬件描述语言搭建32位的CPU,支持大容量的存储空间、宽范围的存储器接口类型,具有多种外设以及高位宽的数据总线,这样就极大的提高了系统的性能,可以更为有效的管理系统资源的分配,不仅能够满足LED大屏幕系统数据传输对速度的要求,改善了电路性能,而且增加了电路设计的灵活性,设计中可以根据实际应用的需求修改相应硬件描述语言程序,而不需要修改电路硬件设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

随着电子技术的发展, 促使集成电路向高速、 高集成度, 低功耗的系统集成方向发展 , SOPC 是现 代电子技术和电子系统设计的聚焦点和发展方向。 Altera 公司开发的基于 SOPC( System on a Program mable Chip) 技术的 NiosⅡ嵌入式处理器是一个可 变结构的、通用型的 RISC 嵌入式处理器。嵌入式设 计者能容 易 地 使 用 SOPC Builder 系 统 开 发 工 具 产 生以处理器为基础的系统。

( 0)

//定义分频器高字节寄存器 #define IORD_AVALON_I2C_PRERH( base) IORD( base, 1) #define IOWR_AVALON_I2C_PRERH( base, data) IOWR( base, 1, data) #define ALTERA_AVALON_I2C_PRERH_MSK ( 0xFFFFFFFF) #define ALTERA_AVALON_I2C_PRERH_OFST ( 0) …… 2.2.2 函数声明文件 Avalon_I2C_routines.h 文件用于声明 I2C 控制器 的功能函数: Void Altera_avalon_I2C_Init ( void) ; //初 始 化 函 数 Unsigned char Altera_avalon_I2C_Read( void) ; // 总线读操作函数 Void Altera_avalon_I2C_Write ( unsigned char Txdata) ; //总线写操作函数 Void Altera_avalon_I2C_Start ( unsigned char slave_address) ; //I2C 启动函数 Void Altera_avalon_I2C_Acknowlegde( void) ; //等待应答函数 Viod Altera_avalon_I2C_stop( void) ; //I2C 停止函 数 2.2.3 功能函数文件 Avalon_I2C_routines.c 文件用于定义 I2C 控制器 的功能函数, 以 I2C 总线启动函数为例简要说明编 写方法。 void Altera_avalon_I2C_Start ( unsigned char slave_address) { do { IOWR_AVALON_I2C_ctr ( slave_address +ctr, core_en) ; //使能 I2C 控制器内核 IOWR_AVALON_I2C_cr ( slave_address +Txr, ( Slaver_address<<1) |write) ; //设 置 从 设 备 地 址 以 及 数据传输方向 IOWR_AVALON_I2C_txr ( slave_address +CR, STA|WR) ; //开始总线传输, 总线活动为写操作 while( ( IORD_AVALON_I2C_sr( slave_address + SR) &&TIP) =0) ; //检测数据是否传输完毕 } }

于其他的一些设备可以按照 Avalon 总线规范将设备驱动程序集成到 SOPC Builder 的硬件抽象层中, 同样可以 加 载

使用, 方便了用户开发一个自定制的片上系统。本文通过在 NiosII 系统内部集成一个 I2C 总线控制器详细说明了自

定制 Avalon 设备的设计方法, 并通过行为仿真和系统测试验证了方法的可行性。

106

中国测试技术

2007 年 7 月

用户程序

C 标准库

HAL 用户接口函数

设备驱动程序

系统硬件

图 1 HAL 系统的基本结构

1.3 Avalon 总线 不同于其他 微处理器的 固定外 设 , NiosⅡ的 外

设是可以任意定制的。这使得用户可以根据具体的 应用需求而定制。所有的 NiosⅡ系统外设都是通过 Avalon 总线与 Nios 软核相连, 从而进行数据交换。 因此对于用户定义的外设必须遵从该总线协议才 可与 Nios 之间建立联系。 1.4 NiosⅡ IDE

GAO Feng, WANG Yu- song ( College of Electrical Engineering, Southwest Jiaotong University, Chengdu 610031, China)

Abstr act: In the development process of the NiosⅡ system, SOPC Builder integrates many generic devices mode for developer to use. But for other devices, the driver should be integrated into hardware abstract layer of the SOPC Builder according to Avalon bus norms. It also can be loaded and make developing a User - Defined SOC conveniently. This paper expounded the method of designing a User - Defined Avalon device through integrating a I2C controller in the NiosⅡ system. The results of behavior simulation and system test demonstrate feasibility. Key wor ds: I2C controller; NiosⅡ; Avalon

关键词: I2C 总线控制器; NiosII; Avalon

中图分类号: TP368.1

文献标识码: A

文章编号: 1672- 4984( 2007) 04- 0105- 04

Design and implementation of user - defined Avalon device on NiosII

据移位模块用于将待发送的数据从发送寄存器中 传输到总线控制模块并由后者发送到总线上, 以及 将接收到的数据从总线控制模块中读出拷贝到接 收寄存器中。

时钟寄存器

时钟模块

Avalon 总线接口

命令寄存器 状态寄存器 发送寄存器 接收寄存器

总线控制 模块

SCL SDA

数据移位 模块

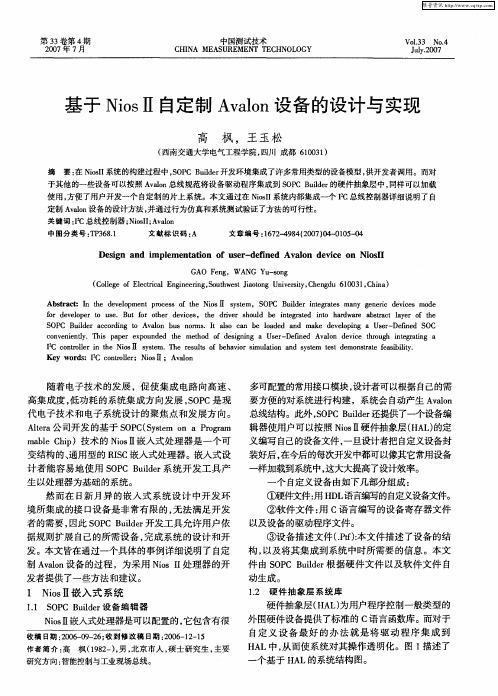

图 2 I2C 总线控制器逻辑结构框图

一个自定义设备由如下几部分组成: ①硬件文件: 用 HDL 语言编写的自定义设备文件。 ②软件文件: 用 C 语言编写的设备寄存器文件 以及设备的驱动程序文件。 ③设备描述文件( .Ptf) :本文件描述了设备的结 构, 以及将其集成到系统中时所需要的信息。本文 件由 SOPC Builder 根 据 硬 件 文 件 以 及 软 件 文 件 自 动生成。 1.2 硬件抽象层系统库 硬件抽象层( HAL) 为用户程序控制一般类型的 外围硬件设备提供了标准的 C 语言函数库。而对于 自定义设备最好的办法就是将驱动程序集成到 HAL 中, 从而使系统对其操作透明化。图 1 描述了 一个基于 HAL 的系统结构图。

如上所述, 设计一个自定义设备需要包括硬件 文 件 、软 件 文 件 以 及 结 构 文 件 。 这 里 所 说 的 硬 件 文 件指的是 HDL 文件, 他由以下几个模块组成:

①逻辑模块: 描述设备的逻辑功能; ②寄存器映射模块: 为内部逻辑模块和 Avalon 总线提供了通信接口; ③Avalon 总线接口模块: 使 Avalon 总线访问寄 存器从而完成相应的逻辑功能。 同样对于自定义的 I2C 总线控制器也是由以上 几部分组成。 2.1.1 逻辑结构 ( 如图 2 所示) 该控制器的逻辑结构由三个模块组成: 时钟模 块用来产生内部时钟使能信号从而触发所有同步 操作; 总线控制模块用于处理实际的总线活动; 数

1

输出

写信号

Avalon_rd_o

1

输出

读信号

Avalon_ship_ce

11

输出

中断信号

2.1.2 特性与硬件仿真 到此为止有关于硬件的设计部分基本完成, 此

控制器具有以下一些特性: 符合 PhilipsI2C 总线的协议; 软件可编程的时钟频率; 软件可编程的应答位; 支持 7 位和 10 位地址模式;

第 33 卷第 4 期

高 枫等: 基于 NiosⅡ自定制 Avalon 设备的设计与实现

107

总线状况检测等。 为 了 检 测 控 制 器 的 逻 辑 功 能 我 们 根 据 Avalon 总线的时序要求编写 TesT Bench 文件对该 模块进 行仿真并通过 Modelsim 软件来检查其时序。仿真波 形如图 3 所示。

结构( 图 1) 编写设备驱动程序。 以 I2C 控制器为例说明 HAL 的文件结构, 如表

3 所示。

表 3 I2C 控制器 HAL 文件结构

文件名

描述

/I2C_SW

软件驱动程序目录

/inc Avalon_Slave_I2C_regs.h

硬件接口文件目录 寄存器头文件

/HAL

硬件抽象层驱动程序目录

Avalon_I2C_routines.h Avalon_I2C_routines.c

然而在日新月异的嵌入式系统设计中开发环 境所集成的接口设备是非常有限的, 无法满足开发 者的需要, 因此 SOPC Builder 开发工具允许用户依 据规则扩展自己的所需设备, 完成系统的设计和开 发。本文皆在通过一个具体的事例详细说明了自定 制 Avalon 设备的过程, 为采用 Nios II 处理器的开 发者提供了一些方法和建议。

表 1 I2C 总线控制器寄存器列表

名称

地址 位宽 R/W

PRERL 0x00

8

RW