Quartus_II设计正弦信号发生器{修}

第二章 QuartusII基本使用方法

为了便于迅速了解SignalTapⅡ的使用方法,本节 以上面设计的信号发生器为例介绍SignalTapⅡ的使 用方法,而后进一步叙述SignalTapⅡ的其他使用方 法。

2.4.1

应用SignalTapII测试singt

2.5

嵌入式锁相环a1tPLL宏功能模块调用

PPCA片内嵌入式锁相环PLL可以与一输入的时钟信号 同步,并以其作为参考信号实现锁相,从而输出一至 多个同步倍频或分频的片内时钟,以供逻辑系统应用。 与直接来自外部的时钟相比,这种片内时钟可以减少 时钟延时和时钟变形,减少片外干扰;还可以改善时 钟的建立时间和保持时间。cyclone系列和Stratix系 列器件中的锁相环能对输入的参考时钟相对于某一输 出时钟同步独立乘以或除以一个因子,并提供任意相 移和输出信号占空比。 2.5.1 2.5.2 建立嵌入式锁相环PLL元件 测试锁相环PLL

2.4

使用嵌入式逻辑分析仪进行实时测试

随着逻辑设计复杂性的不断增加,在计算机上以 软件方式的仿真测试变得更加耗费时间,而不断需 要重复进行的硬件系统的测试同样变得更为困难。 为了解决这些问题,设计者可以将一种高效的硬件 测试手段和传统的系统测试方法相结合来完成。这 就是嵌入式逻辑分析仪的使用。它可以随设计文件 一并下载于目标芯片中,用以捕捉目标芯片内部, 设计者感兴趣的信号节点处的信息,而又不影响原 硬 件 系 统 的 正 常 工 作 。 这 就 是 QuartusⅡ 中 SignalTapⅡ的使用目的。

QuartusⅡ包括模块化的编译器。编译器包括的功 能模块有分析/综合器(Analysis&Synthesis)、适配 器(Fitter)、装配器(Assembler)、时序分析器 (Timing Analyzer)、设计辅助模块(Design Assistant)、EDA网表文件生成器(EDA Netlist Writer)、编辑数据接口(Compiler Database Interface)等。可以通过选择Start Compilation来 运行所有的编译器模块,也可以通过选择Start单独 运行各个模块。还可以通过选择Compiler Tool(Tools菜单),在Compiler Tool窗口中运行该模 块来启动编译器模块。在Compiler Tool窗口中,可 以打开该模块的设置文件或报告文件,或打开其他相 关窗口。

Quartus II软件及其使用

图3 编辑文件类型对话框

6

Quartus II软件及其使用

图5 文本编辑窗口

7

Quartus II软件及其使用

2. 编译设计文件

在编译设计文件前,应先选择下载的目标芯片,否则系统 将以默认的目标芯片为基础完成设计文件的编译。在Quartus II集成环境下,执行Assignments|Device命令,在如图6所示 弹出器件选择对话框的Family栏目中选择目标芯片系列名, 如Cyclone III,然后在Available devices栏目中用鼠标点黑选 择的目标芯片型号,如EP3C16Q240C8,选择结束单击OK 按键。 执行Pricessing|Start Compilation命令,或者按“开始 编译”按键,即可进行编译,编译过程中的相关信息将在 “消息窗口”中出现。

Editor按钮,弹出如图11所示的赋值编辑对话框,在对话框的Category栏 目选择Pin项。

图11 赋值编辑对话框

17

Quartus II软件及其使用 ②用鼠标双击Name栏目下的<<new>>,在其下拉菜单中列 出了设计电路的全部输入和输出端口名,例如全加器的a、b、 cin、cout和sum端口等。用鼠标选择其中的一个端口后,再 用鼠标双击Location栏目下的<<new>>,在其下拉菜单中列 出了目标芯片全部可使用的I/O端口,然后用鼠标选择其中的 一个I/O端口。例如,全加器的a、b、cin、cout和sum端口, 分别选择Pin_23 、Pin_22、 Pin_21、Pin_37和Pin_36。赋 Pin_23 Pin_22 Pin_21 Pin_37 Pin_36 值编辑操作结束后,存盘并关闭此窗口,完成引脚锁定。 ③ 锁定引脚后还需要对设计文件重新编译,产生设计电路的 下载文件(.sof)。

正弦信号发生器的设计

实验四正弦信号发生器的设计1. 实验的目的和要求熟悉QuartusII 及其LPM_ROM 与FPGA 硬件资源的使用方法。

2.实践内容或原理正弦信号发生器的结构由3部分组成,数据计数器或地址发生器、数据ROM 和D/A 。

性能良好的正弦信号发生器的设计,要求此3部分具有高速性能,且数据ROM 在高速条件下,占用最少的逻辑资源,设计流程最便捷,波形数据获最方便。

图1所示是此信号发生器结构图,顶层文件SINGT.VHD 在FPGA 中实现,包含2个部分:ROM 的地址信号发生器由5位计数器担任,和正弦数据ROM ,其原理图如图2所示。

据此,ROM 由LPM_ROM 模块构成能达到最优设计,LPM_ROM 底层是FPGA 中的EAB 或ESB 等。

地址发生器的时钟CLK 的输入频率f 0与每周期的波形数据点数(在此选择64点)以及D/A 输出的频率f 的关系是:640f f图1 正弦信号发生器结构图图2 正弦信号发生器原理图图3 正弦波的64个点的输入在Quartus II上完成正弦信号发生器设计,包括仿真和资源利用情况了解(假设利用Cyclone器件)。

最后在实验系统上实测,包括SignalTap II测试、FPGA中ROM的在系统数据读写测试和利用示波器测试。

最后完成EPCS1配置器件的编程。

3. 实验仪器(1)GW48系列SOPC/EDA实验开发系统(2)配套计算机及Quartus II 软件4.实践步骤或环节(1) 建立工程文件夹。

(2) 生成6位二进制计数器原理图。

(3)定制LPM_ROM元件。

(4)仿真。

(5)选择实验电路模式5,进行引脚下载配置。

(6)嵌入式逻辑分析仪的设置。

5. VHDL仿真实验(1)6位二进制计数器的仿真程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6b ISPORT (CLK,RST,EN: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR (5 DOWNTO 0);COUT:OUT STD_LOGIC);END CNT6b;ARCHITECTURE behav OF CNT6b ISBEGINPROCESS(CLK,RST,EN)VARIABLE CQI:STD_LOGIC_VECTOR(5 DOWNTO 0); BEGINIF RST='1'THEN CQI:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENCQI:=CQI+1;END IF;END IF;IF CQI=63 THEN COUT<='1';ELSE COUT<='0';END IF;CQ<=CQI;END PROCESS;END behav;(2)RTL电路(3)时序仿真波形:(4)硬件验证选择试验箱的模式为模式5,时钟CLK选择为CLOCK0(PIN_28脚),频率f=65536Hz,EN对应的引脚编号PIN-233,RST对应的引脚编号PIN-234,COUT对应的引脚编号PIN-1,Q[7..0]对应的引脚编号PIN-20,19,18,17,16,15,14,13.(5)逻辑分析仪的测试波形6.实践教学报告要求(1)详细分析各模块的逻辑功能,及其他们工作原理,详细记录并分析实验内容和实验内容的过程和结果,完成实验报告。

基于FPGA和Quartus_II设计的智能函数发生器_毕业设计论文

课程设计题目基于FPGA和Quartus II设计的智能函数发生器所在院(系)物理与电信工程学院基于FPGA和Quartus II设计的智能函数发生器[摘要] 信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

它能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波等,在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的信号发生器。

本设计采用FPGA来设计制作多功能信号发生器。

该信号发生器可以产生锯齿波、三角波、方波等波形。

[关键词]信号发生器;VHDL;FPGA;三角波;方波;锯齿波。

目录1.引言 (1)2.FPGA简介 (1)2.1VHDL和V ERILOG简介 (3)2.2设计工具简介 (3)3.系统设计 (3)3.1VHDL程序语言基本设计 (3)3.2波形发生器设计 (5)3.3程序设计原理框图 (5)4 系统的软件设计与仿真 (6)4.1系统仿真时序图 (6)4.2RTL仿真硬件图 (7)5总结体会与展望 (8)参考文献 (9)附录A 设计原理图 (11)附录B 系统仿真图 (11)附录C 源程序清单 (12)1.引言20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法。

电子设计自动化(EDA)工具给电子设计带来了巨大的变革,特别是可编程逻辑器件和硬件描述语言的出现和发展,解决了用传统的方法设计较大系统工程时的诸多不便,成为电子电路设计人员最得力的助手。

随着计算机和EDA技术的发展,基于FPGA的电子设计则是目前发展较为迅速的一个领域,而且广泛应用于计算机、通信等各个领域。

简易正弦信号发生器设计

简易正弦信号发生器设计

一、实验目的

1.进一步熟悉QuartusII及LPM-RAM宏模块与FPGA硬件资源的使用方法。

二、实验设备

计算机、和软件QuartusII和EDA/SOPC试验箱

三、试验内容

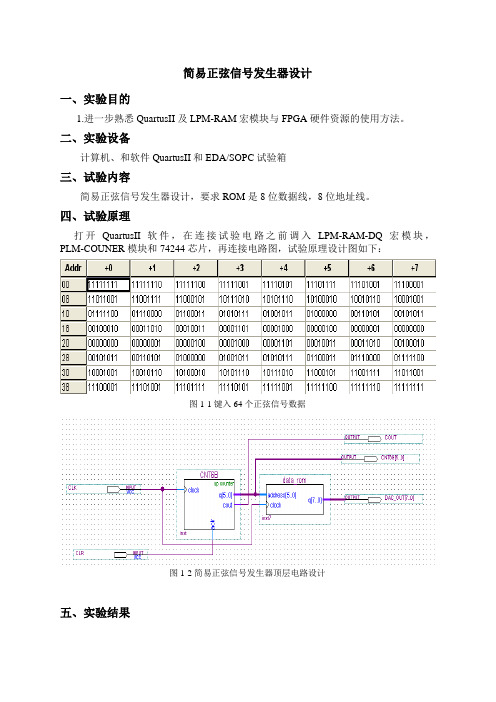

简易正弦信号发生器设计,要求ROM是8位数据线,8位地址线。

四、试验原理

打开QuartusII软件,在连接试验电路之前调入LPM-RAM-DQ宏模块,PLM-COUNER模块和74244芯片,再连接电路图,试验原理设计图如下:

图1-1键入64个正弦信号数据

图1-2简易正弦信号发生器顶层电路设计

五、实验结果

试验结果如下图:

图1-3综合后的RLT图

图1-4仿真波形图3.引脚锁定方案图

图1-5引脚锁定方案图

图1-6编程下载模式图

六、试验小节

一学期匆匆而过,通过大半学期的学习,我们学到了很多处理问题的技巧。

不过我们还要熟记很多单词,大多数的单词我们还不认识,相信通过进一步的学习,我们一定能学好这个软件。

我们也将以浓厚的兴趣和积极的态度去学习。

相信我们一定会有更加长足的进步。

Quartus2组件DSPbuilder设计DDS信号发生器

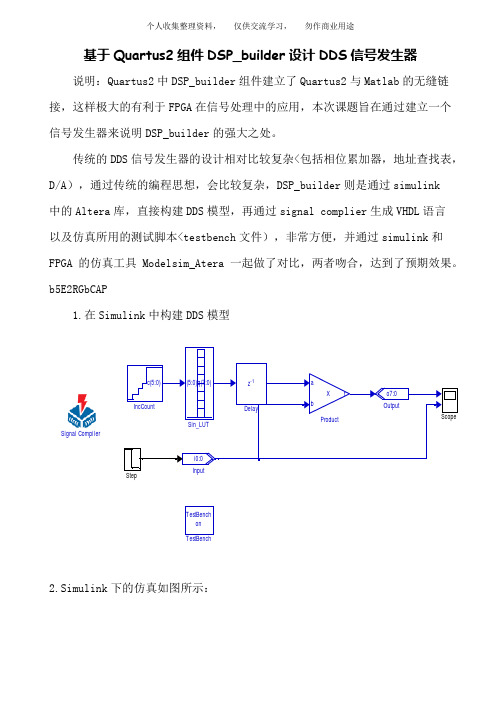

基于Quartus2组件DSP_builder 设计DDS 信号发生器说明:Quartus2中DSP_builder 组件建立了Quartus2与Matlab 的无缝链接,这样极大的有利于FPGA 在信号处理中的应用,本次课题旨在通过建立一个信号发生器来说明DSP_builder 的强大之处。

传统的DDS 信号发生器的设计相对比较复杂<包括相位累加器,地址查找表,D/A ),通过传统的编程思想,会比较复杂,DSP_builder 则是通过simulink 中的Altera 库,直接构建DDS 模型,再通过signal complier 生成VHDL 语言以及仿真所用的测试脚本<testbench 文件),非常方便,并通过simulink 和FPGA 的仿真工具Modelsim_Atera 一起做了对比,两者吻合,达到了预期效果。

b5E2RGbCAP 1.在Simulink 中构建DDS 模型2.Simulink 下的仿真如图所示:Signal Compiler3.RTL级仿真<modelsim 仿真):4.RTL 级视图-200-150-100-5050100150200050100150200250300350400450500-2-1.5-1-0.50.511.52附:.vhl代码-- sinwafe_GN.vhdlibrary IEEE。

use IEEE.std_logic_1164.all。

use IEEE.numeric_std.all。

entity sinwafe_GN isport (Output : out std_logic_vector(7 downto 0>。

-- Output.wirep1EanqFDPwInput : in std_logic_vector(0 downto 0> := (others => '0'>。

实验五 正弦信号发生器设计

实验五正弦信号发生器设计一、实验目的1.熟悉利用QuartusII及其LPM_ROM与FPGA硬件资源的使用方法;2.掌握LPM模块的重要功能;3.熟悉MegaWizard Plug-In Manager的使用方法。

二、实验设备计算机,QuartusII 6.0 版软件,JTAG下载线,EDA实验挂箱(EP1C6Q240C8)。

三、实验原理设计一8位宽、1024点的正弦信号发生器。

正弦信号发生器的结构由四个部分组成:1.计数器或地址发生器(10位地址线);2.正弦信号数据ROM(存放正弦波的采样数据,采样频率20MHz:8位数据线、10位地址线);3.VHDL顶层设计;4.D/A转换器(8位)。

四、实验步骤和内容1.在QuartusII上利用MegaWizard Plug-In Manager功能,调用LPM_ROM函数定制8位宽、1024点ROM,并进行初始化。

然后对设计实体进行编辑、编译、综合、适配、仿真。

2. 利用QuartusII文本编辑器设计10位二进制计数器,做为地址发生器,对设计实体进行编辑、编译、综合、适配、仿真。

3. 利用层次化设计方法设计一8位宽、1024点的正弦信号发生器。

4. D/A转换器采用试验箱配备的DAC0832。

5. 引脚锁定和硬件下载测试。

引脚锁定后进行编译、下载和硬件测试实验。

将实验过程和实验结果写进实验报告。

6. 使用SignalTap II对设计的正弦信号发生器进行实测。

采样时钟使用系统时钟20MHz。

7. 使用在系统存储器数据读写编辑器对设计的正弦信号发生器进行实测,观测结果;8.实验报告。

将实验原理、设计过程、编译仿真波形和分析结果、硬件测试实验结果写进实验报告。

五、思考题如何实现对输出正弦信号的频率和相位可调?。

FPGA实验一、正弦信号发生器

河北大学 电子与信息工程学院 2010 张庆顺1 / 53SOPC 设计技术课程实验一、正弦信号发生器河北大学 电子信息工程学院教师:张庆顺本实验指导书演示了一个简单的正弦信号发生器在QUARTU S Ⅱ上的实现。

通过这个文档,旨在演示利用QUARTUS Ⅱ开发数字电路的基本流程和QUARTUS Ⅱ软件的相关操作,并借此介绍QUARUTS Ⅱ的软件界面。

我们还针对DE Ⅱ-70的实验板,实现了本文档所示硬件模块的相关配置工作以及下载和实现。

实验条件:Quartus II 9.1目录二、实验步骤: (6)1、工程创建 (6)2、sin信号发生器顶层模块的设计 (13)3、定制ROM存储sin波形数据 (17)3.1 建立.mif文件 (17)3.2 ROM数据的生成 (19)3.3 定制ROM元件 (19)3.3.1 调用Mega Wizard Plug-In Manager (20)3.3.2 设置LPM_ROM模块 (21)4、编译、综合等 (27)5、仿真 (28)5.1 编辑波形文件 (28)5.2进行仿真 (36)6、内部电路观察 (38)7、生成symbol (40)8、管脚分配 (46)9、下载 (49)10.作业 (53)一、设计原理:下图所示为正弦信号发生器的结构,共有4个部分组成:顶层文件singt.v 在FPGA 中实现两个部分:1、6位计数器产生地址信号;2、存储正弦信号(6bits 地址线,8bits 数据线)的ROM ,由LPM_ROM 模块实现,LPM_ROM 模块底层由FPGA 的EAB 、ESB 或M4K 来实现。

地址发生器的时钟频率CLK 假设为f0,这里我们设定的地址发生器为6bit ,则周期为26=64,所以一个正弦周期内可以采样64个点,DAC 后的输出频率f 为:64/0f f =我们可以如下生成sin 数据以用于查找表,双、单极性Sin(x)数据波形可如下:x = round((sin(linspace(0,2*pi,64))+1)*127.5);所要得到的单极性信号波形。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

发现文件中的错误。再次进行编译直至排除所有错误。我们会发现在Processing处理栏,编译后出现如下错误信息:

Error:Node instance u1 instabtiates undefined entity DATAROM

原因是在图3-3 所示的主程序中的“DATAROM”元件是空的,因为我们还没有设计此元件对应的文件:DATAROM.VHD。

图 3-9 选择配置器件和配置方式

图 3-10 输出文件.hexout 设置

3.1.4 编译及了解编译结果

QuartusII编译器是由一系列处理模块构成的,这些模块负责对设计项目的检错,逻辑综合和结构综合。即将设计项

目适配进FPGA/CPLD目标器中,同时产生多种用途的输出文件,如功能和时序仿真文件,器件编程的目标文件等。编译

工程名、目标器件、综合器、访真器等。步骤如下:

1、建立新工程管理窗。选择菜单“File”→“New Preject Wizard”,即弹出工程设置对话框(图 3-4)。点击此框最

上一栏右侧的按钮“…”,找到文件夹 e : \SIN_GNT ,选中已存盘的文件 singt.vhd(一般应该设定顶层设计文件为工

2、输入源程序。打开 QuartusII,选择菜单“File”→“New”,在 New 窗中的“Device Design Files”中选择编译文

件的语言类型,这里选“VHDL Files”(如图 3-2 所示)。然后在 VHDL 文本编译窗中键入如图 3-3 所示的 VHDL 程序。

图 3-1 正弦信号发生器结构图

项,在此框的下方有相应的说明,在此可选Configuration方式为Active Serial,这种方式指对专用配置器件进行配置用的

编程方式,而PC机对此FPGA的直接配置方式都是JTAG方式。“Configuration device”项,选择配置器为EPCS1 或EPCS4

(根据实验系统上目标器件配置的EPCS芯片决定如图 3-9 所示)。

第三章 Quartus II 设计正弦信号发生器

Quartus II 设计工具完全支持 VHDL、Verilog 的设计流程,其内部嵌有 VHDL、Verilog 逻辑综合器。QuartusII 与 MATLAB 和 DSP Builder 结合可以进行基于 FPGA 的 DSP 系统开发,是 DSP 硬件系统实现的关键 EDA 工具,与 SOPC Builder 结合,可实现 SOPC 系统开发。本章将以正弦信号发生器设计示例详细介绍 QuartusII 的使用方法。

注意,以下各软件对计算机的要求是:奔腾 4 或以上主机,大于等于 256M 内存。

3.1 顶层 VHDL 文件设计

3.1.1 创建工程和编辑设计文件

本节通过正弦信号发生器的设计对QuartusII的一些重要功能作一些说明。对本节的详细了解有利于对以后章节有关

DSP Builder的应用和设计有更好的理解。正弦信号发生器的结构由 3 部分组成(图 3-1):数据计数器或地址发生器、数

器首先从工程设计文件间的层次结构描述中提取信息,包括每个低层次文件中的错误信息,供设计者排除,然后将这些

层次构建产生一个结构化的以网表文件表达的电路原理图文件,并把各层次中所有的文件结合成一个数据包,以便更有

效地处理。下面首先选择Processing菜单的“Start Compilation”项,启动全程编译。注意这里所谓的编译(Compilation)

程),再点击“打开”,即出现如图 3-4 所示设置情况。其中第一行表示工程所在的工作库文件夹;第二行表示此项工程

的工程名,此工程名可以取任何其它的名,通常直接用顶层文件的实体名作为工程名,第三行是顶层文件的实体名。

2、将设计文件加入工程中。然后点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相

据ROM和D/A。性能良好的正弦信号发生器的设计要求此 3 部分具有高速性能,且数据ROM在高速条件下,占用最少的

逻辑资源,设计流程最便捷,波形数据获最方便。图3-1 所示是此信号发生器结构图,顶层文件SINGT.VHD在FPGA中实现,

包含 2 个部分:ROM的地址信号发生器由 5 位计数器担任,和正弦数据ROM,据此,ROM由LPM_ROM模块构成能达到最优

图 3-11 进入 mif 文件编辑窗

图 3-12 将波形数据填入 mif 文件表中 3

图 3-13 A5 LPM_ROM 宏功能块设定

图 3-16 选择 DATAROM 模块数据线和地址线宽度

图 3-17 选择地址所存信号 inclock

图 3-2 选择编辑文件的语言类型

图 3-3 编辑输入设计文件(顶层设计文件 SINGT.VHD) 1

图 3-4 利用“New Preject Wizard”创建工程

图 3-5 将所有相关的文件都加入进此工程

3、文件存盘。选择“File”→“Save As”,找到已设立的文件夹 e : \SIN_GNT ,存盘文件名应该与实体名

在对工程进行编译处理前,必须作好必要的设置。具体步骤如下:

1、选择目标芯片。目标芯片的选择也可以这样来实现:选择“Assignmemts”菜单中的“settings”项,在弹出的对

话框中选“Compiler Settings” 项下的 Device,首先选目标芯片:EPIC6Q240C8(此芯片已在建立工程时选定了),也可

一致,即 singt.vhd。当出现问句“Do you want to create…”时,若选“否”,可按以下的方法进入创建工程

流程;若选“是”,则直接进入创建工程流程,创建工程流程如下:

3.1.2 创建工程

在此要利用“New Preject Wizard”创建此设计工程,即令 singt.vhd 为工程,并设定此工程一些相关的信息,如

选默认的“NONE”,表示都选 QuartusII 中自带的仿真器和综合器,因此,在此都选默认项“NONE”。

4、选择目标芯片。再次点击“Next”,选择目标芯片。首先在“Family”栏选芯片系列,在此选“Cyclone”系列,

并在此栏下选“Yes”,即选择一确定目标器件。再按键“Next”,选择此系列的具体芯片:EPIC6Q240C8(图 3-6),按

键“Next”后,弹出工程设置统计窗口,以上列出了此项工程的相关设置情况。

5、结束设置。最后按键“Finish”,即已设定好此工程(图 3-7),此工程管理窗主要显示工程项目的层次结构。

图 3-6 选择此系列的具体芯片

图 3-7 SINGT 的工程管理窗

图 3-8 选定目标器件

3.1.3 编译前设置

包括QuartusII对设计输入的多项处理操作,其中包括排错、数据网表文件提取、逻辑综合、适配、装配文件(仿真文件

与编程配置文件)生成,以及基于目标器件的工程时序分析等。如果工程中的文件有错误,在下方的Processing处理栏中

会显示出来。对于Processing栏显示出的语句格式错误,可双击此条文,即弹出vhdl文件,在闪动的光标处(或附近)可

3.2 正弦信号数据 ROM 定制

为了解决以上出现的问题,以下要完成波形数据ROM 的定制和ROM 中波形数据文件,即ROM 的初始化文件的设计。 3.2.1 设计ROM 初始化数据文件。以下介绍生成初始化数据文件的 4 种方法。初始化数据文件格式有 2 种:Memory Initialization File (.mif)格式文件,或 Hexadecimal (Intel-Format) File (.hex)格式。以下以 64 点正弦波形数据为例分别说明: 1、建立.mif 格式文件。首先选择 ROM 数据文件编辑窗,即在 File 菜单中选择“New”,并在 New 窗中选择“Other files”项,并选“Memory Initialization File”(图 3-11),点击 OK 后产生 ROM 数据文件大小选择窗。这里采用 64 点 8 位数据的情况,可选 ROM 的数据数 Number 为 64,数据宽 Word size 取 8 位。点击“OK”,将出现如图 3-12 的空的 mif 数据表格,表格中的数据为 10 进制表达方式,任一数据(如第三行的 99)对应的地址为左列于顶行数之和)。将波形数 据填入此表中,完成后在 File 菜单中点击“Save as”,保存此数据文件,在这里不妨取名为.romd.mif。 2、建立.hex格式文件。建立.hex格式文件的文件有两种方法,第一种方法与以上介绍的方法相同,只是在New窗中 选择“Other files”项,后,选择“Hexadecimal (Intel-Format) File”项,最后存盘.hex格式文件。第二种方法是普通单片 机编译器来产生。方法是利用汇编程序编辑器将此 64 个数据编辑于如图 3-13 所示的编辑窗中,然后用单片机ASM编译 器产生.hex格式文件。在此不妨取名为SIND1.asm,编译后得到SIND1.hex文件,现将sind1.hex或romd.mif文件都存到 e:\sin_gnt\asm\文件夹中,备用。注意,此类文件必须放在当前目录的高一层次目录中:\sin_gnt\asm\!

此工程相关的所有文件的文件夹,此文件夹将被EDA 软件默认为工作库(Work Library)。

在建立了文件夹后就可以将设计文件通过QuartusII 的文本编辑器编辑并存盘,详细步骤如下:

1、 新建一个文件夹。利用资源管理器,新建一个文件夹,如:e : \SIN_GNT 。注意,文件夹名不能用中文。

设计,LPM_ROM底层是FPGA中的EAB或ESB等。地址发生器的时钟CLK的输入频率f0与每周期的波形数据点数(在此选择

64 点),以及D/A输出的频率f的关系是:

f = f0 /64

首先建立工作库,以便设计工程项目的存储。任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与