EDA期末考试考卷及答案

EDA(FPGA)期末考试试题汇总

这是长期总结的EDA期末考试试题试题一1-2与软件描述语言相比,VHDL有什么特点 P6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合有哪些类型综合在电子设计自动化中的地位是什么 P5什么是综合答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中的地位是什么答:是核心地位(见图1-3)。

综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。

1-4在EDA技术中,自顶向下的设计方法的重要意义是什么 P7~10答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。

EDA技术期末试卷含答案资料

精品文档一、单项选择题(30分)9.嵌套使用IF语句,其综合结果可实现 A 。

A.带优先级且条件相与的逻辑电路1.以下描述错误的是 C B.条件相或的逻辑电路C.三态控制电路是A.QuartusIIAltera提供的FPGA/CPLD集成开发环境D.双向控制电路10.在VHDLAlteraB.是世界上最大的可编程逻辑器件供应商之一语言中,下列对时钟边沿检测描述中,错误的是 D 。

A.if clk'event and clk = ‘1' then B.if falling_edge(clk) then 前一代C.MAX+plusII是AlteraFPGA/CPLD集成开发环境QuartusII的更C.if clk'event and clk = ‘0' then 新换代新产品D.if clk'stable and not clk = ‘1' then11.下列那个流程是正确的基于.DQuartusII完全支持VHDL、Verilog的设计流程EDA软件的FPGA / CPLD设计流程 BA.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试开发工具中的专用综合器的是2.以下工具中属于FPGA/CPLD BB.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试C .Active HDL D.QuartusII Leonardo Spectrum .AModelSim B.C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;.3以下器件中属于Xilinx 公司生产的是 C/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试D.BMAX系列器件.原理图A.ispLSI系列器件)语句的语句结构及语法规则语言中,下列对进程(PROCESS系列器件C.XC9500系列器件D.FLEX 12.在VHDL 。

A 的描述中,正确的是以下关于信号和变量的描述中错误的是4. B为一无限循环语句;敏感信号发生更新时启动进程,执行完..信号是描述硬件系统的基本数据对象,它的性质类似于连接线PROCESSAA .信号的定义范围是结构体、进程B 成后,等待下一次进程启动C.除了没有方向说明以外,信号与实体的端口概念是一致的B.敏感信号参数表中,应列出进程中使用的所有输入信号CD.在进程中不能将变量列入敏感信号列表中.进程由说明部分、结构体部分、和敏感信号参数表三部分组成D.当前进程中声明的变量也可用于其他进程以下关于状态机的描述中正确的是5. BB MooreA.型状态机其输出是当前状态和所有输入的函数13.下列语句中,不属于并行语句的是语句B.CASE 型的输出变化要领先一个时钟周期型状态机相比,.与BMooreMealy A.进程语句…语句…ELSE D.WHEN .元件例化语句MealyC.型状态机其输出是当前状态的函数 C设计现行工作VHDL语言共支持四种常用库,其中哪种库是用户的14.以上都不对D .VHDL B 下列标识符中,.库是不合法的标识符。

eda技术实用教程期末考试题及答案

eda技术实用教程期末考试题及答案一、选择题(每题2分,共20分)1. EDA技术中,FPGA代表的是()。

A. 现场可编程逻辑阵列B. 现场可编程门阵列C. 现场可编程逻辑器件D. 现场可编程门器件答案:B2. 在EDA技术中,VHDL是一种()。

A. 硬件描述语言B. 软件描述语言C. 系统描述语言D. 网络描述语言答案:A3. 下列哪个不是EDA工具的主要功能()。

A. 逻辑综合B. 电路仿真C. 代码编译D. 布局布线答案:C4. 在VHDL中,下列哪个关键字用于定义并行语句()。

A. ifB. beginC. loopD. process答案:B5. 在EDA技术中,用于测试和验证数字电路的EDA工具是()。

A. 逻辑综合工具B. 电路仿真工具C. 布局布线工具D. 测试生成工具答案:B6. 下列哪个不是FPGA的配置方式()。

A. 在系统可编程B. 串行配置C. 并行配置D. 网络配置答案:D7. 在VHDL中,用于定义信号的关键字是()。

B. constantC. signalD. type答案:C8. 在EDA技术中,用于描述数字电路行为的模型是()。

A. 结构模型B. 数据流模型C. 行为模型D. 混合模型答案:C9. 在VHDL中,下列哪个关键字用于定义过程()。

A. procedureB. functionD. entity答案:C10. 在EDA技术中,用于优化电路性能的EDA工具是()。

A. 逻辑综合工具B. 电路仿真工具C. 布局布线工具D. 测试生成工具答案:C二、填空题(每题2分,共20分)1. EDA技术中的“EDA”代表的是______、______和______。

答案:电子设计自动化2. VHDL中的并发语句包括______、______、______和______。

答案:信号赋值、条件信号赋值、选择信号赋值、元件实例化3. 在FPGA设计中,______是用于存储配置数据的非易失性存储器。

EDA期末考试试卷

EDA期末考试试卷期末考试《EDA》试卷A一、填空题:(每空1分,共20分)1、一般把EDA技术的发展分为、和三个阶段。

2、VHDL的全称是3、VHDL年正式推出,是目前标准化程度最高的硬件描述语言。

4、一个完整的VHDL设计实体由、和等部分构成。

5、VHDL组成。

6、VHDL字符是以括起来的数字、字母和数字。

7、VHDL,只能在进程、函数和过程中声明和使用。

8、VHDL顺序语句只出现在、和中,是按程序书写的顺序自上而下、一条一条地执行。

9、VHDL子程序有和两种类型。

10、在VHDL二、选择题:(每小题2分,共10分)1、用VHDL语言描写的的源程序文件后缀为()A.某.wdfB.某.gdfC.某.vhdD.某.ym2、IEEE与1987年公布了VHDL的语法标准为()A.IEEESTD1076_1987B.RS232C.IEEE.STD_LOGIC_1164D.IEEESTD1076_19933、一个实体可以拥有一个或者多个()。

A.设计实体B.结构体C.输入D.输出4、在下列标识符中,()是VHDL合法标识符。

A.4h_addeB.h_adde_C.h_addeD._h_adde5、在VHDL中,为目标变量的赋值符号为()A.=:B.=C.:=D.《=三、简答题:(每题5分,共20分)12、变量赋值语句与信号赋值语句的区别?3、PROCESS语句的特点。

4、if语句包括哪几种类型?写出每种类型的语法格式。

四、程序改错:(找出错误并改正,找出每处错误1分,改正1分共20分)1、architecturertloftartiProceclkignalcount:integerrange0to7;beginif(clk'eventandclk='1')count<=count+1;if(count=0)thencarryout<=1;elecarryout<='0';endif;endproce;endrtl;2、libraryieee;ueieee_td_logic_1164.all;entitydm(a,b:intd_logic;c:outtd_logic)endmd;architecturelifordmibeginc:=aandb;五、编程题:(第1题6分,第2题6分,第3题9分,第4题9分,共30分)1、利用VHDL语言描述一个三态门电路2、利用VHDL语言描述4位二进制数据比较器3、利用VHDL语言描述一个同步置位、复位的D触发器4、利用VHDL语言设计一个分频系数为16的分频器期末考试《EDA实验》试卷B一、填空题:(每题6分,共30分)1、常用的设计输入方式有、2、库提供了基本的逻辑元器件。

EDA期末考试试卷及答案(word文档良心出品)

密 封 线 内 不 得 答题班级 学号姓名赣 南 师 范 学 院2010—2011学年第一学期期末考试试卷(A 卷)(闭卷)年级 2008 专业 电子科学与技术 (本)课程名称 EDA 技术基础2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线;3、答题请用蓝、黑钢笔或圆珠笔。

一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 BA .适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件B .适配所选定的目标器件可以不属于原综合器指定的目标器件系列C .适配完成后可以利用适配所产生的仿真文件作精确的时序仿真D .通常,EDAL 软件中的综合器可由专业的第三方EDA 公司提供,而适配器则需由FPGA/CPLD 供应商提供2.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。

A .器件外部特性B .器件的综合约束C .器件外部特性与内部功能D .器件的内部功能 3.下列标识符中, B 是不合法的标识符。

A .State0B .9moonC .Not_Ack_0D .signall 4.以下工具中属于FPGA/CPLD 集成化开发工具的是 DA .ModelSimB .Synplify ProC .MATLABD .QuartusII5.进程中的变量赋值语句,其变量更新是 A 。

A .立即完成B .按顺序完成C .在进程的最后完成D .都不对 6.以下关于CASE 语句描述中错误的是 AA .CASE 语句执行中可以不必选中所列条件名的一条B .除非所有条件句的选择值能完整覆盖CASE 语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>”C .CASE 语句中的选择值只能出现一次D . WHEN 条件句中的选择值或标识符所代表的值必须在表达式的取值范围7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A .STD_LOGIC_ARITHB .STD_LOGIC_1164C .STD_LOGIC_UNSIGNEDD .STD_LOGIC_SIGNED 8.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→ A →综合→适配→时序仿真→编程下载→硬件测试。

(完整word版)EDA期末考试试卷及答案

第1页(共5页)班级 学号 姓名密 封 线 内 不 得 答 题一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 BA .适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件B .适配所选定的目标器件可以不属于原综合器指定的目标器件系列C .适配完成后可以利用适配所产生的仿真文件作精确的时序仿真D .通常,EDAL 软件中的综合器可由专业的第三方EDA 公司提供,而适配器则需由FPGA/CPLD 供应商提供2.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。

A .器件外部特性B .器件的综合约束C .器件外部特性与内部功能D .器件的内部功能 3.下列标识符中, B 是不合法的标识符。

A .State0B .9moonC .Not_Ack_0D .signall4.以下工具中属于FPGA/CPLD 集成化开发工具的是 DA .ModelSimB .Synplify ProC .MA TLABD .QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。

A .立即完成B .按顺序完成C .在进程的最后完成D .都不对6.以下关于CASE 语句描述中错误的是 AA .CASE 语句执行中可以不必选中所列条件名的一条B .除非所有条件句的选择值能完整覆盖CASE 语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>”C .CASE 语句中的选择值只能出现一次D . WHEN 条件句中的选择值或标识符所代表的值必须在表达式的取值范围7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A .STD_LOGIC_ARITH B .STD_LOGIC_1164C .STD_LOGIC_UNSIGNEDD .STD_LOGIC_SIGNED8.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→ A →综合→适配→时序仿真→编程下载→硬件测试。

eda试题及答案

AD574工作时序位转换模式,K12_8、A0在control中如何设置?《EDA技术与项目训练》选择题1. 一个项目的输入输出端口是定义在 A 。

A. 实体中B. 结构体中C. 任何位置D. 进程体2. 描述项目具有逻辑功能的是 B 。

A. 实体B. 结构体C. 配置D. 进程3. 关键字ARCHITECTURE定义的是 A 。

A. 结构体B. 进程C. 实体D. 配置4. MAXPLUSII中编译VHDL源程序时要求 C 。

A.文件名和实体可不同名B.文件名和实体名无关C. 文件名和实体名要相同D. 不确定5. 1987标准的VHDL语言对大小写是 D 。

A. 敏感的B. 只能用小写C. 只能用大写D. 不敏感6. 关于1987标准的VHDL语言中,标识符描述正确的是 A 。

A. 必须以英文字母开头B.可以使用汉字开头C.可以使用数字开头D.任何字符都可以7. 关于1987标准的VHDL语言中,标识符描述正确的是 B 。

A. 下划线可以连用B. 下划线不能连用C. 不能使用下划线D. 可以使用任何字符8. 符合1987VHDL标准的标识符是 A 。

A. A_2B. A+2C. 2AD. 229. 符合1987VHDL标准的标识符是 A 。

A. a_2_3B. a_____2C. 2_2_aD. 2a10. 不符合1987VHDL标准的标识符是 C 。

A. a_1_inB. a_in_2C. 2_aD. asd_111. 不符合1987VHDL标准的标识符是 D 。

A. a2b2B. a1b1C. ad12D. %5012. VHDL语言中变量定义的位置是 D 。

A. 实体中中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置13. VHDL语言中信号定义的位置是 D 。

A. 实体中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置14. 变量是局部量可以写在 B 。

eda考试题及答案

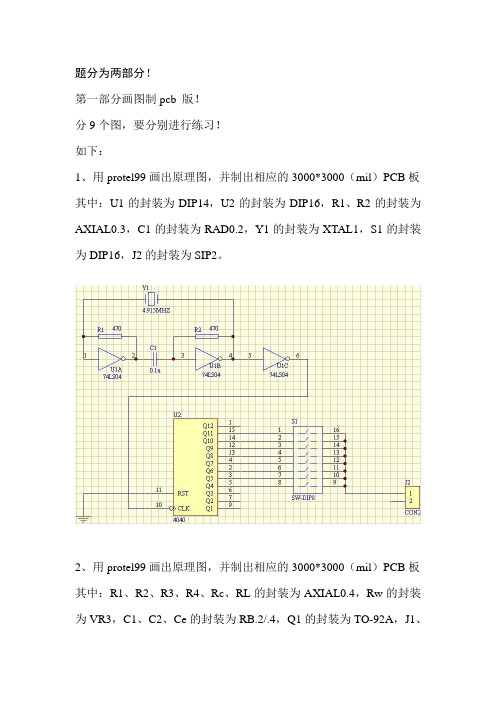

题分为两部分!第一部分画图制pcb 版!分9个图,要分别进行练习!如下:1、用protel99画出原理图,并制出相应的3000*3000(mil)PCB板其中:U1的封装为DIP14,U2的封装为DIP16,R1、R2的封装为AXIAL0.3,C1的封装为RAD0.2,Y1的封装为XTAL1,S1的封装为DIP16,J2的封装为SIP2。

2、用protel99画出原理图,并制出相应的3000*3000(mil)PCB板其中:R1、R2、R3、R4、Rc、RL的封装为AXIAL0.4,Rw的封装为VR3,C1、C2、Ce的封装为RB.2/.4,Q1的封装为TO-92A,J1、J2的封装为SIP2。

3、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:R1、R2、R3的封装为AXIAL0.4,R的封装为VR2,UA741的封装为DIP8,JP1、JP2的封装为SIP2。

4、用protel99画出原理图,并制出相应的3000*3000(mil)PCB板其中:R1、R2、R3、R4、R5、R6、R7的封装为AXIAL0.4,U1、U2、DS1的封装为DIP16。

5、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:U1、U2的封装为DIP14,J1、J2的封装为SIP2。

6、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:U1的封装为DIP16,U2、U3的封装为DIP14,J2的封装为SIP3。

7、用protel99画出原理图,并制出相应的2000*3000(mil)PCB板其中:R1、R2、R3、R4、R5、R6、R7的封装为AXIAL0.4,Rw的封装为VR3,U1的封装为DIP8,J1的封装为SIP2。

8、用protel99画出原理图,并制出相应的2000*2000(mil)PCB板其中:U1的封装为DIP16,U2的封装为DIP14,J1的封装为SIP6。

eda期末考试试卷

eda期末考试试卷EDA期末考试试卷一、选择题(每题2分,共20分)1. EDA是指:A. 电子设计自动化B. 电子数据交换C. 电子文档分析D. 电子设备应用2. 在EDA工具中,用于绘制电路原理图的软件通常被称为:A. PCB DesignerB. Schematic CaptureC. Logic SimulatorD. Layout Editor3. 下列哪个不是数字逻辑门的基本类型:A. ANDB. ORC. NOTD. XOR4. 以下哪个是EDA工具中用于模拟电路行为的软件:A. VHDLB. VerilogC. RTL SimulatorD. PCB Router5. 在设计一个数字电路时,以下哪项不是设计流程的一部分:A. 需求分析B. 原理图绘制C. 电路板设计D. 手工焊接6. FPGA代表:A. 现场可编程门阵列B. 固定门阵列C. 通用门阵列D. 专用集成电路7. 在VHDL或Verilog中,以下哪个关键字用于定义一个过程:A. processB. moduleC. functionD. package8. 以下哪个是EDA工具中用于生成电路板布局的软件:A. Schematic CaptureB. Layout EditorC. PCB DesignerD. Logic Simulator9. 在数字电路设计中,同步设计和异步设计的主要区别在于:A. 使用的逻辑门类型B. 电路的复杂性C. 时钟信号的使用D. 电路的功耗10. 下列哪个不是常用的PCB设计软件:A. Altium DesignerB. EagleC. KiCadD. MATLAB二、简答题(每题10分,共30分)1. 简述EDA工具在电子设计过程中的作用和重要性。

2. 解释什么是信号完整性,并讨论它在高速电路设计中的重要性。

3. 描述一个典型的数字电路设计流程,并解释每个步骤的目的。

三、计算题(每题15分,共30分)1. 给定一个简单的数字逻辑电路,包含两个输入A和B,一个输出Y。

eda期末考试题及答案

eda期末考试题及答案EDA期末考试题及答案一、选择题(每题2分,共20分)1. EDA代表的是:A. 电子设计自动化B. 电子数据交换C. 电子文档管理D. 电子设备分析答案:A2. 在EDA中,HDL指的是:A. 高级硬件描述语言B. 硬件描述语言C. 硬件设计语言D. 硬件开发语言答案:B3. 下列哪个不是EDA工具的常见功能?A. 仿真B. 布局C. 布线D. 编程答案:D4. FPGA代表的是:A. 现场可编程门阵列B. 固定可编程门阵列C. 功能可编程门阵列D. 快速可编程门阵列答案:A5. VHDL是一种:A. 编程语言B. 硬件描述语言C. 数据库语言D. 操作系统答案:B6. 以下哪个是EDA软件的典型应用?A. 网页设计B. 游戏开发C. 电子电路设计D. 办公自动化答案:C7. 在EDA设计流程中,综合是指:A. 将设计从逻辑级别转换为门级别B. 将设计从门级别转换为晶体管级别C. 将设计从晶体管级别转换为物理布局D. 将设计从物理布局转换为最终产品答案:A8. 下列哪个是EDA设计中的错误?A. 功能错误B. 语法错误C. 布局错误D. 所有选项都是答案:D9. 以下哪个不是EDA设计中的测试类型?A. 功能测试B. 性能测试C. 压力测试D. 代码测试答案:D10. 在EDA中,后仿真分析是指:A. 在仿真之前进行的分析B. 在仿真之后进行的分析C. 在仿真过程中进行的分析D. 不进行任何分析答案:B二、简答题(每题10分,共30分)1. 请简述EDA在电子设计中的重要性。

答案:EDA(电子设计自动化)是现代电子设计不可或缺的工具,它允许设计师使用软件工具来设计和验证电子系统,从而提高设计效率,减少错误,加快产品上市时间,并且可以设计出更复杂、更高性能的电子系统。

2. 描述一下在EDA设计流程中,仿真的作用是什么?答案:在EDA设计流程中,仿真是一个关键步骤,它允许设计师在实际制造电路之前验证设计的功能和性能。

EDA期末考试试题

第一部分:填空题1.一般把EDA技术的发展分为CAD、CAE和EDA三个阶段,并向着ESDA方向发展。

2.EDA技术在应用设计领域主要包含哪四个方面的内容(1)HDL (2)PLD(3)EDA工具软件(4)EDA开发系统。

3.EDA技术的基本特征(1)自顶向下的设计方法;(2)采用硬件描述语言;(3)高层综合和优化;(4)并行工程;(5)开放性和标准化。

4.当前最流行的并成为IEEE标准的硬件描语言是V HDL和Verilog-HDL。

5.什么是PLD?答: PLD,Programmable-Logic-Device,即可编程逻辑器件。

是一种具有内建结构、由用户编程以实现某种逻辑功能的新型逻辑器件。

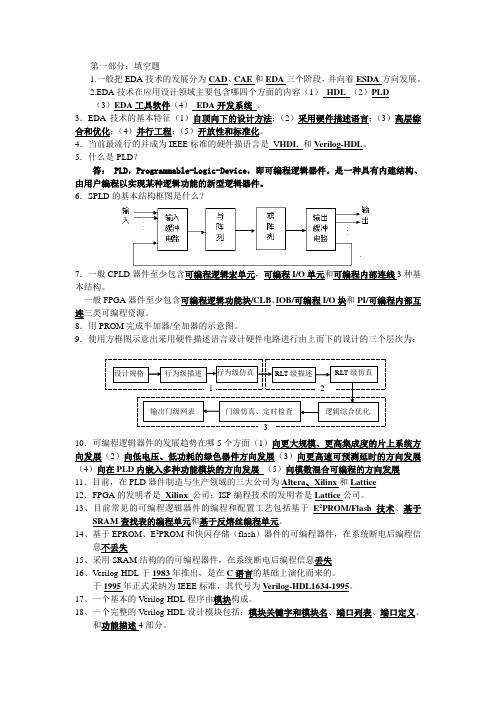

6.SPLD的基本结构框图是什么?7.一般CPLD器件至少包含可编程逻辑宏单元,可编程I/O单元和可编程内部连线3种基本结构。

一般FPGA器件至少包含可编程逻辑功能块/CLB、IOB/可编程I/O块和PI/可编程内部互连三类可编程资源。

8.用PROM完成半加器/全加器的示意图。

9.使用方框图示意出采用硬件描述语言设计硬件电路进行由上而下的设计的三个层次为:10.可编程逻辑器件的发展趋势在哪5个方面(1)向更大规模、更高集成度的片上系统方向发展(2)向低电压、低功耗的绿色器件方向发展(3)向更高速可预测延时的方向发展(4)向在PLD内嵌入多种功能模块的方向发展(5)向模数混合可编程的方向发展11.目前,在PLD器件制造与生产领域的三大公司为Altera、Xilinx和Lattice 12.FPGA的发明者是Xilinx公司;ISP编程技术的发明者是Lattice公司。

13、目前常见的可编程逻辑器件的编程和配置工艺包括基于E2PROM/Flash技术、基于SRAM查找表的编程单元和基于反熔丝编程单元。

14、基于EPROM、E2PROM和快闪存储(flash)器件的可编程器件,在系统断电后编程信息不丢失15、采用SRAM结构的的可编程器件,在系统断电后编程信息丢失16、V erilog-HDL于1983年推出,是在C语言的基础上演化而来的。

EDA技术期末试卷含答案

一、单项选择题(30分)9.嵌套使用IF语句,其综合结果可实现 A 。

A.带优先级且条件相与的逻辑电路1.以下描述错误的是 C B.条件相或的逻辑电路C.三态控制电路A.QuartusII是Altera提供的FPGA/CPLD集成开发环境D.双向控制电路10.在VHDLB.Altera是世界上最大的可编程逻辑器件供应商之一语言中,下列对时钟边沿检测描述中,错误的是 D 。

A.if clk'event and clk = ‘1' then B.if falling_edge(clk) then MAX+plusIIC.是Altera前一代FPGA/CPLD集成开发环境QuartusII的更C.if clk'event and clk = ‘0' then 新换代新产品D.if clk'stable and not clk = ‘1' then11.下列那个流程是正确的基于VerilogD.QuartusII完全支持VHDL、的设计流程EDA软件的FPGA / CPLD设计流程 BA.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试.2以下工具中属于FPGA/CPLD开发工具中的专用综合器的是 BB.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试.Leonardo Spectrum C.Active HDL DQuartusII ModelSim A.B.C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;以下器件中属于3.Xilinx 公司生产的是 C/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试DMAXB.系列器件.原理图.AispLSI系列器件)语句的语句结构及语法规则语言中,下列对进程(PROCESS D .CXC9500系列器件.FLEX系列器件12.在VHDL 。

A 的描述中,正确的是4.以下关于信号和变量的描述中错误的是 B为一无限循环语句;敏感信号发生更新时启动进程,执行完..信号是描述硬件系统的基本数据对象,它的性质类似于连接线A PROCESSA B.信号的定义范围是结构体、进程成后,等待下一次进程启动BC.除了没有方向说明以外,信号与实体的端口概念是一致的.敏感信号参数表中,应列出进程中使用的所有输入信号CD.在进程中不能将变量列入敏感信号列表中.进程由说明部分、结构体部分、和敏感信号参数表三部分组成 D B .5以下关于状态机的描述中正确的是.当前进程中声明的变量也可用于其他进程 B 型状态机其输出是当前状态和所有输入的函数A.Moore 13.下列语句中,不属于并行语句的是语句B.CASE MooreB.与型状态机相比,Mealy型的输出变化要领先一个时钟周期A.进程语句…语句…ELSE D.WHEN .元件例化语句型状态机其输出是当前状态的函数.CMealy C设计现行工作VHDL语言共支持四种常用库,其中哪种库是用户的D.以上都不对14.VHDL 下列标识符中, B 库是不合法的标识符。

eda试题及答案

eda试题及答案一、单选题(每题2分,共10分)1. EDA的全称是:A. 电子数据交换B. 电子设计自动化C. 电子文档自动化D. 电子设备自动化答案:B2. 在EDA中,HDL指的是:A. 高级数据语言B. 硬件描述语言C. 硬件设计语言D. 硬件描述逻辑答案:B3. 以下哪个不是EDA软件的主要功能?A. 逻辑综合B. 布局布线C. 编译代码D. 时序分析答案:C4. 在EDA设计流程中,FPGA指的是:A. 现场可编程逻辑阵列B. 固定可编程逻辑阵列C. 现场可编程门阵列D. 固定可编程门阵列答案:C5. 在EDA设计中,仿真测试的目的是:A. 验证设计的正确性B. 优化设计的性能C. 检查设计的安全性D. 以上都是答案:A二、多选题(每题3分,共15分)6. EDA工具通常包括以下哪些功能?A. 原理图捕获B. 波形仿真C. 代码编译D. 硬件调试答案:ABD7. 在EDA设计中,以下哪些是常见的设计阶段?A. 需求分析B. 逻辑设计C. 物理设计D. 测试验证答案:ABCD8. 以下哪些是EDA设计中常用的硬件描述语言?A. VHDLB. VerilogC. C++D. SystemVerilog9. 在EDA设计流程中,以下哪些是布局布线阶段的任务?A. 确定电路的物理布局B. 优化电路的布线C. 进行时序分析D. 编写测试代码答案:ABC10. 以下哪些是FPGA设计的优势?A. 快速原型验证B. 灵活性高C. 成本较低D. 易于集成答案:ABCD三、判断题(每题2分,共10分)11. EDA工具可以完全替代人工进行电路设计。

()答案:×12. HDL语言可以用来描述数字电路的行为。

()答案:√13. FPGA设计不需要进行时序分析。

()答案:×14. EDA设计流程中,仿真测试是最后一步。

()答案:×15. 逻辑综合是将HDL代码转换为门级网表的过程。

EDA试题题库及参考答案

一、选择题:(20分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是:___D__A. CPLD是基于查找表结构的可编程逻辑器件B. CPLD即是现场可编程逻辑器件的英文简称C. 早期的CPLD是从FPGA的结构扩展而来D. 在Xilinx公司生产的器件中,XC9500系列属CPLD结构2.基于VHDL设计的仿真包括有①门级时序仿真、②行为仿真、③功能仿真和④前端功能仿真这四种,按照自顶向下的设计流程,其先后顺序应该是:_________DA.①②③④ B.②①④③C.④③②①D.②④③①3.下面对利用原理图输入设计方法进行数字电路系统设计,哪一种说法是正确的:__________BA.原理图输入设计方法直观便捷,很适合完成较大规模的电路系统设计B.原理图输入设计方法多用于较规范、规模不大的电路设计,和HDL代码描述方法均可以被综合,相得益彰C.原理图输入设计方法无法对电路进行功能描述D.原理图输入设计方法不适合进行层次化设计4.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是:_______DA.PROCESS为一无限循环语句B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动C.当前进程中声明的变量不可用于其他进程D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成5.对于信号和变量的说法,哪一个是不正确的:_________AA.信号用于作为进程中局部数据存储单元B.变量的赋值是立即完成的C.信号在整个结构体内的任何地方都能适用D.变量和信号的赋值符号不一样6.进程中的信号赋值语句,其信号更新是___C____。

A.按顺序完成;B.比变量更快完成;C.在进程的最后完成;D.都不对。

7.VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库:_______D A.IEEE库B.VITAL库C.STD库D.WORK工作库8.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述___________。

EDA期末试卷

2010—2011学年第一学期期末考试试卷(闭卷)年级专业(本)课程名称 EDA技术基础教师出题时请勿超出边界虚线;2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线;3、答题请用蓝、黑钢笔或圆珠笔。

一、单项选择题(30分)1.以下描述错误的是 CA.QuartusII是Altera提供的FPGA/CPLD集成开发环境B.Altera是世界上最大的可编程逻辑器件供应商之一C.MAX+plusII是Altera前一代FPGA/CPLD集成开发环境QuartusII的更新换代新产品D.QuartusII完全支持VHDL、Verilog的设计流程2.以下工具中属于FPGA/CPLD开发工具中的专用综合器的是 BA.ModelSim B.Leonardo Spectrum C.Active HDL D.QuartusII3.以下器件中属于Xilinx 公司生产的是 CA.ispLSI系列器件 B.MAX系列器件C.XC9500系列器件 D.FLEX系列器件4.以下关于信号和变量的描述中错误的是 BA.信号是描述硬件系统的基本数据对象,它的性质类似于连接线B.信号的定义范围是结构体、进程 //在整个结构体的任何地方都能使用C.除了没有方向说明以外,信号与实体的端口概念是一致的D.在进程中不能将变量列入敏感信号列表中5.以下关于状态机的描述中正确的是 BA.Moore型状态机其输出是当前状态和所有输入的函数//Mealy型状态机其输出信号是当前状态和当前输入的函数B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数D.以上都不对6.下列标识符中, B 是不合法的标识符。

A.PP0 B.END C.Not_Ack D.sig7.大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是 C 。

A//.FPGA即是现场可编程逻辑器件的英文简称CPLD复杂可编程逻辑器件B.CPLD是基于查找表结构的可编程逻辑器件C.早期的CPLD是从GAL的结构扩展而来D.在Altera公司生产的器件中,FLEX10K 系列属CPLD结构8.综合是EDA设计流程的关键步骤,在下面对综合的描述中, D 是错误的。

福师21年2月《EDA技术》期末考试A卷答案

福师21年2月《EDA技术》期末考试A卷答案《EDA技术》期末考试A卷成绩:第一题:填空题(每题3分,共30分,)1.EDA技术的发展分为CAD、CAE和_______EDA____三个阶段。

2.EDA的设计输入主要包括文本输入、图形输入、波形输入。

3.当前最流行的并成为IEEE标准的硬件描述语言包括:_VHDL____和VerilogHDL。

4.有三种端口类型,分别是物理端口、__逻辑端口__和自定义端口。

5.输入和双向端口不能声明为寄存器型。

6.在常量表达示中,二进制是用B字母表示,八进制是用O字母表示,十六进制是用H字母表示。

7.宽度为1位的变量称为标量,如果在变量声明中没有指定位宽,则默认为标量。

线宽大于1位的变量(包括net型和variable型)称为向量。

8.表达式:8`h55&&8`haa的值为1,表达式:8`h55 & 8`haa的值为多少。

9.语句out=sel?1.什么是IP复用技术?IP核对EDA技术的应用和发展有什么意义?IP可重复使用的一种功能设计,可节省设计时间、缩短开发周期,避免重复劳动为大规模SOC设计提供开发基础和开发平台。

IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。

2.基于FPGA/CPLD的数字系统没计流程包括哪些步骤?(1)设计输入,用一定的逻辑表达手段表达出来。

(2)逻辑综合,将用一定的逻辑表达手段表达出来的设计经过一系列的操作,分解成一系列的逻辑电路及对应关系(电路分解)。

(3)目标器件的适配,在选用的目标器件中建立这些基本逻辑电路的对应关系(逻辑实现)。

(4)目标器件的编程/下载,将前面的软件设计经过编程变成具体的设计系统(物理实现)。

(5)仿真/硬件测试,验证所设计的系统是否符合要求。

同时,再设计过程中要进行有关“仿真”,即模拟有关设计结果,验证是否与设计构想相符。

3.说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?具有可编程,可擦除,可长期保持数据的优点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(A卷)

赣南师范学院

2010—2011学年第一学期期末考试试卷(A卷)(闭卷)年级 2008 专业电子科学与技术(本)课程名称 EDA技术基础

2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线;

3、答题请用蓝、黑钢笔或圆珠笔。

一、单项选择题(30分,每题2分)

1.以下关于适配描述错误的是 B

A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件

B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列

C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真

D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供

2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。

A.器件外部特性B.器件的综合约束

C.器件外部特性与内部功能D.器件的内部功能

3.下列标识符中, B 是不合法的标识符。

A.State0 B.9moon C.Not_Ack_0 D.signall

4.以下工具中属于FPGA/CPLD集成化开发工具的是 D

A.ModelSim B.Synplify Pro

C.MATLAB D.QuartusII

5.进程中的变量赋值语句,其变量更新是 A 。

A.立即完成B.按顺序完成

C.在进程的最后完成D.都不对

6.以下关于CASE语句描述中错误的是 A

A.CASE语句执行中可以不必选中所列条件名的一条

B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>”

C.CASE语句中的选择值只能出现一次

D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围

7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH

B.STD_LOGIC_1164

C.STD_LOGIC_UNSIGNED

D.STD_LOGIC_SIGNED

8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→A →综合→适配→时序仿真→编程下载→硬件测试。

A.功能仿真B.逻辑综合C.配置D.引脚锁定

9.不完整的IF语句,其综合结果可实现 D

A.三态控制电路B.条件相或的逻辑电路

C.双向控制电路D.时序逻辑电路

10.下列语句中,属于并行语句的是A

A.进程语句B.IF语句C.CASE语句D.FOR语句11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。

A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件

B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的

C.综合是纯软件的转换过程,与器件硬件结构无关

D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束

12.CPLD的可编程是主要基于什么结构 D 。

A.查找表(LUT)B.ROM可编程

C.PAL可编程D.与或阵列可编程

13.以下器件中属于Altera 公司生产的是 B

A.ispLSI系列器件B.MAX系列器件

C.XC9500系列器件D.Virtex系列器件

14.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D

A.if clk'event and clk = '1' then B.if clk'stable and not clk = '1' then C.if rising_edge(clk) then D.if not clk'stable and clk = '1' then 15.以下关于状态机的描述中正确的是 B

A.Moore型状态机其输出是当前状态和所有输入的函数

B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数

(A卷)

D.以上都不对

(A卷)

二、EDA名词解释,写出下列缩写的中文含义(10分,每题2分)

1.FPGA:现场可编程门阵列

2.HDL:硬件描述语言

3.LE:逻辑单元

4.FSM:有限状态机

5.SOPC:可编程片上系统

三、程序填空题(20分,每空2分)

以下是一个模为60(0~59)的8421BCD码加法计数器VHDL描述,请补充完

请回答问题:在程序中存在两处错误,试指出并修改正确(如果是缺少语句请指出应该插入的行号)

答:

(1)12行begin 改为then

(2)第2行和第3行见加USE IEEE.STD_LOGIC_UNSIGNED.ALL;

(A卷)

五、程序设计题(28分)

1.试用VHDL描述一个外部特性如图所示的数据选择器,S为控制端口。

(10分)

Library IEEE;

Use IEEE.std_logic_1164.all;

Entity sjxz IS

Port(A,B,S:in std_logic;

Q:out std_logic);

END entity sjxz;

Architecture bhv of sjxz IS

Process(S)

Begin

IF S=’0’ Then Q<=A;

ELSE Q<=B;

END IF;

END PROCESS’

END bhv;

2.下图为某一状态机对应的状态图,试用VHDL语言描述这一状态机。

(18分)

1

Library IEEE;

Use IEEE.std_logic_1164.all;

Use IEEE.std_logic_unsigned.all;

Entity FSM1 IS

PORT(clk,rst:in std_logic;

In1:in std_logic;

Out1:out std_logic_vector(3 downto 0)); END entity FSM1;

Architecture bhv of FSM1 IS

TYPE FSM_ST IS(S0,S1,S2,S3);

Singnal C_ST:FSM_ST;

Begin

Process(clk,rst)

Begin

IF rst=’1’ then C_ST<=S0;

ELSIF clk’event AND clk=’1’then

CASE C_ST IS

When S0=>IF In1=’1’ then C_ST<=S1;

ELSE C_ST<=S0;

END IF;

Out1<=”0000”;

When S1=>IF In1=’0’ then C_ST<=S2;

ELSE C_ST<=S1;

END IF;

Out1<=”1001”;

When S2=>IF In1=’1’ then C_ST<=S3;

ELSE C_ST<=S2;

END IF;

Out1<=”1100

”;

When S3=>IF In1=’0’ then C_ST<=S0;

ELSE C_ST<=S3;

END IF;

Out1<=”1111”;

END CASE;

END IF;

END process;

END bhv;。