HT6872

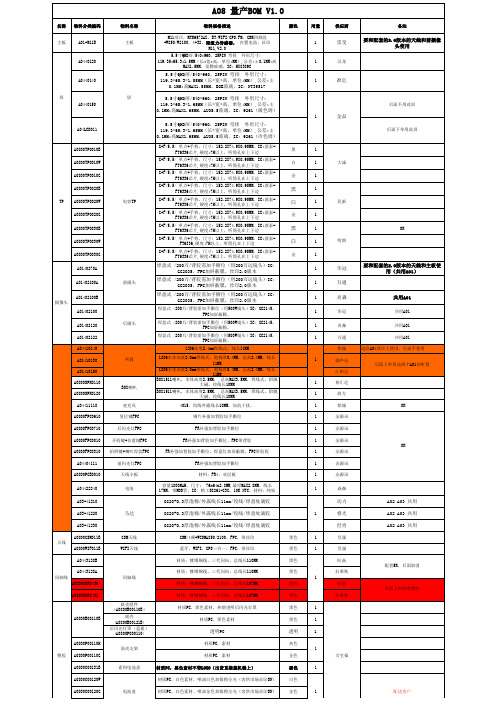

A08 001 C5 量产BOM(不带光感)2015-04-20--后2百万摄像头

黑 白

金

黑 白

金

OK

焊盘式 /200万/背胶需加手撕位(用200万远镜头)IC: GC2035,FPC加屏蔽膜。丝印2.0版本 焊盘式 /200万/背胶需加手撕位(用200万远镜头)IC: GC2035,FPC加屏蔽膜。丝印2.0版本 焊盘式 /200万/背胶需加手撕位(用200万远镜头)IC: GC2035,FPC加屏蔽膜。丝印2.0版本

G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 电容TP G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336,硬度:7H以上,听筒孔在上下边 G+F/5.5/ 单点+手势,尺寸:152.2X74.9X0.95MM. IC:敦泰FT6336芯片,硬度:7H以上,听筒孔在上下边 黑 白 金 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 明朗 民新 大诚

HT-68数字联网型带安防可视对讲系统方案

1 管理中心管理中心服务器台 12 管理中心中心交换机16口台 13 单元竖井工作组交换机8口台 14 单元竖井单模光纤收发器台155 单元竖井电源箱HT68-PY11 台 26 单元竖井数字联网器HT68-SLW11 台157 小区门口机HT68-DM12 台 2 3、系统设计介绍本系统是一种总线制全数字双向对讲报警系统。

其采用数字编码技术和双向通讯传输技术,整个系统内置解码方式、能双向通讯,即室内分机能向管理中心报警,并与管理中心、门口机实现双向呼叫。

其系统网络为室内分机至门口机是5芯线+视频电缆连接;数字联网器至接线交换机是网络线连接;接线交换机至中心交换机是光纤连接,每路接一台光纤收发器。

根据小区特点在小区物业管理中心设置一台管理中心服务器;每个单元入口设置一台可视门口主机、数字联网器、层间平台、每户室内设置一台可视室内机。

4、系统设备功能技术说明4.1 编码式黑白单元门口机:HT68-DD12功能特点:※纯铝压铸一体成型工艺,具有独特整体美观,外观豪华大方。

※LED数码管显示。

※编码式操作,具备中英文房号转换功能。

※最低照度:0.2Lux※视频输出:1Vp_p 75Ω※频率响应:300~3400Hz±3dB※静态工作电流:≤45mA;110 mA(含门禁)※动态工作电流:≤290mA(含摄像头)※工作温度:-20℃~45℃※工作湿度:+45%~85%※埋墙尺寸:(W)130mm*(H)363mm*(D)48mm4.2免提式黑白可视室内机:HT685-A20J/4"功能特点:※外观新颖大方,具备可视对讲、开锁、监视、信息查阅、来访图像查询、呼叫管理中心、安防报警等基本功能。

※可视分机具有分机故障户户隔离的功能,只有在呼叫此室内机时,室内机内的音、视频通道才与系统接通,因此,室内机出现短路故障不会影响系统正常工作。

※门口机呼叫室内机时,室内机显示来访者图像,并有优雅的和弦音乐振铃声(室内若无人接听,则约45秒后门口机自动挂机)。

大型钢轨探伤车X-FIRE70°探轮晶片的应用

设备管理3年第期采用小型探伤仪器(探伤小车)人工检测钢轨伤损漏检率高,工作效率低,劳动强度大,探伤人员工作环境恶劣,安全性差,不能满足铁路提速要求。

采用大型钢轨探伤车可提高探伤检测速度及钢轨伤损检出率,降低错、漏检率,改善探伤人员工作条件,降低劳动强度,提高工作效率,满足铁路发展需求。

根据我国铁路养路机械化的发展方针,武汉铁路局主要干线钢轨探伤采用以大型钢轨探伤车为主、人工检测为辅的模式,特别是武广、合武、宜万、石武等高速线路开通后,人工检测难度增大,主要依靠钢轨探伤车定期进行检测,确保线路运营安全。

1G TC -6型钢轨探伤车X -FI R E 探轮晶片原理偏斜70°探头换能器的声束与钢轨纵向形成了一个经过优化的夹角,用以发现轨头内核伤和钢轨焊接接头头部的夹渣、气孔和裂纹等。

为扩大对轨头的扫查范围,探头在轨面的位置应与纵轴呈20°(或14°)偏角,使入射钢轨中的横波经轨头下颚作二次反射,利用一次波和二次波同时进行探测,主要检查轨头内侧的小核伤(补充直打70°探轮不能检测到的区域),尤其是轨面龟裂等伤损,其探伤灵敏度较高,便于发现较小的缺陷。

(1)一次波。

指从探头直接发射的超声波在钢轨中尚未被轨颚反射之前,由缺陷或端面反射回来的回波。

一次波可探测的范围不到轨头总面积的30%。

(2)二次波。

指超声波经轨颚反射后继续前进,在尚未被轨顶反射之前,由伤损或断面反射回来的波。

二次波探测的范围约占轨头总面积的60%。

二次波在轨头扫查的范围包括一次波的扫查范围。

图1为波束覆盖轨头截面及盲区示意图。

2G TC -6型钢轨探伤车X -FI R E 探轮晶片探伤难度(1)客观局限性。

分析道岔区、曲线、焊缝等地段的伤损困难,因为道岔区、曲线地段的探伤小车对中不是很好,探轮可能不在钢轨的中心位置,探轮打偏致使信息量过大,造成误判或漏判。

焊缝伤损由于焊接工艺不同,超声波反射回来的信息也不同,铝热焊晶粒较为粗大,反射信息过多,且焊筋较宽大,超声波反射回来的信息多而强烈,容易造成误判。

HT6222

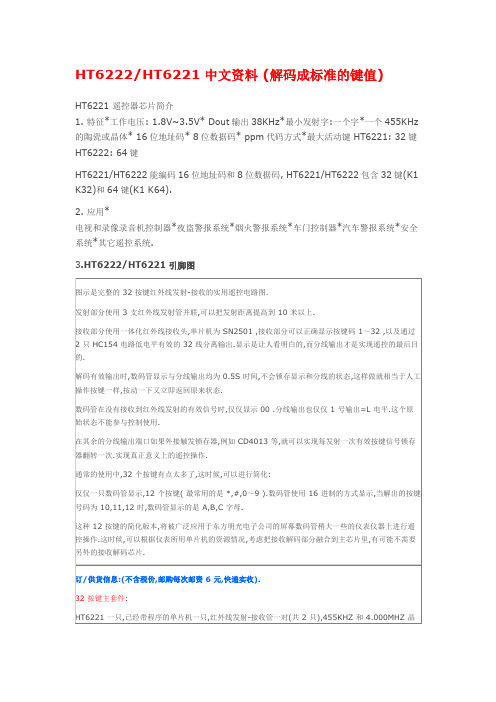

HT6222/HT6221中文资料 (解码成标准的键值)

HT6221 遥控器芯片简介

1. 特征*工作电压: 1.8V~3.5V* Dout输出38KHz*最小发射字:一个字*一个455KHz 的陶瓷或晶体* 16位地址码* 8位数据码* ppm代码方式*最大活动键 HT6221: 32键HT6222: 64键

HT6221/HT6222能编码16位地址码和8位数据码, HT6221/HT6222包含32键(K1 K32)和64键(K1 K64).

2. 应用*

电视和录像录音机控制器*夜盗警报系统*烟火警报系统*车门控制器*汽车警报系统*安全系统*其它遥控系统.

3.HT6222/HT6221引脚图

体各一只.晶体配套电容器共 4 只,按套供货.

12 按键成品:

遥控发射使用带 12 按键的塑料外壳封装,接收解码成品印刷板一件,按套供货.

其它组合情况:例如:为保密而不使用数码管显示...,根据需要自动发射一个或者一组号码...,代替近距离的导线连接,把数字或者控制信号用红外线传递...,制作真正意义上的密码锁(仅仅按动一个按键就发出一组号码,旁人看不到按动了什么按键和号码)...,制作无导线连接的多屏幕显示的子母钟或者仪表...实在不能一一例举.

分享到搜狐微博。

一般对讲机元件清单

0.7 0.38

液晶屏芯片

单价 锐得尔 1.9 嘉立创 3.02 刘志强 网购 备注 10月21日

1

10月23日

0.46 0.3

10月21日 10月21日

其他IC

单价 锐得尔 嘉立创 网购 备注

1.49

1月17日

盒中,暂时无法精确数量; 代表少于100PCS; 代表少于50PCS;

件盒上;其上面数值的颜色表示为元件盒的颜色;

其他IC

单价 网购 1.5 备注 序号 名称 1 2 杭州中科 微 3 4 5 6 7 PL2303TA SGM3005 规格 SSOP8_ 208mil,USB转RS232控制器 MSOP10,模拟开关芯片 数量 6

公网模块

单价 锐得尔 嘉立创 刘志强 网购 ZTE中兴 220 240 备注 备注:元件放置元件盒中,暂时无法精确数量; 代表少于100PCS; 代表少于50PCS;

拆分;其上面颜色表示区分元件的误差值;

黑色,嘉立创为绿色,辉哥朋友为蓝色,其他待定;

值上批示表示为厂商名称;

数量 400

单价 锐得尔 嘉立创 5.17 9.42 刘志强 5.12 5.5 7.5

5

18.22

7.47

电源管理器

序号 名称 1 2 3 4 5 6 7 8 9 10 ETA1039 LC2740CD8TR SG1138CB5TR SOT23-6,5V/3A升压器 SO-8,DC/DC SOT-23-5,DC/DC 0.55 MIC5205-3.3YM5 TP4056 6210A-332 SY8089AAAC 规格 SOT23-5,3.3V/150mA-美国微 芯LDO SOP8-EP,1.2A/8V-南京拓微/ 电池电源管理芯片 SOT23-5 SOT23-5,DC-DC芯片 0 0.55 数量 1500 200 单价 锐得尔 0.65 嘉立创 1.2用完不 买 0.71用完 不买 代理

Intersil推出新款HD-SDI发射器和接收器

Intersil推出新款HD-SDI发射器和接收器

佚名

【期刊名称】《电子设计工程》

【年(卷),期】2014(22)13

【摘要】创新电源管理与精密模拟解决方案领先供应商Intersil公司推出采用

VC-2标准的DIRAC压缩技术的TW6872HD—SDI视频发射器和TW6874HD—SDI四路接收器,这是一款帮助在更长电缆距离上实现画面完美、无延迟视频传输的端到端的解决方案。

这些新产品符合SMPTE(美国电影电视工程师协会)有关标清(SD)、高清(HD)和3G串行数字传输的各项标准,

【总页数】1页(P148-148)

【关键词】四路接收器;SDI;发射器;Intersil公司;HD;视频传输;DIRAC;压缩技术【正文语种】中文

【中图分类】TN85

【相关文献】

1.Vishay推出采用独特SurfLight表面发射器技术的新款850nm红外发射器 [J],

2.安捷伦推出新型光纤发射器和接收器 [J], 无

3.Avago推出光纤短链路发射器/接收器 [J],

4.Intersil推出带ESD保护的超小型RS-485/RS-422单发射器 [J],

5.泰克推出业界完整、灵活的自动PCI Express 3.0 Tx、Rx测试套件全面的接收器和发射器解决方案为集成电路、主机和板卡设计人员提供一站式PCIe 3.0测试与调试 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

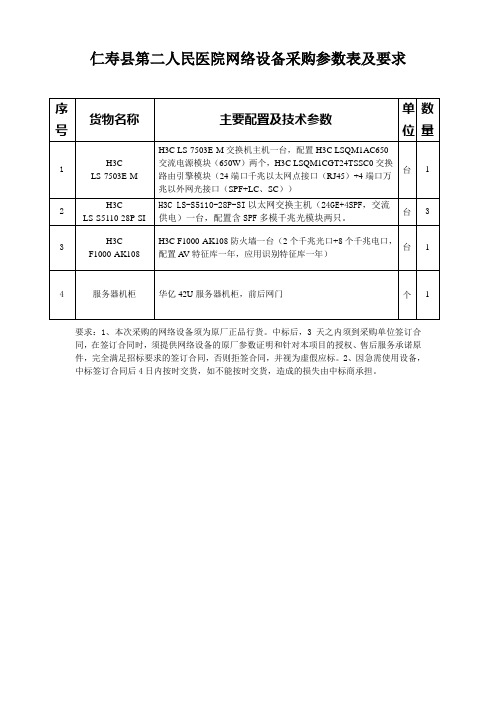

仁寿县第二人民医院网络设备采购参数表及要求

1

2

H3C LS-S5110-28P-SI

H3C LS-S5110-28P-SI以太网交换主机(24GE+4SPF,交流供电)一台,配置含SPF多模千兆光模块两只。

台

3

3

H3C F1000-AK108

H3C F1000-AK108防火墙一台(2个千兆光口+8个千兆电口,配置AV特征库一年,应用识别特征库一年)

仁寿县第二人民医院网络设备采购参数表及要求

序号

货物名称

主要配置及技术参数

单位

数量

1

H3C LS-7503E-M

H3C LS-7503E-M交换机主机一台,配置H3C LSQM1AC650交流电源模块(650W)两个,H3C LSQM1CGT24TSSC0交换路由引擎模块(24端口千兆以太网点接口(R;LC、SC))

台

1

4

服务器机柜

华亿42U服务器机柜,前后网门

个

1

要求:1、本次采购的网络设备须为原厂正品行货。中标后,3天之内须到采购单位签订合同,在签订合同时,须提供网络设备的原厂参数证明和针对本项目的授权、售后服务承诺原件,完全满足招标要求的签订合同,否则拒签合同,并视为虚假应标。2、因急需使用设备,中标签订合同后4日内按时交货,如不能按时交货,造成的损失由中标商承担。

光纤热缩管分类

器件外径( 后)DeviceO.D.(aftershrink)

60601410 1.4±0.05 1.3±0.1

收缩

0c85f9e 易博

60±1 3.0±0.1mm 3、★单芯石英型 产品特征 符合 RoHS

特殊设计由交联聚烯烃,热熔管和增强型不 锈钢(石英,或陶瓷)构成

光纤接续保护元件,不影响光纤旳光导特征 保护接续点,提升机械强度 操作简朴,降低安装时损伤光纤旳危险

密封构造使接续具有良好旳耐温度、湿度性 能

光纤接续保护元件,不影响光纤旳光导特征 保护接续点,提升机械强度 操作简朴,降低安装时损伤光纤旳危险

密封构造使接续具有良好旳耐温度、湿度性 能

产品编号 PartNo. 钢棒外径(mm)

0c85f9e 易博

SteelRodO.D.(mm) 热熔管内径(mm) FusionTubeI.D.(mm) 热缩管长度(mm) HeatShrinkTubeLength(mm)

操作简朴,降低安装时损伤光纤旳危险 密封构造使接续具有良好旳耐温度、湿度性 能 4、★双陶瓷型 产品特征

符合 RoHS 特殊设计由交联聚烯烃,热熔管和增强型不 锈钢(石英,或陶瓷)构成 光纤接续保护元件,不影响光纤旳光导特征 保护接续点,提升机械强度

0c85f9e 易博

操作简朴,降低安装时损伤光纤旳危险

符合 RoHS 特殊设计由交联聚烯烃,热熔管和增强型不 锈钢(石英,或陶瓷)构成 光纤接续保护元件,不影响光纤旳光导特征 保护接续点,提升机械强度

0c85f9e 易博

操作简朴,降低安装时损伤光纤旳危险 密封构造使接续具有良好旳耐温度、湿度性 能 2、★单石英型 产品特征

符合 RoHS 特殊设计由交联聚烯烃,热熔管和增强型不 锈钢(石英,或陶瓷)构成 光纤接续保护元件,不影响光纤旳光导特征 保护接续点,提升机械强度

2018年主流智能音箱方案汇总(更新到7月底)

3.7V/2500mA 18650锂电池; USB5V

BQ27421系统端电量计;MTK

MT6323GA电源管理IC;

N/A

N/A

7MIC

N/A 30W

N/A N/A

DC18V/2A:深圳市 天音电子有限公司

斐讯R1

JBL GO Smart智能 音箱

亲见M10人 工智能视频 音箱

瑞芯微RK3229

喜玛拉雅 小 雅AI音箱

全志R16 内置4核A7

美光MT29F32G08CBADA 4GB FLASH,

南亚NT5CC256M16EP-EK DDR3内存4GB

7MIC

TI TLV320ADC

3101

NTP8825 D类 功放

正基AP6212 WIFI+BT4.2模组,

SY7215升压IC,SY6982两节升压充电

DC12V/1A:江苏辰 阳电子有限公司生 产,产品型号 CYSN12-120100C 。

MTK的MT8516

旺宏1G闪存 MX30LF1G18AC;

TPS653208 3A同步整流降压转换器; DC12V/1A:江苏辰

2MIC (S1869)

TI TLV320ADC 3101 ADC;

NXP TFA9895 D类音频放大器

4MIC

芯智汇 AC108(四 路输入)

上海艾为 AW87318

2W4Ω单喇 芯智汇AXP223的电源系统管理芯

叭,无被动 盆

片;TI的TLV62565降压芯片;

USB5V/2A:制造商 为雅士电业有限公 司,型号为ECVC+ 10050-2000

存;

Micron美光2G Flash

MTK的MT8516

HT7612规格书

Selection TableBlock DiagramRev.1.701July 16,2012·CDS input·CDS debounce time:HT7612:15~20seconds HT7612B:<3seconds·High noise immunity·Output drive buzzer alarm ·Low voltage detector ·Override function·16-pin DIP/NSOP packagesGeneral DescriptionThe HT7612/HT7612B is PIR controller specifically de-signed to interface to PIR sensors to implement motion sensing application products such as intruder alarms.The controller has the features of PIR sensitivity adjust-ment and a CDS can be connected to the controller for automatic detection.The HT7612/HT7612B is available in low profile NSOP &DIP packages.Applications·PIR light control ·Motion detectors·Alarm system ·Auto door bellsPin AssignmentPin DescriptionRev.1.702July16,2012Absolute Maximum RatingsSupply Voltage...........................V SS-0.3V to V SS+6.0V Storage Temperature............................-50°C to125°C Input Voltage..............................V SS-0.3V to V DD+0.3V Operating Temperature...........................-40°C to85°C Zero Crossing Current................................Max.300m ANote:These are stress ratings only.Stresses exceeding the range specified under²Absolute Maximum Ratings²may cause substantial damage to the device.Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability. Electrical Characteristics Ta=25°CNote:When VDD is less than3.4V,then the V REF voltage will be equal to VDD.If the V REF voltage is less than the PIR working voltage,then the PIR sensor will not work normally.Rev.1.703July16,2012Rev.1.704July 16,2012Functional DescriptionThe following gives a description of the functional pins on the device.TESTThe TEST pin is an output which is used to test the 32KHz system frequency.Note that the pin is a shared TEST/SC pin.The TEST output pin can be used within 1second after power-on.SCThe SC pin is an output pin which is used to for LVD and CDS detection.Note the pin is a shared TEST/SC pin.The SC pin can be used 1second after power-on.DTThe DT pin is a delay time oscillator input pin.It is con-nected to an external RC to obtain the desired output turn-on duration.Variable output turn-on durations can be achieved by selecting various values of RC or using a variable resistor.The DT structure is shown in Fig.1.BUZ/BUZThe BUZ &BUZ pins are both CMOS output structures.They will output 4beep sounds within 1second to indi-cate that the warm-up time has completed.These differ-ential output pins can be used to drive a piezo buzzer.The BUZ/BUZ structure are shown in Fig.2.RELAYThe RELAY pin is a CMOS output structure which is nor-mally low and active high.The high duration is con-trolled by the delay time oscillator and the MODE pin.The RELAY pin structure is shown in Fig.3.TRIACThe TRIAC pin is a CMOS output structure which will output a series of pulses when active.The pulse train is synchronised by the ZC (zero crossing)input.The ac-tive duration is controlled by the delay time oscillator and the MODE pin.The TRIAC structure is shown in Fig.4.Fig.1DT Oscillator StructureFig.2Buzzer Pin DriveBuzzerFig.3RELAY Pin Drive RELAYFig.4TRIAC Pin Drive TRIACMODEThe MODE pin is a tristate input which is used to select the desired device operating mode.The device also provides an additional test function on the MODE pin.If the MODE pin is presented with a high pulse,of greater than 400ms duration,within 1second after power-on,the device will be forced into its test mode.When the device enters the test mode the power-on delay time will be changed from its normal op-erating value of 40seconds to 10seconds.ZCThe ZC pin is a CMOS Schmitt trigger input ing suitable ZC signal switching,the device can provide the following functions:·Override controlWhen the device is operating in the AUTO mode,which is when the MODE pin is open,the output will be activated by a valid PIR trigger signal and the out-put active duration will be controlled by a DT oscillat-ing period.The mode can be switched from the AUTO mode to the ²ON ²mode by either connecting the MODE pin to VDD or switching the ZC signal with an OFF/ON operation of the power switch.The term ²override ²refers to the change of operating mode by switching the power switch.The device can be tog-gled from ON to AUTO by an override operation.If thedevice is overridden to ON and there is no further override operations,it will automatically return to the AUTO mode after 8hours.It will flash 3times at a 1Hz rate when returning to the AUTO mode.But if the AUTO mode is changed by switching the MODE switch,it will not flash,as shown in Fig.5.In Fig.6,an external pull-high resistor is required for nor-mal applications.Note:Regarding the priority of the MODE pin and the ZC switching,note that when the MODE pin is connected to VDD or VSS,the MODE state will be determined by the MODE pin.When the MODE pin is OPEN,the MODE state will be determined by the ZC switching.Fig.6ZC Application ExampleRev.1.706July 16,2012CDSThe CDS pin is connected to an internal comparator input.It is used to allow the device to distinguish between day and night conditions.When the CDS input voltage is lower than V L ,the PIR amplifier circuit will be disabled and the TRIAC and RELAY output pins will be inactive.When the input voltage of the CDS is higher than V L ,the outputs are both active.The debounce time for the CDS pin for switch-ing the outputs from an inactive to an active state is about 15~20seconds for the HT7612and less than 3seconds for the HT7612B.Connect this pin to VDD when this func-tion is not used.The CDS timing is shown in Fig.7In Fig.8,R CDS and R Y can be adjusted to obtain the de-sired daytime detection level.LEDThe LED pin is a CMOS output pin which is used as a valid trigger indicator.When the TRIAC/RELAY is acti-vated,this pin will be active until the TRIAC/RELAY has is switched OFF.The LED pin structure is shown in Fig.9.LVDLVD is a low voltage detector.When the detected volt-age is lower than 1.1V,the LED flicker and the buzzer will emit a tone.In Fig10,assume R X ,R LVD can be adjusted to obtain the desired voltage detection level.ComparatorInputV LPIR AmplifierFig.7CDS TimingFig.8CDS Application ExampleFig.9LED Pin Drive LEDFig.10LVD Application ExampleRev.1.707July 16,2012Effective Trigger TimingThe effective input trigger signal width should be ³24ms.The output is valid either with (1)trigger signal width ³0.5seconds or (2)more than 2effective trigger inputs within 2seconds (separation of 2triggers ³0.5s).The separation time between two TRIAC(RELAY)turn-on time must be more than 1sec.The trigger timing is shown in Fig.11.RetriggerWhen the output of the comparator is a valid signal,the RELAY/TRIAC will be activated and the active duration is con-trolled by the DT oscillating period.If the previous ²DelayTime t D²has not been exceeded and the next valid signal oc-curs again,the active duration of the RELAY/TRIAC will be restarted.The timing is shown in Fig.12.Fig.12RetriggerFig.11Trigger TimingRev.1.708July 16,2012LVD &CDS Detecting CircuitThe external and internal detecting circuits for LVD and CDS are shown in Fig.13.When the input voltage V LVD is lower than 1.1V,the comparator outputs a low level which means that V DD is lower than the minimum oper-ating voltage (Vmin).When V CDS is lower than V L ,the comparator outputs a high level which means that it is daytime,otherwise it is night.WhereFig.13External Application CircuitNote:When the CDS input voltage is lower than V L ,it means that a daytime condition exists for the PIR circuit.Relationship LVD and CDSThe LVD and CDS trigger timing are shown in Fig.14and Fig.15respectively.In Fig.14,When an LVD condition occurs,the LED will flicker and the buzzer will emit a tone.In Fig.15,When the CDS state changes from low to high,the output of the PIR is enabled after 10sec for the HT7612or 0sec for the HT7612B,and when the CDS sate changes from high to low,will be disabled.Fig.14Trigger Timing of LVDCDS State (Internal signal)Output EnableComparatorInputComparatorOutput10sec for HT7612-Trigger LevelFig.15Trigger Timing of CDSRev.1.709July 16,2012Trigger TimingNote:The output is activated if the trigger signal conformsto the following criteria:1.Two triggers occur within 2seconds and separation time between two triggers is more than 0.5sec.2.The trigger signal sustains duration ³0.5seconds.Application CircuitAC Power Application·TRIACNote:Adjust R9to fit various CDS.Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Change the value of C10to0.33m F/600V for AC220V application.Rev.1.7010July16,2012·RELAYNote:Adjust R9to fit various CDS.Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Change the value of C10to0.33m F/600V for AC220V application.Rev.1.7011July16,2012Note:Adjust R9to fit various CDS.Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Rev.1.7012July16,2012Note:Adjust R9to fit various CDS.Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Use a Photo-transistor instead of a CDS to meet European RoHS standards.Rev.1.7013July16,2012Simplified LED Lighting Application CircuitNote:Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Pin14and pin13should be connected with pull-high resistors when LVD and CDS detection functions are not used.Rev.1.7014July16,2012HT7612+HT7L4091Application Circuit(7W LED Bulb)Note:Adjust R9to fit various CDS.Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Rev.1.7015July16,2012HT7612+HT7L2102Application CircuitNote:Adjust R9to fit various CDS.Adjust R6to obtain the desired output duration.Adjust R5to change PIR sensitivity.Rev.1.7016July16,2012Package InformationNote that the package information provided here is for consultation purposes only.As this information may be updated at regu-lar intervals users are reminded to consult the Holtek website (/english/literature/package.pdf )for the latest version of the package information.16-pin DIP (300mil)Outline Dimensions·MS-001d (see fig1)Rev.1.7017July 16,2012Fig1.Full LeadPackagesFig2.1/2Lead PackagesRev.1.7018July16,2012Rev.1.7019July16,201216-pin NSOP(150mil)Outline Dimensions·MS-012Rev.1.7020July16,2012Product Tape and Reel SpecificationsReel DimensionsRev.1.7021July16,2012Carrier Tape DimensionsSOP16N(150mil)Rev.1.7022July16,2012Rev.1.7023July16,2012。

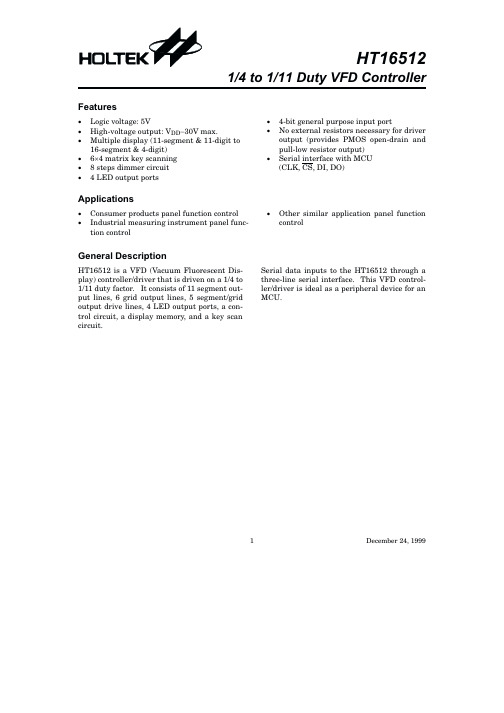

HT16512中文资料

HT165121/4to 1/11Duty VFD Controller1December 24,1999Features·Logic voltage:5V·High-voltage output:V DD -30V max.·Multiple display (11-segment &11-digit to 16-segment &4-digit)·6´4matrix key scanning ·8steps dimmer circuit ·4LED output ports·4-bit general purpose input port·No external resistors necessary for driver output (provides PMOS open-drain and pull-low resistor output)·Serial interface with MCU (CLK,CS,DI,DO)Applications·Consumer products panel function control ·Industrial measuring instrument panel func-tion control·Other similar application panel function controlGeneral DescriptionHT16512is a VFD (Vacuum Fluorescent Dis-play)controller/driver that is driven on a 1/4to 1/11duty factor.It consists of 11segment out-put lines,6grid output lines,5segment/grid output drive lines,4LED output ports,a con-trol circuit,a display memory,and a key scan circuit.Serial data inputs to the HT16512through a three-line serial interface.This VFD control-ler/driver is ideal as a peripheral device for an MCU.Block DiagramPin Assignment2December24,1999Pin DescriptionPin No.Pin Name I/O Description 1~4SW0~SW3I4-bit general purpose input port5DO O Output serial data at the falling edge of the shift clock, starting from low order bit.This is an NMOS open-drain output pin.6DI I Input serial data at the rising edge of the shift clock,start-ing from the low order bit.7,43VSS¾Power supply,ground8CLK I Reads serial data at the rising edge,and outputs data at thefalling edge.9CS I Initializes serial interface at the rising or falling edge of the HT16512.Then it waits to receive a command.Data input after CS has fallen is processed as a command.While com-mand data is processed,current processing is stopped,and the serial interface is initialized.While CS is high,CLK is ignored.10~13K0~K3I Keying data input to these pins is latched at the end of thedisplay cycle.14,38VDD¾Posistive power supply15~20S0/K0~S5/K5O Segment or key source output pins(dual function).This isPMOS open-drain and pull-low resistor output.21~25S6~S10O Segment driver output pins(segment only).This is PMOSopen-drain and pull-low resistor output.26,28~31S11/G10~S15/G6O Segment or Grid driver output pins.These pins are selectable for segment or grid driving.This is PMOS open-drain and pull-low resistor output.27VEE¾VFD power supply37~32G0~G5O Grid driver output pins(Grid only).This is PMOSopen-drain and pull-low resistor output.42~39LED0~LED3O LED driver output ports.This is a CMOS output pin.44OSC I Connected to an external resistor or an RC oscillator cir-cuit.3December24,1999Absolute Maximum RatingsSupply Voltage..............................-0.3V to5.5V Operating Temperature..............-25°C to75°C Input Voltage.................V SS-0.3V to V DD+0.3V Storage Temperature.................-50°C to125°CNote:These are stress ratings only.Stresses exceeding the range specified under²Absolute Maxi-mum Ratings²may cause substantial damage to the device.Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged expo-sure to extreme conditions may affect device reliability.D.C.Characteristics Ta=25°CSymbol ParameterTest ConditionsMin.Typ.Max.Unit V DD ConditionsV DD Logic Supply Voltage¾¾ 4.55 5.5V V EE VFD Supply Voltage¾¾0¾V DD-30V f OSC Oscillation Frequency5V R OSC=51k W350500650kHz R PL Output Pull-low Resistor5V Driver output50100150k WI DD Operating Current5V No load,VFD display off¾¾5mAI OL Driver Leakage Current5V V O=V DD-30VVFD driver off¾¾-10m AI OL1LED Sink Current5V V OL=1VLED0~LED320¾¾mAI OH1LED Source Current5V V OH=0.9V DDLED0~LED3-1¾¾mAI OH21Segment/Key Source Current5V V OH=V DD-2VS0/K0~S5/K5,S6~S10-3¾¾mA 4December24,1999Symbol ParameterTest ConditionsMin.Typ.Max.Unit V DD ConditionsI OH22Segment/Grid Source Current5V V OH=V DD-2VG0~G5,S11/G10~S15/G6-15¾¾mAI OL3DO Sink Current5V V OL=0.4V4¾¾mA V IH²H²Input Voltage¾¾0.7V DD¾V DD V V IL²L²Input Voltage¾¾0¾0.3V DD V V OH1High-level Output Voltage5V LED0~LED3,I OH1=-1mA0.9V DD¾V DD VV OL1Low-level Output Voltage5V LED0~LED3,I OL1=20mA0¾1V V OL2Low-level Output Voltage5V DO,I OL2=4mA0¾0.4V A.C.Characteristics Ta=25°CSymbol ParameterTest ConditionsMin.Typ.Max.Unit V DD Conditionst PHLPropagation Delay Time 5V CLK®DOC L=15pF,R L=10k W¾¾300nst PLH5V¾¾100nst r1Rise Time 5V C L=300pF,S0~S10¾¾2m st r25V C L=300pF,G0~G5,S11/G10~S15/G6¾¾0.5m st f Fall Time5V C L=300pF,Sn,Gn¾¾120m st max Maximum Clock Frequency5V Duty=50%1¾¾MHz C i Input Capacitance5V¾¾¾15pF t CW Clock Pulse Width5V¾400¾¾nst SW Strobe Pulse Width5V¾1¾¾ust SU Data Setup Time5V¾100¾¾nst h Data Hold Time5V¾100¾¾nst CS Clock-Strobe Time5V CLK rising edge toCS rising edge1¾¾m st W Wait Time5V CLK rising edge toCLK falling edge1¾¾m s5December24,1999Functional DescriptionDisplay RAM and display modeThe static display RAM is organized into22´8 bits and stores the data transmitted from an ex-ternal device to the HT16512through a serial interface.The contents of the RAM are directly mapped to the contents of the VFD driver.Data in the RAM can be accessed through the data setting,address setting and display control commands.It is assigned addresses in8-bit unit as follows:Dimming controlHT16512porvides8-step dimmer function on display by controlling the3-bit binary com-mand code.The full pulse width of grid signal is divides into16uniform sections by PWM(pulse width modulation)technology.The16uniform sections available form8steps dimmer via3-bit binary code.The8-step dim-mer includes1/16,2/16,4/16,10/16,11/16, 12/16,13/16and14/16.The1/16pulse width in-dicates minimum lightness.The14/16pulse width represents maximum lightness.(Refer to the display control command).Key matrix and key-input data storage RAM The key matrix scans the series key states at each level of the key strobe signal (S0/K0~S5/K5)output of the HT16512.The key strobe signal outputs are time-multiplexed sig-nals from S0/K0~S5/K5.The states of inputs K0~K3are sampled by strobe signal S0/K0~S5/K5and latched into the register. The key matrix is made up of a6´4matrix,as shown below.The data of each key is stored as illustrated be-low,and is read with the read command,start-ing from the least significant bit.LED portThe LED port belongs to the CMOS output con-figuration.Data is written to the LED port with the write command,starting from the least port¢s least significant bit.In our application(see applica-tion circuits),the user adopts an internal NMOS device to a driver LED component by connecting VDD.When a bit of this port is0, the corresponding LED lights;when the bit is1, the LED turns off.The data of bits5through8 are ignored.6December24,1999SW dataHT16512provides an extra4-bit general input port.The SW data is provided with available binary code.The SW data is read with the read command,starting from the least significant bit.Bits5 through8of the SW data are0.CommandsCommands set the display mode and status of the VFD driver.The first1byte input to the HT16512through the DI pin after the CS pin has fallen,is regarded as a command.If CS is set high while commands/data are transmitted,serial communication is initial-ized,and the commands/data being transmitted are not valid(however,the commands/data previ-ously transmitted remains valid).·Display mode setting commandsThese commands initialize the HT16512and select the number of segments and the number of grids(1/4~1/11duty,11segments to16segments).When these commands are executed,the display is forcibly turned off,and key scanning is also stopped.To resume display,the display command²ON²must be executed.If the same mode is se-lected,nothing happens.7December24,1999HT165128December 24,1999·Data setting commandsThese commands set the data write and data read modes.·Address setting commandsThese commands set the address of the display memory.If address 16H or higher is set,data is ignored until a valid address is set.·Display control commandsTTiming DiagramsKey scanning and display timingT9December24,1999Serial communication format·Reception(command/data write)·Transmission(data read)·Updating display memory by incrementing address10December24,1999·Updating specific addressesApplication CircuitsNote:R OSC=51k W for oscillator resistorR1=1~10k W for external pull-high resistorR2~R5=750W~1.2k WR6~R9=10k W for external pull-low resistorD1~D6=1N4001Ef=Filament voltage for VFD11December24,199912December 24,1999Copyright ã1999by HOLTEK SEMICONDUCTOR INC.The information appearing in this Data Sheet is believed to be accurate at the time of publication.However,Holtek assumes no responsibility arising from the use of the specifications described.The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification,nor recommends the use of its products for application that may pres-ent a risk to human life due to malfunction or otherwise.Holtek reserves the right to alter its products without prior notification.For the most up-to-date information,please visit our web site at .Holtek Semiconductor Inc.(Headquarters)No.3Creation Rd.II,Science-based Industrial Park,Hsinchu,Taiwan,R.O.C.Tel:886-3-563-1999Fax:886-3-563-1189Holtek Semiconductor Inc.(Taipei Office)5F,No.576,Sec.7Chung Hsiao E.Rd.,Taipei,Taiwan,R.O.C.Tel:886-2-2782-9635Fax:886-2-2782-9636Fax:886-2-2782-7128(International sales hotline)Holtek Semiconductor (Hong Kong)Ltd.RM.711,Tower 2,Cheung Sha Wan Plaza,833Cheung Sha Wan Rd.,Kowloon,Hong Kong Tel:852-2-745-8288Fax:852-2-742-8657。

头盔式双目微光夜视仪研制

头盔式双目微光夜视仪研制

詹启海;常本康;钱芸生

【期刊名称】《红外技术》

【年(卷),期】2005(27)1

【摘要】介绍了头盔式双目激光助视/微光夜视仪的设计,它是由激光助视系统,特种光学镜头,高性能微光像增强器组成的主被合一的新型激光夜视仪器.与以往的国内的夜视眼镜相比,它以非球面物镜以及助视功能为特色,以双管高性能超二代像增强器为核心,参照了国外的最新的头盔微光夜视仪的光学系统数据,灵敏度高,图像清晰,并适于头戴和手持两用,其探测阈值延伸到10-3lx以下,改变了目前大多数的微光夜视仪器固有的缺陷,使得在任何恶劣的条件下也可以正常工作.

【总页数】4页(P19-22)

【作者】詹启海;常本康;钱芸生

【作者单位】南京理工大学,电子工程与光电技术学院,江苏,南京,210094;南京理工大学,电子工程与光电技术学院,江苏,南京,210094;南京理工大学,电子工程与光电技术学院,江苏,南京,210094

【正文语种】中文

【中图分类】TN223

【相关文献】

1.头盔式双目微光夜视仪研制 [J], 高明;强西林;陈智利;高丽

2.双目头盔显示器光学设计中对双目叠加的探讨 [J], 李晓霞

3.双目光学透视式头盔显示器的实验研究 [J], 高伟清;周仕娥;吕国强

4.头盔式单目微光夜视仪中光学系统的设计 [J], 尚华;刘钧;高明;毛翠丽;孟立庄

5.头盔式单目微光夜视仪中非球面物镜系统的设计 [J], 刘钧;尚华;宋波

因版权原因,仅展示原文概要,查看原文内容请购买。

HT6873放大芯片说明可代替LM4871.docx

HT6873(3.4W单声道D类音频功放IC)替换LM4871/CSC8002应用原理说明

LM4871是现在小音箱产品上应用最广泛的一颗音频放大IC,大部分工程师对其应用原理和性能特

点了如指掌,但因为LM4871是AB类,效率相对比较低,功率已经不能满足市场对大功率的要求。

先推荐3.4W单声道D类音频功放IC-HT6873的替换LM4871的应用原理。

HT6873性能介绍

HT6873是一款低EMI的,防削顶失真的,单声道免滤波D类音频功率放大器。

在5V电源,10% THD+N,4Ω负载条件下,输出3.4W功率,在各类音频终端应用中维持高效率并提供AB类放大器的性能。

HT6873能驱动2Ω负载,满足小音箱产品对超大功率的要求。

引脚功能对比

图1 LM4871引脚图

图2 HT6873引脚图

表1 HT6873引脚功能说明

应用电路原理说明

图3 LM4871典型应用原理图

图4 HT6873典型应用原理图

HT6873替换LM4871需要改变的外围说明

1: LM4871管脚1(SD)是低电平时,IC工作,高电平时IC关断,HT6873是带有防破音功能的D 类音频功放IC,其管教1 CTRL的工作模式是:

2: LM4871管脚三(同相输入端)是接1UF电容到地,HT6873的同相输入端(INP)要接与INN匹配的输入电阻、电容,构成差分输入,如图4所示。

3: HT6873不需要外置反馈电阻,用HT6873替换LM4871时,需要把反馈电阻去掉。

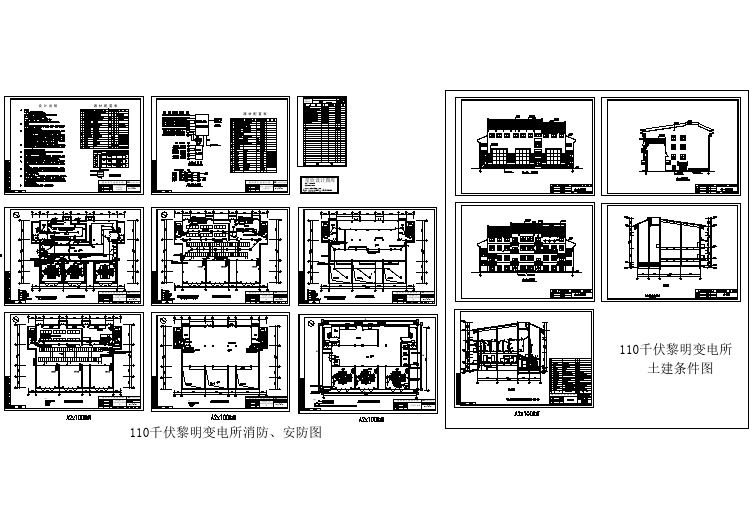

某黎明变电所弱电施工系统方案设计CAD图纸

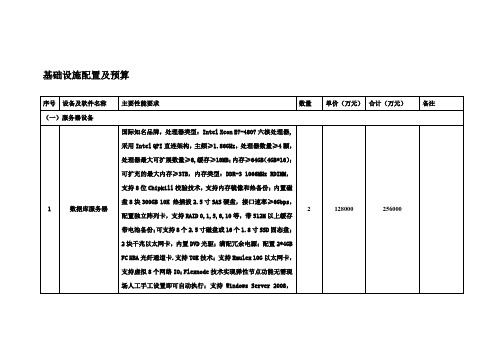

鄂旗二医院基础设施配置-3月17日修改

30000

30000

总计

501000

基础设施配置

序号

设备及软件名称

主要性能要求

数量

单价(万元)

合计(万元)

备注

(一)服务器:Intel XeonE7-4807六核处理器,采用Intel QPI直连架构,主频≥1.86GHz,处理器数量≥4颗,处理器最大可扩展数量≥8,缓存≥18MB;内存≥64GB(4GB*16);可扩充的最大内存≥3TB,内存类型:DDR-3 1066MHz RDIMM,支持8位Chipkill校验技术,支持内存镜像和热备份;内置磁盘8块300GB 10K热插拔2.5寸SAS硬盘,接口速率≥6Gbps,配置独立阵列卡,支持RAID 0,1,5,6,10等,带512M以上缓存带电池备份;可支持8个2.5寸磁盘或16个1.8寸SSD固态盘;2块千兆以太网卡,内置DVD光驱;满配冗余电源;配置2*4GBFCHBA光纤通道卡.支持TOE技术;支持Emulex10G以太网卡,支持虚拟8个网络IO;Flexnode技术实现弹性节点功能无需现场人工手工设置即可自动执行;支持Windows Server 2008,SUSE Linux、Redhat Linux等操作系统;3组(6个)热插拔两段对转式冗余风扇,采用分区散热技术,集成海拔高度计,可根据每个分区的温度传感器及海拔高度来智能调整风扇转速,集成IPMI 2.0支持的IMM(集成管理模块)管理芯片,可支持远程通过浏览器实现设备监控,远程虚拟现场功能;配置光通路诊断面板,可对处理器、VRM、内存、硬盘驱动器、电源及风扇关键部分的故障进行快速诊断,并且在断电后仍能显示故障报警信息,状态LED;BIOS采用最新64位UEFI统一可扩展固件接口技术,ToolsCenter和IMM,Systems Director Active Energy Manage。含机架导轨和线缆走臂、PDU线缆等机架安装配件。提供三年免费保修服务,3年人工,3年现场,3年部件,7*24小时服务,4小时响应。

一种全桥逆变结构高压电源研制

男,

安徽安庆人,

硕士研究生,

工程师。研究方向:

高电压技术、

安检 X 射线源及控制。

-167-

《电子设计工程》2020 年第 4 期

图中可知,除市电输入外,其它各部分间形成一个闭

限制驱动电流,从而减缓驱动脉宽上升和下降沿,减

环控制回路,升压单元进行升压及高压输出,采样、

第 28 卷

Vol.28

第4期

No.4

电子设计工程

Electronic Design Engineering

2020 年 2 月

Feb. 2020

一种全桥逆变结构高压电源研制

徐陈勇

(公安部第一研究所 北京 100048)

摘 要 :为 满 足 X 光 安 全 检 查 领 域 的 X 射 线 管 正 常 工 作 要 求 ,需 要 设 计 满 足 中给阴阳极施加高压的电源及给灯丝

X 射线管用 160 kV/2 mA 高压电源,并给出了相关验

加热的电源是其核心部分,本文主要讨论高压电源

部分的设计。

随着电力电子技术进步,高频逆变技术获得了

大范围应用,且已渗透到各行各业,大力促进了科技

发展。同样在 X 射线领域,其功率电路也已从传统

的工频工作模式转换为了高频逆变模式 [4]。文中采

收稿日期:2019-07-01

稿件编号:201907006

波形。

1 系统结构

为得到满足给定要求输出,整个高压电源系统

需要包括交流输入、高频逆变、升压单元、输出采样、

信号控制、逆变驱动等,各部分之间的相互关系如下

图 1 所示,其中交流输入采用日常市电 220VAC。从

inspection,it is necessary to design a high-voltage power supply that meets the requirements for its use.

holtek ht68fb571 led pwm function application desc

HT68FB571 LED PWM Function Application DescriptionD/N: AN0503EIntroductionThe Holtek HT68FB571 USB Flash LED MCU, which is specially designed for singlecolour LED Gaming Keyboard applications, can simultaneously interface up to 128 singlecolour LEDs by using a matrix scanning method. The integrated 8-bit PWM functions canbe used for finely tuning LED brightness. The I/Os, which are equipped with directlydriving LED capacity, save the added cost of additional external transistors. In addition,the device also offers a high scanning frame update rate of 1.5kHz. The key pins of theauto key scan function are pin-shared with the LED PWM function pins thus greatlyreducing the MCU package pin number which leads to reduced product development timeand cost. This document gives a description of the related registers and operationprocedures for the HT68FB571 LED PWM function to assist users in developing theirproducts.Functional DescriptionThe Holtek HT68FB571 USB Flash LED MCU provides users with a set of LED PWMrelated registers including four LED PWM function enable control registers LMnCE(x=0~3), four LED PWM control registers and twenty auto key scan data registersKEYDATAx (x=0~19). Additionally, an LED PWM dedicated data memory is provided forLED auto scan data storage. In the functional description section, a description of theLED PWM architecture is provided along with descriptions for the control registers, LEDPWM auto mode operation, manual mode operation, LED PWM waveforms andhardware circuits.LED PWM Architecture DescriptionThe HT68FB571 LED PWM functional architecture is composed of four LED PWMmodules, an LED PWM dedicated RAM, a register transfer unit and an LED COM outputunit. The LED PWM function block diagram is shown in the following figure. Here n=0~3,m=0~15, x=0~19.For each LED PWM module, there are two PWM control circuits, namely PWM A and PWM B. The PWM A outputs correspond to LEDSEG2n while the PWM B outputs correspond to LEDSEG(2n+1), where n is the selected module number. The device provides up to 8 groups of 8-bit PWM outputs. The PWM operating frequency, which can be 6MHz, 12MHz, 16MHz or other values is selected using the PWMCK[2:0] bits that is bit 4 ~ bit 2 of the PWMCTL0 register.The LEDCOM output unit is used to generate the external LEDCOMm enable control signals. By using a matrix scanning method combined with LEDSEG outputs, the device can implement up to (m+1)×(n+1)×2 LED applications.The LED PWM dedicated data memory, which is known as the LED RAM, has a capacity of 128 bytes and is located at 80H~FFH in RAM Sector 4. During the LED PWM auto scan period, the device can read out the PWM data from the LED RAM and then output the corresponding PWM duty cycle.To implement the auto key scan function, firstly the rows to be automatically scanned should be selected using the KEYSR4~0 (PWMCTL1 bit 7~3) bits. The columns that will be automatically scanned are KEYC7~KEYC0 and their corresponding pin-shared function should be setup correctly using the PDS0[7:0] and PDS1[7:0] bits. Then the scan result data can be read out from the KEYDATA x~0 registers. The corresponding waveforms for the automatic LED scan and Key scan will be explained in detail in the following chapters.The LED PWM function also provides two interrupts, LEDINT and SCANINT, which are helpful during program design. When completing a frame of data, i.e. (m+1)×2(n+1) LEDSEG signals have been scanned, an LEDINT interrupt signal will be generated. When a key scan frame is completed, the SCANINT interrupt signal will be generated.KSCE & LDCOM[3:0]f f f f (f (f (f f KEYC0LED PWM ArchitectureLED PWM Function Control Register DescriptionThe HT68FB571 LED PWM function includes an LED PWM control function and an auto scan function.The LED PWM function can operate in two modes, manual mode and automatic mode, which are selected and configured by the PWMCTL0, PWMCTL1, PWMCTL2, PWMCTL3 and PWMCTL4 control registers.In the manual mode, the value in the LMnCAR and LMnCBR registers are used to control the PWM duty outputs.In the automatic mode, using the pre-stored data in the LED PWM dedicated data memory in Sector 4, the required duty PWM outputs will be generated by the hardware. The LMnCE register is used to disable the corresponding LED PWM output to turn the LED off.The HT68FB571 LED PWM control and auto key scan related registers are listed in the following table. Refer to the HT68FB571 datasheet for more details.Register NameBit7 6 5 4 3 2 1 0LMnCE — — — — — — MnCBE MnCAE LMnCAR MnCAD7 MnCAD6 MnCAD5 MnCAD4 MnCAD3 MnCAD2 MnCAD1 MnCAD0 LMnCBR MnCBD7 MnCBD6 MnCBD5 MnCBD4 MnCBD3 MnCBD2 MnCBD1 MnCBD0 PWMCTL0 PWMN2 PWMN1 PWMN0 PWMCK2 PWMCK1 PWMCK0 — LDCOME PWMCTL1 KEYSR4 KEYSR3 KEYSR2 KEYSR1 KEYSR0 PWMGE PHRC KSCE PWMCTL2 TDELAY3 TDELAY2 TDELAY1 TDELAY0 TPHRE1 TPHRE0 COMDIR SEGDIR PWMCTL3 COMRD3 COMRD2 COMRD1 COMRD0 LDCOM3 LDCOM2 LDCOM1 LDCOM0 PWMCTL4 — — — — — RAMCK2 RAMCK1 RAMCK0 KEYDATAx D7 D6 D5 D4 D3 D2 D1 D0 LED PWM Control and Auto Key Scan Register List - n=0~3, x=0~19LED PWM Auto Mode and Auto Key Scan OperationOperating in the LED PWM Auto Mode, the registers which include LMnCE, PWMCTL0, PWMCTL1, PWMCTL2, PWMCTL3, PWMCTL4 and KEYDATAx and an LED PWM dedicated data memory of 128 bytes will be used to control the PWM signal output. The control flowcharts are shown below.The number of used LED COM outputs is determined by the LDCOM[3:0] (PWMCTL3 bit 3~0) bits. The selected COM ports must use continuous numbers starting from COM0. For example, if five COM outputs are needed, then they must be output from the COM0 ~ COM4 ports. Additionally the corresponding pin-shared pins should be selected as LEDCOM functions. For example, if the LEDCOM0 pin function is to be used, the PAS1[1:0] bits should be set to 11 to select the PA4 pin function as the LEDCOM0 first. Then setup the LED COM output polarity to be active low or active high using the COMDIR (PWMCTL2 bit 1) bit according to the actual circuit.If using the LEDSEG function, the corresponding pin function should be selected as LEDSEG. For example, if the LEDSEG4 pin function is to be used, the PFS1[1:0] bits should be set to 11 to select the PF4 pin function as the LEDSEG4 first. Then set the LED SEG output polarity to be active high or active low using the SEGDIR (PWMCTL2 bit 0).Users can write their required duty data into the LED RAM. The hardware will generate the LEDINT interrupt signal when the data in the last address has been processed and then restart the data process from the first address of the LED RAM.The following content will illustrate the data format in the LED PWM dedicated data memory along with the PWM duty cycle.LED PWM Output & Auto Key Scan Control Flow ChartFlowchart DescriptionSTEP1: (1) Configure the PWM clock source frequency by setting the PWMCK[2:0] bits(2) Configure the pin-shared control registers to select the LEDCOM/KEYR &LEDSEG function.STEP2: (1) Configure how many LED COM outputs are used using the LDCOM[3:0] bits(2)Setup the LEDCOM and LEDSEG polarity to be active high or active low(3) Configure the PWM cycle output number of each LEDCOM using thePWMN[2:0] bits - a recommended value is 111, i.e. one PWM output per LEDCOM to obtain the maximum frame update rate.STEP3: If the auto key scan function is to be used(1) Set the KSCE bit to 1(2) Select how many key scan outputs are used by setting the KEYSR[4:0] bits(3) Setup the hardware key scan delay time using the TDELAY [3:0] bits(4) Configure the key scan input port pull-high resistor using the PHRC bitSTEP4: Set both the LDCOME and PWMGE bits high to enable the hardware units for the LED PWM automatic calculation and auto key scan functions.In the automatic mode, the LED PWMs can control the LEDs in a matrix scanning method and generate 2×(n+1) LED PWM SEG and (m+1) COM outputs in total. The LED PWM timing diagram is shown below.An LED frame is a period of time when the hardware outputs are low (if the COMDIR bit is 0) from COM0 to COMm. When COMm is low, the CCO outputs the corresponding PWM duty cycle according to the related register settings and the data in the LED PWM dedicated data memory.LED COM Time SlotLED frame Interrupt request flagEnable the corresponding PWM register and output PWM cycle.About 10us between COM m-1 and COM m for Non-overlap.TLED PWM Timing Diagram - m=15LED PWM Dedicated Memory Data Format DescriptionFor the LED PWM auto mode operation, the device provides a 128-byte LED PWM dedicated data memory, known as the LED RAM, to store the PWM duty data. The LED RAM is located at 80H~FFH in Sector 4 of the Data Memory. The LED RAM is subdivided into 16 columns, namely Column0~Column15. The LED RAM data can be allocated as follows.Start address : RAM Sector 4 [80H]LED RAMBit7~0 : PWM_Cm(A/B)n PWM valueColumn 1Column 0Column 3Column 2Column mLED RAM Allocation - n=0~3, m=0~15In each column, there are 2×(n+1) bytes of data which is arranged using the following rule.PWM Column m: Store LED PWM A and PWM B duty data of the COM m and Module n PWM_CmA0: The PWM A duty value for COMm and Module 0 PWM_CmB0: The PWM B duty value for COMm and Module 0 ::PWM_CmAF: The PWM A duty value for COMm and Module F PWM_CmBF: The PWM B duty value for COMm and Module FLED PWM Manual Mode Operation DescriptionIf the LDCOME (PWMCTL0 bit 3) bit is set to 0, the LED PWM Manual Mode will be enabled and the related registers including LMnCAR / LMnCBR (n=0~3), PWMCTL0, PWMCTL1 and PWMCTL2 should be setup correctly. In the manual mode, users should setup the LED PWM duty value and disable/enable the PWM outputs using the application program. The LEDCOMm and LEDSEGn pin function should also be selected using the corresponding pin-shared function control registers.In the manual mode, the LED PWM dedicated data memory is not used. Some registers only related to the auto mode are unavailable. LED PWM Waveform DescriptionThe PWMN[2:0] (PWMCTL0 bit 7~5) bits are used to configure the number of the LED PWM outputs for each LEDCOM active time. The following example, which is an LED PWM output waveform, shows the relationship between the LEDCOM and LEDSEG outputs. In the following figure, two LED PWM (LEDSEG) cycles are output during each LED COM active output and the LED PWM duty is 5.Ex: Duty Value=5(LED-SEG High active)LEDCOM Output Waveform (each COM=2 PWM perod) (LED-COM Low active)LED PWM Module Output WaveformAuto Key Scan DescriptionThe HT68FB571 provides an auto key scan function, which can be enabled by setting the KSCE bit high. This function is implemented using key scan output ports KEYRm which are shared with the LEDCOMm ports or independent key scan output ports KEYR19 ~ KEYR16. The scanning data can be input through the key scan input ports KEYC0~KEYC7 and then stored in the KEYDATAx register. The auto key scan function related register control bits include KSCE, PHRC, TDELAY[3:0] and KEYSR[4:0] as well as the KEYDATAx register used for scanning input data storage.The auto key scan function which is shared with the LED PWM function is controlled using the KSCE, PHRC, KEYSR[4:0], LDCOM[3:0], TDELAY[3:0] and TPHRE[1:0] bits. The waveforms in different configuration conditions are shown below. Condition (1)KSCE=1; Enable hardware Key Scan functionPHRC=0; Disable hardware Key Scan input port pull high resistor T1=TDELAY3~0KEYSR4~0 (x)=LDCOM3~0(m)LED COMTime Slotrequest flagEnable the corresponding PWM (A/B) register and output PWM (A/B) cycle LED SEGLED SEG offCOMm-1 and COMm for Non-overlap● Condition (2)KSCE=1; Enable hardware Key Scan functionPHRC=0; Disable hardware Key Scan input port pull high resistor KEYSR4~0 (x) < LDCOM3~0(m) T1=TDELAY3~0 Ex. x=m-1LED COM Time SlotLED frame Interrupt request flagEnable the corresponding PWM (A/B) register and output PWM (A/B) cycleLED SEGLED SEG offCOMm-1 and COMm for Non-overlap●Condition (3)KSCE=1; Enable hardware Key Scan functionPHRC=0; Disable hardware Key scan input port pull high resistor KEYSR4~0 (x) > LDCOM3~0(m) T1=TDELAY3~0 Ex. x=m+1LED COM Time SlotLED frame Interrupt request flagEnable the corresponding PWM (A/B) register and output PWM (A/B) cycle LED SEGLED SEG offCOMm-1 and COMm for Non-overlap● Condition (4)KSCE=1; Enable hardware Key Scan functionPHRC=1; Enable hardware Key Scan input port pull high resistor T1=TDELAY3~0; T2=TPHRE1~0 KEYSR4~0 (x)=LDCOM3~0 (m)Enable the corresponding PWM (A/B) register and output PWM (A/B) cycle LED SEG offCOMm-1 and COMm for Non-overlap● Condition (5)KSCE=1; Enable hardware Key Scan functionPHRC=1; Enable hardware Key Scan input port pull high resistor KEYSR4~0 (x) < LDCOM3~0 (m) T1=TDELAY3~0; T2=TPHRE1~0Ex. x=m-1;Enable the corresponding PWM (A/B) register and output PWM (A/B) cycle LED SEG offCOMm-1 and COMm for Non-overlapCondition (6)KSCE=1; Enable hardware Key Scan function;PHRC=1; Enable hardware Key Scan input port pull high resistor control T1=TDELAY3~0; T2=TPHRE1~0 KEYSR4~0 (x) > LDCOM3~0 (m) Ex. x=m+1Enable the corresponding PWM (A/B) register and output PWM (A/B) cycle LED SEG offCOMm-1 and COMm for Non-overlapHardware Circuit DescriptionThe circuits related to implementing the LED PWM and Auto Key Scan include the LEDSEG7~0, LEDCOM15~0, KEYR19~0 and KEYC7~0 pins. As the I/Os can be used to directly drive external LEDs, the circuit can be easily designed without requiring external circuits to drive up to 128 single colour LEDs. The recommended circuit is shown below.Key: 20×8(COMDIR=1, SEGDIR=1)Single Colour LED PWM with Auto Key Scan Application CircuitAlthough the HT68FB571 is mainly for single colour LED applications, it can also be usedfor driving RGB LEDs. The following matrix circuit is recommended for common anodeRGB LED applications. In the dashed box, there is a common anode RGB LED. The devicecan drive up to 40 common anode RGB LEDs.The following matrix circuit is recommended for common cathode RGB LED applications.In the dashed box, there is a common cathode RGB LED. The device can drive up to 32common cathode RGB LEDs.Program Example DescriptionThe HT68FB571 LED PWMs are generated using automatic scanning by the hardware.Users only need to setup the related registers correctly and write the required data intothe LED RAM when using the function. The following gives a simple program example toillustrate how to use the function.#include "HT68FB571.h"__attribute__ ((at(0x480))) //set LED RAM locationstatic volatile unsigned char LEDRAM[128];unsigned char j,k;__attribute__ ((interrupt (0x10))) //enable LED PWM frame interrupt vectorvoid led_int() // update LED RAM{k++ ;for (j=0; j≤128;j++)LEDRAM[j]=k;_edf=0;}void main(){GCC_CLRWDT();i=0 ;j=0 ;k=0;_wdtc=0b01010111; //enable wdt_sledc =0b00001111; //set SEG source max_pac =0b00000000; //set pa for output mode_pbc =0b00000000; //set pb for output mode_pec =0b00000000; //set pe for output mode_pfc =0b00000000; //set pf for output mode_pas1 =0b11111111 ; //set PA7~4 for LEDCOM 3~0_pbs0 =0b11111111 ; //set PA3~0 for LEDCOM 7~4_pes0 =0b11111111 ; //set PE3~0 for LEDCOM 11~8_pes1 =0b11111111 ; //set PE7~4 for LEDCOM 15~12_pfs0 =0b11111111; //set pf3~0 for LEDSEG 3~0_pfs1 =0b11111111; //set pf7~4 for LEDSEG 7~4_pwmctl0 =0b00001001; //LED PWM number, PWM freq, LDCOME_pwmctl1 =0b01111000; //KB scan_out number, PWMGE, PHRC, KSCE_pwmctl2 =0b01100000; //set T1 & T2 COM SEG Dir_pwmctl3 =0b00001111; //LED COM number_pwmctl4 =0b00000001; //RAM freq_ldcome=1; //enable LED hardware COM function_emi=1 ; //enable Global_lede=1; //enable LED hardware LED PWM frame interruptfor (j=0; j≤128;j++)//initial LED RAMLEDRAM[j]=0 ;_pwmge=1; //enable Global LED Hardware functionwhile(1)GCC_CLRWDT();}ConclusionThis application note content has summarised the HT68FB571 LED PWM function usageand provided some usage considerations. When combined with the provided programexample, users can use the LED PWM function more flexibly and develop their productsas rapidly as possible.Reference FilesHT68FB571 Data sheetFor more information, refer to the Holtek official website .Version and Modify InformationDate Author Issue and Revision2018.10.18 Jones Wang First VersionDisclaimerAll information, trademarks, logos, graphics, videos, audio clips, links and other itemsappearing on this website ('Information') are for reference only and is subject to change atany time without prior notice and at the discretion of Holtek Semiconductor Inc.(hereinafter 'Holtek', 'the company', 'us', 'we' or 'our'). Whilst Holtek endeavors to ensurethe accuracy of the Information on this website, no express or implied warranty is givenby Holtek to the accuracy of the Information. Holtek shall bear no responsibility for anyincorrectness or leakage.Holtek shall not be liable for any damages (including but not limited to computer virus,system problems or data loss) whatsoever arising in using or in connection with the use ofthis website by any party. There may be links in this area, which allow you to visit thewebsites of other companies. These websites are not controlled by Holtek. Holtek willbear no responsibility and no guarantee to whatsoever Information displayed at such sites.Hyperlinks to other websites are at your own risk.Limitation of LiabilityIn no event shall Holtek Limited be liable to any other party for any loss or damagewhatsoever or howsoever caused directly or indirectly in connection with your access toor use of this website, the content thereon or any goods, materials or services.Governing LawThe Disclaimer contained in the website shall be governed by and interpreted inaccordance with the laws of the Republic of China. Users will submit to the non-exclusivejurisdiction of the Republic of China courts.Update of DisclaimerHoltek reserves the right to update the Disclaimer at any time with or without prior notice,all changes are effective immediately upon posting to the website.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VDD=5V, RL=8Ω, PO=1W

82

%

85

%

输出失调电压

VOS

±7

mV

频响特性

fRES

CIN =0.1µF, f=100Hz~20kHz

-3

-

1

dB

系统增益 ACF衰减增益

Av0

RIN=12 kΩ

23.5

dB

Aa

-10

0

dB

注6: 以上模拟特性随所选元件和PCB布局而有所变化;以上特性在以8Ω或4Ω电阻串联30μH电感作为输出负载的测试条件下获得。

最大值 6.5

85

单位 V ℃ Ω

-2-

04/2014 – V0.3

HT6872

4.7W 防削顶 D 类音频功率放大器

直流特性(DC)

VSS=0V, VDD=2.5V~6.5V, Ta= -40ºC~85ºC, 除非特殊说明.

参数

符号

条件

VDD电源的启动阈值 VDD电源的关断阈值 ACF 模式的设置阈值电压 ACF-Off 模式的设置阈值电压 SD 关断模式的设置阈值电压

参数

符号

条件

最小值

典型值

最大值 单位

输出功率

总谐波失真加噪声 输出噪声 信噪比 电源抑制比

PO

THD+N VN SNR

PSRR

RL=4Ω, VDD=3.6V RL=4Ω, VDD=5.0V RL=4Ω, VDD=6.5V

f=1kHz, THD+N=1%

RL=4Ω, VDD=3.6V RL=4Ω, VDD=5.0V RL=4Ω, VDD=6.5V

HT6872

4.7W 防削顶 D 类音频功率放大器

引脚信息

1

CTRL

2

BYPASS

3

IN-

4

IN+

8

OUT-

7

GND

6

VDD

5

OUT+

IN+

AGND

IN-

1

VDD

BYPASS

CTRL

2

OUT+

PGND

OUT-

3

引脚定义*1

8引脚SOP 顶视图

A

B

C

9焊球WLCSP 底视图

SOP 引脚号

WLCSP 焊球号

HT6872具有独有的电磁辐射(EMI)抑制技术 和优异的全带宽低辐射性能,辐射水平在不加任何辅 助设计时仍远在FCC Part15 Class B 标准之下,不 仅避免了干扰其他敏感电路还降低了系统设计难度。

HT6872内部集成免滤波器数字调制技术,能够 直接驱动扬声器,并最大程度减小脉冲输出信号的失 真和噪音。输出无需滤波网络,极少的外部元器件节 省了系统空间和成本,是便携式应用的理想选择。

CB 1µF

S1

2 BYPASS

ACF 数字控制

载波 发生器

OCP OTP

1 CTRL

关断 控制

HT6872 UVLO

RPD

GND

7

-1-

04/2014 – V0.3

TEL:0755-82863877 13242913995 E-MAIL:panxia168@

ACF-On

0.01 0

0.2 0.4 0.6 0.8

1

Vin(V)

1.2 1.4

10.00

RL =4Ω f =1kHz ACF-Off

VDD VS Po

THD=10% TH+N%

THD+N%

HT6872

4.7W 防削顶 D 类音频功率放大器

Vin VS THD+N

100

ms KHz

-3-

04/2014 – V0.3

典型特性曲线

Po VS THD+N

100

RL =4Ω

f =1kHz

10

ACF-Off

THD+N%

1

0.1

0.01 0.01

0.1

1

Po(W)

VDD=3.6V VDD=5.0V VDD=6.5V

10

Frequency VS THD+N

1 RL =4Ω ACF-Off Po≈ 0.1W

100

1000

10000

Fre que ncy( HZ)

Vin VS Po

100000

Po(W)

1

0.1

0.01 0

VDD=3.6V RL =4Ω f =1kHz GAIN=23.5dB

ACF-Off ACF-On

0.2

0.4

0.6

0.8

Vin(V)

GAIN( dB)

GAIN( dB)

THD+N%

THD+N%

HT6872

4.7W 防削顶 D 类音频功率放大器

4.7W防削顶单声道D类音频功率放大器

特点

・防削顶失真功能(Anti-Clipping Function, ACF) ・优异的全带宽EMI抑制性能 ・免滤波器数字调制,直接驱动扬声器

・输出功率 1.40W (VDD=3.6V, RL=4Ω, THD+N=10%) 2.82W (VDD=5.0V, RL=4Ω, THD+N=10%) 4.71W (VDD=6.5V, RL=4Ω, THD+N=10%)

引脚 名称

I/O

ESD 保护电路

功能

1

C2

CTRL

I

PN

ACF模式和关断模式控制端

2

B2

BYPASS

A

PN

模拟参考电压

3

C1

IN-

A

PN

反相输入端(差分-)

4

A1

IN+

A

PN

同相输入端(差分+)

5

A3

OUT+

O

-

同相输出端(BTL+)

6

A2

VDD

Power

-

电源

7

B1/B3

GND

GND

-

地

8

C3

OUT-

VUVLH VUVLL VMOD1 VMOD2 VMOD3

VDD=3.6V, Vin=0V、 No load

静态电流

IDD

VDD=5.0V, Vin=0V、 No load

关断电流 BYPASS端电压值

注5: HT6872启动时CTRL端电压须大于0.80V。

ISD VBYPASS

VDD=6.5V, Vin=0V、 No load

・卓越的“咔嗒-噼噗”(Click-Pop)噪声抑制性能 ・高信噪比SNR:87dB (VDD=5V, Av=23.5dB) ・低静态电流

2.64mA (VDD=3.6V, Vin=0V、No load) 3.26mA (VDD=5.0V, Vin=0V、No load) 4.04mA (VDD=5.0V, Vin=0V、No load) ・低关断电流:0.01µA ・过流保护及自动恢复功能

CTRL=VSS, Ta=25℃

最小值

1.20 0.40 VSS

典型值 2.06 1.90

0.80*5

2.64

3.26

4.04 0.01 VDD/2

最大值

VDD 0.90 0.20

单位 V V V V V

mA

µA V

模拟特性

VSS=0V, VDD =5V, Av=18dB, Ta=25ºC, CIN=0.1uF, RIN=12 kΩ, ACF-Off模式, 除非特殊说明.

此外,HT6872内置的关断功能使待机电流最小 化,还集成了输出端过流保护、片内过温保护和电源 欠压异常保护等功能。

CS 1µF

6

VDD

单端 输入

CIN 0.1uF

CIN 0.1uF

RIN 4 IN+

12kΩ RIN 3 IN-

12kΩ

前置 放大

数字 PWM 调制器

EMI抑制 +

输出驱动

OUT+ 5 OUT- 8

HT6872的最大特点是防削顶失真(ACF)输出 控制功能,可检测并抑制由于输入音乐、语音信号幅 度过大所引起的输出信号削顶失真(破音),也能自 适应地防止在电池应用中由电源电压下降所造成的 输出削顶,显著提高音质,创造非常舒适的听音享受, 并保护扬声器免受过载损坏。同时芯片具有ACF-Off 模式。

30 RL =4Ω ACF-Off

25 Po≈0.1W

20

15

VDD=3.6V VDD=5.0V VDD=6.5V

10 10

100

1000

10000

Fre que ncy( HZ)

100000

Frequency VS GAIN

30 RL =4Ω ACF-Off

25 Po≈1W

20

VDD=3.6V

VDD=5.0V

tSD

tMOD fPWM

CIN=0.1uF, RIN=12kΩ VDD=3.6V, g=10dB VDD=3.6V, g=10dB

Ta(Min.)= -20℃ Ta(Min.)= -30℃

最小值

35 50 80 0.1

典型值 90 133 72 720

488

最大值

单位 ms Hz ms ms ms

ms

0.1

VDD=3.6V VDD=5.0V VDD=6.5V

THD+N%

0.01 10

100

1000

10000

Fre que ncy( HZ)