STMICROELECTRONICS LM224PT

LM224LM324中文资料

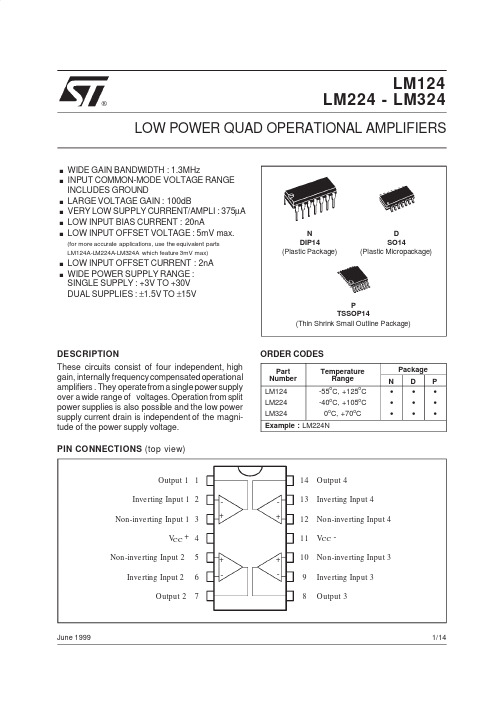

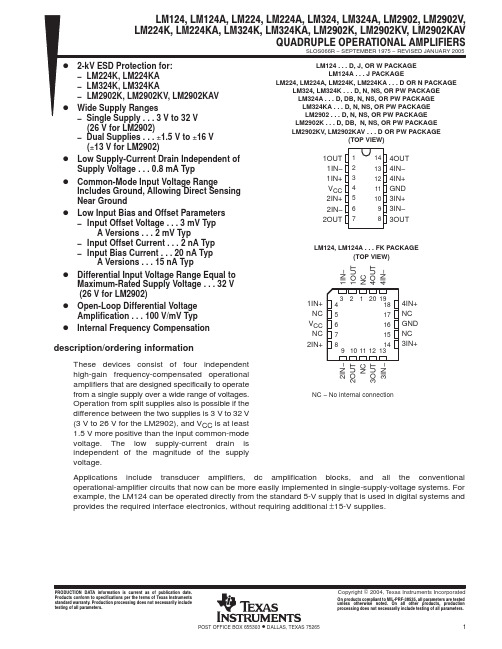

四运算放大器芯片LM124/LM224/LM324中文资料2010-01-30 11:41:29| 分类:电子元件资料| 标签:|字号大中小订阅四运算放大器芯片LM124/LM224/LM324中文资料LM124/LM224/LM324是四运放集成电路,它采用14管脚双列直插塑料(陶瓷)封装,外形如图所示。

它的内部包含四组形式完全相同的运算放大器,除电源共用外,四组运放相互独立。

每一组运算放大器可用图1所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。

两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的相位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。

LM124/LM224/LM324的引脚排列见图2。

图一图二lm324功能引脚图图3 LM324/LM124/LM224集成电路内部电路图1/4 主要参数:参数名称测试条件最小典型最大单位输入失调电压U0≈1.4V RS=0-2.07.0mV输入失调电流--5.050nA输入偏置电流--45250nA大信号电压增益U+=15V,RL=5kΩ88k100k--电源电流U+=30V,Uo=0,RL=∞1.53.0-mA共模抑制比Rs≤10kΩ6570-dB极限参数:LM124为陶瓷封装符号参数LM124LM224LM324单位VccSupply Voltage 电源电压VViInput Voltage 输入电压-0.3 to +32VVidDifferential Input Voltage -(*) 差分输入电压+32+32+32VPtotPower Dissipation功耗后缀N Suffix500500500mW后缀D Suffix-400400-Output Short-circuit Duration -(note 1)Infinite-IinInput Current (note 6) 输入电流505050mAToperOperating Free Air Temperature Range 工作温度 -55 to +125-40 to +105℃TstgStorage Temperature Range 储存温度范围-65 to +150-65 to +150-65 to +150℃由于LM124/LM224/LM324四运放电路具有电源电压范围宽,静态功耗小,可单电源使用,价格低廉等优点,因此被广泛应用在各种电路中。

微斯米微波式芯片公司2014年产品说明书

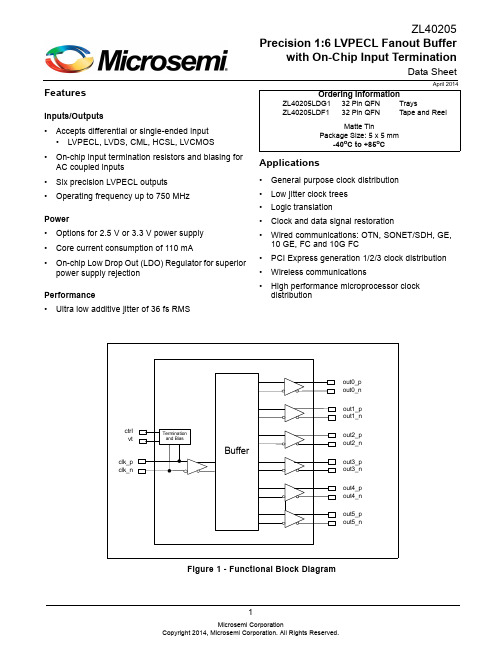

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination resistors and biasing for AC coupled inputs•Six precision LVPECL outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Core current consumption of 110 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 36 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE,10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40205Precision 1:6 LVPECL Fanout Bufferwith On-Chip Input TerminationData SheetOrdering InformationZL40205LDG1 32 Pin QFN TraysZL40205LDF132 Pin QFNTape and ReelMatte TinPackage Size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - Simplified Diagram of Input Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVPECL AC Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - LVPECL AC Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 21 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.8Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. These resistor are not required; however there is no impact to performance if the resistors are included.16Power supply filtering 18Figure 20Clarification of V ID and V OD .Below are the changes from the February 2013 issue to the April 2014 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.Below are the changes from the November 2012 issue to the February 2013 issue:Corrected typo of 0.3 Ohm to 0.15 Ohm.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 728, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40205 is an LVPECL clock fan out buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40205 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40205 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40205 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is logically one and the Vt pin is not connected, the Vt pin can be instead connected to VDD with a capacitor. A capacitor can also help in Figure 4 between Vt and VDD. This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Figure 4 - Clock Input - LVPECL - DC CoupledFigure 5 - Clock Input - LVPECL - AC CoupledFigure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a different device with the same inputs and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40205 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationFigure 16 - LVPECL AC Output TerminationFigure 17 - LVPECL AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40205 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40205 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40205 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive random jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.Figure 18 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40205 is equipped with a low drop out (LDO) regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 19. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 Ohm resistor is recommended3.4.3 PCB layout considerationsThe power nets in Figure 19 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.ZL402051891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 19 - Decoupling Connections for Power PinsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5VDD V 4LVPECL output current I out30mA 5Soldering temperature T260 °C 6Storage temperature T ST-55125 °C 7Junction temperature T j125 °C 8Voltage on input pin V input VDD V 9Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload110mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load209mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1CMOS control logic high-level inputvoltageV CIH0.7*V DD V2CMOS control logic low-level inputvoltageV CIL0.3*V DD V3CMOS control logic Input leakagecurrentI IL1µA V I = V DD or 0 V4Differential input common modevoltageV CM 1.1 2.0V5Differential input voltage difference V ID0.251V6Differential input resistance V IR80100120ohm* This parameter was measured from 125 MHz to 750 MHz.* This parameter was measured from 125 MHz to 750 MHz.Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions7LVPECL output high voltage V OH V DD -1.40V 8LVPECL output low voltage V OL V DD - 1.62V 9LVPECL output differential voltage*V OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3Differential input resistance V IR 80100120ohm 4LVPECL output high voltage V OH V DD -1.40V 5LVPECL output low voltage V OL V DD - 1.62V 6LVPECL output differential voltage*V OD0.40.9VDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAC Electrical Characteristics* - Inputs and Outputs (see Figure 21) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out50100ps4Part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-202Percent6LVPECL Output clock slew rate r SL0.75 1.2V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 21 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1392212.512 kHz - 20 MHz 1093311.0412 kHz - 20 MHz 85442512 kHz - 20 MHz 57550012 kHz - 20 MHz 506622.0812 kHz - 20 MHz 40775012 kHz - 20 MHz36Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1152212.512 kHz - 20 MHz 853311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 55550012 kHz - 20 MHz 486622.0812 kHz - 20 MHz 41775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns.*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 115fs RMS 750MHz25 mV at 100 kHz59fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 2.5 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveformat 155.52 MHzV OD versus FrequencyPropagation Delay versus TemperatureNote:This is for a single device. For more details see thePower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHzPower Supply Tone Magnitude (at 100 kHz) versus PSRR at 125 MHz Power Supply Tone Magnitude (at 100 kHz) versus Additive Jitter at 125 MHz7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

LM224中文资料_数据手册_参数

Parameter Supply Voltage

Input Voltage

Differential Input Voltage - (*)

Power Dissipation

N Suffix D Suffix

Output Short-circuit Duration - (note 1)

Supply Voltage Rejection (VCCT+am=b5=V+t2o53o0CV)

Ratio

(RS

≤

10kΩ)

Tmin. ≤ Tamb ≤ Tmax.

Supply Current, all Amp, no load

Tamb = +25oC

VCC = +5V

VCC = +30V

Tmin. ≤ Tamb ≤ Tmax.

(VCCTa=mb+5=V+,2R5LoC= 2kΩ)

Tmin. ≤ Tamb ≤ Tmax.

RL = 2kΩ RL = 10kΩ

Low Level Tamb =

Output +25oC

Voltage

(RL

=

10kΩ)

Tmin. ≤ Tamb ≤ Tmax.

Slew Rate VCC = 15V, VI = 0.5 to 3V, RL = 2kΩ, CL = 100pF, unity gain)

Input Offset Current Drift

Channel Separation (note 5) 1kHz ≤ f ≤ 20kHz

MHz

1.3 %

0.015

nV

40

STMICROELECTRONICS 2N3904 数据手册

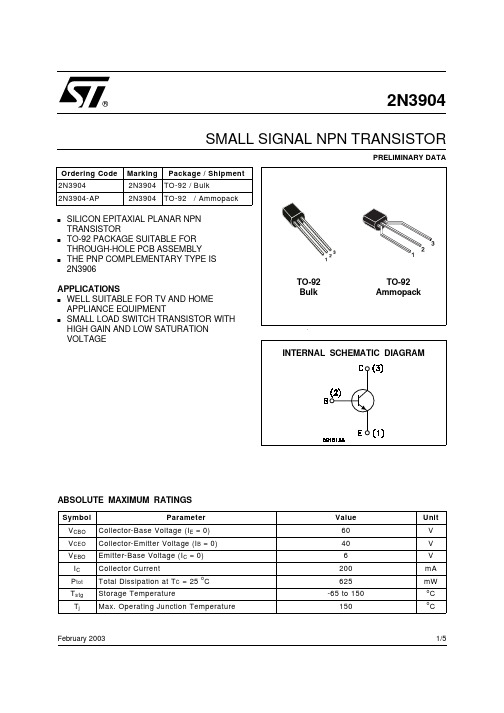

2N3904SMALL SIGNAL NPN TRANSISTORPRELIMINARY DATAsSILICON EPITAXIAL PLANAR NPN TRANSISTORsTO-92 PACKAGE SUITABLE FOR THROUGH-HOLE PCB ASSEMBLY sTHE PNP COMPLEMENTARY TYPE IS 2N3906APPLICATIONS s WELL SUITABLE FOR TV AND HOME APPLIANCE EQUIPMENTs SMALL LOAD SWITCH TRANSISTOR WITH HIGH GAIN AND LOW SATURATION VOLTAGE®February 2003ABSOLUTE MAXIMUM RATINGS1/52N3904THERMAL DATAC unless otherwise specified)ELECTRICAL CHARACTERISTICS (T case = 25 o2N39042N3904Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a trademark of STMicroelectronics © 2003 STMicroelectronics – Printed in Italy – All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.2N3904。

stmicroelectronics意法半导体

stmicroelectronics意法半导体意法半导体(STMicroelectronics),是一家法国意大利合资的半导体公司,总部位于瑞士。

在半导体行业中,意法半导体是市值最大的公司之一。

旗下拥有多个知名品牌,例如STM32、STM8、STLINK等。

本文将从公司历史、产品特点、市场份额和未来展望等四个方面来介绍意法半导体公司。

一、公司历史意法半导体成立于1987年,由法国托姆森半导体公司与意大利位于卡特鲁喀(Catania)的SGS微电子公司(Società Generale Semiconduttori)合作成立。

公司早期主要以生产高效、低功耗的模拟集成电路(IC)为主,后来逐步扩展至数字集成电路、无线通讯等领域,逐渐成为半导体行业的领导者之一。

公司在不断地技术更新和进步中,取得了丰硕的成果。

例如,意法半导体是全球排名第二的微机电系统(MEMS)制造商,该技术主要应用于手机、汽车和数码相机等产品中。

另外,该公司也在高精度电源管理和功率器件领域表现突出,是全球领先的模拟市场供应商。

二、产品特点1. STM32系列STM32系列是意法半导体的一款32位微控制器,以低功耗、高性能、丰富的外设和广泛的应用领域著称。

该系列拥有多个版本,提供不同的内核、存储器和时钟频率。

同时,STM32还为用户提供了一系列可灵活配置的开发套件,方便用户进行软硬件开发和调试。

2. STLINKSTLINK是意法半导体为STM32系列提供的调试和仿真工具,其使用方便,支持在线调试、虚拟仿真和外部调试控制等功能。

此外,STLINK还配备了多种外设接口,方便用户对现有电路进行扩展或接口调试。

3. 数字信号处理器(DSP)意法半导体的数字信号处理器主要应用于音频、图像和视频处理等领域。

该器件顶尖的性能和高精度的数据计算能力,使其受到了广泛的欢迎。

4. 无线通信模块意法半导体的无线通信模块通过集成射频电路、调制解调器等电路,为用户提供高速、低功耗、可靠的无线通讯方案。

stmicroelectronics 意法半导体

意法半导体(STMicroelectronics)是一家国际知名的半导体制造商,总部位于瑞士日内瓦。

作为全球领先的半导体公司之一,意法半导体在模拟、数字和混合信号集成电路领域拥有丰富的经验和技术。

本文将从如下几个方面介绍意法半导体的发展历程、主要产品和技术创新。

一、发展历程意法半导体成立于1987年,是由意大利的SGS微电子公司和法国的汤姆森(Thomson)电子公司合并而成。

公司的发展历程可以追溯到上个世纪60年代,当时SGS微电子公司开始在意大利成立,汤姆森电子公司也在法国进行半导体制造。

两家公司的合并,使得意法半导体在半导体行业中迅速崛起,并在全球范围内建立了领先地位。

二、主要产品意法半导体的主要产品包括模拟集成电路(Analog ICs)、数字集成电路(Digital ICs)和混合信号集成电路(Mixed-Signal ICs)。

其中模拟集成电路主要应用于各种传感器和电源管理系统中,数字集成电路用于微控制器和数字信号处理器等产品中,混合信号集成电路则结合了模拟和数字功能,应用于通信、汽车电子和工业控制等领域。

三、技术创新意法半导体一直致力于技术创新和研发投入,在芯片制造工艺、材料科学和器件设计方面取得了许多重要的突破。

公司拥有世界一流的研发团队和先进的实验室设施,不断推出高性能、低功耗的新产品,满足客户不断增长的市场需求。

在芯片制造工艺方面,意法半导体采用先进的CMOS工艺和封装技术,生产出性能稳定、功耗低的集成电路产品。

在材料科学方面,公司与全球合作伙伴共同研发了各种先进的半导体材料,如碳化硅、氮化镓等,在器件设计方面,意法半导体不断改进电路结构和布局,提高集成电路的可靠性和性能。

四、未来展望随着物联网、人工智能和5G技术的迅猛发展,意法半导体将继续在模拟、数字和混合信号集成电路领域发挥领先优势,不断推出符合市场需求的新产品。

公司还将加大在新能源汽车、智能家居、工业自动化和医疗健康等领域的投入,加强与客户和合作伙伴的合作,共同开拓更广阔的市场空间。

LM224DR中文资料

元器件交易网元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

STMicroelectronics STPS6M100SF数据手册说明书

STPS6M100SFFeatures•Low profile design – package height of 1.1 mm typ.•Wettable flanks for automatic visual inspection •Low forward voltage drop •Avalanche capability •ECOPACK ®2 compliantApplications•Switching diode •Notebook adapter •LED lighting•DC/DC converterDescriptionThis high voltage Schottky barrier rectifier has been optimized for use in highfrequency miniature DC/DC converters, reverse battery protection, battery chargers and adaptors.Packaged in PSMC (TO-277A), the STPS6M100SF provides a high level ofperformance in a compact and flat package which can withstand very high operating junction temperature.100 V power Schottky rectifierSTPS6M100SFDatasheetSTPS6M100SFCharacteristics 1CharacteristicsTable 1. Absolute ratings (limiting values at 25 °C, unless otherwise specified, anode terminals short-circuited)1.(dP tot/dT j) < (1/R th(j-a)) condition to avoid thermal runaway for a diode on its own heatsink.Table 2. Thermal resistance parametersFor more information, please refer to the following application note:•AN5088: Rectifiers thermal management, handling and mounting recommendationsTable 3. Static electrical characteristics (anode terminals short-circuited)1.Pulse test: t p = 5 ms, δ < 2%2.Pulse test: t p = 380 µs, δ < 2%To evaluate the conduction losses, use the following equation:P = 0.49 x I F(AV) + 0.0267 x I F2(RMS)For more information, please refer to the following application notes related to the power losses:•AN604: Calculation of conduction losses in a power rectifier•AN4021: Calculation of reverse losses in a power diodeSTPS6M100SFCharacteristics (curves) 1.1Characteristics (curves)Figure 7. Thermal resistance junction to ambient versus copper surface under tab (typical values, epoxyprinted board FR4, e Cu= 35 µm) (PSMC (TO-277A))020406080100120012345678910STPS6M100SFCharacteristics (curves)2Package informationIn order to meet environmental requirements, ST offers these devices in different grades of ECOPACK ®packages, depending on their level of environmental compliance. ECOPACK ® specifications, grade definitions and product status are available at: . ECOPACK ® is an ST trademark.2.1PSMC (TO-277A) package information•Epoxy meets UL94,V0•Cooling method : by conduction (C)Figure 8.PSMC (TO-277A) package outlineTable 4. PSMC (TO-277A) package mechanical dataSTPS6M100SFPackage informationFigure 9.PSMC (TO-277A) package footprint in mm (in inches)STPS6M100SFPSMC (TO-277A) package informationSTPS6M100SFOrdering information 3Ordering informationTable 5. Ordering informationSTPS6M100SFRevision historyTable 6. Document revision historySTPS6M100SFIMPORTANT NOTICE – PLEASE READ CAREFULLYSTMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers’ products.No license, express or implied, to any intellectual property right is granted by ST herein.Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.Information in this document supersedes and replaces information previously supplied in any prior versions of this document.© 2018 STMicroelectronics – All rights reservedSTPS6M100SF。

LM224集成块说明书

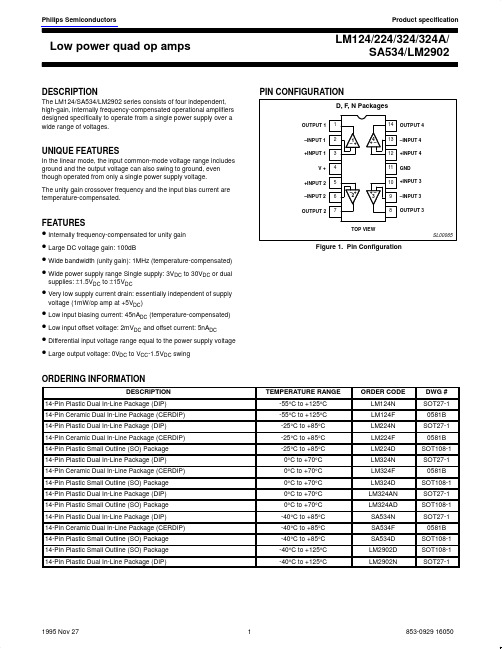

1995 Nov 27

1

853-0929 16050

Philips Semiconductors

Product specification

Low power quad op amps

LM124/224/324/324A/ SA534/LM2902

ABSOLUTE MAXIMUM RATINGS

SYMBOL VCC VIN VIN PD Supply voltage Differential input voltage Input voltage Maximum power dissipation, TA=25°C (still-air)1 N package F package D package Output short-circuit to GND one amplifier2 VCC<15VDC and TA=25°C IIN TA Input current (VIN<-0.3V)3 Operating ambient temperature range LM324/A LM224 SA534 LM2902 LM124 TSTG TSOLD Storage temperature range Lead soldering temperature (10sec max) 0 to +70 -25 to +85 -40 to +85 -40 to +125 -55 to +125 -65 to +150 300 °C °C °C °C °C °C °C 1420 1190 1040 Continuous 50 mA mW mW mW PARAMETER RATING 32 or ±16 32 -0.3 to +32 UNIT VDC VDC VDC

新型芯片T0P224P在开关电源中的应用

保定科技职业学院学生毕业设计(论文)题目:新型开关芯片TOP224P在开关电源中的应用目录摘要 (Ⅱ)关键词 (Ⅱ)1.1开关电源的概念和分类.............................................................................1 1.1.1开关电源的概念.................................................................................1 1.1.2开关电源的分类.................................................................................3 1.2开关电源设计中存在的问题与未来发展.....................................................4 1.2.1开关电源中存在的问题......................................................................1.2.2开关电源的发展趋势.......................................................................... (1)2电子相册优点 (1)2.1电子相册与传统相册相比的优越性 (1)2.2电子相册独特优势 (1)3电子相册介绍 (1)3.1制作电子相册步骤 (1)3.2电子相册图片浏览 (2)4电子相册表现形式 (2)4.1 DVD电子相册是如何诞生的 (2)5电子相册功能介绍及操作步骤 (2)5.1功能介绍 (2)5.2操作步骤 (2)总结 (4)参考文献 (5)致谢 (6)摘要本文介绍了第二代TOP开关芯片TOP224P的工作原理及功能特点,并叙述了其在双路输出开关电源设计中的具体应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Rev 3June 20051/16LM124-LM224-LM324Low Power Quad Operational Amplifiers■Wide gain bandwidth: 1.3MHz■Input common-mode voltage range includes ground■Large voltage gain: 100dB■Very low supply current/ampli: 375µA ■Low input bias current: 20nA■Low input offset voltage: 5mV max.(for more accurate applications, use the equivalent parts LM124A-LM224A-LM324A which feature 3mV max.)■Low input offset current: 2nA ■Wide power supply range:Single supply: +3V to +30V Dual supplies: ±1.5V to ±15VDescriptionThese circuits consist of four independent, high gain, internally frequency compensated operational amplifiers. They operate from a single power supply over a wide range of voltages.Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage.Order CodesPart Number Temperature Range PackagePackaging LM124N -55°C, +125°CDIP TubeLM124D/DT SO Tube or Tape & ReelLM224N -40°C, +105°CDIP TubeLM224D/DT SO Tube or Tape & ReelLM224PT TSSOP(Thin Shrink Outline Package)T ape & Reel LM324N 0°C, +70°CDIP TubeLM324D/DT SO Tube or Tape & ReelLM324PTTSSOP(Thin Shrink Outline Package)T ape & Reel查询"LM224PT"供应商2/161 Absolute Maximum RatingsTable 1.15Key parameters and their absolute maximum ratingsSymbol ParameterLM124LM224LM324Unit VCC Supply voltage ±16 or 32V Vi Input Voltage-0.3 to Vcc + 0.3V V id Differential Input Voltage (1)1.Either or both input voltages must not exceed the magnitude of V CC + or V CC -.-0.3 to Vcc + 0.3V P totPower DissipationN Suffix D Suffix500500400500400mWOutput Short-circuit Duration (2)2.Short-circuits from the output to VCC can cause excessive heating if V CC > 15V. The maximum output currentis approximately 40mA independent of the magnitude of V CC . Destructive dissipation can result from simultaneous short-circuit on all amplifiers.InfiniteI in Input Current (3)3.This input current only exists when the voltage at any of the input leads is driven negative. It is due to thecollector-base junction of the input PNP transistor becoming forward biased and thereby acting as input diodes clamps. In addition to this diode action, there is also NPN parasitic action on the IC chip. this transistor action can cause the output voltages of the op-amps to go to the V CC voltage level (or to ground for a large overdrive) for the time duration than an input is driven negative.This is not destructive and normal output will set up again for input voltage higher than -0.3V.505050mA T oper Operating Free-air Temperature Range -55 to +125-40 to +1050 to +70°C T stgStorage Temperature Range-65 to +150°CR thjaThermal Resistance Junction to Ambient SO14TSSOP14DIP1410310066°C/WESDHBM: Human Body Model (4)4.Human body model, 100pF discharged through a 1.5k Ω resistor into pin of device.250VMM: Machine Model (5)5.Machine model ESD, a 200pF cap is charged to the specified voltage, then discharged directly into the IC withno external series resistor (internal resistor < 5Ω), into pin to pin of device.150CDM: Charged Device Model1500查询"LM224PT"供应商查询"LM224PT"供应商2 Pin & Schematic DiagramFigure 2.Schematic diagram (1/4 LM124)3/163 ElectricalCharacteristicsTable 2.V CC+ = +5V, V CC-= Ground, V o = 1.4V, T amb = +25°C (unless otherwise specified)Symbol Parameter Min.Typ.Max.UnitV io Input Offset Voltage - note (1)T amb = +25°CLM324T min≤ T amb≤ T maxLM32425779mVI io Input Offset CurrentT amb = +25°CT min≤ T amb≤ T max230100nAI ib Input Bias Current - note (2)T amb = +25°CT min≤ T amb≤ T max20150300nAA vd Large Signal Voltage GainV CC+ = +15V, R L = 2kΩ, V o = 1.4V to 11.4VT amb = +25°CT min≤ T amb≤ T max5025100V/mVSVR Supply Voltage Rejection Ratio (R s≤ 10kΩ)V CC+ = 5V to 30VT amb = +25°CT min≤ T amb≤ T max6565110dBI CC Supply Current, all Amp, no loadT amb = +25°C V CC = +5VV CC = +30VT min≤ T amb≤ T max V CC = +5VV CC = +30V0.71.50.81.51.231.23mAV icm Input Common Mode Voltage RangeV CC= +30V - note (3)T amb = +25°CT min≤ T amb≤ T maxV CC -1.5V CC -2VCMR Common Mode Rejection Ratio (R s≤ 10kΩ)T amb = +25°CT min≤ T amb≤ T max706080dBI source Output Current Source (V id = +1V)V CC = +15V, V o = +2V204070mAI sink Output Sink Current (V id = -1V)V CC = +15V, V o = +2VV CC = +15V, V o = +0.2V10122050mAµAV OH High Level Output VoltageV CC = +30VT amb = +25°C R L = 2kΩT min≤ T amb≤ T maxT amb = +25°C R L = 10kΩT min≤ T amb≤ T maxV CC = +5V, R L = 2kΩT amb = +25°CT min≤ T amb≤ T max262627273.532728V查询"LM224PT"供应商4/165/161.V o = 1.4V, R s = 0Ω, 5V < V CC < 30V, 0 < V ic < V CC - 1.5V2.The direction of the input current is out of the IC. This current is essentially constant, independent of the stateof the output so no loading change exists on the input lines.3.The input common-mode voltage of either input signal voltage should not be allowed to go negative by morethan 0.3V. The upper end of the common-mode voltage range is V CC + - 1.5V, but either or both inputs can go to +32V without damage.4.Due to the proximity of external components insure that coupling is not originating via stray capacitancebetween these external parts. This typically can be detected as this type of capacitance increases at higher frequencies.Table 3.V cc + = +15V, V cc - = 0V, T amb = 25°C (unless otherwise specified)Symbol ConditionsValue Unit V io 0mV A vd R L = 2k Ω100V/mV I cc No load, per amplifier 350µA V icm -15 to +13.5V V OH R L = 2k Ω (V CC +=15V)+13.5V V OL R L = 10k Ω5mV I os V o = +2V , V CC = +15V +40mA GBP R L = 2k Ω, C L = 100pF 1.3MHz SRR L = 2k Ω, C L = 100pF0.4V/µsTable 2.V + = +5V , V -= Ground, V = 1.4V , T = +25°C (unless otherwise specified)查询"LM224PT"供应商查询"LM224PT"供应商Figure 3.Input bias current vs. ambient Figure 4.Current limiting6/16查询"LM224PT"供应商7/16查询"LM224PT"供应商Figure 12.Power supply & common mode Figure 13.Voltage gain8/16查询"LM224PT"供应商4 Typical Single - Supply ApplicationsFigure 14.AC coupled inverting amplifier Figure 15.High input Z adjustable gaind DC9/16查询"LM224PT"供应商Figure 20.Activer bandpass filter Figure 21.High input Z, DC differentialFigure ing symmetrical amplifiers toreduce input current (general10/16查询"LM224PT"供应商5 MacromodelsNote:Note: Please consider following remarks before using this macromodel:All models are a trade-off between accuracy and complexity (i.e. simulation time).Macromodels are not a substitute to breadboarding; rather, they confirm the validity of a designapproach and help to select surrounding component values.A macromodel emulates the NOMINAL performance of a TYPICAL device within SPECIFIEDOPERATING CONDITIONS (i.e. temperature, supply voltage, etc.). Thus the macromodel isoften not as exhaustive as the datasheet, its goal is to illustrate the main parameters of theproduct.Data issued from macromodels used outside of its specified conditions (Vcc, T emperature, etc.)or even worse: outside of the device operating conditions (Vcc, Vicm, etc.) are not reliable inany way.** Standard Linear Ics Macromodels, 1993.** CONNECTIONS :* 1 INVERTING INPUT* 2 NON-INVERTING INPUT* 3 OUTPUT* 4 POSITIVE POWER SUPPLY* 5 NEGATIVE POWER SUPPLY.SUBCKT LM124 1 3 2 4 5 (analog)*******************************************************.MODEL MDTH D IS=1E-8 KF=3.104131E-15 CJO=10F* INPUT STAGECIP 2 5 1.000000E-12CIN 1 5 1.000000E-12EIP 10 5 2 5 1EIN 16 5 1 5 1RIP 10 11 2.600000E+01RIN 15 16 2.600000E+01RIS 11 15 2.003862E+02DIP 11 12 MDTH 400E-12DIN 15 14 MDTH 400E-12VOFP 12 13 DC 0VOFN 13 14 DC 0IPOL 13 5 1.000000E-05CPS 11 15 3.783376E-09DINN 17 13 MDTH 400E-12VIN 17 5 0.000000e+00DINR 15 18 MDTH 400E-12VIP 4 18 2.000000E+00FCP 4 5 VOFP 3.400000E+01FCN 5 4 VOFN 3.400000E+01FIBP 2 5 VOFN 2.000000E-03FIBN 5 1 VOFP 2.000000E-03* AMPLIFYING STAGEFIP 5 19 VOFP 3.600000E+0211/16查询"LM224PT"供应商FIN 5 19 VOFN 3.600000E+02RG1 19 5 3.652997E+06RG2 19 4 3.652997E+06CC 19 5 6.000000E-09DOPM 19 22 MDTH 400E-12DONM 21 19 MDTH 400E-12HOPM 22 28 VOUT 7.500000E+03VIPM 28 4 1.500000E+02HONM 21 27 VOUT 7.500000E+03VINM 5 27 1.500000E+02EOUT 26 23 19 5 1VOUT 23 5 0ROUT 26 3 20COUT 3 5 1.000000E-12DOP 19 25 MDTH 400E-12VOP 4 25 2.242230E+00DON 24 19 MDTH 400E-12VON 24 5 7.922301E-01.ENDS12/16查询"LM224PT"供应商6 Package Mechanical DataIn order to meet environmental requirements, ST offers these devices in ECOPACK® packages.These packages have a Lead-free second level interconnect. The category of second levelinterconnect is marked on the package and on the inner box label, in compliance with JEDECStandard JESD97. The maximum ratings related to soldering conditions are also marked onthe inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at:.13/16查询"LM224PT"供应商Package 6.2 SO-1414/16查询"LM224PT"供应商Package6.3 TSSOP1415/167 RevisionHistoryDate Revision Changes Oct. 20031First ReleaseJan. 20052Modifications on AMR Table1 on page2 (explanation of Vid and Vi limits)June 20053ESD protection inserted in T able1 on page2 Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license isgranted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics productsare not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics.All other names are the property of their respective owners© 2005 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America查询"LM224PT"供应商16/16。