K4S560832D-TL7C中文资料

东芝29JH7UC高清

–7–

设计模式

1 . 进入设计模式 1) 29JH7UC、29JK7UC、34JH7UC 的设计模式同维修模式相同,在维护模式内,按遥控器的 MENU 键 3 次出现的 ADDR 000 DATA C8 WRITE OK 可以选择相应的地址,可以将地址内的数据更改。 2)选择调整项目 使用遥控器或者电视机本体的频道 UP/DN 键选择地址项、数据项、写入确认项。 3)调整数据 按遥控器上的 VOL 或本体的 VOL +/- 键可以更改数据。

–6–

3 . 维修模式中的功能说明 1) 各种信号下的数据是分段控制的 偏向数据分为: PAL 50\60\75\100 可选择扫描模式 NTSC 60 默认扫描模式 480P 信号 1080i/50 信号 1080i/60 信号 如果更换数字板这些信号的线性需要全部重新调整。 2) 数据的选择、调整 用遥控器或者本体的按键的频道升、降键 进行各个项目的选择。 用遥控器或者本体的按键的音量 +/- 键 进行各个项目的选择的。 注意: 以上各选项正常情况下不要调整更换记忆元后(拷贝完数据)后需要进行调整。

4 3 6

–4–

5

Xv 4

4 4

Xv

4

6

4

*

• 27

A

D D A B C

A

D

B

E

E F

B

E

C S N

23 948 274 TC-S

F

*

C

23 948 464

ห้องสมุดไป่ตู้

F N S

YHC

YH

YV YHC

YV YV

G G H

H

–5–

维修资料

1 . 进入维修模式 1)按一次遥控器上“消音”键 2)再次按“消音”键 3)按遥控器的“消音”键的 同时按本体的“MENU”

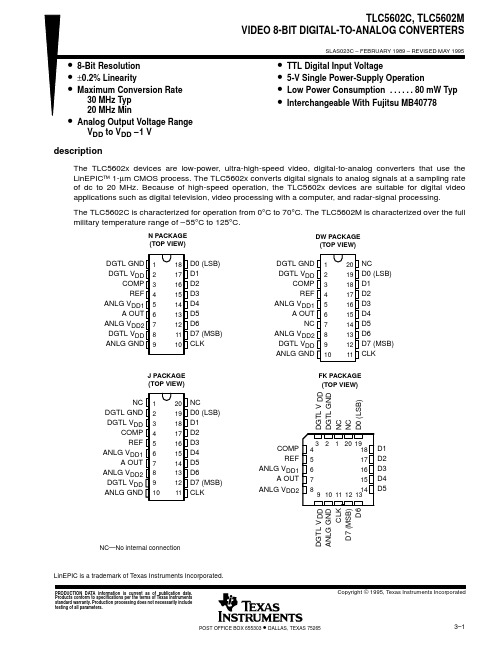

TLC5602中文资料

IMPORTANT NOTICETexas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”).TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.Copyright © 1995, Texas Instruments Incorporated。

K4H560838F-UCCC中文资料

256Mb F-die DDR400 SDRAM Specification66 TSOP-II with Pb-Free(RoHS compliant)Revision 1.1Rev. 1.1 August. 2003256Mb F-die Revision HistoryRevison 1.0 (June. 2003)1. First releaseRevison 1.1 (August. 2003)1. Added x8 org (K4H560838F)Rev. 1.1 August. 2003Rev. 1.1 August. 2003• 200MHz Clock, 400Mbps data rate.• VDD= +2.6V + 0.10V, VDDQ= +2.6V + 0.10V• Double-data-rate architecture; two data transfers per clock cycle • Bidirectional data strobe(DQS)• Four banks operation• Differential clock inputs(CK and CK)• DLL aligns DQ and DQS transition with CK transition • MRS cycle with address key programs-. Read latency 3 (clock) for DDR400 , 2.5 (clock) for DDR333 -. Burst length (2, 4, 8)-. Burst type (sequential & interleave)• All inputs except data & DM are sampled at the positive going edge of the system clock(CK)• Data I/O transactions on both edges of data strobe • Edge aligned data output, center aligned data input • LDM,UDM for write masking only (x16)• Auto & Self refresh• 7.8us refresh interval(8K/64ms refresh) • Maximum burst refresh cycle : 8• 66pin TSOP II Pb-Free package • RoHS compliantOrdering InformationPart .Max Freq.Interface Package K4H560838F-UCCC 32M x 8 CC(DDR400@CL=3)SSTL266pin TSOP IIK4H560838F-UCC4 C4(DDR400@CL=3)K4H561638F-UCCC 16M x 16CC(DDR400@CL=3)SSTL266pin TSOP IIK4H561638F-UCC4C4(DDR400@CL=3)Key Features*CL : CAS LatencyOperating Frequencies- CC(DDR400@CL=3)- C4(DDR400@CL=3)Speed @CL3200MHz 200MHz CL-tRCD-tRP 3 - 3 - 33 -4 - 4Rev. 1.1 August. 2003Pin DescriptionDM is internally loaded to match DQ and DQS identically.256Mb Package PinoutRow & Column address configurationV DD 166Pin TSOP II (400mil x 875mil)DQ 02V DDQ 3NC 4DQ 15V SSQ 6NC 7DQ 28V DDQ 9NC 10DQ 311V SSQ 12BA 020CS 19RAS 18CAS 17WE 16NC 15V DDQ 14NC 13V DD 27A 326A 225A 124A 023AP/A 1022BA 121V SS 54DQ 753V SSQ 52NC 51DQ 650V DDQ 49NC 48DQ 547V SSQ 46NC 45DQ 444V DDQ 43A 113536CKE 37CK 38DM 39V REF 40V SSQ 41NC 42V SS55A 456A 557A 658A 759A 860A 934(0.65mm Pin Pitch)333231302928616263646566NC NC NC NC NC V DDNC DQS NC V SS CK NC A 12 16Mb x 16V SS DQ 15V SSQ DQ 14DQ 13V DDQ DQ 12DQ 11V SSQ DQ 10DQ 9V DDQ A 11CKE CK UDM V REF V SSQ DQ 8V SSA 4A 5A 6A 7A 8A 9NC UDQS NC V SS CK NC A 12V DD DQ 0V DDQ DQ 1DQ 2V SSQ DQ 3DQ 4V DDQ DQ 5DQ 6V SSQ BA 0CS RAS CAS WE LDM V DDQ DQ 7V DD A 3A 2A 1A 0AP/A 10BA 1NC LDQS NC NC NC V DDBank Address BA0~BA1Auto PrechargeA10OrganizationRow Address Column Address32Mx8A0~A12A0-A916Mx16A0~A12A0-A832Mb x 8Package Physical Demension66pin TSOPII / Package dimensionRev. 1.1 August. 2003CK, CKADDCK, CK CKE CS RAS CAS WE Data StrobeBlock Diagram (8Mb x 8 / 4Mb x 16 I/O x 4 Banks)L(U)DMRev. 1.1 August. 2003SYMBOL TYPE DESCRIPTIONCK, CK Input Clock : CK and CK are differential clock inputs. All address and control input signals are sam-pled on the positive edge of CK and negative edge of CK. Output (read) data is referenced to both edges of CK. Internal clock signals are derived from CK/CK.CKE Input Clock Enable : CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and output drivers. Deactivating the clock provides PRECHARGE POWER-DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER-DOWN (row ACTIVE in any bank). CKE is synchronous for all functions except for disabling outputs, which is achieved asynchronously. Input buffers, excluding CK, CK and CKE are disabled dur-ing power-down and self refresh modes, providing low standby power. CKE will recognize an LVCMOS LOW level prior to VREF being stable on power-up.CS Input Chip Select : CS enables(registered LOW) and disables(registered HIGH) the command decoder. All commands are masked when CS is registered HIGH. CS provides for external bank selection on systems with multiple banks. CS is considered part of the command code.RAS, CAS, WE Input Command Inputs : RAS, CAS and WE (along with CS) define the command being entered.LDM,(UDM)Input Input Data Mask : DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For the x16, LDM corresponds to the data on DQ0~D7 ; UDM corresponds to the data on DQ8~DQ15. DM may be driven high, low, or floating during READs.BA0, BA1Input Bank Addres Inputs : BA0 and BA1 define to which bank an ACTIVE, READ, WRITE or PRE-CHARGE command is being applied.A [0 : 12]Input Address Inputs : Provide the row address for ACTIVE commands, and the column address and AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the mem-ory array in the respective bank. A10 is sampled during a PRECHARGE command to deter-mine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code during a MODE REGISTER SET command. BA0 and BA1 define which mode register is loaded during the MODE REGISTER SET command (MRS or EMRS).A12 & A13 are used on device densities of 256Mb and greater, and A13 is used only on 1Gb decices.DQ I/O Data Input/Output : Data busLDQS,(U)DQS I/O Data Strobe : Output with read data, input with write data. Edge-aligned with read data, cen-tered in write data. Used to capture write data. For the x16, LDQS corresponds to the data on DQ0~D7 ; UDQS corresponds to the data on DQ8~DQ15NC-No Connect : No internal electrical connection is present.VDDQ Supply DQ Power Supply : +2.6V ± 0.1V.VSSQ Supply DQ Ground.VDD Supply Power Supply : +2.6V ± 0.1V (device specific).VSS Supply Ground.VREF Input SSTL_2 reference voltage.Input/Output Function DescriptionRev. 1.1 August. 2003Command Truth Table (V=Valid, X=Don′t Care, H=Logic High, L=Logic Low)COMMAND CKEn-1CKEn CS RAS CAS WE BA0,1A10/AP A0 ~ A9,A11, A12NoteRegister Extended MRS H X L L L L OP CODE1, 2 Register Mode Register Set H X L L L L OP CODE1, 2Refresh Auto RefreshHHL L L H X3SelfRefreshEntry L3Exit L HL H H HX3H X X X3Bank Active & Row Addr.H X L L H H V Row AddressRead & Column Address Auto Precharge DisableH X L H L H VLColumnAddress4 Auto Precharge Enable H4Write & Column Address Auto Precharge DisableH X L H L L VLColumnAddress4 Auto Precharge Enable H4, 6Burst Stop H X L H H L X7Precharge Bank SelectionH X L L H LV LXAll Banks X H5Active Power Down Entry H LH X X XXL V V VExit L H X X X XPrecharge Power Down Mode Entry H LH X X XXL H H HExit L HH X X XL V V VDM(UDM/LDM for x16 only)H X X8No operation (NOP) : Not defined H X H X X XX9 L H H H91. OP Code : Operand Code. A0 ~ A12 & BA0 ~ BA1 : Program keys. (@EMRS/MRS)2. EMRS/MRS can be issued only at all banks precharge state.A new command can be issued 2 clock cycles after EMRS or MRS.3. Auto refresh functions are same as the CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto".Auto/self refresh can be issued only at all banks precharge state.4. BA0 ~ BA1 : Bank select addresses.If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.If BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected.If BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected.If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.5. If A10/AP is "High" at row precharge, BA0 and BA1 are ignored and all banks are selected.6. During burst write with auto precharge, new read/write command can not be issued.Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at t RP after the end of burst.7. Burst stop command is valid at every burst length.8. DM(x4/8) sampled at the rising and falling edges of the DQS and Data-in are masked at the both edges (Write DM latency is 0).UDM/LDM(x16 only) sampled at the rising and falling edges of the UDQS/LDQS and Data-in are masked at the both edges (Write UDM/LDM latency is 0).9. This combination is not defined for any function, which means "No Operation(NOP)" in DDR SDRAM.Note :Rev. 1.1 August. 20038M x 8bit x 4 Banks / 4M x 16Bit x 4 Banks Double Data Rate SDRAMGeneral DescriptionThe K4H560838F / K4H561638F is 268,435,456 bits of double data rate synchronous DRAM organized as 4x 8,388,608 / 4x 4,194,304 words by 8 / 16bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 400Mb/s per pin. I/O transactions are possible on both edges of DQS. Range of operating frequen-cies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.Absolute Maximum RatingsParameter Symbol Value Unit Voltage on any pin relative to V SS V IN, V OUT-0.5 ~ 3.6V Voltage on V DD & V DDQ supply relative to V SS V DD, V DDQ-1.0 ~ 3.6V Storage temperature T STG-55 ~ +150°CPower dissipation P D 1.5WShort circuit current I OS50mANote : Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.Functional operation should be restricted to recommend operation condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.DC Operating Conditions Recommended operating conditions(Voltage referenced to V SS=0V, T A=0 to 70°C) Parameter Symbol Min Max Unit Note Supply voltage(for device with a nominal V DD of 2.5V)V DD 2.5 2.75I/O Supply voltage V DDQ 2.5 2.7V5I/O Reference voltage V REF0.49*VDDQ0.51*VDDQ V1I/O Termination voltage(system)V TT V REF-0.04V REF+0.04V2 Input logic high voltage V IH(DC)V REF+0.15V DDQ+0.3VInput logic low voltage V IL(DC)-0.3V REF-0.15VInput Voltage Level, CK and CK inputs V IN(DC)-0.3V DDQ+0.3VInput Differential Voltage, CK and CK inputs V ID(DC)0.36V DDQ+0.6V3V-I Matching: Pullup to Pulldown Current Ratio VI(Ratio)0.71 1.4-4 Input leakage current I I-22uAOutput leakage current I OZ-55uAOutput High Current(Normal strengh driver) ;V OUT = V TT + 0.84V I OH-16.8mAOutput High Current(Normal strengh driver) ;V OUT = V TT - 0.84V I OL16.8mAOutput High Current(Half strengh driver) ;V OUT = V TT + 0.45V I OH-9mAOutput High Current(Half strengh driver) ;V OUT = V TT - 0.45V I OL9mANote :1.VREF is expected to be equal to 0.5*VDDQ of the transmitting device, and to track variations in the dc level of same.Peak-to peak noise on VREF may not exceed +/-2% of the dc value.2. V TT is not applied directly to the device. V TT is a system supply for signal termination resistors, is expected to be set equal toV REF, and must track variations in the DC level of V REF3. V ID is the magnitude of the difference between the input level on CK and the input level on CK.4. The ratio of the pullup current to the pulldown current is specified for the same temperature and voltage, over the entiretemperature and voltage range, for device drain to source voltages from 0.25V to 1.0V. For a given output, it represents the maximum difference between pullup and pulldown drivers due to process variation. The full variation in the ratio of themaximum to minimum pullup and pulldown current will not exceed 1/7 for device drain to source voltages from 0.1 to 1.0.5. This is the DC voltage supplied at the DRAM and is inclusive of all noise up to 20MHz. Any noise above 20MHz at the DRAMgenerated from any source other than the DRAM itself may not exceed the DC voltage range of 2.6V +/-100mV.Rev. 1.1 August. 2003DDR SDRAM Spec Items & Test ConditionsConditions Symbol Operating current - One bank Active-Precharge;tRC=tRCmin; tCK=5ns for DDR400; DQ,DM and DQS inputs changing once per clock cycle;address and control inputs changing once every two clock cycles; CS = high between valid commands.IDD0Operating current - One bank operation ; One bank open, BL=4, Reads- Refer to the following page for detailed test condition; CS = high between valid commands.IDD1 Percharge power-down standby current; All banks idle; power - down mode; CKE = <VIL(max); tCK=5ns forDDR400; Vin = Vref for DQ,DQS and DM.IDD2P Precharge Floating standby current; CS# > =VIH(min);All banks idle; CKE > = VIH(min); tCK=5ns for DDR400;Address and other control inputs changing once per clock cycle; Vin = Vref for DQ,DQS and DMIDD2F Precharge Quiet standby current; CS# > = VIH(min); All banks idle;CKE > = VIH(min); tCK=5ns for DDR400; Address and other control inputs stable at >= VIH(min) or =<VIL(max);Vin = Vref for DQ ,DQS and DMIDD2QActive power - down standby current ; one bank active; power-down mode; CKE=< VIL (max); tCK=5nsDDR400; Vin = Vref for DQ,DQS and DMIDD3PActive standby current; CS# >= VIH(min); CKE>=VIH(min);one bank active; active - precharge; tRC=tRASmax; tCK=5ns for DDR400; DQ, DQS and DM inputs changing twiceper clock cycle; address and other control inputs changing once per clock cycleIDD3NOperating current - burst read; Burst length = 2; reads; continguous burst; One bank active; address and controlinputs changing once per clock cycle; CL=3 at 5ns for DDR400;50% of data changing on every transfer; lout = 0 mAIDD4ROperating current - burst write; Burst length = 2; writes; continuous burst;One bank active address and control inputs changing once per clock cycle; CL=3 at tCK=5ns for DDR400; DQ, DMand DQS inputs changing twice per clock cycle, 50% of input data changing at every transferIDD4W Auto refresh current; tRC = tRFC(min) - 14*tCK for DDR400 at tCK=5ns; IDD5Self refresh current; CKE =< 0.2V; External clock on; tCK = 5ns for DDR400.IDD6 Input/Output Capacitance(V DD=2.6, V DDQ=2.6V, T A= 25°C, f=1MHz) Parameter Symbol Min Max Delta Unit NoteInput capacitance(A0 ~ A12, BA0 ~ BA1, CKE, CS, RAS,CAS, WE)CIN1230.5pF4Input capacitance( CK, CK)CIN2230.25pF4Data & DQS input/output capacitance COUT450.5pF1,2,3,4Input capacitance(DM for 8, UDM/LDM for x16)CIN345pF1,2,3,41.These values are guaranteed by design and are tested on a sample basis only.2. Although DM is an input -only pin, the input capacitance of this pin must model the input capacitance of the DQ and DQS pins.This is required to match signal propagation times of DQ, DQS, and DM in the system.3. Unused pins are tied to ground.4. This parameteer is sampled. VDDQ = +2.6V +0.1V, VDD = +2.6V +0.1V, f=100MHz, tA=25°C, Vout(dc) =VDDQ/2, Vout(peak to peak) = 0.2V. DM inputs are grouped with I/O pins - reflecting the fact that they are matched in loading (to facilitate trace matching at the board level).Note :Rev. 1.1 August. 2003DDR SDRAM I DD spec table (V DD=2.7V, T = 10°C)Symbol32Mx8Unit Notes - CC(DDR400@CL=3)- C4(DDR400@CL=3)IDD0105100mAIDD1130130mAIDD2P44mAIDD2F3030mAIDD2Q2525mAIDD3P5555mAIDD3N7575mAIDD4R185185mAIDD4W220220mAIDD5200200mAIDD6Normal33mA Low power 1.5 1.5mA Optional IDD7A350350mASymbol16Mx16Unit Notes - CC(DDR400@CL=3)- C4(DDR400@CL=3)IDD0110105mAIDD1150145mAIDD2P44mAIDD2F3030mAIDD2Q2525mAIDD3P5555mAIDD3N7575mAIDD4R220220mAIDD4W250250mAIDD5200200mAIDD6Normal33mALow power 1.5 1.5mA Optional IDD7A380380mARev. 1.1 August. 2003< Detailed test conditions for DDR SDRAM IDD1 & IDD7A >IDD1 : Operating current: One bank operation1. Only one bank is accessed with tRC(min), Burst Mode, Address and Control inputs change logic state once per Deselect cycle.Iout = 0mA2. Timing patterns- CC/C4(200Mhz,CL=3) : tCK=5ns, CL=3, BL=4, tRCD=3*tCK(CC) 4*tCK(C4), tRC=11*tCK(CC) 12*tCK(C4), tRAS=8*tCKSetup : A0 N N R0 N N N N P0 N NRead : A0 N N R0 N N N N P0 N N - repeat the same timing with random address changing*50% of data changing at every transferIDD7A : Operating current: Four bank operation1. Four banks are being interleaved with tRC(min), Burst Mode, Address and Control inputs on Deselet edge are not changing.Iout = 1mA2. Timing patterns- CC/C4(200Mhz,CL=3) : tCK=5ns, CL=3, BL=4, tRCD=3*tCK(CC) 4*tCK(C4), tRC=11*tCK(CC) 12*tCK(C4), tRAS=8*tCKSetup : A0 N A1 RA0 A2 RA1 A3 RA2 N RA3 N NRead : A0 N A1 RA0 A2 RA1 A3 RA2 N RA3 N N - repeat the same timing with random address changing*50% of data changing at every transferLegend : A = Activate, R=Read, W=Write, P=Precharge, N=NOPRev. 1.1 August. 2003Rev. 1.1 August. 2003AC Operating ConditionsParameter/ConditionSymbol Min Max-10Unit NoteInput High (Logic 1) Voltage, DQ, DQS and DM signals VIH(AC)VREF + 0.31V Input Low (Logic 0) Voltage, DQ, DQS and DM signals.VIL(AC)VREF - 0.31V Input Differential Voltage, CK and CK inputs VID(AC)0.7VDDQ+0.6V 1Input Crossing Point Voltage, CK and CK inputsVIX(AC)0.5*VDDQ-0.20.5*VDDQ+0.2V2AC Overshoot/Undershoot specification for Address and Control PinsParameterSpecification DDR400Maximum peak amplitude allowed for overshoot 1.5V Maximum peak amplitude allowed for undershoot1.5V The area between the overshoot signal and VDD must be less than or equal to 4.5V-ns The area between the undershoot signal and GND must be less than or equal to4.5V-ns543210-1-2-3-4-50.50.68751.01.52.02.53.03.5 4.04.55.05.5 6.06.31256.57.0VDDOvershootMaximum Amplitude = 1.5VArea = 4.5V-nsMaximum Amplitude = 1.5V undershootGNDV o l t s (V )Tims(ns) AC overshoot/Undershoot DefinitionNotes :1. VID is the magnitude of the difference between the input level on CK and the input level on /CK.2. The value of VIX is expected to equal 0.5*VDDQ of the transmitting device and must track variations in the dc level of the same.Rev. 1.1 August. 2003Overshoot/Undershoot specification for Data, Strobe, and Mask PinsParameterSpecification DDR400Maximum peak amplitude allowed for overshoot 1.2V Maximum peak amplitude allowed for undershoot1.2V The area between the overshoot signal and VDD must be less than or equal to2.5V-ns The area between the undershoot signal and GND must be less than or equal to2.5V-ns543210-1-2-3-4-500.51.01.421.52.02.53.03.54.04.55.05.55.686.06.57.0VDDQOvershootMaximum Amplitude = 1.2VArea = 2.5V-nsMaximum Amplitude = 1.2VundershootGNDV o l t s (V )Tims(ns)DQ/DM/DQS AC overshoot/Undershoot DefinitionAC Timing Parameters and SpecificationsParameter Symbol - CC(DDR400@CL=3)- C4(DDR400@CL=3)Unit Note Min Max Min MaxRow cycle time tRC5560ns Refresh row cycle time tRFC7070ns Row active time tRAS4070K4070K ns RAS to CAS delay tRCD1518ns Row precharge time tRP1518ns Row active to Row active delay tRRD1010ns Write recovery time tWR1515ns Internal write to read command delay tWTR22tCKClock cycle time CL=3.0tCK510510ns16 CL=2.5612612nsClock high level width tCH0.450.550.450.55tCKClock low level width tCL0.450.550.450.55tCKDQS-out access time from CK/CK tDQSCK-0.55+0.55-0.55+0.55nsOutput data access time from CK/CK tAC-0.65+0.65-0.65+0.65nsData strobe edge to ouput data edge tDQSQ-0.4-0.4ns13 Read Preamble tRPRE0.9 1.10.9 1.1tCKRead Postamble tRPST0.40.60.40.6tCKCK to valid DQS-in tDQSS0.72 1.280.72 1.28tCKWrite preamble setup time tWPRES00ps5 Write preamble tWPRE0.250.25tCKWrite postamble tWPST0.40.60.40.6tCK4 DQS falling edge to CK rising-setup time tDSS0.20.2tCKDQS falling edge from CK rising-hold time tDSH0.20.2tCKDQS-in high level width tDQSH0.35 0.35 tCKDQS-in low level width tDQSL0.35 0.35 tCKAddress and Control Input setup time tIS0.60.6ns h,7~10 Address and Control Input hold time tIH0.60.6ns h,7~10 Data-out high impedence time from CK/CK tHZ- tAC max- tAC max ns3 Data-out low impedence time from CK/CK tLZ tAC min tAC max tAC min tAC max ns3 Mode register set cycle time tMRD22tCKDQ & DM setup time to DQS, slew rate 0.5V/ns tDS0.40.4ns i, j DQ & DM hold time to DQS, slew rate 0.5V/ns tDH0.40.4ns i, j DQ & DM input pulse width tDIPW 1.75 1.75ns9 Control & Address input pulse width for each input tIPW 2.2 2.2ns9 Refresh interval time tREFI7.87.8us6Output DQS valid window tQHtHP-tQHS-tHP-tQHS-ns12Clock half period tHPmintCH/tCL-mintCH/tCL-ns11, 12Rev. 1.1 August. 2003Rev. 1.1 August. 2003Component Notes1.V ID is the magnitude of the difference between the input level on CK and the input level on CK.2. The value of VIX is expected to equal 0.5*VDDQ of the transmitting device and must track variations in the dc level of the same.3. tHZ and tLZ transitions occur in the same access time windows as valid data transitions. these parameters are not referenced to a specific voltage level but specify when the device output in no longer driving (HZ), or begins driving (LZ).4. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but sys tem performance (bus turnaround) will degrade accordingly.5. The specific requirement is that DQS be valid (HIGH, LOW, or at some point on a valid transition) on or before this CK edge. A valid transition is defined as monotonic and meeting the input slew rate specifications of the device. when no writes were previ ously in progress on the bus, DQS will be tran sitioning from High- Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on tDQSS.6. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.7. For command/address input slew rate ≥ 0.5 V/ns8. For CK & CK slew rate ≥ 0.5 V/ns9. These parameters guarantee device timing, but they are not necessarily tested on each device. They may be guaranteed by device design or tester correlation.10. Slew Rate is measured between VOH(ac) and VOL(ac).11. Min (tCL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this value can be greater than the minimum specification limits for tCL and tCH).....For example, tCL and tCH are = 50% of theperiod, less the half period jitter (tJIT(HP)) of the clock source, and less the half period jitter due to crosstalk (tJIT(crosstalk)) into the clock traces.12. tQH = tHP - tQHS, where:tHP = minimum half clock period for any given cycle and is defined by clock high or clock low (tCH, tCL). tQHS accounts for 1) The pulse duration distortion of on-chip clock circuits; and 2) The worst case push-out of DQS on one tansition followed by the worst case pull-in of DQ on the next transition, both of which are, separately, due to data pin skew and output pattern effects, and p- channel to n-channel variation of the output drivers.13. tDQSQConsists of data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers for any given cycle.14. tDAL = (tWR/tCK) + (tRP/tCK)For each of the terms above, if not already an integer, round to the next highest integer. Example: For DDR400(CC) at CL=3 and tCK=5ns tDAL = (15 ns / 5 ns) + (15 ns/ 5ns) = {(3) + (3)}CLK tDAL = 6 clocks15. In all circumstances, tXSNR can be satisfied using tXSNR=tRFCmin+1*tCK16. The only time that the clock frequency is allowed to change is during self-refresh mode.ParameterSymbol - CC(DDR400@CL=3)- C4(DDR400@CL=3)Unit Note MinMax MinMax Data hold skew factortQHS 0.50.5ns 12Auto Precharge write recovery + precharge time tDAL ----ns 14Exit self refresh to non-READ command tXSNR 7575ns 15Exit self refresh to READ commandtXSRD200-200-tCKRev. 1.1 August. 2003Table 4 : Input/Output Setup & Hold Derating for Rise/Fall Delta Slew RateTable 5 : Output Slew Rate Characteristice (X8 Devices only)Table 6 : Output Slew Rate Characteristice (X16 Devices only)Table 7 : Output Slew Rate Matching Ratio CharacteristicsDelta Slew Rate tDS tDH Units Notes +/- 0.0 V/ns 00ps i +/- 0.25 V/ns +50+50ps i +/- 0.5 V/ns+100+100psiSlew Rate CharacteristicTypical Range(V/ns)Minimum (V/ns)Maximum (V/ns)Notes Pullup Slew Rate 1.2 ~ 2.5 1.0 4.5a,c,d,f,g Pulldown slew1.2 ~2.51.04.5b,c,d,f,gSlew Rate CharacteristicTypical Range(V/ns)Minimum (V/ns)Maximum (V/ns)Notes Pullup Slew Rate 1.2 ~ 2.50.7 5.0a,c,d,f,g Pulldown slew1.2 ~2.50.75.0b,c,d,f,gAC CHARACTERISTICSDDR400PARAMETERMINMAX Notes Output Slew Rate Matching Ratio (Pullup to Pulldown)--e,kSystem Characteristics for DDR SDRAMThe following specification parameters are required in systems using DDR400 devices to ensure proper system perfor-mance. these characteristics are for system simulation purposes and are guaranteed by design.Table 1 : Input Slew Rate for DQ, DQS, and DMTable 2 : Input Setup & Hold Time Derating for Slew RateTable 3 : Input/Output Setup & Hold Time Derating for Slew RateAC CHARACTERISTICSDDR400PARAMETERSYMBOL MIN MAX Units Notes DQ/DM/DQS input slew rate measured between VIH(DC), VIL(DC) and VIL(DC), VIH(DC)DCSLEW0.54.0V/nsa, kInput Slew RatetIS tIH Units Notes 0.5 V/ns 00ps h 0.4 V/ns +500ps h 0.3 V/ns+100pshInput Slew RatetDS tDH Units Notes 0.5 V/ns 00ps j 0.4 V/ns +75+75ps j 0.3 V/ns+150+150psjSystem Notes :a. Pullup slew rate is characteristized under the test conditions as shown in Figure 1.Test pointOutput50ΩVSSQFigure 1 : Pullup slew rate test loadb. Pulldown slew rate is measured under the test conditions shown in Figure 2.VDDQ50ΩOutputTest pointFigure 2 : Pulldown slew rate test loadc. Pullup slew rate is measured between (VDDQ/2 - 320 mV +/- 250 mV)Pulldown slew rate is measured between (VDDQ/2 + 320 mV +/- 250 mV)Pullup and Pulldown slew rate conditions are to be met for any pattern of data, including all outputs switching and only one output switching.Example : For typical slew rate, DQ0 is switchingFor minmum slew rate, all DQ bits are switching from either high to low, or low to high.For Maximum slew rate, only one DQ is switching from either high to low, or low to high.The remaining DQ bits remain the same as for previous state.d. Evaluation conditionsTypical : 25 °C (T Ambient), VDDQ = 2.6V, typical processMinimum : 70 °C (T Ambient), VDDQ = 2.5V, slow - slow processMaximum : 0 °C (T Ambient), VDDQ = 2.7V, fast - fast processe. The ratio of pullup slew rate to pulldown slew rate is specified for the same temperature and voltage, over the entire temperature and voltage range. For a given output, it represents the maximum difference between pullup and pulldown drivers due to process variation.f. Verified under typical conditions for qualification purposes.g. TSOPII package divices only.h. A derating factor will be used to increase tIS and tIH in the case where the input slew rate is below 0.5V/nsas shown in Table 2. The Input slew rate is based on the lesser of the slew rates detemined by either VIH(AC) to VIL(AC) orVIH(DC) to VIL(DC), similarly for rising transitions.i. A derating factor will be used to increase tDS and tDH in the case where DQ, DM, and DQS slew rates differ, as shown in Tables 3 & 4. Input slew rate is based on the larger of AC-AC delta rise, fall rate and DC-DC delta rise, Input slew rate is based on the lesser of the slew rates determined by either VIH(AC) to VIL(AC) or VIH(DC) to VIL(DC), similarly for rising transitions.The delta rise/fall rate is calculated as:{1/(Slew Rate1)} - {1/(Slew Rate2)}For example : If Slew Rate 1 is 0.5 V/ns and slew Rate 2 is 0.4 V/ns, then the delta rise, fall rate is - 0.5ns/V . Using the table given, this would result in the need for an increase in tDS and tDH of 100 ps.Rev. 1.1 August. 2003。

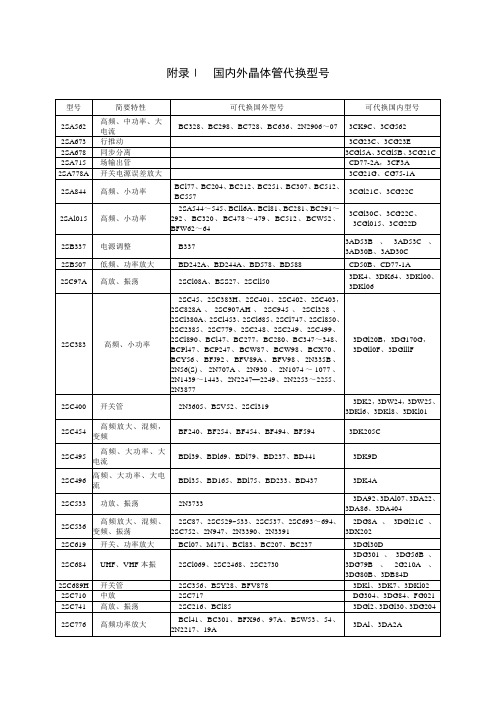

常用三极管参数大全

玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理。

电子技术专科教材013

2SC829

高频、低频放大

2SC62、2SC544、2SC561~562、2SCl686、2N3289~3292

3DGlllE

2SC911A

功放、振荡

2N5644

3DA816

2SC917

UHF高放、混频

2SC2466、2SC2728、2SC2731、2N6389

2DG302、FG024

四2输入与非门(OC)

四2输人或非门

四2输入与非门(OC)

六反相器

六反相器(OC)

六反相缓冲/驱动器(OC)

六缓冲/驱动器(OC)

四2输入与门

四2输入与门(OC)

三3输入与非门

三3输入与门

三3输入与非门(OC)

三3输入与门(OC)

六高压输出反相缓冲/驱动器(OC)

六高压输出缓冲/驱动器(OC)

双4辅人与非门

2SC920

高频放大、混频、变频

2SC33、2SC838~839,BF237~238

3DGlllF

2SC930

高频、小功率

2SC545、2SC772、2SC923、2N1992、2N3293~3294

3DG111D

2SCl008

高频、大电流

BCl41、BC301、BSSl5、BSS42、BSW39、2N5320

4线—七段译码器/驱动器(BCD输入,OC输出)

双2路2—2输入与或非门(一门可扩展)

双2路2—2(3)输入与或非门

4路2—3—2—2输人与或门(可扩展)

4路2—3—2—2输入与或非门(可扩展)

2路4—4输入与或非门(可扩展)

1/50分频器

双4输入与扩展器

K4S561632H-UP75中文资料

RAS

Row address strobe

CAS

Column address strobe

WE

Write enable

DQM

Data input/output mask

GENERAL DESCRIPTION

The K4S560432H / K4S560832H / K4S561632H is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 16,777,216 words by 4 bits / 4 x 8,388,608 words by 8bits / 4 x 4,194,304 words by 16bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

CLK ADD

Row Buffer Refresh Counter

遥控器资料查询

M50431-101SP TMP47C433AN M50453/431-101SP M50453/431-101SP M50453/431-101SP PCA84C440/504/640/641 PCA84C440/504/640/641 PCA84C440/504/640/641 TMP47C432/433/434AN TMP47C432/433/434AN M50436-560SP PCA84C440/504/640/641 M34300N4-012 TMP47C432/433/434AN M50436-560SP M50453/431-101SP TMP47C432/433/434AN M34300N4-012 M50453/431-101SP

127

长虹

K8B

TC901C K9D

TC9012 SAA3010T SAA3010

131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176

遥控器IC型号 遥控器 型号 20142 D6600 D6600 D6600 D6600 D6600

电视机CPU型号 型号 电视机

TC-9028-021 SAA3010 SAA3010 SAA3010 SAA3010

LUKS-5140-M2

SAA3010 SAA3010

TC9012-011

TC9012-011

TMP47C433AN TMP47C433AN TMP47C433AN-3849 TMP47C433AN TMP47C433AN TMP47C433AN TMP47C433AN TMP47C433AN M50436-560SP M50436-560SP PCM84C640/CH05001

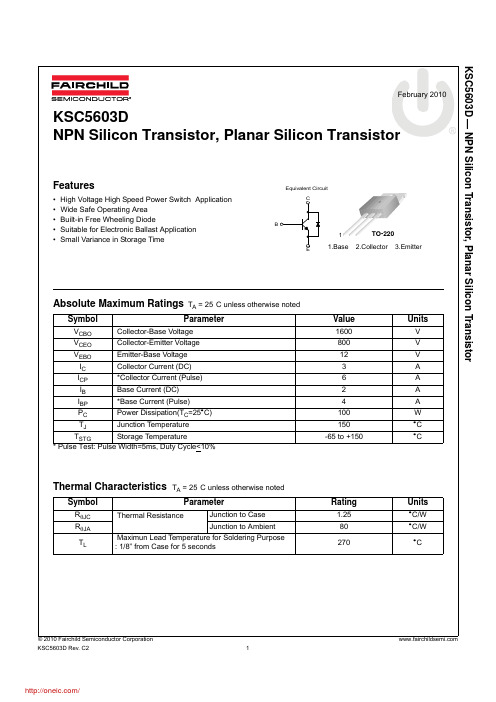

KSC5603DTU;KSC5603D;中文规格书,Datasheet资料

* Pulse Test: Pulse Width=5ms, Duty Cycle<10%Thermal Characteristics T A = 25°C unless otherwise notedI C Collector Current (DC)3A I CP *Collector Current (Pulse)6A I B Base Current (DC)2A I BP *Base Current (Pulse)4A P C Power Dissipation(T C =25°C)100W T JJunction Temperature150°C T STG Storage Temperature-65 to +150°CSymbolParameterRatingUnitsR θJC Thermal ResistanceJunction to Case 1.25°C/W R θJA Junction to Ambient80°C/W T LMaximun Lead Temperature for Soldering Purpose : 1/8” from Case for 5 seconds270°CI C=2A, I B=0.4A T A=25°C0.85 1.2VT A=125°C0.74 1.1V C ib Input Capacitance V EB=10V, I C=0, f=1MHz7451000pF C ob Output Capacitance V CB=10V, I E=0, f=1MHz56500pF f T Current Gain Bandwidth Product I C=0.1A,V CE=10V5MHz V F Diode Forward Voltage I F=0.4A T A=25°C0.76 1.2VT A=125°C VI F=1A T A=25°C0.83 1.5VT A=125°C VI B2=250mA, Vz=300V,L C =200H t STG Storage Time T A =25°C 140175ns T A =125°C ns t FFall TimeT A =25°C 170200ns T A =125°CnsThe following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is notAccuPower¥Auto-SPM¥Build it Now¥CorePLUS¥CorePOWER¥CROSSVOLT¥CTL¥Current Transfer Logic¥DEUXPEED®Dual Cool™ EcoSPARK®EfficientMax¥®Fairchild®Fairchild Semiconductor®FACT Quiet Series¥FACT®FAST®FastvCore¥FETBench¥FlashWriter®*FPS¥F-PFS¥FRFETGlobal Power Resource SMGreen FPS¥Green FPS¥ e-Series¥G max¥GTO¥IntelliMAX¥ISOPLANAR¥MegaBuck¥MICROCOUPLER¥MicroFET¥MicroPak¥MicroPak2¥MillerDrive¥MotionMax¥Motion-SPM¥OptoHiT™OPTOLOGIC®OPTOPLANAR®®PDP SPM™Power-SPM¥PowerTrenchPowerXS™Programmable Active Droop¥QFET®QS¥Quiet Series¥RapidConfigure¥¥Saving our world, 1mW/W/kW at a time™SignalWise¥SmartMax¥SMART START¥SPM®STEALTH¥SuperFET¥SuperSOT¥-3SuperSOT¥-6SuperSOT¥-8SupreMOS¥SyncFET¥Sync-Lock™®*The Power FranchiseTinyBoost¥TinyBuck¥TinyCalc¥TinyLogic®TINYOPTO¥TinyPower¥TinyPWM¥TinyWire¥TriFault Detect¥TRUECURRENT¥*P SerDes¥UHC®Ultra FRFET¥UniFET¥VCX¥VisualMax¥XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) areintended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status Definition分销商库存信息:FAIRCHILDKSC5603DTU KSC5603D。

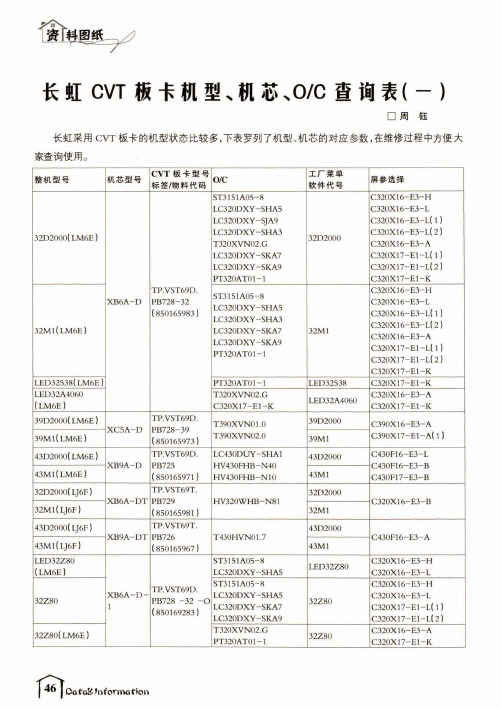

长虹CVT板卡机型、机芯、OC查询表(一)

长虹C V T板卡机型、机芯、0/C查询表(一)□周钮长虹采用C V T板卡的机型状态比较多,下表罗列了机型、机芯的对应参数,在维修过程中方便大 家查询使用。

整机型号机芯型号C V T板卡型号标签/物料代码O/C工厂菜单软件代号屏参选择32D2000(LM6E)X B6A-D T P.VST69D.PB728-32(850165983)ST3151A05-8LC320D X Y-SHA5LC320D X Y-SJA9LC320D X Y-SHA3T320X V N02.GLC320D X Y-SKA7LC320D X Y-SKA9PT320AT01-132D2000C320X16-E3-HC320X16-E3-LC320X16-E3-U1)C320X16-E3-L(2)C320X16-E3-AC320X17-E1-L(1)C320X17-E1-L(2)C320X17-E1-K32M1(LM6E)ST3151A05-8LC320D X Y-SHA5LC320D X Y-SHA3LC320D X Y-SKA7LC320D X Y-SKA9PT320AT01-132M1C320X16-E3-HC320X16-E3-LC320X16-E3-L(1)C320X16-E3-L(2)C320X16-E3-AC320X17-E1-L(1)C320X17-E1-L(2)C320X17-E1-KLED32538( LM6E)PT320A T01-1LED32538C320X17-E1-KLED32A4060 (LM6E)T320X V N02.GC320X17-E1-KLED32A4060C320X16-E3-AC320X17-E1-K39D2000( LM6E)X C5A-D T P.V ST69D.PB728-39(850165973)T390X V N01.0T390X V N02.039D2000C390X16-E3-AC390X17-E1-A(1)39M1(LM6E)39M143D2000( LM6E)X B9A-D T P.VST69D.PB725(850165971)LC430D U Y-SHA1HV430FHB-N40HV430FHB-N1043D2000C430F16-E3-LC430F16-E3-BC430F17-E3-B43M1(LM6E)43M132D2000( LJ6F)X B6A-D T T P.VST69T.PB729(850165981)HV320W HB-N8132D2000C320X16-E3-B32M1(LJ6F)32M143D2000( LJ6F)X B9A-D T T P.VST69T.PB726(850165967)T430HVN01.743D2000C430F16-E3-A43M1(LJ6F)43M1 LED32Z80(LM6E)X B6A-D-1T P.VST69D.PB728 -32 -〇(850169283)ST3151A05-8LC320D X Y-SHA5LED32Z80C320X16-E3-HC320X16-E3-L32Z80ST3151A05-8LC320D X Y-SHA5LC320D X Y-SKA7LC320D X Y-SKA932Z80C320X16-E3-HC320X16-E3-LC320X17-E卜 L(1)C320X17-E1-L(2)32Z80( LM6E)T320X V N02.GPT320AT01-132Z80C320X16-E3-AC320X17-E1-KP f Da I n f o rma t ?onA P P l-I A N J C E R E P A I T R I T S I G (续表)整机型号机芯型号C V T板卡型号标签/物料代码O/C工厂菜单软件代号屏参选择LED32Z80( LJ6F)XB6A-DT-1TP.VST69T.PB729-〇(850169376)HV320WHB—N81LED32Z80C320X16-E3-BLED39Z8〇( LM6E)XC5A-D-1TP.VST69D.PB728-39-0(850169382)T390XVN01.0LED39Z80C390X16-E3-A39Z80T390XVN01.0T390XVN02.039Z80C390X16-E3-AC390X17-E1-A(1)LED43Z80(LJ6F)XB9A-DT-1TP.VST69T.PB726-〇(850169385)T430HVN01.7LED43Z80C430F16-E3-A43Z80(LJ6F)43Z8043D2000(LM7C)XB9A-DT-2TP.VST69T.PB726-1(850170131)T430HVN01.543D2000C430F16-E3-A( 1 )43M1(LM7C)43M1LED43Z8〇( LM7C)XB9A-DT-4TP.VST69T.PB726-2(850170135)T430HVN01.5LED43Z80C430F16-E3-A( 1)43Z80(LM7C)43Z8032D2000(LM8L)XB6A-DT-4TP.VST69T.PB719(850183372)HV320WHB-N56HV320WHB-N8632D2000C320X16-E3-B(3)C320X16-E3-B(4)32M1(LM8L)32M1LED32A4060 (LM8L)XB6A-DT-4TP.VST69T.PB719(850183372)HV320WHB-N86LED32A4060C320X16-E3-B(4)LED32568(LM8L)XB6A-DT-4TP.VST69T.PB719(850183372)HV320WHB-N86LED32568C320X16-E3-B(4)32Z80( LM8L)XB6A-DT-5TP.VST69T.PB719-OBL( 850183376)HV320WHB-N56HV320WHB-N8632Z80C320X16-E3-B(3)C320X16-E3-B(4)LED32568(LM6E)XB6A-D TP.VST69D.PB728-32(850165983)T320XVN02.GPT320AT01-1LED32568C320X16-E3-AC320X17-E1-K32D200〇( LMBF)XB6A-DT-9TP.VST69T.PB719-1(850201465)PT320AT01-432D2000C320X17-E1-K(2)32M1(LMBF)32M1LED32A4060(LMBF)LED32A4060 LED32538(LMBF)LED32538 LED32568( LMBF)LED3256832Z8〇( LMBF)XB6A -DT -10TP.VST69T.PB719-OBL—1(850201466)32Z80C320X17-E1-K(2)32CE122〇(LMBR)XB6A-DT-4TP.VST69T.PB719-SY(850205410)HV320WHB-N8632CE1220C320X16-E3-B(5)43D200〇(LMCW)XB6A -D T -11TP.VST69T.PB926(850214088)HV430FHB-N1043D2000C430F17-E3-B( 1)43M1(LMCW)43M143Z80( LMCW)TP.VST69T.PB926 -OBL( 850217285)43Z80Oatck&lnt'ormatfo “47(续表)整机型号机芯型号CVT板卡型号标签/物料代码O/C工厂菜单软件代号屏参选择32M1(LM EW)X B6G-D T T P.VST69T.PB928-32(850225395)HV320W H B-N8632M1C320X18-E3-B32M1(LM EW) CS32L1X B6G-D TT P.VST69T.PB928-32-1(850235851 )HV320W H B-N5632M1C320X18-E3-B(3)32M1(L M E U)CS32L1(LM M N) C S32L1(L M E U)X B6G-DT P.VST69D.PB921-32(850225381)T P.VST69D.PB921-32-F L l(850275296)T P.VST69D.PB921-32-F L(811140903)ST3151A07-2ST3151A07 -2(V2.3)ST3151A07-2ST3151A07 -2(V2.3)C320X18-E3-HC320X20-E2-HC320X18-E3-H39M1(L M E U)X B6G-D T P.VST69D.PB921-39 (850225389)T390X V N02.039M1C390X18-E3-ALC390T U1A39M1C390X18-E3-P43M1(L M E U)X B6G-D T-1T P.VST69T.PB922-43(850225393)HV430FHB-N1043M1C430F18-E3 -B(1)43M1(L M E U)X B6G-D T-1T P.VST69T.PB922-43-1(850245420)HV430FH B-N4243M1C430F18-E3-B(4)32M1(L JG P)X B6G-D T-4T P.VST69T.PB929(850236205)HV320W H B-N5632M1C320X18-E3-B(3)32Z8〇(LM EW)X B6G-D T T P.VST69T.PB928-32 -O BL(850241934)HV320W H B-N5632Z80C320X18- E3-B(3)32C E310X B6G-D T T P.VST69T.PB928-32-S Y(850241935)HV320W H B-N5632C E310C320X18-E3-B(3)39C E310X B6G-D T P.VST69D.PB921-39-S Y(850241936)T390X V N02.039C E310C390X18-E3-A43C E310X B6G-D T-1T P.V ST69T.PB922-43-S Y(850241937)HV430FH B-N4243M1C430F18-E3-B(4)43C E310X B6G-D T-1T P.VST69T.PB922-43 -S Y1(850269613)HV430FH B-N1043M1C430F18—E3-B(1)32C E1220(LM LE)X B6G-D T T P.VST69T.PB928-32 -1 -S Y(850257677)HV320W H B-N5632C E1220(LM LE)C320X18—E3-B(3)32C E1220(LM LH)X B6G-D T-4T P.VST69T.PB929-S Y(850257678)HV320W H B-N5632C E1220(LM LH)C320X18-E3-B(3)32G5FX D3G-iD TPD.M T5510.PB702 -32(850225371 )ST3151A07-232G5F C320X18-E3-H32A1(L M E T) 32D3F(L M E T)32G5F(L M E V)X D3G-iD T TPD.M T5510T.PB709 -32(850225367)HV320W H B-N8632G5F C320X18-E3-B(1)32A1(L M E V)32D3F(L M E V)32Z80I(L M E V)32C E F10園(未完待续)1^1O ata&fnformat?on。

AFND5608U1-CKAK规格书 (K9F5608)

256Mbit (32Mx8Bit)NAND FLASH256Mb NAND FLASHAFND5608U1 (/CE Don’t Don t Care mode)PreliminaryConfidential1256Mbit (32Mx8Bit)NAND FLASHRevision No. Rev.00 Initial DraftHistoryDraft Date June. 2012Remark PreliminaryPreliminaryConfidential2256Mbit (32Mx8Bit)NAND FLASHFEATURES SUMMARY• Power Supply-3.3V Device(AFND5608U1) 2.7V ~ 3.6V• Copy-Back PROGRAM Operation-Fast Page copy without external buffering• Organization-Memory Cell Array : (32M + 1024K) x 8bits -Data Register : (512 + 16) x 8bits• Command Register Operation y features • Security-OTP area, 16Kbytes(32 pages)• Automatic Program and Erase-Page Program : (512 + 16)Bytes -Block Erase : (16K +512)Bytes• Hardware Data Protection-Program / Erase locked during Power transitions• Page Read Operation-Page g Size : (512 + 16)Bytes y -Random Access : 12us(Max.) -Serial Page Access : 30ns(Min.)• Data Integrity-Endurance : 100K Program / Erase Cycles (With 1bit/528byte ECC) -Data Retention : 10 years• Fast Write Cycle Time-Program time : 200us(Typ.) -Block Erase time : 2ms(Typ.)• Package-AFND5608U1 : Pb-Free Package 48-pin TSOP(12 x 20 / 0.5 mm pitch) 48-Ball FBGA: 9.0 x 9.0 x 1.0mmPreliminaryConfidential3256Mbit (32Mx8Bit)NAND FLASHProduct InformationPart number AFND5608U1-CKAK AFND5608U1-CKCK Voltage 2.7~3.6V Bus Width x8 Package 12x20mm TSOP 9x9mm FBGAPreliminaryConfidential4256Mbit (32Mx8Bit)NAND FLASHGENERAL DESCRIPTIONThe AFND5608U1 is 256Mbit with spare 8Mbit capacity. The device is offered in 3.3V power supply. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. A program operation can be performed in typical 200us on the 528-bytes and an erase operation can be performed in typical 2ms on a 16K-bytes block. Data in the page can be read out at 30ns cycle time per byte. byte The I/O pins serve as the ports for address and data input/output as well as command input. Command, data and address are synchronously introduced using /CE, /WE, ALE and CLE input pin. The output pin R/B(open drain buffer) signals the status of the device during each operation. In a system with multiple memories the R/B pins can be connected all together to provide a global status signal. The on-chip write control automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take advantage of the AFND5608U1’s extended reliability of 100K program / erase cycles by providing ECC(Error Correction Code) with real time mapping-out algorithm. The chip could be offered with the /CE don’t care function. This function allows the direct download of the code form the NAND flash memory device by a microcontroller, since the /CE transitions do not stop the read operation. The copy back function allows the optimization of defective blocks management : when a page program operation fails the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase. Also, this device includes extra features like OTP area. The AFND5608U1 is an optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility.PreliminaryConfidential5256Mbit (32Mx8Bit)NAND FLASHOrdering InformationAF ND XXATO Solution S l i Co. LtdXX X X X - X XX XPage Read Mode K : /CE don’t care Package Typeyp Product type ND : NAND FlashKA : 48pin-TSOP 12x20mm KC : 48ball-FBGA 9x9mm Temperature C : 0℃~70℃Generation NAND Flash Density 56 : 256Mbit Blank : 1st A : 2nd B : 3rd Classification 1 : SLC S/BNAND Flash I/O 8 : x8Operation Voltage U : 2.7~3.6VPreliminaryConfidential6256Mbit (32Mx8Bit)NAND FLASHPIN CONFIGURATION (TSOP1)PACKAGE DIMENSIONS48-PIN LEAD/LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)PreliminaryConfidential7256Mbit (32Mx8Bit)NAND FLASHPIN CONFIGURATION (48ball-FBGA )1 A23456WP#ALEVSSCE#WE#R/BBNCRE#CLENCNCNCCNCNCNCNCNCNCDNCNCNCNCNCNCENCNCNCNCNCNCFNCIO0NCNCNCVCCGNCIO1NCVCCIO5IO7HVSSIO2IO3IO4IO6VSSPreliminaryConfidential8256Mbit (32Mx8Bit)NAND FLASHPACKAGE OUTLINE DRAWING (48ball-FBGA 9x9mm)DescriptionFBGA 48BALLDimension9.0mm x 9.0mm x 0.90mm (Max. 1.0mm T)1. ALL DIMENSIONS are in Millimeters. 2. POST REFLOW SOLDER BALL DIAMETER. (Pre Reflow diameter : Ø0 Ø0.40 40±0.02) 0 02)PreliminaryConfidential9256Mbit (32Mx8Bit)NAND FLASHPIN DESCRIPTIONPin Name I/O0 ~ I/O7 Pin Function DATA INPUTS/OUTPUTS The I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled. COMMAND LATCH ENABLE The CLE input controls the activating path for commands sent to the command register. register When active high, commands are latched into the command register through the I/O ports on the rising edge of the /WE signal. ADDRESS LATCH ENABLE The ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of /WE with ALE high CHIP ENABLE The /CE input is the device selection control. When the device is in the Busy state, /CE high is ignored, and the device does not return to standby mode in program or erase operation. Regarding /CE control during read operation, refer to ‘Page Read’ section of device operation. READ ENABLE The /RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of /RE which also increments the internal column address counter by one. WRITE ENABLE The /WE input p controls writes to the I/O p port. Commands, address and data are latched on the rising edge of the /WE pulse. WRITE PROTECT The /WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the /WP pin is active low. READY/BUSY OUTPUT The R/B output indicates the status of the device operation. When low, it indicates that a program, erase of random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled. POWER Vcc is the power supply for device. GROUND NO CONNECTION Lead is not internally connected.CLEALE/CE/RE/WE/WPR/BVcc Vss N.CN t :C Note Connect t all ll V Vcc and dV Vss pins i of f each hd device i t to common power supply l outputs t t Do not leave Vcc or Vss disconnected.PreliminaryConfidential10256Mbit (32Mx8Bit)NAND FLASHFigure 1. AFND5608U1 FUNCTIONAL BLOCK DIAGRAMFigure 2. AFND5608U1 ARRAY ORGANIZATIONPreliminaryConfidential11NOTE : Column Address : Starting Address of the Register.00h Command(Read) : Defines the starting address of the 1st half of the register.01h Command(Read) : Defines the starting address of the 2nd half of the register.* A8 is set to “Low” or “High” by the 00h or 01h Command.* The device ignores any additional input of address cycles than required.256Mbit (32Mx8Bit)NAND FLASHPRODUCT INTRODUCTIONThe AFND5608U1 is a 264Mbits(276,824,064 bits) memory organized as 65,536 rows(pages) by 528 columns. Spare sixteen columns are located from column address of 512 to 527. A 528-bytes data register is connected to memory cell arrays accommodating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 16 cells that are serially connected to form a NAND structure. Each of the 16 cells resides in a different page. A block consists two NAND structures. A NAND structure consists of 16 cells. Total 135,168 NAND structures reside in a block. The program and read operations are executed on a page basis while the erase operation is executed on a block operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 2,048 separately erasable 16K-bytes blocks. It indicates that the bit by bit erase operation is prohibited on the AFND5608U1.The AFND5608U1 has addresses multiplexed into 8 I/O’s. This scheme dramatically reduces pin counts and allows systems upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O’s by bringing /WE to low while /CE is low. Data is latched on the rising edge of /WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. The 32M byte physical space requires 24 addresses, thereby requiring three cycles for byte-level addressing : 1 cycle of column address, 2 cycles of row address, in that order. Page Read and Page Program need the same three address cycles following the required command input. In Block Erase operation, however only the 2 cycles of row address are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the AFND5608U1.Table 1. Command SetsFunction1’st Cycle 2’nd CycleAcceptable CommandDuring BusyRead 100h/01h(1)-Read 250h -Read ID 90h -Reset FFh -oNOTE : Caution : Any undefined command inputs are prohibited except for above command set of Table 1.Page Program 80h 10h Copy Back Program 00h 8Ah Block Erase 60h D0h Read Status70h-o PreliminaryConfidential12256Mbit (32Mx8Bit)NAND FLASH ABSOLUTE MAXIMUM RATINGSParameter Symbol Rating UnitVoltage on any pin relative to Vss Vcc-0.6 to + 4.6V VIN-0.6 to + 4.6VI/O-0.6 to +4.6Temperature Under Bias TBIAS-50 to + 125˚CStorage Temperature TSTG-65 to + 150˚Cg pNOTE :1.Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to –2.0V for periods<20ns.Maximum DC voltage on input/output pins is VCC+0.3V which, during transition, may overshoot toVCC+0.2V for periods < 20ns.2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATING are exceeded. Functional operationshould be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure top p absolute maximum rating conditions for extended periods may affect reliability.RECOMMENDED OPERATING CONDITIONS(Voltage reference to GND, AFND5608U1-CX : T A= 0 to 70℃, AFND5608U1-IX : T A= -40 to 85℃)Parameter Symbol3.3VUnit Min Typ MaxSupply Voltage Vcc 2.7 3.3 3.6V Vss000VPreliminary Confidential13256Mbit (32Mx8Bit)NAND FLASHDC AND OPERATING CHARACTERISTICSParameterSymbol Test Conditions 3.3VUnitMin Typ Max OperatingCurrentSequential Read ICC1tRC=30ns, /CE=VIL,Iout=0mA-1020mAProgram ICC2-1020EraseICC3-1020Standby Current(TTL)ISB1/CE-VIH, /WP=0V/Vcc--1Standby Current(CMOS)ISB2/CE=Vcc-0.2, /WP=0V/Vcc -1050uAInput Leakage Current ILI VIN=0 to Vcc(max)--±10Output Leakage Current ILO Vout=0 to Vcc(max)--±10Input High Volgate VIH -0.8*VCC-Vcc +03+0.3VInput Low Voltage, All inputs VIL --0.3-0.2*VCCOutput High Voltage Level VOH AFND5608U1: IOH = -400uA 2.4--Output Low Voltage Level VOL AFND5608U1: IOL = 2.1mA --0.4Output Low Current(R/B)IOLVOL=0.4V 810-mAp (/)(R/B)VALID BLOCKParameter Symbol Min Typ Max Unit Valid Block NumberNVB2,008-2,048BlocksNote :1.The device may include invalid blocks when first shipped. Additional invalid blocks may developwhile being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or program factory-marked bad blocks. Refer to the attached technical notes for a appropriate management of invalid blocks.2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erasecycles with 1bit/528Byte ECC.3. Minimum 1,004 valid blocks are guaranteed for each contiguous 128Mb memory space.PreliminaryConfidential14256Mbit (32Mx8Bit)NAND FLASHAC TEST CONDITION(AFND5608U1CX:T=0to70℃AFND5608U1IX:T=40to85℃)ParameterValue AFND5608U1(3.3V)Input Pulse Levels0.4V to 2.4VInput Rise and Fall Times5nsInput and Output Timing Levels 1.5V(AFND5608U1-CX : T A= 0 to 70℃, AFND5608U1-IX : T A= -40 to 85℃)Output Load 1 TTL GATE and CL=100pF CAPACITANCE (Temp=25℃, Vcc=3.3V, f=1.0Mhz)Item Symbol Test Condition Min Typ Max Input/Output Capacitance CI/O VIL=0V-10pF Input Capacitance CIN VIN=0V-10pFMODE SELECTIONCLE ALE/CE/WE/RE/WP ModeH L L↑edge H XRead Mode Command InputL H L↑edge H X Address Input(3 clocks) NOTE: Capacitance is periodically sampled and not 100% tested.H L L↑edge H HWrite Mode Command InputL H L↑edge H H Address Input(3 clocks) L L L↑edge H H Data InputL L L H↓edge X Data OutputX X X X H X During Read(Busy)During Program(Busy) X X X X X H During Program(Busy)X X X X X H During Erase(Busy)X X X X X L Write ProtectX X H X X0V/Vcc(1)StandbyNote : 1. /WP should be biased to CMOS high or CMOS low for standby.Preliminary Confidential15256Mbit (32Mx8Bit)NAND FLASH Program / Erase CharacteristicsParameter Symbol Min Typ Max Unit Program Time tPROG-200500usNumber of Partial Program Cycles in the same page Main ArrayNop--2Cycle Spare Array--3CycleBlock Erase Time tVERS-23msAC TIMING CAHARACTERISTICS FOR COMMAND / ADDRESS / DATA INPUTParameter Symbol Min Max UnitCLE setup Time tCLS0 -nsCLE Hold Time tCLH10-ns/CE setup Time tCS0 -ns/CE Hold Time tCH10-ns//WE Pulse Width tWP(1)15-nsALE setup Time tALS0 -nsALE Hold Time tALH10-nsData setup Time tDS10-nsData Hold Time tDH5-nsW it C l Ti30Write Cycle Time tWC30 -ns/WE High Hold Time tWH10-ns Address to Data Loading Time tADL100-ns Note : 1. If tCS is set less than 10ns, tWP must be minimum 25ns, otherwise, tWP may be minimum 15ns.Preliminary Confidential16256Mbit (32Mx8Bit)NAND FLASHAC CAHARACTERISTICS FOR OPERATIONParameterSymbol Min Max Unit Data Transfer from Cell to RegistertR -12us ALE to /RE Delay tAR 10-ns CLE to /RE Delay tCLR 10-ns Ready to /RE Low tRR 20-ns RE Pulse Width tRP/ tRPB 15-ns WE High to Busy tWB -100ns Read Cycle Time tRC 30-ns /RE Access Time tREA/tREAB -18ns /CE Access Time tCEA -23ns /RE High to Output Hi-Z tRHZ -30ns /CE High to Output Hi-Z tCHZ -20ns /CE High to ALE or CLE Don’t Care tCSD 10-ns /RE or /CE High to Output holdtOH 15-ns /RE High Hold Time tREH 10-ns Output Hi-Z to /RE Low tIR 0-ns /WE High to /RE Low tWHR 50-ns ParameterSymbol Min Max Unit Last /RE High to Busy(at sequential read)tRB -100ns /CE High to Ready(in case of interception by /CE at read)tCRY -50+tr(R/B)ns /CE High Hold Time(at the last serial read)(2)/g /Device resetting time(Read/Program/Erase)tRST-5/10/500(1)us/CE High Hold Time(at the last serial read)(2)tCEH100-nsNote : 1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us.2. The time to Ready depends on the value of the pull-up resistor tied R/B pin.PreliminaryConfidential17256Mbit (32Mx8Bit)NAND FLASHNAND FLASH TECHNICAL NOTESInitial Invalid Block(s)Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability isnot guaranteed by ATO. The information regarding the initial invalid block(s) is so called as the initial invalid block information.Devices with initial invalid block(s) have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s) does not affect the performance of valid block(s)because it is isolated from the bit line and the common source line by a select transistor The block(s) because it is isolated from the bit line and the common source line by a select transistor. The system design must be able to mask out the initial invalid block(s) address mapping. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit/528Byte ECC.Identifying Initial Invalid Block(s)All device locations are erased(FFh) except locations where the initial invalid block(s) information is written prior to shipping. The initial invalid block(s) status is defined by the 6th byte in the spare area. ATO makes f sure that either the 1st or 2nd page of every initial invalid block has non-FFh data at the column address of 517. Since the initial invalid block Information is also erasable in most cases, it is impossible to recover the information once it has been erased.Therefore, the system must be able to recognize the initial invalid block(s) based on the initial invalid block information and create the initial invalid block table via the following suggested flow chart(Figure3). Any intentional erasure of the Initial invalid block information is prohibited.PreliminaryConfidentialFigure 3. Flow chart to create initial invalid block table18Error in write or read operationWithin its life time, the additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the block failure rate. The following possible failure modes should be considered to implement a highly reliable system. In the case of status read failure after erase orConfidential256Mbit (32Mx8Bit)NAND FLASH Erase Flow Chart Read Flow ChartBlock Replacement* Step1. When an error happens in the nth page of the Block ‘A’ during erase or program operation.* Step2. Copy the nth page data of the Block ‘A’ in the buffer memory to the nth page of another free block (Block ‘B) * Step3. Then, copy the data in the 1st ~ (n-1)th page to the same location of the Block ‘B’* Step4. Do not further erase Block ‘A’ by creating an ‘invalid Block’ table or other appropriate scheme.ConfidentialPointer Operation of AFND5608U1ATO NAND Flash has three address pointer commands as a substitute for the two most significant column address. ‘00h’ Command sets the pointer to ‘A’ area(0~255byte), ‘01h’ command sets the pointer to ‘B’Figure 4. Block Diagram of Pointer Operation (1) Command input sequence for programming ‘A’ area(2) Command input sequence for programming ‘B’ area(3) Command input sequence for programming ‘C’ areaPreliminary Confidential256Mbit (32Mx8Bit)NAND FLASHSystem Interface Using /CE don’t-careFor an easier system interface, /CE may be inactive during the data-loading or sequential data-reading as shown below. The internal 528bytes page registers are utilized as separate buffers for thisoperation and the system design gets more flexible. In addition, for voice or audio applications whichuse slow cycle time on the order of u-seconds, de-activating /CE during the data-loading and reading would provide significant savings in power consumption.Figure 5. Program Operation with /CE don’t careFigure 6. Read Operation with /CE don’t-carePreliminary Confidential22256Mbit (32Mx8Bit)NAND FLASH * Command Latch Cycle* Address Latch CyclePreliminary Confidential23256Mbit (32Mx8Bit)NAND FLASH * Input Data Latch Cycle* Sequential Out Cycle after Read(CLE=L, /WE=H, ALE=L)Note : Transition is measured ±200mV from steady state voltage with load.This parameter is sampled and not 100% tested.Confidential256Mbit (32Mx8Bit)NAND FLASH * Status Read Cycle (During Ready State)* Status Read Cycle (During Busy State)Preliminary Confidential25256Mbit (32Mx8Bit)NAND FLASH * READ1 OPERATION (READ ONE PAGE)* READ1 Operation (Intercepted by /CE)Preliminary Confidential26256Mbit (32Mx8Bit)NAND FLASH * READ2 Operation (Read One Page)Preliminary Confidential27256Mbit (32Mx8Bit)NAND FLASH * Page Program Operation* Copy-Back Program OperationPreliminary Confidential28256Mbit (32Mx8Bit)NAND FLASH* Block Erase Operation (Erase One Block)* Read ID OperationPreliminary Confidential 2975h 75h256Mbit (32Mx8Bit)NAND FLASH ID DEFINITION TABLE90 ID : Access command =90hValue Description1st byte9Bh Maker Code2nd byte75h Device CodeDEVICE OPERATIONDEVICE OPERATIONPAGE READUpon initial device power up, the device defaults to Read1 mode. This operation is also initiated by writing 00h to the command register along with four address cycles. Once the command is latched, it does not need to be written for the following page read operation. Three types of operations are available : random read, serial page read and sequential row read. The random read mode is enabled when the page address is changed. The 528 bytes of data within the selected page are transferred to the data registers in less than changed The528bytes of data within the selected page are transferred to the data registers in less than 12us(tR). The system controller can detect the completion of this data transfer(tR) by analyzing the output of R/B pin. /CE must be held low while in busy for AFND5608U1, while /CE is don’t care with AFND5608U1. If /CE goes high before the device returns to Ready, the random read operation is interrupted and Busy returns to Ready as the defined by tCRY. Since the operation was aborted, the serial page read does not output valid data. Once the data in a page is loaded into the registers, they may be read out in 50ns cycle time bysequentially pulsing /RE, high to low transitions of the /RE clock output the data stating from the selected column address up to the last column address.The way the Read1 and Read2 commands work is like a pointer set to either the main area or the spare area.The spare area of 512 to 527 bytes may be selectively accessed by writing the Read2 command. Address A0 to A3 set the starting address of the spare area while addresses A4 to A7 are ignored. The Read1command(00h/01h) is needed to move the pointer back to the main area. Figure 7 to 10 show typicalsequence and timings for each read operation.Preliminary Confidential30256Mbit (32Mx8Bit)NAND FLASH Figure 7. Read1 OperationPreliminary Confidential31256Mbit (32Mx8Bit)NAND FLASH Figure 8. Read2 OperationPreliminary Confidential32256Mbit (32Mx8Bit)NAND FLASHPAGE PROGRAMTh d i i d b i ll b i b i d ll l i l i l i f The device is programmed basically on a page basis, but it does allow multiple partial page programming of a byte or consecutive bytes up to 528 bytes, in a single page program cycle. The number of consecutive partial page programming operation within the same page without an intervening erase operation must not exceed 2 for main array and 3 for spare array. The addressing may be done in any random order in a block. A page program cycle consists of a serial data loading period in which up to 528bytes of data may be loaded into the page register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell. Serial data loading can be started from 2nd half array by moving pointer. About the pointer operation please refer to the attached technical notes operation, please refer to the attached technical notes.The serial data loading period begins by inputting the Serial Data Input command(80h), followed by the three cycle address input and then serial data loading. The bytes other than those to be programmed do not need to be loaded. The Page Program confirm command(10h) initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the programming process. The internal write state control automatically executes the algorithms and timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command may be entered, with /RE and /CE low, to read the status register. The system controller can detect thecompletion of a program cycle by monitoring the R/B output, or the Status bit(I/O 6) of the Status Register. Only the Read Status command and Reset command are valid while programming is in progress. When the Page Program is complete, the Status Bit(I/O 0) may be checked(Figure 11). The internal program verifydetects only errors for “1” s that are not successfully programmed to “0”s. The command register remains in Read Status command mode until another valid command is written to the command register.Figure 9. Program Operation g g pBLOCK ERASEThe Erase operation is done on block(16K Bytes) basis. Block address loading is accomplished in threecycles initiated by an Erase Setup command(60h). Only address A14 to A24 is valid while A9 to A13ignored. The Erase Confirm command(D0h) following the block address loading initiates the internalerasing process. This two-step sequence of setup followed by execution command ensures thatmemory contents are not accidentally erased due to external noise conditions. At the rising edge ofPreliminary Confidential /WE after the erase confirm command input, the internal write controller handles erase and erase-verify. When the erase operation is completed, the Status Bit(I/O 0) may be checked.Figure 12 details the sequence.33256Mbit (32Mx8Bit)NAND FLASH Figure 10. Block Erase OperationCopy-Back Programpy p g p q y y p g pThe Copy-back program is provided to quickly and efficiently rewrite data stored in one page within the plane to another page within the same plane without using an external memory. Since the time-consuming sequential-reading and its reloading cycles are removed, the system performance is improved. The benefit is especially obvious when a portion of a block is updated and the rest of the block also need to be copied to the newly assigned free block. The operation for performing a copy-back program is a sequential execution of page-read without burst-reading cycle and copying-program with the address of destination page. A normal read operation with “00h” command and the address of the source page moves the whole 528bytes data into the internal buffer. As soon as the device returns to Ready state, Page-Copy data-input command(8Ah) with the address cycles of destination page followed may be written. The Program Confirm command(10h) is not needed to actually begin the programming operation. For backward-compatibility, issuing Program Confirm command during copy-back does not affect correct device operation.Copy-Back Program operation is allowed only within the same memory plane. Once the Copy-Back Program is finished, any additional partial page programming into the copied pages is prohibited before erase. Plane address must be the same between source and target page“When there is a program-failure at Copy-Back operation, error is reported by pass/fail status. But, if Copy-Back operations are accumulated over time, bit error due to charge loss is not checked by external errorBack operations are accumulated over time bit error due to charge loss is not checked by external error detection/correction scheme. For this reason, two bit error correction is recommended for the use of Copy-Back operation.”Preliminary Confidential34。

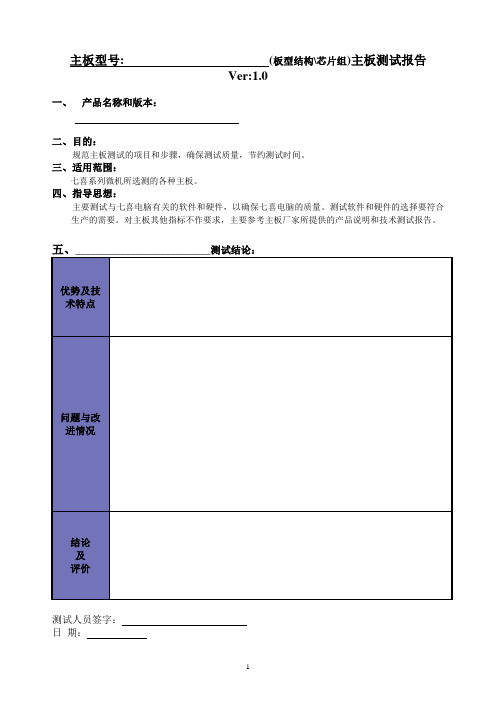

七喜研发部主板测试标准V1.0

主板型号: (板型结构\芯片组)主板测试报告Ver:1.0一、产品名称和版本:二、目的:规范主板测试的项目和步骤,确保测试质量,节约测试时间。

三、适用范围:七喜系列微机所选测的各种主板。

四、指导思想:主要测试与七喜电脑有关的软件和硬件,以确保七喜电脑的质量。

测试软件和硬件的选择要符合生产的需要。

对主板其他指标不作要求,主要参考主板厂家所提供的产品说明和技术测试报告。

___________________________测试结论:测试人员签字:日期:附:(板型结构\芯片组)主板测试数据注:1.测试前,仔细阅读红色备注。

测试后,填写报告并删除所有红色备注及附+。

如需在测试报告中添加注解,请使用蓝色字体。

2.测试中测试软件的得分仅作为参考,不作为测试是否通过的判定依据;以测试软件正常运行并取得测试分数为测试通过的判定依据。

注:1.主板芯片型号要写全,包括表示芯片版本的标识,如9903CD、SL3P7……。

在备注中注明北桥是否有散热片。

2.防火等级从高到低为5V、V-0、V-1,板上的94v-0标识等同于UL认证3.向厂家要求提供证书。

4.主要功放芯片有TL071、TL072、TL074、LM78L、AD8532……,如没有功放,填“无”。

5.请标注跳线位置、序号.6.标注集成显示卡AGP类型,速度7.测试最初版本与最终确认版本8.所支持CPU的STEPING版本9.主板上的ATX20PIN,3.3/12V 6PIN,12V 4PIN,WOL,AOL电源提供口,FAN电源及其他电源接口数量10前置Audio、USB注跳线位置11功能键、功能灯注明是几键几灯注:BIOS测试项目可根据具体情况,进行相关项目的测试。

该测试规范测试BIOS的项目仅供参考。

全部的BIOS可正常更改项目要求确认实现该项目相应完成功能。

针对不同应用范围的主板,测试通知将详细表述BIOS要求。

注:如有其它功能键、功能灯请注明,并进行相关的测试。

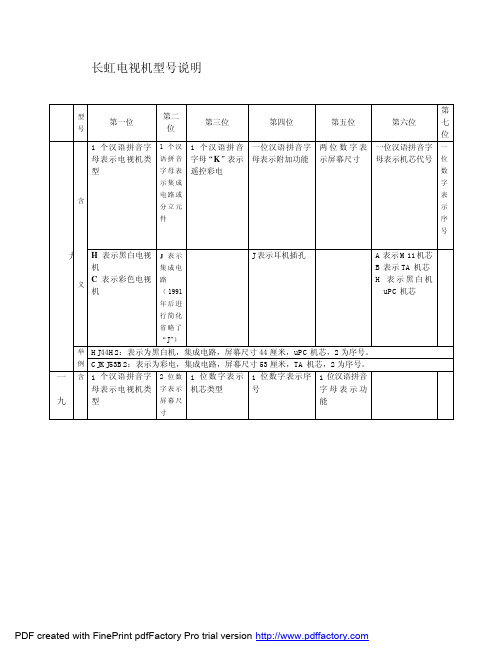

长虹电视机型号说明

型

第一位

号

第二 位

第三位

第四位

第五位

第

第六位

七

位

1 个汉语拼音字 1 个汉 1 个 汉语拼 音 一位汉语拼音字 两 位 数 字 表 一位汉语拼音字 一

母表示电视机类 语拼音 字母“K”表示 母表示附加功能 示屏幕尺寸 母表示机芯代号 位

型

字 母 表 遥控彩电

数

示集成

字

电路或

表

含

分立元

喜

始使用)

尺寸 的派生产品

PDF created with FinePrint pdfFactory Pro trial version

A 表示 A6 机芯

一

D 表示 TDA 机芯

N -6 机芯

T 表示 CN-7 及

九

H 表示黑白电视

机

二

C 表示彩色电视

机

年

后

义

1 为 NC-3 机芯 2 为单片集成

电路黑白机 3 为 NC-3 机芯 4 为 M11 机芯 5 为 A3 机芯 6 为 TA 机芯 8 为 NC-2 机芯 9 为 TDA 机芯 0 为数字机芯

同一类型电视, 造型不同用序号 区分

S 为 S 端子 P 为射频画中

一 含 1 个汉语拼音字 2 位数 1 位 数字表 示 1 位数字表示序 1 位汉语拼音

母表示电视机类 字表示 机芯类型

号

字母表示功

九

型

屏幕尺

能

寸

PDF created with FinePrint pdfFactory Pro trial version

举 D2965A:D 表示 TDA 机芯,29 表示屏幕尺寸,65 表示机壳代号,A 表示该电视是 D2965 的派生

K4S640832D资料

PIN CONFIGURATION (Top view)

VDD DQ0 VDDQ N.C DQ1 VSSQ N.C DQ2 VDDQ N.C DQ3 VSSQ N.C VDD N.C WE CAS RAS CS BA0 BA1 A10/AP A0 A1 A2 A3 VDD 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 VSS DQ7 VSSQ N.C DQ6 VDDQ N.C DQ5 VSSQ N.C DQ4 VDDQ N.C VSS N.C/RFU DQM CLK CKE N.C A11 A9 A8 A7 A6 A5 A4 VSS

CMOS SDRAM

54Pin TSOP (II) (400mil x 875mil) (0.8 mm Pin pitch)

PIN FUNCTION DESCRIPTION

Pin CLK CS Name System clock Chip select Input Function Active on the positive going edge to sample all inputs. Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQM Masks system clock to freeze operation from the next clock cycle. CKE should be enabled at least one cycle prior to new command. Disable input buffers for power down in standby. Row/column addresses are multiplexed on the same pins. Row address : RA0 ~ RA11, Column address : CA0 ~ CA8 Selects bank to be activated during row address latch time. Selects bank for read/write during column address latch time. Latches row addresses on the positive going edge of the CLK with RAS low. Enables row access & precharge. Latches column addresses on the positive going edge of the CLK with CAS low. Enables column access. Enables write operation and row precharge. Latches data in starting from CAS, WE active. Makes data output Hi-Z, tSHZ after the clock and masks the output. Blocks data input when DQM active. Data inputs/outputs are multiplexed on the same pins. Power and ground for the input buffers and the core logic. Isolated power supply and ground for the output buffers to provide improved noise immunity. This pin is recommended to be left No Connection on the device.

K9S5608V0C资料

tCH tCSTO tWHR tCHZ

RE

tDS

tDH tIR

tRSTO tRHZ

Status Output

I/O0~7

70h

tCLS

CLE

tCLS tCLH tCS

CE

tWP

WE

tCH tCEA tWHR tCHZ

RE

tDH tDS

I/O0~7 70h

tIR

tREA tRHZ

Status Output

≈

1

元器件交易网

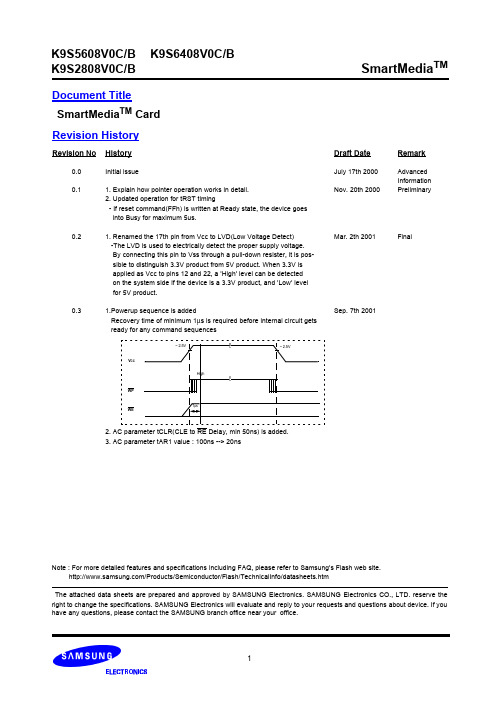

K9S5608V0C/B K9S2808V0C/B

Revision History

Revision No

0.4

K9S6408V0C/B

SmartMediaTM

History

1. Unified access timing parameter definition for multiple operating modes - Changed AC characteristics (Before) Parameter ALE to RE Delay (ID read) ALE to RE Delay (Read cycle) RE Low to Status Output CE Low to Status Output RE access time(Read ID) - AC characteristics (After) . Deleted tRSTO, tCSTO and tREADID / Added tCLR, tCEA Parameter ALE to RE Delay (ID read) ALE to RE Delay (Read cycle) CLE to RE Delay CE Access Time Symbol tAR1 tAR2 tCLR tCEA Min 50 50 10 45 Max ns Unit Symbol tAR1 tAR2 tRSTO tCSTO tREADID Min 100 100 Max 35 45 35detailed features and specifications including FAQ, please refer to Samsung Flash web site. /Products/Semiconductor/Flash/TechnicalInfo/datasheets.htm The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near your office.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

M366S3253DTS

M366S3253DTS SDRAM DIMM

PC133/PC100 Unbuffered DIMM

32Mx64 SDRAM DIMM based on 32Mx8, 4Banks, 8K Refresh, 3.3V Synchronous DRAMs with SPD GENERAL DESCRIPTION

* These pins are not used in this module. ** These pins should be NC in the system which does not support SPD.

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

PIN NAMES

Pin Name A0 ~ A12 BA0 ~ BA1 DQ0 ~ DQ63 CLK0, CLK2 CKE0 CS0, CS2 RAS CAS WE DQM0 ~ 7 VDD VSS *VREF SDA SCL SA0 ~ 2 *WP DU NC Function Address input (Multiplexed) Select bank Data input/output Clock input Clock enable input Chip select input Row address strobe Column address strobe Write enable DQM Power supply (3.3V) Ground Power supply for reference Serial data I/O Serial clock Address in EEPROM Write protection Don′t use No connection

Burst mode operation Auto & self refresh capability (8192 Cycles/64ms) LVTTL compatible inputs and outputs Single 3.3V ± 0.3V power supply MRS cycle with address key programs Latency (Access from column address) Burst length (1, 2, 4, 8 & Full page) Data scramble (Sequential & Interleave) • All inputs are sampled at the positive going edge of the system clock • Serial presence detect with EEPROM • PCB : Height (1,375mil), single sided component

FEATURE

• Performance range Part No. M366S3253DTS-L7C/C7C M366S3253DTS-L7A/C7A M366S3253DTS-L1H/C1H M366S3253DTS-L1L/C1L • • • • • Max Freq. (Speed) 133MHz (7.5ns@CL=2) 133MHz (7.5ns@CL=3) 100MHz (6.0ns@CL=2) 100MHz (6.0ns@CL=3)

REV. 0.0 Jan. 2002

元器件交易网

M366S3253DTS

PIN CONFIGURATION DESCRIPTION

Pin CLK CS Name System clock Chip select

PC133/PC100 Unbuffered DIMM

Input Function Active on the positive going edge to sample all inputs. Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQM Masks system clock to freeze operation from the next clock cycle. CKE should be enabled at least one cycle prior to new command. Disable input buffers for power down in standby. CKE should be enabled 1CLK+tSS prior to valid command. Row/column addresses are multiplexed on the same pins. Row address : RA0 ~ RA12, Column address : CA0 ~ CA9 Selects bank to be activated during row address latch time. Selects bank for read/write during column address latch time. Latches row addresses on the positive going edge of the CLK with RAS low. Enables row access & precharge. Latches column addresses on the positive going edge of the CLK with CAS low. Enables column access. Enables write operation and row precharge. Latches data in starting from CAS, WE active. Makes data output Hi-Z, tSHZ after the clock and masks the output. Blocks data input when DQM active. (Byte masking) Data inputs/outputs are multiplexed on the same pins. Power and ground for the input buffers and the core logic.

PIN CONFIGURATIONS (1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 VSS DQ0 DQ1 DQ2 DQ3 VDD DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VDD DQ14 DQ15 *CB0 *CB1 VSS NC NC VDD WE DQM0 Front Pin Front Pin Back VSS DQ32 DQ33 DQ34 DQ35 VDD DQ36 DQ37 DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VDD DQ46 DQ47 *CB4 *CB5 VSS NC NC VDD CAS DQM4 Pin 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 Back DQM5 *CS1 RAS VSS A1 A3 A5 A7 A9 BA0 A11 VDD *CLK1 A12 VSS CKE0 *CS3 DQM6 DQM7 *A13 VDD NC NC *CB6 *CB7 VSS DQ48 DQ49 Pin 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 Back DQ50 DQ51 VDD DQ52 NC *VREF NC VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VDD DQ60 DQ61 DQ62 DQ63 VSS *CLK3 NC **SA0 **SA1 **SA2 VDD 29 DQM1 57 DQ18 85 58 DQ19 86 CS0 30 59 87 VDD 31 DU 60 DQ20 88 32 VSS 61 89 NC 33 A0 62 *VREF 90 34 A2 63 *CKE1 91 35 A4 64 92 VSS 36 A6 65 DQ21 93 37 A8 38 A10/AP 66 DQ22 94 67 DQ23 95 39 BA1 68 96 VSS 40 VDD 69 DQ24 97 41 VDD 42 CLK0 70 DQ25 98 71 DQ26 99 43 VSS 72 DQ27 100 44 DU 73 45 CS2 VDD 101 46 DQM2 74 DQ28 102 47 DQM3 75 DQ29 103 76 DQ30 104 48 DU 77 DQ31 105 49 VDD 78 50 VSS 106 NC 79 CLK2 107 51 NC NC 108 52 *CB2 80 53 *CB3 81 *WP 109 82 **SDA 110 54 VSS 55 DQ16 83 **SCL 111 VDD 112 56 DQ17 84