781000中文资料

10408;10409;中文规格书,Datasheet资料

Made in AmericaThe two most important characteristics for successful applicationConductive Acrylic Paint applications are:1. The surface must be clean, dry, dull, and smooth. Heavy dirt or grease build-up should be removed with a stripper or degreaser. Cleaning methods range from: sweeping, vacuuming, wire brush, air-blasting, water jet, steam cleaning, or stripping.2. If the surface is concrete, it must be in good condition.New concrete should cure for a minimum of 28 days beforeConductive Acrylic Paint. Not all concrete is created equal -- concrete surfaces vary widely in physical and chemical qualities due to the way the concrete was formulated,There are several methods to prepare problem concrete. Each method depends on the condition of the concrete. Adhesion properties can be increased by profiling or roughing the surface through acid etching, rotary drum sanding, scarifying, or mechanically scratching the surface.You must test for moisture in the concrete. If moisture is present, the floor should not be coated until the source of the moisture isConductive Acrylic Paint bonds well to clean, dry concrete. However, a standard industrial primer can be used on certain difficult to bond substrates and enhance the adhesion of Conductive Acrylic Paint.PREVIOUSLY PAINTED SURFACES:The surface should be clean and free of dust, grease, wax, and soap residue. Wash with ordinary detergent and water. Rinse thoroughly with clean water and let dry. Glossy surfaces can be dulled by lightly sanding and then vacuuming and cleaning. Cracks and holes should be repaired before applying the Statguard Conductive Acrylic Paint. Adhesion can be improved by using atest area be coated to ensure that the adhesion and electrical of the paint is acceptable. (See Adhesion Testing, Figure 5.) If the 3. Saturate a 1/4” (6.35 mm) fine nap roller or an industrial brush ure must be above 50°F (10°C).Conductive Acrylic Paint is recommended for appropriate static protection.Mix any settled solids to produce a uniform grey color.Saturate a 1/4” fine nap roller with paint, remove excess paint and trapped bine separate cans into a larger A minimum number of strokes from the applicator is recommended.Figure 2. Paint application with roller.Figure 3. Spray paint application Clean UpWash applicators with water immediately after painting. Remove paint spills promptly with a wet cloth. Close container after each use. Keep container from freezing.Drying TimeIt is recommended that Statguard ® Conductive Acrylic Paint be allowed to dry at a temperature in excess of 45°F (7°C) until dry. A minimum of 1 to 2 hours drying time should be allowed before applying the second coat. The finish can be applied after 48-72 hours or until the last coat of paint is cured. Wait a minimum of 12 hours drying time after the last coat before allowing light traffic on the coated area. At high humidity levels, a longer drying time may be necessary. Do not force dry.MaintenanceUse sweeper, vacuum, or broom to remove dirt. Allow two weeks drying time before using a damp mop to clean the coated area. Do not use abrasive cleaners, floor rinse, or scrubbing machine to clean the floor.Finish/SealerDesco Statguard Conductive Acrylic Paint can be overcoated or sealed with Statguard Floor Finish static dissipative coating to increase durability, enhance shine, improve ease of maintenance, and seal out dirt and debris. Desco Statguard ® Conductive Light Grey Acrylic Paint needs the Statguard ® Floor Finish for gloss and ease of maintenance . Statguard ® is a polymer base floor finish/sealer that can be used as a top coat on the Conductive Acrylic Paint. Surface resistivity will then be in the 10E6-10E7 ohms range. Two coats are recommended. Three coats will improve electrical properties, durability and reduce frequency ofLead free, iron oxide, titanium dioxide and extenders 10.27 lbs per gallon (1.0 kilograms per Use a razor to cut into a painted, dried floor.3.Pull the tape off.Apply tape on the precut area.4.Examine the degree of paint separationfrom the concrete.Figure 5. Adhesion test on the painted floor.10E5 ohms/sq. per ASTM D257Static Charge Decay:<0.01 sec. per FTMS 101B, Method 4046Charge Generation:Zero per AATCC Step Test, Method 134-1979RTT:10E5 ohms per ANSI ESD-S7.1RTG:10E5 ohms per ANSI ESD-S7.1TestingTest patch areas should be tested for adhesion and electricalperformance of the paint before applying paint to the entire floor. To best ensure consistent results, the test should be done at various locations.ELECTRICAL PROPERTIES:Test the surface resistivity, point-to-point resistance, and resistance-to-ground properties of coated area per ANSI ESD-S7.1 test method. For quick and easy verification of the paint’s electrical properties, we recommend the use of our a Surface Resistance Test Kit (Figure 4). For more information contact any of the Desco Industries Inc. companies.ADHESION:Allow newly applied paint to dry a minimum of 48 hours before proceeding with the test. At humidity levels over 55% RH, allow 72 hours of drying time before testing. Use a razor to cut a cross or a few perpendicular lines over a 3” by 3” (75 mm by 75 mm) area on several spots of the thoroughly dried area. Use a piece of masking tape to cover the marked area. Make sure the tape is thoroughly adhered to the test area. Pull the tape off the surface and examine the amount of paint which has peeled off during the test. If any significant portion is transferred to the tape, better surface preparation (acid etching, cleaning or sanding) should be done on the substrate to enhance the adhesion.8. EXPOSURE CONTROL/PERSONAL EXPOSUREControl Parameters TLV-value 50 ppm maximum for n-butanol and 25 ppm for Ethylene GlycolMonobutyl EtherOther Regulations NoneMeasures For Technical Control Preferences of technical measure to prevent or control contact with the product.Isolating process and personnel, mechanical ventilation (dilution and localexhaust) and the regulation of process conditions. In case of non-prevention or non-control, a proper protective wearing should be used. Respiratory Protection Not required. Wear MSHA/NIOSH approved respirator where exposure limits areexceeded.Hand Protection Impervious/Neoprene GlovesEye Protection Chemical Splash Goggles (ANSI Z-87.1)Work/Hygienic Practices Wash hands before eating, smoking, or using washroom facilities9. PHYSICAL AND CHEMICAL PROPERTIESForm FluidColor Grey, OpaqueSmell MildpH 8.5Boiling Point at °C >100-101°C (212-214°F)Freezing Point at °C 0.0°C (32.0 °F)Flash Point at °C 65 °CExplosive Limits LEL: 0.8 UEL: 25.0Inflammability Limits N/A(vol.% in air)Solubility in water CompleteVOC per method 24 of EPA 2.3 -2.5 lbs VOC/ galVapor Pressure (mmHg) 92.43 mm @ 20 °CVapor Density (air=1) Heavier than airDensity at 20°C 8.17 lbs./gal or 1.14 g/cm3Specific Gravity (H20=1) 1.21Inflammability Classification according to OSHA and EC-regulations “non-flammable”Ignition Temperature 240.0 °CEvaporation Rate Slower than n-butyl acetate% Volatile by Volume 13.229%10. STABILITY AND REACTIVITYStability/Reactivity Stable product at normal conditionsConditions to avoid Temperatures above 49°C/120°F and below 1°C/34°F, Open flames and sparks. Materials to avoid Strong Oxidizing agents and alkalies.Hazardous Decomposition Oxides of carbon and nitrogen. If involved in fire (from other sources) could conceivably result in release of Carbon Dioxide and Carbon Monoxide fumes.11. TOXICOLOGICAL INFORMATIONIngredient-Material Description PEL TLV (twa) LD50 (mg/kg) LC50 (ppm)mg/m3 ppm (rat) (rbt) (rat)oral dermal inhalEthylene Glycol Monobutyl Ether * 50.0 0.0 25.0 470.0 220.0 0.0Butanol* 50.0 0.0 50.0 0.0 0.0 0.0Mineral Spirits 100.00 0.0 100.0 0.0 0.0 0.02-(2-Butoxyethoxy)ethanol 0.0 0.0 0.0 6560.0 4120.0 0.02-ethyl-1-Hexanol 0.0 0.0 0.0 3730 1970 0.0Ammonium Hydroxide 0.0 35.0 50.0 350.0 0.0 0.0*Listed Chemical Subject To Reporting Requirement of SARA Section 313 of Title III• Acute toxicity• Primary irritant effect:• On the skin: No irritant effect• On the eye: No irritant effect• Sensatization: No sensitizing effects known• Additional toxicological information:The product in not classified according to the calculation method of the General EU Classification guideline for Preparations as issued in the latest version. When used and handled according to specifications, the product does not have any harmful effects to our experience and the information provided to us.12. ECOLOGICAL INFORMATIONGeneral Notes:Water hazard class 1 (German Regulations) (self-assessment): slightly hazardous for water. Do not allow undiluted product or large quantities of it to reach ground water, water course or sewage system.Mobility The product is aqueous and will be separated in aqueous conditions Degradability N/ABioaccumulation Not likelyEcotoxicity None knownReference to BimSchV N/A13. DISPOSAL CONSIDERATIONSProduct Dike and collect material into plastic container. Water rinse and drain, flush smallamounts. Use sanitary landfill d isposal. Follow state and local regulations(RCRA; Subtitle D).Hazardous Waste Number Nonregulated14. TRANSPORT INFORMATIONThis product is not classified for transport under ADR/IMDG regulations.15. REGULATORY INFORMATIONLabeling according To EU guideline: Observe the general safety regulations when handeling chemicals. The product is not subject to identification regulations under EU Directives and the Ordinance on Hazardous Materials (Genman GefStoffV).National Regualtions:Waterhazard class: Water hazard class 1 (Self-assessment): slightly hazard for waterPhysical/Chemical Indication Non-flammableSafety Phrase (S2): keep away from children, (S7): keep containers well closed, (S24/25): avoidcontact with skin and eyes, (S45): in case of accident or if you feel unwell, seekmedical advice immediately, show label where possible, (S53): avoid exposureobtain special instruction before use, (S62): if swallowed, do not induce vomiting;seek medical advice immediately and show this container or label.EU Classification This product does not have to be classified according to the EU Regulations.(67/548/EEC-88/379/EEC)EINECS Status All components are included in the EINECS Inventories except cas #104-76-7 TSCA All ingredients of this product are listed or are excluded from the listing on the U.S. Toxic Substance Control Act (TSCA) Chemical Substance inventory.16. OTHER INFORMATIONFurther Information None KnownDisclaimerThe information given in this publication has been worked up to the best of the knowledge of Desco Industries Inc, as well as taking into consideration the applicable laws and regulations. We cannot anticipate all conditions under which this information and our products or the products of the manufacturers in combination with our products may be used. We accept no responsibility for the results obtained by the application information or the safety and suitability of our product or product combination with other products. Users are advised to make their own tests to determine the safety and suitability of each such product or product combination for their own purposes. Unless otherwise agreed in writing, we sell the products without warranty, and buyers end users assume responsibility and liability for loss or damage arising from the handling and use of our products, whether used alone or in combination with other products.分销商库存信息:DESCO1040810409。

资料(中文)

概述TC1002 是一个高性能细分步进马达控制器。

它包含一个模拟SINE/COSINE信号发生器,完整的数字控制集成在一颗IC中,高集成度减少产品的设计周期。

尽量的减少了外部的分立元件,提供给设计者一个简单但又高效的产品。

在一个完整的细分控制系统上,TC1002全面的控制马达运行状况,14种细分等级,它能在任何时候改变马达状态,没有必要要复位控制器。

它很容易使马达前进使用者设定的固定步数。

另外在“整步”输出上,当马达长时间工作后,它会指出马达是否还处于整步状态上。

TC1002通过输入时钟和方向两种信号就可控制马达,并可以工作在离散状态下。

芯片采用QFP44封装。

特点¾44引脚QFP封装¾高达10MHz时钟¾内部集成模拟SINE/COSINE发生器,DAC¾PWM电流控制,可自动减少电流¾14种细分选择,细分数的改变不会中断马达的运行¾Standalone or Buss 模式¾5V电源供电¾过流保护¾过温保护¾错误输出¾整步输出¾消除共振结构图引脚分布图TC1002引脚分布图引脚描述44脚 名称 引脚功能37 SCLK 阶跃时钟输入。

一个正边沿能够使电机前进一个增量。

36 RESET 当RESET脚为低时,这一输入会复位芯片。

当重新释放时,控制器会在它的初始状态(OUTA为0,OUTB为峰值)38 DIR 方向输入。

这一输入用来改变电机的方向。

物理位置也和电机线圈连接有关。

12 CSEL 时钟选择输入。

为低时,内部的正弦余弦发生器作为SCLK输入且不依赖于EN输入电平。

为高时,当EN输入为低时,COUT输出将作为SCLK输入,相反地,当EN输入为高时,内部的正弦余弦发生器将作为SCLK信号。

10 RSEL ROM选择脚,为低选择SIN/COS发生器,为高选择外部查找表39 EN 使能输入。

78172中文资料

SPECIFICATIONSFEATURES AND SPECIFICATIONSMolex's new 1.20mm pitch Pico-EZmate™connectors are compact and low profile, with a mated height of 1.40mm for wire-to-board applications.The Pico-EZmate connector design includes secure locking features between the receptacle housing and the PCB header, with an audible click to ensure mating integrity. The receptacle is mated vertically with the header, which allows excellent workability in production lines.The header design also provides sufficient space to allow stable pick-and-place operations in SMT lines. The headers are packed in the embossed tape packing for automatic insertion equipment.Both header and receptacle housings are made from a halogen-free resin with a 94 V-0 rated material. The series also complies to European RoHS directives.•Ultra low profile •Space savings•Easy vertical mating •Excellent workability in production line •Multiple mating cycles •Allows multiple testing cycles •Assembly suction space on header •Stable pick-and-place area •RoHS & halogen free compliance•Environmentally friendlyReference Information Packaging:Embossed Tape UL File No.: TBD CSA File No.: TBD Designed In:mmElectrical Voltage:50V Current:1.5AApplicable wire range: AWG #28 to #30UL3302Contact Resistance:20 milliohms max. Dielectric Withstanding Voltage: 500V AC Insulation Resistance: 100 Megohms minimumPhysicalHousing: LCP, UL94V-0, Black Contact: Copper alloy Plating: GoldOperating Temperature:-25°C to +85°C1.20mm (.047”) Pitch Pico-EZmate™W-to-B Connectors Series 78171Header78172-Receptacle housing-TerminalNotebookMobile PhoneGPSMP3, MP4Any compact mobile device application Ordering InformationAmericas Headquarters 2222 Wellington Ct. Lisle, Illinois 60532 USA 1-800-78MOLEX amerinfo@ Asia Pacific NorthHeadquartersYamato, Kanagawa, Japan81-462-65-2324feninfo@Asia Pacific SouthHeadquartersJurong, Singapore65-6-268-6868fesinfo@European HeadquartersMunich, Germany49-89-413092-0eurinfo@Corporate Headquarters2222 Wellington Ct.Lisle, Illinois 60532 USA630-969-4550Visit our Web site at Markets and ApplicationsOrder No. : 9876501961©2008, Molex1.20mm (.047”) PitchPico-EZmate™W-to-BConnectorsSeries78171Header78172-Receptacle housing-TerminalOrder No.Circuits78171-1002278171-1003378171-1004478171-10055PCB HeaderOrder No.Circuits78172-0002278172-0003378172-0004478172-00055Receptacle HousingReceptacle Crimp TerminalOrder No.Circuits78172-0410N/A。

trf7960

1Introduction1.1Features1.2APPLICATIONS1.3DescriptionTRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFID ANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008–Standby 120µA•Completely Integrated Protocol Handling–Active (Rx only)10mA•Separate Internal High-PSRR Power Supplies •Parallel 8-Bit or Serial 4-Pin SPI Interface With for Analog,Digital,and PA Sections Provide MCU Using 12-Byte FIFONoise Isolation for Superior Read Range and Reliability•Ultrasmall 32-Pin QFN Package (5mm ×5mm)•Dual Receiver Inputs With AM and PM•Available ToolsDemodulation to Minimize Communication –Reference Design/EVM With Development HolesSoftware•Receiver AM and PM RSSI–Source Code Available for MSP430•Reader-to-Reader Anti-Collision•High Integration Reduces Total BOM and Board Area•Secure Access Control –Single External 13.56-MHz Crystal Oscillator•Product Authentication –MCU-Selectable Clock-Frequency Output of –Printer Ink Cartridges RF,RF/2,or RF/4–Blood Glucose Monitors –Adjustable 20-mA,High-PSRR LDO for •Contactless Payment Systems Powering External MCU•Medical Systems•Easy to Use With High Flexibility–Auto-Configured Default Modes for Each Supported ISO Protocol–12User-Programmable Registers The TRF7960/61is an integrated analog front –Selectable Receiver Gain and AGC end and data-framing system for a 13.56-MHz –Programmable Output Power RFID reader system.Built-in programming (100mW or 200mW)options make it suitable for a wide range of –Adjustable ASK Modulation Range applications for proximity and vicinity RFID (8%to 30%)systems.–Built-In Receiver Band-Pass Filter With User-Selectable Corner FrequenciesThe reader is configured by selecting the •Wide Operating Voltage Range of 2.7V to 5.5V desired protocol in the control registers.Direct •Ultralow-Power Modes access to all control registers allows fine tuning –Power Down <1µAof various reader parameters as needed.Table 1-1.PRODUCT SELECTION TABLEPROTOCOLSDEVICEISO14443A/BISO15693Tag-it™ISO18000-3106kbps212kbps424kbps848kbpsTRF7960√√√√√√TRF7961√√Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.Tag-it is a trademark of Texas Instruments Incorporated.PRODUCTION DATA information is current as of publication date.Copyright ©2006–2008,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.ContentsTRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 20084.4.1Application Schematic for the TRF7960EVM1Introduction ...............................................(Parallel Mode).......................................1.1Features ..............................................4.4.2ApplicationSchematicfortheTRF7961EVM(SPI1.2APPLICATIONS......................................Mode).................................................1.3Description (5)System Description ....................................2Description (continued)................................ 5.1Power Supplies .. (3)Physical Characteristics ............................... 5.2Receiver –Analog Section ..........................3.1Terminal Functions ................................... 5.3Register Descriptions ................................3.1PACKAGING/ORDERING INFORMATION..........5.4Direct Commands From MCU to Reader...........4ELECTRICAL SPECIFICATIONS ...................... 5.5Reader Communication Interface ...................4.1ABSOLUTE MAXIMUM RATINGS ................... 5.6Parallel Interface Communication ...................4.2DISSIPATION RATINGS TABLE .................... 5.7Serial Interface Communication .....................4.3RECOMMENDED OPERATING CONDITIONS ...... 5.8External Power Amplifier Application ................4.4ELECTRICAL CHARACTERISTICS .................2Contents Submit Documentation Feedback2Description (continued)TRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFID ANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008Figure 2-1.Typical ApplicationA parallel or serial interface can be used for communication between the MCU and reader.When hardware encoders and decoders are used (accelerators for different standards),transmit and receive functions use a 12-byte FIFO register.For direct transmit or receive functions,the encoders/decoders can be bypassed so the MCU can process the data in real time.The transmitter has selectable output-power levels of 100mW (20dBm)or 200mW (23dBm)into a 50-Ωload (at 5-V supply)and is capable of ASK or OOK modulation.Integrated voltage regulators ensure power-supply noise rejection for the complete reader system.Data transmission comprises low-level encoding for ISO15693,modified Miller for ISO14443-A,high-bit-rate systems and Tag-it coding systems.Included with the data encoding is automatic generation of SOF,EOF,CRC,and/or parity bits.The receiver system enables AM and PM demodulation using a dual-input architecture.The receiver also includes an automatic gain control option and selectable gain.Also included is a selectable bandwidth to cover a broad range of input subcarrier signal options.The received signal strength for AM and PM modulation is accessible via the RSSI register.The receiver output is selectable among a digitized subcarrier signal and any of ten integrated subcarrier decoders (two for ISO15693low bit rate,two for ISO15693high bit rate,two for ISO14443,three for ISO14443high bit rates and one for Tag-it systems).Selected decoders also deliver bit stream and a data clock as outputs.The receiver system also includes a framing system.This system performs the CRC and/or parity check,removes the EOF and SOF settings,and organizes the data in bytes.Framed data is then accessible to the MCU via a 12-byte FIFO register and MCU interface.The framing supports ISO14443and ISO15693protocols.The TRF7960/61supports data communication levels from 1.8V to 5.5V for the MCU I/O interface while also providing a data synchronization clock.An auxiliary 20-mA regulator (pin 32)is available for additional system circuits.Submit Documentation Feedback Description (continued)33Physical Characteristics3.1Terminal Functions242322212019181723456781109116151413123231302928272625TRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008Figure 3-1.TRF796x Pin Assignments (Top View)Table 3-1.Terminal FunctionsTERMINAL TYPE (1)DESCRIPTIONNAME NO.Also can be configured to provide the received analog signal output (ANA_OUT)ASK/OOK 12BID Direct mode,selection between ASK and OOK modulation (0=ASK,1=OOK)BAND_GAP 11OUT Band-gap voltage (1.6V);internal analog voltage reference;must be ac-bypassed to ground.DATA_CLK 26INP Clock input for MCU communication (parallel and serial)EN 28INP Chip enable input (If EN =0,then chip is in power-down mode).Pulse enable and selection of power down mode.If EN2is connected to VIN,then VDD_X is EN225INP active during power down to support the MCU.Pin can also be used for pulse wake-up from power-down mode.I/O_017BID I/O pin for parallel communication I/O_118BID I/O pin for parallel communication I/O_219BID I/O pin for parallel communication I/O_320BID I/O pin for parallel communication I/O_421BID I/O pin for parallel communication I/O pin for parallel communication I/O_522BIDStrobe out clock for serial communication Data clock output in direct mode I/O pin for parallel communicationI/O_623BIDMISO for serial communication (SPI)Serial bit data output in direct mode 1or subcarrier signal in direct mode 0I/O pin for parallel communication.I/O_724BID MOSI for serial communication (SPI)IRQ 13OUT Interrupt requestMOD 14INPDirect mode,external modulation input(1)SUP =Supply,INP =Input,BID =Bi-directional,OUT =OutputPhysical Characteristics4Submit Documentation Feedback3.1PACKAGING/ORDERING INFORMATION(1)TRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEM SLOU186E–AUGUST2006–REVISED JULY2008Table3-1.Terminal Functions(continued)TERMINALTYPE(1)DESCRIPTIONNAME NO.OSC_IN31INP Crystal oscillator inputOSC_OUT30OUT Crystal oscillator outputRX1_IN18INP RX input,used for AM receptionRX2_IN29INP RX input,used for PM receptionClock for MCU(3.39/6.78/13.56MHz)at EN=1and EN2=don't careSYS_CLK27OUTIf EN=0and EN2=1,then system clock is set to60kHzTX_OUT5OUT RF output(selectable output power,100mW at8Ωor200mW at4Ω,with VDD=5V)VDD_A1OUT Internal regulated supply(2.7V–3.4V)for analog circuitrySupply for I/O communications(1.8V–5.5V).Should be connected to VIN for5-VVDD_I/O16SUPcommunication,VDD_X for3.3-V communication,or any other voltage from1.8V to5.5V.VDD_PA4INP Supply for PA;normally connected externally to VDD_RF(pin3)VDD_RF3OUT Internal regulated supply(2.7V–5V),normally connected to VDD_PA(pin4)VDD_X32OUT Internally regulated supply(2.7V–3.4V)for external circuitry(MCU)VIN2SUP External supply input to chip(2.7V–5.5V)VSS10SUP Chip substrate groundVSS_A15SUP Negative supply for internal analog circuits;normally connected to circuit groundVSS_D29SUP Negative supply for internal digital circuits;normally connected to circuit groundVSS_PA6SUP Negative supply for PA;normally connected to circuit groundVSS_RX7SUP Negative supply for RX inputs;normally connected to circuit groundPACKAGED DEVICES PACKAGE TYPE(2)TRANSPORT MEDIA QUANTITY TRF7960RHBT Tape and reel250RHB-32TRF7960RHBR Tape and reel3000TRF7961RHBT Tape and reel250RHB-32TRF7961RHBR Tape and reel3000(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIWeb site at .(2)Package drawings,standard packing quantities,thermal data,symbolization,and PCB design guidelines are available at/sc/package.Submit Documentation Feedback Physical Characteristics54ELECTRICAL SPECIFICATIONS4.1ABSOLUTE MAXIMUM RATINGS4.2DISSIPATION RATINGS TABLE4.3RECOMMENDED OPERATING CONDITIONSTRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008over operating free-air temperature range (unless otherwise noted)(1)VALUEUNIT VIN Supply voltage 6V I OOutput current150mA Continuous power dissipationSee Dissipation Ratings TableMaximum junction temperature,any condition (2)140°C T J Maximum junction temperature,continuous operation,long-term reliability (2)125°C T stgStorage temperature range–55to 150°C Lead temperature 1,6mm (1/16inch)from case for 10seconds300°C HBM (human body model)2kV ESDS ratingCDM (charged device model)500VMM (machine model)200(1)The absolute maximum ratings under any condition is limited by the constraints of the silicon process.Stresses above these ratings may cause permanent damage.Exposure to absolute maximum conditions for extended periods may degrade device reliability.These are stress ratings only and functional operation of the device at these or any other conditions beyond those specified are not implied.(2)The maximum junction temperature for continuous operation is limited by package constraints.Operation above this temperature may result in reduced reliability and/or lifetime of the device.POWER RATING (2)θJC θJA (1)PACKAGE (°C/W)(°C/W)T A ≤25°C T A =85°C RHB (32)3136.42.7W1.1W(1)This data was taken using the JEDEC standard high-K test PCB.(2)Power rating is determined with a junction temperature of 125°C.This is the point where distortion starts to increase substantially.Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and long-term reliability.over operating free-air temperature range (unless otherwise noted)MINTYP MAX UNIT VIN Supply voltage2.75 5.5V T J Operating virtual junction temperature range –40125°C T AOperating ambient temperature range –4025110°C Load impedance at TX OUT (pin 5)10ΩELECTRICAL SPECIFICATIONS 6Submit Documentation Feedback4.4ELECTRICAL CHARACTERISTICSTRF7960,TRF7961 MULTI-STANDARD FULLY INTEGRATED13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEM SLOU186E–AUGUST2006–REVISED JULY2008over temperature range V S=5V(unless otherwise noted)TYP–40°CPARAMETER CONDITIONS MIN/25°C TO UNITMAX110°CI PD Supply current in power-down mode All systems disabled,including supply-voltage regulators110µA MAXThe reference voltage generator and the VDD_X remainI PD2Supply current in power-down mode2120300µA MAXactive to support external circuitry.Oscillator running,supply-voltage regulators inI STBY Supply current in standby mode 1.54mA MAXlow-consumption modeSupply current without antenna driver Oscillator,regulators,Rx and AGC,are all active.Tx isI ON11016mA MAXcurrent off.Supply current with antenna driver Oscillator,regulators,Rx,AGC,and Tx are all active.I ON270mA MAXcurrent Pout=100mW.Supply current with antenna driver Oscillator,regulators,Rx,AGC,and Tx are all active.I ON3120mA MAXcurrent Pout=200mW.1.4MINBG Band Gap voltage Internal analog reference voltage 1.6V1.7MAX1.4MINV POR Power on reset voltage(POR)2V2.5MAX3.1MINV DD_A Regulated supply for analog circuitry 3.5V3.8MAX4MINV DD_RF Regulated supply for RF circuitry Regulator set for5-V system with250-mV difference. 4.6V5.2MAX3.1MINV DD_X Regulated supply for external circuitry 3.4V3.8MAXThe difference between the external supply and theRejection of external supply noise onP PSRR regulated voltage is higher than250mV.Measured at2620dB MIN the supply VDD_RF regulator212kHz.Half-power mode812ΩMAXR RFOUT ANT driver output resistanceFul-power mode46ΩMAXRX1_IN1and RX2_IN2input5MINR RFIN10kΩresistance20MAXV RFIN Maximum input voltage At RX1_IN1and RX2_IN2inputs 3.5V PP MAXf SUBCARRIER=424kHz 1.2 2.5mV PP MAXV SENS Input sensitivityf SUBCARRIER=848kHz 1.23mV PP MAXt SET_PD Set up time after power down1020ms MAXt SET_STBY Set up time after standby mode30100µs MAXRecovery time after modulationt REC Modulation signal:sine,424-kHz,10-mVpp60µs MAX (ISO14443)30MINf SYS CLK SYS_CLK frequency In PD2mode EN=0and EN2=160kHz120MAX CLK MAX Maximum CLK frequency20MHz MAXV IL Input logic low0.20.2VDD_I/O MAXV IH Input logic high0.8VDD_I/O MINR OUT Output resistance I/O_0to I/O_7low_io=H for VDD_I/O<2.7V400800ΩMAXR SYS CLK Output resistance SYS_CLK low_io=H for VDD_I/O<2.7V200400ΩMAX Submit Documentation Feedback ELECTRICAL SPECIFICATIONS74.4.1Application Schematic for the TRF7960EVM (ParallelMode)50 R +j xTRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008ELECTRICAL SPECIFICATIONS8Submit Documentation Feedback4.4.2Application Schematic for the TRF7961EVM (SPIMode)50 R +j xTRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFID ANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008Submit Documentation FeedbackELECTRICAL SPECIFICATIONS 95System Description5.1Power Supplies5.1.1Negative Supply Connections5.1.2Digital I/O InterfaceTRF7960,TRF7961MULTI-STANDARD FULLY INTEGRATED 13.56-MHZ RFIDANALOG FRONT END AND DATA-FRAMING READER SYSTEMSLOU186E–AUGUST 2006–REVISED JULY 2008The positive supply pin,VIN (pin 2)has an input voltage range of 2.7V to 5.5V.The positive supply input sources three internal regulators with output voltages V DD_RF ,V DD_A and V DD_X that use external bypass capacitors for supply noise filtering.These regulators provide enhanced PSRR for the RFID reader system.The regulators are not independent and have common control bits for output voltage setting.The regulators can be configured to operate in either automatic or manual mode.The automatic regulator setting mode ensures an optimal compromise between PSRR and the highest possible supply voltage for RF output (to ensure maximum RF power output).Whereas,the manual mode allows the user to manually configure the regulator settings.V DD_RFThe regulator V DD_RF (pin 3)is used to source the RF output stage.The voltage regulator can be set for either 5-V or 3-V operation.When configured for the 5-V operation range,the output voltage can be set from 4.3V to 5V in 100-mV steps.The current sourcing capability for 5-V operation is 150mA maximum over the adjusted output voltage range.When configured for 3-V operation,the output can be set from 2.7V to 3.4V,also in 100-mV steps.The current sourcing capability for 3-V operation is 100mA maximum over the adjusted output voltage range.V DD_ARegulator V DD_A (pin 1)supplies voltage to analog circuits within the reader chip.The voltage setting is divided in two ranges.When configured for 5-V operation,the output voltage is fixed at 3.5V.When configured for 3-V operation,the output can be set from 2.7V to 3.4V in 100-mV steps.Note that when configured,both V DD_A and V DD_X regulators are configured together (their settings are not independent).V DD_XRegulator V DD_X (pin 32)can be used to source the digital I/O of the reader chip together with other external system components.When configured for 5-V operation,the output voltage is fixed at 3.4V.When configured for 3-V operation,the output voltage can be set from 2.7to 3.4V in 100-mV steps.The total current sourcing capability of the V DD_X regulator is 20mA maximum over the adjusted output range.Note that when configured,both V DD_A and V DD_X regulators are configured together (their settings are not independent).V DD_PAThe V DD_PA pin (pin 4)is the positive supply pin for the RF output stage and is externally connected to the regulator output V DD_RF (pin 3).The negative supply connections are all externally connected together (to GND).The substrate connection is V SS (pin 10),the analog negative supply is V SS_A (pin 15),the logic negative supply is V SS_D (pin 29),the RF output stage negative supply is V SS_TX (pin 6),and the negative supply for the RF receiver input is V SS_RX (pin 7).To allow compatible I/O signal levels,the TRF7960/61has a separate supply input V DD_I/O (pin 16),with an input voltage range of 1.8V to 5.5V.This pin is used to supply the I/O interface pins (I/O_0to I/O_7),IRQ,SYS_CLK,and DATA_CLK pins of the reader.In typical applications,V DD_I/O is connected directly to V DD_X to ensure that the I/O signal levels of the MCU are the same as the internal logic levels of the reader.System Description 10Submit Documentation Feedback5.1.3Supply Regulator ConfigurationThe supply regulators can be automatically or manually configured by the control bits.The available options are shown in Table5-1through Table5-4.Table5-1shows a5-V system and the manual-mode regulator settings.Table5-2shows manual mode for selection of a3-V system.Table5-3and Table5-4 show the automatic-mode gain settings for5-V and3-V systems.The automatic mode is the default configuration.In automatic mode,the regulators are automatically set every time the system is activated by asserting the EN input HIGH.The internal regulators are also automatically reconfigured every time the automatic regulator selection bit is set HIGH(on the rising edge).The user can re-run the automatic mode setting from a state in which the automatic setting bit is already high by changing the automatic setting bit from high to low to high.The regulator-configuration algorithm adjusts the regulator outputs250mV below the V IN level,but not higher than5V for V DD_RF,3.5V for V DD_A,and3.4V for V DD_X.This ensures the highest possible supply voltage for the RF output stage while maintaining an adequate PSRR(power supply rejection ratio).As an example,the user can improve the PSRR if there is a noisy supply voltage from V DD_X by increasing the target voltage difference across the V DD_X regulator as shown for automatic regulator settings in Table5-3and Table5-4.Table5-1.Supply-Regulator Setting–Manual–5-V System Byte Option Bits Setting in Control Register ActionAddress B7B6B5B4B3B2B1B00015-V system0B0Manual regulator setting0B0111V DD_RF=5V,V DD_A=3.5V,and V DD_X=3.4V0B0110V DD_RF=4.9V,V DD_A=3.5V,and V DD_X=3.4V0B0101V DD_RF=4.8V,V DD_A=3.5V,and V DD_X=3.4V0B0100V DD_RF=4.7V,V DD_A=3.5V,and V DD_X=3.4V0B0011V DD_RF=4.6V,V DD_A=3.5V,and V DD_X=3.4V0B0010V DD_RF=4.5V,V DD_A=3.5V,and V DD_X=3.4V0B0001V DD_RF=4.4V,V DD_A=3.5V,and V DD_X=3.4V0B0000V DD_RF=4.3V,V DD_A=3.5V,and V DD_X=3.4VTable5-2.Supply-Regulator Setting–Manual–3-V System Byte Option Bits Setting in Control Register ActionAddress B7B6B5B4B3B2B1B00003V system0B0Manual regulator setting0B0111V DD_RF=3.4V,V DD_A,and V DD_X=3.4V0B0110V DD_RF=3.3V,V DD_A,and V DD_X=3.3V0B0101V DD_RF=3.2V,V DD_A,and V DD_X=3.2V0B0100V DD_R F=3.1V,V DD_A,and V DD_X=3.1V0B0011V DD_RF=3.0V,V DD_A,and V DD_X=3.0V0B0010V DD_RF=2.9V,V DD_A,and V DD_X=2.9V0B0001V DD_RF=2.8V,V DD_A,and V DD_X=2.8V0B0000V DD_RF=2.7V,V DD_A,and V DD_X=2.7VTable5-3.Supply-Regulator Setting–Automatic–5-V System Byte Option Bits Setting in Control Register ActionAddress B7B6B5B4B3B2(1)B1B00015-V system0B1x11Automatic regulator setting≈250-mV difference0B1x10Automatic regulator setting≈350-mV difference0B1x00Automatic regulator setting≈400-mV difference(1)X are don't caresTable5-4.Supply-Regulator Setting–Automatic–3-V System Byte Option Bits Setting in Control Register ActionAddress B7B6B5B4B3B2(1)B1B00003-V system0B1x11Automatic regulator setting≈250-mV difference0B1x10Automatic regulator setting≈350-mV difference0B1x00Automatic regulator setting≈400-mV difference(1)X are don't cares5.1.4Power ModesThe chip has seven power states,which are controlled by two input pins(EN and EN2)and three bits in the chip status control register(00h).The main reader enable input is EN(which has a threshold level of1V minimum).Any input signal level from1.8V to V IN can be used.When EN is set high,all of the reader regulators are enabled,together with the13.56-MHz oscillator,while the SYS_CLK(output clock for external micro controller)is made available.The auxiliary-enable input EN2has two functions.A direct connection from EN2to V IN ensures availability of the regulated supply(V DD_X)and an auxiliary clock signal(60kHz)on the SYS_CLK output(same for the case EN=0).This mode is intended for systems in which the MCU controlling the reader is also being supplied by the reader supply regulator(V DD_X)and the MCU clock is supplied by the SYS_CLK output of the reader.This allows the MCU supply and clock to be available during power-down.A second function of the EN2input is to enable start-up of the reader system from complete power down(EN=0,EN2=0).In this case the EN input is being controlled by the MCU or other system device that is without supply voltage during complete power down(thus unable to control the EN input).A rising edge applied to the EN2input(which has a1-V threshold level)starts the reader supply system and13.56-MHz oscillator(identical to condition EN=1).This start-up mode lasts until all of the regulators have settled and the13.56-MHz oscillator has stabilized.If the EN input is set high by the MCU(or other system device),the reader stays active.If the EN input is not set high within100µs after the SYS_CLK output is switched from auxiliary clock(60kHz)to high-frequency clock(derived from the crystal oscillator),the reader system returns to complete power-down mode.This option can be used to wake the reader system from complete power down by using a pushbutton switch or by sending a single pulse.After the reader EN line is high,the other power modes are selected by control bits.The power mode options and functions are listed in Table5-5.Table5-5.Power ModesByte Option Bits Setting in Chip Status Control Register EN EN2Functionality Current AddressB7B6B5B4B3B2B1B0STBY RFON RF PWR REC ON0000Complete power down<1µA 0001VDD_X available120µASYS_CLK auxiliary frequency60kHz is ON 001x x x1x All supply regulators active and in low power 1.5mAmode13.56-MHz oscillator ONSYS_CLK clock available 0000x01x All supply regulators active 3.5mA13.56-MHz oscillator ONSYS_CLK clock available 0000x11x All supply regulators active10mA13.56-MHz oscillator ONSYS_CLK clock availableReceiver active00011x1x All supply regulators active70mA13.56-MHz oscillator ON(at5V)SYS_CLK clock availableReceiver activeTransmitter active–half-power mode 00010x1x All supply regulators active120mA13.56-MHz oscillator running(at5V)SYS_CLK clock availableReceiver activeTransmitter active–full-power mode During reader inactivity,the TRF7960/61can be placed in power down-mode(EN=0).The power down can be complete(EN=0,EN2=0)with no function running,or partial(EN=0,EN=1)where the regulated supply(V DD_X)and auxiliary clock60kHz(SYS_CLK)are available to the MCU or other system device.When EN is set high(or on rising edge of EN2and then confirmed by EN=1),the supply regulators are activated and the13.56-MHz oscillator started.When the supplies are settled and the oscillator frequency is stable,the SYS_CLK output is switched from the auxiliary frequency of60kHz to the selected frequency derived from the crystal oscillator.At this point,the reader is ready to communicate and perform the required tasks.The control system(MCU)can then write appropriate bits to the chip status control register(address00)and select the operation mode.The STANDBY mode(bit7=1of register00)is the active mode with the lowest current consumption.The reader is capable of recovering from this mode to full operation in100µs.The active mode with RF section disabled(bit5=0and bit1=0of register00)is the next active mode with low power consumption.The reader is capable of recovering from this mode to full operation in25µs.The active mode with only the RF receiver section active(bit1=1of register00)can be used to measure the external RF field(as described in RSSI measurements paragraph)if reader-to-reader anticollision is implemented.The active mode with the entire RF section active(bit5=1of register00)is the normal mode used for transmit and receive operations.5.1.5Timing DiagramsCHIP POWER UP TO CLOCK STARTC001Figure5-1.Power Up[V IN(Blue)to Crystal Start(Red)] CHIP ENABLE TO CLOCK STARTC002Figure5-2.EN2Low and EN High(Blue)to Start of System Clock(Red)。

KA7810中文资料

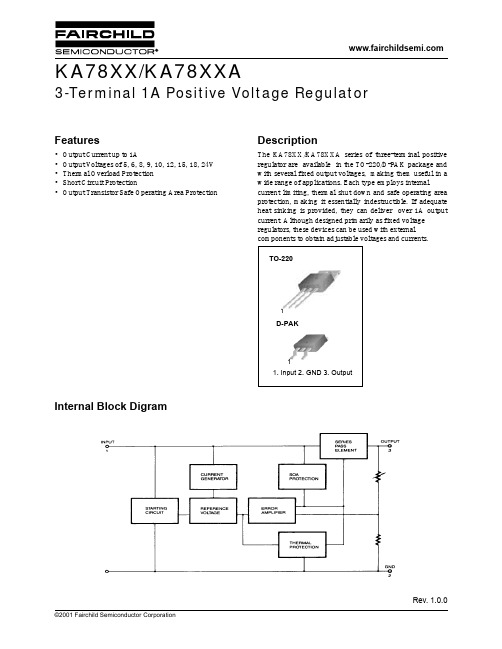

Rev. 1.0.0Features•Output Current up to 1A •Output V oltages of 5, 6, 8, 9, 10, 12, 15, 18, 24V•Thermal Overload Protection •Short Circuit Protection•Output Transistor Safe Operating Area ProtectionDescriptionThe KA78XX/KA78XXA series of three-terminal positive regulator are available in the TO-220/D-PAK package and with several fixed output voltages, making them useful in a wide range of applications. Each type employs internalcurrent limiting, thermal shut down and safe operating area protection, making it essentially indestructible. If adequate heat sinking is provided, they can deliver over 1A output current. Although designed primarily as fixed voltage regulators, these devices can be used with external components to obtain adjustable voltages and currents.TO-220D-PAK1. Input2. GND3. Output11Internal Block DigramKA78XX/KA78XXA3-Terminal 1A Positive Voltage RegulatorKA78XX/KA78XXAAbsolute Maximum RatingsElectrical Characteristics (KA7805/KA7805R)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =10V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V o due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol Value Unit Input Voltage (for V O = 5V to 18V)(for V O = 24V)V I V I 3540V V Thermal Resistance Junction-Cases (TO-220)R θJC 5°C/WThermal Resistance Junction-Air (TO-220)R θJA 65°C/WOperating Temperature Range (KA78XX/A/R)T OPR 0 ~ +125°C Storage Temperature RangeT STG-65 ~ +150°CParameterSymbolConditionsKA7805UnitMin.Typ.Max.Output VoltageV OT J =+25 o C4.85.0 5.25.0mA ≤Io ≤1.0A, P O ≤15W V I = 7V to 20V 4.75 5.0 5.25 V Line Regulation (Note1)Regline T J =+25 o C V O = 7V to 25V - 4.0100mV V I = 8V to 12V - 1.650Load Regulation (Note1)Regload T J =+25 o C I O = 5.0mA to1.5A -9100mV I O =250mA to 750mA -450Quiescent Current I Q T J =+25 o C - 5.08.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A -0.030.5mA V I = 7V to 25V -0.3 1.3Output Voltage Drift ∆V O /∆T I O = 5mA--0.8-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -42-µV/V O Ripple Rejection RR f = 120HzV O = 8V to 18V 6273-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-15-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -230-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7806/KA7806R)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =11V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7806UnitMin.Typ.Max.Output VoltageV OT J =+25 o C5.756.0 6.255.0mA ≤I O ≤1.0A, P O ≤15W V I = 8.0V to 21V 5.7 6.0 6.3 V Line Regulation (Note1)Regline T J =+25 o C V I = 8V to 25V -5120mV V I = 9V to 13V - 1.560Load Regulation (Note1)Regload T J =+25 o C I O =5mA to 1.5A -9120mV I O =250mA to750mA -360Quiescent Current I Q T J =+25 o C - 5.08.0mA Quiescent Current Change ∆I Q I O = 5mA to 1A --0.5mA V I = 8V to 25V -- 1.3Output Voltage Drift ∆V O /∆T I O = 5mA--0.8-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -45-µV/Vo Ripple Rejection RR f = 120HzV I = 9V to 19V 5975-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-19-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7808/KA7808R)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =14V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7808UnitMin.Typ.Max.Output VoltageV OT J =+25 o C7.78.08.35.0mA ≤ I O ≤1.0A, P O ≤15W V I = 10.5V to 23V 7.68.08.4 V Line Regulation (Note1)ReglineT J =+25 o C V I = 10.5V to 25V - 5.0160mV V I = 11.5V to 17V - 2.080Load Regulation (Note1)Regload T J =+25 o C I O = 5.0mA to 1.5A-10160mV I O = 250mA to 750mA - 5.080Quiescent Current I Q T J =+25 o C - 5.08.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A -0.050.5mA V I = 10.5A to 25V -0.5 1.0Output Voltage Drift ∆V O /∆T I O = 5mA--0.8-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -52-µV/Vo Ripple Rejection RR f = 120Hz, V I = 11.5V to 21.5V 5673-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -230-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7809/KA7809R)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =15V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7809UnitMin.Typ.Max.Output VoltageV OT J =+25 o C8.6599.355.0mA ≤ I O ≤1.0A, P O ≤15W V I = 11.5V to 24V 8.699.4 V Line Regulation (Note1)Regline T J =+25 o C V I = 11.5V to 25V -6180mV V I = 12V to 17V -290Load Regulation (Note1)Regload T J =+25 o C I O = 5mA to 1.5A -12180mV I O = 250mA to 750mA -490Quiescent Current I Q T J =+25 o C - 5.08.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A --0.5mA V I = 11.5V to 26V -- 1.3Output Voltage Drift ∆V O /∆T I O = 5mA--1-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -58-µV/Vo Ripple Rejection RR f = 120HzV I = 13V to 23V 5671-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J = +25 o C- 2.2-AElectrical Characteristics (KA7810)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =16V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7810UnitMin.Typ.Max.Output VoltageV OT J =+25 o C9.61010.45.0mA ≤ I O ≤ 1.0A, P O ≤ 15W V I = 12.5V to 25V 9.51010.5 V Line Regulation (Note1)Regline T J =+25 o C V I = 12.5V to 25V -10200mV V I = 13V to 25V -3100Load Regulation (Note1)Regload T J =+25 o C I O = 5mA to 1.5A -12200mV I O = 250mA to 750mA -4400Quiescent Current I Q T J =+25 o C - 5.18.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A --0.5mA V I = 12.5V to 29V -- 1.0Output Voltage Drift ∆V O /∆T I O = 5mA--1-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -58-µV/Vo Ripple Rejection RR f = 120HzV I = 13V to 23V 5671-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J =+25 o C- 2.2-AElectrical Characteristics (KA7812/KA7812R)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =19V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7812/KA7812R UnitMin.Typ.Max.Output VoltageV OT J =+25 o C11.51212.55.0mA ≤ I O ≤1.0A, P O ≤15W V I = 14.5V to 27V 11.41212.6 V Line Regulation (Note1)ReglineT J =+25 o CV I = 14.5V to 30V -10240mV V I = 16V to 22V - 3.0120Load Regulation (Note1)Regload T J =+25 o C I O = 5mA to 1.5A -11240mV I O = 250mA to 750mA - 5.0120Quiescent Current I Q T J =+25 o C - 5.18.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A -0.10.5mA V I = 14.5V to 30V -0.5 1.0Output Voltage Drift ∆V O /∆T I O = 5mA--1-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -76-µV/Vo Ripple Rejection RR f = 120HzV I = 15V to 25V 5571-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-18-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -230-mA Peak CurrentI PKT J = +25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7815)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =23V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7815UnitMin.Typ.Max.Output VoltageV OT J =+25 o C14.41515.65.0mA ≤ I O ≤1.0A, P O ≤15W V I = 17.5V to 30V 14.251515.75 V Line Regulation (Note1)Regline T J =+25 o C V I = 17.5V to 30V -11300mV V I = 20V to 26V -3150Load Regulation (Note1)Regload T J =+25 o C I O = 5mA to 1.5A -12300mV I O = 250mA to 750mA -4150Quiescent Current I Q T J =+25 o C - 5.28.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A --0.5mA V I = 17.5V to 30V -- 1.0Output Voltage Drift ∆V O /∆T I O = 5mA--1-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -90-µV/Vo Ripple Rejection RR f = 120HzV I = 18.5V to 28.5V 5470-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-19-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7818)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =27V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7818UnitMin.Typ.Max.Output VoltageV OT J =+25 o C17.31818.75.0mA ≤ I O ≤1.0A, P O ≤15W V I = 21V to 33V 17.11818.9 V Line Regulation (Note1)Regline T J =+25 o C V I = 21V to 33V -15360mV V I = 24V to 30V -5180Load Regulation (Note1)Regload T J =+25 o C I O = 5mA to 1.5A -15360mV I O = 250mA to 750mA - 5.0180Quiescent Current I Q T J =+25 o C - 5.28.0mA Quiescent Current Change ∆I Q I O = 5mA to 1.0A --0.5mA V I = 21V to 33V --1Output Voltage Drift ∆V O /∆T I O = 5mA--1-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -110-µV/Vo Ripple Rejection RR f = 120HzV I = 22V to 32V 5369-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-22-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J =+25 o C-2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7824)(Refer to test circuit ,0°C < T J < 125°C, I O = 500mA, V I =33V, C I = 0.33µF, C O =0.1µF, unless otherwise specified)Note:1. Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsKA7824UnitMin.Typ.Max.Output VoltageV OT J =+25 o C2324255.0mA ≤ I O ≤ 1.0A, P O ≤ 15W V I = 27V to 38V 22.82425.25 V Line Regulation (Note1)ReglineT J =+25 o CV I = 27V to 38V -17480mV V I = 30V to 36V -6240Load Regulation (Note1)Regload T J =+25 o C I O = 5mA to 1.5A -15480mV I O = 250mA to 750mA - 5.0240Quiescent Current I Q T J =+25 o C - 5.28.0mA Quiescent Current Change ∆I QI O = 5mA to 1.0A -0.10.5mA V I = 27V to 38V-0.51Output Voltage Drift ∆V O /∆T I O = 5mA --1.5-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz, T A =+25 o C -60-µV/Vo Ripple Rejection RR f = 120HzV I = 28V to 38V 5067-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-28-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -230-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7805A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 10V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 o C4.955.1V I O = 5mA to 1A, P O ≤ 15W V I = 7.5V to 20V 4.85 5.2Line Regulation (Note1)ReglineV I = 7.5V to 25V I O = 500mA-550mV V I = 8V to 12V -350T J =+25 o CV I = 7.3V to 20V -550V I = 8V to 12V- 1.525Load Regulation (Note1)RegloadT J =+25 o CI O = 5mA to 1.5A -9100mV I O = 5mA to 1A -9100I O = 250mA to 750mA -450Quiescent Current I Q T J =+25 o C - 5.0 6.0mA Quiescent Current Change∆I Q I O = 5mA to 1A--0.5mA V I = 8 V to 25V, I O = 500mA --0.8V I = 7.5V to 20V, T J =+25 o C --0.8Output Voltage Drift ∆V/∆T Io = 5mA--0.8-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25 o C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 8V to 18V -68-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J = +25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7806A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 11V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 o C5.5866.12V I O = 5mA to 1A, P O ≤ 15W V I = 8.6V to 21V 5.766 6.24Line Regulation (Note1)ReglineV I = 8.6V to 25V I O = 500mA-560mV V I = 9V to 13V -360T J =+25 o CV I = 8.3V to 21V -560V I = 9V to 13V- 1.530Load Regulation (Note1)RegloadT J =+25 o CI O = 5mA to 1.5A -9100mV I O = 5mA to 1A -4100I O = 250mA to 750mA - 5.050Quiescent Current I Q T J =+25 o C - 4.3 6.0mA Quiescent Current Change ∆I Q I O = 5mA to 1A--0.5mA V I = 9V to 25V, I O = 500mA --0.8V I = 8.5V to 21V, T J =+25 o C --0.8Output Voltage Drift ∆V/∆T I O = 5mA--0.8-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25 o C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 9V to 19V -65-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7808A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 14V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 o C7.8488.16V I O = 5mA to 1A, P O ≤15W V I = 10.6V to 23V 7.788.3Line Regulation (Note1)ReglineV I = 10.6V to 25V I O = 500mA-680mV V I = 11V to 17V -380T J =+25 o CV I = 10.4V to 23V -680V I = 11V to 17V-240Load Regulation (Note1)RegloadT J =+25 o CI O = 5mA to 1.5A -12100mV I O = 5mA to 1A -12100I O = 250mA to 750mA -550Quiescent Current I Q T J =+25 o C - 5.0 6.0mA Quiescent Current Change ∆I Q I O = 5mA to 1A--0.5mA V I = 11V to 25V, I O = 500mA --0.8V I = 10.6V to 23V, T J =+25 o C --0.8Output Voltage Drift ∆V/∆T I O = 5mA--0.8-mV/ o C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25 o C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 11.5V to 21.5V -62-dB Dropout Voltage V Drop I O = 1A, T J =+25 o C -2-V Output Resistance r O f = 1KHz-18-m ΩShort Circuit Current I SC V I = 35V, T A =+25 o C -250-mA Peak CurrentI PKT J =+25 o C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7809A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 15V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25°C8.829.09.18V I O = 5mA to 1A, P O ≤15W V I = 11.2V to 24V 8.659.09.35Line Regulation (Note1)ReglineV I = 11.7V to 25V I O = 500mA-690mV V I = 12.5V to 19V -445T J =+25°CV I = 11.5V to 24V -690 V I = 12.5V to 19V -245Load Regulation (Note1)RegloadT J =+25°CI O = 5mA to 1.0A -12100mV I O = 5mA to 1.0A -12100I O = 250mA to 750mA -550Quiescent Current I Q T J =+25 °C- 5.0 6.0mA Quiescent Current Change ∆I Q V I = 11.7V to 25V, T J =+25 °C --0.8mA V I = 12V to 25V, I O = 500mA --0.8I O = 5mA to 1.0A --0.5Output Voltage Drift ∆V/∆T I O = 5mA--1.0-mV/ °C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25 °C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 12V to 22V -62-dB Dropout Voltage V Drop I O = 1A, T J =+25 °C - 2.0-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 °C -250-mA Peak CurrentI PKT J =+25°C- 2.2-A(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 16V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbolConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25°C9.81010.2V I O = 5mA to 1A, P O ≤ 15W V I =12.8V to 25V 9.61010.4Line Regulation (Note1)ReglineV I = 12.8V to 26V I O = 500mA-8100mV V I = 13V to 20V -450 T J =+25 °CV I = 12.5V to 25V -8100 V I = 13V to 20V -350Load Regulation (Note1)RegloadT J =+25 °CI O = 5mA to 1.5A -12100mV I O = 5mA to 1.0A -12100 I O = 250mA to 750mA -550Quiescent Current I Q T J =+25 °C- 5.0 6.0mA Quiescent Current Change ∆I QV I = 13V to 26V, T J =+25 °C --0.5mA V I = 12.8V to 25V, I O = 500mA --0.8 I O = 5mA to 1.0A--0.5Output Voltage Drift ∆V/∆T I O = 5mA --1.0-mV/ °C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25 °C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 14V to 24V -62-dB Dropout Voltage V Drop I O = 1A, T J =+25°C - 2.0-V Output Resistance r O f = 1KHz-17-m ΩShort Circuit Current I SC V I = 35V, T A =+25 °C -250-mA Peak CurrentI PKT J =+25 °C- 2.2-A(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 19V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 °C11.751212.25V I O = 5mA to 1A, P O ≤15W V I = 14.8V to 27V 11.51212.5Line Regulation (Note1)ReglineV I = 14.8V to 30V I O = 500mA-10120mV V I = 16V to 22V -4120 T J =+25 °CV I = 14.5V to 27V -10120 V I = 16V to 22V-360Load Regulation (Note1)RegloadT J =+25 °CI O = 5mA to 1.5A -12100mV I O = 5mA to 1.0A -12100 I O = 250mA to 750mA -550Quiescent Current I Q T J =+25°C- 5.16.0mA Quiescent Current Change ∆I QV I = 15V to 30V, T J =+25 °C -0.8mA V I = 14V to 27V, I O = 500mA -0.8 I O = 5mA to 1.0A-0.5Output Voltage Drift ∆V/∆T I O = 5mA --1.0-mV/°C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25°C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 14V to 24V -60-dB Dropout Voltage V Drop I O = 1A, T J =+25°C - 2.0-V Output Resistance r O f = 1KHz-18-m ΩShort Circuit Current I SC V I = 35V, T A =+25 °C -250-mA Peak CurrentI PKT J =+25 °C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7815A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I =23V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 °C14.71515.3V I O = 5mA to 1A, P O ≤15W V I = 17.7V to 30V 14.41515.6Line Regulation (Note1)ReglineV I = 17.9V to 30V I O = 500mA-10150mV V I = 20V to 26V -5150 T J =+25°CV I = 17.5V to 30V -11150 V I = 20V to 26V-375Load Regulation (Note1)RegloadT J =+25 °CI O = 5mA to 1.5A -12100mV I O = 5mA to 1.0A -12100 I O = 250mA to 750mA -550Quiescent Current I Q T J =+25 °C- 5.2 6.0mA Quiescent Current Change ∆I QV I = 17.5V to 30V, T J =+25 °C --0.8mA V I = 17.5V to 30V, I O = 500mA --0.8 I O = 5mA to 1.0A--0.5Output Voltage Drift ∆V/∆T I O = 5mA --1.0-mV/°C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25 °C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 18.5V to 28.5V -58-dB Dropout Voltage V Drop I O = 1A, T J =+25 °C - 2.0-V Output Resistance r O f = 1KHz-19-m ΩShort Circuit Current I SC V I = 35V, T A =+25 °C -250-mA Peak CurrentI PKT J =+25°C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7818A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 27V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 °C17.641818.36V I O = 5mA to 1A, P O ≤15W V I = 21V to 33V 17.31818.7Line Regulation (Note1)ReglineV I = 21V to 33V I O = 500mA-15180mV V I = 21V to 33V -5180 T J =+25 °CV I = 20.6V to 33V -15180 V I = 24V to 30V-590Load Regulation (Note1)RegloadT J =+25°CI O = 5mA to 1.5A -15100mV I O = 5mA to 1.0A -15100 I O = 250mA to 750mA -750Quiescent Current I Q T J =+25 °C- 5.2 6.0mA Quiescent Current Change ∆I QV I = 21V to 33V, T J =+25 °C --0.8mA V I = 21V to 33V, I O = 500mA --0.8 I O = 5mA to 1.0A--0.5Output Voltage Drift ∆V/∆T I O = 5mA --1.0-mV/ °C Output Noise Voltage V N f = 10Hz to 100KHz T A =+25°C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 22V to 32V -57-dB Dropout Voltage V Drop I O = 1A, T J =+25°C - 2.0-V Output Resistance r O f = 1KHz-19-m ΩShort Circuit Current I SC V I = 35V, T A =+25°C -250-mA Peak CurrentI PKT J =+25 °C- 2.2-AKA78XX/KA78XXAElectrical Characteristics (KA7824A)(Refer to the test circuits. 0o C < T J < +125 o C, I o =1A, V I = 33V, C I =0.33µF, C O =0.1µF, unless otherwise speci-fied)Note:1. Load and line regulation are specified at constant junction temperature. Change in V O due to heating effects must be takeninto account separately. Pulse testing with low duty is used.ParameterSymbol ConditionsMin.Typ.Max.UnitOutput VoltageV OT J =+25 °C23.52424.5V I O = 5mA to 1A, P O ≤15W V I = 27.3V to 38V 232425Line Regulation (Note1)ReglineV I = 27V to 38V I O = 500mA-18240mV V I = 21V to 33V -6240 T J =+25 °CV I = 26.7V to 38V -18240 V I = 30V to 36V-6120Load Regulation (Note1)RegloadT J =+25 °CI O = 5mA to 1.5A -15100mV I O = 5mA to 1.0A -15100 I O = 250mA to 750mA -750Quiescent Current I Q T J =+25 °C- 5.2 6.0mA Quiescent Current Change ∆I QV I = 27.3V to 38V, T J =+25 °C --0.8mA V I = 27.3V to 38V, I O = 500mA --0.8 I O = 5mA to 1.0A--0.5Output Voltage Drift ∆V/∆T I O = 5mA --1.5-mV/ °C Output Noise Voltage V N f = 10Hz to 100KHz T A = 25 °C-10-µV/Vo Ripple Rejection RR f = 120Hz, I O = 500mA V I = 28V to 38V -54-dB Dropout Voltage V Drop I O = 1A, T J =+25 °C - 2.0-V Output Resistance r O f = 1KHz-20-m ΩShort Circuit Current I SC V I = 35V, T A =+25 °C -250-mA Peak CurrentI PKT J =+25 °C- 2.2-AKA78XX/KA78XXATypical Perfomance CharacteristicsFigure 1.Quiescent Current Figure 3.Output Voltage Figure 2.Peak Output Current Figure 4.Quiescent CurrentITypical ApplicationsInput OutputFigure 5.DC ParametersInput OutputFigure 6.Load RegulationInput OutputFigure 7.Ripple RejectionInput OutputFigure 8.Fixed Output Regulator2122Figure 9.Constant Current RegulatorNotes :(1)To specify an output voltage. substitute voltage value for "XX." A common ground is required between the input and the Outputvoltage. The input voltage must remain typically 2.0V above the output voltage even during the low point on the input ripple voltage.(2)C I is required if regulator is located an appreciable distance from power Supply filter.(3)C O improves stability and transient response.V O = V XX (1+R 2/R 1)+I Q R 2Figure 10.Circuit for Increasing Output VoltageI RI ≥5 I QV O = V XX (1+R 2/R 1)+I Q R 2Figure 11.Adjustable Output Regulator (7 to 30V)InputOutputC ICOInput OutputC IC OI RI 5IQ≥Input OutputC IC O23Figure 12.High Current Voltage RegulatorFigure 13.High Output Current with Short Circuit ProtectionFigure 14.Tracking Voltage RegulatorInputOutputInputOutput24Figure 15.Split Power Supply ( ±15V-1A)Figure 16.Negative Output Voltage CircuitFigure 17.Switching RegulatorInputOutputInput OutputMechanical DimensionsPackageTO-22025Mechancal Dimensions (Continued)PackageD-PAK2627Ordering InformationProduct Number Output Voltage TolerancePackageOperating TemperatureKA7805 / KA7806 ±4%TO-2200 ~ + 125°CKA7808 / KA7809KA7810 KA7812 / KA7815KA7818 / KA7824KA7805A / KA7806A ±2%KA7808A / KA7809A KA7810A / KA7812A KA7815A / KA7818AKA7824A KA7805R / KA7806R ±4%D-PAKKA7808R / KA7809RKA7812R。

XX1000中文资料

Mimix Broadband ’s single ended fed (no external balun required) 7.5-25.0/15.0-50.0 GHz GaAs MMIC doubler has a +15.0 dBm output drive and is an excellent LO doubler that can be used to drive fundamental mixer devices. It is also well suited to drive Mimix's XR1002 receiver device. This MMIC uses Mimix Broadband ’s 0.15 µm GaAs PHEMT device model technology, and is based upon electron beam lithography to ensure high repeatability anduniformity. The chip has surface passivation to protect and provide a rugged part with backside via holes and gold metallization to allow either a conductive epoxy or eutectic solder die attach process. This device is well suited for Millimeter-wavePoint-to-Point Radio, LMDS, SATCOM and VSAT applications.7.5-25.0/15.0-50.0 GHz GaAs MMIC Excellent Broadband Mixer DriverSingle Ended Fed Doubler with Distributed Buffer AmplifierExcellent LO Driver for Mimix Receivers +15 dBm Output Drive100% On-Wafer RF, DC and Output Power Testing 100% Visual Inspection to MIL-STD-883Method 2010FeaturesElectrical Characteristics (Ambient T emperature T = 25 o C)ParameterInput Frequency Range (fin)Output Frequency Range (fout)Input Return Loss (S11)Output Return Loss (S22)Harmonic Gain (fout)Fundamental Rejection (fin) Saturated Output Power (Psat)RF Input Power (RF Pin)Output Power at +0.0 dBm Pin (Pout)Drain Bias Voltage (Vd1,2)Gate Bias Voltage (Vg1)Gate Bias Voltage (Vg2)Supply Current (Id1,2) (Vd=5.0V, Vg1=-0.6V, Vg2=0.0V Typical)Source Voltage (Vss)Source Current (Iss)Units GHz GHz dB dB dB dBc dBm dBm dBm VDC VDC VDC mA VDC mA Min.7.515.0------10.0---1.2-1.2--5.525Typ.--TBD 12.01320+15-+13.0+5.0-0.60.0220-5.050Max.25.050.0-----+10.0-+5.5+0.1+0.1250-2.060Absolute Maximum RatingsSupply Voltage (Vd)Supply Voltage (Vss)Supply Current (Id)Supply Current (Iss)Gate Bias Voltage (Vg)Input Power (RF Pin)Storage Temperature (Tstg)Operating Temperature (Ta)Channel Temperature (Tch)+6.0 VDC -6.0 VDC 300 mA 60 mA +0.3 VDC +12.0 dBm -65 to +165 O C -55 to MTTF Table MTTF Table Chip Device Layout1(1) Channel temperature affects a device's MTTF. It is recommended to keep channel temperature as low as possible for maximum life.1April 2006 - Rev 10-Apr-06General DescriptionDoubler Measurements0458_4_sa mples: Po ut (2xFin) vs. Fin (GHz)Pin=0dBm, VD1=5V, VG1=-0.6V, VS S=-5V, VD2=5V ~150mA, VG2=open101214161820Fin (GHz)Pout(2xFin)0458_4_s amples: Pout (Fin) vs. F in (GHz)Pin=0dBm, VD1=5V, VG1=-0.6V, VS S=-5V, VD2=5V ~150mA, VG2=open-5101520810121416182022Fin (GHz)Pout(Fin)7.5-25.0/15.0-50.0 GHz GaAs MMICHarmonic Gain and Fundamental Rejection vs Output Freq.Pin = 0 dBm XX1000: Po ut (2xFin) an d Po ut (F in) v s. F in (GHz)Pin = -8 to +6 dBm810121416182022Fin (GHz)Pout(dBm)April 2006 - Rev 10-Apr-06Mechanical DrawingBypass Capacitors- See App Note [2] (Note: Engineering designator is 40DBL0458)Units: millimeters (inches) Bond pad dimensions are shown to center of bond pad. Thickness: 0.110 +/- 0.010 (0.0043 +/- 0.0004), Backside is ground, Bond Pad/Backside Metallization: GoldAll Bond Pads are 0.100 x 0.100 (0.004 x 0.004).Bond pad centers are approximately 0.109 (0.004) from the edge of the chip.Dicing tolerance: +/- 0.005 (+/- 0.0002). Approximate weight: 1.566 mg.Bond Pad #1 (RF In) Bond Pad #2 (Vd1)Bond Pad #3 (Vd2)Bond Pad #4 (RF Out)Bond Pad #5 (Vg2)Bond Pad #6 (Vss)Bond Pad #7 (Vg1)7.5-25.0/15.0-50.0 GHz GaAs MMICApril 2006 - Rev 10-Apr-061.620(0.064)0.2950.6950.196(0.035)(0.061)(0.019)(0.012)0.01234567Vd2Vg1App Note [1] Biasing - It is recommended to separately bias each doubler stage Vd1 through Vd2 at Vd(1,2)=5.0V with Id1=80mAand Id2=140mA and Vss=-5.0V with Iss=50mA. XX1000 provides good performance at reduced bias with Vss=-2.0V and Iss=25mA.Maximum output power is achieved with Vss=-5.0V and Iss=50mA. Separate biasing is recommended if the doubler is to be used at high levels of saturation, where gate rectification will alter the effective gate control voltage. It is also recommended to use active biasing to keep the currents constant as the RF power and temperature vary; this gives the most reproducible results. Depending on the supply voltage available and the power dissipation constraints, the bias circuit may be a single transistor or a low power operational amplifier, with a low value resistor in series with the drain supply used to sense the current. The gate of the pHEMT is controlled to maintain correct drain current and thus drain voltage. The typical gate voltages needed to do this are Vg1=-0.6V and Vg2=0.0V. Typically the gate is protected with Silicon diodes to limit the applied voltage. Also, make sure to sequence the applied voltage to ensure negative gate bias is available before applying the positive drain supply.App Note [2] Bias Arrangement -For Individual Stage Bias (Recommended for doubler applications) -- Each DC pad (Vd1, 2, Vss and Vg1, 2) needs to have DC bypass capacitance (~100-200 pF) as close to the device as possible. Additional DC bypass capacitance (~0.01 uF) is also recommended.MTTF T able s (TBD)These numbers were calculated based on accelerated life test information and thermal model analysis received from the fabricating foundry.Backplate Temperature 55 deg Celsius 75 deg Celsius 95 deg CelsiusChannel Temperature deg Celsius deg Celsius deg CelsiusFITs E+E+E+MTTF HoursE+E+E+Rth C/W C/W C/WBias Conditions: Vd1=Vd2=4.0V, Id1=40 mA, Id2=140 mA, Vss=-5.0V, Iss=50mA7.5-25.0/15.0-50.0 GHz GaAs MMICApril 2006 - Rev 10-Apr-06Device SchematicMimix Broadband MMIC-based 18.0-34.0 GHz Doubler/Receiver Block Diagram(Changing LO and IF frequencies as required allows design to operate as high as 34 GHz)T ypical ApplicationXR10027.5-25.0/15.0-50.0 GHz GaAs MMIC April 2006 - Rev 10-Apr-06Handling and Assembly InformationCAUTION! - Mimix Broadband MMIC Products contain gallium arsenide (GaAs) which can be hazardous to the human body and the environment. For safety, observe the following procedures:Do not ingest.Do not alter the form of this product into a gas, powder, or liquid through burning, crushing, or chemical processing as these by-products are dangerous to the human body if inhaled, ingested, or swallowed.Observe government laws and company regulations when discarding this product. This product must be discarded in accordance with methods specified by applicable hazardous waste procedures.Life Support Policy - Mimix Broadband's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President and General Counsel of MimixBroadband. As used herein: (1) Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in asignificant injury to the user. (2) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ESD - Gallium Arsenide (GaAs) devices are susceptible to electrostatic and mechanical damage. Die are supplied in antistatic containers, which should be opened in cleanroom conditions at an appropriately grounded anti-static workstation. Devices need careful handling using correctly designed collets, vacuum pickups or, with care,sharp tweezers.Die Attachment - GaAs Products from Mimix Broadband are 0.100 mm (0.004") thick and have vias through to the backside to enable grounding to the circuit. Microstrip substrates should be brought as close to the die as possible. The mounting surface should be clean and flat. If using conductive epoxy, recommended epoxies are Ablestick 84-1LMI or 84-1LMIT cured in a nitrogen atmosphere per manufacturer's cure schedule. Apply epoxy sparingly to avoid getting any on to the top surface of the die. An epoxy fillet should be visible around the total die periphery. If eutectic mounting is preferred, then a fluxless gold-tin (AuSn) preform, approximately 0.001thick, placed between the die and the attachment surface should be used. A die bonder that utilizes a heated collet and provides scrubbing action to ensure total wetting to prevent void formation in a nitrogen atmosphere is recommended. The gold-tin eutectic (80% Au 20% Sn) has a melting point of approximately 280 C (Note: GoldGermanium should be avoided). The work station temperature should be 310 C 10 C. Exposure to these extreme temperatures should be kept to minimum. The collet should be heated, and the die pre-heated to avoidexcessive thermal shock. Avoidance of air bridges and force impact are critical during placement.Wire Bonding - Windows in the surface passivation above the bond pads are provided to allow wire bonding to the die's gold bond pads. The recommended wire bonding procedure uses 0.076 mm x 0.013 mm (0.003" x0.0005") 99.99% pure gold ribbon with 0.5-2% elongation to minimize RF port bond inductance. Gold 0.025 mm (0.001") diameter wedge or ball bonds are acceptable for DC Bias connections. Aluminum wire should beavoided. Thermo-compression bonding is recommended though thermosonic bonding may be used providing the ultrasonic content of the bond is minimized. Bond force, time and ultrasonics are all critical parameters.Bonds should be made from the bond pads on the die to the package or substrate. All bonds should be as short as possible.2+-7.5-25.0/15.0-50.0 GHz GaAs MMIC April 2006 - Rev 10-Apr-06。

109101907资料