ADR444A中文资料

MMPQ2222A;FFB2222A;中文规格书,Datasheet资料

ON CHARACTERISTICS

hFE DC Current Gain IC = 0.1 mA, VCE = 10 V IC = 1.0 mA, VCE = 10 V IC = 10 mA, VCE = 10 V IC = 150 mA, VCE = 10 V* IC = 150 mA, VCE = 1.0 V* IC = 500 mA, VCE = 10 V* IC = 150 mA, IB = 15 mA IC = 500 mA, IB = 50 mA IC = 150 mA, IB = 15 mA IC = 500 mA, IB = 50 mA 35 50 75 100 50 40

*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

Spice Model

NPN (Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

Thermal Characteristics

Symbol

PD RθJA

TA = 25°C unless otherwise noted

Characteristic

Total Device Dissipation Derate above 25°C Thermal Resistance, Junction to Ambient Effective 4 Die Each Die FFB2222A 300 2.4 415

E3643A中文资料(Agilent(Hewlett-Packard))中文数据手册「EasyDatasheet - 矽搜」

防护

一年E364xA系列电源

三个月标准运附件

产品监管

设计符合UL3111-1;认证,CSA 22.2 1010.1号; 符合IEC 1010-1;符合EMC指令89/336/EEC(第1组,A类)

订购信息

安捷伦E364xA系列电源 E3640A 30瓦单电源 E3641A 30瓦单电源 E3642A 50瓦单电源 E3643A 50瓦单电源 E3644A 80瓦单电源 E3645A 80瓦单电源 E3646A 60瓦双电源 E3647A 60瓦双电源 E3648A 100瓦双电源 E3649A 100瓦双电源

E3640A

E3641A

E3642A

E3643A

E3644A

E3645A

30 W

50 W

80 W

1

0至8 V / 3 A或 0 to 20 V/1.5 A

5.3千克

1

0〜35 V / 0.8 A或 0 to 60 V/0.5 A

5.2千克

1

0至8 V / 5 A或 0 to 20 V/2.5 A

6.3千克

*与1CM或锁定链接机架安装/ FL法兰套件需要

安捷伦或客户支持轨

安捷伦支持RailsE3663AC

5

(标准命令 可编程仪器)允许快速和简单编程程

序. 此外,用户手册,为所有最终用户 编程足够信息,从初学者到退伍军人 .

广泛支持

VXI 即插即用 软件驱动程序 适用于VEE,国家 仪器公司LabVIEW and LabWin dows .有这些驱动程序, 整合E364xA到您 系统不能有任何容易.该

驱动程序在微软支持

准确度 编程 电压

12个 月

(@ 25ºC±5°C),±(%输出+偏移)

ADR444- 具有吸电流和源电流能力的超低噪声基准电压源

ADR444: 具有吸电流和源电流能力的超低噪声基准电压

源

ADR44x 是XFET®系列基准电压源,具有超低噪声、高精度和低温度漂移性能。

利用ADI 的温度漂移曲率校正专利技术和XFET(外加离子注入场效应管)技术,可以使ADR44x 电压随温度变化的非线性度大幅降至最小。

XFET 基准电压源的噪声性能优于嵌入式齐纳基准电压源,且所需的电源电压裕量较小(0.5 V)。

这些特性相结合,使ADR44x 系列非常适合高端数据采集系统、光纤网络和医疗应用中的精密信号转换。

ADR44x 系列的源电流输出最高达10 mA,最大吸电流能力为-5 mA。

它还具有调整引脚,可以在0.5%范围内调整输出电压,而性能则不受影响。

ADR44x 系列分为两种电气等级,提供8 引脚MSOP 和窄体SOIC 两种封装。

所有型号产品的额定温度范围均为?40°C至+125°C扩展工业温度范围。

特性

·超低噪声(0.1 Hz 至10 Hz)

·输入范围: (VOUT + 500 mV) 至18 V

·出色的温度系数

A 级: 10 ppm/°C

B 级: 3 ppm/°C

·低压差工作:500 mV

·高输出源电流和吸电流,分别为+10 mA 和-5 mA

·宽温度范围:-40°C至+125°C

ADR444 引脚配置图。

FDS4435A中文资料

Test Conditions

VGS = 0 V, ID = -250 µA ID = -250 µA,Referenced to 25°C VDS = -24 V, VGS = 0 TJ = 125°C VGS = 20 V, VDS = 0 V VGS = -20 V, VDS = 0 V

°C

Thermal Characteristics

RθJA RθJC Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case

(Note 1a) (Note 1)

50 25

°C/W °C/W

Package Marking and Ordering Information

0.07

1.6

RDS(ON), ON RESISTANCE (OHM)

NORMALIZED ON-RESISTANCE

VGS = -10V ID = -9A

ID = -4.5A

0.06 0.05 0.04 0.03 0.02 0.01 0

1.4

1.2

1

TJ = 125 C

O

0.8

TJ = 25 C

O

Scale 1 : 1 on letter size paper 2: Pulse Test: Pulse Width £ 300 ms, Duty Cycle £ 2.0%

FDS4435A Rev. D

元器件交易网

FDS4435A

Typical Characteristics

40

Figure 4. On-Resistance Variation with Gate-to-Source Voltage

LOC111中文资料

LOC111中⽂资料LOC111Linear OptocouplersApplicationsFeaturesDescriptionApprovalsOrdering Information Pin ConfigurationLOC111 is a linear optocoupler for use in telecom, med-ical and power supply isolation circuits. They are available in 8 pin DIP , surface mount or flatpack packages.Modem Transformer Replacement With No Insertion LossDigital Telephone IsolationPower Supply Feedback Voltage/Current Medical Sensor Isolation Audio Signal InterfacingIsolation of Process Control TransducersUL Recognized: File Number E76270CSA Certified: File Number LR 43639-10BSI Certified:BS EN 60950:1992 (BS7002:1992)Certificate #:7344 BS EN 41003:1993Certificate #:73448 Pin Flatpack or DIP PAckage (PCMCIA Compatible)?Couples Analog and Digital Signals ?Wide Bandwidth (>200kHz)?High Gain StabilityLow Input/Output Capacitance Low Power Consumption 0.01% Servo Linearity THD 87dB TypicalMachine Insertable, Wave SolderableSurface Mount and Tape Reel Versions Available VDE CompatibleLOC111 PinoutDLED +LED +V cc 1I1NC NC +V cc 2I 2LOC111Absolute Maximum Ratings are stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this data sheet is not implied. Exposure of the device to the absolute maximum ratings for an extended period may degrade the device and effect its reliability.Absolute Maximum Ratings (@ 25o C)Electrical Characteristics2Derate Linearly 6.67 mW/°CK3 Sorted Bins Bin A= 0.550-0.605Bin B = 0.606-0.667Bin C = 0.668-0.732Bin D = 0.733-0.805Bin E = 0.806-0.886Bin F = 0.887-0.974Bin G = 0.975-1.072Bin H = 1.073-1.179Bin I = 1.180-1.297Bin J= 1.298-1.426The LOC110/LOC111/LOC112 are shipped in anti-static tubes of 50pieces. Each tube will contain one K3 sorted bin.Bin designation marked on each device (A-J).Orders for the LOC110 product will be shipped using bins available at the date of the order. Any bin (A-J) can be shipped.For customers requiring selected bins D E F G we offer part num-bers LOC111 or LOC112.LOC111Performance Data*The Performance data shown in the graphs above is typical of device performance. For guaranteed parameters not indicated in the written specifications, please contact our application department.LOC111Dimensionsmm (inches)Mechanical DimensionsCPC7581 Mechanical DimensionsDimensionsmm(inches)CLARE LOCATIONSClare Headquarters78 Cherry Hill DriveBeverly, MA01915Tel: 1-978-524-6700Fax: 1-978-524-4900Toll Free: 1-800-27-CLARE Clare Micronix Division 145 ColumbiaAliso Viejo, CA92656-1490 Tel: 1-949-831-4622Fax: 1-949-831-4628SALES OFFICES AMERICASAmericas HeadquartersClare78 Cherry Hill DriveBeverly, MA01915Tel: 1-978-524-6700Fax: 1-978-524-4900Toll Free: 1-800-27-CLARE Eastern RegionClareP.O. Box 856Mahwah, NJ 07430Tel: 1-201-236-0101Fax: 1-201-236-8685Toll Free: 1-800-27-CLARE Central RegionClare Canada Ltd.3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066 Fax: 1-905-333-1824Western RegionClare1852 West 11th Street, #348 Tracy, CA95376Tel: 1-209-832-4367Fax: 1-209-832-4732Toll Free: 1-800-27-CLARE CanadaClare Canada Ltd.3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066 Fax: 1-905-333-1824EUROPEEuropean HeadquartersCP Clare nvBampslaan 17B-3500 Hasselt (Belgium)Tel: 32-11-300868Fax: 32-11-300890FranceClare France SalesLead Rep99 route de Versailles 91160 ChamplanFranceTel: 33 1 69 79 93 50Fax: 33 1 69 79 93 59 GermanyClare Germany Sales ActiveComp Electronic GmbH Mitterstrasse 1285077 ManchingGermanyTel: 49 8459 3214 10Fax: 49 8459 3214 29ItalyC.L.A.R.E.s.a.s.Via C. Colombo 10/AI-20066 Melzo (Milano) Tel: 39-02-95737160Fax: 39-02-95738829 SwedenClare SalesComptronic ABBox 167S-16329 Sp?ngaTel: 46-862-10370Fax: 46-862-10371United KingdomClare UK SalesMarco Polo HouseCook WayBindon RoadTauntonUK-Somerset TA2 6BG Tel: 44-1-823 352541Fax: 44-1-823 352797ASIA PACIFICAsian HeadquartersClareRoom N1016, Chia-Hsin, Bldg II,10F, No. 96, Sec. 2Chung Shan North RoadTaipei, Taiwan R.O.C.Tel: 886-2-2523-6368Fax: 886-2-2523-6369/doc/0fd841f2770bf78a64295400.html Worldwide Sales OfficesSpecification: DS-LOC111-R6Copyright 2001, Clare, Inc.All rights reserved. Printed in USA.02/23/01Clare cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in this Clare product. No circuit patent licenses nor indemnity are expressed or implied. Clare reserves the right to change the specification and circuitry, with-out notice at any time. The products described in this document are not intended for use in medical implantation or other direct life support applications where malfunction may result in direct phys-ical harm, injury or death to a person.。

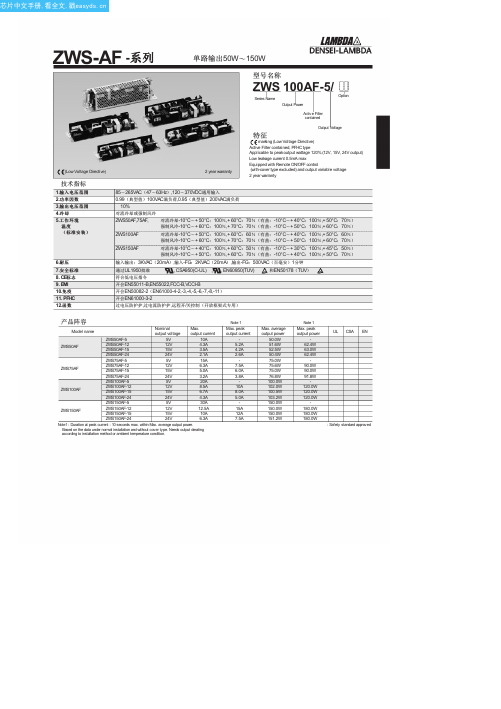

ZWS150PAF-24JA中文资料(DENSEI-LAMBDA)中文数据手册「EasyDatasheet - 矽搜」

推荐线束

P134 P209

(Unit: mm)

(Unit: mm)

(Unit: mm)

推荐噪声滤波器

MAW-1203-22 GO!!

推荐线束

P134 P209

(Unit: mm)

Nominal output voltage

3.3V 5V 12V 15V 24V

36V 48V 3.3V 5V 12V 15V

24V 36V 48V 24V 36V 3.3V

5V 12V 15V 24V 36V 48V

Max. output current

15A 15A 6.3A 5A 3.2A

2.1A 1.6A 20A 20A 8.5A 6.7A

芯片中文手册,看全文,戳

ZWS-PF -系列

ZWS75PF (STD型号:MOLEX连接器) ZWS75PF (/ J型:JST连接器) ZWS75PF (/ JA类型:有盖型JST连接器)

ZWS100PF (STD型号:MOLEX连接器)

推荐噪声滤波器

MAW-1203-22 GO!!

120.0W 120.0W 120.0W

180.0W 180.0W 180.0W

UL CSA EN : Safety standard approved

芯片中文手册,看全文,戳

ZWS-AF -系列

ZWS50AF (STD型号:MOLEX连接器,/ J型:JST连接器)

ZWS50AF (/ JA类型:有盖型)

开会EN61000-3-2

ZWS75PF,ZWS100PF(输入功率:50W以上) ZWS120PPF,ZWS150PF(输入功率:over75W)

过电压防护护,过电流防护护

飞兆芯片RD-444规格书

© 2014 Fairchild Semiconductor Corporation

1

RD-444_FSFR2100 • Rev. 1.0

ቤተ መጻሕፍቲ ባይዱ

1. Schematics

Figure 1.

Schematic Part 1

© 2014 Fairchild Semiconductor Corporation

2. Transformer

2.1. Transformer Schematic Diagram

Figure 3.

Transformer Configuration and Winding Stackup

2.2. Winding Specification

Winding

W1a W3 W4 W1b W2

RD-444_FSFR2100 • Rev. 1.0

Bill of Materials

Reference

OC1 Q1, Q2, Q3, Q4, Q5, Q6 Q91 R2, R3, R4, R5, R6, R24 R102 R7, R8, R9, R17, R20, R23

Application

Street Lamp

Fairchild Device

FSFR2100

Input Voltage Range

90-265 VAC

Rated Output Power

180 W

Output Voltage (Rated Current)

6 x 86 V (0.35 A)

Topology

Pin

Inductance Leakage 4→6 4→6

Specification

AO4449中文资料

SymbolTyp Max 31406075R θJL 1624Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-Ambient A t ≤ 10s R θJA °C/W Maximum Junction-to-Ambient A Steady-State °C/W AO4449AO4449SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1-2-3V I D(ON)-40A 2734T J =125°C384354m Ωg FS 15S V SD -0.77-1V I S-3.5A C iss 9801225pF C oss 150pF C rss 115pF R g2.23.3ΩQ g (10V)18.724nC Q g (4.5V)9.6nC Q gs 3.2nC Q gd 4.8nC t D(on)7.7ns t r 6ns t D(off)20ns t f 7ns t rr 2126ns Q rr13nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery TimeBody Diode Reverse Recovery Charge I F =-7A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-7AReverse Transfer Capacitance I F =-7A, dI/dt=100A/µsElectrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions I DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-30V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current R DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward Voltage m ΩV GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-7ATurn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.2Ω, R GEN =3ΩGate resistanceV GS =0V, V DS =0V, f=1MHzTurn-Off Fall TimeSWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Maximum Body-Diode Continuous CurrentInput Capacitance Output Capacitance Turn-On DelayTime DYNAMIC PARAMETERS V GS =0V, V DS =-15V, f=1MHz Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-7AA: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using <300 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.F.The current rating is based on the t ≤ 10s thermal resistance rating.Rev0: Dec 2006AO4449AO4449。

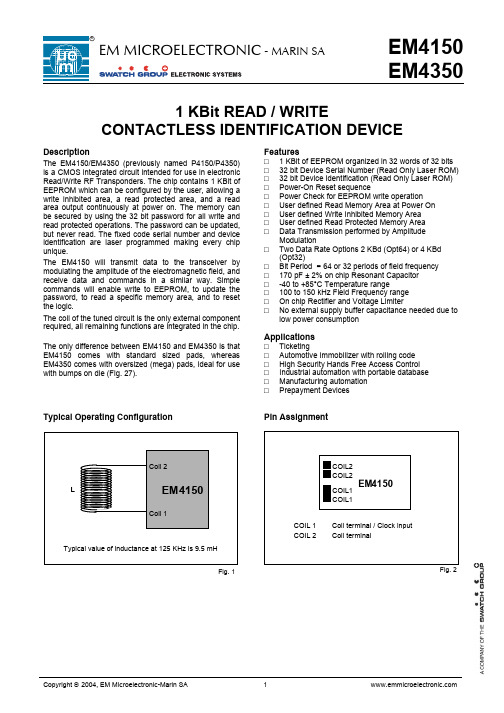

EM4150A5WW11中文资料

1 KBit READ / WRITE CONTACTLESS IDENTIFICATION DEVICEDescriptionThe EM4150/EM4350 (previously named P4150/P4350) is a CMOS integrated circuit intended for use in electronic Read/Write RF Transponders. The chip contains 1 KBit of EEPROM which can be configured by the user, allowing a write inhibited area, a read protected area, and a read area output continuously at power on. The memory can be secured by using the 32 bit password for all write and read protected operations. The password can be updated, but never read. The fixed code serial number and device identification are laser programmed making every chip unique.The EM4150 will transmit data to the transceiver by modulating the amplitude of the electromagnetic field, and receive data and commands in a similar way. Simple commands will enable write to EEPROM, to update the password, to read a specific memory area, and to reset the logic.The coil of the tuned circuit is the only external component required, all remaining functions are integrated in the chip. The only difference between EM4150 and EM4350 is that EM4150 comes with standard sized pads, whereas EM4350 comes with oversized (mega) pads, ideal for use with bumps on die (Fig. 27). Features□ 1 KBit of EEPROM organized in 32 words of 32 bits □32 bit Device Serial Number (Read Only Laser ROM) □32 bit Device Identification (Read Only Laser ROM) □Power-On Reset sequence□Power Check for EEPROM write operation□User defined Read Memory Area at Power On□User defined Write Inhibited Memory Area□User defined Read Protected Memory Area□Data Transmission performed by Amplitude Modulation□Two Data Rate Options 2 KBd (Opt64) or 4 KBd (Opt32)□Bit Period = 64 or 32 periods of field frequency□170 pF ± 2% on chip Resonant Capacitor□-40 to +85°C Temperature range□100 to 150 kHz Field Frequency range□On chip Rectifier and Voltage Limiter□No external supply buffer capacitance needed due tolow power consumptionApplications□ Ticketing□Automotive Immobilizer with rolling code□High Security Hands Free Access Control□Industrial automation with portable database□Manufacturing automation□ Prepayment DevicesTypical Operating ConfigurationFig. 1Pin AssignmentFig. 2Absolute Maximum RatingsParameter Symbol ConditionsMaximum AC peak current induced on COIL1 and COIL2I COIL ± 30 mAPower Supply V DD -0.3 to 6.0V Maximum voltage other pads V max V DD + 0.3VMinimum voltage other pads V min V SS – 0.3V Storage temperatureT store-55 to °125°CElectrostatic discharge maximum to MIL-STD-883C method 3015 V ESD 1000VStresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.Handling ProceduresThis device has built-in protection against high static voltages or electric fields; however, anti-static precautions should be taken as for any other CMOS component.Unless otherwise specified, proper operation can onlyoccur when all terminal voltages are kept within the supply voltage range.Operating ConditionsParameter Symbol Min Typ Max Units Operating temperature T op -40 +85 °C Maximum coil currentI COIL 10 mA AC Voltage on coilV coil 1) Vpp Supply frequency f coil 100 150 kHzNote 1): Maximum voltage is defined by forcing 10mA on Coil1-Coil2Fig. 3Electrical CharacteristicsV DD = 2.5V, V SS = 0V, f coil = 125 kHz Sine wave, V coil = 1V pp, T op = 25°C unless otherwise statedParameter SymbolTestConditions MinTypMaxUnitsSupply voltage V DD 2.05.5VMinimum EEPROM write voltage V DDee 2.6VPower Check EEPROM write I PWcheck V DD = 3V 80 µA Supply current / read I rd Read Mode 3.0 5.0 µA Suppy current / write I wr Write mode (V DD = 3V) 40 70 µAModulator ON voltage drop V ON V(COIL1–Vss) and V(COIL2-Vss) I coil = 100µAV(COIL1–Vss) and V(COIL2-Vss) I coil = 5mA 0.50 2.50VVResonance Capacitor C r166.5 170 173.5 pF Power On Reset level high V prh Rising Supply 2.0 2.6 VClock extractor input min. V clkmin Minimum voltage for Clock Extraction 1.0 V pp Clock extractor input max. V clkmax Maximum voltage to detect modulation stop 50 mV pp EEPROM data endurance N cy Erase all / Write all at V DD = 5V 100'000 cycles EEPROM retention T ret T op = 55°C after 100'000 cycles (Note 1) 10 yearsNote 1: Based on 1000 hours at 150°CTiming CharacteristicsV DD = 2.5V, V SS = 0V, f coil = 125 kHz Sine wave, V coil = 1V pp, T op = 25°C unless otherwise statedAll timings are derived from the field frequency and are specified as a number of RF periods.Parameters SymbolTestconditionsValueUnits Option : 64 clocks per bit Opt64Read Bit PeriodLIW/ACK/NACK pattern Duration Read 1 Word Duration Processing Pause TimeWrite Access TimeInitialization TimeEEPROM write time trdbtpatttrdwtpptwatinittweeincluding LIWVDD = 3 V643203200646421123200RF periodsRF periodsRF periodsRF periodsRF periodsRF periodsRF periodsOption : 32 clocks per bit Opt32Read Bit PeriodLIW/ACK/NACK pattern Duration Read 1 Word Duration Processing Pause TimeWrite Access TimeInitialization TimeEEPROM write time trdbtpatttrdwtpptwatinittweeincluding LIWVDD = 3 V321601600323210562624RF periodsRF periodsRF periodsRF periodsRF periodsRF periodsRF periodsRF periods represent periods of the carrier frequency emitted by the transciever unit. For example, if 125 kHz is used :The Read bit period (Opt64) would be : 1/125'000*64 = 512 µs, and the time to read 1 word : 1/125'000*3200 = 25.6 ms. The Read bit period (Opt32) would be : 1/125'000*32 = 256 µs, and the time to read 1 word : 1/125'000*1600 = 12.8 ms. ATTENTIONDue to amplitude modulation of the coil-signal, the clock-extractor may miss clocks or add spurious clocks close to the edges of the RF-envelope. This desynchronisation will not be larger than ±3 clocks per bit and must be taken into account when developing reader software.Block DiagramFig. 5Standard Read ModeAfter a Power-On Reset and upon completion of a command, the chip will execute the Standard Read Mode, in which it will send data continuously, word by word from the memory section defined between the First Word Read (FWR) and Last Word Read (LWR). When the last word is output, the chip will continue with the first word until the transceiver sends a request. If FWR and LWR are the same, the same word will be sent repetitively. The Listen Window (LIW) is generated before each word to check if the transceiver is sending data. The LIW has a duration of 320 (160 opt 32) periods of the RF field. FWR and LWR have to be programmed as valid addresses (FWR ≤ LWR and ≤ 33).The words sent by the EM4150 comprise 32 data bits and parity bits. The parity bits are not stored in the EEPROM, but generated while the message is sent as described below. The parity is even for rows and columns, meaning that the total number of "1's" is even (including the parity bit).Word Organisation (Words 0 to 32)When a word is read protected, the output will consist of 45 bits set to logic "0". The password has to be used to output correctly a read protected memory area.Word Organisation (Word 33)C0 ID2 R0 CK0 PC0C1ID3R1CK1PC1C2ID4R2CK2PC2C3ID5R3CK3PC3C4ID6R4CK4PC4C5ID7R5CK5PC5ID0ID8R6CK6PC6ID1ID9R7CK7PC7P0P1P2P3: P4150 Code set to Hexadecimal 32: Version Code: EM reserved, and Check bitsC0 ID0 R0- C5- ID9- R7 / CK0 - CK7Fig. 7bReceive ModeTo activate the Receive Mode, the Transceiver sends to the chip the RM pattern (while in the modulated phase of a Listen Window LIW). The EM4150 will stop sending data upon reception of a valid RM. The chip then expects a command. The RM pattern consists of 2 bits "0" sent by the transceiver. The first bit "0" transmitted is to be detected during the 64 (32 opt 32) periods where theFig. 9 CommandsThe commands are composed of nine bits : eight data bits and one even parity bit (total amount of "ones" isFig. 10 Selective Read ModeThe Selective Read Mode is used to read other data than that defined between FWR and LWR. To enter Selective Read Mode, the Transceiver has to send during LIW a Receive mode pattern (RM) to turn the EM4150 in Receive Mode. Then the Selective Read Mode Command is sent by the transceiver followed by the First and Last addresses to be read. The FWR and LWR are then replaced by the new addresses and the chip is operating in the same way as the Standard Read Mode. The control word is not modified by this command, and the next standard read mode operation will work with original FWR and LWR (Selected area is read once and then the chip returns to Standard Read Mode).To read words which are Read Protected, a Login command has to be sent by the transceiver prior to the Selective Read command. The Login command is to be used only once for all subsequent commands requiring a password.Selective Read Mode cont.The Selective Read mode command is followed by a single 32-bit word containing the new first and last addresses. Bits 0 to 7 correspond to the First Word Read and bits 8 to 15 correspond to the Last Word Read. Bits 16 to 31 have to be sent but are not used in the chip. The parities must be sent according to the word organisation as described in fig.7. Note that bit 31 is transmitted first.To read the device Identification or the Serial Number, the Selective Read Command allows direct access to the Laser programmed words. These words can also be addressed in the standard read mode by selecting the addresses accordingly.If bit 16 of the control word is disabled (Password Check ON/OFF), the Login is still mandatory to modify the Protection Word, the Control Word, and the Password, but not to write in the EEPROM which is not write inhibited. In order to modify a write inhibited word, the Protection word has to be modified first. The Read protected area always requires the Login to be read. If the Write Protection Word is write protected, the write protection configuration is locked.Write PasswordWhen a Write Password command is received, the chip next expects information on the actual valid password. The chip sends back an ACK pattern if the password is correct. Then the chip expects the new password consisting of 32 bits + parity bit to be stored in the EEPROM. The chip will respond with an ACK pattern for a correct reception of data upon reception of the new password, and then will send another acknowledge pattern (ACK) to announce that the data is stored in the EEPROM. The Read after Write function has no effect on this command. If the password is wrong or the transmission is faulty, the chip will : send a NAK pattern; return to the Standard Read Mode; and, the password will remain the same. (Refer to Write Word for password data structure).Fig. 16 The Write Word command is followed by the address and data. The address consists of a 9 bit block containing 8 data bits and 1 even parity bit. Only 6 bits from the data section are used for the word addressing, and the first three bits sent must be "0". The data consists of 4 times 9 bit blocks, each block consisting of 8 data bits and 1 associated even parity bit and one additional block consisting of 8 column parity bits and "0" as stop bit (Refer to fig. 7)Write Word (cont.)After reception of the command, the address, and the data, the EM4150 will check the parity, the write protection status, the Login status, and also if the available power from the RF field is sufficient. If all the conditions are satisfied, an acknowledge pattern (ACK) will be issued afterward and the EEPROM writing process will start. At the end of programming, the chip will send an Acknowledge pattern (ACK). If at least one of the checks fails, the chip will issue a no acknowledge pattern (NAK) instead of ACK and return to the Standard Read Mode. The Transceiver will keep the RF field permanently "ON" during the whole writing process time.The Read After Write function (bit 17 of Control word) controls the mode of operation following a write operation. When "ON" the latest written word will be read out and output next to the ACK pattern and two Listen Windows (LIW-LIW) even if the word is read protected. When "OFF", the ACK is followed immediately by a LIW-LIW and FWR. The last written word is not output.If a request from the transceiver to return in receive mode (RM) is generated during the LIW, another word can be written in. Otherwise, the EM4150 will return in the Standard Read Mode.Fig. 17Power On Reset (POR)When the EM4150 with its attached coil enters an electromagnetic field, the built in AC/DC converter will supply the chip. The DC voltage is monitored and a Reset signal is generated to initialise the logic. The contents of the Control word and Protection word will be downloaded to enable the functions (INIT). The Power On Reset is also provided in order to make sure that the chip will start issuing correct data. Hysteresis is providedData ExtractorThe transceiver generated field will be amplitude modulated to transmit data to the EM4150. The Data extractor demodulates the incoming signal to generate logic levels, and decodes the incoming data.ModulatorThe Data Modulator is driven by the serial data output from the memory which is Manchester encoded. The modulator will draw a large current from both coil terminals, thus amplitude modulating the RF field according to the memory data.AC/DC Converter and Voltage LimiterThe AC/DC converter is fully integrated on chip and will extract the power from the incident RF field. The internal DC voltage will be clamped to avoid high internal DC voltage in strong RF fields.Resonance CapacitorThe Resonance Capacitor is integrated, and its tolerance is adjusted to ± 2% over the whole production.Communication from Transponder to the Transceiver ( READ MODE)The EM4150 modulates the amplitude of the RF field to transmit data to the transceiver. Data are output serially from theFig. 22 Communication from the Transceiver to the Transponder (RECEIVE MODE)The EM4150 can be switched to the Receive Mode ONLY DURING A LISTEN WINDOW. The Transceiver is synchronized with the incoming data from the transponder and expects a LIW before each word. During the phase where the chip has its modulator "ON" (64/32 periods of RF [Opt64/Opt32] ), the transceiver has to send a bit "0". A certain phase shift in the read path of the transceiver can be accepted due to the fact that when entering Receive Mode, the Transceiver becomes the Master.At reception of the first "0", the chip immediately stops the LIW sequence and then expects another bit "0" to activate the receive mode. Once the EM4150 has received the first bit "0", the transceiver is imposing the timing for synchronisation. The EM4150 turns "ON" its modulator at the beginning of each frame of a bit period. To send a logic "1" bit, the transceiver continues to send clocks without modulation. After half a bit period, the modulation device of the EM4150 is turned "OFF" allowing recharge of the internal supply capacitor. To send a logic "0" bit, the transceiver stops sending clocks (100% modulation) during the first half of a bit period. The transceiver must not turn "OFF" the field after 7/4 clocks of the bit period (Opt64/Opt32). The field is stopped for the remaining first half of the bit period, and then turned "ON" again for the second half of the bit period. The 32rd/16th clock (Opt64/Opt32) defines the end of the bitTo ensure synchronisation between the transceiver and the transponder, a logic bit set to "0" has to be transmitted at regular intervals. The RM pattern consists of two bits set to "0" thus allowing initial synchronisation. In addition, the chosen data structure contains even parity bits which will not allow more than eight consecutive bits set to logic "1" where no modulation occurs.Communication from the Transceiver to the Transponder (RECEIVE MODE) (cont.)While the transceiver is sending data to the transponder, two different modulations will be observed on both coils. During the first half of the bit period, the EM4150 is switching "ON" its modulation device causing a modulation of the RF field. This modulation can also be observed on the transceiver's coil. The transceiver sending a bit "0" will switch "OFF" the field, causing a 100% modulation being observed on the transponder coil.Fig. 23Pad DescriptionPad Name Function1 2 3 4 5 6 7 8 9COIL1 VPOS TEST_IN VDDTEST_OUT TESTTEST_CLK VSS COIL2Coil Terminal 1 Internal supplyTest input with pull-downPositive Internal Supply Voltage Test OutputTest Mode Input with pull-down Test Clock input with pull-down Negative Internal Supply Voltage Coil terminal 2Fig. 24 Fig. 25Chip DimensionsFig. 26 Fig. 27Ordering InformationDie FormThis chart shows general offering; for detailed Part Number to order, please see the table “Standard Versions” below.WS = Sawn Wafer/Frame 7 = 7 mils (178um)WT = Sticky Tape11 = 11 mils (280um)WP = Waffle Pack (note 1)21 = 21 mils (533um)27 = 27 mils (686um)Packaged Devices This chart shows general offering; for detailed Part Number to order, please see the table “Standard Versions” below.CI2LC = CID Pack, 2 long pins (2.5mm), in bulk CI2SB = CID Pack, 2 short pins (1.25mm), in tape CI2SC = CID Pack, 2 short pins (1.25mm), in bulk CB2RC = PCB Package, 2 pins, in bulk SO8A = SO-8 Package, in stick (note 1)Remarks:• For ordering please use table of “Standard Version” table below.• For specifications of Delivery Form, including gold bumps, tape and bulk, as well as possible other delivery form orpackages, please contact EM Microelectronic-Marin S.A.• Note 1: This is a non-standard package. Please contact EM Microelectronic-Marin S.A for availability.• Note 2: EM4350 is preferably used with gold bumps. Use of EM4150 with gold bump together with direct technology issubject to license, please contact EM Sales Office.Standard Versions & Samples: For samples please order exclusively:Part Number Bit coding Cycle/bitPads PackageDeliveryFormEM4150A6CI2LC Manchester64Standard CIDpackage, 2 pins (length 2.5mm) bulkEM4150A6CB2RC Manchester 64 Standard PCB Package, 2 pins bulkThe versions below are considered standards and should be readily available. For other versions or other delivery form, please contact EM Microelectronic-Marin S.A. Please make sure to give complete part number when ordering, without spaces between characters.Part Number Bit coding Cycle/bitPads Package/DieForm DeliveryForm/ BumpingEM4150A5CB2RC Manchester 32 Standard PCB Package, 2 pins bulkEM4150A5CI2LC Manchester32StandardCIDpackage, 2 pins (length 2.5mm) bulkEM4150A5CI2SC Manchester32StandardCIDpackage, 2 pins (length 1.25mm) bulkEM4150A6CB2RC Manchester 64 Standard PCB Package, 2 pins bulkEM4150A6CI2LB Manchester64StandardCIDpackage, 2 pins (length 2.5mm) tapeEM4150A6CI2LC Manchester64StandardCIDpackage, 2 pins (length 2.5mm) bulkEM4150A6CI2SB Manchester64StandardCIDpackage, 2 pins (length 1.25mm) tapeEM4150A6CI2SC Manchester64StandardCIDpackage, 2 pins (length 1.25mm) bulkEM4150A6SO8A Manchester64StandardSO-8package stickEM4150A6WS6 Manchester 64 Standard Sawn wafer, 6 mils no bumpsEM4150A6WS7 Manchester 64 Standard Sawn wafer, 7 mils no bumpsEM4150A6WW27 Manchester 64 Standard Unsawn wafer, 27 mils no bumpsEM4150A6WW7 Manchester 64 Standard Unsawn wafer, 7 mils no bumpsEM4150XXYYY-%%% Manchester 32/64 Standardcustom customEM4350A6WP11E Manchester 64 Mega Die in waffle pack, 11 mils with gold bumpsEM4350A6WS11E Manchester 64 Mega Sawn wafer, 11 mils with gold bumpsEM4350A6WT11E Manchester 64 Mega Die on sticky tape, 11 mils with gold bumpsEM4350XXYYY-%%% Manchester 32/64 Mega custom customProduct SupportCheck our Web Site under Products/RF Identification section.Questions can be sent to info@EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.© EM Microelectronic-Marin SA, 08/04, Rev. F。

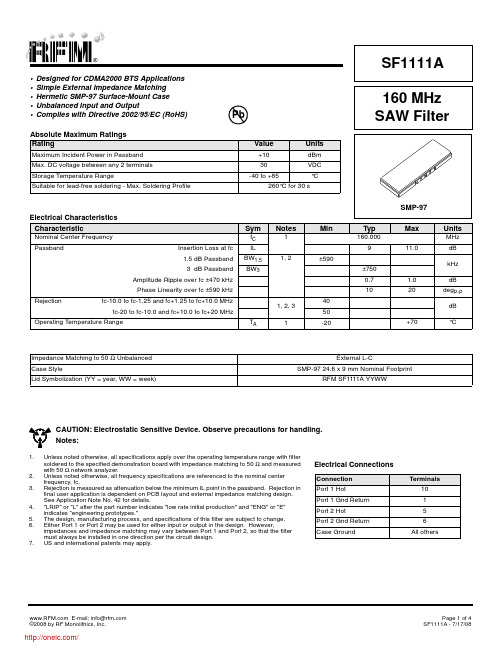

SF1111A;中文规格书,Datasheet资料

Electrical Connections

Connection Port 1 Hot Port 1 Gnd Return Port 2 Hot Port 2 Gnd Return Case Ground

Terminals 10 1 5 6

All others

E-mail: info@ ©2008 by RF Monolithics, Inc.

/

Page 1 of 4 SF1111A - 7/17/08

CH1 S11

1 U FS

1 : 52 . 115

-12 . 555

160 . 00 000 MHz

SF1111A DEMO # 3

FULL 2 PORTS CAL.

79 . 231 pF

PRm

1

Cor Full

Fe-Ni-Co Alloy Electroless Nickel Plate (8-11% Phosphorus) 100-200 uInches Thick

Al2O3 Ceramic

Case Dimensions

Dimension

A B C D E H M N P

Min

24.41 8.80

mm

Nom

SPAN

2 . 000 MHz

AO4459中文资料

SymbolTyp Max 33406275R θJL 1824Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-Ambient ASteady-State °C/W AO4459AO4459SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.5-1.85-2.5V I D(ON)-30A 3846T J =125°C53685872m Ωg FS 11S V SD -0.78-1V I S-3.5A C iss 668830pF C oss 126pF C rss 92pF R g69ΩQ g (10V)12.716nC Q g (4.5V) 6.4nC Q gs 2nC Q gd 4nC t D(on)7.7ns t r 6.8ns t D(off)20ns t f 10ns t rr 2230ns Q rr15nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.DYNAMIC PARAMETERS Maximum Body-Diode Continuous CurrentGate resistanceV GS =0V, V DS =0V, f=1MHzV GS =0V, V DS =-15V, f=1MHz Input Capacitance Output Capacitance Turn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.5Ω, R GEN =3ΩTurn-Off Fall TimeTurn-On DelayTime SWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-6.5Am ΩV GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-6.5AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward VoltageI DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-24V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =-6.5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-6.5AReverse Transfer Capacitance I F =-6.5A, dI/dt=100A/µs A: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using < 300µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev0 Sept 2006AO4459AO4459。

AOD444 PDF规格书

In descending order D=0.5, 0.3, 0.1, 0.05, 0.02, 0.01, single pulse

1

0.1 PD Ton 0.0001 0.001 0.01 0.1 1 10 T 100 1000

Байду номын сангаас

0.01

Single Pulse

0.001 0.00001

Pulse Width (s) Figure 16: Normalized Maximum Transient Thermal Impedance (Note H)

Single Pulse 0.0001

Pulse Width (s) Figure 11: Normalized Maximum Transient Thermal Impedance (Note F)

AOD444 N-Channel MOSFET

■ Typical Characterisitics

10000

TA=25°C

1000

Power (W)

100

10

1 0.00001

0.001

0.1

10

1000

Pulse Width (s) Figure 15: Single Pulse Power Rating Junction-toAmbient (Note H)

D=Ton/T TJ,PK=TA+PDM.ZθJA.RθJA RθJA=60°C/W

AOD444 N-Channel MOSFET

■ Electrical Characteristics Ta = 25℃

Parameter Drain-Source Breakdown Voltage Zero Gate Voltage Drain Current Gate-Body Leakage Current Gate Threshold Voltage Static Drain-Source On-Resistance On State Drain Current Forward Transconductance Input Capacitance Output Capacitance Reverse Transfer Capacitance Gate Resistance Total Gate Charge (10V) Total Gate Charge (4.5V) Gate Source Charge Gate Drain Charge Turn-On DelayTime Turn-On Rise Time Turn-Off DelayTime Turn-Off Fall Time Body Diode Reverse Recovery Time Body Diode Reverse Recovery Charge Maximum Body-Diode Continuous Current Diode Forward Voltage Symbol VDSS IDSS IGSS VGS(th) RDS(On) ID(ON) gFS Ciss Coss Crss Rg Qg Qgs Qgd td(on) tr td(off) tf trr Qrr IS VSD IS=1A,VGS=0V IF= 12A, dI/dt= 100A/μs VGS=10V, VDS=30V, RL=2.5Ω,RG=3Ω VGS=10V, VDS=30V, ID=12A VGS=0V, VDS=0V, f=1MHz VGS=0V, VDS=30V, f=1MHz Test Conditions ID=250μA, VGS=0V VDS=48V, VGS=0V VDS=48V, VGS=0V, TJ=55℃ VDS=0V, VGS=±20V VDS=VGS , ID=250μA VGS=10V, ID=12A VGS=10V, ID=12A VGS=4.5V, ID=6A VGS=10V, VDS=5V VDS=5V, ID=20A 360 40 16 0.6 7.5 3.8 1.2 1.9 4.2 3.4 16 2 27 30 12 1 35 nC A V ns 30 14 450 61 27 540 80 40 2 10 5 nC Ω pF TJ=125℃ 1 Min 60 1 5 ±100 3 60 100 85 A S mΩ Typ Max Unit V uA nA V

ADR445BRZ中文资料

元器件交易网

ADR440/ADR441/ADR443/ADR444/ADR445

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 Pin Configurations ........................................................................... 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3

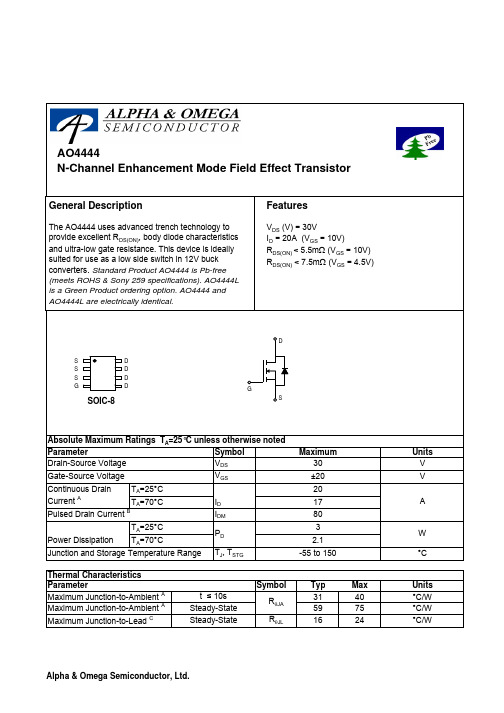

AO4444中文资料

SymbolTyp Max 31405975R θJL 1624Maximum Junction-to-Ambient A Steady-State °C/W Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-Ambient A t ≤ 10s R θJA °C/W AO4444AO4444SymbolMin TypMaxUnits BV DSS 30V 1T J =55°C5I GSS 100nA V GS(th)1 1.83V I D(ON)60A 3.9 5.5T J =125°C5.16.25.17.5m Ωg FS 106S V SD 0.721V I S4A C iss 32003840pF C oss 590pF C rss 414pF R g0.540.7ΩQ g (10V)6376nC Q g (4.5V)3340nC Q gs 8.6nC Q gd 17.6nC t D(on)12ns t r 15.5ns t D(off)40ns t f 14ns t rr 3441ns Q rr30nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery Charge I F =20A, dI/dt=100A/µsGate Source Charge V GS =0V, V DS =15V, f=1MHz SWITCHING PARAMETERS Total Gate Charge Total Gate Charge Gate resistanceV GS =0V, V DS =0V, f=1MHzV GS =4.5V, V DS =15V, I D =20ATurn-On DelayTime Turn-On Rise Time Turn-Off DelayTime Gate Drain Charge Maximum Body-Diode Continuous CurrentInput Capacitance Output Capacitance DYNAMIC PARAMETERS m ΩV GS =4.5V, I D =15AI S =1A,V GS =0V V DS =5V, I D =20AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward Voltage I DSS µA Gate Threshold Voltage V DS =V GS I D =250µA V DS =24V, V GS =0VV DS =0V, V GS = ±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Turn-Off Fall TimeBody Diode Reverse Recovery TimeI F =20A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =250µA, V GS =0V V GS =10V, V DS =5V V GS =10V, I D =20AReverse Transfer Capacitance V GS =10V, V DS =15V, R L =0.75Ω, R GEN =3ΩA: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev 1 : June 2005AO4444AO4444。

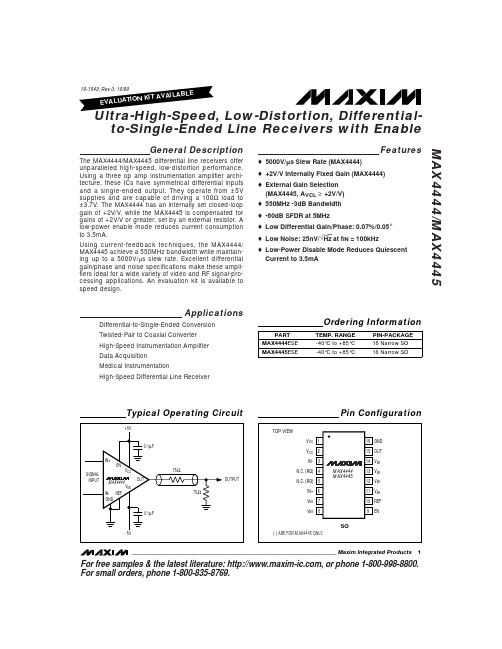

MAX4444中文资料

Features

o 5000V/µs Slew Rate (MAX4444) o +2V/V Internally Fixed Gain (MAX4444) o External Gain Selection

(MAX4445, AVCL ≥ +2V/V) o 550MHz -3dB Bandwidth o -60dB SFDR at 5MHz o Low Differential Gain/Phase: 0.07%/0.05° o Low Noise: 25nV/√Hz at fIN = 100kHz o Low-Power Disable Mode Reduces Quiescent

10

55

0.25

45

82

170

2

(1 + 600/RG)

0.5

2

2.6

8

0.003

±3.4 ±3.7

±3.3 ±3.6

90

120

53

70

40

55

1.8

0.8

2

2.2

10

2.6

10

41

55

3.5

5.5

ADR435中文资料

TP 1

8 TP

VIN 2 ADR43x 7 NC

TOP VIEW NC 3 (Not to Scale) 6 VOUT

GND 4

5 TRIM

NC = NO CR Suffix)

All versions are specified over the extended industrial temperature range (−40°C to +125°C).

PIN CONFIGURATIONS

TP 1

8 TP

VIN 2 ADR43x 7 NC

NC

3

TOP VIEW (Not to Scale)

6

VOUT

GND 4

5 TRIM

NC = NO CONNECT

04500-0-001

Figure 1. 8-Lead MSOP (RM Suffix)

04500-0-041

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

ADG441BR中文资料

85 110 45 60 30 1 6 60 100 4 4 16

170 80

85 110 45 60 30 1 6 60 100 4 4 16

170 80

RL = 1 kΩ, CL = 35 pF; VS = ± 10 V; Test Circuit 4 RL = 1 kΩ, CL = 35 pF; VS = ± 10 V; Test Circuit 4 RL = 1 kΩ, CL = 35 pF; VS = 0 V, RS = 0 Ω, CL= 1 nF; VDD = +15 V, VSS = –15 V; Test Circuit 5 RL = 50 Ω, CL = 5 pF; f = 1 MHz; Test Circuit 6 RL = 50 Ω, CL = 5 pF; f = 1 MHz; Test Circuit 7 f = 1 MHz f = 1 MHz f = 1 MHz VDD = +16.5 V, VSS = –16.5 V Digital Inputs = 0 V or 5 V

± 0.01 ± 0.5 ± 0.01 ± 0.5 ± 0.08 ± 0.5

±3 ±3 ±3 2.4 0.8 ± 0.00001 ± 0.5

± 0.01 ± 0.5 ± 0.01 ± 0.5 ± 0.08 ± 0.5

± 20 ± 20 ± 40 2.4 0.8 ± 0.00001 ± 0.5

VIN = VINL or VINH

1. Extended Signal Range The ADG441/ADG442/ADG444 are fabricated on an enhanced LC2MOS, trench-isolated process, giving an increased signal range that extends to the supply rails. 2. Low Power Dissipation 3. Low RON 4. Trench Isolation Guards Against Latch Up A dielectric trench separates the P and N channel transistors thereby preventing latch up even under severe overvoltage conditions. 5. Break-Before-Make Switching This prevents channel shorting when the switches are configured as a multiplexer. 6. Single Supply Operation For applications where the analog signal is unipolar, the ADG441/ADG442/ADG444 can be operated from a single rail power supply. The parts are fully specified with a single +12 V power supply.

CAV444

上海芸生微电子有限公司 上海 108-009 信箱 邮政编码:201108

E–Mail: zzhiyun@

November 2008 - Rev 1.0 - Page 3/11

电容式信号线性转换电压输出接口集成电路

测量原理

CAV444

CAV444 是一个可测量多种电容式传感器信号的线性转换比例电压输出的接口集成电路。它 同时具有信号采集、处理和差分电压输出的功能,还带有一个内置的温度传感器。电容信号 ΔCM = CM,max– CM,min 和输出电压是线性关系,这里 CM,min 是电容传感器 CM 的本底电容, CM,max 是电容传感器的最大电容值。

电容式信号线性转换电压输出接口集成电路

C M , max

CAV444

这里要求: CW

。. CW 是 f/U 频率电压转换电路电容,它的取值与 CM 有一定相关 1,6 性。电阻 RCM 和 RCW 与充放电流大小有关,通常取固定数值 RCM = 250kΩ 和 RCW = 500kΩ。 从公式(5)可以看出,输出电压 VOUT*是测量电容 CM 的函数 VOUT* = f(CM),并且是线性函数 关系。此时其他所有的变量都已设定为固定不变数值了。

VO UT

VREF 2,5V

CM CM Min CM Max CM

图 4:对地的输出电压 VOUT*

从图 4 中看出,输出电压 VOUT*被抬高了一个数值 VREF。

信号传递函数(带有附加的零点调准电路)

为了使输出信号可调整,就要考虑传递函数公式(5) 中的零点输出的调整。通过一个附加 的零点调准电路(见图 5),使传递函数公式(5)变换为下式: VOUT VDIFF VREF A VTPAS B VREF 其中二个调准系数 A(满度)和 B(零点)由下式表示: (6)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Low dropout operation: 500 mV Input range: (VOUT + 500 mV) to 18 V High output source and sink current: +10 mA and −5 mA Wide temperature range: −40°C to +125°C

Figure 1. 8-Lead SOIC_N (R-Suffix)

TP 1 VIN 2 NC 3 GND 4

ADR440/ ADR441/ ADR443/ ADR444/ ADR445

TOP VIEW

(Not to Scale)

8 TP 7 NC 6 VOUT 5 TRIM

NOTES 1. NC = NO CONNECT 2. TP = TEST PIN (DO NOT CONNECT)

元器件交易网

Ultralow Noise, LDO XFET® Voltage References with Current Sink and Source ADR440/ADR441/ADR443/ADR444/ADR445

FEATURES

Ultralow noise (0.1 Hz to 10 Hz) ADR440: 1 μV p-p ADR441: 1.2 μV p-p ADR443: 1.4 μV p-p ADR444: 1.8 μV p-p ADR445: 2.25 μV p-p

Figure 2. 8-Lead MSOP (RM-Suffix)

05428-002

Offered in two electrical grades, the ADR44x family is available in 8-lead MSOP and narrow SOIC packages. All versions are specified over the extended industrial temperature range of −40°C to +125°C.

APPLICATIONS

Precision data acquisition systems High resolution data converters Battery-powered instrumentations Portable medical instruments Industrial process control systems Precision instruments Optical control circuits

元器件交易网

ADR440/ADR441/ADR443/ADR444/ADR445

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 Pin Configurations ........................................................................... 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3

The ADR44x family has the capability to source up to 10 mA of output current and sink up to 5 mA. It also comes with a trim terminal to adjust the output voltage over a 0.5% range without compromising performance.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

The XFET references offer better noise performance than buried Zener references, and XFET references operate off low supply voltage headroom (0.5 V). This combination of features makes the ADR44x family ideally suited for precision signal conversion applications in high-end data acquisition systems, optical networks, and medical applications.

1.2

ADR444A 4.096

5

ADR444B 4.096

1.6

ADR445A 5.000

6

ADR445B 5.000

2

Temperature Coefficient (ppm/°C) 10 3 10 3 10 3 10 3 10 3

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Table 1. Selection Guide

Model

Output Voltage (V)

Initial Accuracy, ± (mV)

ADR440B 2.048

1

ADR441A 2.500

3

ADR441B 2.500

1

ADR443A 3.000

4

ADR443B 3.000

ADR440 Electrical Characteristics............................................. 3 ADR441 Electrical Characteristics............................................. 4 ADR443 Electrical Characteristics............................................. 5 ADR444 Electrical Characteristics............................................. 6 ADR445 Electrical Characteristics............................................. 7 Absolute Maximum Ratings............................................................ 8 Thermal Resistance ...................................................................... 8 ESD Caution.................................................................................. 8 Typical Performance Characteristics ............................................. 9

GENERAL DESCRIPTION

The ADR44x series is a family of XFET voltage references featuring ultralow noise, high accuracy, and low temperature drift performance. Using Analog Devices, Inc., patented temperature drift curvature correction and XFET (eXtra implanted junction FET) technology, voltage change vs. temperature nonlinearity in the ADR44x is greatly minimized.