KSZ9031RNX datasheet

KSZ8795 Evaluation Board 用户指南说明书

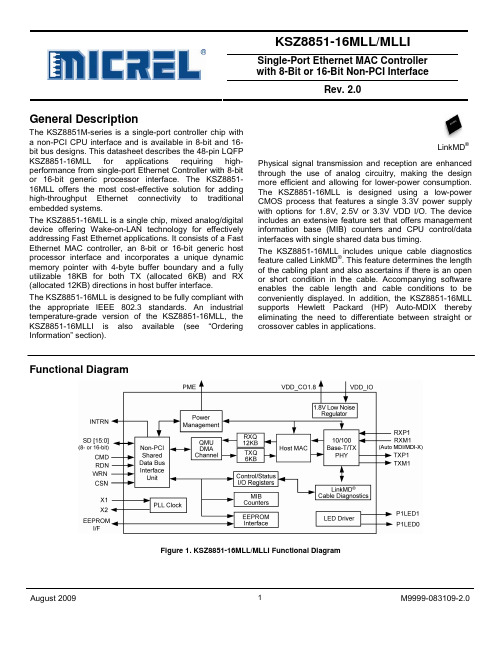

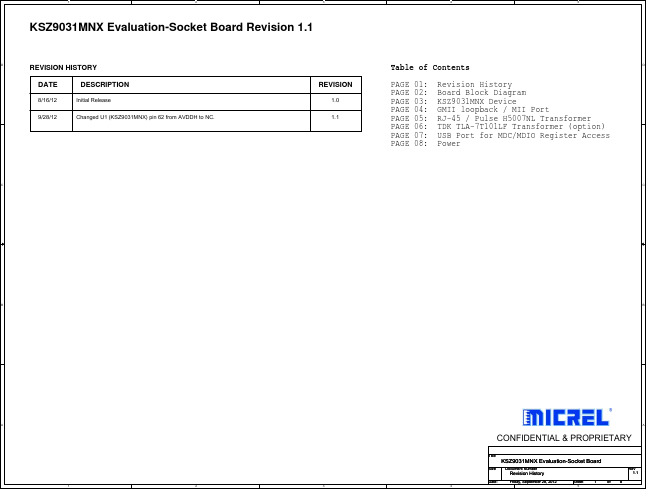

KSZ8795-POE-EVAL Board(KSZ8795CLX+KSZ9031RNX)Demo Evaluation Board User’s GuideKSZ8795 Family Integrated 5-port Managed Switch with 4 10/100 Copper Ports and Port 5 Gigabit port Rev 1.0 January 2015Table of contents1.0 Introduction (4)2.0 Features (4)3.0 Evaluation Kit Contents (4)4.0 Hardware Description (5)4.1 Strap in Mode (6)4.2 Feature Setting Jumpers (7)4.3 SPI Mode (8)4.4 10/100 Ethernet Ports (8)4.4 10/100/1000 Gigabit Ports (8)4.5 LED indicators (9)5.0 Software Tools Description (10)5.1 Introducing Application Software Tools (10)5.2 Window Driver Installation First (10)5.3 Installation Application Software Tools (13)5.4 DOS SPI Tool (15)5.5 Window SPI Software Tool (16)5.6 LinkMD Software Tool (17)6.0 Reference Documents (19)7.0 Bill of Material (19)8.0 Schematics (19)List of Figures and TablesFigure 1 KSZ8795-POE-EVAL Board (5)Figure 2 KSZ8795-POE-EVAL Board Block Diagram (6)Table 1 General Setting Jumpers (7)Table 2 Power Setting Jumpers (7)Table 3 LED Modes (9)Revision History1.0 IntroductionThe KSZ8795 family is Micrel Operations new generation integrated 5-port switch with Gigabit up-link. The KSZ8795CLX is one of KSZ8795 family. KSZ8795CLX contains four MAC/PHYs for four copper ports and one GMAC5 interface with configurable GMII/RGMII/MII/RMII interfaces. The device had been designed with cost sensitive systems in mind but still offers a multitude of new features such as port based security ACL filtering, 802.1az EEE, LinkMD and so on. Also support port and tag based VLAN; QoS priority; SPI and MDC/MDIO interfaces for the registers access. The KSZ8795 family is an excellent choice in broadband gateway applications, integrated broadband router applications, industrial automatic, automotive, etc. fields and as a standalone switch. The KSZ8795-POE-EVAL board is designed to allow the user to experience Gigabit up-link with KSZ9031 Gigabit PHY to Gigabit port of any processor board directly, and can provide PoE PSE power to other four ports. Other rich feature set can be evaluated on this board. The evaluation board is highly configurable and easy to use.2.0 Features∙Micrel KSZ8795 Integrated 5-port 10/100 Managed Ethernet Switch∙ 4 RJ-45 Jacks for 10/100Base-T/TX Ethernet LAN with Corresponding Isolation Magnetics. ∙Auto MDI/MDIX on All Ports.∙Port 5 SW5-RGMII hook-up with a KSZ9031RNX GPHY and provide a Gigabit port.∙Easily set to different VDDIO of 3.3V, 2.5V and 1.8V by jumpers.∙ 1 USB Port Interface Configurable to Emulate an SPI Interface for all registers access by using Window GUI and DOS based software tools.∙ 2 LEDs per Port with 5 LED sets to indicate the Status and Activity for 4 fast Ethernet ports and1 Gigabit port.∙The board powered can be used by a 12V DC power supply.3.0 Evaluation Kit ContentsThe KSZ8795-POE-EVAL Evaluation kit includes the following:∙KSZ8795-POE-EVAL Evaluation Board Rev. 1.x∙KSZ8795-POE-EVAL Ev aluation Board User’s Guide Rev 1.x∙Micrel SPI Configuration Software tools∙KSZ8795-POE-EVAL Evaluation Board Schematics and BOM∙KSZ8795-POE-EVAL PCB file, Gerber file and IBIS model∙The software, reference schematics and other design information will be found in the Design Kit (Design Package) of the KSZ8795 Ethernet switch products on Micrel website.(Contact your Micrel FAE for the latest schematic).∙One 12V DC power supply.∙The USB cable is not included.4.0 Hardware DescriptionThe KSZ8795-POE-EVAL evaluation board is in a compact form factor and can sit on a bench near a computer with USB connector. There are two options for configuration: strap in mode; SPI mode and Strap-in mode that is easily done with on board jumper options. SPI mode is accomplished through a built in USB port interface. You can configure the KSZ8795 device on board by the USB port. Using Micrel SPI software and your PC, you can access the KSZ8795’s full feature set registers by the USB to SPI interface. The board also features RGMII to hook up a KSZ9031RNX as a Gigabit uplink for Gigabit port 5.The KSZ8795-POE-EVAL evaluation board is easy to use. There are programmable LED indicators for link and activity on all ports and a power LED. A manual reset button allows the user to reset the board without removing the power plug. A standard 12VDC power supply can be used by the power jack so that the user can supply power from any 110-240 Volt AC wall or bench socket.Figure 1 KSZ8795-POE-EVAL BoardFigure 2 KSZ8795-POE-EVAL Board Block Diagram4.1 Strap in ModeStrap in configuration mode is the quickest and easiest way to get started. In the default mode, the KSZ8795 acts as a stand-alone 4 port switch and one RGMII up-link. The user has to simply set the board’s configuration jumpers to the desired settings and apply power to the board. The user can also change jumper settings while power is applied to the board and press the convenient manual reset button for the new settings to take effect. Note that even if there is no external strap in values are set, internal pull up and pull down resistors will set the KSZ8795 default configuration. Section 4.1.1 covers each jumper on the board and describes its function.The KSZ8795 will start automatically after power up or reset.4.2 Feature Setting JumpersThe evaluation board provides jumpers to allow the user to easily set strap in configurations for the KSZ8795. Tables below describe the jumpers and their functions in the open or closed state.Table 1 General Setting JumpersTable 2 Power Setting Jumpers4.3 SPI ModeFrom SPI interface to the KSZ8795, use a USB to SPI converter that allows accessing all of the KSZ8795 features and registers. The user can easily access the SPI interface using a computer connected to the evaluation board’s USB port interface. Micrel provides a Windows GUI based program for the user to evaluate the KSZ8795’s full feature set. KSZ8795’s SP I interface will be able to access all static MAC table, the VLAN table, dynamic MAC address table, the MIB counters and all enhanced features.To prepare the KSZ8795CLXD-EVAL board for SPI mode configuration follow these steps:1. Copy the Micrel provided SPI interface software on your computer.2. KSZ8795-POE-EVAL board is fixed at SPI slave mode.3.Connect the computer’s USB port to the KSZ8795CLXD-EVAL board with a USB port cable.4.Connect the 12V DC power supply to J7 of the KSZ8795-POE-EVAL board.5.Open the Windows and navigate to the directory where the Window SPI file is stored. Click itsicon to invoke the software.6.Program the desired settings using the Micrel SPI interface software. See the softwareoperation description section for details.4.4 10/100 Ethernet PortsThere are five 10/100 Ethernet ports on the KSZ8795-POE-EVAL board. The ports J1, J2, J3 and J4 are the standard RJ45 connectors and using CAT-5 cables. Each port can be used as either an uplink or downlink. All ports support Auto-MDI/MDIX, so there is no need for cross over cables. J1 = RJ45 connector for port 1J2 = RJ45 connector for port 2J3 = RJ45 connector for port 3J4 = RJ45 connector for port 4JM1, JM2, JM3, JM4 and JS1, JS2, JS3, JS4 special connectors for Automotive used only.4.4 10/100/1000 Gigabit PortsThere is one KSZ9031RNX with 10/100/1000 Ethernet ports on the KSZ8795-POE-EVAL board. The ports RJ1 is the standard RJ45 connectors for port 5 and can connect to one Gigabit port of a processor platform by using CAT-5 cables. The port supports Auto-MDI/MDIX, so there is no need for the cross over cables.RJ1 = RJ45 connector for port 54.5 LED indicatorsEthernet Port LEDsThere are four columns of LED indicators on the board, one column for each of the four ports. The LED indicators are programmable to two different modes. You can program the LED mode through Register 11 bits [5:4]. The mode definitions are shown in Table below. There are two LEDs per port. The naming convention is “LEDx_y”, where “x” is the port number, and “y” is the number of the LED for that port.Table 3 LED ModesLED1_y are assigned to port 1LED2_y are assigned to port 2LED3_y are assigned to port 3LED4_y are assigned to port 4Gigabit Port LEDThe board also has a Gigabit port LED D3 to indicate the link-up speed for port 5.Green Color: 1G LinkRed Color: 100M LinkOrange Color: 10M LinkPower LEDThe board also has a power LED D7 for the 3.3V power supply. D7 LED indicates Power on and off.5.0 Software Tools Description5.1 Introducing Application Software ToolsThe Design Kit provides some software tools to support SPI access for all registers andMDC/MDIO access for MIIM registers. The installation file is located folders in the software tool directory within subdirectory of Window SPI_MDIO_Tools, this file name is MicrelSwitchPhyTool_x.xx.msi.5.2 Window Driver Installation FirstBefore use the Window based application software tool, the support drivers need to be installed to PC/Laptop first and this installation is just one times only. When connect one standard USB cable with type A and type B connectors between the evaluation board and PC computer first time, the Found New Hardware Wizard window will pop-up and then follow the instructions step by step as below.. Choose ‘No, not this time’ radio button and click the ‘Next’ button.Choose the ‘Install from a list or specific location (Advanced)’ radio button and click the ‘Next’ button.Click the ‘Include this location in the search’ check box, and use ‘Browse’ button to select the‘C:\MicrelEthernetChipConfig\D2XXDriver\CDM 2.02.04 WHQL Certified’ directory and click the ‘Next’ button. The window will install the drivers from this location.Click ‘Finish’ button. The Window will install another driver called ‘USB Serial Converter B’. After the drivers installed, Window Device Manager will show ‘USB Serial Converter A’ and ‘USB Serial Converter B’ as below figure. That means the installation successful.5.3 Installation Application Software ToolsIn the Design Kit, the installation file is located folders in the software tool directory within subdirectory of Window SPI_MDIO_Tools, this file name is MicrelSwitchPhyTool_x.xx.msi. Double click this file name, an installation Window will pop-up and then follow the instructions step by step as below.In this pop-up Window, this application software tools can be assigned to default Micrel directory in above window shown or is assigned to a specified folder what you want. Click ‘Next’ button, next Window will pop-up as below.Click ‘Next’ button to start the installation.Click ‘Close’ button to finish the installation. All application software tools are installed into the default Micrel directory or assigned directory in installation as below.5.4 DOS SPI ToolThis is a simple and powerful tool to access all register. The tool located in the default or assigned folder in the installation. There is an USBSPI.exe file which can be executed directly by clicking its icon. Before run the software tool, the SPI jumper setting should follows Table 5 in 4.3 SPI mode section and USB cable is plugged in both KSZ8795-POE-EVAL board and PC/Laptop. After click its icon, a DOS Window will pop up as follow:T ype a ‘help’ and press Enter, all commands will display as follows,For Read or Write registers, reg is the offset address of the register, value is Hex number.The ‘run file’ command can execute multiple commands by a script file, the script file is a .txt file which can be created by any edit tools.run xxxx.txt //will run the .txt script file.5.5 Window SPI Software ToolThis is a powerful tool to access all register. The tool located in the default or assigned folder in the installation. There is a MicrelSwitchConfigApp.exe file which can be executed directly by clicking its icon.Before run the software tool, the SPI jumper setting should follows Table 5 in 4.3 SPI mode section and USB cable should be plugged in both KSZ8795CLXD-EVAL board and PC/Laptop. After click its icon, a GUI Window will pop up as follow:The default is SPI interface to do switch configuration. From the device selection window to select any devices then press ‘Continue’ button or click ‘Continue’ button directly, the software tool can detect devices automatically. A control Window will be pop up as follow.All register can be read/ written in the window.The control Window includes all application registers, static MAC table, VLAN table, dynamic table and MIB counters that are supported by SPI. The software can save and open the configuration file as a back-up.5.6 LinkMD Software ToolThis is a simple and powerful tool to test Micrel LinkMD feature. The tool is in the installation folder. There is a LinkMDUSB.exe file which can be executed directly by clicking its icon.After click the icon of this executed file, a GUI Window will pop up as follow:Select one part and clik ‘Next’ button, using SPI interface and clik ‘Next’ button again, pop up a test windown as below:An example for CAT-5 cable diagnostic with open on port 1, just clic k ‘TEST’ button, a test result shows as below.The test result shows both MDIX mode for pair 3-6 and MDI mode for 1-2 pair. The detail LinkMD diagnostic testing configuration is described in the datasheet.6.0 Reference DocumentsKSZ8795CLX Data Sheets (Contact Micrel for Latest Datasheet), KSZ8795 Design Package includes all design information as a Design kit. The Design Kit will be found on Micrel website (Contact Micrel for the updates).7.0 Bill of MaterialPlease see the detail BOMs in the BOM folder of the hardware design package for theKSZ8795-POE-EVAL Boards.8.0 SchematicsPlease see the schematics of the evaluation board and reference design in the schematicsfolder of the hardware design package (Design kit) for the KSZ8795-POE-EVAL Board. Magnetics Vendors:See the datasheets for the recommendation.MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http:/ The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to thecustomer.Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a signi ficant injury to the user. A Purchaser’s use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser’s own risk and Purchaser agrees to fully indemnify Micrel for any damagesresulting from such use or sale.© 2015 Micrel, Incorporated.。

KSA1010YTU;KSA1010OTU;KSA1010RTU;KSA1010Y;中文规格书,Datasheet资料

PNP Epitaxial Silicon TransistorAbsolute Maximum Ratings T C =25°C unless otherwise noted* PW ≤300µs, Duty Cycle ≤10%Symbol ParameterValue Units V CBO Collector-Base Voltage - 100V V CEO Collector-Emitter Voltage - 100V V EBO Emitter-Base Voltage - 7V I C Collector Current (DC) - 7A I CP *Collector Current (Pulse)- 15A I B Base Current- 3.5A P C Collector Dissipation (T C =25°C) 40W Collector Dissipation (T a =25°C) 1.5W T J Junction Temperature 150°C T STGStorage Temperature- 55 ~ 150°CKSA1010High Speed High Voltage Switching•Industrial Use•Complement to KSC23341.Base2.Collector3.Emitter1TO-220Pulse Test: PW≤350µs, Duty Cycle≤2% h FE Classification V BE(off) = 5V, L = 180µH ClampedV CEX(sus)2Collector-Emitter Sustaining Voltage I C = - 10A, I B1 = - 1AI B2 = 0.5A, V BE(off) = 5VL = 180µH, Clamped- 100VI CBO Collector Cut-off Current V CB = - 100V, I E = 0- 10µA I CER Collector Cut-off Current V CE = - 100V, R BE = 51ΩT C = 125°C- 1mAI CEX1Collector Cut-off Current V CE = - 100V, V BE(off) = 1.5V- 10µA I CEX2Collector Cut-off Current V CE = - 100V, V BE(off) = 1.5VT C = 125°C- 1mAI EBO Emitter Cut-off Current V EB = - 5V, I C= 0- 10uAh FE1 h FE2 h FE3* DC Current Gain V CE = - 5V, I C = - 0.5AV CE = - 5V, I C = - 3AV CE = - 5V, I C = - 5A404020200V CE(sat)* Collector-Emitter Saturation Voltage I C = - 5A, I B = - 0.5A- 0.6V V BE(sat)* Base-Emitter Saturation Voltage I C = - 5A, I B = - 0.5A- 1.5Vt ON Turn On Time V CC = - 50V, I C = - 5A,I B1 = - I B2 = - 0.5AR L = 10Ω0.5µst STG Storage Time 1.5µs t F Fall Time0.5µsClassification R O Yh FE240 ~ 8060 ~ 120100 ~ 200KSA1010KSA1010DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body,or (b) support or sustain life, or (c) whose failure to performwhen properly used in accordance with instructions for useprovided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can bereasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.A CEx™Bottomless™CoolFET™CROSSVOLT ™DenseTrench™DOME™EcoSPARK™E 2CMOS™EnSigna™FACT™FACT Quiet Series™FAST ®FASTr™FRFET™GlobalOptoisolator™GTO™HiSeC™ISOPLANAR™LittleFET™MicroFET™MICROWIRE™OPTOLOGIC™OPTOPLANAR™PACMAN™POP™Power247™PowerTrench ®QFET™QS™QT Optoelectronics™Quiet Series™SLIENT SWITCHER ®SMART START™STAR*POWER™Stealth™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TruTranslation™TinyLogic™UHC™UltraFET ®VCX™STAR*POWER is used under license分销商库存信息:FAIRCHILDKSA1010YTU KSA1010OTU KSA1010RTU KSA1010Y。

赛德凯斯电子KW系列匀胶机配件选型手册说明书

北京赛德凯斯电子有限责任公司KW系列匀胶机配件选型手册2014.11V1版SC-5-7(5mm-7mm)----------------------------------------1 SC-8-10(8mm-10mm)--------------------------------------2 SC-11-13(11mm-13mm)-----------------------------------3 SC-14-18(14mm-18mm)-----------------------------------4 SC-19-23(19mm-23mm)-----------------------------------5 SC-24-28(24mm-28mm一寸片托)-------------------------6 SC-29-33(29mm-33mm)-----------------------------------7 SC-34-38(34mm-38mm)-----------------------------------8 SC-39-43(39mm-43mm)-----------------------------------9 SC-44-48(44mm-48mm)----------------------------------10 SC-49-53(49mm-53mm二寸片托)------------------------11 SC-54-58(54mm-58mm)----------------------------------12 SC-59-63(59mm-63mm)----------------------------------13 SC-64-68(64mm-68mm)----------------------------------14 SC-70-74(70mm-74mm)----------------------------------15 SC-75-79(75mm-79mm三寸片托)------------------------16 SC-80-84(80mm-84mm)----------------------------------17 SC-85-89(85mm-89mm)----------------------------------18 SC-97-101(97mm-101mm四寸片托)----------------------19 SCS-9-13(9mm-13mm)------------------------------------20 SCS-14-18(14mm-18mm盖玻片)--------------------------21 SCS-19-23(19mm-23mm)----------------------------------22 SC-24-28-75-79(载玻片)------------------------------------23 SCL-5-44----------------------------------------------------24 SCH-44-68--------------------------------------------------25 SCH-70-84--------------------------------------------------26 SCH-80------------------------------------------------------27圆片直径:80-84mm 选择片托示意说明KW系列匀胶机配件内部编号i c s C o ., L t d适用于:方片边长范围85-89mm 圆片直径:85-89mm选择片托示意说明KW系列匀胶机配件内部编号n i c s C o ., L t dtL,.oCscino圆片直径:97mm-101mm标准4寸圆片片托选择片托示意说明KW系列匀胶机配件内部编号SC-97-101第 19 頁,共 27 頁适用于:方片边长范围19-23mmSCS-19-23选择片托示意说明KW系列匀胶机配件内部编号北京赛德凯斯电子有限责任公司 第 22 頁,共 27 頁适用于:用于客户定制 边长或直径44mm-68mm之间片子SCH-44-68选择片托示意说明KW系列匀胶机配件内部编号第 25 頁,共 27 頁SCH-70-84适用于:客户定制 边长或直径范围:70-84mm选择片托示意说明KW系列匀胶机配件内部编号第 26 頁,共 27 頁适用于:用于客户定制 边长或直径大于80mm以上片子SCH-80选择片托示意说明KW系列匀胶机配件内部编号第 27 頁,共 27 頁。

CS5361-KZZ;CS5361-KSZ;CS5361-DZZ;CS5361-KZZR;CS5361-KSZR;中文规格书,Datasheet资料

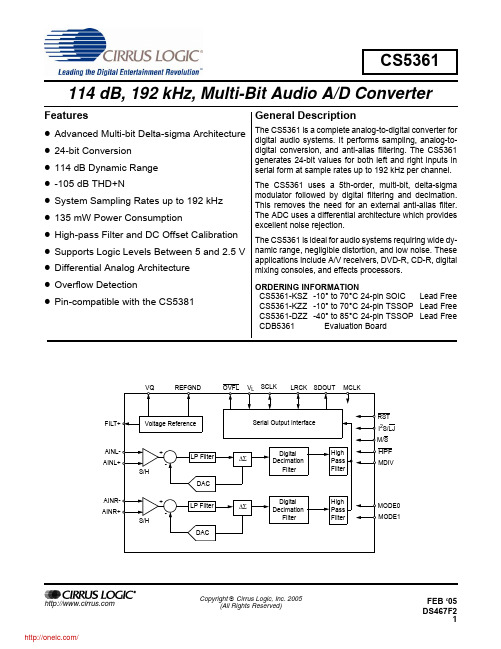

Copyright © Cirrus Logic, Inc. 2005CS5361114 dB, 192 kHz, Multi-Bit Audio A/D ConverterFeaturesz Advanced Multi-bit Delta-sigma Architecture z 24-bit Conversion z 114dB Dynamic Range z -105dB THD+Nz System Sampling Rates up to 192 kHz z 135 mW Power Consumptionz High-pass Filter and DC Offset Calibration z Supports Logic Levels Between 5 and 2.5V z Differential Analog Architecture z Overflow DetectionzPin-compatible with the CS5381General DescriptionThe CS5361 is a complete analog-to-digital converter for digital audio systems. It performs sampling, analog-to-digital conversion, and anti-alias filtering. The CS5361generates 24-bit values for both left and right inputs in serial form at sample rates up to 192kHz per channel.The CS5361 uses a 5th-order, multi-bit, delta-sigma modulator followed by digital filtering and decimation.This removes the need for an external anti-alias filter.The ADC uses a differential architecture which provides excellent noise rejection.The CS5361 is ideal for audio systems requiring wide dy-namic range, negligible distortion, and low noise. These applications include A/V receivers, DVD-R, CD-R, digital mixing consoles, and effects processors.ORDERING INFORMATIONCS5361-KSZ -10° to 70°C 24-pin SOIC Lead Free CS5361-KZZ -10° to 70°C 24-pin TSSOP Lead Free CS5361-DZZ -40° to 85°C 24-pin TSSOP Lead Free CDB5361Evaluation BoardVoltage ReferenceSerial Output InterfaceDigital FilterHighPass FilterHigh Pass FilterDecimation Digital FilterDecimation DAC-+S/HDAC -+S/HAINR+SCLKSDOUT MCLKRST VQ LRCK AINR-AINL+AINL-FILT+I 2S/LJ M/SHPF MODE0MODE1REFGND V L MDIVLP FilterLP Filter∆Σ∆ΣOVFLFEB ‘05TABLE OF CONTENTS1.0 CHARACTERISTICS AND SPECIFICATIONS (4)Specified Operating Conditions (4)Absolute Maximum Ratings (4)Analog Characteristics (CS5361-KSZ/KZZ) (5)Analog Characteristics (CS5361-DZZ) (6)Digital Filter Characteristics (7)DC Electrical Characteristics (10)Digital Characteristics (10)Switching Characteristics - Serial Audio Port (11)2.0 PIN DESCRIPTIONS (14)3.0 TYPICAL CONNECTION DIAGRAM (15)4.0 APPLICATIONS (16)4.1 Operational Mode/Sample Rate Range Select (16)4.2 System Clocking (16)4.2.1 Slave Mode (16)4.2.2 Master Mode (17)4.3 Power-up Sequence (18)4.4 Analog Connections (18)4.5 High-pass Filter and DC Offset Calibration (19)4.6 Overflow Detection (19)4.6.1 OVFL Output Timing (19)4.7 Grounding and Power Supply Decoupling (19)4.8 Synchronization of Multiple Devices (19)5.0 PARAMETER DEFINITIONS (20)6.0 PACKAGE DIMENSIONS (21)7.0 REVISION HISTORY (23)LIST OF FIGURESFigure 1. Single Speed Mode Stopband Rejection (8)Figure 2. Single Speed Mode Transition Band (8)Figure 3. Single Speed Mode Transition Band (Detail) (8)Figure 4. Single Speed Mode Passband Ripple (8)Figure 5. Double Speed Mode Stopband Rejection (8)Figure 6. Double Speed Mode Transition Band (8)Figure 7. Double Speed Mode Transition Band (Detail) (9)Figure 8. Double Speed Mode Passband Ripple (9)Figure 9. Quad Speed Mode Stopband Rejection (9)Figure 10. Quad Speed Mode Transition Band (9)Figure 11. Quad Speed Mode Transition Band (Detail) (9)Figure 12. Quad Speed Mode Passband Ripple (9)Figure 13. Master Mode, Left Justified SAI (12)Figure 14. Slave Mode, Left Justified SAI (12)Figure 15. Master Mode, I2S SAI (12)Figure 16. Slave Mode, I2S SAI (12)Figure 17. OVFL Output Timing (12)Figure 18. Left Justified Serial Audio Interface (13)Figure 19. I2S Serial Audio Interface (13)Figure 20. OVFL Output Timing, I2S Format (13)Figure 21. OVFL Output Timing, Left-Justified Format (13)Figure 22. Typical Connection Diagram (15)Figure 23. CS5361 Master Mode Clocking (17)Figure 24. CS5361 Recommended Analog Input Buffer (18)LIST OF TABLESTable 1.CS5361 Mode Control (16)Table 2.CS5361 Slave Mode Clock Ratios (16)Table 3.CS5361 Common Master Clock Frequencies (17)Table 4.Revision History (23)1.0CHARACTERISTICS AND SPECIFICATIONSAll Min/Max characteristics and specifications are guaranteed over the specified operating conditions. Typical per-formance characteristics and specifications are derived from measurements taken at typical supply voltages and T A = 25°C.SPECIFIED OPERATING CONDITIONSGND = 0V, all voltages with respect to GND.ABSOLUTE MAXIMUM RATINGSGND = 0V, All voltages with respect to GND. (Note 1)Notes: 1.Operation beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.2.Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCRlatch-up.3.The maximum over/under voltage is limited by the input current.ParameterSymbol Min Typ Max Unit DC Power Supplies:Positive Analog Positive Digital Positive LogicVA VD VL 4.753.12.37 5.03.33.3 5.255.255.25V V V Ambient Operating TemperatureCommercial (-KSZ/-KZZ) Automotive (-DZZ)T AC T AA-10-40--7085°C °CParameterSymbol Min Max Units DC Power Supplies:Analog Logic Digital VA VL VD -0.3-0.3-0.3+6.0+6.0+6.0V V V Input Current (Note 2)I in -10+10mA Analog Input Voltage (Note 3)V IN -0.7VA +0.7V Digital Input Voltage(Note 3)V IND -0.7VL +0.7V Ambient Operating Temperature (Power Applied)T A -50+95°C Storage TemperatureT stg-65+150°CANALOG CHARACTERISTICS (CS5361-KSZ/KZZ)Test conditions (unless otherwise specified): Input test signal is a 1kHz sine wave; measurement bandwidth is 10Hz to 20kHz.Notes: 4.Referred to the typical full-scale input voltage.5. Measured between AIN+ and AIN-ParameterSymbolMin Typ Max Unit Single Speed Mode Fs = 48kHzDynamic Range A-weightedunweighted108105114111--dB dBTotal Harmonic Distortion + Noise (Note 4)-1dB -20dB -60dBTHD+N----105-91-51-99--dB dB dB Double Speed Mode Fs = 96kHzDynamic Range A-weightedunweighted40kHz bandwidth unweighted108105-114111108---dB dB dBTotal Harmonic Distortion + Noise (Note 4)-1dB -20dB -60dB40kHz bandwidth -1dBTHD+N-----105-91-51-102-99---dB dB dB dB Quad Speed Mode Fs = 192kHzDynamic Range A-weightedunweighted40kHz bandwidth unweighted108105-114111108---dB dB dBTotal Harmonic Distortion + Noise (Note 4)-1dB -20dB -60dB40kHz bandwidth -1dBTHD+N-----105-91-51-102-99---dB dB dB dB Dynamic Performance for All Modes Interchannel Isolation -110-dB DC AccuracyInterchannel Gain Mismatch -0.1-dB Gain Error -2-2%Gain Drift -100-100ppm/°C Offset Error HPF enabledHPF disabled----0100LSB LSB Analog Input Characteristics Full-scale Input Voltage1.10*VA 1.13*VA1.15*VAVpp Input Impedance (Differential)(Note 5)7.5--k ΩCommon Mode Rejection RatioCMRR-82-dBANALOG CHARACTERISTICS (CS5361-DZZ)Test conditions (unless otherwise specified): Input test signal is a 1kHz sine wave; measurement bandwidth is 10Hz to 20kHz.Parameter Symbol Min Typ Max Unit Single Speed Mode Fs = 48kHzDynamic Range A-weightedunweighted 106103114111--dBdBTotal Harmonic Distortion + Noise(Note 4)-1dB-20dB-60dB THD+N----105-91-51-95--dBdBdBDouble Speed Mode Fs = 96kHzDynamic Range A-weightedunweighted40kHz bandwidth unweighted 106103-114111108---dBdBdBTotal Harmonic Distortion + Noise (Note 4)-1dB-20dB-60dB40kHz bandwidth -1dB THD+N-----105-91-51-102-95---dBdBdBdBQuad Speed Mode Fs = 192kHzDynamic Range A-weightedunweighted40kHz bandwidth unweighted 106103-114111108---dBdBdBTotal Harmonic Distortion + Noise (Note 4)-1dB-20dB-60dB40kHz bandwidth -1dB THD+N-----105-91-51-102-95---dBdBdBdBDynamic Performance for All ModesInterchannel Isolation-110-dB Interchannel Phase Deviation-0.0001-Degree DC AccuracyInterchannel Gain Mismatch-0.1-dB Gain Error-5-5% Gain Drift-100-100ppm/°COffset Error HPF enabledHPF disabled ----100LSBLSBAnalog Input CharacteristicsFull-scale Input Voltage 1.07*VA 1.13*VA 1.18*VA Vpp Input Impedance (Differential)(Note 5)7.5--kΩCommon Mode Rejection Ratio CMRR-82-dBDIGITAL FILTER CHARACTERISTICSNotes: 6.The filter frequency response scales precisely with Fs.7.Response shown is for Fs equal to 48kHz. Filter characteristics scale with Fs.ParameterSymbolMinTypMaxUnitSingle Speed Mode (2kHz to 51kHz sample rates)Passband (-0.1dB)(Note 6)0-0.47Fs Passband Ripple -0.1-0.035dB Stopband(Note 6)0.58--Fs Stopband Attenuation-95--dB Total Group Delay (Fs = Output Sample Rate)t gd-12/Fs -s Interchannel Phase Deviation-0.0001-DegDouble Speed Mode (50kHz to 102kHz sample rates)Passband (-0.1dB)(Note 6)0-0.45Fs Passband Ripple -0.1-0.035dB Stopband(Note 6)0.68--Fs Stopband Attenuation-92--dB Total Group Delay (Fs = Output Sample Rate)t gd-9/Fs -s Interchannel Phase Deviation-0.0001-DegQuad Speed Mode (100kHz to 204kHz sample rates)Passband (-0.1dB)(Note 6)0-0.24Fs Passband Ripple -0.1-0.035dB Stopband(Note 6)0.78--Fs Stopband Attenuation-92--dB Total Group Delay (Fs = Output Sample Rate)t gd-5/Fs -s Interchannel Phase Deviation -0.0001-DegHigh-pass Filter Characteristics Frequency Response -3.0dB -0.13dB (Note 7)-120--Hz Hz Phase Deviation @ 20Hz(Note 7)-10-Deg Passband Ripple --0dB Filter Settling Time105/FssFigure 1. Single Speed Mode Stopband Rejection Figure 2. Single Speed Mode Transition BandFigure 3. Single Speed Mode Transition Band (Detail )Figure 4. Single Speed Mode Passband RippleFigure 7. Double Speed Mode Transition Band (Detail)Figure 8. Double Speed Mode Passband RippleFigure 9. Quad Speed Mode Stopband Rejection Figure 10. Quad Speed Mode Transition BandA m p l i t u d e (dB )F re q u e n c y (n o rm a liz e d to F s )A m p li t u d e (d B )F re q u e n c y (n o rm a liz e d to F s )Figure 11. Quad Speed Mode Transition Band (Detail)Figure 12. Quad Speed Mode Passband RippleF re q u e n c y (n o rm a liz e d to F s )A m p l i t u d e (dB )A m p l i t u d e (dB )F re q u e n c y (n o rm a liz e d to F s )DC ELECTRICAL CHARACTERISTICSGND = 0V, all voltages with respect to ground. MCLK=12.288MHz; Master Mode.Notes:8.Power Down Mode is defined as RST = Low with all clocks and data lines held static.9.Valid with the recommended capacitor values on FILT+ and VQ as shown in the Typical ConnectionDiagram.DIGITAL CHARACTERISTICSTHERMAL CHARACTERISTICSParameterSymbol Min Typ Max Unit Power Supply Current VA = 5V (Normal Operation)VL,VD = 5V VL,VD = 3.3V I A I D I D ---17.52214.521.527.517mA mA mA Power Supply CurrentVA = 5V (Power-Down Mode) (Note 8)VL,VD = 5VI A I D --100100--µA µA Power Consumption (Normal Operation)VA, VD, VL = 5V VA = 5V, VL, VD = 3.3V(Power-Down Mode)------1981351243161-mW mW mW Power Supply Rejection Ratio (1 kHz)(Note 9)PSRR-65-dB V Q Nominal Voltage Output ImpedanceMaximum allowable DC current source/sink --- 2.5250.01---Vk ΩmA Filt+ Nominal Voltage Output ImpedanceMaximum allowable DC current source/sink---5150.01---Vk ΩmAParameterSymbol Min Typ Max Units High-Level Input Voltage (% of VL)V IH 70%--V Low-Level Input Voltage(% of VL)V IL --30%V High-Level Output Voltage at I o = 100µA (% of VL)V OH 70%--V Low-Level Output Voltage at I o = 100µA (% of VL)V OL --15%V OVFL Current SinkI ovfl -- 4.0mA Input Leakage Current (all pins except SCLK and LRCK)I in -10-10µA Input Leakage Current (SCLK and LRCK)I in-25-25µAParameterSymbolMin Typ Max Unit Allowable Junction Temperature--135°C Junction to Ambient Thermal Impedance(Multi-layer PCB) TSSOP (Multi-layer PCB) SOIC (Single-layer PCB) TSSOP (Single-layer PCB) SOICθJA-TM θJA-SM θJA-TS θJA-SS----706010580----°C/W °C/W °C/W °C/W分销商库存信息:CIRRUS-LOGICCS5361-KZZ CS5361-KSZ CS5361-DZZ CS5361-KZZR CS5361-KSZR。

ARTIX-7 FPGA 开发平台 用户手册说明书

ARTIX-7FPGA开发平台用户手册AX7203REV1.2版芯驿电子科技(上海)有限公司黑金动力社区目录一、开发板简介 (5)二、FPGA核心板 (8)(一)简介 (8)(二)FPGA (9)(三)有源差分晶振 (11)(四)DDR3 (13)(五)QSPI Flash (17)(六)LED灯 (19)(七)复位按键 (20)(八)JTAG接口 (20)(九)电源接口 (21)(十)扩展接口 (22)(十一)电源 (28)(十二)结构图 (30)三、扩展板 (31)(一)简介 (31)(二)千兆以太网接口 (32)(三)PCIe x4接口 (35)(四)HDMI输出接口 (37)(五)HDMI输入接口 (39)(六)SD卡槽 (41)(七)USB转串口 (42)(八)EEPROM24LC04 (43)(九)扩展口 (44)(十)JTAG接口 (48)(十一)XADC接口(默认不安装) (49)(十二)按键 (51)(十三)LED灯 (52)(十四)供电电源 (53)黑金ARTIX-7系列的高端FPGA开发平台(型号:AX7203)正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ARTIX-7FPGA开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

在底板设计上我们设计了丰富的外围接口,比如一路PCIex4接口,两路千兆以太网接口,一路HDMI输出接口,一路HDMI输入接口,Uart接口,SD卡接口等等。

满足用户各种PCIe高速数据传输,视频图像处理和工业控制的要求,是一款"全能级“的FPGA开发平台。

为高速视频传输,网络和PCIe通信及数据处理的前期验证和后期应用提供了可能。

相信这样的一款产品非常适合从事FPGA开发的学生、工程师等群体。

一、开发板简介在这里,对这款AX7203FPGA开发平台进行简单的功能介绍。

开发板的整个结构,继承了我们一贯的核心板+扩展板的模式来设计的。

nichicon FW series DATA SHEET

3300

332 10 × 20 1170 12.5 × 20 1420 12.5 × 25 1700 16 × 25 1950 16 × 35.5 2220 18 × 35.5 2360 20 × 40 2700 25 × 50 2900

4700

472 12.5 × 20 1350 12.5 × 25 1800 16 × 25 2100 16 × 31.5 2360 18 × 35.5 2490 20 × 40 2900 22 × 50 3400

Series name Type

Please refer to page 21, 22, 23 about the formed or taped product spec. Please refer to page 3 for the minimum order quantity.

Dimension table in next page.

Printed with black color letter on Gold sleeve.

D+ MAX. B P ± 0.5

Radial Lead Type

Sleeve (P.E.T.)

Bd

Pressure relief vent

(B 6.3up)

L+ MAX.

15MIN

4MIN

(mm)

BD

5

6.3

tan δ

Rated voltage (V) tan δ (MAX.)

6.3 0.28

10 0.24

16 0.20

25 0.16

35 0.14

50 0.12

For capacitance of more than 1000µF, add 0.02 for every increase of 1000µF.

TL-4096UCL Line scan camera Instruction Manual

1/ 18(ver.0.3) Line scan cameraInstruction ManualModel: TL-4096UCLTAKENAKA SENSOR GROUPTAKENAKA SYSTEM CO.,LTD.□H e a d O f f i c e86-66 Nomizo-cho Otsuka Yamashina-ku 607-8135 Kyoto JAPANTEL:+81-75-593-9300 FAX +81-75-593-9790□C a m e r a D e p t. 4F Matsumasa Bld.1-17-14 Ogaya Otsu Shiga 520-2144 JAPANTEL:+81-77-545-4331 FAX +81-77-545-4335□I mag e Inspect ion Dept.86-66 Nomizo-cho Otsuka Yamashina-ku 607-8135 Kyoto JAPANTEL:+81-75-593-9300 FAX +81-75-593-9790□T o k y o O f f i c e 2F MK Bldg. 2-2-19 Sotokanda Chiyoda-ku 101-0021 Tokyo JAPANTEL :+81-3-3255-0361FAX:+81-3-3255-0362TAKENAKA SYSTEM CO.,LTD. URL http://www.takex-system.co.jp/2 / 18 Table of Contents1. Outline (3)2. Features (3)3.Applications (3)4. CCD image sensor ........................................... (3)5.Specifications (4)6. Camera I/O (4)6-1. Connector pin assignment of the Power connector6-2. Connector pin assignment of the Camera Link connector7. How to change settings (6)8. Timing chart (7)9. Serial communication protocol (8)10. Exposure control (12)11. Setup steps of Hyper terminal (13)12. Notes (17)13. External dimensions (18)3 / 181. Outline● CCD line scan camera with 4096 pixels of image sensor and of 50MHz data rate. ● Video signal is output complying with Camera Link standard (Base Configuration).2. Features● It can perform high-speed inspection with 4096 image pixels at 50MHz data rate.● GAIN and OFFSET characteristics, 8/10 bit format etc. can be easily changed with RS232C command from capture board.● The equipment operates with a single DC12V power source.● Reduction in size and weight has been realized by adopting original circuit and mechanism design. ● Since the output signal level hardly vary among the ODD and EVEN pixels, It can display crisp image. ●Exposure control function is incorporated.3. Applications● Image processing device for Image inspection.● Foreign substance detector on high-speed production line ● Surface inspection apparatus of sheet-like object . ●Pinhole detector4. CCD image sensorThe CCD image sensor Is characterized by 10μm square sized pixel, effective 4096 pixels, and high-speed and high-sensitivity characteristic features.Charges accumulated in single-row photo diodes are output thorough two shift registers, respectively.(No.1 for ODD numbered charges, No.2 for EVEN numbered charges) Each shift register operates at the rate of 25MHz.D 2PORT A Block diagram of CCDdevice D 2D 2D 7D 7S 1S 2S 3S 5D 7D 7D 9D 9D 9S 5S 5S 5Photo diode Shift gate CCD analog shift register Shift gate CCD analog shift register Output buffer OS1PORT B OS2Output buffer 1~4095(ODD)2~4096(EVEN)Spectral responsivity4 / 185. Specifications6. Camera I / O6-1 Power connectorConnector panelCamera Link connectorPower connectorPower indicatorPower connector pin assignment654321Power connector (HR10A-7P-6S HIROSE) (Pin arrangement viewed from the outside of the camera)5 / 186-2 Camera Link connectorConforming cable 3M madeCf. 14B26-SZLB-*00-0LC (*m)※14B26-SZ3B-*00-04C (*m)※Flex resistance cableBit assignment of Base Configuration8 Bit: 10Bit:1261413Camera Link connector pin-out6 / 187. How to change settingsThe ODD/EVEN video signal gain and the camera gain are changeable as needed by removing the camera cover,.7-1 Fine adjustment of ODD/EVEN video signal gainGain adjustment of ODD/EVEN video signal is not normally needed, as it has been set before shipment. However, when it is needed, make a fine adjustment following the diagram below.7-2 How to change camera GAINThe camera gain has been set to “×4” as a factory default. It can double the gain using the built-in GAIN switch.Select “×1” when high-quality image is needed, and select “×8” when high sensitivity is needed even if image quality degrades. Select “×2 to ×6” depending on the degree.SW No.8: ON EXT SYNCOFF AUTO EXT SYNC(When the period of EXT SYNC is less than 1msec, it is automatically changed to INT SYNC.)OFF ← VR1: Pixel No.2 to 4096 (EVEN number) Fine control volume for gain7 / 188. Timing chart000STROBE (25MHz)EX SYNC In (CC1IN)LINE VALIDPIXEL DATA PORT A (OS1)1~4095(ODD)Dummy Signal(16pixels)1Line Output Period (2074CLOCK)TL-4096UCLTiming Chart0059clock8C L OC KPIXEL DATA PORT B (OS2)2~4096(EVEN)000000Effective Data period9. Serial communication protocolOperation under the RS232C communication(1)Selection of output bit format 8/10 bit(2)SYNC system switchingAUTO When EXT SYNC is not designated, it automatically switches to INT SYNC.EXT.SYNC EXT. SYNC operation onlyINT. SYNC INT. SYNC operation only※SYNC period is determined from the following equation.SYNC period = Minimum period + n ×aWhereInternal sync(sync=2) n= expt (exposure time)a= 12.8μsec …10.24μsec …(3) Exposure control system switching (Refer to the time chart on P.12)Line period exposure Exposure during periodic timeFixed time exposure Exposure during pre-set timePulse width exposure Exposure during the pulse width of EXT.SYNC(4) GAIN switchingSelection of GAIN position 1,2,3,…………8 ×Selection of GAIN position for each channel ODD/EVEN adjustment(5) Adjustment of OFFSETOFFSET adjustment for each channel (ODD/EVEN)[Network transmission setting]Baud rate :9600bpsData Length :8bitStart Bit :1bitStop Bit :1bitParity :NonXon / Xoff Control :Non[Communication overall]1. ViewingTo view the status of the camera.e.g. Id? <CR> To view the camera ID.2. SettingTo set the status of the camera.e.g. sync=1 <CR> To set SYNC system to EXT.SYNC[Glossary][ ] ……omissible<CR> ……carriage returnN ……arbitrary numeral indicating some valueA ……arbitrary numeral indicating GAIN positionX ……arbitrary numeral indicating channelGain position……GAIN position of the cameraChannel …….Channel to specify the GAIN control device for each CCD output line EEPROM …….EEPROM incorporated in the camera[Notes]・Command name must be lower-case. Upper-case character is not valid.・Input character must be one-byte character. Double-byte character is not valid.・Blank is not valid.・Line feed code is indicated by “CR(0x0D)”. And also “LF(0×0A)” and “CR+LF” are usable. However returning line feed code must be CR only.<When in use of Hyper terminal>・Retyping is required in case of inputting error .(Correction by cursor movement is not valid.)[ Description of exceptional case]*NG is returned when in command input error or in inputting nonexistent command.e.g. : Command input error (Gain position No. is not designated. )Input: ch1gain=96Output: NGe.g. : Input of nonexistent commandInput: chakeOutput: NG*NE is returned when in numeric entry error.e.g. : Input error (Input value is beyond the setting range.)Input: gainpos=96Output: NEe.g. : Input error (Input value is beyond the setting range.)Input: ch1gain1=2000Output: NE*NC is returned when in inputting invalid value under the condition that the ctrl setting (DIP-SW setting) is 0.e.g. :Input: ch1gain=9 (at ctrl=0)Output: NC*TO is returned when a command input period overruns the time-out period (15 sec.).e.g. :Input: gainpo (No CR entry)Output: TO*” ? ” at the bottom of Command is omissiblee.g. :Input: idOutput: 010. Exposure controlEXT.SYNC INLVALPIXEL DATAST-1Exposure timeST-1DATA output durationS T-2ST-2DATA output duration ST OU T-1ST OU T-2S T-3ST-0DATA output durationS T OUT -0ST-3DATA output durationST O UT-2Exposure timeExposure time11.Setup steps of Hyper terminal.[Setup of Hyper terminal ]1)Select “Start”→“Programs”→”Accessories”→”Communications”→”Hyper Terminal”2)The windows will appear with the picture below.3)When the next picture appears, enter any name.(e.g. GMA_RS232C)Then click the “OK” button.4)When the next picture appears, select “ COM? ” on Connect using.(? changes depending on the setting of the computer. )Then click the “OK” button.5)When the next picture appears, select each items as follows.(9600,8,None,1,Non)Then click the “OK” button.[Communication settings]Baud Rate : 9600bpsData Length : 8bitStart Bit : 1bitStop Bit : 1bitParity : NonXon/Xoff Control : Non6)The next picture will appear.7)Select [File]→[Properties]8)When the next picture appears, select “Settings” tag.9)When the next picture appears, click the “ASCII Setup” button.10)When the next picture appears, select each items as follows.(☑, ☑, 0, 0,☑, blank, blank)Then click the “OK” button.11)The screen display will return to the screen of 9).Then click the OK button.12)End of setup.Confirm the connection of the camera ,enter “check” on the screen belowand then send it out.If “OK” is displayed on the screen, communication processing has been completed.13) Select “Start”→“Programs”→”Accessories”→”Communications”→”Hyper Terminal”→”(*1) ”, when to launchthe Hyper terminal again with the same settings after having exited the above screen.*1………The name which was entered at section 3)11. NotesPrecautions for use■Do not make an impact on the equipment.■Do not lag the equipment with heat insulating agent. If the equipment is covered with heat insulating agent, It produces an increase in temperature and it causes the equipment to malfunction.(except for low-temperature environment use)■Take appropriate measures such as heat removal or cold removal to prevent dew condensation, when to move It to the place where temperature difference is extremely severe. Usage with dew condensation causes the equipment to malfunction.■When the equipment is not used for a long time, protect the imaging device from dust or scratch by attaching a lens cap. Do not store the equipment at the following places.・The place where is subjected to a lot of dust and moisture.・The place where is subjected to direct sunlight.・The place where is extremely hot or cold.・The place in the vicinity of an object which generates intensive electromagnetic field.・The place where is subjected to intensive vibration.■Please wipe off the dirt on the lens surface with a cotton swab preventing scratch to the lens surface.Use a soft cloth to clean up the camera body.■Use the equipment with a voltage within the range of specifications and do not connect the equipment to a power source that contains intense noise components. In such case, the image output from the camera may contains noise components.■Do not use the equipment in an environment subject to intense electromagnetic field.In such an environment, malfunction of the camera, disturbance of image and noise are caused by the field.■In case of the high-intensity object, it may happen that even the low intensity part is displayed whitely like a vertical streak above and below the high-intensity object. This phenomenon is called “smear”. However it is the problem specific to CCD and it is not the camera-related failure.■In case of the linear object, jagged picture may be displayed. Also in case of the pinstripe or checkered pattern, annual rings- like picture may be displayed. However these are also the problem specific to CCD and it is not the camera-related failure.■The lighting using a commercial power source may cause a perceptible flicker at higher shutter speed.In cases like this, consider to adjust shutter speed setting of the camera or to use the DC lighting or high- frequency lighting.Attention■All rights on this manual reserved.■The specifications and operational details described in the manual are subject to change for performance improvement or other reasons without notice.12.External dimensions。

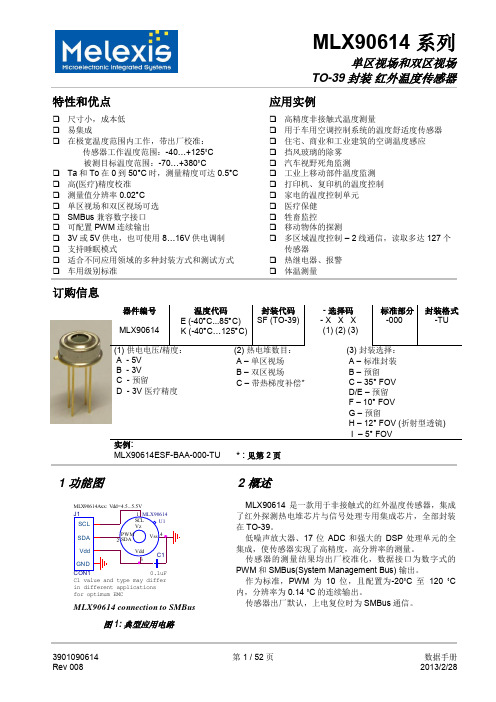

Datasheet MLX90614 中文 数据手册 rev008

10-位 PWM 输出模式是连续输出所测物体温度的标准配置,测量物体的温度范围为-20…120 °C,分辨 率为 0.14 °C。PWM 通过修改 EEPROM 内 2 个单元的值,实际上可以根据需求调整至任何温度范围,而这对 出厂校准结果并无影响。

传感器的测量结果均出厂校准化,数据接口为数字式的 PWM 和 SMBus(System Management Bus) 输出。

作为标准,PWM 为 10 位,且配置为-20˚C 至 120 ˚C 内,分辨率为 0.14 ˚C 的连续输出。

传感器出厂默认,上电复位时为 SMBus 通信。

3901090614 Rev 008

PWM 引脚也可配置为热继电器(输入是 To),这样可以实现简单且性价比高的恒温控制器或温度报警(冰 点/沸点)应用,其中的温度临界值是用户可编程的。在 SMBus 系统里,这个功能可以作为处理器的中断信号, 以此触发读取主线上从动器的值,并确定精度条件。

传感器有两种供电电压选择:5V 或 3V(电池供电)。其中,5V 也可简便的从更高供电电压(例如 8 至 16V)上通过外接元件调制。(具体请参考“应用信息”)

MLX90614 connection to SMBus

图 1: 典型应用电路

2 概述

MLX90614 是一款用于非接触式的红外温度传感器,集成 了红外探测热电堆芯片与信号处理专用集成芯片,全部封装 在 TO-39。

低噪声放大器、17 位 ADC 和强大的 DSP 处理单元的全 集成,使传感器实现了高精度,高分辨率的测量。

科尔摩根AKM 同步伺服电机 选型指南说明书

K O L L M O R G E N | A K o l l m o r g e n C O M PA N Y欢迎来到科尔摩根官方微信科尔摩根3目录u AKM ™ 同步伺服电机4u AKD ™ 伺服驱动器8u AKM ™ 各种选件12u AKM ™ 防水型和食品级防水型电机13u AKM ™ 系统综述14u AKM ™ 图纸和性能数据AKM1x 16AKM2x 20AKM3x24AKM4x 28AKM5x 34AKM6x 40AKM7x 44AKM8x48u L 10 轴承疲劳寿命和轴负载53u 反馈选件56u 抱闸选件60u 伺服电机连接器选件61u 型号命名67u MOTIONEERING ® Online71科尔摩根A K M 同步伺服电机选型指南克服设计、采购和时间障碍科尔摩根明白:帮助原始设备制造商的工程师克服障碍,可以显著提高其工作成效。

因而,我们主要通过如下三种方式来提供帮助:集成标准和定制产品在很多情况下,理想方案都不是一成不变的。

我们拥有专业应用知识,可以根据全面的产品组合来修改标准产品或开发全定制解决方案,从而为设计奠定良好的基础。

提供运动控制解决方案而不仅仅是部件在各公司减少供应商数量和工程人力的过程中,他们需要一家能够提供多种集成解决方案的全系统供应商。

科尔摩根就采用了全面响应模式,为客户提供全套解决方案,这些方案将编程软件、工程服务以及同类优秀的运动控制部件结合起来。

覆盖全球我们在美洲、欧洲、中东和亚洲拥有众多直销、工程支持单位、生产工厂以及分销商,临近全球各地的原始设备制造商。

这种便利优势可以加速我们的供货过程,根据客户需要随时随地供货。

财务和运营稳定性科尔摩根隶属于Fortive 公司。

Fortive 业务系统是推动Fortive 各部门发展的一个关键力量。

该系统采用“不断改善”(Kaizen )原理。

由高素质人才构成的多学科团队使用世界级的工具对过程进行评估,并制定相关计划以达到卓越的性能。

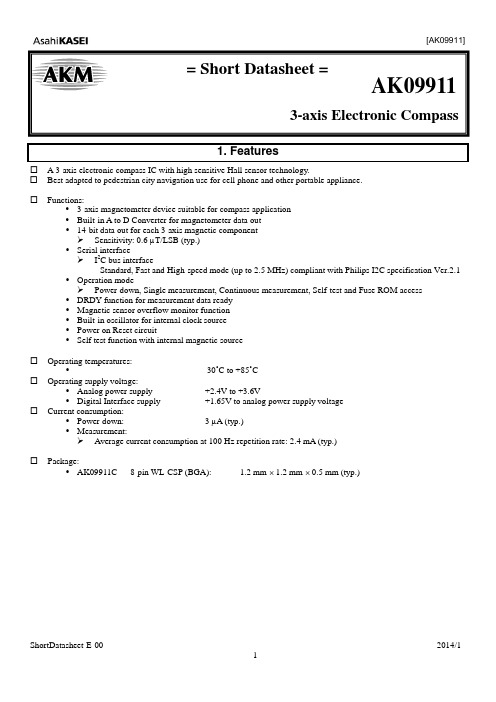

datasheet_AK09911

ShortDatasheet-E-00 -2-

ቤተ መጻሕፍቲ ባይዱ

2014/1

[AK09911]

3. Table of Contents

1. Features ..............................................................................................................................1 2. Overview..............................................................................................................................2 3. Table of Contents.................................................................................................................3 4. Circuit Configration ..............................................................................................................4 4.1. Block Diagram ..............................................................................................................4 4.2. Block Function ..............................................................................................................4 4.3. Pin Function ..................................................................................................................5 5. Overall Characteristics ........................................................................................................6 5.1. Absolute Maximum Ratings ..........................................................................................6 5.2. Recommended Operating Conditions ..........................................................................6 5.3. Electrical Characteristics ..............................................................................................6 5.3.1. DC Characteristics .................................................................................................6 5.3.2. AC Characteristics .................................................................................................7 5.3.3. Analog Circuit Characteristics ................................................................................8 5.3.4. I2C Bus Interface ....................................................................................................9 6. Function Explanation .........................................................................................................12 6.1. Power States ...............................................................................................................12 6.2. Reset Functions ..........................................................................................................12 6.3. Operation Mode ..........................................................................................................13 7. Example of Recommended External Connection .............................................................14 8. Package.............................................................................................................................15 8.1. Marking .......................................................................................................................15 8.2. Pin Assignment ...........................................................................................................15 8.3. Outline Dimensions.....................................................................................................16 8.4. Recommended Foot Print Pattern ..............................................................................16 9. Relationsip between the Magnetic Field and Output Code ..............................................17

INIC3619_Datasheet_V1.00

Revision 1.00 August 14, 2013 Initio Corporation

Revision 1.00

Page 1 of 28

INIC-3619 Datasheet _______________________________________________________________________________

批注本地保存成功开通会员云端永久保存去开通

INIC-3619 Datasheet _______________________________________________________________________________

INIC-3619 USB 3.0 SATA Bridge Datasheet

Contents

1 Introduction.......................................................................................................................................................................4 1.1 Feature Summary.......................................................................................................................................................4 1.2 Firmware Support..........................

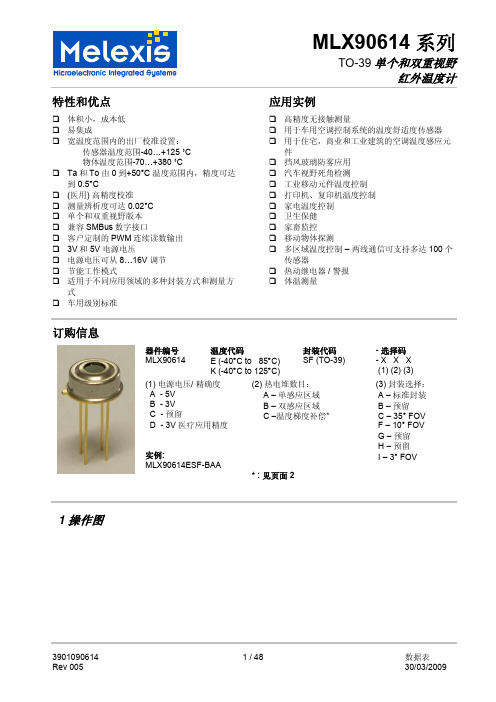

MLX90614红外温度计数据表

传感器测量的温度为视场里所有物体温度的平均值。MLX90614 室温下的标准精度为±0.5ºC。医疗应用版本的 传感器可在人体温度范围内达到±0.1ºC 的精度。

在应用设计中需要注意上述精度是当传感器在热平衡和等温条件下才能保证和达到的。(传感器封装里没有温差) 封装内部的温差会影响温度计测量的精度,如下因素会造成温差:传感器背部的热电子,传感器背部或旁边的 加热器/冷却器, 或当热/冷物体靠近传感器,不仅会加热传感元件,而且会加热温度计封装。

数据表 30/03/2009

MLX90614Axx: Vdd=4.5...5.5V

J1

1 MLX90614

SCL

SCL

U1

Vz

SDA

PWM 2 SDA

Vss 4

Vdd GND

Vdd C1 3

CON1

0.1uF

C1 value and type may differ

in different applications

7.1MLX90614Axx........................................................................................................................................................................................... 7 7.2MLX90614Bxx, MLX90614Dxx ................................................................................................................................................................. 9 8 详细描述......................................................................................................................................................................................................... 11 8.1 模块图表 ................................................................................................................................................................................................. 11 8.2 信号处理原理 .......................................................................................................................................................................................... 11 8.3 模块描述 ................................................................................................................................................................................................. 12

Eaton 9SX11KI 商品说明说明书

Eaton 9SX11KIEaton 9SX UPS, 11 kVA, 10 kW, Input: Hardwired, Outputs: Hardwired, Rack/tower, 6UGeneral specificationsEaton 9SX UPS 9SX11KI74317204021370 cm 44 cm 26 cm 78 kg 2 year CE Marked TUVIEC/EN 62040-1 IEC/EN 62040-2 CE EACEaton 9SX 11000iProduct Name Catalog Number UPCProduct Length/Depth Product Height Product Width Product Weight Warranty Compliances Certifications Model CodeSealed, lead-acidView runtime graphHot-swappable battery modules 2012 V / 7 AhYes Hardwired230V10 kW0.9200/208/220/230/240/250 V +/- 1%Sine wave230V default (200/208/220/230/240/250V) 21Online/Double-conversion11 kVAHardwired/fixed connection230V default (200/208/220/230/240/250V) 50/60 Hz>.99176-276 V (100-276 V with derating)NoBattery typeRuntime graphBattery replacement Battery quantityBattery managementBattery ratingExtended battery capability ReceptacleVoltageWattageOutput power factorOutput voltage rangeOutput waveformOutput nominal voltageVoltage distortion output (linear load) - max Feed typeTopologyVA ratingInput connection Input nominal voltage Nominal frequency Input power factor Input voltage range Includes network card CommunicationABM & Temperaturecompensated chargingmethod (user selectable)Automatic battery testDeep discharge protectionAutomatic recognition ofexternal battery unitsUSB port (HID compliant)Serial port (RS232)Mini terminal block forremote On/OffMini-terminal block forremote power offDry contacts (4 outputs,relay, DB9)40-70 HzNoMultilingual graphical LCD display YesOne slot for optional communication card Eaton Intelligent Power Manager, Eaton Intelligent Power Protector Other3000 m <50 dB at 1 meter 0° to 40°C (32° to 104°F)0-95% non-condensingFree standing model 1YesYes BlackInput frequency range Ethernet interface User interfacePotential free switch contact Expansion slotsSoftware compatibilityType of interface Altitude Noise level Temperature range Relative humidity Construction type Package contents Phase (output)Internal bypass Auto shutdown function Color Power ModuleExtended battery module (EBM)USB cable Serial cableBattery cable with comms for automatic battery cabinet recognition(2) Supports for tower mounting Link plate Safety instructions Quickstart guideEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All rights reserved. Eaton is a registered trademark.All other trademarks areproperty of their respective owners./socialmedia95No1NoEaton UPS and battery services Eaton UPS Services Quick Guide 2021EU declaration of conformity Eaton 9SX UPS Eaton 9SX-9PX UPS - 8-11 kVA-EBM 240V - Installation and user manualEaton 9SX UPS - 5/6/8/11 kVA - DatasheetEfficiency Rack mounting kit Phase (input)Hot swap power BrochuresCompliance informationManuals and user guidesTechnical data sheets。

KSZ9021RN to KSZ9031RNX Migration Guide

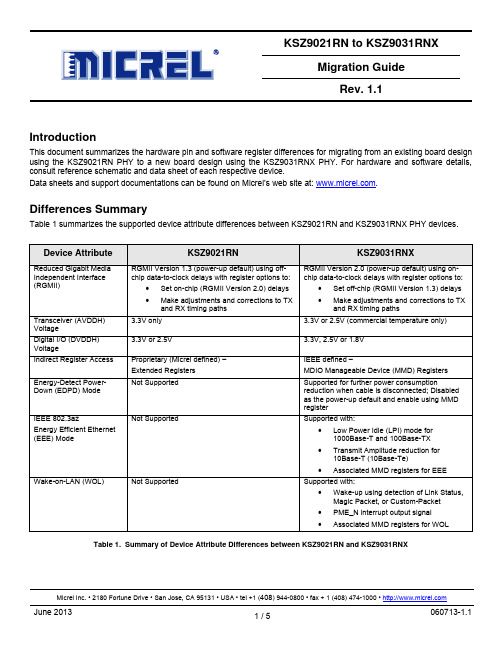

KSZ9021RN to KSZ9031RNXMigration GuideRev. 1.1IntroductionThis document summarizes the hardware pin and software register differences for migrating from an existing board design using the KSZ9021RN PHY to a new board design using the KSZ9031RNX PHY. For hardware and software details, consult reference schematic and data sheet of each respective device.Data sheets and support documentations can be found on Micrel’s web site at: .Differences SummaryTable 1 summarizes the supported device attribute differences between KSZ9021RN and KSZ9031RNX PHY devices.Device Attribute KSZ9021RN KSZ9031RNXReduced Gigabit Media Independent Interface (RGMII) RGMII Version 1.3 (power-up default) using off-chip data-to-clock delays with register options to:•Set on-chip (RGMII Version 2.0) delays•Make adjustments and corrections to TXand RX timing pathsRGMII Version 2.0 (power-up default) using on-chip data-to-clock delays with register options to:•Set off-chip (RGMII Version 1.3) delays•Make adjustments and corrections to TXand RX timing pathsTransceiver (AVDDH)Voltage3.3V only 3.3V or 2.5V (commercial temperature only)Digital I/O (DVDDH)Voltage3.3V or 2.5V 3.3V, 2.5V or 1.8VIndirect Register Access Proprietary (Micrel defined) –Extended Registers IEEE defined –MDIO Manageable Device (MMD) RegistersEnergy-Detect Power-Down (EDPD) Mode Not Supported Supported for further power consumptionreduction when cable is disconnected; Disabledas the power-up default and enable using MMDregisterIEEE 802.3azEnergy Efficient Ethernet (EEE) Mode Not Supported Supported with:•Low Power Idle (LPI) mode for1000Base-T and 100Base-TX•Transmit Amplitude reduction for10Base-T (10Base-Te)•Associated MMD registers for EEEWake-on-LAN (WOL) Not Supported Supported with:•Wake-up using detection of Link Status,Magic Packet, or Custom-Packet•PME_N interrupt output signal•Associated MMD registers for WOL Table 1. Summary of Device Attribute Differences between KSZ9021RN and KSZ9031RNXPin DifferencesTable 2 summarizes the pin differences between KSZ9021RN and KSZ9031RNX PHY devices. Pin #KSZ9021RNKSZ9031RNXPin NameType Pin FunctionPin NameTypePin Function1 AVDDH P 3.3V analog V DD AVDDH P 3.3V/2.5V (commercial temp only) analog V DD 12 AVDDH P 3.3V analog V DD AVDDH P 3.3V/2.5V (commercial temp only) analog V DD 13VSS_PSGndDigital groundNC–No connectThis pin is not bonded and can be connected to digital ground for footprint compatibility with the Micrel KSZ9021RN Gigabit PHY.16 DVDDH P3.3V / 2.5V digital V DD DVDDH P 3.3V, 2.5V, or 1.8V digital V DD_I/O 17 LED1 /PHYAD0I/OLED Output:Programmable LED1 OutputConfig Mode:The pull-up/pull-down value is latched as PHYAD[0] during power-up / reset.LED1 /PHYAD0 /PME_N1I/O LED1 output:Programmable LED1 outputConfig mode:The voltage on this pin issampled and latched during the power-up/reset process to determine the value of PHYAD[0].PME_N output:Programmable PME_N output (pin option 1). This pin function requires an external pull-up resistor to DVDDH (digital V DD_I/O ) in a range from 1.0k Ω to 4.7k Ω. When asserted low, this pin signals that a WOL event has occurred.When WOL is not enabled, this pin function behaves as per the KSZ9021RN pin definition.This pin is not an open-drain for all operating modes.34 DVDDH P3.3V / 2.5V digital V DD DVDDH P 3.3V, 2.5V, or 1.8V digital V DD_I/O38 INT_N O Interrupt OutputThis pin provides aprogrammable interrupt output and requires an external pull-up resistor to DVDDH in the range of 1K to 4.7K ohms for active low assertion.INT_N/O Interrupt OutputThis pin provides aprogrammable interrupt output and requires an external pull-up resistor to DVDDH in the range of 1K to 4.7K ohms for active low assertion.This pin is an open-drain.PME_N2 PME_N output: Programmable PME_N output (pin option 2). When asserted low, this pin signals that a WOL event has occurred.When WOL is not enabled, this pin function behaves as per the KSZ9021RN pin definition. This pin is not an open-drain for all operating modes.40 DVDDH P 3.3V / 2.5V digital V DD DVDDHP3.3V, 2.5V, or 1.8V digitalV DD_I/O47 AVDDH P 3.3V analog V DD NC–NoconnectThis pin is not bonded and canbe connected to AVDDH powerfor footprint compatibility withthe Micrel KSZ9021RN GigabitPHY.48 ISET I/O Set transmit output levelConnect a 4.99KΩ 1%resistor to ground on thispin. ISET I/O Set the transmit output levelConnect a 12.1kΩ 1% resistorto ground on this pin.Table 2. Pin Differences between KSZ9021RN and KSZ9031RNXStrapping Option DifferencesThere is no strapping pin difference between KSZ9021RN and KSZ9031RNX.Register Map DifferencesThe register space within the KSZ9021RN and KSZ9031RNX consists of direct-access registers and indirect-access registers.Direct-access RegistersThe direct-access registers comprise of IEEE-Defined Registers (0h – Fh) and Vendor-Specific Registers (10h – 1Fh). Between the KSZ9021RN and KSZ9031RNX, the direct-access registers and their bits have the same definitions, except for the following registers in Table 3.Direct-access RegisterKSZ9021RN KSZ9031RNXName Description Name Description3h PHYIdentifier2 Bits [15:10] (part of OUI) – same asKSZ9031RNXBits [9:4] (model number) – unique forKSZ9021RNBits [3:0] (revision number) – uniquedepending on chip revision PHY Identifier 2 Bits [15:10] (part of OUI) – same asKSZ9021RNBits [9:4] (model number) – unique forKSZ9031RNXBits [3:0] (revision number) – uniquedepending on chip revisionBh ExtendedRegister –Control Indirect Register AccessSelect read/write control andpage/address of Extended RegisterReserved ReservedDo not change the default value ofthis registerCh ExtendedRegister –Data Write Indirect Register AccessValue to write to Extended RegisterAddressReserved ReservedDo not change the default value ofthis registerDh ExtendedRegister –Data Read Indirect Register AccessValue read from Extended RegisterAddressMMD Access –ControlIndirect Register AccessSelect read/write control and MMDdevice addressEh Reserved ReservedDo not change the default value ofthis register MMD Access –Register/DataIndirect Register AccessValue of register address/data for theselected MMD device address1Fh, bit [1] Software Reset 1 = Reset chip, except all registers0 = Disable resetReserved ReservedTable 3. Direct-access Register Differences between KSZ9021RN and KSZ9031RNXIndirect-access RegistersThe indirect register mapping and read/write access are completely different for the KSZ9021RN (uses Extended Registers) and KSZ9031RNX (uses MMD Registers). Refer to respective devices’ data sheets for details.Indirect registers provide access to the following commonly used functions:•1000Base-T link-up time control (KSZ9031RNX only)• Pin strapping status• Pin strapping override•Skew adjustments for RGMII clocks, control signals, and datao Resolution of skew steps are different between KSZ9021RN and KSZ9031RNX•Energy-Detect Power-Down Mode enable/disable (KSZ9031RNX only)•Energy Efficient Ethernet function (KSZ9031RNX only)•Wake-on-LAN function (KSZ9031RNX only)Revision HistoryRevision Date Summary of ChangesMigration Guide created1.0 12/7/121.1 6/7/13 Indicate PME_N1 (pin 17) for KSZ9031RNX is not an open-drain.Indicate INT_N (pin 38) is an open-drain for KSZ9021RN, but is not an open-drain for KSZ9031RNX.Indicate direct-access register 1Fh, bit [1] difference.。

ksz8851