LatticeXP2 High-Speed IO Interface

Lattice编程电缆用户指南说明书

Programming CablesUser’s GuideFeatures•Support for all Lattice programmable products–1.2 V to 3.3 V programming (HW-USBN-2B)–1.2 V to 5 V programming (All other cables)–Ideal for design prototyping and debugging•Connect to multiple PC interfaces–USB (v.1.0, v.2.0)–PC Parallel Port•Easy-to-use programming connectors•Versatile flywire, 2 x 5 (.100”) or 1 x 8 (.100”) connectors•6 feet (2 meters) or more of programming cable length (PC to DUT)•Lead-free/RoHS compliant constructionFigure 1. USB Cable – HW-USBN-2BProgramming CablesLattice Programming Cable products are the hardware connection for in-system programming of all Lattice devices. After completion of the logic design and creation of a programming file with the Lattice Diamond®, ispLEVER® Clas-sic or PAC-Designer® software, the Lattice Diamond Programmer, or Lattice's ispVM™ System software is used to control the programming of devices directly on the PC board. No additional components are required to program a device.After you complete your logic design and create a programming file with the Lattice Diamond/ispLEVER Classic development tools, you can use Diamond Programmer or ispVM™ System software ispVM™ System software or Diamond Programmer to program devices on your board. The ispVM System/Diamond Programmer software auto-matically generates the appropriate programming commands, programming addresses and programming data based on information stored in the programming file and parameters you set in Diamond Programmer/ispVM Sys-tem. Programming signals are then generated from the USB or parallel port of a PC and directed through the Pro-gramming Cable to the device. No additional components are required for programming.Diamond Programmer/ispVM System software is included with all Lattice design tool products and is available for download from the Lattice web site at .Programming Cable Pin DefinitionsThe functions provided by the Programming cables correspond with available functions on Lattice programmable devices. Since some devices contain different programming features, the specific functions provided by the Pro-gramming cable may depend on the selected target device. ispVM System/Diamond Programmer software will automatically generate the appropriate functions based on the selected device. See Table 1 for an overview of the Programming cable functions.Table 1. Programming Cable Pin DefinitionsProgramming Cable Pin NameProgramming CablePin TypeDescriptionVCCProgramming VoltageInputConnect to V CC or V CCJ plane of the target device. T ypical I CC = 10mA. Y our board design supplies the power for V CC . Note: This may not be the same as a target device’s V CCO plane.SDO/TDO Test Data Output Input Used to shift data out via the IEEE1149.1 (JT AG) programming standard.SDI/TDITest Data InputOutput Used to shift data in via the IEEE1149.1 programming standard.ispEN/Enable/PROG/SN EnableOutput Enable device to be programmed.SN = SSPI Chip select for HW-USBN-2B TRST Test Reset Output Optional IEEE 1149.1 state machine reset. DONE DONEInput DONE indicates status of configuration MODE/TMS Test Mode Select Input Output Used to control the IEEE1149.1 state machine.GND GroundInput Connect to ground plane of the target device SCLK/TCK Test Clock Input Output Used to clock the IEEE1149.1 state machineINIT Initialize Input Indicates that ORCA ® device is ready for configuration.I2C: SCL 1I2C SCL Output Provides the I2C signal SCL I2C: SDA 1I2C SDA Output Provides the I2C signal SDA.5V Out 15V OutOutputProvides a 5V signal for the iCEprog M1050 Programmer.1.Only found on the HW-USBN-2B cable.Figure 2. Programming Cable In-System Programming Interface for the PC (HW-USBN-2B)11.Requires Diamond Programmer 3.1 or laterFigure 3. Programming Cable In-System Programming Interface for the PC (HW-USB-1A or HW-USB-2A)1ttice PAC-Designer® software does not support programming with USB cables. To program ispPAC devices with these cables, use the Dia-mond Programmer/ispVM System software.Figure 4. Programming Cable In-System Programming Interface for the PC (HW-DLN-3C and Equivalents)11.HW7265-DL3, HW7265-DL3A, HW-DL-3B, HW-DL-3C and HW-DLN-3C are functionally equivalent products.Figure 5. Programming Cable In-System Programming Interface for the PC (pDS4102-DL2 or pDS4102-DL2A)Figure 6. Programming Cable In-System Programming Interface for the PC (HW7265-DL2 or HW7265-DL2A)1.For reference purposes, the 2x10 connector on the HW7265-DL2 or HW7265-DL2A is equivalent to Tyco 102387-1. This will interface tostandard 100-mil spacing 2x5 headers, or a 2x5 keyed, recessed male connector such as the 3M N2510-5002RB.Programming SoftwareDiamond Programmer and ispVM System for Classic devices is the preferred programming management soft-ware tool for all Lattice devices and download cables. The latest version of Lattice Diamond Program-mer or ispVM System software is available for download from the Lattice web site at /software. Target Board Design ConsiderationsA 4.7K pull-down resistor is recommended on the TCK connection of the target board. This pull-down is recom-mended to avoid inadvertent clocking of the TAP controller induced by fast clock edges or as V CC ramps up. This pull-down is recommended for all Lattice programmable families.The I2C signals SCL and SDA are open drain. A 2.2K pull-up resistor to VCC is required on the target board.For Lattice device families that feature low power, it is recommended to add a 500 ohm resistor between V CCJ and GND during the programming interval when a USB Programming cable is connected to a very low power board design. A FAQ is available that discusses this in more depth at:/en/Support/AnswerDatabase/2/2/0/2205The JTAG programming port speed may need to be governed when using the Programming cables connected to customer PCBs. This is especially important when there is long PCB routing or with many daisy-chained devices. The Lattice programming software can adjust the timing of TCK applied to the JTAG programming port from the cable. This low-precision port setting of TCK depends on many factors, including the PC speed and the type of cable used (parallel port, USB or USB2). This software feature provides an option to slow the TCK for debug or noisy environments. A FAQ is available that discusses this in more depth at:/en/Support/AnswerDatabase/9/7/974.aspxThe USB Download Cable can be used to program Power Manager or ispClock products with Lattice programming software. When using the USB cable with the Power Manager I devices, (POWR604, POWR1208, POWR1208P1), you must slow do TCK by a factor of 2. A FAQ is available that discusses this in more depth at:/en/Support/AnswerDatabase/3/0/306.aspxProgramming Flywire and Connection ReferenceRefer to T able 2 when connecting a flywire download cable to systems that use the 1x8-position or 2x5-position connectors. For newer Lattice FPGA families, a 1x10 connector used in conjunction with the Programming USB cable adds support for the DONE and INITN signals. Both of these signals are inputs to the cable, and can be used to help verify device configuration.Table 2. Flywire Conversion ReferenceFunction FlywireCableWireLabel1x10Connector1x8Connector2x5ConnectorV CC1Red VCC116 TDO/SO/SPI_SO Brown TDO227TDI/SI/SPI_SI Orange TDI335 ispEN2/Enable/PROGRAMN/SN/SPI_SS_B Y ellow ispEN/PROG4410 TRST3/CRESET_B Green TRST/DONE559 TMS/MODE Purple TMS663 GND Black GND77 4 (2 and 8) TCK4/SCLK/CCLK/SPI_SCK White TCK881 DONE3Green TRST/DONE9INITN/CDONE Blue INITN10I2C SCL5, 6Y ellow/White I2C: SCLI2C SDA5,6Green/White I2C: SDATable 3 lists the recommend pin connections. Please contact Lattice technical support for information on unlisted devicefamilies.(e-mail:***************************).Table 3. Recommended Pin ConnectionsDevice FamilyTDITDOTMSTCKispEN/P ROG 1,6TRST 2/D ONE 3,6INITN 3,6VCCGNDSCLSDAECP5™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeECP3™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeECP2M™/LatticeECP2™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeECP™/LatticeEC™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeXP2™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeXP™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeSC™/LatticeSCM™Mandatory Mandatory MandatoryMandatory Optional Optional Optional Mandatory Mandatory N/A N/A iCE40™/iCE40LM/iCE40 Ultra™Mandatory Mandatory N/A Mandatory MandatoryRecom-mended Recom-mended Mandatory Mandatory N/A N/A MachXO2™/MachXO3™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory Optional Optional MachXO™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ORCA ®/FPSC Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A ispXPGA®Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispXPLD™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispMACH ®4000Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispMACH/ispLSI® 5000Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A MACH ®4A4Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispGDX2™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispClock™Mandatory Mandatory Mandatory Mandatory N/A N/A5N/A Mandatory Mandatory N/A N/A Platform Manager™Mandatory Mandatory Mandatory Mandatory N/A Optional 5N/A Mandatory Mandatory N/A N/A Power Manager/Power Manager II Mandatory Mandatory Mandatory Mandatory N/A Optional 5N/A Mandatory Mandatory N/A N/A ispPAC ®MandatoryMandatoryMandatoryMandatoryN/AN/AN/AMandatoryMandatoryN/AN/A1. Refer to the Programming Cable ispEN Pin section below for detailed information on connecting the ispEN/ENABLE pin.2. Refer to the Programming Cable TRST Pin section below for detailed information on connecting the TRST pin.3. The DONE and INITN signals are only available on the Programming USB cable. These signals are inputs to the cable and can be used to help verify deviceconfiguration.4. Please refer to the device data sheet. Not all packages have the ENABLE or TRST pin.5.When using P AC-Designer ® software to program ispPAC devices, do not connect this pin.6.When using these connections, be sure to select the correct settings in the Cable and I/O Port Setup dialog in the ispVM System/Diamond Programmer soft-ware.5V Output 5Red/White5V Out1.For devices that have a V CCJ pin, the V CCJ must be connected to the cable’s V CC, and a 0.1µF decoupling capacitor is required on V CCJ close to the device. Please refer to the device data sheet to determine if the device has a V CCJ pin.2.For older Lattice ISP devices, a 0.01µF decoupling capacitor is required on ispEN/ENABLE of the target board.3.The TRST and DONE pin is multiplexed on the Programming USB cable. If the device TRST signal is available on the board, connect the USB flywire TRST/DONE wire to TRST. If the device DONE signal is available on the board (or if both TRST and DONE are available), con-nect the USB flywire TRST/DONE wire to DONE. Please make sure the correct setting is selected in ispVM/Diamond Programmer (Options, Cable and I/O Port Setup). This will tell ispVM/Diamond Programmer whether the TRST/DONE cable is used as a TRST or a DONE signal.4.A 4.7K pull-down resister is recommended on TCK of the target board.5.Only on the HW-USB2N-2B cable6.Open drain signals. External pull-up ~2.2KOhm resistor to VCC is required.Table 2. Flywire Conversion Reference (Continued)FunctionFlywire Cable Wire Label 1x10 Connector1x8 Connector2x5 ConnectorConnecting the Programming CableThe target board must be un-powered when connecting, disconnecting, or reconnecting the Programming Cable. Always connect the Programming Cable’s GND pin (black wire), before connecting any other JTAG pins. Failure to follow these procedures can result in damage to the target programmable device.Programming Cable TRST PinConnecting the board TRST pin to the cable TRST pin is not recommended. Instead, connect the board TRST pin to Vcc. If the board TRST pin is connected to the cable TRST pin, instruct ispVM/Diamond Programmer to drive the TRST pin high as follows:1.Select the Options menu item.2.Select Cable and I/O Port Setup.3.Check the TRST/Reset Pin Connected checkbox.4.Select the Set High radio button.If the proper option is not selected, the TRST pin will be driven low by ispVM/Diamond Programmer. Consequently, the BSCAN chain will not work because the chain will be locked into RESET state.Programming Cable ispEN PinThe following pins should be grounded:•BSCAN pin of the 2000VE devices•ENABLE pin of MACH4A3/5-128/64, MACH4A3/5-64/64 and MACH4A3/5-256/128 devices.However, the user has the option of having the BSCAN and ENABLE pins driven by the ispEN pin from the cable. In this case, ispVM/Diamond Programmer must be configured to drive the ispEN pin low as follows:1.Select the Options menu item.2.Select Cable and I/O Port Setup.3.Check the ispEN/BSCAN Pin Connected checkbox.4.Select the Set Low radio button.Table 4.Feature HW-USBN-2B HW-USBN-2A HW-USB-2A HW-USB-1A HW-DLN-3CHW7265-DL3,HW7265-DL3A,HW-DL-3B,HW-DL-3C HW7265-DL2HW7265-DL2A PDS4102-DL2PDS4102-DL2AUSB X X X XPC-Parallel X X X X X X 1.2 V Support X X X1.8 V Support X X X X X X X X2.5-3.3 V Support X X X X X X X X X X 5.0 V Support X X X X X X X X X 2x5 Connector X X X X X X X1x8 Connector X X X X X X X Flywire X X X X X XLead-freeConstruction X X XAvailable for order X XProgramming Cable Feature SummaryEach Programming Cable ships with two small connectors that help you keep the flywires organized. The following manufacturer and part number is one possible source for equivalent connectors:•1x8 Connector (e.g. Samtec SSQ-108-02-T-S)•2x5 Connector (e.g. Samtec SSQ-105-02-T-D)The Programming Cable flywire or headers are intended to connect to standard 100-mil spacing headers (pins spaced 0.100 inch apart). Lattice recommends a header with length of 0.243 inches or 6.17 mm. Though, headers of other lengths may work equally well.Ordering InformationDescription Ordering PartNumberChina RoHS Environment-Friendly Use Period (EFUP)Programming cable (USB). Contains 6' USB cable, flywire connectors,8-position (1x8) adapter and 10-position (2x5) adapter, lead-free, RoHScompliant construction.HW-USBN-2BProgramming cable (PC only). Contains parallel port adapter, 6' cable,flywire connectors, 8-position (1x8) adapter and 10-position (2x5) adapter,lead-free, RoHS compliant construction.HW-DLN-3CNote: Additional cables are described in this document for legacy purposes only, these cables are no longer produced. The cables currently available for order are fully equivalent replacement items.Technical Support Assistancee-mail:***************************Internet:Revision HistoryDate Version Change SummaryJanuary 201524.7Updated Programming Cable Pin Definitions section.— In Table 1, Programming Cable Pin Definitions, ispEN/Enable/PROGchanged to ispEN/Enable/PROG/SN and its description revised.— Updated Figure 2, Programming Cable In-System ProgrammingInterface for the PC (HW-USBN-2B).Updated Programming Cable ispEN Pin section.In T able 4, Programming Cable Feature Summary, HW-USBN-2Bmarked as available for order.Updated Ordering Information section. HW-USBN-2A changed to HW-USBN-2BJuly 201424.6Changed document title to Programming Cables User’s GuideChanged ispDOWNLOAD Cables to Programming Cables.Updated Target Board Design Considerations section. Updated FAQlink on ispVM tool control of TCK duty cycle and/or frequency.Updated Table 3, Recommended Pin Connections. Added ECP5,iCE40LM, iCE40 Ultra, and MachXO3 device families.Updated Technical Support Assistance information.October 201224.5Added iCE40 configuration port pin names to the Flywire ConversionReference table.Added iCE40 information to Recommended Cable Connections table.February 201224.4Updated document with new corporate logo.November 201124.3Document transferred to user’s guide format.Added Figure USB Cable – HW-USBN-2A.Updated Recommend Cable Connections table for MachXO2 devices.Updated Target Board Design Considerations section.Added Appendix A.October 200924.2Added information related to the physical specifications of the flywireconnectors.July 200924.1Added Target Board Design Considerations text section.Added Programming Flywire and Connection Reference section head-ing.——Previous Lattice releases.Appendix A. Troubleshooting the USB Driver InstallationIt is essential that you install the drivers before connecting your PC to the USB cable. If the cable is connected before installing the drivers, Windows will try to install its own drivers that may not work.If you have attempted to connect the PC to the USB cable without first installing the appropriate drivers, or have trouble communicating with the Lattice USB cable after installing the drivers, following the steps below:1.Plug in the Lattice USB cable. Choose Start > Settings > Control Panel > System. In the System Propertiesdialog box, click the Hardware tab and Device Manager button. Under Universal Serial Bus controllers, you should see Lattice USB ISP Programmer. If you do not see this, look for the Unknown Device with the yellow flag.2.Double click on the Unknown Device icon.3.Click Reinstall Driver.4.Select Browse for driver software on your computer.For Lattice EzUSB DriverFor FTDI FTUSB Driver5.Browse to the isptools\ispvmsystem directory for the Lattice EzUSB driver or the isptools\ispvmsystem\Drivers\FTDIUSBDriver directory for the FTDI FTUSB driver. For Diamond installations, browse tolscc/diamond/data/vmdata/drivers. Click Next.6.Select Install this Driver software anyway. The system will update the driver.7.Click Close and finish installing the USB driver. Under Control Panel >System >Device Manager > Univer-sal Serial Bus Controllers should include the following:For the Lattice EzUSB Driver: Lattice USB ISP Programmer device installed.For the FTDI FTUSB Driver: USB Serial Converter A and Converter B devices installed.If you are experiencing problems or need additional information, contact Lattice Technical Support.。

lattice FPGA简介

为什么Lattice在进入FPGA市场的第一年就能取得这么好的成绩?我想这里面可能有三个层次的深层原因:第一,针对Altera和Xilinx在高端有Stratix和Virtex、在低端有Cyclone和Spartan产品的情况下,我们选择了从中端切入的策略,从而在刚进入FPGA应用市场时能够有效地避免与已在高端和低端市场确立了自己领导地位的Altera和Xilinx发生正面冲撞,二年多来的实践证明这一策略是非常正确的;第二,我们在满足市场要求的严格质量前提下做出了自己的产品特色,例如,我们的低端LatticeECP2/M FPGA产品在保持对Cyclone和Spartan价格竞争力的前提下,再增加了一些切合用户实际应用需要而主要竞争对手还没有的功能,如更多的高速串行接口、更多的I/O口、128位AES加密和更大的内部存储空间等;第三,系统制造商心里也期望市场能涌现出较强的第3个FPGA供应商,因为这样才能形成稳定的三足鼎立之势,促进市场的有序竞争,并帮助它们稳定供应链和进一步降低运营成本。

目前FPGA和CPLD在哪些主要应用空间具有不可替代的关键地位?目前FPGA和CPLD的目标应用主要可分为以下三大类:低成本应用、对价格敏感的高性能应用、以及需要极高性能的应用。

第一类应用包括等离子或LCD TV、VoIP、机顶盒、图像渲染、音频处理和控制逻辑,第二类应用包括企业联网、GPON、企业存储、无线基站、协议转换、网络交换、图像滤波和存储器桥接,第三类应用包括光纤联网、SDH线路卡、下一代40G光通道卡、局域网交换机、DDR3存储器测试仪、高端服务器、背板高速接口、数据包成帧和分拆、高速存储器控制和高速信号处理。

Lattice目前主要有哪几条产品线?它们各针对什么目标应用?Lattice目前主要有4条产品线:针对低端市场的低成本FPGA LatticeECP2/M、针对高端市场的系统级高性能FPGA LatticeSC/M、带嵌入式闪存的非易失性FPGA LatticeXP和MachXO、以及混合信号PLD ispClock和Power Manager II,LatticeECP2和LatticeECP2M的主要区别是后者还带有SRAM存储器,LatticeSC和LatticeSCM的主要区别也一样。

Lattice Semiconductor 产品选择指南:FPGA、CPLD、混合信号等 - 201

PRODUCT SELECTOR GUIDE2012FPGA • CPLD • MIXED SIGNAL • INTELLECTUAL PROPERTY • DEVELOPMENT KITS • DESIGN TOOLSCONTENTS■A dvanced Packaging (4)■F PGA Products (6)■CPLD Products (8)■Power Management and Clock Management Products (8)■Intellectual Property and Reference Designs (10)■Development Kits and Evaluation Boards (14)■P rogramming Hardware (18)■FPGA and CPLD Design Software (19)■PAC-Designer® Design Software (19)Page 2Affordable InnovationLattice Semiconductor is committed to delivering value through innovative low cost, low power solutions.We’re innovating every day to drive down costs and deliver greater value. From cost sensitive consumerelectronics to leading edge communications equipment, designers are using Lattice products in a growingnumber of applications. We’ve shipped over a billion devices to customers worldwide and we understandthat we must deliver cost effective solutions and excellent service in order to succeed.Low Density and Ultra-Low Density FPGAsWe are committed to providing design engineers with the low cost and low power solutions they needto implement their designs quickly, easily and affordably. Lattice FPGA solutions offer unique features,low power, and excellent value for FPGA designs. Our low density LatticeECP3™ family is comprisedof the lowest power, SERDES-enabled FPGAs in the market today, and is ideally suited for deploymentin high volume cost- and power-sensitive wireless and wireline infrastructure, video camera and displayapplications. Our ultra-low density, low cost and low power iCE40™ and MachXO2™ FPGA familiesare ideal for applications ranging from glue logic and bridging to instant-on system control and flexibleI/O expansion. From mobile handsets to leading-edge telecommunications infrastructure, Lattice offerssolutions that minimize cost and power while maximizing value.Power Management and Clock ManagementOur Platform Manager™, Power Manager II and ispClock™ mixed signal product families feature acombination of programmable logic and programmable analog circuitry that allows system designersto reduce system cost and design time. These innovative products provide a fast and easy solution forintegrating a wide range of power and clock management functions within a single integrated circuit. Theseproducts can replace numerous discrete components, reducing cost and conserving board space, whileproviding users with additional design flexibility and time-to-market benefits.Software and Intellectual PropertyOur Lattice Diamond® development tool suite, iCEcube2™ design software, PAC-Designer software, and IPcore program allow design engineers to easily customize our devices for their unique system requirements.Lattice Diamond software tools enable users to synthesize a design, perform analysis, debug, anddownload a logic configuration to our FPGA devices, while iCEcube2 software supports our iCE40 family ofFGPAs. PAC-Designer software is used in the design of our mixed signal products.Our IP core program, LatticeCORE™, provides pre-tested, reusable functions, allowing designers to focuson their unique system architectures. These IP cores provide industry-standard functions including PCIExpress, DDR, Ethernet, CPRI, Serial RapidIO 2.1, SPI4, and embedded microprocessors. In addition, anumber of independent IP providers have teamed with Lattice to offer additional high quality, reusable IPcores. Partners are selected for their industry leadership, high development standards, and commitment tocustomer support.Page 3Page 4Organic Flip Chip BGAFine Pitch BGA1704-BallOrganic fcBGA 42.5 x 42.5 mm 3.25 mm height 1.00 mm pitch1020-BallOrganic fcBGA Revision 233 x 33 mm 3.25 mm height 1.00 mm pitch1152-Ball fpBGA 1156-Ball fpBGA 35 x 35 mm 2.60 mm height 1.00 mm pitc h900-Ball fpBGA 31 x 31 mm 2.60 mm height 1.00 mm pitch672-Ball fpBGA 27 x 27 mm 2.60 mm height 1.00 mm pitch484-Ball fpBGA 23 x 23 mm 2.60 mm height 1.00 mm pitch324-Ball ftBGA 19 x 19 mm 1.70 mm height 1.00 mm pitch256-Ball ftBGA 17 x 17 mmOption 1: 1.55 mm height Option 2: 2.10 mm height Option 3: 1.70 mm height 1.00 mm pitch 256-Ball caBGA 14 x 14 mm 1.70 mm height 0.80 mm pitch332-Ball caBGA 17 x 17 mm 2.00 mm height 0.80 mm pitch208-Ball ftBGA 17 x 17 mm 1.55 mm height 1.00 mm pitch256-Ball fpBGA 17 x 17 mm 2.10 mm height1.00 mm pitchFine Pitch BGAChip Array BGANote: Packages shown actual size. Height specification is max.Page 5208-Pin PQFP 28 x 28 mm (body)4.10 mm height 0.50 mm pitch176-Pin TQFP 24 x 24 mm (body)1.60 mm height 0.50 mm pitch144-Pin TQFP 20 x 20 mm (body)1.60 mm height 0.50 mm pitch100-Pin VQFP 14 x 14 mm (body)1.2 mm height 0.50 mm pitch100-Pin TQFP 128-Pin TQFP 14 x 14 mm (body)1.6 mm height0.50 mm pitch (100 TQFP)0.40 mm pitch (128 TQFP )44-Pin TQFP10 x 10 mm (body)1.20 mm height 1.60 mm height 0.80 mm pitch 48-Pin TQFP 7 x 7 mm (body)1.20 mm height 1.60 mm height0.50 mm pitchVQFP/TQFP/PQFP64-Pin QFNS 9 x 9 mm1.00 mm height 0.50 mm pitch 100-Ball csBGA 8 x 8 mm1.35 mm height 0.50 mm pitch132-Ball csBG A 8 x 8 mmOption 1: 1.35 mm heightOption 2: 1.00 mm height (iCE40)0.50 mm pitch 184-Ball csBG A 8 x 8 mm1.35 mm height 0.50 mm pitch284-Ball csBGA 12 x 12 mm 1.00 mm height 0.50 mm pitch 328-Ball csBGA 10 x 10 mm 1.50 mm height 0.50 mm pitch 132-Ball ucBGA 6 x 6 mm1.00 mm height 0.40 mm pitch 25-Ball WLCSP2.5 x 2.5 mm 0.62 mm height 0.40 mm pitch84-Pin QFNS 7 x 7 mm1.00 mm height 0.50 mm pitch 48-Pin QFNS 7 x 7 mm1.00 mm height 0.50 mm pitch144-Ball csBGA 7 x 7 mm1.10 mm height 0.50 mm pitch 64-Ball ucBGA 4 x 4 mm1.00 mm height 0.40 mm pitch 32-Pin QFNS 5 x 5 mm1.00 mm height 0.50 mm pitch 32-Pin QFN 5 x 5 mm0.60 mm height 0.50 mm pitch 56-Ball csBGA 6 x 6 mm1.35 mm height 0.50 mm pitch 81-Ball csBGA 5 x 5 mm1.00 mm height 0.50 mm pitch 225-Ball ucBGA 7 x 7 mm1.00 mm height 0.40 mm pitch 24-Pin QFNS 4 x 4 mm1.00 mm height 0.50 mm pitch64-Ball csBGA 5 x 5 mm1.10 mm height 0.50 mm pitch121-Ball csBGA 6 x 6 mm1.00 mm height 0.50 mm pitch 121-Ball ucBGA 5 x 5 mm1.00 mm height 0.40 mm pitch 81-Ball ucBGA 4 x 4 mm1.00 mm height 0.40 mm pitch 49-Ball ucBGA 3 x 3 mm1.00 mm height 0.40 mm pitch 36-Ball ucBGA2.5 x 2.5 mm 1.00 mm height0.40 mm pitchQFNS / QFNChip Scale BGAUltra Chip Scale BGAWafer Level Chip ScaleNote: Packages shown actual size. Height specification is max.NEWiCE40™Page 6Page 71) Pb-free only.ispClock ProductsPage 8Platform Manager and Power Manager II Device Selector Guide* ispPAC-POWR1014A OnlyPage 9LatticeCORE IP CoresThe following is a partial listing of LatticeCORE IP, for a complete listing of IP cores from Lattice and its 3rd party partners, please go to /ip.1. LatticeSCM™ MACO®-based IP cores are not included in this table.Page 10IP SuitesLattice IP Suites provide many of the functions required to develop a total solution for common FPGA applications. In addition, multipleLattice FPGA families are supported with each IP Suite, so designers can develop solutions across multiple Lattice families, taking advantage of the best features of each. The following table summarizes which IP cores are included in each IP Suite, and which FPGA families are supported.Page 11Page 12Page 13Page 14Features- Power connections and power sources - ispVM™ programming support- On-board and external reference clock sources• Available on Windows and Linux platforms • Software and IP with a 60-day license (Windows or Linux)• Variety of demos • USB download cable• Comprehensive Image Processing IP Library • On-board Broadcom ® Broadreach™ PHY Enables IP over Coax• On-board FTDI Chip provides easy programming via low cost USB cable- Gigabit Ethernet MAC Demo using Mico32- DDR3 Memory Controller Demo• Available on Windows and Linux platforms • USB A to USB B (Mini) Cable for FPGA Programming via a PC• 12V AC Power Adapter and International Plug Adapters•QuickSTART GuideFeaturesFeaturesFeaturesLatticeECP3 Versa Development KitHDR-60 Video Camera Development KitLatticeECP3 PCI Express Development KitLatticeXP2 Brevia2 Development Kit• LatticeECP3 PCI Express x1/x4 Solutions Board- PCI Express x1 and x4 edge connector interfaces- On-board Boot Flash- Both Serial SPI Flash and Parallel Flash via MachXO programming bridge - Shows interoperation with a highperformance DDR2 memory component - Switches, LEDs, displays for demo purposes- Input connection for lab-power supply• FPGA-based Image Signal Processing• Fully Production-Ready HDR Camera Design • 1080p Capable @ 60 frames per second• Supports up to 16 Megapixel Sensors • Supports up to two sensors simultaneously • Full 60fps in streaming mode needs no external frame buffer• Fast Auto Exposure Instantly Adjust to Changing Light• Greater than 120 dB High Dynamic Range (HDR) Performance• Direct HDMI/DVI output from FPGA • Extremely Low-Latency• The LatticeECP3 Versa Evaluation Board:- PCI Express 1.1 x1 Edge Connector Interface- Two Gigabit Ethernet Ports (RJ45)- 4 SMA Connectors for SERDES Access - USB Mini for FPGA Programming- LatticeECP3 FPGA: LFE3-35EA-FF484- 64 Mbit Serial Flash memory - 1 Gbit DDR3 Memory- 14-segment alpha-numeric display - Switches and LEDs for demos - SERDES Eye Quality Demo - 4 PCI Express Demos• LatticeXP2 FPGA: LFXP2-5E-6TN144C • 2 Mbit SPI Flash Memory • 1 Mbit SRAM• Programmed via included mini-USB Cable • 2x20 and 2x5 Expansion Headers• Push buttons for General Purpose I/O and Reset• 4-bit DIP Switch for user-defined inputs • 8 Status LEDs for user-defined outputsDevelop PCIe-based platforms using a low-cost, low-power SERDES-basedFPGA with proprietary and Lattice provided designs.A fully production ready High Dynamic Range (HDR) camera, designed to fit into commercially available camera housings. Supports full 1080p resolution at 60 frames per second in streaming mode through the FPGA, without the need for an external frame buffer.Industry’s lowest cost platform for design-ing PCI Express and Gigabit Ethernet based systems. The kit includes free demos and reference designs.Easy-to-use, low-cost platform for evaluat-ing and designing with LatticeXP2 FPGAs.Page 15FeaturesFeaturesiCEblink40 Evaluation KitMachXO2 Pico Development KitMachXO2 Control Development Kit• Two versions:- High Performance: iCE40HX1K-VQ100 - Low Power: iCE40LP1K-QN84• Powered by USB input• 1Mbit SPI PROM (enough for two iCE40HX1K images using WarmBoot)• Four capacitive-touch buttons (requires FPGA logic)• Four user LEDs• Dual PMOD header compatible with Digilent PMOD boards (6x2 header)• MachXO2 LCMXO2-1200ZE• 4-character 16-segment LCD display • 4 capacitive touch sense buttons • 1 Mbit SPI Flash• I 2C temperature sensor• Current and voltage sensor circuits • Expansion header for JTAG, I 2C• Standard USB cable for device programming and I 2C communication• RS-232/USB & JTAG/USB interface• RoHS-compliant packaging and process• MachXO2 LCMXO2-4000HC• Power Manager II ispPAC-POWR1014A • 128Mbit LPDDR memory, 4Mbit SPI Flash • Current and voltage sensor circuits • SD memory card socket • Microphone• Audio Amplifier and Delta-Sigma ADC• Up to two DVI sources and one DVI output.• Up to two Display Inputs (7:1 LVDS) and one Display Output (7:1 LVDS)• Audio output channel• Expansion header for JTAG, SPI, I 2C and PLD I/Os.• 3.33 MHz oscillator (can be modified to support 33.33 MHz or 333 kHz)• 1.2V and 3.3V power supplies• All iCE40HX1K I/O available on headers or 0.1” through-holes• Watch battery• QuickSTART Guide• LEDs & switches• Standard USB cable for device programming • RS-232/USB & JTAG/USB interface• RoHS-compliant packaging and process • AC adapter (international plugs)• QuickSTART Guide31, 2012. Standard list price: $39.MachXO Control Development Kit FeaturesMachXO Pico Dev. Kit & MachXO Control Dev. Kit• Preloaded Control SoC Demo • MachXO LCMXO2280• Power Manager II ispPAC-POWR1014A• 2Mbit SPI Flash & 1Mbit SRAM • I 2C temperature sensor • Current and voltage sensor circuits • On-board fan • Interface to 16 x 2 LCD panel*• SD memory and Compact Flash memory card sockets*• Audio output channel• Expansion header for SPI & I 2C • LEDs & switches• Standard USB cable for device programming and I 2C communication • RS-232/USB & JTAG/USB interface • 3” x 1” prototyping area • RoHS-compliant packaging and process * LCD panel and SD/Compact Flash memory not included in the development kit MachXO Mini Development Kit Features• MachXO PLD: LCMXO2280C-4TN144C• 2 Mbit SPI Flash memory • 1 Mbit SRAM• I 2C temperature sensor • USB mini jack sockets for power, JTAG programming, and RS-232 debugging • 2X16 header for off-board expansion provides access to top and right side MachXO banks• Push-buttons for sleep mode and reset• 4-bit DIP switch to user-defined inputs • ADC/DAC circuit • Sleep circuit• 8 LEDs for user-defined outputs• RoHS-compliant packaging and process• Two USB connector cables • QuickSTART GuidePage 16FeaturesFeaturesFeaturesPower Manager II Hercules Development KitProcessorPM Development KitPlatform Manager Development Kit• The Standard Edition Hercules DevelopmentKit features the following:- Preloaded Board Digital ManagementDemo- Hercules Standard Edition eval board- Power Manager II ispPAC-POWR1220AT8 and MachXOLCMXO2280 PLD• The Advanced Edition Hercules DevelopmentKit features the following:- Preloaded Board Digital ManagementDemo- Hercules Advanced Edition evaluationboard with CompactPCI headers- Power Manager II ispPAC-POWR1220AT8 and MachXOLCMXO2280 PLD- Backplane accessory evaluation boardand power supply for live hot-swap• AC adapter (international plugs)• USB Connector Cable• RoHS-compliant packaging and process• Pre-configured Processor Support Demo• ProcessorPM-POWR605• Power Manager II POWR6AT6• 3.3V, 2.5V, and 1.8V supply rails• LEDs• Slide potentiometer• 2x14 expansion header• USB mini jack socket (program/power)• 2 Push-Buttons• Preloaded Power Management Demo• LPTM10-12107, Platform Manager, 208-ballftBGA package• 35mm slide pots to emulate supply railvariations• Pads for user I/O, LED, and switches• JTAG and I2C interface headers• USB Cable• 4-Bit DIP Switch• JTAG and I2C Header Landings• RoHS-compliant packaging and process• USB connector cable• QuickSTART Guide• AC adapter with international plugs• Programmable with ispVM System software• QuickSTART GuideVersatile, ready to use hardware platformsfor evaluating and designing with PowerManager II devices. A Standard and Ad-vanced Edition of each kit is available.Versatile, ready-to-use hardware platformfor evaluating and designing with Proces-sorPM power management devices.A versatile, ready-to-use hardware plat-form for evaluating and designing withPlatform Manager devices.Features:Breakout Board Evaluation Kits•Preprogrammed with hardware test programLCMXO2-1200ZE-1TG144C PLD (MachXO2Breakout Board), LCMXO2280C-FTN256CPLD (MachXO2280 Breakout Board),POWR1014A-02TN48I (POWR1014ABreakout Board), or LC4256ZE-TN144C CPLD(ispMACH 4256ZE Breakout Board)• LEDs•Expansion Header LandingsBreakout Board Evaluation Kits for selectMachXO2, MachXO, ispMACH 4000ZE,Power Manager II devices offer convenienthardware evaluations by providing easyhand-access to PLD I/Os.•Prototyping Area•USB Mini Jack Socket (Program/Power)•JTAG Header Landing•RoHS-compliant packaging and process•USB connector cableFeaturesispMACH 4000ZE Pico Development Kit• Pre-programmed Pico Power Demo• ispMACH 4000ZE device(LC4256ZE-5MN144C)• Power Manager II device(ispPAC-POWR6AT6-01SN32I)• LCD panel• USB mini jack socket for power, JTAGprogramming, and I2C interface• 2X15 header landing for off-board expansionprovides access to LC4256ZE GPIOs,POWR6AT6 VMON inputs, I2C, and JTAG chain• Push-button for global reset• 4-bit DIP switch to user-defined inputs• 3.3V and 2.5V supply rails• Current and voltage sensor circuits• Battery or USB power source• RoHS-compliant packaging and process• Marked for CE, China RoHS Environmental-Friendly Use Period (EFUP) and WasteElectrical and Electronic Equipment (WEEE)Directives• One USB connector cable• QuickSTART GuideBattery-powered, low-cost platform toaccelerate the evaluation of ispMACH4000ZE CPLDs.Page 17Programming HardwarePage 18PAC-Designer — Mixed-Signal Design SoftwarePage 19Technical SupportUSA & Canada: 1-800-LATTICE (528-8423)For other locations: +1-503-268-8001PLDTechnicalandSoftware:***************************MixedSignal:***********************Additionally, customers can receive technical support for Lattice’s Programmable Logic Products from our Asia based applications group, by contacting Lattice Asia applications during the hours of 8:30 a.m. to 5:30 p.m. Beijing Time (CST) +0800 UTC (Chinese and English language only).Asia: +86-21-52989090********************************Corporate HeadquartersLattice Semiconductor Corporation 5555 Northeast Moore CourtHillsboro, Oregon 97124-6421 USA Telephone: +1-503-268-8000Facsimile: +1-503-268-8347Web: Software LicensingEmail:************************Web: /licensing/index.cfmCopyright © 2012 Lattice Semiconductor Corporation. All brand names or product names are trademarks or registered trademarks of their respective holders. Lattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), Lattice Diamond, LSC, E 2CMOS, FlashBAK, flexiFLASH, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, iCE40, iCEblink, iCEcube2, IPexpress, ISP , ispATE, ispClock, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDXV, ispGDX2, ispGENERATOR, ispJTAG, ispLeverCORE, ispLSI, ispMACH, ispPAC, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP , ispXPGA, ispXPLD, LatticeCORE, LatticeECP3, LatticeECP2, LatticeECP2M, LatticeECP , LatticeECP-DSP , LatticeMico, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM, LatticeXP , LatticeXP2, MACH, MachXO, MachXO2, MACO, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, Platform Manager, ProcessorPM, PURESPEED, Reveal, Silicon Forest, Speedlocked, Speed Locking, sysCLOCK, sysCONFIG, sysDSP , sysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TransFR, UltraMOS, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP is a service mark of Lattice Semiconductor Corporation.October 2012 • Order #: I0211K。

lattice 产品介绍

XP2 系列

LFXP2-17ELFXP2-17E-5FT256C

SC 系列

LFSCM3GA25EP1LFSCM3GA25EP1-5FN900C

SC 系统芯片在业 界领先的FPGA 体 系中集成了4到32 个3.8G Serdes , 可灵活配置成 GE/10GE.PCIE,OC12/48,Fiber channel,业界最 高速率2Gbps的 I/O接口,以及创 新的把结构化Asic 的MACO 块嵌入 了内部,因此和同 类产品相比,性能 更高,集成度更强

Low-Cost FPGAs

• Mainstream FPGA Features/Performance at Lower Cost – DDR/DDR2 – Full-Featured DSP – SERDES

System FPGAs

• Full System-level Solution for Communications Applications – World Class SERDES – Embedded Hard IP

Lattice 第一代通用 型FPGA,低成本, 外围配置芯片可采 用spi flash ,含有 dsp 模块,支持 DDR memory , 是实现简单算法设 计最好的选择

ECP2 系列

LFE2-6ELFE2-6E-5TN144C

ECP2 是业界最低成本 的90 nm的FPGA,以 前只有高端器件才有的 特点和性能,比如说pll 和dll的支持,高速的源 同步I/O,DDR,DDR2, 128Bit AES算法加密, 双端口dual-boot启动, SPI FLASH 加载,近 乎完美

XP 是单芯片,可以单 电源供电的FPGA,应用 于对安全性,单板面积 有要求的场合,而且 lattice 特有的TFR技 术,可以远程的不掉电 系统升级 XP2 也是单芯片的 FPGA ,但是加入了dsp 模块和供用户自己使用 的memory ,成本相比 xp也有降低,

Lattice XO2内部RAM使用手册

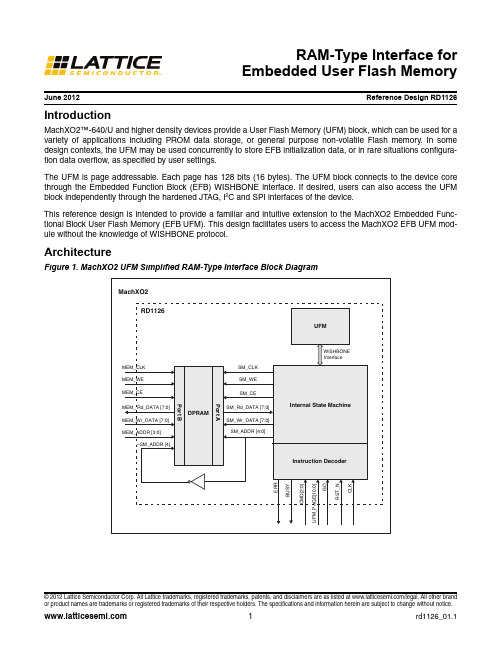

June 2012Reference Design RD1126© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.IntroductionMachXO2™-640/U and higher density devices provide a User Flash Memory (UFM) block, which can be used for a variety of applications including PROM data storage, or general purpose non-volatile Flash memory. In some design contexts, the UFM may be used concurrently to store EFB initialization data, or in rare situations configura-tion data overflow, as specified by user settings.The UFM is page addressable. Each page has 128 bits (16 bytes). The UFM block connects to the device core through the Embedded Function Block (EFB) WISHBONE interface. If desired, users can also access the UFM block independently through the hardened JTAG, I 2C and SPI interfaces of the device.This reference design is intended to provide a familiar and intuitive extension to the MachXO2 Embedded Func-tional Block User Flash Memory (EFB UFM). This design facilitates users to access the MachXO2 EFB UFM mod-ule without the knowledge of WISHBONE protocol.ArchitectureFigure 1. MachXO2 UFM Simplified RAM-Type Interface Block DiagramRAM-Type Interface forEmbedded User Flash MemoryPort DescriptionsTable 1. Port DescriptionsPort Direction Width (Bits)DescriptionCLK Input1Clock input1RST_N Input1Active low reset signalCommand InterfaceGO Input1High (‘1’) starts command process. GO is ignored if BUSY is asserted. CMD Input3Command operationUFM_P AGE Input11Target UFM PageBUSY Output1Status bit. Indicates operation in progress.ERR Output1Error bit. The last operation failed. Will be cleared on subsequent GO. Data InterfaceMEM_CLK Input1Clock for the DPRAM moduleMEM_WE Input1Write enable for the DPRAM moduleMEM_CE Input1Clock enable for the DPRAM moduleMEM_ADDR Input4DPRAM addressMEM_Wr_DA T A Input8DPRAM write dataMEM_Rd_DA T A Output8DPRAM read data1.Modify the design parameter READ_DELAY when CLK > 16.6 MHz. See discussion below.Functional DescriptionThis design facilitates user access to the MachXO2 EFB UFM module without the knowledge of WISHBONE proto-col. The user has to provide the necessary command sequence with UFM page address. A GO signal will trigger the interface to perform the necessary WISHBONE transactions to read or write the UFM.UFMThe User Flash Memory of the MachXO2 device features non-volatile storage in a single sector. Other features include:•Non-volatile storage up to 256Kbits•100K write cycles•Write access is performed page-wise; each page has 128 bits (16 bytes)•Auto-increment addressingTypical of Flash technology, the array must be cleared (erased) before data can be overwritten. The erased state of the UFM bits is ‘0’. The smallest erasable unit is the entire sector. Thus, any data which must be preserved (e.g. Config data overflow, or EBR init data) must be read out and stored in another available memory (e.g. EBR) prior to the Erase command. After the erase is complete, the data is written back to the UFM. The user is responsible for performing the storage operation. This requirement, along with limited erase cycles and long erase/program times, renders the UFM a poor solution for ‘scratch pad’ RAM (or similar) applications. MachXO2 Embedded Block RAM (EBR) is the recommended on-board memory type for high-churn, volatile data storage.In the design’s default configuration, the internal UFM read operation has been optimized for lower CLK rates. For CLK rates exceeding 16.6 MHz, this design must be configured to insert additional Retrieval Delay into the state machine which generates the UFM read command. A parameter, READ_DELAY, is provided for this purpose. The source file “UFM_WB_top.v” can be modified directly or the parameter passed in the module instantiation. The min-imum value for READ_DELAY can be calculated as follows:READ_DELAY(min) = 240/PERIOD - 4where PERIOD = CLK period in nsExample, for CLK = 47MHz, PERIOD = 21.28ns thus READ_DELAY >= 8 (7.28 rounded up)Refer to the “Reading Flash Pages” section of TN1204, MachXO2 Programming and Configuration Usage Guide for more information on the Read UFM command structure and timing requirements.DPRAMThe design incorporates a 32-byte (2 UFM page), byte addressable True Dual port RAM. The internal state machine accesses one port of the DPRAM. During the UFM write operation the state machine reads data from the DPRAM and writes it to the UFM. During UFM read operations the data read from the UFM is stored in the DPRAM.The second DPRAM port is accessed by the user to exchange data to or from the UFM. The DPRAM memory is divided into two pages of 16 bytes data each. The Most Significant Bit (MSB) of the DPRAM addresses are con-trolled by the internal state machine for page swapping. Thus, only one page (16 bytes) of the DPRAM is available through the user port at any given time. The available page is synchronized by the reference design and optimized for maximum throughput.During a UFM write operation, the DPRAM page swap happens once a GO is recognized. For higher throughput in back-to-back writes, this allows the user to immediately start loading the next page to be transferred to the UFM. During a read operation, the DPRAM page swap happens at the end of a read UFM operation and the user can start reading the DPRAM data once BUSY signal is low. In the case of back-to-back Read operations, the data remains available in the DPRAM until the subsequent Read is complete, allowing for higher throughput operation. CommandsTable 2. List of CommandsCommand Operation BUSY Signal Page Swap 000Read 1 page Clear when finished End of transaction001Read next page Clear when finished End of transaction010Write 1 page Clear upon UFM busy clear.Beginning of transaction011Write next page Clear upon UFM busy clear Beginning of transaction100Enable UFM access Clear upon UFM busy clear.N/A101Disable UFM access Clear when finished N/A110(undefined)––111Erase UFM Clear upon UFM busy clear N/ACommand Descriptions•Enable UFM access (100) – Required to enable UFM read/write access. Exercising this command will tempo-rarily disable certain features of the device, notably GSR, User SPI port and Power Controller. These features are restored when UFM access is disabled using Disable UFM access command (101). See TN1246, MachXO2 EFB User’s Guide, for more information on this behavior. BUSY is asserted until the devices internal Flash pumps are fully charged.•Write 1 page (010) – The 16 bytes of data from DPRAM is written into the UFM page specified by UFM_PAGE. The internal UFM page pointer is auto incremented at the completion of the command. Make sure that 16 bytes of data that has to be written to the UFM is loaded to the DPRAM prior to issuing a GO. BUSY will be asserted as soon as a GO is recognized and will be de-asserted when programming is complete.•Write next page (011) – The 16 bytes of data from DPRAM are written into the subsequent UFM page pointed by the internal UFM page pointer. The internal UFM page pointer is auto-incremented at the completion of thecommand. Make sure that 16 bytes of data that has to be written to the UFM is loaded to the DPRAM prior to issuing a GO. BUSY will be asserted as soon as a GO is recognized and will be de-asserted when programming is complete.•Read 1 page (000) – 16 bytes of data is read back from the UFM page specified by UFM_PAGE and stored in the DPRAM. The internal UFM page pointer is auto-incremented at the completion of the command. Following a Read command, the 16 bytes of UFM data can be read from the DPRAM after BUSY de-asserts.•Read next page (011) – The subsequent UFM page pointed by the internal UFM page pointer is read and stored into the DPRAM. The internal UFM page pointer is auto-incremented at the completion of the command. Follow-ing a Read command, the 16 bytes of UFM data can be read from the DPRAM after BUSY de-asserts.•Disable UFM access (101) – This command disables UFM interface for change access.•Erase UFM (111) – This command is issued to completely erase (set to ‘0’) the UFM. BUSY is asserted until era-sure is complete.Typical Command SequencesNotes:• A GO will be ignored when BUSY is asserted.•Any UFM read/write or erase command while UFM is disabled will assert the ERR signal.Write to UFMThe following sequence explains the necessary commands to be followed for a UFM write operation. The sequence assumes the target UFM row is in the erased state.1.Enable UFM access (100) – Check for BUSY signal to be low and issue enable UFM command on theCMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.2.Write 1 page (010) – Load the DPRAM with one page (16 bytes) of data to be written to the UFM. Checkfor BUSY signal to be low, issue the Write 1 Page command on the CMD bus, UFM page address on the UFM_PAGE bus and issue a GO. The DPRAM page swap happens once a GO is recognized so that the user can load the next page to be written to the UFM into the DPRAM while the first page is being trans-ferred to the UFM.3.Write next page (011) – Wait for the previous page to be transferred to the UFM successfully and theBUSY signal goes low. Now issue a write next page command and issue GO. The internal UFM pagepointer is auto-incremented.4.Repeat steps 2 and 3 until all desired pages are written. Figure 2 illustrates steps 2 and 3.5.Disable UFM access (101) – Check for BUSY signal to be low and issue disable UFM command on theCMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.Figure 2. Write to UFM Waveform DescriptionRead from UFMThe following sequence explains the necessary commands to be followed for a UFM read operation.1.Enable UFM access (100) – Check for the BUSY signal to be low and issue an enable UFM commandon the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.2.Read 1 page (000) – Check for BUSY signal to be low, issue the Read 1 Page command on the CMDbus, UFM page address on the UFM_PAGE bus and issue a GO. Data read from UFM will be loaded in the DPRAM and user can access the data once BUSY signal goes low.3.Read next page (011) – Check for the BUSY signal to be low, issue the read next page command on theCMD bus and issue a GO. The internal UFM page pointer is auto. Data read from UFM will be loaded in the DPRAM and user can access the data once the BUSY signal goes low.4.Repeat steps 2 and 3 until all desired pages have been read. Figure 3 illustrates steps 2 and 3.5.Disable UFM access (101) – Check for the BUSY signal to be low and issue a disable UFM commandon the CMD bus and issue a GO. The BUSY signal is asserted once a GO is recognized.Figure 3. Read from UFM Waveform DescriptionRead Modify Write Back to UFMThe page read from UFM can be retained in the DPRAM and data modification may be performed directly on the DPRAM, followed by a Write 1 Page operation. The following sequence explains the necessary commands to be followed in order to modify the contents of UFM.Note: The modified data cannot be arbitrary. Only erased bits/bytes (=‘0’) of the UFM can be given new values. This sequence is provided to support applications where small amounts of data, or data unaligned to UFM page boundaries, is accumulated over time (e.g. a data logger application).1.Enable UFM access (100) – Check for BUSY signal to be low and issue an enable UFM command onthe CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.2.Read 1 page (000) – Check for BUSY signal to be low, issue the Read 1 Page command on the CMDbus, UFM page address on the UFM_PAGE bus and issue a GO. Data read from the UFM will be loaded in the DPRAM and is available to read or edit once the BUSY signal goes low.3.Modify DPRAM data as needed. The DPRAM data is byte addressable. The user may modify theintended byte(s) directly in the DPRAM. Alternatively, the data may be read from, and re-written to, theDPRAM.4.Write 1 page (010) – Once the data in the DPRAM has been modified or re-written, check for the BUSYsignal to be low, issue the Write 1 Page command on the CMD bus, set the UFM page address on theUFM_PAGE bus and issue a GO. Note that UFM page address must be specified for both read and write.5.Repeat steps 2 through 4 until all desired pages have been modified. Figure 4 illustrates steps 2through 4.6.Disable UFM access (101) – Check for the BUSY signal to be low and issue a disable UFM commandon the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.Figure 4. Read-Modify and Write Back to UFM Waveform DescriptionHDL Simulation and VerificationEnable CommandFigure 5. Enable Command HDL Simulation WaveformWrite CommandFigure 6. Loading of DPRAM HDL Simulation WaveformFigure 7. Write to UFM Command Sequence HDL Simulation WaveformRead CommandFigure 8. Read from UFM Command Sequence HDL Simulation WaveformDisable CommandFigure 9. Disable Command HDL Simulation WaveformImplementationTable 3. Performance and Resource UtilizationTechnical Support AssistanceHotline:1-800-LATTICE (North America)+1-503-268-8001 (Outside North America)e-mail:techsupport@ Internet:Revision HistoryFamily Language Speed GradeUtilization fmax (MHZ)I/Os Architecture Resources MachXO21Verilog-3239 LUTs>50421- EFB1- EBR1. Performance and utilization characteristics are generated using LCMXO2-1200ZE-3TG100C with Lattice Diamond ® 1.4 design software.Date Version Change SummaryApril 201201.0Initial release.June 201201.1Updated design and document to include READ_DELAY parameteriza-tion.Appendix A. UFM Command SequencesThe following table explains the different UFM internal command structure involved for the various operations of this reference design.Table 4. MachXO2 Embedded Function Block CommandsOperation Command (Hex)Operand (Hex)Write Data Read Data Enable UFM Access (100)Enable UFM74 08 00 00——Status check F000 00 00— 1 byte status data Write One Page (010)Set Address B400 00 0040 00 aa aa1—Write UFM C900 00 0116 bytes data fromDPRAM—Status check F000 00 00— 1 byte status data Write Next Page (011)Write UFM C900 00 0116 bytes data fromDPRAM—Status check F000 00 00— 1 byte status data Read One Page (000)Set Address B400 00 0040 00 aa aa1—Read UFM CA10 00 01—16 bytes data from UFM Read Next Page (011)Read UFM CA10 00 01—16 bytes data from UFM Disable UFM Access (101)Disable UFM2600 00 00——Bypass FF FF FF FF——Erase UFM (111)Erase UFM0E08 00 00——Status check F000 00 00— 1 byte status data 1.The aa aa value is copied from the 11-bit UFM_PAGE module input.。

LATTICE XP2