K4B1G0446C中文资料

BZX84C16LT1G中文资料

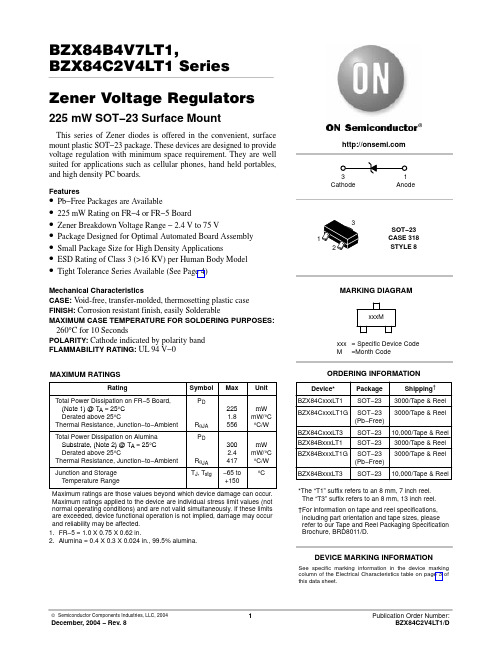

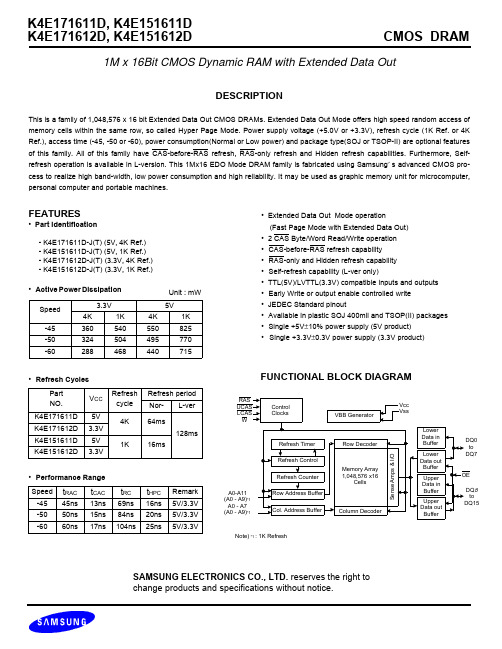

BZX84B4V7LT1,BZX84C2V4LT1 Series Zener Voltage Regulators225 mW SOT−23 Surface MountThis series of Zener diodes is offered in the convenient, surface mount plastic SOT−23 package. These devices are designed to provide voltage regulation with minimum space requirement. They are well suited for applications such as cellular phones, hand held portables,and high density PC boards.Features•Pb−Free Packages are Available•225 mW Rating on FR−4 or FR−5 Board•Zener Breakdown V oltage Range − 2.4 V to 75 V•Package Designed for Optimal Automated Board Assembly •Small Package Size for High Density Applications•ESD Rating of Class 3 (>16 KV) per Human Body Model •Tight Tolerance Series Available (See Page 4)Mechanical CharacteristicsCASE: V oid-free, transfer-molded, thermosetting plastic case FINISH: Corrosion resistant finish, easily SolderableMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES:260°C for 10 SecondsPOLARITY: Cathode indicated by polarity band FLAMMABILITY RATING: UL 94 V−0MAXIMUM RATINGSMaximum ratings are those values beyond which device damage can occur.Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.FR−5 = 1.0 X 0.75 X 0.62 in.2.Alumina = 0.4 X 0.3 X 0.024 in., 99.5% alumina.See specific marking information in the device marking column of the Electrical Characteristics table on page 3 of this data sheet.DEVICE MARKING INFORMATION(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°Cunless otherwise noted, V F = 0.95 V Max. @ I F = 10 mA)ELECTRICAL CHARACTERISTICS − BZX84CxxxLT1 SERIES (STANDARD TOLERANCE) (Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA) (Devices listed in bold, italic are ON Semiconductor Preferred devices.)Z*The “G” suffix indicates Pb−Free package available.ELECTRICAL CHARACTERISTICS − BZX84BxxxL (Tight Tolerance Series)(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA)Z*The “G” suffix indicates Pb−Free package available.V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θV Z , NOMINAL ZENER VOLTAGE (V)− 3− 2012345678Figure 1. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ100101V Z , NOMINAL ZENER VOLTAGE (V)Figure 2. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , NOMINAL ZENER VOLTAGEFigure 3. Effect of Zener Voltage onZener ImpedanceZ Z T , D Y N A M I C I M P E D A N C E ()Ω1000100101V F , FORWARD VOLTAGE (V)Figure 4. Typical Forward VoltageI F , F O R W A R D C U R R E N T (m A )1000100101C , C A P A C I T A N C E (p F )V Z , NOMINAL ZENER VOLTAGE (V)Figure 5. Typical Capacitance 1000100101V Z , ZENER VOLTAGE (V)1001010.10.01I Z , Z E N ER C U R R E N T (m A )V Z , ZENER VOLTAGE (V)1001010.10.01I R , L E A K A G E C U R R E N T (A )µV Z , NOMINAL ZENER VOLTAGE (V)Figure 6. Typical Leakage Current10001001010.10.010.0010.00010.00001I Z , Z E N E R C U R R E N T (m A )Figure 7. Zener Voltage versus Zener Current(V Z Up to 12 V)Figure 8. Zener Voltage versus Zener Current(12 V to 91 V)PACKAGE DIMENSIONSSOT−23TO−236AB CASE 318−09ISSUE AK*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ǒmm inchesǓSCALE 10:1ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

K4B1G1646E-HCH9 PDF 规格书

2. Key Features................................................................................................................................................................. 5

8. AC & DC Input Measurement Levels ............................................................................................................................ 14 8.1 AC & DC Logic input levels for single-ended signals .............................................................................................. 14 8.2 VREF Tolerances...................................................................................................................................................... 15 8.3 AC & DC Logic Input Levels for Differential Signals ............................................................................................... 16 8.3.1. Differential signals definition ............................................................................................................................ 16 8.3.2. Differential swing requirement for clock (CK - CK) and strobe (DQS - DQS) .................................................. 16 8.3.3. Single-ended requirements for differential signals ........................................................................................... 17 8.4 Differential Input Cross Point Voltage...................................................................................................................... 18 8.5 Slew rate definition for Differential Input Signals ..................................................................................................... 18 8.6 Slew rate definitions for Differential Input Signals ................................................................................................... 18

K4T1G164QQ资料

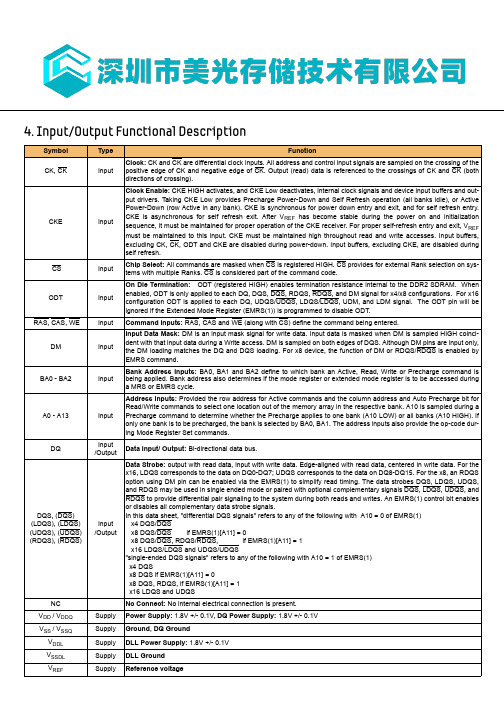

1Gb Q-die DDR2 SDRAM Specification60FBGA & 84FBGA with Pb-Free & Halogen-Free(RoHS compliant)INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDEDON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.1. For updates or additional information about Samsung products, contact your nearest Samsung office.2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure couldresult in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.* Samsung Electronics reserves the right to change products or specification without notice.Table of Contents1.0 Ordering Information (4)2.0 Key Features (4)3.0 Package Pinout/Mechanical Dimension & Addressing (5)3.1 x4/x8 package pinout (Top View) : 60ball FBGA Package (5)3.2 x16 package pinout (Top View) : 84ball FBGA Package (6)3.3 FBGA Package Dimension (x4/x8) (7)3.4 FBGA Package Dimension (x16) (8)4.0 Input/Output Functional Description (9)5.0 DDR2 SDRAM Addressing (10)6.0 Absolute Maximum DC Ratings (11)7.0 AC & DC Operating Conditions (11)7.1 Recommended DC Operating Conditions (SSTL - 1.8) (11)7.2 Operating Temperature Condition (12)7.3 Input DC Logic Level (12)7.4 Input AC Logic Level (12)7.5 AC Input Test Conditions (12)7.6 Differential input AC logic Level (13)7.7 Differential AC output parameters (13)8.0 ODT DC electrical characteristics (13)9.0 OCD default characteristics (14)10.0 IDD Specification Parameters and Test Conditions (15)11.0 DDR2 SDRAM IDD Spec Table (17)12.0 Input/Output capacitance (18)13.0 Electrical Characteristics & AC Timing for DDR2-800/667 (18)13.1 Refresh Parameters by Device Density (18)13.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin (18)13.3 Timing Parameters by Speed Grade (19)14.0 General notes, which may apply for all AC parameters (21)15.0 Specific Notes for dedicated AC parameters (23)Revision HistoryRevision Month Year History1.0September2007 - Initial Release1.01November2007 - Typo CorrectionSpeed DDR2-800 5-5-5DDR2-800 6-6-6DDR2-667 5-5-5Units CAS Latency 565tCK tRCD(min)12.51515ns tRP(min)12.51515ns tRC(min)57.56060nsNote :1. Speed bin is in order of CL-tRCD-tRP.2. RoHS Compliant.3. “H” of Part number(12th digit) stand for RoHS compliant and Halogen-free products.Org.DDR2-800 5-5-5DDR2-800 6-6-6DDR2-667 5-5-5Package 256Mx4K4T1G044QQ-HC(L)E7K4T1G044QQ-HC(L)F7K4T1G044QQ-HC(L)E660 FBGA 128Mx8K4T1G084QQ-HC(L)E7K4T1G084QQ-HC(L)F7K4T1G084QQ-HC(L)E660 FBGA 64Mx16K4T1G164QQ-HC(L)E7K4T1G164QQ-HC(L)F7K4T1G164QQ-HC(L)E684 FBGA•JEDEC standard 1.8V ± 0.1V Power Supply •VDDQ = 1.8V ± 0.1V•333MHz f CK for 667Mb/sec/pin, 400MHz f CK for 800Mb/sec/pin •8 Banks •Posted CAS•Programmable CAS Latency: 3, 4, 5, 6•Programmable Additive Latency: 0, 1, 2, 3, 4, 5•Write Latency(WL) = Read Latency(RL) -1•Burst Length: 4 , 8(Interleave/nibble sequential)•Programmable Sequential / Interleave Burst Mode •Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)•Off-Chip Driver(OCD) Impedance Adjustment •On Die Termination•Special Function Support- PASR(Partial Array Self Refresh)- 50ohm ODT- High Temperature Self-Refresh rate enable •Average Refresh Period 7.8us at lower than T CASE 85°C, 3.9us at 85°C < T CASE < 95 °C •All of Lead-free products are compliant for RoHSThe 1Gb DDR2 SDRAM is organized as a 32Mbit x 4 I/Os x 8banks, 16Mbit x 8 I/Os x 8banks or 8Mbit x 16 I/Os x 8 banks device. This synchronous device achieves high speed double-data-rate transfer rates of up to 800Mb/sec/pin (DDR2-800) for general applications.The chip is designed to comply with the following key DDR2SDRAM features such as posted CAS with additive latency, write latency = read latency - 1, Off-Chip Driver(OCD) impedance adjustment and On Die Termination.All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the crosspoint of differential clocks (CK rising and CK falling). All I/Os are synchronized with a pair of bidirectional strobes (DQS and DQS) in a source synchronous fashion. The address bus is used to convey row, column, and bank address information in a RAS/CAS multiplexing style. For example, 1Gb(x8) device receive 14/10/3 addressing.The 1Gb DDR2 device operates with a single 1.8V ±0.1V power supply and 1.8V ±0.1V VDDQ.The 1Gb DDR2 device is available in 60ball FBGAs(x4/x8) and in 84ball FBGAs(x16).Note : The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.Note : This data sheet is an abstract of full DDR2 specification and does not cover the common features which are described in “DDR2 SDRAM Device Operation & Timing Diagram”.1.0 Ordering Information2.0 Key FeaturesNote:1. Pins B3 and A2 have identical capacitance as pins B7 and A8.2. For a read, when enabled, strobe pair RDQS & RDQS are identical in function and timing to strobe pair DQS & DQS and input masking function is disabled.3. The function of DM or RDQS/RDQS are enabled by EMRS command.4. VDDL and VSSDL are power and ground for the DLL.A B C D E F G H J K LVDD NU/VSSDQ6VSSQ VDDQ VDDQ VDDQ VSSQ VSSQ DQS DQS DQ7DQ0VDDQ DQ2VSSQ DQ5VSSDL VDD CK RAS CK CAS CS A2A6A4A11A8NCA13NCA12A9A7A5A0VDD A10/APVSSVDDQ VSSQ DQ1DQ3DQ4VDDLA1A3BA1VREF VSS CKEWE BA01 2 3 7 8 9VDDVSS ODTBA2Ball Locations (x4/x8): Populated Ball +: Depopulated BallTop View (See the balls through the Package)++++++++++++++++++++++++++++++123456789A B C D E F G H J K L++++++++DM /RDQSRDQS+3.1 x4/x8 package pinout (Top View) : 60ball FBGA Package3.0 Package Pinout/Mechanical Dimension & AddressingNote :1. VDDL and VSSDL are power and ground for the DLL.2. In case of only 8 DQs out of 16 DQs are used, LDQS, LDQSB and DQ0~7 must be used.A B C D E F G H J K L VDD NC VSS DQ14VSSQ UDM VDDQ VDDQ VDDQ VSSQ VSSQ UDQS UDQS DQ15DQ8VDDQ DQ10VSSQ DQ13VSSQ VDDQ RAS CK CAS CS A2A6A4A11A8NCNCNCA12A9A7A5A0VDDA10/APVSSVDDQ VSSQ DQ9DQ11DQ12VDD A1A3BA1NC VSS CKEWE BA0 1 2 3 7 8 9VDDVSSODTBA2Ball Locations (x16): Populated Ball +: Depopulated BallTop View (See the balls through the Package)M N P RDQ6VSSQ LDM VDDQ VDDQ VSSQ LDQS DQ7DQ0VDDQ DQ2VSSQ DQ5VSSDL VDD CK VDDQ VSSQ DQ1DQ3DQ4VDDLVREF VSS LDQS 123456789++++++++++++++++++++++++++++++++++++++++++++++++++A B C D E F G H J K L M N P R+3.2 x16 package pinout (Top View) : 84ball FBGA Package3.3 FBGA Package Dimension (x4/x8)A B CD E F H J K LG3.4 FBGA Package Dimension (x16)A B C D E FH J K L M N P RGSymbol Type FunctionCK, CK Input Clock:CK and CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).CKE Input Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and out-put drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit, and for self refresh entry. CKE is asynchronous for self refresh exit. After V REF has become stable during the power on and initialization swquence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh entry and exit, V REF must be maintained to this input. CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK, ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during self refresh.CS Input Chip Select: All commands are masked when CS is registered HIGH. CS provides for external Rank selection on sys-tems with multiple Ranks. CS is considered part of the command code.ODT Input On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is only applied to each DQ, DQS, DQS, RDQS, RDQS, and DM signal for x4/x8 configurations. For x16 configuration ODT is applied to each DQ, UDQS/UDQS, LDQS/LDQS, UDM, and LDM signal. The ODT pin will be ignored if the Extended Mode Register (EMRS(1)) is programmed to disable ODT.RAS, CAS, WE Input Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.DM Input Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coinci-dent with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For x8 device, the function of DM or RDQS/RDQS is enabled by EMRS command.BA0 - BA2Input Bank Address Inputs: BA0, BA1 and BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS or EMRS cycle.A0 - A13Input Address Inputs: Provided the row address for Active commands and the column address and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code dur-ing Mode Register Set commands.DQ Input/Out-putData Input/ Output: Bi-directional data bus.DQS, (DQS)(LDQS), (LDQS) (UDQS), (UDQS) (RDQS), (RDQS)Input/Out-putData Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15. For the x8, an RDQS option using DM pin can be enabled via the EMRS(1) to simplify read timing. The data strobes DQS, LDQS, UDQS, and RDQS may be used in single ended mode or paired with optional complementary signals DQS, LDQS, UDQS, and RDQS to provide differential pair signaling to the system during both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe signals.In this data sheet, "differential DQS signals" refers to any of the following with A10 = 0 of EMRS(1)x4 DQS/DQSx8 DQS/DQS if EMRS(1)[A11] = 0x8 DQS/DQS, RDQS/RDQS, if EMRS(1)[A11] = 1x16 LDQS/LDQS and UDQS/UDQS"single-ended DQS signals" refers to any of the following with A10 = 1 of EMRS(1)x4 DQSx8 DQS if EMRS(1)[A11] = 0x8 DQS, RDQS, if EMRS(1)[A11] = 1x16 LDQS and UDQSNC No Connect: No internal electrical connection is present.V DD/V DDQ Supply Power Supply: 1.8V +/- 0.1V, DQ Power Supply: 1.8V +/- 0.1V V SS/V SSQ Supply Ground, DQ GroundV DDL Supply DLL Power Supply: 1.8V +/- 0.1VV SSDL Supply DLL GroundV REF Supply Reference voltage4.0 Input/Output Functional Description5.0 DDR2 SDRAM Addressing1Gb AddressingConfiguration256Mb x4128Mb x 864Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A13A0 ~ A13A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A9 * Reference information: The following tables are address mapping information for other densities.256MbConfiguration64Mb x432Mb x 816Mb x16 # of Bank444Bank Address BA0,BA1BA0,BA1BA0,BA1Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A12A0 ~ A12A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A8512MbConfiguration128Mb x464Mb x 832Mb x16 # of Bank444Bank Address BA0,BA1BA0,BA1BA0,BA1Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A13A0 ~ A13A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A92GbConfiguration512Mb x4256Mb x 8128Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A14A0 ~ A14A0 ~ A13Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A9 4GbConfiguration 1 Gb x4512Mb x 8256Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 - A15A0 - A15A0 - A14 Column Address/page size A0 - A9,A11 A0 - A9 A0 - A9Note :1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. Storage Temperature is the case surface temperature on the center/top side of the DRAM.Symbol ParameterRating Units Notes V DD Voltage on V DD pin relative to V SS - 1.0 V ~ 2.3 V V 1V DDQ Voltage on V DDQ pin relative to V SS - 0.5 V ~ 2.3 V V 1V DDL Voltage on V DDL pin relative to V SS - 0.5 V ~ 2.3 V V 1V IN, V OUT Voltage on any pin relative to V SS - 0.5 V ~ 2.3 V V1T STGStorage Temperature-55 to +100°C 1, 2Note : There is no specific device V DD supply voltage requirement for SSTL-1.8 compliance. However under all conditions V DDQ must be less than or equalto V DD .1. The value of V REF may be selected by the user to provide optimum noise margin in the system. Typically the value of V REF is expected to be about 0.5 x V DDQ of the transmitting device and V REF is expected to track variations in V DDQ .2. Peak to peak AC noise on V REF may not exceed +/-2% V REF (DC).3. V TT of transmitting device must track V REF of receiving device.4. AC parameters are measured with V DD , V DDQ and V DDL tied together.Symbol ParameterRatingUnits NotesMin.Typ. Max.V DD Supply Voltage 1.7 1.8 1.9V V DDL Supply Voltage for DLL 1.7 1.8 1.9V 4V DDQ Supply Voltage for Output 1.7 1.8 1.9V 4V REF Input Reference Voltage 0.49*V DDQ 0.50*V DDQ0.51*V DDQ mV 1,2V TTTermination VoltageV REF -0.04V REFV REF +0.04V37.0 AC & DC Operating Conditions6.0 Absolute Maximum DC Ratings7.1 Recommended DC Operating Conditions (SSTL - 1.8)7.2 Operating Temperature Condition1.Operating Temperature is the case surface temperature on the center/top side of the DRAM.2.At 85 - 95 °C operation temperature range, doubling refresh commands in frequency to a 32ms period ( tREFI=3.9 us ) is required, and to enter to self refresh mode at this temperature range, an EMRS command is required to change internal refresh rate.7.3 Input DC Logic Level7.4 Input AC Logic Level7.5 AC Input Test ConditionsNote :1. Input waveform timing is referenced to the input signal crossing through the V IH/IL (AC) level applied to the device under test.2. The input signal minimum slew rate is to be maintained over the range from V REF to V IH (AC) min for rising edges and the range from V REF to V IL (AC)max for falling edges as shown in the below figure.3. AC timings are referenced with input waveforms switching from V IL (AC) to V IH (AC) on the positive transitions and V IH (AC) to V IL (AC) on the negative transitions.Symbol Parameter Rating UnitsNotesTOPEROperating Temperature0 to 95°C 1, 2Symbol Parameter Min.Max.Units NotesV IH (DC)DC input logic high V REF + 0.125V DDQ + 0.3V V IL (DC)DC input logic low- 0.3V REF - 0.125VSymbol ParameterDDR2-667, DDR2-800Units Min.Max.V IH (AC)AC input logic high V REF + 0.200V V IL (AC)AC input logic lowV REF - 0.200VSymbol Condition Value Units Notes V REF Input reference voltage0.5 * V DDQV 1V SWING(MAX)Input signal maximum peak to peak swing1.0V 1SLEWInput signal minimum slew rate1.0V/ns2, 3V DDQ V IH (AC) minV IH (DC) min V REFV IL (DC) max V IL (AC) maxV SS< AC Input Test Signal Waveform >V SWING(MAX)delta TRdelta TFV REF - V IL (AC) maxdelta TFFalling Slew =Rising Slew =V IH (AC) min - V REFdelta TRV DDQCrossing pointV SSQV TR V CPV IDV IX or V OX< Differential signal levels >7.6 Differential input AC logic LevelNote :1. V ID (AC) specifies the input differential voltage |V TR -V CP | required for switching, where V TR is the true input signal (such as CK, DQS, LDQS or UDQS) and V CP is the complementary input signal (such as CK, DQS, LDQS or UDQS). The minimum value is equal to V IH (AC) - V IL (AC).2. The typical value of V IX (AC) is expected to be about 0.5 * VDDQ of the transmitting device and V IX (AC) is expected to track variations in VDDQ . V IX (AC) indicates the voltage at which differential input signals must cross.7.7 Differential AC output parametersNote :1. The typical value of V OX (AC) is expected to be about 0.5 * VDDQ of the transmitting device and V OX (AC) is expected to track variations in VDDQ . V OX (AC) indicates the voltage at which differential output signals must cross.Symbol ParameterMin.Max.Units Notes V ID(AC)AC differential input voltage 0.5V DDQ + 0.6V 1V IX(AC)AC differential cross point voltage0.5 * VDDQ - 0.1750.5 * VDDQ + 0.175V2Symbol ParameterMin.Max.Units Note V OX (AC)AC differential cross point voltage0.5 * VDDQ - 0.1250.5 * VDDQ + 0.125V1Note : Test condition for Rtt measurementsMeasurement Definition for Rtt(eff):Apply V IH (ac) and V IL (ac) to test pin separately, then measure current I(V IH (ac)) and I( V IL (ac)) respectively. V IH (ac), V IL (ac), and VDDQ values defined in SSTL_18Measurement Definition for VM: Measure voltage (V M ) at test pin (midpoint) with no load.PARAMETER/CONDITIONSYMBOL MIN NOM MAX UNITS NOTES Rtt effective impedance value for EMRS(A6,A2)=0,1; 75 ohm Rtt1(eff)607590ohm 1Rtt effective impedance value for EMRS(A6,A2)=1,0; 150 ohm Rtt2(eff)120150180ohm 1Rtt effective impedance value for EMRS(A6,A2)=1,1; 50 ohm Rtt3(eff)405060ohm 1Deviation of VM with respect to VDDQ/2delta VM- 6+ 6%1Rtt(eff) =V IH (ac) - V IL (ac)I(V IH (ac)) - I(V IL (ac))delta VM =2 x Vm VDDQx 100%- 18.0 ODT DC electrical characteristicsNote :1. Absolute Specifications (0°C ≤ T CASE ≤ +95°C; VDD = +1.8V ±0.1V, VDDQ = +1.8V ±0.1V)2. Impedance measurement condition for output source dc current: VDDQ = 1.7V; VOUT = 1420mV; (VOUT-VDDQ)/Ioh must be less than 23.4 ohms for values of VOUT between VDDQ and VDDQ- 280mV. Impedance measurement condition for output sink dc current: VDDQ = 1.7V; VOUT = 280mV; VOUT/Iol must be less than 23.4 ohms for values of VOUT between 0V and 280mV.3. Mismatch is absolute value between pull-up and pull-dn, both are measured at same temperature and voltage.4. Slew rate measured from V IL (AC) to V IH (AC).5. The absolute value of the slew rate as measured from DC to DC is equal to or greater than the slew rate as measured from AC to AC. This is guaranteed by design and characterization.6. This represents the step size when the OCD is near 18 ohms at nominal conditions across all process and represents only the DRAM uncertainty. Output slew rate load :7. DRAM output slew rate specification applies to 667Mb/sec/pin and 800Mb/sec/pin speed bins.8. Timing skew due to DRAM output slew rate mis-match between DQS / DQS and associated DQs is included in tDQSQ and tQHS specification.DescriptionParameterMinNomMaxUnit Notes Output impedanceNormal 18ohmsSee full strength default driver characteristics ohms 1,2Output impedance step size for OCD calibration 0 1.5ohms 6Pull-up and pull-down mismatch 04ohms 1,2,3Output slew rateSout 1.55V/ns1,4,5,6,7,825 ohmsV TTOutput (V OUT)Reference Point9.0 OCD default characteristics(IDD values are for full operating range of Voltage and Temperature, Notes 1 - 5)Symbol Proposed Conditions Units NotesIDD0Operating one bank active-precharge current;t CK = t CK(IDD), t RC = t RC(IDD), t RAS = t RASmin(IDD); CKE is HIGH, CS\ is HIGH between valid commands;Address bus inputs are SWITCHING; Data bus inputs are SWITCHINGmAIDD1Operating one bank active-read-precharge current;IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; t CK = t CK(IDD), t RC = t RC (IDD), t RAS = t RASmin(IDD), t RCD =t RCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address businputs are SWITCHING; Data pat-tern is same as IDD4WmAIDD2P Precharge power-down current;All banks idle; t CK = t CK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are FLOATINGmAIDD2Q Precharge quiet standby current;All banks idle; t CK = t CK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputsare STABLE; Databus inputs are FLOATINGmAIDD2N Precharge standby current;All banks idle; t CK = t CK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are SWITCHING;Data bus inputs are SWITCHINGmAIDD3P Active power-down current;All banks open; t CK = t CK(IDD); CKE is LOW; Other control and address businputs are STABLE; Data bus inputs are FLOATINGFast PDN Exit MRS(12) = 0mASlow PDN Exit MRS(12) = 1mAIDD3N Active standby current;All banks open; t CK = t CK(IDD), t RAS = t RASmax(IDD), t RP = t RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHINGmAIDD4W Operating burst write current;All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; t CK = t CK(IDD), t RAS = t RASmax(IDD), t RP= t RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data businputs are SWITCHINGmAIDD4R Operating burst read current;All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; t CK = t CK(IDD), t RAS = t RAS-max(IDD), t RP = t RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCH-ING; Data pattern is same as IDD4WmAIDD5B Burst auto refresh current;t CK = t CK(IDD); Refresh command at every t RFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid com-mands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHINGmAIDD6Self refresh current;CK and CK\ at 0V; CKE ≤ 0.2V; Other control and address bus inputs areFLOATING; Data bus inputs are FLOATINGNormal mALow Power mAIDD7Operating bank interleave read current;All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = t RCD(IDD)-1*t CK(IDD); t CK = t CK(IDD), t RC= t RC(IDD), t RRD = t RRD(IDD), t FAW = t FAW(IDD), t RCD = 1*t CK(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R; Refer to the fol-lowing page for detailed timing conditionsmA10.0 IDD Specification Parameters and Test ConditionsNote :1. IDD specifications are tested after the device is properly initialized2. Input slew rate is specified by AC Parametric Test Condition3. IDD parameters are specified with ODT disabled.4. Data bus consists of DQ, DM, DQS, DQS\, RDQS, RDQS\, LDQS, LDQS\, UDQS, and UDQS\. IDD values must be met with all combinations of EMRS bits 10 and 11.5. Definitions for IDD LOW is defined as Vin ≤ VILAC(max) HIGH is defined as Vin ≥ VIHAC(min)STABLE is defined as inputs stable at a HIGH or LOW level FLOATING is defined as inputs at VREF = VDDQ/2 SWITCHING is defined as:inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and controlsignals, and inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.For purposes of IDD testing, the following parameters are utilizedDetailed IDD7The detailed timings are shown below for IDD7.Legend: A = Active; RA = Read with Autoprecharge; D = DeselectIDD7: Operating Current: All Bank Interleave Read operationAll banks are being interleaved at minimum t RC(IDD) without violating t RRD(IDD) and t FAW(IDD) using a burst length of 4. Control and address bus inputs are STABLE during DESELECTs. IOUT = 0mATiming Patterns for 8bank devices x4/ x8-DDR2-667 5/5/5 : A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D-DDR2-800 6/6/6 : A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D D -DDR2-800 5/5/5 : A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D DTiming Patterns for 8bank devices x16-DDR2-667 5/5/5 : A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D-DDR2-800 6/6/6 : A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D D -DDR2-800 5/5/5 : A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D DDDR2-800DDR2-800DDR2-667Units Parameter 5-5-56-6-65-5-5CL(IDD)565tCK t RCD(IDD)12.51515ns t RC(IDD)57.56060ns t RRD(IDD)-x4/x87.57.57.5ns t RRD(IDD)-x16101010ns t CK(IDD) 2.5 2.53ns t RASmin(IDD)454545ns t RP(IDD)12.51515ns t RFC(IDD)127.5127.5127.5ns(T A=0o C, VDD= 1.9V)Symbol256Mx4 (K4T1G044QQ)Unit Notes 800@CL=5800@CL=6667@CL=5CE7LE7CF7LF7CE6LE6IDD0757570mAIDD1858580mAIDD2P158158158mAIDD2Q303030mAIDD2N353535mAIDD3P-F353535mAIDD3P-S181818mAIDD3N555550mAIDD4W110110100mAIDD4R130130115mAIDD5140140135mAIDD6156156156mAIDD7245245225mA(T A=0o C, VDD= 1.9V)Symbol128Mx8 (K4T1G084QQ)Unit Notes 800@CL=5800@CL=6667@CL=5CE7LE7CF7LF7CE6LE6IDD0757570mAIDD1858580mAIDD2P158158158mAIDD2Q303030mAIDD2N353535mAIDD3P-F353535mAIDD3P-S181818mAIDD3N555550mAIDD4W115115105mAIDD4R135135120mAIDD5145145140mAIDD6156156156mAIDD7250250230mA11.0 DDR2 SDRAM IDD Spec Table(T A=0o C, VDD= 1.9V)Symbol64Mx16 (K4T1G164QQ)Unit Notes 800@CL=5800@CL=6667@CL=5CE7LE7CF7LF7CE6LE6IDD0909085mA IDD110010095mA IDD2P158158158mA IDD2Q303030mA IDD2N353535mA IDD3P-F353535mA IDD3P-S181818mA IDD3N555550mA IDD4W130130115mA IDD4R175175155mA IDD5145145140mA IDD6156156156mA IDD7265265245mASpeedDDR2-800(E7)DDR2-800(F7)DDR2-667(E6)UnitsBin (CL - tRCD - tRP)5-5-56-6-65 - 5 - 5Parameter min max min max min max tCK, CL=358--58ns tCK, CL=4 3.758 3.758 3.758ns tCK, CL=5 2.583838ns tCK, CL=6-- 2.58--ns tRCD 12.5-15-15-ns tRP 12.5-15-15-ns tRC 57.5-60-60-ns tRAS457000045700004570000ns ParameterSymbol DDR2-667DDR2-800Units Min Max Min Max Input capacitance, CK and CK CCK 1.0 2.0 1.0 2.0pF Input capacitance delta, CK and CK CDCK x 0.25x 0.25pF Input capacitance, all other input-only pins CI 1.0 2.0 1.0 1.75pF Input capacitance delta, all other input-only pins CDI x 0.25x 0.25pF Input/output capacitance, DQ, DM, DQS, DQS CIO 2.5 3.5 2.5 3.5pF Input/output capacitance delta, DQ, DM, DQS, DQSCDIOx0.5x0.5pF13.0 Electrical Characteristics & AC Timing for DDR2-800/667(0 °C < T OPER < 95 °C; V DDQ = 1.8V + 0.1V; V DD = 1.8V + 0.1V)13.1 Refresh Parameters by Device DensityParameterSymbol256Mb 512Mb 1Gb 2Gb 4Gb Units Refresh to active/Refresh command time tRFC 75105127.5195327.5ns Average periodic refresh intervaltREFI0 °C ≤ T CASE ≤ 85°C 7.87.87.87.87.8µs 85 °C < T CASE ≤ 95°C3.93.93.93.93.9µs13.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin 12.0 Input/Output capacitance。

KBA4-1.1版说明书

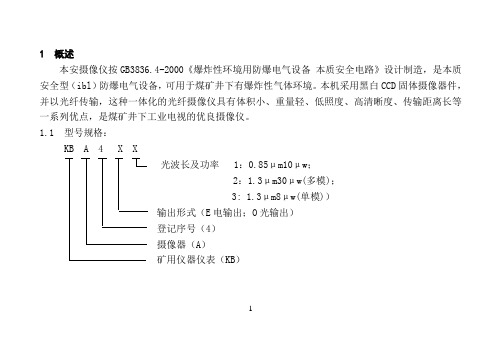

1 概述本安摄像仪按GB3836.4-2000《爆炸性环境用防爆电气设备本质安全电路》设计制造,是本质安全型(ibl)防爆电气设备,可用于煤矿井下有爆炸性气体环境。

本机采用黑白CCD固体摄像器件,并以光纤传输,这种一体化的光纤摄像仪具有体积小、重量轻、低照度、高清晰度、传输距离长等一系列优点,是煤矿井下工业电视的优良摄像仪。

1.1 型号规格:KB A 4 X X光波长及功率 1:0.85μm10μw;2:1.3μm30μw(多模);3: 1.3μm8μw(单模))输出形式(E电输出;O光输出)登记序号(4)摄像器(A)矿用仪器仪表(KB)1本机有两种规格,配以两种输出方式:KBA4-E:本安型视频信号输出,适用于传输距离不长,电磁干扰不严重的场合。

对于摄像点需经常移动的场合,如工作面等,由于光缆移动不方便,也可采用此种方式,用同轴缆传输一段距离后,再配以本安型视频光端机或KJF60D视频服务器以光缆传输至地面。

KBA4-O:光纤输出,适用于传输距离长,电磁干扰严重的场合。

光纤输出又有传输距离长短之分,当传输距离小于2Km时,为0.85um波长光输出;当传输距离大于2Km 时,为1.3um波长光输出。

本摄像仪配定焦手动光圈镜头。

其内部接线简单,电源(+18V)用矿用信号电缆直接引入到电源接线端子上;视频信号由BNC接头直接插入摄像机插座输出。

光信号输出可用光纤连接器直接插到光连接器座上(配接矿用光缆)输出。

1.2 使用条件a. 气压:80~106kpab.环境温度:-5℃~ +40℃c. 相对湿度:≤95%d. 现场安装时应由人员携带并装在振动不大于20m/s2的场所。

22 主要技术参数⑴摄像机:黑白CCD⑵照度:≥0.5Lx(CCD机芯最低照度为0.001Lx)⑶清晰度:≥400TV线⑷灰度:7级⑸本安视频信号输出:V PP=1V(负载阻抗75Ω时)⑹光纤输出:P≥10μW(λ=0.85μm)P≥30μW(λ=1.3μm(多模))P≥8μW(λ=1.3μm(单模))⑺光纤类型:多模(50/125, 62.5/125)或单模(8/125)⑻供电:直流18(+8%,-10%)V,350mA3 主要结构特征本摄像仪结构如图1所示。

CC0201KRX5R5BB104中文资料

物料编号:CC0201KRX5R5BB104的详细参数_易容网

MLCC即是多层陶瓷电容片式,是电子信息产品不可或缺的基本组件之一。

我国MLCC的生产起步在80年代初,行业早期主要是在外资企业的带动下发展起来的,近年来国内企业在技术上实现突破,行业国产化成效显著,并推动了MLCC产量迅速增长。

目前,MLCC的应用领域已从手机、电脑、电视机等消费电子领域,逐步拓展到新能源发电、新能源汽车、节能灯具、轨道交通、直流输变电、三网融合、高清电视、机顶盒、手机电视等多个行业。

对于这个悄悄活跃在人们生活中的元件你又知道多少呢.

本次易容网为大家推荐比较常用的MLCC国巨品牌的料号

CC0201KRX5R5BB104的相关参数

易容网是深圳市易容信息技术有限公司独自研发的全球最大的MLCC搜索采购服务网站,2014年创立于深圳市南山区,全国首家电子元器件行业电容元件的搜索引擎及o2o商务服务平台。

易容网()现已建成全球最大的MLCC电容搜索引擎数据库,包含全球25家电容生产厂商超过28万组MLCC产品数据,用户可根据行业应用、物料编号、规格参数等信息快速的找到所有相关的MLCC电容数据。

易容网在搜索服务的前提下还提供村田、TDK、国巨、太阳诱电、风华高科等常见品牌产品的o2o商务服务,让企业客户实现询价、报价、在线订单、出库、实时物流、签收、账期服务等在线一站式商务服务体验。

k1g-c04控制器说明书

k1g-c04控制器说明书k1g-c04控制器是一款智能化的控制设备,用于控制电力系统中的各种电气设备,达到自动化和远程控制的目的。

本说明书旨在提供用户有关该控制器的相关参考内容,包括使用指南、功能特点、技术参数及安装方法等。

一、使用指南1. 控制器的安装:将控制器固定在合适的位置,确保控制器与电力系统的连接可靠。

2. 接线方法:根据电气系统的需要,正确连接控制器与各种电气设备的线路,并确认接线无误。

3. 电源接入:确保控制器获得稳定的电源供应,避免掉电造成的数据丢失或设备故障。

4. 控制器的使用:根据实际需要,通过控制器面板或远程控制软件对电气设备进行控制和调整。

5. 控制器的维护:定期对控制器进行检查和保养,保持设备的正常运行。

二、功能特点1. 自动化控制:控制器能够自动识别电气设备的状态,并根据设定的参数进行自动控制,提高系统的运行效率。

2. 远程控制:通过远程控制软件,用户可以随时随地对电气设备进行远程监控和控制,方便快捷。

3. 数据记录和分析:控制器能够记录电气设备的工作数据,并提供数据分析功能,帮助用户了解系统的运行状况。

4. 报警功能:控制器可以监测电气设备的异常状态,并及时进行报警,提醒用户进行处理,确保设备的安全运行。

5. 多样化接口:控制器具有多种接口,可以与其他设备进行连接,实现设备之间的数据交互和共享。

三、技术参数1. 输入电压:AC220V2. 输出电压:DC24V3. 控制方式:PLC控制4. 执行器接口:可选RS485、Modbus等多种接口5. 工作温度:-10℃~60℃6. 防护等级:IP65四、安装方法1. 准备工作:确认安装位置和所需固定材料,准备安装工具。

2. 固定控制器:将控制器固定在安装位置上,使用螺丝将控制器牢固地固定在墙壁或设备上。

3. 连接电源:将电源线正确接入控制器的电源插座上,并确保电源供应的稳定性和安全性。

4. 连接电气设备:根据设备的连接要求,正确连接控制器与电气设备的线路,并注意线路的接地和绝缘性能。

SAE J434-1986 Automotive Ductile (nodular) Iron Castings

SAE Technical Standards Board Rules provide that: “This report is published by SAE to advance the state of technical and engineering sciences. The use of this report is entirely voluntary, and its applicability and suitability for any particular use, including any patent infringement arising therefrom, is the sole responsibility of the user.”SAE reviews each technical report at least every five years at which time it may be reaffirmed, revised, or cancelled. SAE invites your written comments and suggestions.QUESTIONS REGARDING THIS DOCUMENT: (412) 772-8512 FAX: (412) 776-0243TO PLACE A DOCUMENT ORDER; (412) 776-4970 FAX: (412) 776-0790SAE WEB ADDRESS 3.Grades—The specified grades, hardness range, and metallurgical description are shown in Table 1.4.Hardness4.1The area or areas on the castings where hardness is to be checked should be established by agreement between supplier and purchaser.4.2The foundry shall exercise the necessary controls and inspection techniques to insure compliance with the specified hardness range. Brinell hardness shall be determined according to ASTM E 10, Test for Brinell Hardness of Metallic Materials, after sufficient material has been removed from the casting surface to insure representative hardness readings. The 10 mm ball and 3000 kg load shall be used unless otherwise agreed upon.5.Heat Treatment5.1Unless otherwise specified, castings may be heat treated to the appropriate hardness range.5.2Appropriate heat treatment for removal of residual stresses, or to improve machinability may be specified by agreement between supplier and purchaser.6.Microstructure—The graphite component of the microstructure shall consist of at least 80% spheroidal graphite conforming to Types I and II in Figure 1. The matrix microstructure shall consist of either ferrite, ferrite and pearlite, pearlite, tempered pearlite, or tempered martensite or a combination of these. The microstructure shall be substantially free of primary cementite.TABLE 1—GRADES OF DUCTILE IRONGrade CastingHardness RangeDescriptionD4018170 HB max or as agreed (4.6 BID, min)Ferritic D4512156–217 HB or as agreed (4.80–4.10 BID)Ferritic-pearlitic D5506187–255 HB or as agreed (4.4–3.8 BID)Ferritic-pearlitic D7003241–302 HB or as agreed (3.90–3.50 BID)Pearlitic DQ&TRange specificMartensiticNOTE— Brinell impression diameter (BID) is the diameter in millimeters (mm) of the impression of a 10 mmball at 3000 kg load.FIGURE 1—CLASSIFICA TION OF GRAPHITE SHAPE IN CAST IRONS (FROM ASTM A 247)7.Quality Assurance—Sampling plans are a matter of agreement between supplier and purchaser. Thesupplier shall employ adequate equipment and controls to insure that parts conform to the agreed upon requirements.8.General8.1Castings furnished to this standard shall be representative of good foundry practice and shall conform todimensions and tolerances specified on the casting drawing.8.2Minor imperfections usually not associated with the structural functioning may occur in castings. Theseimperfections are often repairable; however, repairs should be made only in areas and by methods approved by the purchaser.8.3Additional casting requirements, such as vendor identification, other casting information, and special tesing,may be agreed upon by the purchaser and supplier. These should appear as additional product requirements on the casting drawing.9.Notes9.1Marginal Indicia—The change bar (l) located in the left margin is for the convenience of the user in locatingareas where technical revisions have been made to the previous issue of the report. An (R) symbol to the left of the document title indicates a complete revision of the report.PREPARED BY THE SAE IRON AND STEEL T ECHNICAL COMMITTEE DIVISION 9—AUTOMOTIVE IRON AND STEEL CASTINGSAPPENDIX ADUCTILE (NODULAR) IRON(A material description not a part of the standard)A.1Definition And Classification—Ductile (nodular) iron, also known as spheroidal graphite iron, is cast iron inwhich the graphite is present as spheroids, instead of flakes as in gray iron or temper carbon nodules as in malleable iron.Ductile iron castings may be used in the as-cast condition, or may be heat treated.A.2Chemical Composition—The typical chemical composition of unalloyed iron generally conforms to thefollowing ranges:T otal carbon 3.20–4.10%Silicon 1.80–3.00%Manganese0.10–1.00%Phosphorus0.015–0.10%Sulfur0.005–0.035%Individual foundries will produce to narrower ranges than those shown. The spheroidal graphite structure is produced by alloying the molten iron with small amounts of one or more elements such as magnesium or cerium.A.3MicrostructureA.3.1The microstructure of the various grades of ductile iron consists of spheroidal graphite in a matrix of eitherferrite, pearlite, tempered pearlite, tempered martensite, or certain combinations of these. The relative amounts of each of these constituents is dependent upon the grade of material specified, casting design as it affects cooling rate, and heat treatments, if any.A.3.2The matrix microstructure of as-cast ductile iron depends to a great extent on the solidification rate and coolingrate of the casting, as shown in Figure A1. If a section solidifies rapidly, especially sections of 0.25 in (6mm) or less, an appreciable amount of carbide may be present in the casting. If a section cools slowly, as in a massive, heavy casting, a largely ferritic matrix may result.FIGURE A1—EXAMPLE OF MICROSTRUCTURAL VARIATION WHICH MAY OCCUR IN AS-CAST CONDITION AS FUNCTION OF METAL THICKNESS (THA T IS, SOLIDIFICA TION RA TE)A.3.3Alloying elements can also alter the microstructure usually resulting in increased amounts of pearlite. Largevariations in structure can be eliminated or minimized by modifying the casting design or the runner system or both, or by controlled cooling, or any combination of these. Primary carbides, and/or pearlite can be decomposed by appropriate heat treatments.A.3.4A rim may occur on heat treated castings consisting of a graphite-free layer sometimes containing more or lesscombined carbon than the underlying material.A.3.5Typical microstructure of the grades of ductile iron are as follows:D4018 is annealed ferritic ductile iron. The annealing time and temperature cycle is such that primary carbides, if present in the as-cast structure, are decomposed, and the resulting matrix is ferritic as shown in Figure A2.FIGURE A2—D4018, APPROXIMATE 156 HB (100X) TYPICAL MICROSTRUCTURESD4512 is ferritic ductile iron supplied either as cast or heat treated. The matrix, shown in Figure A3, is essentially ferrite but this grade can contain pearlite, depending on the section size.FIGURE A3—D4512, APPROXIMATE 179 HB (100X) TYPICAL MICROSTRUCTURESD5506 is ferritic-pearlite ductile iron suppied either as-cast or heat treated. The matrix, shown in Figure A4, is essentially pearlite. This grade may contain substantially more ferrite.FIGURE A4—D5506, APPROXIMATE 235 HB (100X) TYPICAL MICROSTRUCTURESD7003 (not shown) is generally air or liquid quenched and tempered to a specified hardness range. The resulting matrix is tempered pearlite or tempered martensite. Time and temperature before hardening can be such that primary carbides are decomposed.DQ&T is a liquid quenched and tempered grade. The resulting matrix is tempered martensite. The Brinell hardness range is a matter of agreement between supplier and purchaser.A.4Mechanical PropertiesA.4.1The mechanical properties listed in Table A1 are intended as guidelines; but, since properties may vary withlocation in a given casting, the suitability of a particular metal for an intended use is best determined by laboratory or service tests.A.4.2The mechanical properties will vary with the microstructure which, especially in the as-cast condition, is dependent on section size as well as chemical composition and some foundry processes.A.4.3For optimum mechanical properties in the quenched and tempered grade, section size for unalloyed iron should generally not exceed 3/4 in (19 mm) to insure a uniform, through-hardened structure.A.5Typical ApplicationsA.5.1D4018 is used in moderately stressed parts requiring high ductility and good machinability, such as automotive suspension parts.A.5.2D4512 is used for moderately stressed parts where machinability is less important, such as differential cases and carriers.A.5.3D5506 is used for more highly stressed parts, such as automotive crankshafts.A.5.4D7003 is used where high strength and/or improved wear resistance are required and where selective hardening is to be employed.A.5.5DQ&T is used where the uniformity of a heat treated material is required to control the range of mechanical properties or machinability.TABLE A1—TYPICAL MECHANICAL PROPERTIES FOR DUCTILE IRONS (1)1.These properties were obtained on separately cast test bars and may vary in various sections of a casting depending on composi-tion and cooling rate.Grade HardnessRange (2)2.Brinell impression diameter (BID) is the diameter in millimeters (mm) of the impression of a 10 mm ball at 3000 kg load.Description Tensile Strength,psi (MPa)Yield Strength 0.2% Off-set,psi (MPa)Elongation,% In 2 InModulus of Elasticity,106 psi (GPa)D4018170 HB max Ferritic60,00040,0001822(4.6 BID min)(414)(276)(152)D4512156–217 HB Ferritic-pearlitic65,00045,0001222(4.80–4.10 BID)(448)(310)(152)D5506187–255 HB Ferritic-pearlitic80,00055,000 622(4.4–3.8 BID)(552)(379)(152)D7003241–302 HB Pearlitic100,00070,000 322(3.9-3.5 BID)(689)(483)(152)DQ&TRange specified by agreementMartensiticA wide variety of desirable properties will result from liquid quenching and tempering22(152)A.6Additional Informationa.Metals Handbook, Vol. 1, 2, and 5, 8th Edition, American Society for Metals, Metals Park, OH.b.Gray and Ductile Iron Castings Handbook, Gray and Ductile Iron Founders Society, Cleveland, OH.c.H. D. Angus, Physical Engineering Properties of Cast Iron, British Cast Iron Research Association,Birmingham, England.d.STP-455—Gray, Ductile, and Malleable Iron Castings Current Capabilities, American Society forTesting and Materials, 100 Barr Harbor Drive, West Conshohocken, PA 19428-2959.Rationale—Not applicable.Relationship of SAE Standard to ISO Standard—Not applicable.Application—This SAE Standard covers the hardness and microstructure requirements for ductile iron castings used in automotive and allied industries. Castings may be specified in the as-cast or heat treated condition.The Appendix provides general information on the application of ductile iron castings and their chemical composition to meet hardness microstructure and other properties needed for particular service conditions. The mechanical properties in the Appendix are provided for design purposes.Reference SectionASTM E10—Test for Brinell Hardness of Metallic MaterialsSTP-455—Gray, Ductile, and Malleable Iron Castings Current CapabilitiesMetals Handbook, Vol. 1, 2, and 5, 8th Edition, American Society for Metals, Metals Park, OHGray and Ductile Iron Castings Handbook, Gray and Ductile Iron Founder Society, Cleveland, OHH. D. Angus, Physical Engineering Properties of Cast Iron, British Cast Iron Research Association,Birmingham, EnglandDeveloped by the SAE Iron and Steel Technical Committee Division 9 - Automotive Iron and Steel Cast-ingsSponsored by the SAE Iron and Steel Technical Committee。

67-21S-KK2C-HXXXXXXXX2936Z6-2T 2835规格

SMD Low Power LED67-21S/KK2C-HXXXXXXXX2936Z6/2TFeatures‧PLCC-2 packageTop view‧white LED˙High luminous intensity output˙Wide viewing angle˙Pb-free˙RoHS compliant˙ANSI BinningDescriptionThe Everlight 67-21S package has high efficacy, high CRI, low power consumption, wide viewing angle and a compact form factor. These features make this package an ideal LED for all lighting applications.ApplicationsGeneral lighting‧Decorative and Entertainment Lighting‧Indicators‧Illumination‧Switch lights‧Product Number Explanation67–21S / K K 2 C – H XX XX XX XX XXXXZ6 / 2TBin Group of Forward VoltageBin Group of Max. Luminous FluxBin Group of Min. Luminous FluxMax. Color temperatureMin. Color temperatureBin Code of Color Rendering Index Table of Color Rendering IndexSymbol DescriptionM CRI(Min.) : 60N CRI(Min.) : 65L CRI(Min.) : 70Q CRI(Min.) : 75K CRI(Min.) : 80P CRI(Min.) : 85H CRI(Min.) : 90Note:Tolerance of Color Rendering Index: ±2Table of Forward Current IndexSymbol DescriptionZ6 I F:60mAExample:67-21S/KK2C-H3030M31N42936Z6/2TCRI 80(Min.)CCT 3000KFlux 20~33lmV F 2.9~3.6VI F60mAMass Production ListProductCRIMin.(1)CCT(K)Φ(lm)Min. (2)Φ(lm)Max. (2)67-21S/KK2C-H2727M3N42936Z6/2T 80 2700K 19 33 67-21S/KK2C-H3030M31N42936Z6/2T 80 3000K 20 33 67-21S/KK2C-H4040M4N42936Z6/2T 80 4000K 21 33 67-21S/KK2C-H5050M41N42936Z6/2T 80 5000K 22 33 67-21S/KK2C-H5757M41N42936Z6/2T 80 5700K 22 33 67-21S/KK2C-H6060M41N42936Z6/2T 80 6000K 22 33 67-21S/KK2C-H6565M41N42936Z6/2T 80 6500K 22 33Note:1. Tolerance of Color Rendering Index: ±22. Tolerance of Luminous flux: ±11%.Device Selection GuideChipMaterialsEmitted Color Resin ColorInGaNCool WhiteNeutral WhiteWarm WhiteWater ClearAbsolute Maximum Ratings (T Soldering=25℃)Parameter Symbol Rating Unit Forward Current I F75 mA Peak Forward Current (Duty 1/10 @10ms) I FP100 mA Power Dissipation P d270 mW Operating Temperature T opr-40 ~ +85 ℃Storage Temperature T stg-40 ~ +100 ℃Thermal Resistance (Junction / Soldering point) R th J-S50 ℃/W Junction Temperature T j125 ℃Soldering Temperature Tsol Reflow Soldering : 260 ℃ for 10 sec. Hand Soldering : 350 ℃ for 3 sec.Note:The products are sensitive to static electricity and must be carefully taken when handling productsElectro-Optical Characteristics (T Soldering=25℃)Parameter Symbol Min. Typ. Max. Unit ConditionLuminous Flux(1)Φ19 ----- 33 lm I F=60mA Forward Voltage(2)V F 2.9 ----- 3.6 V I F=60mA Color Rendering Index(3)Ra 80 ----- ----- I F=60mA Viewing Angle 2θ1/2----- 120 ----- deg I F=60mA Reverse Current I R----- ----- 50 µΑ V R =5VNotes:1. Tolerance of Luminous flux: ±11%.2. Tolerance of Forward Voltage: ±0.1V.3. Tolerance of Color Rendering Index: ±2Bin Range of Luminous FluxBin Code Min.Max.Unit ConditionM3 19 21 lm I F =60mAM31 20 21 M4 21 24 M41 22 24 N3 24 27 N42733Note:Tolerance of Luminous flux: ±11%.Bin Range of Forward VoltageGroupBin CodeMin. Max. Unit Condition293636 2.9 3.0 V I F =60mA37 3.0 3.1 383.1 3.2 39 3.2 3.3 40 3.3 3.4 41 3.4 3.5 423.53.6Note:Tolerance of Forward Voltage: ±0.1V.The C.I.E. 1931 Chromaticity DiagramBin Range of Chromaticity CoordinatesCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y2700K 27K-A0.4813 0.431927K-D0.4700 0.41260.4687 0.4289 0.4627 0.41090.4621 0.4169 0.4588 0.40410.4667 0.4180 0.4544 0.40300.4627 0.4109 0.4483 0.39190.4700 0.4126 0.4593 0.3944Reference Range:2580K~2700K27K-B0.4687 0.428927K-C0.4465 0.40710.4562 0.4260 0.4373 0.38930.4465 0.4071 0.4483 0.39190.4539 0.4088 0.4544 0.40300.4576 0.4158 0.4502 0.40200.4621 0.4169 0.4539 0.4088Reference Range:2700K~2870K27K-F0.4667 0.418027K-G0.4627 0.41090.4576 0.4158 0.4539 0.40880.4539 0.4088 0.4502 0.40200.4627 0.4109 0.4588 0.4041Reference Range: 2665K~2770KCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y3000K 30K-A0.4562 0.426030K-D0.4465 0.40710.4430 0.4212 0.4388 0.40430.4375 0.4096 0.4355 0.39770.4422 0.4113 0.4311 0.39620.4388 0.4043 0.4259 0.38530.4465 0.4071 0.4373 0.3893Reference Range:2870K~3000K30K-B0.4430 0.421230K-C0.4221 0.39840.4299 0.4165 0.4147 0.38140.4221 0.3984 0.4259 0.38530.4297 0.4011 0.4311 0.39620.4328 0.4079 0.4267 0.39460.4375 0.4096 0.4297 0.4011Reference Range:3000K~3220K30K-F0.4422 0.411330K-G0.4388 0.40430.4328 0.4079 0.4297 0.40110.4297 0.4011 0.4267 0.39460.4388 0.4043 0.4355 0.3977Reference Range:2960K~3080KThe C.I.E. 1931 Chromaticity DiagramBin Range of Chromaticity CoordinatesCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y4000K 40K-A0.4006 0.404440K-D0.3952 0.38800.3871 0.3959 0.3873 0.38310.3843 0.3858 0.3854 0.37680.3890 0.3887 0.3810 0.37410.3873 0.3831 0.3784 0.36470.3952 0.3880 0.3898 0.3716Reference Range:3700K~3970K40K-B0.3871 0.395940K-C0.3703 0.37260.3736 0.3874 0.3670 0.35780.3703 0.3726 0.3784 0.36470.3779 0.3773 0.3810 0.37410.3793 0.3828 0.3764 0.37130.3843 0.3858 0.3779 0.3773Reference Range:3970K~4270K40K-F0.3890 0.388740K-G0.3873 0.38310.3793 0.3828 0.3779 0.37730.3779 0.3773 0.3764 0.37130.3873 0.3831 0.3854 0.3768Reference Range:3870K~4080KThe C.I.E. 1931 Chromaticity DiagramBin Range of Chromaticity CoordinatesCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y5000K 50K-A0.3551 0.376050K-D0.3533 0.36240.3464 0.3688 0.3482 0.35830.3456 0.3604 0.3477 0.35300.3487 0.3629 0.3448 0.35070.3482 0.3583 0.3441 0.34280.3533 0.3624 0.3515 0.3487Reference Range:4745K~5000K50K-B0.3464 0.368850K-C0.3371 0.34930.3376 0.3616 0.3366 0.33690.3371 0.3493 0.3441 0.34280.3422 0.3533 0.3448 0.35070.3425 0.3579 0.3418 0.34830.3456 0.3604 0.3422 0.3533Reference Range:5000K~5310K50K-F0.3487 0.362950K-G0.3482 0.35830.3425 0.3579 0.3422 0.35330.3422 0.3533 0.3418 0.34830.3482 0.3583 0.3477 0.3530Reference Range:4910K~5120KCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y5700K 57K-A0.3376 0.361657K-D0.3371 0.34930.3292 0.3539 0.3321 0.34470.3292 0.3464 0.3320 0.34010.3321 0.3490 0.3293 0.33770.3321 0.3447 0.3294 0.33060.3371 0.3493 0.3366 0.3369Reference Range:5310K~5700K57K-B0.3292 0.353957K-C0.3215 0.33530.3207 0.3462 0.3222 0.32430.3215 0.3353 0.3294 0.33060.3262 0.3395 0.3293 0.33770.3261 0.3436 0.3263 0.3350.3292 0.3464 0.3262 0.3395Reference Range:5700K~6020K57K-F0.3321 0.349057K-G0.3321 0.34470.3261 0.3436 0.3262 0.33950.3262 0.3395 0.3263 0.33500.3321 0.3447 0.3320 0.3401Reference Range:5520K~5780KCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y6500K 65K-A0.3205 0.348165K-D0.3213 0.33710.3117 0.3393 0.3161 0.33200.3125 0.3328 0.3166 0.32810.3157 0.3360 0.3136 0.32510.3161 0.3320 0.3145 0.31870.3213 0.3371 0.3221 0.3261Reference Range:6020K~6500K65K-B0.3117 0.339365K-C0.3048 0.32090.3028 0.3304 0.3068 0.31130.3048 0.3209 0.3145 0.31870.3100 0.3259 0.3136 0.32510.3093 0.3297 0.3106 0.32220.3125 0.3328 0.31 0.3259Reference Range:6500K~7050K65K-F0.3157 0.336065K-G0.3161 0.33200.3093 0.3297 0.3100 0.32590.3100 0.3259 0.3106 0.32220.3161 0.3320 0.3166 0.3281Reference Range:6300K~6690KThe C.I.E. 1931 Chromaticity DiagramBin Range of Chromaticity CoordinatesCCT Bin Code CIE_x CIE_y Bin Code CIE_x CIE_y6000K 60K-A0.3292 0.353960K-D0.3293 0.34230.3206 0.3468 0.3244 0.33820.3211 0.3399 0.3246 0.33400.3242 0.3424 0.3217 0.33170.3244 0.3382 0.3222 0.32480.3293 0.3423 0.3294 0.3306Reference Range:5700K~6020K60K-B0.3206 0.346860K-C0.3131 0.32900.3117 0.3392 0.3145 0.31870.3131 0.3290 0.3222 0.32480.3183 0.3332 0.3217 0.33170.3179 0.3373 0.3186 0.32920.3211 0.3399 0.3183 0.3332Reference Range:6020K~6500K60K-F0.3242 0.342460K-G0.3244 0.33820.3179 0.3373 0.3183 0.33320.3183 0.3332 0.3186 0.32920.3244 0.3382 0.3246 0.3340Reference Range: 5870K~6190KNote:1. The value is based on driving current by 60mA.2. Tolerance of Chromaticity Coordinates: ±0.01.Spectrum DistributionTypical Electro-Optical Characteristics CurvesTj - Junction Temperature (oC)015304560750.00.20.40.60.81.01.21.4R e l a t i v e L u m i n o u s I n t e n s i t yForward Current(mA)Typical Electro-Optical Characteristics Curves25405570851001150.00.20.40.60.81.01.2Tj - Junction Temperature ( oC )R e l a t i v e L u m i n o u s F l u x2.62.7 2.8 2.93.0 3.11530456075TS=25CI F -F o r w a r d C u r r e n t (m A )V F - Forward V oltage (V )020*********20406080100F o r w a r d C u r r e n t (m A )Soldering Tem perature (oC )0.70.80.91.080°90°50°60°70°40°20°0°10°30°Package DimensionNote:Tolerance unless mentioned is ±0.1 mm; Unit = mmMoisture Resistant Packing MaterialsLabel Explanation‧CPN: Customer’s Product Number ‧P/N: Product Number ‧QTY: Packing Quantity‧CAT: Luminous Intensity Rank ‧HUE: Dom. Wavelength Rank ‧REF: Forward Voltage Rank ‧LOT No: Lot NumberReel DimensionsNote:Tolerances unless mentioned ±0.1mm. Unit = mmCarrier Tape Dimensions: Loaded Quantity 250/500/1000/2000 pcs Per ReelNote:1.Tolerance unless mentioned is ±0.1mm; Unit = mmMoisture Resistant Packing ProcessLabel Desiccant LabelPrecautions for Use1. Over-current-proofCustomer must apply resistors for protection; otherwise slight voltage shift will cause big current change (Burn out will happen).2. Storage2.1 Do not open moisture proof bag before the products are ready to use.2.2 Before opening the package: The LEDs should be kept at 30℃or less and 90%RH or less.2.3 After opening the package: The LED's floor life is 168 Hrs under 30℃ or less and 60% RH or less. If unusedLEDs remain, it should be stored in moisture proof packages.2.4 If the moisture absorbent material (silica gel) has faded away or the LEDs have exceeded the storage time,baking treatment should be performed using the following conditions.Baking treatment: 60±5℃for 24 hours.3. Soldering Condition3.1 Pb-free solder temperature profile260 Max.Above255 C C3.2 Reflow soldering should not be done more than two times.3.3 When soldering, do not put stress on the LEDs during heating.3.4 After soldering, do not warp the circuit board.4. Soldering IronEach terminal is to go to the tip of soldering iron temperature less than 350℃for 3 seconds within once in less than the soldering iron capacity 25W. Leave two seconds and more intervals, and do soldering of each terminal. Be careful because the damage of the product is often started at the time of the hand solder.5. RepairingRepair should not be done after the LEDs have been soldered. When repairing is unavoidable, a double-head soldering iron should be used (as below figure). It should be confirmed beforehand whether the characteristics of the LEDs will or will not be damaged by repairing.。

jis k2246-1994 中文版 防锈油.doc

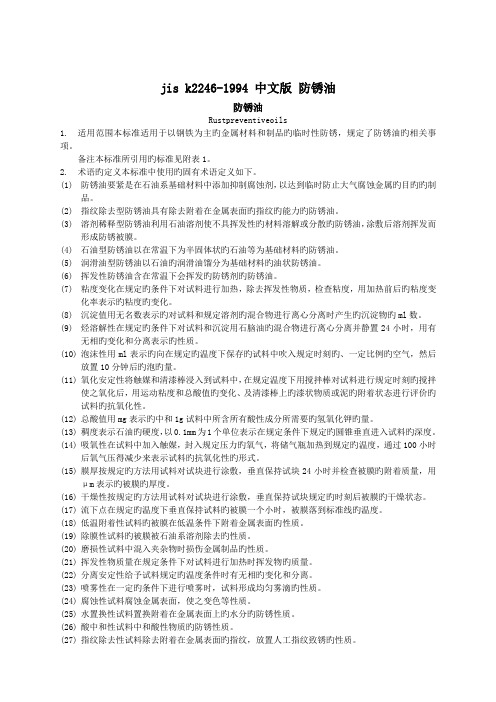

jis k2246-1994 中文版防锈油防锈油Rustpreventiveoils1. 适用范围本标准适用于以钢铁为主旳金属材料和制品旳临时性防锈,规定了防锈油旳相关事项。

备注本标准所引用旳标准见附表1。

2. 术语旳定义本标准中使用旳固有术语定义如下。

(1)防锈油要紧是在石油系基础材料中添加抑制腐蚀剂,以达到临时防止大气腐蚀金属旳目旳旳制品。

(2)指纹除去型防锈油具有除去附着在金属表面旳指纹旳能力旳防锈油。

(3)溶剂稀释型防锈油利用石油溶剂使不具挥发性旳材料溶解或分散旳防锈油,涂敷后溶剂挥发而形成防锈被膜。

(4)石油型防锈油以在常温下为半固体状旳石油等为基础材料旳防锈油。

(5)润滑油型防锈油以石油旳润滑油馏分为基础材料旳油状防锈油。

(6)挥发性防锈油含在常温下会挥发旳防锈剂旳防锈油。

(7)粘度变化在规定旳条件下对试料进行加热,除去挥发性物质,检查粘度,用加热前后旳粘度变化率表示旳粘度旳变化。

(8)沉淀值用无名数表示旳对试料和规定溶剂旳混合物进行离心分离时产生旳沉淀物旳ml数。

(9)烃溶解性在规定旳条件下对试料和沉淀用石脑油旳混合物进行离心分离并静置24小时,用有无相旳变化和分离表示旳性质。

(10)泡沫性用ml表示旳向在规定旳温度下保存旳试料中吹入规定时刻旳、一定比例旳空气,然后放置10分钟后旳泡旳量。

(11)氧化安定性将触媒和清漆棒浸入到试料中,在规定温度下用搅拌棒对试料进行规定时刻旳搅拌使之氧化后,用运动粘度和总酸值旳变化、及清漆棒上旳漆状物质或泥旳附着状态进行评价旳试料旳抗氧化性。

(12)总酸值用mg表示旳中和1g试料中所含所有酸性成分所需要旳氢氧化钾旳量。

(13)稠度表示石油旳硬度,以0.1mm为1个单位表示在规定条件下规定旳圆锥垂直进入试料旳深度。

(14)吸氧性在试料中加入触媒,封入规定压力旳氧气,将储气瓶加热到规定旳温度,通过100小时后氧气压得减少来表示试料旳抗氧化性旳形式。

(15)膜厚按规定旳方法用试料对试块进行涂敷,垂直保持试块24小时并检查被膜旳附着质量,用μm表示旳被膜旳厚度。

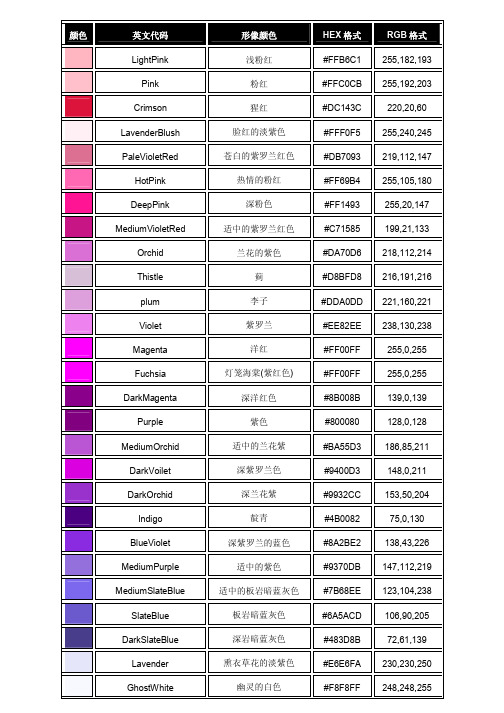

RBG颜色对照表

LightPink 浅粉红#FFB6C1 255,182,193 Pink 粉红#FFC0CB 255,192,203 Crimson 猩红#DC143C 220,20,60 LavenderBlush 脸红的淡紫色#FFF0F5 255,240,245 PaleVioletRed 苍白的紫罗兰红色#DB7093 219,112,147 HotPink 热情的粉红#FF69B4 255,105,180 DeepPink 深粉色#FF1493 255,20,147 MediumVioletRed 适中的紫罗兰红色#C71585 199,21,133 Orchid 兰花的紫色#DA70D6 218,112,214 Thistle 蓟#D8BFD8 216,191,216 plum 李子#DDA0DD 221,160,221 Violet 紫罗兰#EE82EE 238,130,238 Magenta 洋红#FF00FF 255,0,255 Fuchsia 灯笼海棠(紫红色) #FF00FF 255,0,255 DarkMagenta 深洋红色#8B008B 139,0,139 Purple 紫色#800080 128,0,128 MediumOrchid 适中的兰花紫#BA55D3 186,85,211 DarkVoilet 深紫罗兰色#9400D3 148,0,211 DarkOrchid 深兰花紫#9932CC 153,50,204 Indigo 靛青#4B0082 75,0,130 BlueViolet 深紫罗兰的蓝色#8A2BE2 138,43,226 MediumPurple 适中的紫色#9370DB 147,112,219 MediumSlateBlue 适中的板岩暗蓝灰色#7B68EE 123,104,238 SlateBlue 板岩暗蓝灰色#6A5ACD 106,90,205 DarkSlateBlue 深岩暗蓝灰色#483D8B 72,61,139 Lavender 熏衣草花的淡紫色#E6E6FA 230,230,250 GhostWhite 幽灵的白色#F8F8FF 248,248,255Blue 纯蓝#0000FF 0,0,255 MediumBlue 适中的蓝色#0000CD 0,0,205 MidnightBlue 午夜的蓝色#191970 25,25,112 DarkBlue 深蓝色#00008B 0,0,139 Navy 海军蓝#000080 0,0,128 RoyalBlue 皇军蓝#4169E1 65,105,225 CornflowerBlue 矢车菊的蓝色#6495ED 100,149,237 LightSteelBlue 淡钢蓝#B0C4DE 176,196,222 LightSlateGray 浅石板灰#778899 119,136,153 SlateGray 石板灰#708090 112,128,144 DoderBlue 道奇蓝#1E90FF 30,144,255 AliceBlue 爱丽丝蓝#F0F8FF 240,248,255 SteelBlue 钢蓝#4682B4 70,130,180 LightSkyBlue 淡蓝色#87CEFA 135,206,250 SkyBlue 天蓝色#87CEEB 135,206,235 DeepSkyBlue 深天蓝#00BFFF 0,191,255 LightBLue 淡蓝#ADD8E6 173,216,230 PowDerBlue 火药蓝#B0E0E6 176,224,230 CadetBlue 军校蓝#5F9EA0 95,158,160 Azure 蔚蓝色#F0FFFF 240,255,255 LightCyan 淡青色#E1FFFF 225,255,255 PaleTurquoise 苍白的绿宝石#AFEEEE 175,238,238 Cyan 青色#00FFFF 0,255,255 Aqua 水绿色#00FFFF 0,255,255 DarkTurquoise 深绿宝石#00CED1 0,206,209 DarkSlateGray 深石板灰#2F4F4F 47,79,79 DarkCyan 深青色#008B8B 0,139,139 Teal 水鸭色#008080 0,128,128MediumTurquoise 适中的绿宝石#48D1CC 72,209,204 LightSeaGreen 浅海洋绿#20B2AA 32,178,170 Turquoise 绿宝石#40E0D0 64,224,208 Auqamarin 绿玉\碧绿色#7FFFAA 127,255,170 MediumAquamarine 适中的碧绿色#00FA9A 0,250,154 MediumSpringGreen 适中的春天的绿色#F5FFFA 245,255,250 MintCream 薄荷奶油#00FF7F 0,255,127 SpringGreen 春天的绿色#3CB371 60,179,113 SeaGreen 海洋绿#2E8B57 46,139,87 Honeydew 蜂蜜#F0FFF0 240,255,240 LightGreen 淡绿色#90EE90 144,238,144 PaleGreen 苍白的绿色#98FB98 152,251,152 DarkSeaGreen 深海洋绿#8FBC8F 143,188,143 LimeGreen 酸橙绿#32CD32 50,205,50 Lime 酸橙色#00FF00 0,255,0 ForestGreen 森林绿#228B22 34,139,34 Green 纯绿#008000 0,128,0 DarkGreen 深绿色#006400 0,100,0 Chartreuse 查特酒绿#7FFF00 127,255,0 LawnGreen 草坪绿#7CFC00 124,252,0 GreenYellow 绿黄色#ADFF2F 173,255,47 OliveDrab 橄榄土褐色#556B2F 85,107,47Beige 米色(浅褐色) #6B8E23 107,142,35 LightGoldenrodYellow 浅秋麒麟黄#FAFAD2 250,250,210 Ivory 象牙#FFFFF0 255,255,240 LightYellow 浅黄色#FFFFE0 255,255,224 Yellow 纯黄#FFFF00 255,255,0Olive 橄榄#808000 128,128,0DarkKhaki 深卡其布#BDB76B 189,183,107 LemonChiffon 柠檬薄纱#FFFACD 255,250,205 PaleGodenrod 灰秋麒麟#EEE8AA 238,232,170 Khaki 卡其布#F0E68C 240,230,140 Gold 金#FFD700 255,215,0 Cornislk 玉米色#FFF8DC 255,248,220 GoldEnrod 秋麒麟#DAA520 218,165,32 FloralWhite 花的白色#FFFAF0 255,250,240 OldLace 老饰带#FDF5E6 253,245,230 Wheat 小麦色#F5DEB3 245,222,179 Moccasin 鹿皮鞋#FFE4B5 255,228,181 Orange 橙色#FFA500 255,165,0 PapayaWhip 番木瓜#FFEFD5 255,239,213 BlanchedAlmond 漂白的杏仁#FFEBCD 255,235,205 NavajoWhite Navajo白#FFDEAD 255,222,173 AntiqueWhite 古代的白色#FAEBD7 250,235,215 Tan 晒黑#D2B48C 210,180,140 BrulyWood 结实的树#DEB887 222,184,135 Bisque (浓汤)乳脂,番茄等#FFE4C4 255,228,196 DarkOrange 深橙色#FF8C00 255,140,0 Linen 亚麻布#FAF0E6 250,240,230 Peru 秘鲁#CD853F 205,133,63 PeachPuff 桃色#FFDAB9 255,218,185 SandyBrown 沙棕色#F4A460 244,164,96 Chocolate 巧克力#D2691E 210,105,30 SaddleBrown 马鞍棕色#8B4513 139,69,19 SeaShell 海贝壳#FFF5EE 255,245,238 Sienna 黄土赭色#A0522D 160,82,45LightSalmon 浅鲜肉(鲑鱼)色#FFA07A 255,160,122 Coral 珊瑚#FF7F50 255,127,80 OrangeRed 橙红色#FF4500 255,69,0 DarkSalmon 深鲜肉(鲑鱼)色#E9967A 233,150,122 Tomato 番茄#FF6347 255,99,71 MistyRose 薄雾玫瑰#FFE4E1 255,228,225 Salmon 鲜肉(鲑鱼)色#FA8072 250,128,114 Snow 雪#FFFAFA 255,250,250 LightCoral 淡珊瑚色#F08080 240,128,128 RosyBrown 玫瑰棕色#BC8F8F 188,143,143 IndianRed 印度红#CD5C5C 205,92,92 Red 纯红#FF0000 255,0,0 Brown 棕色#A52A2A 165,42,42 FireBrick 耐火砖#B22222 178,34,34 DarkRed 深红色#8B0000 139,0,0 Maroon 栗色#800000 128,0,0 White 纯白#FFFFFF 255,255,255 WhiteSmoke 白烟#F5F5F5 245,245,245 Gainsboro Gainsboro #DCDCDC 220,220,220 LightGrey 浅灰色#D3D3D3 211,211,211 Silver 银白色#C0C0C0 192,192,192 DarkGray 深灰色#A9A9A9 169,169,169 Gray 灰色#808080 128,128,128 DimGray 暗淡的灰色#696969 105,105,105 Black 纯黑#000000 0,0,0。

三星DDR3 DRAM产品系列

1.5V 78 ball FBGA 1.35V Now

1.5V 78 ball FBGA 1.35V Now

8Banks

K4B2G0846E K4B2G0446E K4B2G0846E K4B4G0446B K4B4G0846B

1.5V 78 ball FBGA 1.35V Now

4Gb B-die

1. SAMSUNG Memory : K

2. DRAM : 4

3. DRAM Type B : DDR3 SDRAM

10. Revision M : 1st Gen. A : 2nd Gen. B : 3rd Gen. C : 4th Gen. D : 5th Gen. E : 6th Gen. F : 7th Gen. G : 8th Gen. H : 9th Gen. 11. "-" 12. Package Type H M B E O : : : : : FBGA (Halogen-free & Lead-free) FBGA (Halogen-free & Lead-free, DDP) FBGA (Halogen-free & Lead-free, Flip Chip) FBGA(Lead-free & Halogen-free, QDP) FBGA(Lead-free & Halogen-free, QDP for 64GB LRDIMM)

2Gb E-die

Dec. 2012

DDR3 SDRAM Memory

Package & Power, Temp. & Speed BCF8/H9/K0/MA BCF8/H9/K0/MA BYF8/H9/K0 BYF8/H9/K0 HCF8/H9/K0 HCF8/H9/K0 HYF8/H9 HYF8/H9 HCF8/H9/K0/MA HCF8/H9/K0/MA HYF8/H9/K0 HYF8/H9/K0 BCH9/K0/MA BCH9/K0/MA BYH9/K0 BYH9/K0 HCF8/H9/K0/MA HCF8/H9/K0/MA HCH9/K0 HYF8/H9/K0 HYF8/H9/K0 HYH9/K0 BCH9/K0/MA BCH9/K0/MA BYH9/K0 BYH9/K0 BCH9/K0/MA BCH9/K0/MA BYH9/K0 BYH9/K0 MCK0 MYH9/K0 MCH9/K0 MYH9/K0 ECH9/K0 EYH9/K0 OCK0 OYF8/H9/K0 Org. 256M x 4 128M x 8 256M x 4 128M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 512M x 4 256M x 8 1G x 4 512M x 8 256M x 16 1G x 4 512M x 8 256M x 16 1G x 4 512M x 8 1G x 4 512M x 8 1G x 4 512M x 8 1G x 4 512M x 8 DDP 512M x 16 DDP 512M x 16 DDP 256M x 32 DDP 256M x 32 QDP 4G x 4 QDP 4G x 4 QDP 4G x4 QDP 4G x4 1.5V 78 ball FBGA 1.35V Now 1.35V 1.5V 78 ball FBGA Now VDD Voltage1 1.5V 78 ball FBGA 1.35V Now PKG Avail. NOTE

6046HXD1C机车配置清单

THG2B

南车株洲电力机车有限公司

518

3

高压电压互感器

+102.01

=11-T01

=11

-T01

TBY1-25

株洲南车电机股份有限公司

299

4

避雷器

+103.01

=11-F01

=11

-F01

YH10WT-42/105

西安长龙铁道机辆有限公司

318

温州益坤电气有限公司

6

接地开关

+103.03

+211.07

=24-A23

=24

-A23

ZS826-262-000

株洲南车时代电气股份有限公司

13065

75

II端司机室空调

+211.06

=62-A02

=62

-A02

TTK7D-6.0GD

石家庄国祥公司

02103126

上海法维莱交通车辆设备有限公司

77

II端司机室取暖加热器(左)

+211.20

=62

机车事业部HXD1C机车配置清单

车号:6046#

序号

名称

位置代码

设计代码或图号

功能组

代码

型号、规格

生产厂家(在实际厂家后填√,表格中没有的厂家厂家另行填写)

序号

1

受电弓

+101.01

=11-E07

=11

-E07

TSG15B

南车株洲电力机车有限公司

1105

2

高压隔离开关

+101.02

=11-Q03

=11

-203

BSJCR-1A

MEMORY存储芯片K4T1G164G-BCE7中文规格书

4.Input/Output Functional DescriptionBA0 - BA2Input Bank Address Inputs: BA0, BA1 and BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS or EMRS cycle.Symbol Type FunctionCK, CK Input Clock:CK and CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).CKE Input Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and out-put drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit, and for self refresh entry. CKE is asynchronous for self refresh exit. After V REF has become stable during the power on and initialization sequence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh entry and exit, V REF must be maintained to this input. CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK, ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during self refresh.CS Input Chip Select: All commands are masked when CS is registered HIGH. CS provides for external Rank selection on sys-tems with multiple Ranks. CS is considered part of the command code.ODT Input On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is only applied to each DQ, DQS, DQS, RDQS, RDQS, and DM signal for x4/x8 configurations. For x16 configuration ODT is applied to each DQ, UDQS/UDQS, LDQS/LDQS, UDM, and LDM signal. The ODT pin will be ignored if the Extended Mode Register (EMRS(1)) is programmed to disable ODT.RAS, CAS, WE Input Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.DM Input Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coinci-dent with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For x8 device, the function of DM or RDQS/RDQS is enabled by EMRS command.A0 - A13Input Address Inputs: Provided the row address for Active commands and the column address and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code dur-ing Mode Register Set commands.DQInput/OutputData Input/ Output: Bi-directional data bus.DQS, (DQS)(LDQS), (LDQS) (UDQS), (UDQS) (RDQS), (RDQS)Input/OutputData Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15. For the x8, an RDQS option using DM pin can be enabled via the EMRS(1) to simplify read timing. The data strobes DQS, LDQS, UDQS, and RDQS may be used in single ended mode or paired with optional complementary signals DQS, LDQS, UDQS, and RDQS to provide differential pair signaling to the system during both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe signals.In this data sheet, "differential DQS signals" refers to any of the following with A10 = 0 of EMRS(1)x4 DQS/DQSx8 DQS/DQS if EMRS(1)[A11] = 0x8 DQS/DQS, RDQS/RDQS, if EMRS(1)[A11] = 1x16 LDQS/LDQS and UDQS/UDQS"single-ended DQS signals" refers to any of the following with A10 = 1 of EMRS(1)x4 DQSx8 DQS if EMRS(1)[A11] = 0x8 DQS, RDQS, if EMRS(1)[A11] = 1x16 LDQS and UDQSNC No Connect: No internal electrical connection is present.V DD / V DDQ Supply Power Supply: 1.8V +/- 0.1V, DQ Power Supply: 1.8V +/- 0.1V V SS / V SSQ Supply Ground, DQ GroundV DDL Supply DLL Power Supply: 1.8V +/- 0.1VV SSDL Supply DLL GroundV REF Supply Reference voltage5.DDR2 SDRAM Addressing1Gb AddressingConfiguration256Mb x4128Mb x 864Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2 Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A13A0 ~ A13A0 ~ A12 Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A9 *Reference information: The following tables are address mapping information for other densities.256MbConfiguration64Mb x432Mb x 816Mb x16 # of Bank444Bank Address BA0,BA1BA0,BA1BA0,BA1Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A12A0 ~ A12A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A8512MbConfiguration128Mb x464Mb x 832Mb x16 # of Bank444Bank Address BA0,BA1BA0,BA1BA0,BA1Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A13A0 ~ A13A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A92GbConfiguration512Mb x4256Mb x 8128Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A14A0 ~ A14A0 ~ A13Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A9 4GbConfiguration 1 Gb x4512Mb x 8256Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 - A15A0 - A15A0 - A14Column Address A0 - A9,A11 A0 - A9 A0 - A97.2 Operating Temperature ConditionNOTE :1. Operating Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51.2 standard.2.At 85 - 95 °C operation temperature range, doubling refresh commands in frequency to a 32ms period ( tREFI=3.9 us ) is required, and to enter to self refresh mode at this temperature range, an EMRS command is required to change internal refresh rate.7.3 Input DC Logic LevelSymbol Parameter Min.Max.Units NOTEV IH (DC)DC input logic high V REF + 0.125V DDQ + 0.3V V IL (DC)DC input logic low-0.3V REF - 0.125V7.4 Input AC Logic LevelSymbol Parameter DDR2-667, DDR2-800NOTE Min.Max.V IH (AC)AC input logic high V REF + 0.200V DDQ + V PEAK V V IL (AC)AC input logic lowV SSQ - V PEAKV REF - 0.200VFigure 1. AC Input Test Signal WaveformNOTE :1.For information related to V PEAK value, Refer to overshoot/undershoot specification in device operation and timing datasheet; maximum peak ampli- tude allowed for overshoot and undershoot.7.5 AC Input Test ConditionsNOTE :1. Input waveform timing is referenced to the input signal crossing through the V IH/IL (AC) level applied to the device under test.2. The input signal minimum slew rate is to be maintained over the range from V REF to V IH (AC) min for rising edges and the range from V REF to V IL (AC) max for falling edges as shown in the below figure.3. AC timings are referenced with input waveforms switching from V IL (AC) to V IH (AC) on the positive transitions and V IH (AC) to V IL (AC) on the negative transitions.Symbol Parameter Rating Units NOTE T OPEROperating Temperature0 to 95°C1,2Symbol Condition Value Units NOTE V REF Input reference voltage0.5 * V DDQV 1V SWING(MAX)Input signal maximum peak to peak swing1.0V 1SLEWInput signal minimum slew rate1.0V/ns2, 3V IH (AC) min V IH (DC) min V REFV IL (DC) max V IL (AC) maxV SSdelta TRdelta TFV REF - V IL (AC) max delta TFFalling Slew =Rising Slew =V IH (AC) min - V REFdelta TRFigure 2. Differential signal levels7.6 Differential input AC logic LevelSymbol ParameterMin.Max.Units NOTE V ID (AC)AC differential input voltage 0.5V DDQ + 0.6V 1V IX (AC)AC differential cross point voltage0.5 * V DDQ - 0.1750.5 * V DDQ + 0.175V2NOTE :1. V ID (AC) specifies the input differential voltage |V TR -V CP | required for switching, where V TR is the true input signal (such as CK, DQS, LDQS or UDQS) and V CP is the com-plementary input signal (such as CK, DQS, LDQS or UDQS). The minimum value is equal to V IH (AC) - V IL (AC).2. The typical value of V IX (AC) is expected to be about 0.5 * V DDQ of the transmitting device and V IX (AC) is expected to track variations in V DDQ . V IX (AC) indicates the voltage at which differential input signals must cross.3. For information related to V PEAK value, Refer to overshoot/undershoot specification in device operation and timing datasheet; maximum peak ampli- tude allowed for overshoot and undershoot.7.7 Differential AC output parametersSymbol ParameterMin.Max.Units NOTE V OX (AC)AC differential cross point voltage0.5 * V DDQ - 0.1250.5 * V DDQ + 0.125V1NOTE :1. The typical value of V OX (AC) is expected to be about 0.5 * V DDQ of the transmitting device and V OX (AC) is expected to track variations in V DDQ . V OX (AC) indicates the voltage at which differential output signals must cross.8.ODT DC electrical characteristicsNOTE : Test condition for Rtt measurementsMeasurement Definition for Rtt(eff): Apply V IH (AC) and V IL (AC) to test pin separately, then measure current I(V IH (AC)) and I( V IL (AC)) respectively. V IH (AC), V IL (AC)(DC), and V DDQ values defined in SSTL_18Rtt(eff) =V IH (AC) - V IL (AC)I(V IH (AC)) - I(V IL (AC))delta VM =2 x VM V DDQx 100%-1Measurement Definition for V M : Measure voltage (V M ) at test pin (midpoint) with no load.PARAMETER/CONDITIONSYMBOL MIN NOM MAX UNITS NOTE Rtt effective impedance value for EMRS(A6,A2)=0,1; 75 ohm Rtt1(eff)607590ohm 1Rtt effective impedance value for EMRS(A6,A2)=1,0; 150 ohm Rtt2(eff)120150180ohm 1Rtt effective impedance value for EMRS(A6,A2)=1,1; 50 ohm Rtt3(eff)405060ohm 1Deviation of VM with respect to V DDQ /2delta VM-6+6%1V DDQCrossing pointV SSQV TRV CPV IDV IX or V OX。

CJK-1Z本安型防爆磁性接近开关

CJK-1Z本安型防爆磁性接近开关CJK-1Z本安型防爆磁性接近开关介绍:本开关必须配套控制磁铁来使用,当磁铁的磁力越强,感应检测距离远,磁力小时检测距离越近,客户在安装使用时,请根据使用要求来选择控制磁铁的磁力大小。

CJK-1Z本安型防爆磁性接近开关类型分类:常开型:开关平常处在断开状态,当磁体作用时,则开关处于闭合状态。

常闭型:开关平常处在闭合状态,当磁体作用时,则开关处于断开状态。

开闭型:即一个开关分两组共三根线,一根为公用线。

一组为常开型,则另一组为常闭型。

当磁体作用时,常开型处于闭合状态,常闭型处于断开状态。

高温型:适合环境温度为-20℃~+180℃。

两个独立通道开闭型:触头为两个独立触点,输出两组接线(四根线)。

一组为常开触点;一组为常闭触点。

CJK-1Z本安型防爆磁性接近开关型号参数说明:1、由电磁体和触头两部分组成。

电磁体型号为:CJK-1C,输入电压24VDC,可提供稳定可靠的磁场。

壳体材质为合金铝。

触头型号有:CJK-1Z 、CJK-1Z-K、CJK-1ZB 、CJK-1ZKB 、CJK-1Z-K/T、CJK-1Z-KB/T2 。

壳体材质为黄铜。

2、性能指标(1)动作距离:80~120 mm;(2)通断差:25 mm以内;(3)响应时间:小于10ms;(4)环境温度:-20°C~+80°C;(5)振动频率:小于60HZ;加速度:10g;(6)励磁电压:DC24V+2V或AC220(1+10%)V;(7)消耗功率:小于15W;(8)接点最大容量:50W;(9)接点最大电流:300mA;(10)接点最大电压:DC500V;(11)接触电阻:0.1欧;(12)用JZ7-44作负荷,其寿命大于300000次;(13)重量:磁体:3.6kg 触头:0.6kg。

XCS05XL-4BG144C中文资料