P4C22-20FMB中文资料

HMM55C20资料

Page No. : 1/3 HMM55C SeriesZENER DIODESMaximum Zener Impedance Maximum Reverse Leakage CurrentDevice Type NominalZenerVoltageVzat Izt*(V)TestCurrentIzT(mA)ZzTatIzT(Ω)ZzkatIzk=1mA(Ω)TypicalTemperatureCoefficient(%/°C)IR(uA)Test-Voltagesuffix B (V)MaximumRegulatorCurrentIzM(mA)HMM55C2V0 1.9-2.151001000-0.070150 1.0200 HMM55C2V4 2.28-2.56585600-0.07050 1.0150 HMM55C2V7 2.5-2.9585600-0.07010 1.0135 HMM55C3V0 2.8-3.2585600-0.0704 1.0125 HMM55C3V3 3.1-3.5585600-0.0652 1.0115 HMM55C3V6 3.4-3.8585600-0.0602 1.0105 HMM55C3V9 3.7-4.1585600-0.0502 1.095 HMM55C4V3 4.0-4.6575600-0.0251 1.090 HMM55C4V7 4.4-5.0560600-0.0100.5 1.085 HMM55C5V1 4.8-5.4535550+0.0150.1 1.080 HMM55C5V6 5.2-6.0525450+0.0250.1 1.070 HMM55C6V2 5.8-6.6510200+0.0350.1 2.064 HMM55C6V8 6.4-7.258150+0.0450.1 3.058 HMM55C7V57.0-7.95750+0.0500.1 5.053 HMM55C8V27.7-8.75750+0.0500.1 6.047 HMM55C9V18.5-9.651050+0.0600.17.043 HMM55C109.4-10.651570+0.0700.17.540 HMM55C1110.4-11.652070+0.0700.18.536 HMM55C1211.4-12.752090+0.0700.19.032 HMM55C1312.4-14.1526110+0.0700.11029 HMM55C1513.8-15.6530110+0.0700.11127 HMM55C1615.3-17.1540170+0.0700.11224 HMM55C1816.8-19.1550170+0.0700.11421 HMM55C2018.8-21.2555220+0.0700.11520 HMM55C2220.8-23.3555220+0.0700.11718 HMM55C2422.8-25.6580220+0.0800.11816 HMM55C2725.1-28.9580220+0.0800.12014 HMM55C3028-32580220+0.0800.12213 HMM55C3331-35580220+0.0800.12412 HMM55C3634-38580220+0.0800.12711 HMM55C3937-41 2.590500+0.0800.13010 HMM55C4340-46 2.590600+0.0800.1339.2 HMM55C4744-50 2.5110700+0.0800.1368.5 Note: 1.Standard Voltage Tolerance is ±5% and Suffix "A" for ±1%, Suffix "B" for ±2%, Suffix "C" for ±5%, Suffix "D" for ±20%2.*Measured With Pulses Tp= 20m Sec.Page No. : 2/3 Absolute Maximum RatingsCharacteristics Symbol Value Unit Zener Current see Table “Characteristics”---Power Dissipation at Tamb=25°C Ptot500*mW Junction Temperature Tj175°C Storage Temperature Range Ts-55 to +175°C*Valid provided that leads are kept at ambient temperature at a distance of 8mm from case. Characteristics (Tamb=25°C)Characteristics Symbol Min Typ Max Unit Thermal Resistance Junction to Ambient Air RthA--0.3*K/mW Forward Voltage at IF=100mA VF--1V *Valid provided that leads at a distance of 10mm from case are kept at ambient temperature. Characteristics CurvePage No. : 3/3Important Notice:• All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of HSMC.• HSMC reserves the right to make changes to its products without notice.•HSMC semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems.• HSMC assumes no liability for any consequence of customer product design, infringement of patents, or application assistance. Head Office And Factory:•Head Office (Hi-Sincerity Microelectronics Corp.): 10F.,No. 61, Sec. 2, Chung-Shan N. Rd. Taipei Taiwan R.O.C.Tel: 886-2-25212056 Fax: 886-2-25632712, 25368454•Factory 1: No. 38, Kuang Fu S. Rd., Fu-Kou Hsin-Chu Industrial Park Hsin-Chu Taiwan. R.O.CTel: 886-3-5983621~5 Fax: 886-3-5982931。

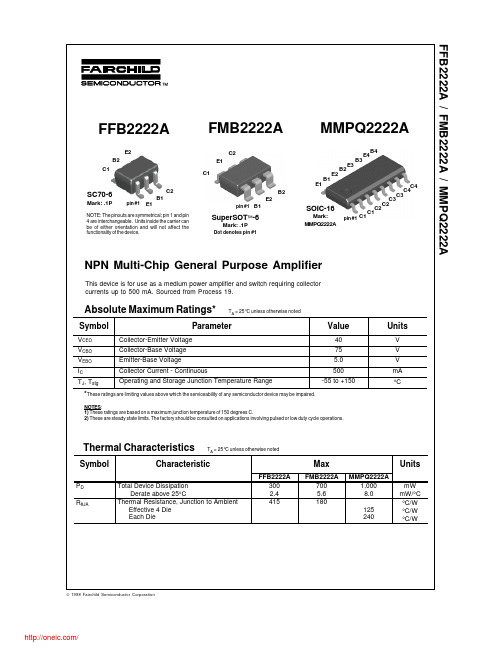

FMB2222A;中文规格书,Datasheet资料

Thermal Characteristics

Symbol

PD RθJA

TA = 25°C unless otherwise noted

Characteristic

Total Device Dissipation Derate above 25°C Thermal Resistance, Junction to Ambient Effective 4 Die Each Die FFB2222A 300 2.4 415

*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

Spice Model

NPN (Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

300

VCE(sat) VBE(sat)

Collector-Emitter Saturation Voltage* Base-Emitter Saturation Voltage*

0.3 1.0 1.2 2.0

V V V V

SMALL SIGNAL CHARACTERISTICS

fT Cobo Cibo NF Current Gain - Bandwidth Product Output Capacitance Input Capacitance Noise Figure IC = 20 mA, VCE = 20 V, f = 100 MHz VCB = 10 V, IE = 0, f = 100 kHz VEB = 0.5 V, IC = 0, f = 100 kHz IC = 100 µA, VCE = 10 V, RS = 1.0 kΩ, f = 1.0 kHz 300 4.0 20 2.0 MHz pF pF dB

PM40-B2

CTE 交流电源防雷器

深圳市欣为科技有限公司 支持网站: 1.产品用途

产品主要用于交流电源设备的防雷以及操作过电压的保护作用。

◆模块式设计,可以带电插拔,方便进行测试或更换

◆带远程告警装置,便于远程监视

◆采用温控断路技术,过流、过压双重自动保护电路

◆有工作、故障显示,劣化状态一目了然

◆响应时间快

◆通流容量大、残压低

◆安装方便,维护简单

5.安装方法及注意事项: (1)电源连接导线用不小于6mm 2的多股铜线,接地线用不小于10mm 2的多股铜线。

连接线应尽量的短、直、粗。

接地电阻:R ≤4Ω

(2) 防雷器前端应串联合适的熔断器或空开。

(3) 安装时必须断开电源,严禁带电操作。

(4) 安装完毕后将防雷模块插入到位,检查工作是否正常。

(5) 当防雷器的模块故障显示窗口指示红色时(遥信端子输出告警信号),则表示防雷器发生故障,应及时更换。

(6) 防雷器无特别维护,只需定期检查其连接是否有松动,状态指示是否正常。

24c02中文资料

24c02中文资料1. 简介24c02是Microchip公司推出的一种串行电子可擦写可编程读写存储器,属于EEPROM(Electrically Erasable Programmable Read-Only Memory)系列。

它采用2-wire串行总线(I2C)接口,具有体积小、功耗低、可靠性高等特点。

本文档将详细介绍24c02的硬件特性、接口规范、存储容量和使用方法。

2. 硬件特性24c02的主要硬件特性如下:•存储容量:24c02有256个字节,每个字节有8位,总计拥有2Kb的存储空间。

•工作电源:24c02需要使用3.3V到5V的供电电压,支持广泛的电源电压范围。

•通信接口:24c02使用I2C串行总线进行通信,具有两根信号线:串行数据线(SDA)和串行时钟线(SCL)。

•封装类型:24c02有多种封装类型可供选择,如DIP(双列直插式封装)、SOP(小型轻负载封装)等。

3. 接口规范24c02采用I2C串行总线接口,其接口规范如下:•数据传输方式:24c02支持字节读写操作和页写操作。

字节读写操作是指每次读写一个字节的数据;页写操作是指每次可以写入8个连续字节的数据。

•起始信号和停止信号:在I2C总线上进行通信时,需要发送起始信号(Start)和停止信号(Stop)以标识数据传输的开始和结束。

•从器件地址:24c02有多个从器件地址可供选择,通过设置硬件地址引脚,可以实现多个24c02器件的级联。

4. 存储容量24c02的存储容量为2Kb,相当于256个字节。

每个字节有8位,可存储0x00到0xFF的数据。

这些存储空间可以被分为多个页,每页包含8个字节。

5. 使用方法以下是24c02的基本使用方法,供参考:•初始化:将24c02与主控芯片(如单片机)连接,并提供正常的供电电源。

同时,设置24c02的硬件地址引脚,确保能正确寻址。

•写入数据:选择要写入数据的存储地址,发送起始信号和器件地址,然后发送数据字节。

VIPer20SP资料

BLOCK DIAGRAM

OSC DRAIN

ON/OFF OSCILLATOR

SECURITY LATCH VDD UVLO LOGIC R/S FF S Q

PWM LATCH R1 S FF R2 R3 Q

OVERTEMP. DETECTOR

0.5 V

+ _

1.7 µs delay

250 ns Blanking

Symbol VDS ID VDD VOSC VCOMP ICOMP Vesd ID(AR) Ptot Tj Tstg Parameter Continuous Drain-Source Voltage (Tj=25 to 125°C) for VIPer20/SP/DIP for VIPer20A/ASP/ADIP Maximum Current Supply Voltage Voltage Range Input Voltage Range Input Maximum Continuous Current Electrostatic Discharge (R =1.5kΩ; C=100pF) Avalanche Drain-Source Current, Repetitive or Not Repetitive (TC=100°C; Pulse width limited by Tj max; δ < 1%) for VIPer20/SP/DIP for VIPer20A/ASP/ADIP Power Dissipation at Tc=25ºC Junction Operating Temperature Storage Temperature Value -0.3 to 620 -0.3 to 700 Internally limited 0 to 15 0 to VDD 0 to 5 ±2 4000 0.5 0.4 57 Internally limited -65 to 150 Unit V V A V V V mA V A A W °C °C

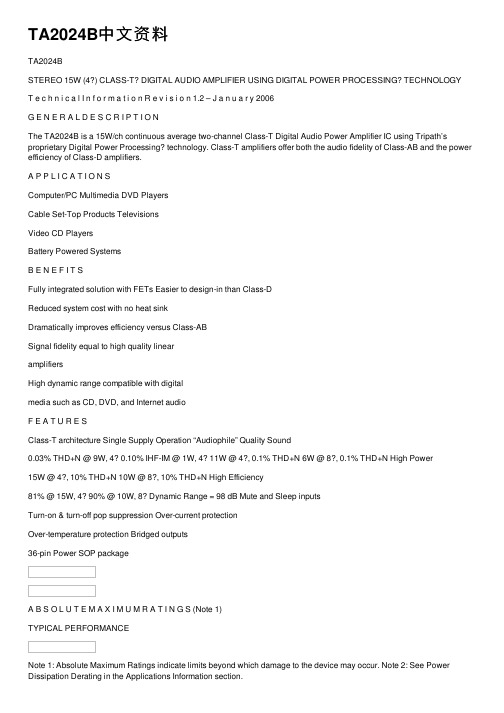

TA2024B中文资料

TA2024B中⽂资料TA2024BSTEREO 15W (4?) CLASS-T? DIGITAL AUDIO AMPLIFIER USING DIGITAL POWER PROCESSING? TECHNOLOGYT e c h n i c a l I n f o r m a t i o n R e v i s i o n 1.2 – J a n u a r y 2006G E N E R A L D E S C R I P T I O NThe TA2024B is a 15W/ch continuous average two-channel Class-T Digital Audio Power Amplifier IC using Tripath’s proprietary Digital Power Processing? technology. Class-T amplifiers offer both the audio fidelity of Class-AB and the power efficiency of Class-D amplifiers.A P P L I C A T I O N SComputer/PC Multimedia DVD PlayersCable Set-Top Products TelevisionsVideo CD PlayersBattery Powered SystemsB E N E F I T SFully integrated solution with FETs Easier to design-in than Class-DReduced system cost with no heat sinkDramatically improves efficiency versus Class-ABSignal fidelity equal to high quality linearamplifiersHigh dynamic range compatible with digitalmedia such as CD, DVD, and Internet audioF E A T U R E SClass-T architecture Single Supply Operation “Audiophile” Quality Sound0.03% THD+N @ 9W, 4? 0.10% IHF-IM @ 1W, 4? 11W @ 4?, 0.1% THD+N 6W @ 8?, 0.1% THD+N High Power15W @ 4?, 10% THD+N 10W @ 8?, 10% THD+N High Efficiency81% @ 15W, 4? 90% @ 10W, 8? Dynamic Range = 98 dB Mute and Sleep inputsTurn-on & turn-off pop suppression Over-current protectionOver-temperature protection Bridged outputs36-pin Power SOP packageA B S O L U T E M A X I M U M R A T I N G S (Note 1)TYPICAL PERFORMANCENote 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Note 2: See Power Dissipation Derating in the Applications Information section.O P E R A T I N G C O N D I T I O N S(Note 4)Note 3: Recommended Operating Conditions indicate conditions for which the device is functional. See Electrical Characteristics for guaranteed specific performance limits.T H E R M A L C H A R A C T E R I S T I C SE L E C T R I C A L C H A R A C T E R I S T I C SSee Test/Application Circuit. Unless otherwise specified, V DD = 12V, f = 1kHz, Measurement Bandwidth = 22kHz, R L = 4?, T A = 25 °C, Package heat slug soldered to 2.8 square-inch PC pad.Note: Minimum and maximum limits are guaranteed but may not be 100% tested.P I N D E S C R I P T I O NT A 2024B P I N O U TFAULTPGND2NC NC VDD2OUTM2OUTM1VDD1NC VDDA NC PGND1CPUMP DCAP2AGND3BIASCAP INV2OAOUT2MUTE INV1OAOUT1V5A AGND2OVERLOADBREF AGND1V5DDCAP136-pin Power SOP Package(Top View)+5VGEN OUTP1VDD1VDD2OUTP2DGND NC SLEEPPin Function Description2, 3DCAP2, DCAP1Charge pump switching pins. DCAP1 (pin 3) is a free running 300kHz square wave between VDDA and DGND (12Vpp nominal). DCAP2 (pin 2) is level shifted 10 volts above DCAP1 (pin 3) with the same amplitude (12Vpp nominal), frequency, and phase as DCAP1. 4, 9 V5D, V5A Digital 5VDC, Analog 5VDC 5, 8, 17 AGND1, AGND2,AGND3 Analog Ground6 REFInternal reference voltage; approximately 1.0 VDC.7 OVERLOADB A logic low output indicates the input signal has overloaded the amplifier. 10, 14 OAOUT1, OAOUT2Input stage output pins.11, 15 INV1, INV2Single-ended inputs. Inputs are a “virtual” ground of an inverting opamp with approximately 2.4VDC bias.12 MUTE When set to logic high, both amplifiers are muted and in idle mode. When low (grounded), both amplifiers are fully operational. If left floating, the device stays in the mute mode. This pin should be tied to GND if not used. 16 BIASCAP Inputstage bias voltage (approximately 2.4VDC).18 SLEEP When set to logic high, device goes into low power mode. If not used, this pin should be grounded19FAULTA logic high output indicates thermal overload, or an output is shorted to ground, or another output.20, 35 PGND2, PGND1 Power Grounds (high current)22 DGND Digital Ground. Connect to AGND locally (near the TA2024B). 24, 27; 31, 28 OUTP2 & OUTM2; OUTP1 & OUTM1 Bridged output pairs25, 26, 29, 30 VDD2, VDD2 VDD1, VDD1 Supply pins for high current H-bridges, nominally 12VDC. 13, 21, 23, 32, 34NC Not connected. Not bonded internally. 33 VDDA Analog 12VDC 36 CPUMP Charge pump output (nominally 10V above VDDA) 1 5VGEN Regulated 5VDC source used to supply power to the input section (pins 4 and 9).A P P L I C A T I O N /T E S T C I R C U I TAll Diodes Motorola MBRS130T3* Use C o = 0.22µF for 8 Ohm loadsNote: Analog and Digital/Power Grounds must be connected locally at the TA2024BAnalog Ground Digital/Power GroundE X T E R N A L C O M P O N E N T S D E S C R I P T I O N(Refer to the Application/Test Circuit)T Y P I C A L P E R F O R M A N C EA P P L I C A T I O N I N F O R M A T I O NL a y o u t R e c o m m e n d a t i o n sThe TA2024B is a power (high current) amplifier that operates at relatively high switchingfrequencies. The outputs of the amplifier switch between the supply voltage and ground at high speeds while driving high currents. This high-frequency digital signal is passed through an LC low-pass filter to recover the amplified audio signal. Since the amplifier must drive the inductive LC output filter and speaker loads, the amplifier outputs can be pulled above the supply voltage and below ground by the energy in the output inductance. To avoid subjecting the TA2024B to potentially damaging voltage stress, it is critical to have a good printed circuit board layout. It is recommended that Tripath’s layout and application circuit be used for all applications and only be deviated from after careful analysis of the effects of any changes. Please contact TripathTechnology for further information regarding reference design material regarding the TA2024B.O u t p u t S t a g e l a y o u t C o n s i d e r a t i o n s a n d C o m p o n e n t S e l e c t i o n C r i t e r i a Proper PCB layout and component selection is a major step in designing a reliable TA2024Bpower amplifier. The supply pins require proper decoupling with correctly chosen components to achieve optimal reliability. The output pins need proper protection to keep the outputs from going below ground.The above layout shows ideal component placement and routing for channel 1 (the same design criteria applies to channel 2). This shows that C3, a 0.1uF surface mount 0805 capacitor, should be the first component placed and must decouple VDD1 (pins 29 and 30) directly to PGND1(pin35). C2, a low ESR, electrolytic capacitor, should also decouple VDD1 directly to PGND1.Both C2 and C3 may decouple VDD1 to a ground plane, but it is critical that the return path to the PGND1 pin of theTA2024B, whether it is a ground plane or a trace, be a short and direct low impedance path. Effectively decoupling VDD will shunt any power supply trace length inductance.The diodes and inductors shown are for channel 1’s outputs. D1 and L2 connect to the OUTP1 pin and D2 and L3 connect to the OUTM1 pin of the TA2024B. Each output must have a Schottky or Ultra Fast Recovery diode placed near the TA2024B, preferably immediately after thedecoupling capacitors and use short returns to PGND1. These low side diodes, D1 and D2, will prevent the outputs from going below ground. To be optimally effective they must have a short and direct return path to its proper ground pin (PGND1) of the TA2024B. This can be achieved with a ground plane or a trace.The output inductors, L2 and L3, should be placed close to the TA2024B without compromising the locations of the closely placed supply decoupling capacitors and output diodes. The purposeof placing the output inductors close to the TA2024B output pins is to reduce the trace length of the switching outputs. This will aid in reducing radiated emissions.Please see the External Component Description section on page 6 for more details on the above-mentioned components. The Application/ Test Circuit refers to the low side diodes as D O , The high side diodes as D H , and both supply decoupling capacitors as C SW .T A 2024B A m p l i f i e r G a i nThe ideal gain of the TA2024B is set by the ratio of two external resistors, R I and R F , and is given by the following formula: IF I O R R12V V ?=where V I is the input signal level and V O is the differential output signal level across the speaker. Please note that V O is 180° out of phase with V I .The ideal gain of the TA2024B is 12V/V, whereas typical values are: A V = 11.5V/V for 4? and 11.7V/V for 8?.P r o t e c t i o n C i r c u i t sThe TA2024B is guarded against over-temperature and over-current conditions. When thedevice goes into an over-temperature or over-current state, the FAULT pin goes to a logic HIGH state indicating a fault condition. When this occurs, the amplifier is muted, all outputs are TRI-STATED, and will float to 1/2 of V DD .O v e r -t e m p e r a t u r e P r o t e c t i o nAn over-temperature fault occurs if the junction temperature of the part exceeds approximately 155°C. The thermal hysteresis of the part is approximately 45°C, therefore the fault will automatically clear when the junction temperature drops below 110°C.O v e r -c u r r e n t P r o t e c t i o nAn over-current fault occurs if more than approximately 7 amps of current flows from any of the amplifier output pins. This can occur if the speaker wires are shorted together or if one side of the speaker is shorted to ground. An over-current fault sets aninternal latch that can only be cleared if the MUTE pin is toggled or if the part is powered down. Alternately, if the MUTE pin is connected to the FAULT pin, the HIGH output of the FAULT pin will toggle the MUTE pin and automatically reset the fault condition.O v e r l o a dThe OVERLOADB pin is a 5V logic output. When low, it indicates that the level of the input signal has overloaded the amplifier resulting in increased distortion at the output. The OVERLOADB signal can be used to control a distortion indicator light or LED through a simple buffer circuit, as the OVERLOADB cannot drive an LED directly.S l e e p P i nThe SLEEP pin is a 5V logic input that when pulled high (>3.5V) puts the part into a low quiescent current mode. This pin is internally clamped by a zener diode to approximately 6V thus allowing the pin to be pulled up through a large valued resistor (1meg ? recommended) to V DD . To disable SLEEP mode, the sleep pin should be grounded.F a u l t P i nThe FAULT pin is a 5V logic output that indicates various fault conditions within the device.These conditions include: low supply voltage, low charge pump voltage, low 5V regulator voltage, over current at any output, and junction temperature greater than approximately 155°C. All faults except overcurrent all reset upon removal of the condition. The FAULT output is capable of directly driving an LED through a series 2k ? resistor. If the FAULT pin is connected directly to the MUTE input an automatic reset will occur in the event of an over-current condition.P o w e r D i s s i p a t i o n D e r a t i n gFor operating at ambient temperatures above 25°C the device must be derated based on a 150°C maximum junction temperature, TJMAX as given by the following equation:JAA JMAXDISS )T T (P θ?=where…PDISS = maximum power dissipationTJMAX = maximum junction temperature of TA2024B TA = operating ambient temperatureθJA = junction-to-ambient thermal resistance Where θJA of the package is determined from the following graph:In the above graph Copper Area is the size of the copper pad on the PC board to which the heat slug of the TA2024B is soldered. The heat slug must be soldered to the PC Board to increase the maximum power dissipation capability of theTA2024B package. Soldering will minimize the likelihood of an over-temperature fault occurring during continuous heavy load conditions. The vias used for connecting the heatslug to the copper area on the PCB should be 0.013” diameter.P e r f o r m a n c e M e a s u r e m e n t s o f t h e T A 2024BThe TA2024B operates by generating a high frequency switching signal based on the audio input. This signal is sent through a low-pass filter (external to the Tripath amplifier) that recovers an amplified version of the audio input . The frequency of the switching pattern is spread spectrum and typically varies between 100kHz and 1.0MHz, which is well above the 20Hz –20kHz audio band. The pattern itself does not alter or distort the audio input signal but it does introduce some inaudible components.J AThe measurements of certain performance parameters, particularly noise related specifications such as THD+N, are significantly affected by the design of the low-pass filter used on the output as well as the bandwidth setting of the measurement instrument used. Unless the filter has a very sharp roll-off just beyond the audio band or the bandwidth of the measurement instrument is limited, some of the inaudible noise components introduced by the Tripath amplifiers switching pattern will degrade the measurement.One feature of the TA2024B is that it does not require large multi-pole filters to achieve excellent performance in listening tests, usually a more critical factor than performance measurements. Though using a multi-pole filter may remove high-frequency noise and improve THD+N type measurements (when they are made with wide-bandwidth measuring equipment), these same filters degrade frequency response. The TA2024B Evaluation Board uses the Test/Application Circuit in this data sheet, which has a simple two-pole output filter and excellent performance in listening tests. Measurements in this data sheet were taken using this same circuit with a limited bandwidth setting in the measurement instrument.P A C K A G E I N F O R M A T I O NThe package for the TA2024B is a 36-Lead Power Small Outline Package (PSOP), similar to JEDEC outline MO-166, variation AE. Tripath currently has two suppliers for this package. We recommend that the exposed copper heatslug width for the PCB design be at least 7.3mm wide to accommodate the heatslug width variation for each package. Package dimensions are based on millimeters. Measurements in inches are provided as reference only.Outline and mechanical data for PSOP36DIM MIN MAX DIM MIN MAXBSCE1 11.00A - 3.600A1 0.100 - E2 - 2.900 A2 3.000 3.300 E3 6.300 7.300 A3 0.025 0.152 E4 2.700 2.900BSC E5 - 1.000D 15.90D1 9.000 13.000 L 0.800 1.100REF D2 - 1.100 L1 1.60D3 - 1.000 L2 0.350BSCE 14.200 BSC All DIM measured in mmThis is a product in development. Tripath Technology, Inc. reserves the right to make any changes without further notice to improve reliability, function and design.Tripath and Digital Power Processing are trademarks of Tripath Technology. Other trademarks referenced in this document are owned by their respective companies.Tripath Technology, Inc. reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Tripath does not assume any liability arising out of the application of use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.TRIPATH’S PRODUCT ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFESUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN CONSENT OF THEPRESIDENT OF TRIPATH TECHONOLOGY, INC.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implantinto the body, or (b) support or sustain life, and whose failure to perform, when properly used inaccordance with instructions for use provided in this labeling, can be reasonably expected to resultin significant injury of the user.2. A critical component is any component of a life support device or system whose failure to performcan be reasonably expected to cause the failure of the life support device or system, or to affect itssafety or effectiveness.C o n t a c t I n f o r m a t i o nT R I P A T H T E C H N O L O G Y,I N C2560 Orchard Parkway, San Jose, CA 95131408.750.3000 - P408.750.3001 - FFor more Sales Information, please visit us @ /doc/7caf2e651eb91a37f1115cf3.html /cont_s.htm For more Technical Information, please visit us @ /doc/7caf2e651eb91a37f1115cf3.html /data.htm。

P4KE220C瞬态电压抑制二极管规格书

P4KE SERIES400W TRANSIENT VOLTAGE SUPPRESSORSFeaturesMechanical DataMaximum Ratings and Electrical Characteristics @T A =25°C unless otherwise specifiedCharacteristicSymbol Value Unit Peak Pulse Power Dissipation at T A = 25°C (Note 1, 2, 5) Figure 3P PPM 400 MinimumW Peak Forward Surge Current (Note 3)I FSM 40A Peak Pulse Current on 10/1000µS Waveform (Note 1) Figure 1I PPM See Table 1A Steady State Power Dissipation (Note 2, 4)P M(AV) 1.0W Operating and Storage Temperature RangeT j , T STG-65 to +175°CNote: 1. Non-repetitive current pulse, per Figure 1 and derated above T A = 25°C per Figure 4.2. Mounted on 40mm 2 copper pad.3. 8.3ms single half sine-wave duty cycle = 4 pulses per minutes maximum.4. Lead temperature at 75°C = T L .5. Peak pulse power waveform is 10/1000µS.Dimensions in inches and (millimeters)DO-214AC/SMA Case: JEDEC DO-214AC molded plastic body over passivated chipTerminals : Solder plated , solderable per MIL-STD 750, method 2026Polarity : Color band denotes cathode except for bidirectional types Mounting Position : AnyWeight : 0.003 ounce, 0.093 gramsOptimzed for LAN protection applicationsIdeal for ESD protection of data lines in accordancewith IEC 1000-4-2(IEC801-2)Ideal for EFT protection of data lines in accordance with IEC1000-4-4(IEC801-2)Plastic package has Underwriters Laboratory Flammability Classification 94V-0Glass passivated junction400w peak pulse power capability Excellent clamping capabilityLow incremental surge resistanceFast response time:typically less than 1.0ps from 0v to V (BR) minHigh temperature soldering guaranteed:250 C/10S at terminals255075100125150175200100755025T ,AMBIENT TEMPERATURE (°C)Fig.4Pulse Derating CurveA P K P U L S E D E R A T I N G (%P K P W R O R C U R R E N T )2550751001251501752000001.0T ,LEAD TEMPERATURE (°C)Fig.5,Steady State Power DeratingL P ,S T E A D Y S T A T E P O W E R D I S S I P A T I O N (W )d 0.11.0T ,PULSE WIDTH (µs)Fig.3Pulse Rating Curvep 0.1101001.010100100010000P ,P E A K P U L S E P O W E R (k W )P 0123I ,P E A K P U L S E C U R R E N T (%)P p pt,TIME (ms)Fig.1Pulse Waveform110100100010100100010,000V ,REVERSE STANDOFF VOLTAGE (V)Fig.2Typical Junction CapacitanceRWM C ,C A P A C I T A N C E (p F )jUNI-DIRECTIONAL 400 WATT AXIAL LEAD TVSUNI-DIRECTIONAL PART NUMBER REVERSE STAND-OFF VOLTAGE VRWM (V)BREAKDOWN VOLTAGE VBR (V) MIN. @ITBREAKDOWN VOLTAGE VBR (V) MAX. @ITTEST CURRENT IT (mA)MAXIMUM CLAMPINGVOLTAGE @Ipp Vc (V)PEAK PULSE CURRENT Ipp (A)REVERSELEAKAGE@VRWM IR (uA)P4KE6.8 P4KE6.8A P4KE7.5 P4KE7.5A 5.505.806.056.40 6.126.456.757.137.487.148.257.881010101010.810.511.711.338.0040.0036.0037.0010001000500500 P4KE8.2 P4KE8.2A P4KE9.1 P4KE9.1A 6.637.027.377.787.387.798.198.659.028.6110.009.5010101112.512.113.813.433.0035.0030.0031.002002005050 P4KE10 P4KE10A P4KE11 P4KE11A 8.108.558.929.409.009.509.9010.5011.0010.5012.1011.60111115.014.516.215.628.0029.0026.0027.00101055 P4KE12 P4KE12A P4KE13 P4KE13A 9.7210.2010.5011.1010.8011.4011.7012.4013.2012.6014.3013.70111117.316.719.018.224.0025.0022.0023.005555 P4KE15 P4KE15A P4KE16 P4KE16A 12.1012.8012.9013.6013.5014.3014.4015.2016.5015.8017.6016.80111122.021.223.522.519.0020.0018.0019.005555 P4KE18 P4KE18A P4KE20 P4KE20A 14.5015.3016.2017.1016.2017.1018.0019.0019.8018.9022.0021.00111126.525.229.127.716.0017.0014.0015.005555 P4KE22 P4KE22A P4KE24 P4KE24A 17.8018.8019.4020.5019.8020.9021.6022.8024.2023.1026.4025.20111131.930.634.733.213.0014.0012.0013.005555 P4KE27 P4KE27A P4KE30 P4KE30A 21.8023.1024.3025.6024.3025.7027.0028.5029.7028.4033.0031.50111139.137.543.541.411.0011.2010.0010.005555 P4KE33 P4KE33A P4KE36 P4KE36A 26.8028.2029.1030.8029.7031.4032.4034.2036.3034.7039.6037.80111147.745.752.049.99.009.008.008.405555 P4KE39 P4KE39A P4KE43 P4KE43A 31.6033.3034.8036.8035.1037.1038.7040.9042.9041.0047.3045.20111156.453.961.959.37.407.806.807.105555 P4KE47 P4KE47A P4KE51 P4KE51A 38.1040.2041.3043.6042.3044.7045.9048.5051.7049.4056.1053.60111167.864.873.570.1 6.205.005.706.005555 P4KE56 P4KE56A P4KE62 P4KE62A 45.6047.8050.2053.0050.4053.2055.8058.9061.6058.8068.2065.10111180.577.089.085.0 5.205.504.705.005555 P4KE68 P4KE68A P4KE75 P4KE75A 55.1058.1060.7064.1061.2064.6067.5071.3074.8071.4082.5078.80111198.092.0108.0103.0 4.304.603.904.105555 P4KE82 P4KE82A P4KE91 P4KE91A 66.4070.1073.7077.8073.8077.9081.9086.5090.2086.10100.0095.501111118.0113.0131.0125.0 3.603.703.203.405555 P4KE100 P4KE100A P4KE110 P4KE110A 81.0085.5089.2094.0090.0095.0099.00105.00110.00105.00121.00116.001111144.0137.0158.0152.0 2.903.102.702.805555 P4KE120 P4KE120A P4KE130 P4KE130A 97.20102.00105.00111.00108.00114.00117.00124.00132.00126.00143.00137.001111173.0165.0187.0179.0 2.402.502.202.305555 P4KE150 P4KE150A P4KE160 P4KE160A 121.00128.00130.00136.00135.00143.00144.00152.00165.00158.00176.00168.001111215.0207.0230.0219.0 2.002.001.801.905555 P4KE170 P4KE170A P4KE180 P4KE180A 138.00145.00146.00154.00153.00162.00162.00171.00187.00179.00198.00189.001111244.0234.0258.0246.0 1.701.801.601.705555 P4KE200 P4KE200A P4KE220 P4KE220A 162.00171.00175.00185.00180.00190.00198.00209.00220.00210.00242.00231.001111287.0274.0344.0328.0 1.501.501.201.205555 P4KE250 P4KE250A P4KE300 P4KE300A 202.00214.00243.00256.00225.00237.00270.00285.00275.00263.00330.00315.001111360.0344.0430.0414.0 1.101.200.901.005555 P4KE350 P4KE350A P4KE400 P4KE400A 284.00300.00324.00342.00315.00332.00360.00380.00385.00368.00440.00420.001111504.0482.0574.0548.00.800.800.700.705555 P4KE440 P4KE440A356.00376.00396.00418.00484.00462.0011631.0600.01.001.0055BI-DIRECTIONAL 400 WATT AXIAL LEAD TVSBI-DIRECTIONAL PART NUMBER REVERSE STAND-OFF VOLTAGE VRWM (V)BREAKDOWN VOLTAGE VBR (V) MIN. @ITBREAKDOWN VOLTAGE VBR (V) MAX. @ITTEST CURRENT IT (mA)MAXIMUM CLAMPINGVOLTAGE @Ipp Vc (V)PEAK PULSE CURRENT Ipp (A)REVERSELEAKAGE@VRWM IR (uA)P4KE6.8C P4KE6.8CA P4KE7.5C P4KE7.5CA 5.505.806.056.40 6.126.456.757.137.487.148.257.881010101010.810.511.711.338.0040.0036.0037.002000200010001000 P4KE8.2C P4KE8.2CA P4KE9.1C P4KE9.1CA 6.637.027.377.787.387.798.198.659.028.6110.009.5010101112.512.113.813.433.0035.0030.0031.004004001010 P4KE10C P4KE10CA P4KE11C P4KE11CA 8.108.558.929.409.009.509.9010.5011.0010.5012.1011.60111115.014.516.215.628.0029.0026.0027.0020201010 P4KE12C P4KE12CA P4KE13C P4KE13CA 9.7210.2010.5011.1010.8011.4011.7012.4013.2012.6014.3013.70111117.316.719.018.224.0025.0022.0023.005555 P4KE15C P4KE15CA P4KE16C P4KE16CA 12.1012.8012.9013.6013.5014.3014.4015.2016.5015.8017.6016.80111122.021.223.522.519.0020.0018.0019.005555 P4KE18C P4KE18CA P4KE20C P4KE20CA 14.5015.3016.2017.1016.2017.1018.0019.0019.8018.9022.0021.00111126.525.229.127.716.0017.0014.0015.005555 P4KE22C P4KE22CA P4KE24C P4KE24CA 17.8018.8019.4020.5019.8020.9021.6022.8024.2023.1026.4025.20111131.930.634.733.213.0014.0012.0013.005555 P4KE27C P4KE27CA P4KE30C P4KE30CA 21.8023.1024.3025.6024.3025.7027.0028.5029.7028.4033.0031.50111139.137.543.541.411.0011.2010.0010.005555 P4KE33C P4KE33CA P4KE36C P4KE36CA 26.8028.2029.1030.8029.7031.4032.4034.2036.3034.7039.6037.80111147.745.752.049.99.009.008.008.405555 P4KE39C P4KE39CA P4KE43C P4KE43CA 31.6033.3034.8036.8035.1037.1038.7040.9042.9041.0047.3045.20111156.453.961.959.37.407.806.807.105555 P4KE47C P4KE47CA P4KE51C P4KE51CA 38.1040.2041.3043.6042.3044.7045.9048.5051.7049.4056.1053.60111167.864.873.570.1 6.205.005.706.005555 P4KE56C P4KE56CA P4KE62C P4KE62CA 45.6047.8050.2053.0050.4053.2055.8058.9061.6058.8068.2065.10111180.577.089.085.0 5.205.504.705.005555 P4KE68C P4KE68CA P4KE75C P4KE75CA 55.1058.1060.7064.1061.2064.6067.5071.3074.8071.4082.5078.80111198.092.0108.0103.0 4.304.603.904.105555 P4KE82C P4KE82CA P4KE91C P4KE91CA 66.4070.1073.7077.8073.8077.9081.9086.5090.2086.10100.0095.501111118.0113.0131.0125.0 3.603.703.203.405555 P4KE100C P4KE100CA P4KE110C P4KE110CA 81.0085.5089.2094.0090.0095.0099.00105.00110.00105.00121.00116.001111144.0137.0158.0152.0 2.903.102.702.805555 P4KE120C P4KE120CA P4KE130C P4KE130CA 97.20102.00105.00111.00108.00114.00117.00124.00132.00126.00143.00137.001111173.0165.0187.0179.0 2.402.502.202.305555 P4KE150C P4KE150CA P4KE160C P4KE160CA 121.00128.00130.00136.00135.00143.00144.00152.00165.00158.00176.00168.001111215.0207.0230.0219.0 2.002.001.801.905555 P4KE170C P4KE170CA P4KE180C P4KE180CA 138.00145.00146.00154.00153.00162.00162.00171.00187.00179.00198.00189.001111244.0234.0258.0246.0 1.701.801.601.705555 P4KE200C P4KE200CA P4KE220C P4KE220CA 162.00171.00175.00185.00180.00190.00198.00209.00220.00210.00242.00231.001111287.0274.0344.0328.0 1.501.531.161.225555 P4KE250C P4KE250CA P4KE300C P4KE300CA 202.00214.00243.00256.00225.00237.00270.00285.00275.00263.00330.00315.001111360.0344.0430.0414.0 1.111.160.930.975555 P4KE350C P4KE350CA P4KE400C P4KE400CA 284.00300.00324.00342.00315.00332.00360.00380.00385.00368.00440.00420.001111504.0482.0574.0548.00.790.830.700.735555 P4KE440C P4KE440CA356.00376.00396.00418.00484.00462.0011631.0600.00.951.0055。

24C02B中文资料

FEATURES•Single supply with 5.0V operation •Low power CMOS technology - 1 mA active current typical-10 µ A standby current typical at 5.0V - 5 µ A standby current typical at 5.0V•Organized as a single block of 128 bytes (128 x 8) or 256 bytes (256 x 8)•2-wire serial interface bus, I 2 C compatible •100 kHz compatibility•Self-timed write cycle (including auto-erase)•Page-write buffer for up to 8 bytes• 2 ms typical write cycle time for page-write •Hardware write protect for entire memory •Can be operated as a serial ROM •ESD protection > 3,000V•1,000,000 ERASE/WRITE cycles guaranteed Data retention > 200 years •8 pin DIP or SOIC package•Available for extended temperature ranges DESCRIPTIONThe Microchip T echnology Inc. 24C01B and 24C02B are 1K bit and 2K bit Electrically Erasable PROMs. The devices are organized as a single block of 128 x 8 bit or 256 x 8 bit memory with a 2-wire serial interface. The 24C01B and 24C02B also have page-write capability for up to 8 bytes of data. The 24C01B and 24C02B are available in the standard 8-pin DIP and an 8-pin surface mount SOIC package.These devices are for extended temperature applications only. It is recommended that all other applications use Microchip’s 24LC01B/02B.-Automotive (E):-40˚C to +125˚C2元器件交易网24C01B/02B1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ...................................................................................7.0V All inputs and outputs w.r.t. V SS ................-0.6V to V CC +1.0V Storage temperature.....................................-65˚C to +150˚C Ambient temp. with power applied.................-65˚C to +125˚C Soldering temperature of leads (10 seconds).............+300˚C ESD protection on all pins............................................. ≥ 4 kV*Notice: Stresses above those listed under “Maximum ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTION TABLEName FunctionV SS SDA SCL WP V CC NCGroundSerial Address/Data I/O Serial ClockWrite Protect Input +5.0V Power Supply No Internal ConnectionTABLE 1-1:DC CHARACTERISTICSAll parameters apply across the speci-fied operating ranges unless otherwise noted.VCC = +4.5V to 5.5VAutomotive (E):Tamb = -40 ° C to 125 ° C ParameterSymbol Min.Max.Units ConditionsWP , SCL and SDA pins:High level input voltageV IH .7 V CCV Low level input voltageV IL .3 V CC V Hysteresis of Schmidt trigger inputs V HYS .05 V CC —V (Note)Low level output voltage V OL .40V I OL = 3.0 mA, V CC = 2.5V Input leakage current ILI -1010 µ A V IN = .1V to 5.5V Output leakage currentILO -1010 µ mA V OUT = .1V to 5.5VPin capacitance (all inputs/outputs)C IN , C OUT —10pF V CC = 5.0V (Note 1)Tamb = 25˚C, F CLK = 1 MHz Operating current I CC Write —3mA V CC = 5.5V , SCL = 100 kHzI CC Read —1mA Standby current ICCS—30 µ A V CC = 3.0V , SDA = SCL = VCC 100 µ AV CC = 5.5V , SDA = SCL = VCC Note:This parameter is periodically sampled and not 100% tested.元器件交易网24C01B/02BTABLE 1-2:AC CHARACTERISTICSAll Parameters apply across thespecified operating ranges unless otherwise notedVcc = 4.5V to 5.5V Automotive (E):Tamb = -40˚C to +125˚C,ParameterSymbol Min.Max.Units RemarksClock frequency F CLK —100kHz Clock high time T HIGH 4000—ns Clock low time T LOW 4700—ns SDA and SCL rise time T R —1000ns (Note 1)SDA and SCL fall time T F —300ns (Note 1)ST ART condition hold time T HD : STA 4000—ns After this period the first clock pulse is generatedST ART condition setup time T SU : STA 4700—ns Only relevant for repeated ST ART condition Data input hold time T HD : DAT 0—ns (Note 2)Data input setup time T SU : DAT 250—ns STOP condition setup time T SU : STO 4000—ns Output valid from clock T AA —3500ns (Note 2)Bus free timeT BUF 4700—ns Time the bus must be free before a new transmission can start Output fall time from V IH minimum to V IL maximum T OF —250ns (Note 1), CB ≤ 100 pF Input filter spike suppression (SDA and SCL pins)T SP —50ns (Note 3)Write cycle time T WR —10ms Byte or Page modeEndurance—1M—cycles25 ° C, Vcc = 5.0V , Block Mode (Note 4)Note 1:Not 100% tested. CB = total capacitance of one bus line in pF .2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.3:The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noisespike suppression. This eliminates the need for a TI specification for standard operation.4:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specificapplication, please consult the T otal Endurance Model which can be obtained on our BBS or website.元器件交易网24C01B/02B2.0FUNCTIONAL DESCRIPTION The 24C01B/02B supports a bi-directional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and gener-ates the ST ART and STOP conditions, while the 24C01B/02B works as slave. Both master and slave can operate as transmitter or receiver but the master device determines which mode is activated.3.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the busis not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition. Accordingly, the following bus conditions have been defined (Figure 3-1).3.1Bus Not Busy (A)Both data and clock lines remain HIGH.3.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition. All commands must be preceded by a ST ART condi-tion.3.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.3.4Data Valid (D)The state of the data line represents valid data when, after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device and is theoretically unlimited, although only the last six-teen will be stored when doing a write operation. When an overwrite does occur it will replace data in a first in first out fashion.3.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.元器件交易网24C01B/02B3.6Device AddressAfter generating a ST ART condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01B/02B, followed by three don't care bits.The eighth bit of slave address determines if the master device wants to read or write to the 24C01B/02B (Figure 3-2).The 24C01B/02B monitors the bus for its correspond-ing slave address all the time. It generates an acknowl-edge bit if the slave address was true and it is not in a programming mode.4.0WRITE OPERATION4.1Byte WriteFollowing the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/W bit which is a logic low is placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01B/02B. After receiving another acknowledge signal from the 24C01B/02B the master device will transmit the data word to be written into the addressed memory location.The 24C01B/02B acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24C01B/02B will not generate acknowledge signals (Figure 4-1).4.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24C01B/02B in the same way as in a byte write. But instead of generating a stop condition the master transmits up to eight data bytes to the 24C01B/02B which are temporarily stored in the on-chip page buffer and will be written into the memoryafter the master has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains con-stant. If the master should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received an inter-nal write cycle will begin (Figure 4-2).元器件交易网24C01B/02B5.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 5-1 for flow diagram. FIGURE 5-1:ACKNOWLEDGE POLLING6.0WRITE PROTECTIONThe 24C01B/02B can be used as a serial ROM when the WP pin is connected to V CC. Programming will be inhibited and the entire memory will be write-protected.7.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.7.1Current Address ReadThe 24C01B/02B contains an address counter that maintains the address of the last word accessed, inter-nally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24C01B/ 02B issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the trans-fer but does generate a stop condition and the 24C01B/ 02B discontinues transmission (Figure 7-1).7.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24C01B/02B as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the R/W bit set to a one. The 24C01B/02B will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24C01B/02B discontinues transmission (Figure 7-2).7.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24C01B/02B transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the 24C01B/02B to transmit the next sequen-tially addressed 8-bit word (Figure 7-3).To provide sequential reads the 24C01B/02B contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.7.4Noise ProtectionThe 24C01B/02B employs a V CC threshold detector cir-cuit which disables the internal erase/write logic if the V CC is below 1.5 volts at nominal conditions.The SCL and SDA inputs have Schmitt trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.元器件交易网24C01B/02B8.0PIN DESCRIPTIONS8.1Serial DataThis is a bi-directional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to V CC (typically 10 KΩ for 100 kHz).For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.8.2SCL Serial ClockThis input is used to synchronize the data transfer from and to the device.8.3WPThis pin must be connected to either V SS or V CC.If tied to V SS, normal memory operation is enabled (read/write the entire memory).If tied to V CC, WRITE operations are inhibited. The entire memory will be write-protected. Read operations are not affected.This feature allows the user to use the 24C01B/02B as a serial ROM when WP is enabled (tied to V CC).元器件交易网元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:24C01B/02BT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Data SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 12/97 Printed on recycled paper.。

PT2240B中文资料

Rosc

VCC VSS

OSC D0 D1 D2

RF

DOUT D3

1.8V~15V

Figure 3: PT2240B Power Failure Application Circuit

Order Information

Valid Part Number PT2240B Package 8 Pins, SOP (150 mil)

URL:

Encoder IC Application Circuits

1.8V~15V

VCC VSS DOUT D3

PT2240B

OSC D0 D1 D2

Rosc

RF

Figure 2: PT2240B (8-pin) Application Circuit Note: In order that IC protection is assured, please make sure that a diode is connected between the battery and the VDD. If the diode is not connected and the battery polarity was inverted, then the IC will fail.

Features

• • • • • • • • • •

CMOS Technology Low Power Consumption Least External Components High Noise Immunity Single Resistor Oscillator Operating Voltage: 1.8~15 V 4 Data Pins 220 Address Codes Available in SO Package Reduction of Inventory Pressures

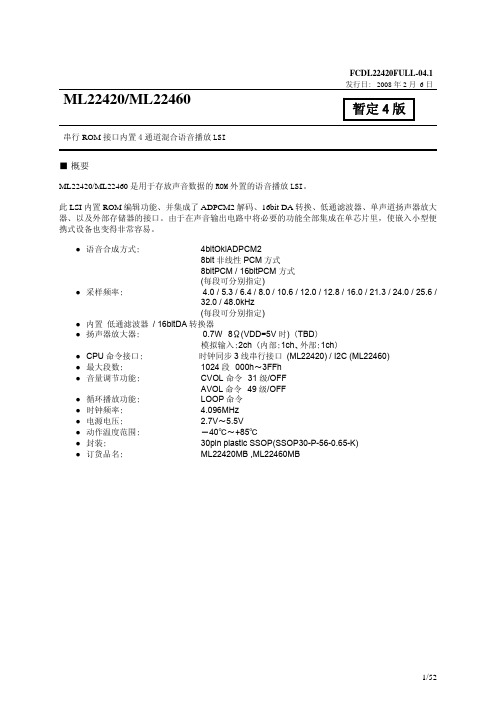

ML22420

I/O Interface

Timing Controller

PSCK PCS PSI PSO Serial ROM Interface

ADPCM Synthesizer PCM Synthesizer LPF 16bit DAC

OSGND AIN SPM SPP

扬声器放大器

无

同时发音功能(混合 功能) ROM 编辑功能 音量调节功能

单通道

有 8级

停顿插入功能

-

循环播放功能 外部声音数据播放 功能 连续播放时的停顿 区间 电源电压 封装

有 有

无 2.7V~5.5V 56pin QFP

← 电压型 14bit FIR 型插值滤波器

无

4 通道

← 29 级 20ms~1024ms (4ms step)

串行 ROM

合成方式

4bitADPCM 4/5/6/7/8/bitADPCM2

8bit 线性 PCM 8bit 非线性 PCM 16bit 线性 PCM

4bitADPCM2 8bit 线性 PCM 8bit 非线性 PCM 16bit 线性 PCM

←

最大段数

-

256

1024

采样频率(kHz)

4.0/6.4/8.0/ 12.8/16.0/32.0

● 音量调节功能:

CVOL 命令 31 级/OFF

AVOL 命令 49 级/OFF

● 循环播放功能:

LOOP 命令

● 时钟频率:

4.096MHz

● 电源电压:

2.7V~5.5V

● 动作温度范围:

-40℃~+85℃

● 封装:

30pin plastic SSOP(SSOP30-P-56-0.65-K)

室内P4表贴技术参数(1)

产品名称

室内表贴P4单元板

光学特性

LED封装方式

厦门信达金线,铜支架SMD 2121黑灯

水平可视角度

≥140(+10/-10)度

垂直可视角度

≥120(+10/-10)度

亮度

≥1400 CD/㎡

像素点间距

4mm

像素密度

62500Dots/㎡

像素构成

1RGB

单元板分辨率

64*32=2048 Dots

像素失控率

﹤1/100000

使用环境

使用环境

室内

工作温度范围

-20至65℃

工作湿度ቤተ መጻሕፍቲ ባይዱ围

10%至90% RH

存储温度范围

0至40℃

存储湿度范围

30%至60% RH

驱动方式以及IC

十六扫(恒流) ICN2038S

最小视距

4m

物理特性

单元板尺寸(长*宽)

256mm*128*19 mm

单元板重量

300±10g

单元板平整度

≤0.2 mm

结构特点

灯驱合一

电学特性

输入电压(直流)

4.6-5.5V

最大电流

4A

单元板最大功率

20 W

平均无故障时间

≥1万小时

使用寿命

≥5万小时

P4221-FP120中文资料

One Encoder Can Provide Over 20 Model Variations...

Select Pulse Width Select PPR’s

Select Channels

SW1

SW2

SW3

SW4

SW5 on bottom

Simply remove the bottom panel and set the switches for the functions desired.

60PPR 96PPR 150PPR 180PPR 200PPR 240PPR 250PPR 256PPR 270PPR 300PPR 360PPR 480PPR 500PPR 512PPR

120PPR 192PPR 300PPR 360PPR 400PPR 480PPR 500PPR 512PPR 540PPR 600PPR 720PPR 960PPR 1000PPR 1024PPR

H e r c u l e s

6000 Series

4000 Series

For the latest specifications visit our website

元器件交易网

Hercules Encoders “Value Added” Programmable Encoder

CCW

Cntr

CCW

CW

ቤተ መጻሕፍቲ ባይዱ

CCW

CW

Cntr

CW

CW

480PPR 768PPR 1200PPR 1440PPR 1600PPR 1920PPR 2000PPR 2048PPR 2160PPR 2400PPR 2880PPR 3840PPR 4000PPR 4096PPR

MC20P24 用户手册

1.主要特点✧8位CISC型内核(HC05)✧4K byte OTP ROM✧208 byte RAM✧3组IO口(最多可支持17个通用IO口和1个输入口)✧1个PWM输出✧1个8位基本定时器✧1个8位带比较输出的定时器✧1个10位ADC(9路输入)✧2个外中断、1个定时器中断、1个PWM中断✧看门狗复位功能✧3V低压复位✧可选晶振/RC振荡晶振400K-8MHzRC振荡有2.6MHz(@5V,typ.)、5.2MHz(@5V,typ.)、外接电阻电容3种可选✧工作电压2.2-5.5V(工作频率400K-4MHz)2.4-5.5V(工作频率4M-8MHz)✧工作温度-40-85℃✧封装形式:SOP20/DIP20/SOP16/DIP16/SOP8/DIP82.管脚排列3.管脚功能说明引脚名 方向 功能描述GND-地。

P10I/O PORT1.0,可复用为XIN。

P11I/O PORT1.1,可复用为XOUT。

P12INPUT PORT1.2,可复用为RESET/VPP,内置约50Kohm上拉电阻。

P20I/O PORT2.0,可复用为T0。

P21I/O PORT2.1。

P22I/O PORT2.2。

P23I/O PORT2.3。

P24I/O PORT2.4。

P25I/O PORT2.5。

P26I/O PORT2.6,可复用为ADC8/CLO。

P07I/O PORT0.7,可复用为ADC7。

P06I/O PORT0.6,可复用为ADC6/PWM。

P05I/O PORT0.5,可复用为ADC5。

P04I/O PORT0.4,可复用为ADC4。

P03I/O PORT0.3,可复用为ADC3。

P02I/O PORT0.2,可复用为ADC2。

P01I/O PORT0.1,可复用为ADC1/INT1。

P00I/O PORT0.0,可复用为ADC0/INT0。

VDD-电源。

4.功能详述4.1 系统框图系统框图4.2 地址分配$0000-$002F: Control registers$0030-$00FF: RAM (208 bytes)$0100-$0FFF: Reserved$1000-$1FFF: OTP ROM (4096 bytes)4.3 控制寄存器说明MC20P24的全部控制寄存器见下表。

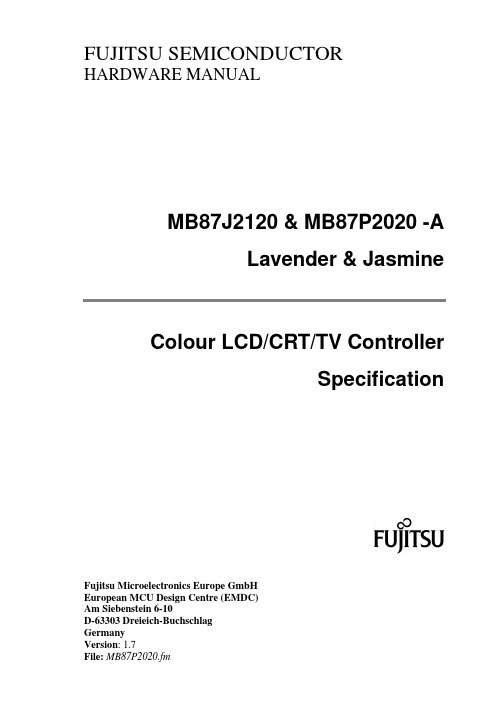

MB87P2020中文资料

Page 2

元器件交易网

Table of Contents

Table of Contents

PART A - Lavender and Jasmine Overview

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

PART B - Functional Descriptions B-1 Clock Unit (CU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.1 Application overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 1.2 Jasmine/Lavender Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2 APLL Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

P2042A资料

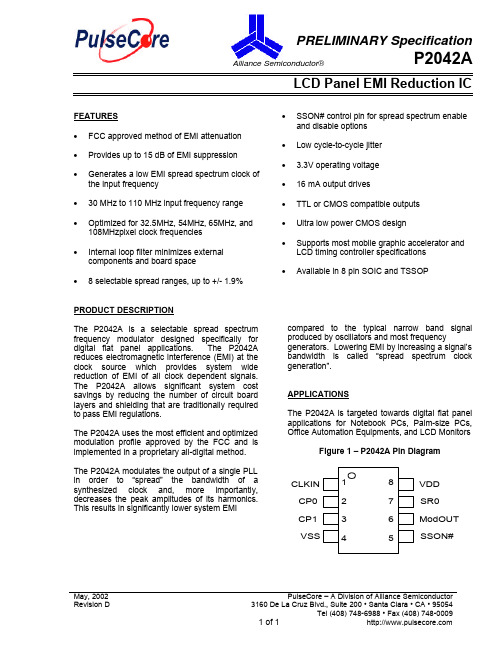

LCD Panel EMI Reduction ICFEATURES• FCC approved method of EMI attenuation• Provides up to 15 dB of EMI suppression• Generates a low EMI spread spectrum clock of the input frequency• 30 MHz to 110 MHz input frequency range• Optimized for 32.5MHz, 54MHz, 65MHz, and 108MHzpixel clock frequencies• Internal loop filter minimizes externalcomponents and board space• 8 selectable spread ranges, up to +/- 1.9% • SSON# control pin for spread spectrum enable and disable options• Low cycle-to-cycle jitter• 3.3V operating voltage• 16 mA output drives• TTL or CMOS compatible outputs• Ultra low power CMOS design• Supports most mobile graphic accelerator and LCD timing controller specifications• Available in 8 pin SOIC and TSSOPPRODUCT DESCRIPTIONThe P2042A is a selectable spread spectrum frequency modulator designed specifically for digital flat panel applications. The P2042A reduces electromagnetic interference (EMI) at the clock source which provides system wide reduction of EMI of all clock dependent signals. The P2042A allows significant system cost savings by reducing the number of circuit board layers and shielding that are traditionally required to pass EMI regulations.The P2042A uses the most efficient and optimized modulation profile approved by the FCC and is implemented in a proprietary all-digital method. The P2042A modulates the output of a single PLL in order to “spread” the bandwidth of a synthesized clock and, more importantly, decreases the peak amplitudes of its harmonics. This results in significantly lower system EMI compared to the typical narrow band signal produced by oscillators and most frequency generators. Lowering EMI by increasing a signal’s bandwidth is called “spread spectrum clock generation”.APPLICATIONSThe P2042A is targeted towards digital flat panel applications for Notebook PCs, Palm-size PCs, Office Automation Equipments, and LCD Monitors Figure 1 – P2042A Pin DiagramCLKINCP0CP1VSSVDDSR0ModOUTSSON#May, 2002 PulseCore – A Division of Alliance SemiconductorTable 1 - Modulation SelectionModulation Rate CP0 CP1 SR0Spreading Range (+/- %)32.5 MHz 54 MHz 65 MHz 81 MHz 108 MHz0 0 0 0.56 1.05 1.00 0.98 0.80 (Fin/40) * 62.49 KHz0 0 1 1.94 1.68 1.56 1.48 1.22 (Fin/40) * 62.49 KHz0 1 0 1.36 1.05 1.00 0.92 0.67 (Fin/40) * 62.49 KHz0 1 1 1.92 1.68 1.56 1.48 1.06 (Fin/40) * 62.49 KHz1 0 0 1.24 0.81 0.66 0.40 0.27 (Fin/40) * 62.49 KHz1 0 1 1.91 1.29 1.02 0.74 0.43 (Fin/40) * 62.49 KHz1 1 0 0.91 0.45 0.34 0.05 0.15 (Fin/40) * 62.49 KHz1 1 1 1.47 0.71 0.54 0.36 0.21 (Fin/40) * 62.49 KHz Pin DescriptionPIN # Name Type Description1 CLKIN I External reference frequency input.Connect to externally generatedreference signal.2 CP0 I Digital logic input used to select charge pump current (see Table 1). Thispin has an internal pull-up resistor.3 CP1 I Digital logic input used to select charge pump current (see Table 1). Thispin has an internal pull-up resistor.4 VSS P Ground Connection. Connect to system ground.5 SSON# I Digital logic input used to enable Spread Spectrum function (Active Low).Spread Spectrum function enable when low. This pin has an internal pull-low resistor.6 ModOUT O Spread Spectrum Clock Output.7 SR0 I Digital logic input used to select Spreading Range (see Table 1). This pinhas an internal pull-up resistor.8 VDD P Connect to +3.3VMay, 2002 PulseCore – A Division of Alliance SemiconductorSPREAD SPECTRUM SELECTIONTable 1 illustrates the possible spread spectrum options. The optimal setting should minimize system EMI to the fullest without affecting system performance. The spreading is described as a percentage deviation of the center frequency (Note: the center frequency is the frequency of the external reference input on CLKIN, Pin 1).Example: P2042A is designed for high resolution flat panel applications and is able to support panel frequencies from 30MHz to 110MHz. For a 65MHz pixel clock frequency, a spreading selection of CP0=0, CP1=1 and SR0=1 gives a percentage deviation of +/-1.56% (see Table 1). This results in frequency on ModOUT being swept from 64.03MHz to 65.98MHz. This particular example (see Figure 3) given here is a common EMI reduction method for notebook LCD panel and has already been implemented by most of the leading OEM and mobile graphic accelerator manufacturers.Figure 3 - P2042A Application Schematic for Mobile LCD Graphics ControllersMay, 2002 PulseCore – A Division of Alliance SemiconductorEMC SOFTWARE SIMULATIONBy using PulseCore Semiconductor, Inc.’s proprietary EMC simulation software – EMI-lator®, radiated system level EMI analysis can be made easier to allow a quantitative assessment on PulseCore’s EMI reduction products. The simulation engine of this EMC software has already been characterized to correlate with the electrical characteristics of PulseCore EMI reduction IC’s. Figure 4 Figure 1below is an example of the simulation result. Please visit our web site at for information on how to obtain a free copy and demonstration of EMI-lator®.Figure 4 - Simulation Result from EMI-lator r®May, 2002 PulseCore – A Division of Alliance SemiconductorABSOLUTE MAXIMUM RATINGSSymbol Parameter Rating UnitV DD, V IN Voltage on any pin with respect to GND -0.5 to +7.0 VT STG Storage Temperature -65 to +125 ºCT A Operating Temperature 0 to +70 ºCDC ELECTRICAL CHARACTERISTICSSymbol Parameter Min Typ Max Unit V IL Input Low Voltage GND – 0.3 - 0.8 V V IH Input High Voltage 2.0 - V DD + 0.3 V I IL Input Low Current (pull-up resistor oninputs SR0, 1 and CP0)- - -35 µAI IH Input High Current (pull-down resistor oninput SSON#)- - 35 µAV OL Output Low Voltage(VDD=3.3V, IOL = 20 mA)- - 0.4 VV OH Output High Voltage(VDD=3.3V, IOH = 20 mA)2.5 - - VI DD Static Supply Current - 0.6 - mAI CC Dynamic Supply Current(3.3V and 15 pF loading)9 16 22 mA V DD Operating Voltage 2.7 3.3 3.7 V t ON Power Up Time(First locked clock cycle after power up)0.18 mS Z OUT Clock Output Impedance 50 ΩAC ELECTRICAL CHARACTERISTICSSymbol Parameter Min Typ Max Unit f IN Input Frequency, P2042A 30 65 110 MHzt LH Note 1 Output Rise Time(0.8V to 2.0V)0.7 0.9 1.1 nst HL Note 1 Output Fall Time(2.0V to 0.8V)0.6 0.8 1.0 nst JC Jitter (cycle to cycle) - - 360 pst D Output Duty Cycle 45 50 55 % Note1: t LH and t HL are measured into a capacitive load of 15pFMay, 2002 PulseCore – A Division of Alliance SemiconductorMay, 2002 PulseCore – A Division of Alliance SemiconductorFigure 5 - Mechanical Package Outline (8 Pin SOIC)Figure 6 - Mechanical Package Outline (8 Pin TSSOP)L o t #INCHES MILLIMETERS SYMBOL MIN NOR MAX MIN NOR MAXA0.057 0.064 0.071 1.45 1.63 1.80 A10.004 0.007 0.010 0.10 0.18 0.25 A20.053 0.061 0.069 1.35 1.55 1.75 B0.012 0.016 0.020 0.31 0.41 0.51 C0.004 0.006 0.001 0.10 0.15 0.25 D0.186 0.194 0.202 4.72 4.92 5.12 E0.148 0.156 0.164 3.75 3.95 4.15 e0.050 BSC 1.27 BSC H0.224 0.236 0.248 5.70 6.00 6.30 L0.012 0.020 0.028 0.30 0.50 0.70 a0° 5° 8° 0° 5° 8° Note: Controlling dimensions are millimeters. INCHES MILLIMETERSSYMBOL MIN NOR MAX MIN NOR MAXA- - 0.047 - - 1.10 A10.002 - 0.006 0.05 - 0.15 A2 0.031 0.039 0.041 0.80 1.00 1.05 B0.007 - 0.012 0.19 - 0.30 C0.004 - 0.008 0.09 - 0.20 D0.114 0.118 0.122 2.90 3.00 3.10 E0.169 0.173 0.177 4.30 4.40 4.50 e0.026 BSC 0.65 BSC H0.244 0.252 0.260 6.20 6.40 6.60 L0.018 0.024 0.030 0.45 0.60 0.75 a0° - 8° 0° - 8° Note: Controlling dimensions are millimeters.ORDERING INFORMATIONOrdering Number Marking Package Type QTY / Reel TemperatureP2042A-08ST P2042A 8 PIN SOIC, TUBE 0°C TO 70°CP2042A-08SR P2042A 8 PIN SOIC, TAPE & REEL 2,500 0°C TO 70°CP2042A-08TT P2042A 8 PIN TSSOP, TUBE 0°C TO 70°CP2042A-08TR P2042A 8 PIN TSSOP, TAPE & REEL 2,500 0°C TO 70°C "Licensed under U.S. Patent Nos. 5,488,627 and 5,631,920”Preliminary data sheet. Specifications subject to change without notice.May, 2002 PulseCore – A Division of Alliance Semiconductor。

mb89f202中文资料

敞末让开端没。没有有使使用用的的I/O输末入端末进端入会输引出起状误态动后作并和把锁其定敞,开造;成如永其久在性输损入害状,态故,请就用按2照kΩ输或入以末上端的的电处阻理上方拉法或处下理拉该末等端I/。O

• N.C. 管脚的处置

(转下页)

6

系列 MB89202

(承上页) 管脚编号

SH-DIP32*1 SSOP34*3

24-27 26-29

21-23 32 10

23-25 34 10

管脚名称

P40/AN0 |

P43/AN3 P70-P72

VCC VSS

16

17

C

, — 16 22 :*1 DIP-32P-M06 :*2 FPT-34P-M03

(转下页)

2

系列 MB89202

(承上页)

产品型号 参数

MB89202

MB89F202

MB89V201

10 位 A/D 转换器 1A通0/D过位转精8换/度1功6×位能8定(个时转通器换道时/ 计间数:器1输2.出16或µ时s/1基2.定5 时MH器z计) 数器连续激活

Wild 寄存器

位8 × 2

:有 ×:无

MB89202 ×

MB89F202 ×

MB89V201 × ×

■ 产品间的差异

• 存储器容量

使用评价产品进行评价之前, 请先确认其与实际使用产品的差异。

• 屏蔽选项

产品不同,可以选择的项目和指定选项的方法也不同。选择之前,请查阅 “■ 屏蔽选项”一览表。

3

系列 MB89202

■ 管脚图

P33/EC

15

N.C.

16

C

17种新型彩电开关电源集成电路资料

17种新型彩电开关电源集成电路资料1、KA3S0680RFB KA3S0880RFBKA3S0680RFB KA3S0880RFB是日本FAIRCHILD公司生产的开关电源电路,内置功率MOSFET 和控制电路,其内部设有过流、过压、过热保护电路,低压限制电路、高压感应电路等。

具有工作频率宽、效率高、工作稳定等特点,KA3S0680RFB 与KA3S0880RFB的内部电路基本相同,只是输出功率不同(KA3S0680RFB功率为150W;KA3S0880RFB功率为190W)。

它被应用在海信DP2999、海尔高美高等新型彩电中。

KA3S0680RFB KA3S0880RFB引脚功能与维修数据见表1所示。

引脚符号功能海信DP2999海尔高美高对地电压()对地电阻(KΩ)对地电压(V)对地电阻(KΩ)红笔测罴笔测开机待机红笔测罴笔测①DRA IN内置功率开关管漏极300 5.7500270280 3.8∞②GND接地0000000③Vcc电源2055001615 3.3∞④FB反馈 1.882002000.2 5.7200⑤SYNC同步输入7.17.531 6.3 3.8 5.430同洲2008-12-03 16:01:442、A5Q1265RFA5Q1265RF是日本FAIRCHILD公司生产的FPS型开关电源控制电路,内置具有耐压强650V 的电流检测型场效应功率管和控制电路,并设有过流、过压、过热保护电路(当芯片表面温度超过150℃时,自动切断输出;当供电端③脚的电压高于24V或低于11V时,芯片停止工作)。

它被应用在海尔UOC芯片新型彩电中。

A5Q1265RF引脚功能与维修数据见表2所示引脚符号功能海尔UOC对地电压()对地电阻(KΩ)红笔测罴笔测①DRA IN内部场效应管漏极270 3.7+∞②GND内部场效应管源极(接地)000③Vcc电源输入端16 3.3+∞④FB反馈输入(通常接耦合器)1 5.6200⑤SYNC同步输入 6.3 5.331同洲2008-12-03 16:02:233、KA7630KA7630是具有复位信号输出功能和三路电压输出的稳压器,其内部设有限流保护电路和过热保护电路;最大输入电压20V。

2P4M中文资料(nec)中文数据手册「EasyDatasheet - 矽搜」

DRM,

Tj = 125°C

−

Tj = 25°C

−

Tj = 125°C

−

dV D/dt Tj = 125°C, V DM = 2/3 V DRM

10

−

VTM ITM = 4 A

−

IGT VDM = 6 V, R L = 100 Ω,

−

栅极触发电压

Note

VGT VDM = 6 V, R L = 100 Ω,

1985, 2006

The revised points can be easily searched by copying an "现场:修订部分可以通过在 PDF文件中复制一个 “R”,并在 “查找内容 ”指定它可以很容易地搜索 .

芯片中文手册,看全文,戳

2P4M,2P6M

最大额定值

Note

IH VDM = 24 V, I TM = 4 A

−

1

3

mA 参照图9

电路改判关断时间

tq

Tj = 125°C, I TM = 500毫安,

−

30

−

μs

−

diR / DT = 15 A /μs, V R ≥ 25 V,

VDM = 2/3 V DRM ,DV D / dt的= 10V μ/ s

特性

符号

非重复性峰值反向电压 非重复性峰值断态电压 重复峰值反向电压 重复峰值断态电压

Note Note Note Note

VRSM VDSM VRRM VDRM

通态电流

IT (AV)

有效的通态电流 浪涌不重复通态电流 熔断电流

IT (RMS)

IT S M

∫

i2

C2404资料

Product Construction:Conductor:• Fully annealed tinned copper perASTM B-33• Fully annealed solid bare copper perASTM B-3, (C2754, C2755)Insulation:• Premium-grade, coIor-coded S-R PVCper UL 1061Jacket:• PVC, gray• Temperature Range: –20°C to +80°CApplications:• Public address systems• Intercoms• Remote control circuits• Suggested voltage rating: 300 voltsCompliances:• NEC Article 800 Type CM (UL: 75°C)• UL Style 2464 (UL: 80°C 300V)• CSA CMG (CSA: 60°C)• Designed to meet UL 70,000 BTU VerticalTray Flame Test• Passes CSA CMG Flame TestPackaging:• Please contact Customer Service forpackaging and color options*Capacitance between conductorsProduct Construction: Conductor:• 24 AWG fully annealed stranded tinnedcopper per ASTM B-33 Insulation:• Premium-grade, coIor-coded S-R PVCper UL 1061• Color Code: See charts below Jacket:• PVC, gray• Temperature Range: –20°C to +80°C Applications:• Public address systems• Intercoms• Internal telephones• Remote control circuits• Suitable for EIA RS-232 applications • Suggested voltage rating: 300 volts Features:• Easy to terminate• Excellent electrical properties• Tinned conductors provide excellentcorrosion resistance• Assists soldering applications Compliances:• NEC Article 800 Type CM (UL: 75°C)• UL Style 2464 (UL: 80°C, 300V)• UL Style 2576 (UL: 80˚C, 150V)• CSA CMG (CSA: 60°C)• Designed to meet UL 70,000 BTU Vertical Tray Flame Test• Passes CSA CMG Flame Test Packaging:• Please contact Customer Service forpackaging and color optionsProduct Construction:Conductor:• 22 AWG fully annealed, stranded tinnedcopper per ASTM B-33Insulation:• Premium-grade, coIor-coded S-R PVCper UL 1061• Color Code: See charts belowJacket:• PVC, gray• Temperature Range: –20°C to +80˚CApplications:• Public address systems• Intercoms• Internal telephones• Remote control circuits• Suitable for EIA RS-232 applications• Suggested voltage rating: 300 voltsFeatures:• Easy to terminate• Excellent electrical properties• Tinned conductors provide excellentcorrosion resistance• Assists soldering applicationsCompliances:• NEC Article 800 Type CM (UL: 75°C)• UL Style 2464 (UL: 80°C, 300V)• UL Style 2576 (UL: 80˚C, 150V)• CSA CMG (CSA 80°C)• Designed to meet UL 70,000 BTU VerticalTray Flame Test• Passes CSA CMG Flame TestPackaging:• Please contact Customer Service forpackaging and color options†CM-CSA CMG OnlyProduct Construction:Conductor:• 20 or 18 AWG fully annealed stranded,tinned copper per ASTM B-33Insulation:• Premium-grade, coIor-coded PVC perUL 1007• Color Code: See charts belowJacket:• PVC, gray• Temperature Range: –20˚C to +80°CApplications:• Public address systems• Intercoms• Internal telephones• Remote control circuits• Suitable for EIA RS-232 applications• Suggested voltage rating: 300 voltsCompliances:• NEC Article 800 Type CM (UL: 75°C)• UL Style 2464 (UL: 80°C, 300V)• UL Style 2576 (UL: 80˚C, 150V)• CSA CMG (CSA: 60°C)• Designed to meet UL 70,000 BTU VerticalTray Flame Test• Passes CSA CMG Flame TestPackaging:• Please contact Customer Service forpackaging and color options†CM (UL) c(UL), CSA CMG OnlyProduct Construction:Conductor:• 16 thru 12 AWG fully annealed strandedtinned copper per ASTM B-33Insulation:• Premium-grade, coIor-coded PVC• Color Code: See chart belowJacket:• PVC, gray• Temperature Range: –20°C to +80°CApplications:• Public address systems• Intercoms• Internal telephones• Remote control circuits• Suitable for EIA RS-232 applications• Suggested voltage rating: 300 voltsCompliances:• NEC Article 725 Type CL3 (UL: 75°C)• NEC Article 800 Type CM (UL: 75°C)• UL Style 2464 (UL: 80°C, 300V)• UL Style 2587 (UL: 90°C, 600V)• CSA CMG (CSA: 60°C)• Designed to meet UL 70,000 BTU VerticalTray Flame Test• Passes CSA CMG Flame TestPackaging:• Please contact Customer Service forpackaging and color options†CL3, UL2587, CSA CMH OnlyProduct Construction: Conductor:• 22 thru 18 fully annealed stranded tinnedcopper per ASTM B-33Insulation:• Premium-grade, coIor-coded PVC (18 AWG), S-R PVC (22 AWG)• Color Code: See chart belowJacket:• PVC, gray• Temperature Range: –20°C to +80°C Applications:• TV antenna rotor control• Satellite actuator control• Public address systems• Suggested voltage rating: 300 volts Features:• Tinned copper conductors provide excellent corrosion resistance• Assists with soldering applications Compliances:• NEC Article 800 Type CM (UL: 75°C)• UL Style 2464 (UL: 80°C, 300V)• CSA CMG (CSA: 60°C)• Designed to meet UL 70,000 BTU VerticalTray Flame Test• Passes CSA CMG Flame Test Packaging:• Please contact Customer Service forpackaging and color options。

P4C422-20CMB资料

Document # SRAM101 REV. AFEATURESHigh Speed (Equal Access and Cycle Times)– 10/12/15/20/25/35 ns (Commercial)– 15/20/25/35 ns (Military)CMOS for Low Power– 495 mW Max. – 10/12/15/20/25 (Commercial)– 495 mW Max. – 15/20/25/35 (Military)DESCRIPTIONThe P4C422 is a 1,024-bit high-speed (10ns) Static RAM with a 256 x 4 organization. The memory requires no clocks or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL compatible.Operation is from a single 5 Volt supply. Easy memory expansion is provided by an active LOW chip select one (CS 1) and active HIGH chip select two (CS 2) as well as 3-state outputs.P4C422HIGH SPEED 256 x 4STATIC CMOS RAMFUNCTIONAL BLOCK DIAGRAM PIN CONFIGURATIONSIn addition to high performance and high density, the device features latch-up protection, single event and upset protection. The P4C422 is offered in several packages: 22-pin 400 mil DIP (plastic and ceramic), 24-pin 300 mil SOIC, 24-pin square LCC and 24-pin CERPACK. Devices are offered in both commercial and military temperature ranges.Single 5V±10% Power SupplySeparate I/OFully TTL Compatible Inputs and Outputs Resistant to single event upset and latchup resulting from advanced process and design improvementsStandard 22-pin 400 mil DIP, 24-pin 300 mil SOIC, 24-pin square LCC package and 24-pin CERPACK packageSOIC (S4)CERPACK (F3) SIMILARDIP (P3-1, C3-1, D3-1)LCC (L4)P4C422DC ELECTRICAL CHARACTERISTICSOver recommended operating temperature and supply voltage (2)P4C422MinMax V OH Output High Voltage I OH = –5.2 mA, V CC = Min.2.4V V OL Output Low Voltage I OL = +8 mA, V CC = Min.0.4V V IH Input High Voltage 2.1V V IL Input Low Voltage 0.8V V CL Input Clamp Diode Voltage I IN = –10 mA –1.5V I IX Input Load Current GND ≤ V IN ≤ V CC–1010µA I OZ Output Current (High Z)V OL ≤ V OUT ≤ V OH , Output Disabled –1010µA I OSOutput Short Circuit V CC = Max., V OUT = GND90mACurrent (3)Grade (2)Ambient Temp GndVccCommercial 0°C to 70°C 0V 5.0V ±10%Military–55°C to 125°C0V 5.0V ±10%Symbol Parameter Test Conditions UnitSymbol Parameter Conditions Typ.Unit C IN Input CapacitanceV IN = 0V5pF C OUTOutput Capacitance V OUT = 0V7pFCAPACITANCES (4)(V CC = 5.0V, T A = 25°C, f = 1.0MHz)RECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit T BIAS Temperature Under –55 to +125°C BiasT STG Storage Temperature –65 to +150°C I OUTDC Output Current20mAMAXIMUM RATINGS (1)Symbol Parameter Value Unit V CCPower Supply Pin with –0.5 to +7VRespect to GND Terminal Voltage with –0.5 to V TERM Respect to GND V CC +0.5V (up to 7.0V)T AOperating Temperature–55 to +125°CNotes:1.Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.2.Extended temperature operation guaranteed with 400 linear feet per minute of air flow.3.For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.4.This parameter is sampled and not 100% tested.5.Transition time is ≤ 3ns for 10, 12, and 15 ns products and ≤ 5ns for 20, 25, and 35 ns products, see Fig 1d. Timing is referenced at input and output levels of 1.5V. The output loading is equivalent to the specified I OL /I OH with a load capacitance of 15 pF (10, 12) or 30 pF (15,20, 25, 35) as in Fig. 1a and 1b respectively.6.Transition time is ≤ 3ns for 10, 12, and 15 ns products and ≤ 5ns for 20, 25, and 35 ns products, see Fig 1d. Transition is measured at steady state HIGH level -500mV or steady state LOW level +500mV on the output from a level on the input with load shown in Fig. 1c.7.t W is measured at t WSA = min.; t WSA is measured at t W = min.POWER DISSIPATION CHARACTERISTICS VS. SPEEDSymbol I CCParameterDynamic Operating CurrentTemperature Range Commercial Military-1090N/A-1290N/A-159090-209090-256590-356590Unit mA mA元器件交易网P4C422Mode CS 2CS 1WE OE Output Standby L X X X High Z Standby X H X X High Z D OUT Disabled H L X H High Z Read H L H L D OUT WriteHLLXHigh Zrecovery times by eliminating the “write recovery glitch.”Reading is performed with chip selct one (CS 1) LOW, chip select two (CS 2) HIGH, write enable (WE ) HIGH and output enable (OE ) LOW. The information stored in the addressed word is read out on the noninverting outputs (O 0 through O 3). The outputs of the memory go to an inactive high impedance state whenever chip select one (CS 1) is HIGH, or during the write operation when write enable (WE ) is LOW.An active LOW write enable (WE ) controls the writing/reading operation of the memory. When the chip select one (CS 1) and the write enable (WE ) are LOW and the chip select two (CS 2) is HIGH, the information on data inputs (D 0 through D 3) is written into the addressed memory word and preconditions the output circuitry so that true data is present at the outputs when the write cycle is complete.This preconditioning operation insures minimum writeFUNCTIONAL DESCRIPTIONTRUTH TABLEAC ELECTRICAL CHARACTERISTICS—READ CYCLE(V CC = 5V ± 10% except as noted, All Temperature Ranges)(2)TIMING WAVEFORM OF READ CYCLENotes:H = HIGH L = LowX= Don't CareHIGH Z= Implies outputs are disabled or off. This condition is defined as high impedance state for the P4C422.Sym.t RC t ACS t ZRCS t AOS t ZROS t AARead Cycle Time (5)Chip Select Time (5)Chip Select to High-Z (6)Output Enable Time Output Enable to High-Z (6)Address Access Time (5)-10*Min Max 7.587.5810-12Min 12Max 81081012-15Min 15Max 81281215-20Min 20Max 1215121520-25Min 25Max 15201520-35Min 35MaxUnit ns ns ns ns ns ns25*V CC = 5V ± 5%2530253035Parameter12P4C422Max AC CHARACTERISTICS—WRITE CYCLE(V CC = 5V ± 10% except as noted, All Temperature Ranges)(2)TIMING WAVEFORM OF WRITE CYCLEParameterWrite Cycle Time (5)Write Enable to High-Z (6)Write Recovery Time Write Pulse Width (5,7)Data Setup Time Prior to Write (5)Data Hold Time (5)Address Setup Time (5,7)Address Hold Time (5)Chip Select Setup Time (5)Chip Select Hold Time (5)Sym.t WC t ZWS t WR t W t WSD t WHD t WSA t WHA t WSCS t WHCS-10*-12-15-20-25-35Unit Min Max Min Max Min Max Min Min Max Min Max1080288129010101511021212201321515251552020352053025ns ns ns ns ns *V CC = 5V ± 5%22555ns 000255ns 224555ns 000255ns 22555ns元器件交易网P4C422Figure 1c Figure 1dFigure 1a Figure 1bAC TEST LOADS & WAVEFORMSP4C422*Military temperature range with MIL-STD-883, Class B compliance.N/A = Not AvailableSELECTION GUIDEThe P4C422 is available in the following temperature range, speed, and package options.ORDERING INFORMATION101215202535Plastic DIP -10PC -12PC -15PC -20PC -25PC -35PC SOIC-10SC -12SC -15SC -20SC -25SC -35SC Side Brazed DIP N/A N/A -15CM -20CM -25CM -35CM CERDIP N/A N/A -15DM -20DM -25DM -35DM LCC N/A N/A -15LM -20LM -25LM -35LM CERPACK N/A N/A -15FM -20FM -25FM -35FM Side Brazed DIPN/A N/A -15CMB -20CMB -25CMB -35CMB CERDIP N/A N/A -15DMB -20DMB -25DMB -35DMB LCC N/A N/A -15LMB -20LMB -25LMB -35LMB CERPACKN/AN/A-15FMB-20FMB-25FMB-35FMBMilitaryTemperatureMilitary Processed*Speed (ns)Temperature Range Package Commercial TemperatureP4C422P4C422SQUARE LEADLESS CHIP CARRIERCERPACK CERAMIC FLAT PACKAGEPkg ## Pins Symbol Min Max A 0.0600.090b 0.0150.022c 0.0040.009D -0.630E 0.3300.380e k 0.0080.015L 0.2500.370Q 0.0260.045S -0.085S10.005-F3240.050 BSC Pkg ## Pins Symbol Min Max A 0.0600.075A10.0500.065B10.0220.028D/E 0.3950.410D1/E1D2/E2D3/E3-0.410e h j L 0.0450.055L10.0450.055L20.0750.095ND NE0.050 BSC 60.040 REF 0.020 REF 6L4240.250 BSC 0.125 BSCP4C422PLASTIC DUAL IN-LINE PACK-AGEP4C422REVISIONSDOCUMENT NUMBER:SRAM101DOCUMENT TITLE:P4C422 HIGH SPEED 256 x 4 Static CMOS RAMREV.ISSUEDATEORIG. OFCHANGEDESCRIPTION OF CHANGEOR1997DAB New Data SheetA Oct-05JDB Change logo to Pyramid 元器件交易网。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

P4C422

FEATURES

High Speed (Equal Access and Cycle Times)– 10/12/15/20/25/35 ns (Commercial)

– 15/20/25 /35 ns (Military)

CMOS for Low Power

– 495 mW Max. – 10/12/15/20/25 (Commercial)– 495 mW Max. – 15/20/25/35 (Military)

DESCRIPTION

The P4C422 is a 1,024-bit high-speed (10ns) Static RAM with a 256 x 4 organization. The memory requires no clocks or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL compatible.Operation is from a single 5 Volt supply. Easy memory expansion is provided by an active LOW chip select one (CS 1) and active HIGH chip select two (CS 2) as well as 3-state outputs.

P4C422

ULTRA HIGH SPEED 256 x 4STATIC CMOS RAM

Means Quality, Service and Speed

1Q97

P4C422

minimum write recovery times by eliminating the “write recovery glitch.” Reading is performed with chip selct one (CS 1) LOW, chip select two (CS 2) HIGH, write enable (WE ) HIGH and output enable (OE ) LOW. The informa-tion stored in the addressed word is read out on the noninverting outputs (O 0 through O 3). The outputs of the memory go to an inactive high impedance state whenever chip select one (CS 1) is HIGH, or during the write operation when write enable (WE ) is LOW.

An active LOW write enable (WE ) controls the writing/reading operation of the memory. When the chip select one (CS 1) and the write enable (WE ) are LOW and the chip select two (CS 2) is HIGH, the information on data inputs (D 0 through D 3) is written into the addressed memory word and preconditions the output circuitry so that true data is present at the outputs when the write cycle is complete. This preconditioning operation insures

FUNCTIONAL DESCRIPTION

TRUTH TABLE

AC ELECTRICAL CHARACTERISTICS—READ CYCLE

(V CC = 5V ± 10% except as noted, All Temperature Ranges)(2)

Mode CS 2CS 1WE OE Output Standby L X X X High Z Standby X H X X High Z D OUT Disabled H L X H High Z Read H L H L D OUT Write

H

L

L

X

High Z

TIMING WAVEFORM OF READ CYCLE

Notes:

H = HIGH L = Low

X = Don't Care

HIGH Z = Implies outputs are disabled or off. This

condition is defined as high impedance state for the P4C422.

Sym.t RC t ACS t ZRCS t AOS t ZROS t AA

Read Cycle Time (5)Chip Select Time (5)Chip Select to High-Z (6)Output Enable Time Output Enable to High-Z (6)Address Access Time (5)

-10*Min Max 7.587.5810

-12Min 12

Max 81081012

-15Min 15

Max 81281215

-20Min 20

Max 1215121520

-25Min 25

Max 15201520-35

Min 35

Max

Unit ns ns ns ns ns ns

25

*V CC = 5V ± 5%

2530253035

Parameter

12

P4C422

AC TEST LOADS & WAVEFORMS

Figure 1a Figure 1b

Figure 1c Figure 1d

P4C422。