MCOM中文资料

DS91M040TSQ中文资料

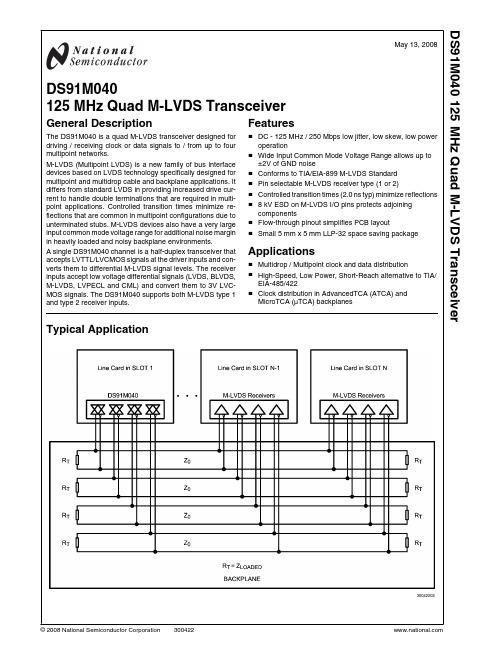

May 13, 2008 DS91M040125 MHz Quad M-LVDS TransceiverGeneral DescriptionThe DS91M040 is a quad M-LVDS transceiver designed for driving / receiving clock or data signals to / from up to four multipoint networks.M-LVDS (Multipoint LVDS) is a new family of bus interface devices based on LVDS technology specifically designed for multipoint and multidrop cable and backplane applications. It differs from standard LVDS in providing increased drive cur-rent to handle double terminations that are required in multi-point applications. Controlled transition times minimize re-flections that are common in multipoint configurations due to unterminated stubs. M-LVDS devices also have a very large input common mode voltage range for additional noise margin in heavily loaded and noisy backplane environments.A single DS91M040 channel is a half-duplex transceiver that accepts LVTTL/LVCMOS signals at the driver inputs and con-verts them to differential M-LVDS signal levels. The receiver inputs accept low voltage differential signals (LVDS, BLVDS, M-LVDS, LVPECL and CML) and convert them to 3V LVC-MOS signals. The DS91M040 supports both M-LVDS type 1 and type 2 receiver inputs.Features■DC - 125 MHz / 250 Mbps low jitter, low skew, low power operation■Wide Input Common Mode Voltage Range allows up to ±2V of GND noise■Conforms to TIA/EIA-899 M-LVDS Standard■Pin selectable M-LVDS receiver type (1 or 2)■Controlled transition times (2.0 ns typ) minimize reflections ■8 kV ESD on M-LVDS I/O pins protects adjoining components■Flow-through pinout simplifies PCB layout■Small 5 mm x 5 mm LLP-32 space saving package Applications■Multidrop / Multipoint clock and data distribution■High-Speed, Low Power, Short-Reach alternative to TIA/ EIA-485/422■Clock distribution in AdvancedTCA (ATCA) and MicroTCA (μTCA) backplanesTypical Application30042202© 2008 National Semiconductor DS91M040 125 MHz Quad M-LVDS TransceiverOrdering InformationOrder Number Receiver Input FunctionPackage TypeDS91M040TSQType 1 or 2Quad M-LVDS TranscieverLLP-32Connection Diagram30042201Logic Diagram30042203 2D S 91M 040Pin DescriptionsNumber Name I/O, Type Description1, 3, 5, 7RO O, LVCMOS Receiver output pin.26, 28, 13, 15RE I, LVCMOS Receiver enable pin: When RE is high, the receiver is disabled.When RE is low, the receiver is enabled. There is a 300 kΩ pullupresistor on this pin.25, 27, 14, 16DE I, LVCMOS Driver enable pin: When DE is low, the driver is disabled. WhenDE is high, the driver is enabled. There is a 300 kΩ pulldownresistor on this pin.2, 4, 6, 8DI I, LVCMOS Driver input pin.31, DAP GND Power Ground pin and pad.17, 19, 21, 23A I/O, M-LVDS Non-inverting driver output pin/Non-inverting receiver input pin 18, 20, 22, 24B I/O, M-LVDS Inverting driver output pin/Inverting receiver input pin11, 12, 29, 30VDDPower Power supply pin, +3.3V ± 0.3V32FSEN1I, LVCMOS Failsafe enable pin with a 300 kΩ pullup resistor. This pinenables Type 2 receiver on inputs 0 and 2.FSEN1 = L --> Type 1 receiver inputsFSEN1 = H --> Type 2 receiver inputs9FSEN2I, LVCMOS Failsafe enable pin with a 300 kΩ pullup resistor. This pinenables Type 2 receiver on inputs 1 and 3.FSEN2 = L --> Type 1 receiver inputsFSEN2 = H --> Type 2 receiver inputs10MDE I, LVCMOS Master enable pin. When MDE is H, the device is powered up.When MDE is L, the device overrides all other control and powersdown.M-LVDS Receiver TypesThe EIA/TIA-899 M-LVDS standard specifies two differenttypes of receiver input stages. A type 1 receiver has a con-ventional threshold that is centered at the midpoint of the inputamplitude, VID /2. A type 2 receiver has a built in offset that is100mV greater then VID /2. The type 2 receiver offset acts asa failsafe circuit where open or short circuits at the input willalways result in the output stage being driven to a low logicstate.30042240FIGURE 1. M-LVDS Receiver Input Thresholds DS91M040Absolute Maximum Ratings (Note 4)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Power Supply Voltage −0.3V to +4V LVCMOS Input Voltage −0.3V to (V DD + 0.3V)LVCMOS Output Voltage −0.3V to (V DD + 0.3V)M-LVDS I/O Voltage −5.5V to +5.5V M-LVDS Output Short Circuit Current Duration Continuous Junction Temperature +140°C Storage Temperature Range −65°C to +150°C Lead Temperature Range Soldering (4 sec.)+260°C Maximum Package Power Dissipation @ +25°C SQ Package 833 mW Derate SQ Package 6.67 mW/°C above +25°C Package Thermal Resistance θJA +150°C/W θJC +63.8°C/WESD Susceptibility HBM (Note 1)≥8 kV MM (Note 2)≥250V CDM (Note 3)≥1250VNote 1:Human Body Model, applicable std. JESD22-A114C Note 2:Machine Model, applicable std. JESD22-A115-A Note 3:Field Induced Charge Device Model, applicable std.JESD22-C101-CRecommended Operating ConditionsMin Typ Max Units Supply Voltage, V DD3.0 3.3 3.6V Voltage at Any Bus Terminal−1.4 +3.8V (Separate or Common-Mode)Differential Input Voltage V ID 2.4V LVTTL Input Voltage High V IH 2.0 V DD V LVTTL Input Voltage Low V IL 0 0.8V Operating Free Air Temperature T A −40+25+85°CDC Electrical Characteristics(Notes 5, 6, 7, 9)Over recommended operating supply and temperature ranges unless otherwise specified.Symbol ParameterConditionsMin Typ Max Units M-LVDS Driver |V AB |Differential output voltage magnitudeR L = 50Ω, C L = 5 pF 480 650mV ΔV AB Change in differential output voltage magnitude between logic statesFigures 2, 4−500+50mV V OS(SS)Steady-state common-mode output voltageR L = 50Ω, C L = 5 pF 0.3 1.6 2.1V |ΔV OS(SS)|Change in steady-state common-mode outputvoltage between logic states Figures 2, 30 +50mV V A(OC)Maximum steady-state open-circuit output voltage Figure 50 2.4V V B(OC)Maximum steady-state open-circuit output voltage0 2.4V V P(H)Voltage overshoot, low-to-high level output (Note 12)R L = 50Ω, C L = 5pF, C D = 0.5 pF Figures 7, 81.2V SSV V P(L)Voltage overshoot, high-to-low level output (Note 12)−0.2V SSV I IH High-level input current (LVTTL inputs)V IH = 2.0V -15 15μA I IL Low-level input current (LVTTL inputs)V IL = 0.8V -15 15μA V CL Input Clamp Voltage (LVTTL inputs)I IN = -18 mA -1.5 V I OS Differential short-circuit output current (Note 8)Figure 6-43 43mA M-LVDS ReceiverV IT+Positive-going differential input voltage threshold See Function Tables Type 1 1650mV Type 2 100150mV V IT−Negative-going differential input voltage threshold See Function Tables Type 1−5020 mV Type 25094 mV V OH High-level output voltage (LVTTL output)I OH = −8mA 2.4 2.7 V V OL Low-level output voltage (LVTTL output)I OL = 8mA 0.280.4V I OZ TRI-STATE output currentV O = 0V or 3.6V−10 10μA I OSRShort-circuit receiver output current (LVTTL output)V O = 0V-50-90mA 4D S 91M 040Symbol ParameterConditionsMin Typ Max Units M-LVDS Bus (Input and Output) PinsI ATransceiver input/output currentV A = 3.8V, V B = 1.2V 32µA V A = 0V or 2.4V, V B = 1.2V −20 +20µA V A = −1.4V, V B = 1.2V−32 µA I BTransceiver input/output currentV B = 3.8V, V A = 1.2V 32µA V B = 0V or 2.4V, V A = 1.2V −20 +20µA V B = −1.4V, V A = 1.2V−32 µA I AB Transceiver input/output differential current (I A − I B )V A = V B , −1.4V ≤ V ≤ 3.8V −4 +4µA I A(OFF)Transceiver input/output power-off currentV A = 3.8V, V B = 1.2V,DE = V CC = 1.5V32µA V A = 0V or 2.4V, V B = 1.2V,DE = V CC = 1.5V −20 +20µA V A = −1.4V, V B = 1.2V,DE = V CC = 1.5V−32 µA I B(OFF)Transceiver input/output power-off currentV B = 3.8V, V A = 1.2V,DE = V CC = 1.5V32µA V B = 0V or 2.4V, V A = 1.2V,DE = V CC = 1.5V −20 +20µA V B = −1.4V, V A = 1.2V,DE = V CC = 1.5V−32 µA I AB(OFF)Transceiver input/output power-off differential current (I A(OFF) − I B(OFF))V A = V B , −1.4V ≤ V ≤ 3.8V,V DD = 1.5V, DE = 1.5V −4 +4µA C A Transceiver input/output capacitance V DD = OPEN7.8 pF C B Transceiver input/output capacitance7.8 pF C AB Transceiver input/output differential capacitance 3 pF C A/BTransceiver input/output capacitance balance (C A /C B )1SUPPLY CURRENT (V CC )I CCD Driver Supply Current R L = 50Ω, DE = H, RE = H 6775mA I CCZ TRI-STATE Supply Current DE = L, RE = H 2226mA I CCR Receiver Supply Current DE = L, RE = L 3238mA I CCPDPower Down Supply CurrentMDE = L35mANote 4:“Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.Note 5:The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.Note 6:Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V OD and ΔV OD .Note 7:Typical values represent most likely parametric norms for V DD = +3.3V and T A = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.Note 8:Output short circuit current (I OS ) is specified as magnitude only, minus sign indicates direction only.Note 9:C L includes fixture capacitance and C D includes probe capacitance.DS91M040Switching Characteristics(Notes 10, 11, 17)Over recommended operating supply and temperature ranges unless otherwise specified.SymbolParameterConditionsMin Typ Max Units DRIVER AC SPECIFICATIONS t PLH Differential Propagation Delay Low to High R L = 50Ω, C L = 5 pF, 1.5 3.3 5.5ns t PHL Differential Propagation Delay High to Low C D = 0.5 pF 1.5 3.3 5.5ns t SKD1Pulse Skew (Notes 12, 13)Figures 7, 8 30125ps t SKD2Channel-to-Channel Skew (Notes 12, 14) 100200ps t SKD3Part-to-Part Skew (Notes 12, 15) 0.8 1.6ns t SKD4Part-to-Part Skew (Notes 12, 16) 4ns t TLH Rise Time (Note 12)1.22.03.0ns t THL Fall Time (Note 12)1.22.03.0ns t PZH Enable Time (Z to Active High)R L = 50Ω, C L = 5 pF, 7.511.5ns t PZL Enable Time (Z to Active Low )C D = 0.5 pF 8.011.5ns t PLZ Disable Time (Active Low to Z)Figures 9, 10 7.011.5ns t PHZ Disable Time (Active High to Z)7.011.5ns RECEIVER AC SPECIFICATIONSt PLH Propagation Delay Low to High C L = 15 pF 1.5 3.0 4.5ns t PHL Propagation Delay High to Low Figures 11, 12, 13 1.5 3.1 4.5ns t SKD1A Pulse Skew (Receiver Type 1)(Notes 12, 13)55325ps t SKD1B Pulse Skew (Receiver Type 2)(Notes 12, 13)475800ps t SKD2Channel-to-Channel Skew (Notes 12, 14) 60300ps t SKD3Part-to-Part Skew (Notes 12, 15) 0.6 1.2ns t SKD4Part-to-Part Skew (Notes 12, 16) 3ns t TLH Rise Time (Note 12) 0.3 1.1 1.6ns t THL Fall Time (Note 12)0.30.65 1.6ns t PZH Enable Time (Z to Active High)R L = 500Ω, C L = 15 pF 3 5.5ns t PZL Enable Time (Z to Active Low)Figures 14, 15 3 5.5ns t PLZ Disable Time (Active Low to Z) 3.5 5.5ns t PHZ Disable Time (Active High to Z) 3.5 5.5ns GENERIC AC SPECIFICATIONSt WKUP Wake Up Time (Note 12)(Master Device Enable (MDE) time) 500ms f MAXMaximum Operating Frequency (Note 12)125MHzNote 10:The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.Note 11:Typical values represent most likely parametric norms for V DD = +3.3V and T A = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.Note 12:Specification is guaranteed by characterization and is not tested in production.Note 13:t SKD1, |t PLHD − t PHLD |, Pulse Skew, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.Note 14:t SKD2, Channel-to-Channel Skew, is the difference in propagation delay (t PLHD or t PHLD ) among all output channels.Note 15:t SKD3, Part-to-Part Skew, is defined as the difference between the minimum and maximum differential propagation delays. This specification applies to devices at the same V DD and within 5°C of each other within the operating temperature range.Note 16:t SKD4, Part-to-Part Skew, is the differential channel-to-channel skew of any event between devices. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution. t SKD4 is defined as |Max − Min| differential propagation delay.Note 17:C L includes fixture capacitance and C D includes probe capacitance.Note 18:Measured on a clock edge with a histogram and an acummulation of 1500 histogram hits. Input stimulus jitter is subracted geometrically. 6D S 91M 040Test Circuits and Waveforms30042214FIGURE 2. Differential Driver Test Circuit30042224FIGURE 3. Differential Driver Waveforms30042222FIGURE 4. Differential Driver Full Load Test Circuit30042212FIGURE 5. Differential Driver DC Open Test CircuitDS91M04030042225FIGURE 6. Differential Driver Short-Circuit Test Circuit30042216FIGURE 7. Driver Propagation Delay and Transition Time Test Circuit30042218FIGURE 8. Driver Propagation Delays and Transition Time Waveforms 8D S 91M 04030042219FIGURE 9. Driver TRI-STATE Delay Test Circuit30042221FIGURE 10. Driver TRI-STATE Delay Waveforms30042215FIGURE 11. Receiver Propagation Delay and Transition Time Test Circuit DS91M04030042217FIGURE 12. Type 1 Receiver Propagation Delay and Transition Time Waveforms30042223FIGURE 13. Type 2 Receiver Propagation Delay and Transition Time Waveforms30042213FIGURE 14. Receiver TRI-STATE Delay Test Circuit 10D S 91M 040DS91M04030042220FIGURE 15. Receiver TRI-STATE Delay WaveformsTruth TablesDS91M040 Transmitting InputsOutputsRE DE DI B A X H H L H X H L H L XLXZZX — Don't care condition Z — High impedance stateDS91M040 as Type 1 ReceivingInputsOutput FSEN RE DE A − BRO L L L ≥ +0.05V H L L L ≤ −0.05VL L L L 0V X LHLXZX — Don't care condition Z — High impedance state DS91M040 as Type 2 ReceivingInputs Output FSEN RE DE A − BR H L L ≥ +0.15V H H L L ≤ +0.05VL H L L 0V L HHLXZX — Don't care condition Z — High impedance stateDS91M040 Type 1 Receiver Input Threshold Test VoltagesApplied Voltages Resulting Differential InputVoltageResulting Common-ModeInput VoltageReceiver OutputV IA V IB V ID V ICM R 2.400V 0.000V 2.400V 1.200V H 0.000V 2.400V −2.400V 1.200V L 3.800V 3.750V 0.050V 3.775V H 3.750V 3.800V −0.050V 3.775V L −1.350V −1.400V 0.050V −1.375V H −1.400V−1.350V−0.050V−1.375VLH — High Level L — Low LevelOutput state assumes that the receiver is enabled (RE = L)DS91M040 Type 2 Receiver Input Threshold Test VoltagesApplied Voltages Resulting Differential InputVoltageResulting Common-ModeInput VoltageReceiver OutputV IA V IB V ID V IC R 2.400V 0.000V 2.400V 1.200V H 0.000V 2.400V −2.400V 1.200V L 3.800V 3.650V 0.150V 3.725V H 3.800V 3.750V 0.050V 3.775V L −1.250V −1.400V 0.150V −1.325V H −1.350V−1.400V0.050V−1.375VLH — High Level L — Low LevelOutput state assumes that the receiver is enabled (RE = L) 12D S 91M 040Typical Performance30042250 Driver Rise Time as a Function of Temperature30042251 Driver Fall Time as a Function of Temperature30042258 Driver Output Signal Amplitude as a Function ofResistive Load30042252Driver Propagation Delay (tPLHD) as a Function ofTemperature30042253Driver Propagation Delay (tPHLD) as a Function ofTemperatureDS91M04030042254Driver Power Supply Current as a Function of Frequency30042255Receiver Power Supply Current as a Function ofFrequency30042256Receiver Propagation Delay (tPLHD) as a Function ofInput Common Mode Voltage30042257Receiver Propagation Delay (tPHLD) as a Function ofInput Common Mode Voltage 14D S 91M 040Physical Dimensions inches (millimeters) unless otherwise notedOrder Number DS91M040TSQSee NS package Number SQA32A(See AN-1187 for PCB Design and Assembly Recommendations) DS91M040NotesD S 91M 040 125 M H z Q u a d M -L V D S T r a n s c e i v e rFor more National Semiconductor product information and proven design tools, visit the following Web sites at:ProductsDesign SupportAmplifiers /amplifiers WEBENCH /webench Audio/audio Analog University /AU Clock Conditioners /timing App Notes /appnotes Data Converters /adc Distributors /contacts Displays /displays Green Compliance /quality/green Ethernet /ethernet Packaging/packaging Interface /interface Quality and Reliability /quality LVDS/lvds Reference Designs /refdesigns Power Management /power Feedback /feedback Switching Regulators /switchers LDOs /ldo LED Lighting /led PowerWise/powerwise Serial Digital Interface (SDI)/sdiTemperature Sensors /tempsensors Wireless (PLL/VCO)/wirelessTHE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION (“NATIONAL”) PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS,IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL’S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.EXCEPT AS PROVIDED IN NATIONAL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.LIFE SUPPORT POLICYNATIO NAL’S PRO DUCTS ARE NO T AUTHO RIZED FO R USE AS CRITICAL CO MPO NENTS IN LIFE SUPPO RT DEVICES O R SYSTEMS WITHO UT THE EXPRESS PRIO R WRITTEN APPRO VAL O F THE CHIEF EXECUTIVE O FFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.Copyright© 2008 National Semiconductor CorporationFor the most current product information visit us at National Semiconductor Americas Technical Support CenterEmail: support@ Tel: 1-800-272-9959National Semiconductor Europe Technical Support CenterEmail: europe.support@ German Tel: +49 (0) 180 5010 771English Tel: +44 (0) 870 850 4288National Semiconductor Asia Pacific Technical Support Center Email: ap.support@National Semiconductor Japan Technical Support Center Email: jpn.feedback@。

LF398M中文资料

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

LF398/LF398A

0˚C to +70˚C

Storage Temperature Range

−65˚C to +150˚C

Input Voltage

Equal to Supply Voltage

Logic To Logic Reference

Differential Voltage (Note 3)

Electrical Characteristics

The following specifcations apply for −VS + 3.5V ≤ VIN ≤ +VS − 3.5V, +VS = +15V, −VS = −15V, TA = Tj = 25˚C, Ch = 0.01 µF, RL = 10 kΩ, LOGIC REFERENCE = 0V, LOGIC HIGH = 2.5V, LOGIC LOW = 0V unless otherwise specified.

0.5

2

4

0.5

4

Ω

6

Ω

“HOLD” Step, (Note 6) Supply Current, (Note 5) Logic and Logic Reference Input Current

Tj = 25˚C, Ch = 0.01 µF, VOUT = 0 Tj≥25˚C Tj = 25˚C

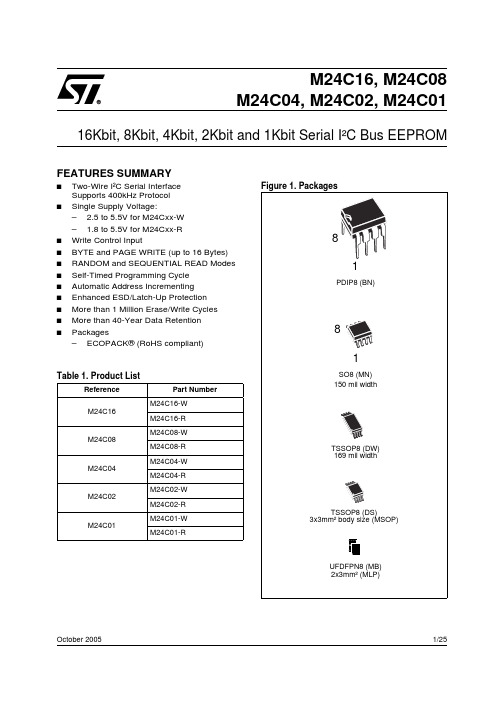

UPC4574G2-E1中文资料

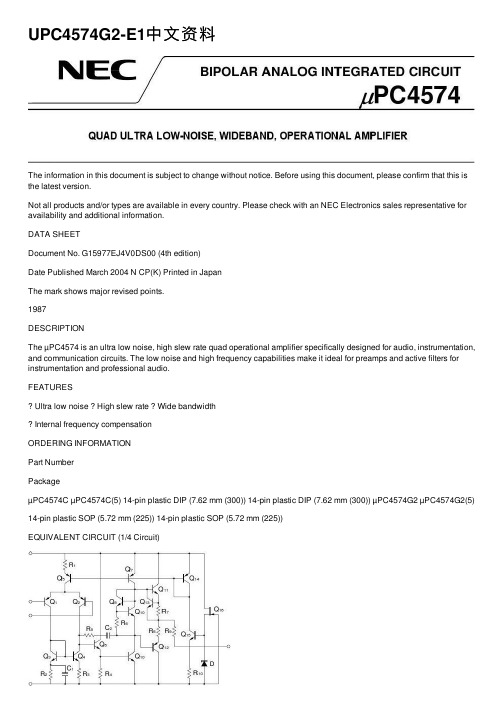

UPC4574G2-E1中⽂资料The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.DATA SHEETDocument No. G15977EJ4V0DS00 (4th edition)Date Published March 2004 N CP(K) Printed in JapanThe mark shows major revised points.1987DESCRIPTIONThe µPC4574 is an ultra low noise, high slew rate quad operational amplifier specifically designed for audio, instrumentation, and communication circuits. The low noise and high frequency capabilities make it ideal for preamps and active filters for instrumentation and professional audio.FEATURESUltra low noise High slew rate Wide bandwidthInternal frequency compensationORDERING INFORMATIONPart NumberPackageµPC4574C µPC4574C(5) 14-pin plastic DIP (7.62 mm (300)) 14-pin plastic DIP (7.62 mm (300)) µPC4574G2 µPC4574G2(5) 14-pin plastic SOP (5.72 mm (225)) 14-pin plastic SOP (5.72 mm (225))EQUIVALENT CIRCUIT (1/4 Circuit)I I I NVVPIN CONFIGURATION (Top View)OUT 4I I4I N4V ?I N3I I3OUT 3OUT 1I I1I N1V +I N2I I2OUT 2PC4574C, 4574C(5), 4574G2, 4574G2(5)µData Sheet G15977EJ4V0DS2ABSOLUTE MAXIMUM RATINGS (T A = 25°C)Parameter SymbolRatings Unit Voltage between V +and V ? Note1V +V0.3 to +36VDifferential Input Voltage V ID ±30 V Input VoltageNote2V IV ??0.3 to V ++0.3 V Output VoltageNote3V OV ??0.3 to V + +0.3VC Package Note4570 mW Power Dissipation G2 PackageNote5P T 550 mW Output Short Circuit DurationNote610 sec Operating Ambient Temperature T A ?20 to +80 °C Storage TemperatureT stg55 to +125°CNotes 1. Reverse connection of supply voltage can cause destruction.2. The input voltage should be allowed to input without damage or destruction. Even during the transition periodof supply voltage, power on/off etc., this specification should be kept. The normal operation will establish when the both inputs are within the Common Mode Input Voltage Range of electrical characteristics.3. This specification is the voltage which should be allowed to supply to the output terminal from externalwithout damage or destructive. Even during the transition period of supply voltage, power on/off etc., this specification should be kept. The output voltage of normal operation will be the Output Voltage Swing of electrical characteristics.4. Thermal derating factor is –7.6 mW/°C when ambient temperature is higher than 50°C.5. Thermal derating factor is –5.5 mW/°C when ambient temperature is higher than 25°C.6. Pay careful attention to the total power dissipation not to exceed the absolute maximum ratings, Note 4 andNote 5.RECOMMENDED OPERATING CONDITIONSParameter Symbol MIN. TYP. MAX. UnitSupply Voltage V ± ±4 ±16 V Output Current I O±10 mASource Resistance R S 50k ?Capacitive Load (A V = +1)C L 100 pFµPC4574C, µPC4574G2±Notes 7. Input bias currents flow out from IC. Because each currents are base current of PNP-transistor on input stage.8.This current flows irrespective of the existence of use.Data Sheet G15977EJ4V0DS 3µPC4574C(5), µPC4574G2(5)±Notes 7. Input bias currents flow out from IC. Because each currents are base current of PNP-transistor on input stage.8.This current flows irrespective of the existence of use.4Data Sheet G15977EJ4V0DSMEASUREMENT CIRCUITFig.1 Total Harmonic Distortion Measurement CircuitnFig.3 Flat Noise Measurement Circuit (FLAT+JIS A)V O = 40 dB x V n100 V n =V O40 dBData Sheet G15977EJ4V0DS 5Data Sheet G15977EJ4V0DS6TYPICAL PERFORMANCE CHARACTERISTICS (T A = 25°C, TYP.) T A - Operating Ambient Temperature - ?CPOWER DISSIPATIONP T - T o t a l P o w e r D i s s i p a t i o n - m W800600400200020*********20406080100120110010 k 1 M 1 k 10100 k 10 Mf - Frequency - HzOPEN LOOP FREQUENCY RESPONSEA V - O p e n L o o p V o l t a g e G a i n - d BV ± = ±15 V202040608021.510.50?0.5?1?1.5?2T A - Operating Ambient Temperature - ?CINPUT OFFSET VOLTAGEV I O - I n p u t O f f s e t V o l t a g e - m V= ±15 VV ±each 5 samples data806040200?20550530510490470450T A - Operating Ambient Temperature - ?CINPUT BIAS CURRENTI B - I n p u t B i a s C u r r e n t - n A= ±15 VV ±f - Frequency - HzLARGE SIGNAL FREQUENCY RESPONSE V o m - O u t p u t V o l t a g e S w i n g - V p -p 01020301001 k 10 k 100 k 1 M 10 MV = ±15 V±R L = 10 k ?I O - Output Current - mAOUTPUT CURRENT LIMITV O - O u t p u t V o l t a g e - V±±5±10±15T A - Operating Ambient Temperature - ?CSUPPLY CURRENTI C C - S u p p l y C u r r e n t - m A12963204020060800V = ±15 V±SUPPLY CURRENTI C C - S u p p l y C u r r e n t - m A12963±10±20V - Supply Voltage - V±Data Sheet G15977EJ4V0DS7COMMON MODE INPUT VOLTAGE RANGE V I C M - C o m m o n M o d e I n p u t V o l t a g e R a n g e - V 20100±10±20V - Supply Voltage - V±VOLTAGE FOLLOWER PULSE RESPONSE V O - O u t p u t V o l t a g e - V10551002468t - Time - sµV = ±15 V ±A V = 1R L = 2 k ?INPUT NOISE VOLTAGE (FLAT + JIS A)V n - I n p u t N o i s e V o l t a g e - V r .m .s .1001010.1101001 k10 k100 kR S - Source Resistance - ?V = ±15 V±µf - Frequency - HzINPUT EQUIVALENT NOISE VOLTAGE DENSITY e n - I n p u t E q u i v a l e n t N o i s e V o l t a g e D e n s i t y - n V / H z20468100 1 k10 k 100 k10±R S = 100 VTOTAL HARMONIC DISTORTIONT H D - T o t a l H a r m o n i c D i s t o r t i o n - %10.0010.010.10.000110100 1 k10 k 100 kf - Frequency - HzV = ±15 V ±V O = 3 V r.m.s.A V = 1R L = 2 k ?Data Sheet G15977EJ4V0DS8PACKAGE DRAWINGS (Unit: mm)14-PIN PLASTIC DIP (7.62 mm (300))ITEM MILLIMETERS A 19.22±0.22.14 MAX.F I J D 1.32±0.12G 3.6±0.3C B 2.54 (T.P.)0.50±0.10R 0~15°H 0.51 MIN.K 7.62 (T.P.)L 6.4±0.23.554.3±0.2N 0.25NOTES1. Each lead centerline is located within 0.25 mm ofits true position (T.P.) at maximum material condition.2. ltem "K" to center of leads when formed parallel.P14C-100-300B1-3M 0.25+0.10?0.05Data Sheet G15977EJ4V0DS9ITEM B C I 14-PIN PLASTIC SOP (5.72 mm (225))D E G H J PMILLIMETERS 1.27 (T.P.)1.42 MAX.A 10.2±0.264.4±0.10.1±0.10.426.5±0.21.49+0.08?0.071.1±0.163°+7°?3°NOTEEach lead centerline is located within 0.1 mm ofits true position (T.P.) at maximum material condition.F 1.59+0.21?0.2K L M N 0.6±0.20.170.10.10+0.08?0.07S14GM-50-225B, C-6RECOMMENDED SOLDERING CONDITIONSThe µPC4574 should be soldered and mounted under the following recommended conditions.For soldering methods and conditions other than those recommended below, contact an NEC Electronics sales representative.For technical information, see the following website.Semiconductor Device Mount Manual (/doc/015a7dda76a20029bd642de6.html/pkg/en/mount/index.html)Type of Surface Mount DeviceµPC4574G2, 4574G2(5): 14-pin plastic SOP (5.72 mm (225))Process ConditionsSymbol Infrared Ray Reflow Peak temperature: 230°C or below (Package surface temperature),Reflow time: 30 seconds or less (at 210°C or higher),Maximum number of reflow processes: 1 time.IR30-00-1Vapor Phase Soldering Peak temperature: 215°C or below (Package surface temperature),Reflow time: 40 seconds or less (at 200°C or higher),Maximum number of reflow processes: 1 time.VP15-00-1Wave Soldering Solder temperature: 260°C or below, Flow time: 10 seconds or less,Maximum number of flow processes: 1 time,Pre-heating temperature: 120°C or below (Package surface temperature).WS60-00-1Partial Heating Method Pin temperature: 300°C or below,Heat time: 3 seconds or less (Per each side of the device).–Caution Apply only one kind of soldering condition to a device, except for "partial heating method", or thedevice will be damaged by heat stress.Type of Through-hole DeviceµPC4574C, 4574C(5): 14-pin plastic DIP (7.62 mm (300))Process ConditionsWave Soldering (only to leads) Solder temperature: 260°C or below, Flow time: 10 seconds or less.Partial Heating Method Pin temperature: 300°C or below,Heat time: 3 seconds or less (per each lead).Caution For through-hole device, the wave soldering process must be applied only to leads, and make sure that the package body does not get jet soldered.Data Sheet G15977EJ4V0DS10The information in this document is current as of March, 2004. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of N EC Electronics products. N ot all products and/or types are available in every country. Please check with an N EC Electronics sales representative for availability and additional information.No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application."Standard":Computers, office equipment, communications equipment, test and measurement equipment, audioand visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots. "Special":Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support). "Specific":Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems and medical equipment for life support, etc.The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.(Note)(1)"NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes itsmajority-owned subsidiaries.(2)"NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (asdefined above).M8E 02. 11-1。

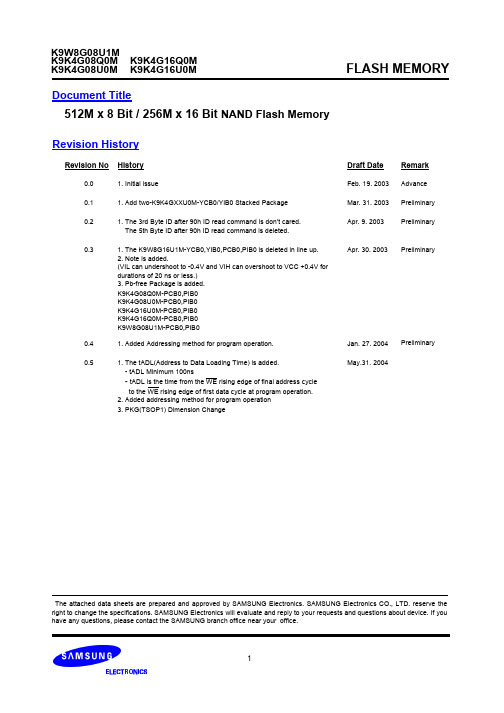

M12L64164A资料

ESMT

SDRAM

M12L64164A

1M x 16 Bit x 4 Banks

Synchronous DRAM

FEATURES

JEDEC standard 3.3V power supply LVTTL compatible with multiplexed address Four banks operation MRS cycle with address key programs - CAS Latency (2 & 3) - Burst Length (1, 2, 4, 8 & full page) - Burst Type (Sequential & Interleave) All inputs are sampled at the positive going edge of the system clock DQM for masking Auto & self refresh 15.6 μ s refresh interval

Write Enable Data Input / Output Mask Data Input / Output Power Supply / Ground Data Output Power / Ground No Connection

INPUT FUNCTION

Active on the positive going edge to sample all inputs Disables or enables device operation by masking or enabling all inputs except CLK , CKE and L(U)DQM Masks system clock to freeze operation from the next clock cycle. CKE should be enabled at least one cycle prior new command. Disable input buffers for power down in standby.

2KBP08M中文资料

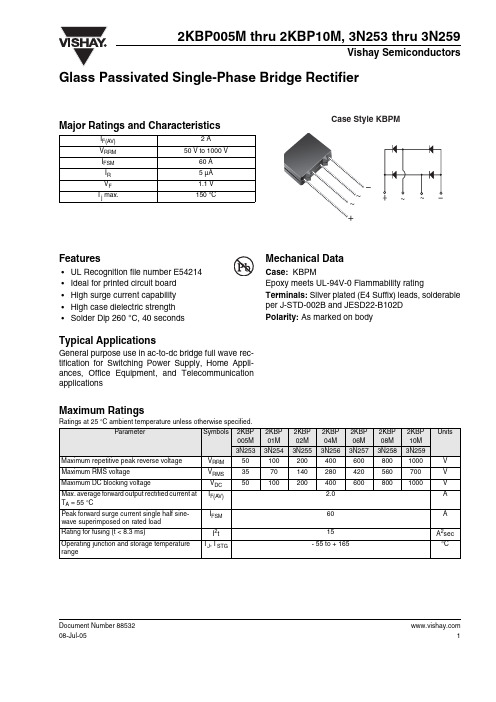

2KBP005M thru 2KBP10M, 3N253 thru 3N259Document Number 8853208-Jul-05Vishay Semiconductors1Glass Passivated Single-Phase Bridge RectifierMajor Ratings and CharacteristicsI F(AV) 2 A V RRM 50 V to 1000 VI FSM 60 A I R 5 µA V F 1.1 V T j max.150 °CFeatures•UL Recognition file number E54214 •Ideal for printed circuit board •High surge current capability •High case dielectric strength •Solder Dip 260 °C, 40 secondsTypical ApplicationsGeneral purpose use in ac-to-dc bridge full wave rec-tification for Switching Power Supply, Home Appli-ances, Office Equipment, and Telecommunication applicationsMechanical DataCase: KBPMEpoxy meets UL-94V-0 Flammability ratingTerminals: Silver plated (E4 Suffix) leads, solderable per J-STD-002B and JESD22-B102D Polarity: As marked on bodyMaximum RatingsRatings at 25 °C ambient temperature unless otherwise specified.ParameterSymbols 2KBP005M2KBP 01M 2KBP 02M 2KBP 04M 2KBP 06M 2KBP 08M 2KBP 10M Units3N2533N2543N2553N2563N2573N2583N259Maximum repetitive peak reverse voltage V RRM 50 100 200 400 600 8001000 V Maximum RMS voltage V RMS 35 70 140 280 420 560 700 V Maximum DC blocking voltageV DC 50 100 200 400 600 800 1000 VMax. average forward output rectified current at T A = 55 °CI F(AV) 2.0A Peak forward surge current single half sine-wave superimposed on rated load I FSM 60 A Rating for fusing (t < 8.3 ms)I 2t 15A 2sec Operating junction and storage temperature rangeT J , T STG- 55 to + 165°C2KBP005M thru 2KBP10M, 3N253 thru 3N259Vishay SemiconductorsElectrical CharacteristicsRatings at 25 °C ambient temperature unless otherwise specified.Thermal CharacteristicsRatings at 25 °C ambient temperature unless otherwise specified.ParameterT est conditionSymbols2KBP 005M 2KBP 01M 2KBP 02M 2KBP 04M 2KBP 06M 2KBP 08M 2KBP 10M Units3N2533N2543N2553N2563N2573N2583N259Maximum instantaneous forward voltage drop per legat 3.14 AV F 1.1V Maximum DC reversecurrent at rated DC blocking voltage per legT A = 25 °C T A = 125 °C I R 5.0500µATypical junction capacitance per legat 4.0 V , 1 MHz C J25pF2KBP005M thru 2KBP10M, 3N253 thru 3N259Document Number 8853208-Jul-05Vishay Semiconductors3Package outline dimensions in inches (millimeters)Figure 4. Typical Reverse Leakage Characteristics Per Leg。

RA30H4047M中文资料

MITSUBISHI RF MOSFET MODULERA30H4047M400-470MHz 30W 12.5V MOBILE RADIOELECTROSTATIC SENSITIVE DEVICEOBSERVE HANDLING PRECAUTIONSDESCRIPTIONThe RA30H4047M is a 30-watt RF MOSFET Amplifier Module for 12.5-volt mobile radios that operate in the 400- to 470-MHz range.The battery can be connected directly to the drain of the enhancement-mode MOSFET transistors. Without the gate voltage (V GG =0V), only a small leakage current flows into the drain and the RF input signal attenuates up to 60 dB. The output power and drain current increase as the gate voltage increases. With a gate voltage around 4V (minimum), output power and drain current increases substantially. The nominal output power becomes available at 4.5V (typical) and 5V (maximum). At V GG =5V, the typical gate current is 1 mA.This module is designed for non-linear FM modulation, but may also be used for linear modulation by setting the drain quiescent current with the gate voltage and controlling the output power with the input power.FEATURES• Enhancemen- Mode MOSFET Transistors (I DD ≅0 @ V DD =12.5V, V GG =0V)• P out >30W, ηT >40% @ V DD =12.5V, V GG =5V, P in =50mW • Broadband Frequency Range: 400-470MHz• Low-Power Control Current I GG =1mA (typ) at V GG =5V • Module Size: 66 x 21 x 9.88 mm• Linear operation is possible by setting the quiescent drain current with the gate voltage and controlling the output power with the input powerORDERING INFORMATION:ORDER NUMBER SUPPLY FORM RA30H4047M-E01RA30H4047M-01(Japan - packed without desiccator)Antistatic tray, 10 modules/tray1 RF Input (Pin )2 Gate Voltage (VGG ), Power Control3 Drain Voltage (V DD ), Battery4 RF Output (P out )5 RF Ground (Case)SALES CONTACTJAPAN:Mitsubishi Electric Corporation Semiconductor Sales Promotion Department 2-2-3 Marunouchi, Chiyoda-kuTokyo, Japan 100Email: sod.sophp@hq.melco.co.jp Phone: +81-3-3218-4854Fax: +81-3-3218-4861GERMANY:Mitsubishi Electric Europe B.V. SemiconductorGothaer Strasse 8D-40880 Ratingen, Germany Email: @ Phone: +49-2102-486-0Fax: +49-2102-486-3670HONG KONG:Mitsubishi Electric Hong Kong Ltd. Semiconductor Division41/F. Manulife Tower, 169 Electric Road North Point, Hong KongEmail: scdinfo@ Phone: +852 2510-0555Fax: +852 2510-9822 FRANCE:Mitsubishi Electric Europe B.V. Semiconductor25 Boulevard des BouvetsF-92741 Nanterre Cedex, France Email: @ Phone: +33-1-55685-668Fax: +33-1-55685-739SINGAPORE:Mitsubishi Electric Asia PTE Ltd Semiconductor Division307 Alexandra Road#3-01/02 Mitsubishi Electric Building, Singapore 159943Email: semicon@ Phone: +65 64 732 308Fax: +65 64 738 984 ITALY:Mitsubishi Electric Europe B.V. SemiconductorCentro Direzionale Colleoni, Palazzo Perseo 2, Via ParacelsoI-20041 Agrate Brianza, Milano, Italy Email: @ Phone: +39-039-6053-10Fax: +39-039-6053-212TAIWAN:Mitsubishi Electric Taiwan Company, Ltd., Semiconductor Department9F, No. 88, Sec. 6Chung Shan N. RoadTaipei, Taiwan, R.O.C.Email: metwnssi@ Phone: +886-2-2836-5288Fax: +886-2-2833-9793 U.K.:Mitsubishi Electric Europe B.V. SemiconductorTravellers Lane, Hatfield Hertfordshire, AL10 8XB, England Email: @ Phone: +44-1707-278-900Fax: +44-1707-278-837U.S.A.:Mitsubishi Electric & Electronics USA, Inc. Electronic Device Group1050 East Arques AvenueSunnyvale, CA 94085Email: customerservice@ Phone: 408-730-5900Fax: 408-737-1129CANADA:Mitsubishi Electric Sales Canada, Inc. 4299 14th AvenueMarkham, Ontario, Canada L3R OJ2 Phone: 905-475-7728Fax: 905-475-1918AUSTRALIA:Mitsubishi Electric Australia, Semiconductor Division348 Victoria Road Rydalmere, NSW 2116 Sydney, AustraliaEmail: semis@ Phone: +61 2 9684-7210+61 2 9684 7212+61 2 9684 7214+61 3 9262 9898 Fax: +61 2 9684-7208+61 2 9684 7245元器件交易网。

MM74HC594中文资料

MM74HC594

2

元器件交易网

MM74HC594

Absolute Maximum Ratings(Note 1)

(Note 2)

Recommended Operation Conditions

Supply Voltage (VCC) DC Input Voltage (VIN) DC Output Voltage (VOUT) Clamp Diode Current (IIK, IOK) DC Output Current, per pin (IOUT) DC VCC or GND Current, per pin (ICC) Storage Temperature Range (TSTG) Power Dissipation (PD)

General Description

This high speed shift register utilizes advanced silicon-gate CMOS technology. This device possesses the high noise immunity and low power consumption of standard CMOS integrated circuits, as well as the ability to drive 15 LS-TTL loads.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating—plastic “N” package: −12 mW/°C from 65°C to 85°C.

MIL-PRF-19500中文资料

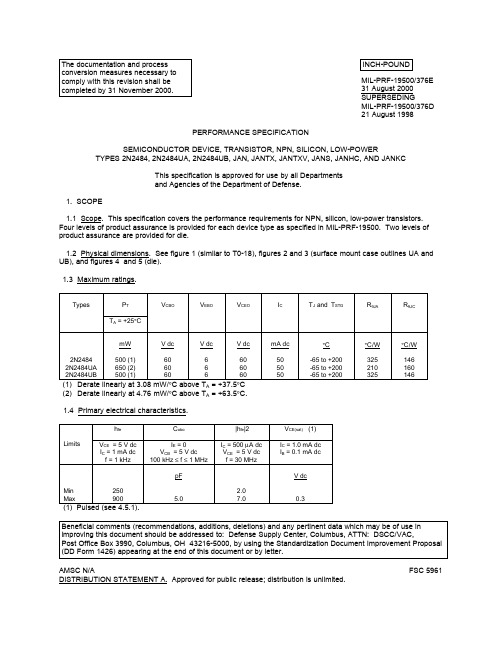

MIL-PRF-19500/376E 31 August 2000SUPERSEDINGMIL-PRF-19500/376D 21 August 1998PERFORMANCE SPECIFICATIONSEMICONDUCTOR DEVICE, TRANSISTOR, NPN, SILICON, LOW-POWERTYPES 2N2484, 2N2484UA, 2N2484UB, JAN, JANTX, JANTXV, JANS, JANHC, AND JANKCThis specification is approved for use by all Departments and Agencies of the Department of Defense.1. SCOPE1.1 Scope. This specification covers the performance requirements for NPN, silicon, low-power transistors. Four levels of product assurance is provided for each device type as specified in MIL-PRF-19500. Two levels of product assurance are provided for die.1.2 Physical dimensions. See figure 1 (similar to T0-18), figures 2 and 3 (surface mount case outlines UA and UB), and figures 4 and 5 (die).1.3 Maximum ratings.P TV CBOV EBOV CEOI CT J and T STGR θJAR θJCTypesT A = +25°CmWV dc V dc V dc mA dc °C °C/W °C/W 2N2484500 (1)6066050-65 to +2003251462N2484UA 650 (2)6066050-65 to +2002101602N2484UB500 (1)6066050-65 to +200325146(1)Derate linearly at 3.08 mW/°C above T A = +37.5°C (2)Derate linearly at 4.76 mW/°C above T A = +63.5°C. 1.4 Primary electrical characteristics.h feC obo|h fe |2V CE(sat) (1)LimitsV CE = 5 V dc I C = 1 mA dc f = 1 kHzI E = 0V CB = 5 V dc 100 kHz ≤ f ≤ 1 MHzI C = 500 µA dc V CE = 5 V dc f = 30 MHzI C = 1.0 mA dc I B = 0.1 mA dcMin Max250900pF5.02.07.0V dc 0.3(1) Pulsed (see 4.5.1).AMSC N/AFSC 5961DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.The documentation and process conversion measures necessary to comply with this revision shall be completed by 31 November 2000.INCH-POUND Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Defense Supply Center, Columbus, ATTN: DSCC/VAC,Post Office Box 3990, Columbus, OH 43216-5000, by using the Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.2Dimensions Symbol Inches Millimeters NoteMin Max Min Max CD .178.195 4.52 4.95CH .170.210 4.32 5.33HD .209.230 5.31 5.84LC .100 TP 2.54 TP 6LD .016.0210.410.537,8LL .500.75012.7019.057,8LU .016.0190.410.487,8L1---.050--- 1.277,8L2.250--- 6.35---7,8Q ---.040---0.865TL .028.0480.71 1.223,4TW .036.0460.91 1.173r ---.010---0.2510α45° TP 45° TP6NOTES:1.Dimension are in inches.2.Metric equivalents are given for general information only.3.Beyond r (radius) maximum, TW shall be held for a minimum length of .011 (0.28 mm).4.Dimension TL measured from maximum HD.5.Body contour optional within zone defined by HD, CD, and Q.6.Leads at gauge plane .054 +.001 -.000 inch (1.37 +0.03 -0.00 mm) below seating plane shallbe within .007 inch (0.18 mm) radius of true position (TP) at maximum material condition (MMC) relative to tab at MMC.7.Dimension LU applies between L 1 and L 2. Dimension LD applies between L 2 and LLminimum. Diameter is uncontrolled in L 1 and beyond LL minimum.8.All three leads.9.The collector shall be internally connected to the case.10.Dimension r (radius) applies to both inside corners of tab.11.In accordance with ANSI Y14.5M, diameters are equivalent to φx symbology.12.Lead 1 = emitter, lead 2 = base, lead 3 = collector.FIGURE 1. Physical dimensions (similar to TO-18).3DimensionsSymbol Inches Millimeters Note Min Max Min Max A .061.075 1.55 1.903A1.029.0410.74 1.04B1.022.0280.560.71B2.075 REF 1.91 REF B3.006.0220.150.565D .145.155 3.68 3.93D1.045.055 1.14 1.39D2.0375 BSC .952 BSC D3---.155--- 3.93E .215.225 5.46 5.71E3---.225--- 5.71L1.032.0480.81 1.22L2.072.088 1.83 2.23L3.003.0070.080.185NOTES:1.Dimensions are in inches.2.Metric equivalents are given for general information only.3.Dimension "A" controls the overall package thickness. When a window lid is used, dimension "A" mustincrease by a minimum of .010 inch (0.254 mm) and a maximum of .040 inch (1.020 mm).4.The corner shape (square, notch, radius, etc.) may vary at the manufacturer's option, from that shown onthe drawing.5.Dimensions "B3" minimum and "L3" minimum and the appropriately castellation length define anunobstructed three-dimensional space traversing all of the ceramic layers in which a castellation was designed. (Castellations are required on bottom two layers, optional on top ceramic layer.) Dimension "B3" maximum and "L3" maximum define the maximum width and depth of the castellation at any point on its surface. Measurement of these dimensions may be made prior to solder dipping.6.Lead 4 = no connection.FIGURE 2. Physical dimensions, surface mount (2N2484UA).4DimensionsInches Millimeters NotesLtrMin.Max.Min.Max.A .046.0560.97 1.42A1.017.0350.430.89B1.016 .024 0.41 0.61 3D .085 .108 2.41 2.74 D1 .071 .079 1.81 2.01 D2 .035 .039 0.89 0.99 D3E .115 .128 2.82 3.25 E3 L1.022.0380.560.964NOTES:1.Dimensions are in inches.2.Metric equivalents are given for general information only.3.Dimensions B2 and B3 are identical to B14.Dimension L2 is identical to L1.FIGURE 3. Physical dimensions, surface mount (2N2484UB).5A- versionNOTES:1.Die size...............................................0.015 x 0.019 inches ± 0.001 inch2.Die thickness.......................................0.010 ± 0.0015 inches3.Top metal............................................Aluminum 15,000Å minimum, 18,000Å nominal4.Back metal..........................................A.Gold 2,500Å minimum, 3,000Å nominalB.Eutectic Mount – No Gold5.Backside.............................................Collector6.Bonding pad........................................B = 0.003 inches, E = 0.004 inches diameter7.Passivation.........................................Si 3N 4 (Silicon Nitride) 2kÅ min, 2.2kÅ nom.FIGURE 4. Physical dimensions, JANHC and JANKC die, A - version.B - versionDie size:.....................................................0.018 x 0.018 inchesDie thickness:............................................0.008 ± 0.0016 inchesBase pad:..................................................0.0025 inches diameterEmitter pad:...............................................0.003 inches diameterBack metal:................................................Gold, 6500 ± 1950 ÅTop metal:.................................................Aluminum, 19500 ± 2500 ÅBack side:..................................................Collector Glassivation:..............................................SiO2, 7500 ± 1500 ÅFIGURE 5. Physical dimensions, JANHC and JANKC die, B - version.61.4 Primary electrical characteristics.NFI C = 10 µA dc, V CE = 5 V dcR g = 10 kΩh FE2h FE5f = 100 Hz f = 1000 Hz f = 10 kHz V CE = 5 V dcI C = 10 µA dc V CE = 5 V dc I C = 1 mA dcMin Max dB7.5dB3dB22005002508002. APPLICABLE DOCUMENTS2.1 General. The documents listed in this section are specified in sections 3 and 4 of this specification. This section does not include documents cited in other sections of this specification or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements documents cited in sections 3 and 4 of this specification, whether or not they are listed.2.2 Government documents.2.2.1 Specifications, standards, and handbooks. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation (see 6.2).SPECIFICATIONDEPARTMENT OF DEFENSEMIL-PRF-19500 - Semiconductor Devices, General Specification for.STANDARDDEPARTMENT OF DEFENSEMIL-STD-750 - Test Methods for Semiconductor Devices.(Unless otherwise indicated, copies of the above specifications, standards, and handbooks are available from the Document Automation and Production Services (DAPS), Building 4D (DPM-DODSSP), 700 Robbins Avenue, Philadelphia, PA 19111-5094.)2.3 Order of precedence. In the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.73. REQUIREMENTS3.1 General. The requirements for acquiring the product described herein shall consist of this document and MIL-PRF-19500.3.2 Qualification. Devices furnished under this specification shall be products that are manufactured by a manufacturer authorized by the qualifying activity for listing on the applicable qualified manufacturer’s list (QML) before contract award (see4.2 and 6.3).3.3 Abbreviations, symbols, and definitions. Abbreviations, symbols, and definitions used herein shall be as specified in MIL-PRF-19500.3.4 Interface and physical dimensions. The interface and physical dimensions shall be as specified in MIL-PRF-19500 and figures 1, 2, 3, 4, and 5 herein.3.4.1 Lead finish. Unless otherwise specified, lead finish shall be solderable in accordance with MIL-PRF-19500, and herein.3.5 Marking. Marking shall be in accordance with MIL-PRF-19500. At the option of the manufacturer, marking may be omitted from the body, but shall be retained on the initial container.3.6 Electrical performance characteristics. Unless otherwise specified herein, the electrical performance characteristics are as specified in 1.3, 1.4, and table I.3.7 Electrical test requirements. The electrical test requirements shall be the subgroups specified in table I herein.3.8 Workmanship. Semiconductor devices shall be processed in such a manner as to be uniform in quality and shall be free from other defects that will affect life, serviceability, or appearance.4. VERIFICATION4.1 Classification of inspections. The inspection requirements specified herein are classified as follows:a. Qualification inspection (see 4.2).b. Screening (see 4.3).c. Conformance inspection (see 4.4).4.2 Qualification inspection. Qualification inspection shall be in accordance with MIL-PRF-19500 and as specified herein.4.2.1. JANHC and JANKC Qualification. JANHC and JANKC qualification inspection shall be in accordance with MIL-PRF-19500.84.3 Screening (JANS, JANTX, and JANTXV levels only). Screening shall be in accordance with table IV of MIL-PRF-19500, and as specified herein. The following measurements shall be made in accordance with table I herein. Devices that exceed the limits of table I herein shall not be acceptable.Screen (see tableIVMeasurementof MIL-PRF-19500)JANS level JANTX and JANTXV levels 3c Thermal impedance (see 4.3.2)Thermal impedance (see 4.3.2)9I CBO2, h FE4Not applicable1048 hours minimum48 hours minimum11I CBO2; h FE4;∆I CBO2 = 100% of initial value or 2 nA dc,whichever is greater.∆h FE4 = ±15%I CBO2 ,h FE412See 4.3.1240 hours minimum See 4.3.180 hours minimum13Subgroups 2 and 3 of table I herein;∆I CBO2 = 100% of initial value or 2 nA dc,whichever is greater;∆h FE4 = ±15%Subgroup 2 of table I herein;∆I CBO2 = 100% of initial value or 2 nA dc, whichever is greater;∆h FE4 = ±25%4.3.1 Power burn-in conditions. Power burn-in conditions are as follows: V CB = 10 to 30 V dc:Power shall be applied to achieve T J = 135°C minimum and a minimum power dissipation = 75 percent of maximum rated P T (see 1.3). T A = room ambient as defined in 4.5 of MIL-STD-750.NOTE: No heat sink or forced air cooling on the devices shall be permitted.4.3.2 Thermal impedance (ZθJX measurements). The ZθJX measurements shall be performed in accordance with method 3131 of MIL-STD-750.a. I M measurement current-------------5 mA.b. I H forward heating current -----------50 mA (min).c. t H heating time -------------------------25 - 30 ms.d. t md measurement delay time ------60 µs max.e. V CE collector-emitter voltage ------10 V dc minimum.The maximum limit for ZθJX under these test conditions are ZθJX (max) = 150°C/W for 2N2484, ZθJX (max) = 67°C/W for 2N2484UA and 2N2484UB.94.4 Conformance inspection. Conformance inspection shall be in accordance with MIL-PRF-19500, and as specified herein. If alternate screening is being performed in accordance with MIL-PRF-19500, a sample of screened devices shall be submitted to and pass the requirements of group A1 and A2 inspection only (table VIb, group B, subgroup 1 is not required to be performed again if group B has already been satisfied in accordance with 4.4.2).4.4.1 Group A inspection. Group A inspection shall be conducted in accordance with MIL-PRF-19500 and table I herein.4.4.2 Group B inspection. Group B inspection shall be conducted in accordance with the conditions specified for subgroup testing in table VIa (JANS) of MIL-PRF-19500 and 4.4.2.1. Electrical measurements (end-points) shall be in accordance with group A, subgroup 2 herein. Delta requirements shall be in accordance with table III herein. See 4.4.2.2 for JAN, JANTX, and JANTXV group B testing. Electrical measurements (end-points) and delta requirements for JAN, JANTX, and JANTXV shall be after each step in 4.4.2.2 and shall be in accordance with group A, subgroup 2 herein. Delta requirements shall be after each step and shall be in accordance with table III herein.4.4.2.1 Group B inspection, table VIa (JANS) of MIL-PRF-19500.Subgroup Method ConditionB41037V CB = 10 V dcB5 1027V CB = 10 V dc; T A = +125°C ±25°C for 96 hours with P T adjusted according to the chosen T A to give T J = +275°C minimum. Optionally, the test may be conducted forminimum 216 hours with P T adjusted to achieve T J = 225°C minimum, sample size (foroption) n = 45, c = 0. In this case, the ambient temperature shall be adjusted such that aminimum 75 percent of maximum rated P T (see 1.3) is applied to the device under test.(Note: If a failure occurs, resubmission shall be at the test conditions of the originalsample.)4.4.2.2 Group B inspection, (JAN, JANTX, and JANTXV). Separate samples may be used for each step. In the event of a group B failure, the manufacturer may pull a new sample at double size from either the failed assembly lot or from another assembly lot from the same wafer lot. If the new “assembly lot” option is exercised, the failed assembly lot shall be scrapped.Step Method Condition11039Steady-state life: Test condition B, 340 hours, V CB = 10 -30 V dc, T J = 150°C min.,external heating of the device under test to achieve T J = +150°C minimum is allowedprovided that a minimum of 75% of rated power is dissipated. No heat sink or forced-aircooling on the devices shall be permitted. n = 45 devices, c = 021039The steady state life test of step 1 shall be extended to 1,000 hours for each die design.Samples shall be selected from a wafer lot every twelve months of wafer production.Group B, step 2 shall not be required more than once for any single wafer lot. n = 45,c = 0.31032High-temperature life (non-operating), t = 340 hours, T A = +200°C. n = 22, c = 0.104.4.2.3 Group B sample selection. Samples selected from group B inspection shall meet all of the following requirements:a.For JAN, JANTX, and JANTXV, samples shall be selected randomly from a minimum of three wafers (orfrom each wafer in the lot) from each wafer lot. For JANS, samples shall be selected from each inspection lot. See MIL-PRF-19500.b.Must be chosen from an inspection lot that has been submitted to and passed group A, subgroup 2conformance inspection. When the final lead finish is solder or any plating prone to oxidation at hightemperature, the samples for life test (subgroups B4 and B5 for JANS, and group B for JAN, JANTX, and JANTXV) may be pulled prior to the application of final lead finish.4.4.3 Group C inspection, Group C inspection shall be conducted in accordance with the conditions specified for subgroup testing in table VII of MIL-PRF-19500, and in 4.4.3.1 (JANS).and 4.4.3.2 (JAN, JANTX, and JANTXV) herein for group C testing. Electrical measurements (end-points) shall be in accordance with group A, subgroup 2 herein. Delta requirements shall be in accordance with table III herein.4.4.3.1 Group C inspection, table VII (JANS) of MIL-PRF-19500.Subgroup Method ConditionC22036Test condition E (not applicable to UA and UB suffix devices).C610261,000 hours at V CB = 10 -30 V dc; power shall be applied to achieve T J = 150°C minimum and a minimum power dissipation P D = 75 percent of maximum rated P T as defined in 1.3herein.4.4.3.2 Group C inspection, table VII (JAN, JANTX, and JANTXV) of MIL-PRF-19500.Subgroup Method ConditionC2 2036Test condition E (not applicable to UA and UB suffix devices).C6Not applicable.4.4.3.3 Group C sample selection. Samples for subgroups in group C shall be chosen at random from any inspection lot containing the intended package type and lead finish procured to the same specification which is submitted to and passes group A tests for conformance inspection. Testing of a subgroup using a single device type enclosed in the intended package type shall be considered as complying with the requirements for that subgroup.4.4.4 Group E inspection. Group E inspection shall be performed for qualification or re-qualification only. The tests specified in table II herein must be performed to maintain qualification.4.5 Method of inspection. Methods of inspection shall be as specified in the appropriate tables and as follows.4.5.1 Pulse measurements. Conditions for pulse measurement shall be as specified in section 4 of MIL-STD-750.1112TABLE I. Group A inspection.MIL-STD-750LimitInspection 1/MethodConditionsSymbolMinMaxUnitSubgroup 1 2/Visual and mechanical examination 3/2071n = 45 devices, c = 0Solderability 3/ 4/2026n = 15 leads, c = 0Resistance to solvents 3/ 4/ 5/1022n = 15 devices, c = 0Temperature cycling 3/ 4/1051Test condition C, 25 cycles.n = 22 devices, c = 0 Hermetic seal 4/1071n = 22 devices, c = 0Fine leak Gross leakElectrical measurements 4/Group A, subgroup 2Bond strength 3/ 4/2037Precondition T A = +250°C at t = 24 hrs or T A = 300°C at t = 2 hrs; n = 11 wires, c = 0Subgroup 2Collector to emitter breakdown voltage3011Bias condition D; I C = 10 mA dc pulsed (see 4.5.1)V (BR)CEO 60V dcCollector to base cutoff current 3036Bias condition D; V CB = 60 V dc I CBO110µA dc Emitter to base cutoff current 3061Bias condition D; V EB = 6 V dc I EBO110µA dc Collector to base cutoff current 3036Bias condition D; V CB = 45 V dc I CBO25nA dc Collector to emitter cutoff current3041Bias condition D; V CE = 5 V dc I CEO 2nA dc Emitter to base cutoff current 3061Bias condition D; V EB = 5 V dc I EBO22nA dc Collector to emitter cutoff current3041Bias condition C; V CE = 45 V dc I CES 5nA dcForward-current transfer ratio3076V CE = 5 V dc; I C = 1 µA dch FE145See footnote at end of table.13TABLE I. Group A inspection - Continued.MIL-STD-750LimitInspection 1/MethodConditionsSymbolMinMaxUnitSubgroup 2 - continued.Forward-current transfer ratio 3076V CE = 5 V dc; I C = 10 µA dc h FE2200500Forward-current transfer ratio 3076V CE = 5 V dc; I C = 100 µA dc h FE3225675Forward-current transfer ratio 3076V CE = 5 V dc; I C = 500 µA dc h FE4250800Forward-current transfer ratio 3076V CE = 5 V dc; I C = 1 mA dc h FE5250800Forward-current transfer ratio 3076V CE = 5 V dc; I C = 10 mA dc pulsed (see 4.5.1)h FE6225800Collector to emitter voltage (saturated)3071I C = 1.0 mA dc; I B = 100 µA dc V CE(sat)0.3V dc Base emitter voltage (nonsaturated)3066Test condition B; V CE = 5 V dc;I C = 100 µA dcV BE(ON)0.50.7V dcSubgroup 3High-temperature operation T A = +150°CCollector to base cutoff current 3036Bias condition D; V CB = 45 V dc I CBO310µA dcLow-temperature operation T A = -55°CForward-current transfer ratio 3076V CE = 5 V dc; I C = 10 µA dch FE735Subgroup 4Magnitude of common emitter small-signal short-circuit forward-current transfer ratio 3306V CE = 5 V dc; I C = 50 µA dc;f = 5 MHz|h fe |13.0Magnitude of common emitter small-signal short-circuitforward- current transfer ratio 3306V CE = 5 V dc; I C = 500 µA dc;f = 30 MHz|h fe |2 2.07.0Small-signal open-circuit output admittance3216V CE = 5 V dc; I C = 1.0 mA dc;f = 1 kHzh oe 40µmhosSmall-signal open- circuit reverse-voltage transfer ratio 3211V CE = 5 V dc; I C = 1.0 mA dc;f = 1 kHzh re 8.0 x 10-4Small-signal short- circuit input impedance3201V CE = 5 V dc; I C = 1 mA dc;f = 1 kHzh ie3.524k ΩSee footnote at end of table.14TABLE I. Group A inspection - Continued.MIL-STD-750LimitInspection 1/MethodConditionsSymbolMinMaxUnitSubgroup 4 - continued.Small-signal short- circuit forward current transfer ratio 3206V CE = 5 V dc; I C = 1 mA dc;f = 1 kHzh fe 250900Open circuit output capacitance3236V CB = 5 V dc; I E = 0;100 kHz ≤ f ≤ 1 MHz C obo 5.0pFInput capacitance (output open-circuited)3240V EB = 0.5 V dc; I C = 0;100 kHz ≤ f ≤ 1 MHzC ibo 6.0pF Noise figure3246f = 100 Hz; V CE = 5 V dc; I C = 10µA dc; Rg = 10 k Ω;NF17.5dBNoise figure 3246 f = 1 kHz; V CE = 5 V dc; I C = 10µA dc; R g = 10 k Ω;NF23dBNoise figure 3246 f = 10 kHz; V CE = 5 V dc; I C = 10µA dc; R g = 10 k Ω;NF32dBNoise figure (wideband)3246Noise bandwidth = 10 Hz to 15.7kHz; V CE = 5 V dc; I C = 10 µA dc;R g = 10 k Ω;NF43dBSubgroups 5 and 6Not applicable Subgroup 7 4/Decap internal visual (design verification)2075n = 1 device, c = 01/For sampling plan see MIL-PRF-19500.2/For resubmission of failed subgroup A1, double the sample size of the failed test or sequence of tests. Afailure in group A, subgroup 1 shall not require retest of the entire subgroup. Only the failed test shall be rerun upon submission.3/Separate samples may be used.4/Not required for JANS devices.5/Not required for laser marked devices.TABLE II. Group E inspection (all quality levels) - For qualification only.Inspection MIL-STD-750QualificationMethod ConditionsSubgroup 1Temperature cycling (air to air)Hermetic sealFine leakGross leak Electrical measurements Subgroup 2 Intermittent lifeElectrical measurements Subgroup 3Not applicable Subgroup 4Not applicable Subgroup 5Not applicable 105110711037Test condition C, 500 cyclesSee group A, subgroup 2 and table III herein.Intermittent operation life: V CB = 10 V dc ,6,000 cycles.See group A, subgroup 2 and table III herein.12 devicesc = 045 devicesc = 015TABLE III. Groups B and C delta measurements. 1/ 2/ 3/Step Inspection MIL-STD-750Symbol Limit UnitMethod Conditions1Forward-current transfer ratio 3076V CE = 5 V dc; I C = 500µA dc; pulsed see 4.5.14/∆h FE4±25 percent change frominitial recorded reading2.Collector to emittervoltage (saturated)3071I C = 1.0 mA dc; I B = 100µA dc∆V CE(sat)4/ 5/±50 mV dc change frompreviously measured value.3.Collector to emittercutoff current 3041Bias condition C;V CB = 45 V dc∆I CES4/100 percent of initial valueor 2 nA dc, whichever isgreater.1/The delta measurements for group B, table VIa (JANS) of MIL-PRF-19500 are as follows:a.Subgroup 4, see table III herein, step 2.b.Subgroup 5, see table III herein, steps 1 and 3.2/The delta measurements for 4.4.2.2 herein (group B, JAN, JANTX, and JANTXV) are as follows: Steps 2 and 3 of table III shall be performed after each step in 4.4.2.2 herein.3/The delta measurements for group C, table VII of MIL-PRF-19500 are as follows: Subgroup 6, see table III herein, steps 1 and 3 for JANS, step 1 for JAN, JANTX, and JANTXV.4/Devices which exceed the group A limits for this test shall not be accepted.5/Applies to JANS level only.165. PACKAGING5.1 Packaging. For acquisition purposes, the packaging requirements shall be as specified in the contract or order (see6.2). When actual packaging of materiel is to be performed by DoD personnel, these personnel need to contact the responsible packaging activity to ascertain requisite packaging requirements. Packaging requirements are maintained by the Inventory Control Points' packaging activity within the Military Department or Defense Agency, or within the Military Departments' System Command. Packaging data retrieval is available from the managing Military Departments' or Defense Agency's automated packaging files, CD-ROM products, or by contacting the responsible packaging activity.6. NOTES(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)6.1 Intended use. The notes specified in MIL-PRF-19500 are applicable to this specification.6.2 Acquisition requirements. Acquisition documents should specify the following:a.Title, number, and date of this specification.b.Issue of DoDISS to be cited in the solicitation, and if required, the specific issue of individual documentsreferenced (see 2.2.1).c.Lead formation and finish may be specified (see 3.4.1).d.Type designation and product assurance level.e.Packaging requirements (see 5.1).6.3 Qualification. With respect to products requiring qualification, awards will be made only for products which are, at the time of award of contract, qualified for inclusion in Qualified Manufacturers List QML-19500 whether or not such products have actually been so listed by that date. The attention of the contractors is called to these requirements, and manufacturers are urged to arrange to have the products that they propose to offer to the Federal Government tested for qualification in order that they may be eligible to be awarded contracts or orders for the products covered by this specification. Information pertaining to qualification of products may be obtained from Defense Supply Center, Columbus, ATTN: DSCC-VQE, P.O. Box 3990, Columbus, OH 43216-5000.6.4 Suppliers of JANHC die. The qualified JANHC suppliers with the applicable letter version (example JANHCA1N645-1) will be identified on the QML.JANC ordering informationPIN Manufacturer43611341562N2484JANHCA2N2484JANHCB2N2484JANKCA2N2484JANKCB2N24846.5 Changes from previous issue. Marginal notations are not used in this revision to identify changes with respect to the previous issue due to the extensiveness of the changes.17。

M74VHC1GT08DFT2G中文资料

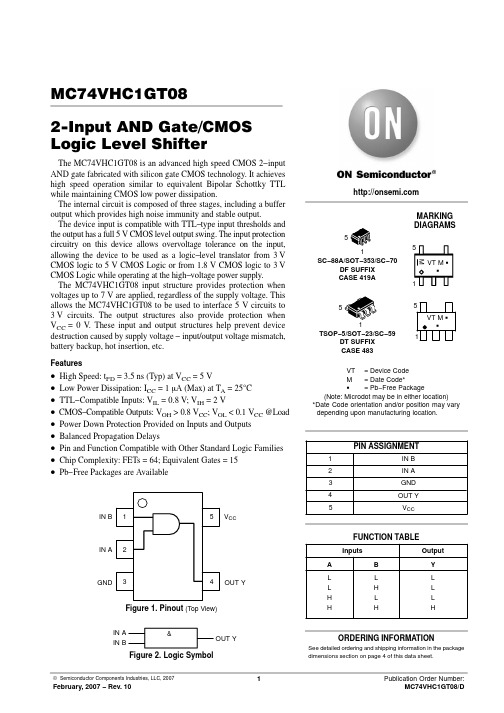

MC74VHC1GT082−Input AND Gate/CMOS Logic Level ShifterThe MC74VHC1GT08 is an advanced high speed CMOS 2−input AND gate fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power dissipation.The internal circuit is composed of three stages, including a buffer output which provides high noise immunity and stable output.The device input is compatible with TTL−type input thresholds and the output has a full 5 V CMOS level output swing. The input protection circuitry on this device allows overvoltage tolerance on the input,allowing the device to be used as a logic−level translator from 3 V CMOS logic to 5 V CMOS Logic or from 1.8 V CMOS logic to 3 V CMOS Logic while operating at the high−voltage power supply.The MC74VHC1GT08 input structure provides protection when voltages up to 7 V are applied, regardless of the supply voltage. This allows the MC74VHC1GT08 to be used to interface 5 V circuits to 3 V circuits. The output structures also provide protection when V CC = 0 V . These input and output structures help prevent device destruction caused by supply voltage − input/output voltage mismatch,battery backup, hot insertion, etc.Features•High Speed: t PD = 3.5 ns (Typ) at V CC = 5 V•Low Power Dissipation: I CC = 1 m A (Max) at T A = 25°C •TTL−Compatible Inputs: V IL = 0.8 V; V IH = 2 V•CMOS−Compatible Outputs: V OH > 0.8 V CC ; V OL < 0.1 V CC @Load •Power Down Protection Provided on Inputs and Outputs •Balanced Propagation Delays•Pin and Function Compatible with Other Standard Logic Families •Chip Complexity: FETs = 64; Equivalent Gates = 15•Pb−Free Packages are AvailableV CCIN B IN AOUT YGNDIN A IN BOUT Y &Figure 1. Pinout (Top View)Figure 2. Logic Symbol12345PIN ASSIGNMENT123GND IN B IN A 45V CCOUT Y L L H HL H L HFUNCTION TABLEInputsOutput AB L L L HY See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATIONMARKING DIAGRAMSSC−88A/SOT−353/SC−70DF SUFFIX CASE 419ATSOP−5/SOT−23/SC−59DT SUFFIXCASE 4831515VT = Device Code M = Date Code*G = Pb−Free Package*Date Code orientation and/or position may vary depending upon manufacturing location.(Note: Microdot may be in either location)15VT M G G MMAXIMUM RATINGSSymbol CharacteristicsValue Unit V CC DC Supply Voltage −0.5 to +7.0V V IN DC Input Voltage −0.5 to +7.0V V OUT DC Output Voltage V CC = 0High or Low State−0.5 to 7.0−0.5 to V CC + 0.5V I IK Input Diode Current −20mA I OK Output Diode Current V OUT < GND; V OUT > V CC+20mA I OUT DC Output Current, per Pin +25mA I CC DC Supply Current, V CC and GND +50mA P D Power dissipation in still air SC−88A, TSOP−5200mW q JA Thermal resistanceSC−88A, TSOP−5333°C/W T L Lead temperature, 1 mm from case for 10 s 260°C T J Junction temperature under bias +150°C T stg Storage temperature −65 to +150°C V ESDESD Withstand VoltageHuman Body Model (Note 1)Machine Model (Note 2)Charged Device Model (Note 3)> 2000> 200N/A VI LatchupLatchup Performance Above V CC and Below GND at 125°C (Note 4)±500mAStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Tested to EIA/JESD22−A114−A2.Tested to EIA/JESD22−A115−A3.Tested to JESD22−C101−A4.Tested to EIA/JESD78RECOMMENDED OPERATING CONDITIONSSymbol CharacteristicsMin Max Unit V CC DC Supply Voltage 3.0 5.5V V IN DC Input Voltage 0.0 5.5V V OUT DC Output VoltageV CC = 0High or Low State0.00.0 5.5V CC V T A Operating Temperature Range −55+125°C t r , t fInput Rise and Fall TimeV CC = 3.3 V ± 0.3 V V CC = 5.0 V ± 0.5 V 0010020ns/VDevice Junction Temperature versus Time to 0.1% Bond FailuresJunction Temperature °CTime, Hours Time, Years801,032,200117.890419,30047.9100178,70020.411079,6009.412037,000 4.213017,800 2.01408,9001.011101001000TIME, YEARSN O R M A L I Z E D F A I L U R E R A T EFigure 3. Failure Rate vs. Time Junction TemperatureDC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions V CC(V)T A = 25°C T A≤ 85°C−55 ≤ T A≤ 125°CUnit Min Typ Max Min Max Min MaxV IH Minimum High−LevelInput Voltage 3.04.55.51.42.02.01.42.02.01.42.02.0VV IL Maximum Low−LevelInput Voltage 3.04.55.50.530.80.80.530.80.80.530.80.8VV OH Minimum High−LevelOutput VoltageV IN = V IH or V IL V IN = V IH or V ILI OH = −50 m A3.04.52.94.43.04.52.94.42.94.4VV IN = V IH or V ILI OH = −4 mAI OH = −8 mA3.04.52.583.942.483.802.343.66VV OL Maximum Low−LevelOutput VoltageV IN = V IH or V IL V IN = V IH or V ILI OL = 50 m A3.04.50.00.00.10.10.10.10.10.1VV IN = V IH or V ILI OL = 4 mAI OL = 8 mA3.04.50.360.360.440.440.520.52VI IN Maximum InputLeakage Current V IN = 5.5 V or GND0 to5.5±0.1±1.0±1.0m AI CC Maximum QuiescentSupply CurrentV IN = V CC or GND 5.5 1.02040m AI CCT Quiescent SupplyCurrentInput: V IN = 3.4 V 5.5 1.35 1.50 1.65mAI OPD Output LeakageCurrentV OUT = 5.5 V0.00.5 5.010m A AC ELECTRICAL CHARACTERISTICS C load = 50 pF, Input t r = t f= 3.0 nsSymbol Parameter Test ConditionsT A = 25°C T A≤ 85°C−55 ≤ T A≤ 125°CUnit Min Typ Max Min Max Min Maxt PLH, t PHL Maximum PropagationDelay, Input A or B to YV CC = 3.3 ± 0.3 V C L = 15 pFC L = 50 pF4.15.98.812.310.514.012.516.5nsV CC = 5.0 ± 0.5 V C L = 15 pFC L = 50 pF3.54.25.97.97.09.09.011.0C IN Maximum Input Capaci-tance5.5101010pFC PD Power Dissipation Capacitance (Note 5)Typical @ 25°C, V CC = 5.0 VpF115.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC. C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.*Includes all probe and jig capacitanceC L *GNDInput A or BOutput YV OLV OH Figure 4. Switching WaveformsFigure 5. Test CircuitORDERING INFORMATIONDevicePackageShipping †MC74VHC1GT08DFT1SC−88A / SOT−353 / SC−703000 / Tape & ReelM74VHC1GT08DFT1G SC−88A / SOT−353 / SC−70(Pb−Free)MC74VHC1GT08DFT2SC−88A / SOT−353 / SC−70M74VHC1GT08DFT2G SC−88A / SOT−353 / SC−70(Pb−Free)MC74VHC1GT08DTT1TSOP−5 / SOT−23 / SC−59M74VHC1GT08DTT1GTSOP−5 / SOT−23 / SC−59(Pb−Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.419A−01 OBSOLETE. NEW STANDARD 419A−02.4.DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.DIM A MIN MAX MIN MAX MILLIMETERS1.802.200.0710.087INCHES B 1.15 1.350.0450.053C 0.80 1.100.0310.043D 0.100.300.0040.012G 0.65 BSC 0.026 BSC H −−−0.10−−−0.004J 0.100.250.0040.010K 0.100.300.0040.012N 0.20 REF 0.008 REF S2.00 2.200.0790.087SC−88A, SOT−353, SC−70CASE 419A−02ISSUE J*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*PACKAGE DIMENSIONSTSOP−5CASE 483−02ISSUE FNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.5.OPTIONAL CONSTRUCTION: ANADDITIONAL TRIMMED LEAD IS ALLOWED IN THIS LOCATION. TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY .DIM MIN MAX MILLIMETERS A 3.00 BSC B 1.50 BSC C 0.90 1.10D 0.250.50G 0.95 BSC H 0.010.10J 0.100.26K 0.200.60L 1.25 1.55M 0 10 S2.503.00__ǒmm inchesǓ*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*2X2XON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

T8XX-XXXH中文资料