K4S561632C中文资料

电子元器件参数大全

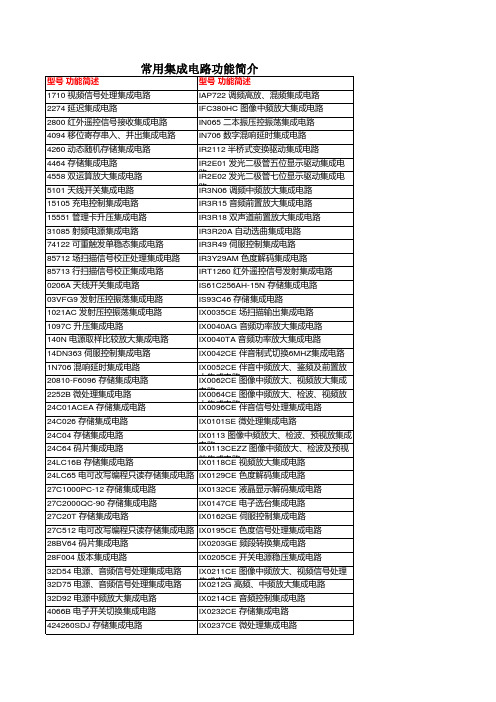

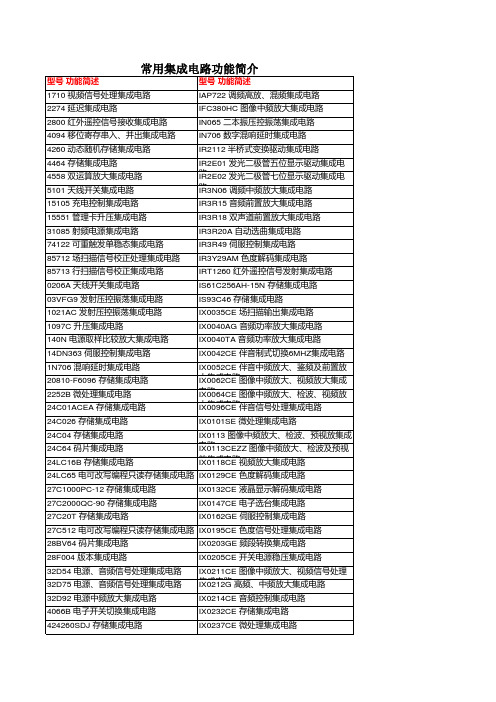

AK4321-VF-E1 音频数/模转换集成电路 IX2915CE 色度、亮度及行场扫描信号处 理集成电路 微处理集成电路 AN1319 双高速电压比较集成电路 IX3081CE2 AN1358S 双运算放大集成电路 AN1393 双运算放大集成电路 AN1431T 稳压电源集成电路 AN1452 音频前置放大集成电路 AN1458S 双运算放大集成电路 AN206 伴音中频及前置放大集成电路 AN222 自动频率控制集成电路 AN236 副载波信号处理集成电路 IZ0052CE 字符信号处理集成电路 IZ0055CE 音频控制集成电路 IZ0068CE 视频缓冲放大集成电路 JCE4501 数/模转换集成电路 JLC1562BF 输入/输出扩展接口集成电路 JQ5544H 电子石英闹钟集成电路 JRC4555D 双运算放大集成电路 JRC6308B 话筒信号放大集成电路

ACP2371 多伴音、多语言改善集成电路 IX1461GE 射频前置放大集成电路 ACVP2205 色度、亮度信号分离集成电 IX1463GE 误差信号发生集成电路 路 AD1853 立体声数/模转换集成电路 IX1473GE 伺服控制集成电路 AD1858 音频解调集成电路 AD722 视频编码集成电路 ADC2300E 音频数/模转换集成电路 ADC2300J 音频数/模转换集成电路 ADC2310E 音频数/模转换集成电路 ADV7172 视频编码集成电路 ADV7175A 视频编码集成电路 AE31201 频率显示集成电路 AJ7080 射频调制集成电路 IX1474GE 解码、纠错集成电路 IX1504AF 状态控制集成电路 IX1763CEN1 视频、色度及行场扫描信号 处理集成电路 IX1807CE 微处理集成电路 IX2164CE 微处理集成电路 IX2249AF 系统控制处理集成电路 IX2287CE 存储集成电路 IX2341AF 伺服控制集成电路 IX2372CE 微处理集成电路

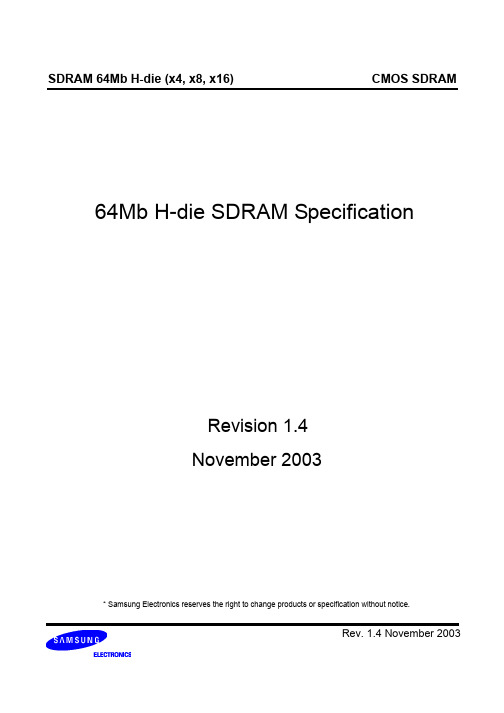

SDRAM存储器k4s641632详细参数及说明

SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAM 64Mb H-die SDRAM SpecificationRevision 1.4November 2003* Samsung Electronics reserves the right to change products or specification without notice.Rev. 1.4 November 2003SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAM Revision HistoryRevision 0.0 (May, 2003)• Target spec releaseRevision 0.1 (July, 2003)• Preliminary spec releaseRevision 0.2 (August, 2003)• Modified IBIS characteristic.Revision 1.0 (September, 2003)• FinalizedRevision 1.1 (September, 2003)• Corrected IBIS Specification.Revision 1.2 (October, 2003)• Deleted speed 7C at x4/x8.Revision 1.3 (October, 2003)• Deleted AC parameter notes 5.Revision 1.4 (November, 2003)• Modified Pin Function description.Rev. 1.4 November 2003SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003Part No.Orgainization Max Freq.InterfacePackageK4S640432H-TC(L)7516Mb x 4 133MHz(CL=3)LVTTL54pin TSOP(II)K4S640832H-TC(L)758Mb x 8133MHz(CL=3) K4S641632H-TC(L)604Mb x 16166MHz(CL=3) K4S641632H-TC(L)70143MHz(CL=3) K4S641632H-TC(L)75133MHz(CL=3)The K4S640432H / K4S640832H / K4S641632H is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 4,194,304 words by 4 bits, / 4 x 2,097,152 words by 8 bits, / 4 x 1,048,576 words by 16 bits, fabricated with SAMSUNG ′s high perfor-mance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.• JEDEC standard 3.3V power supply• LVTTL compatible with multiplexed address • Four banks operation• MRS cycle with address key programs -. CAS latency (2 & 3)-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)• All inputs are sampled at the positive going edge of the system clock• Burst read single-bit write operation• DQM (x4,x8) & L(U)DQM (x16) for masking • Auto & self refresh• 64ms refresh period (4K cycle)GENERAL DESCRIPTIONFEATURESOrdering Information4M x 4Bit x 4 / 2M x 8Bit x 4 / 1M x 16Bit x 4 Banks Synchronous DRAMSDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAM Package Physical Dimension54Pin TSOP(II) Package DimensionRev. 1.4 November 2003SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003LWE LDQMDQiSamsung Electronics reserves the right to change products or specification without notice.*SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003123456789101112131415161718192021222324252627545352515049484746454443424140393837363534333231302928PIN CONFIGURATION (Top view)54Pin TSOP (II)(400mil x 875mil)(0.8 mm Pin pitch)PIN FUNCTION DESCRIPTIONPin NameInput FunctionCLK System clock Active on the positive going edge to sample all inputs.CSChip selectDisables or enables device operation by masking or enabling all inputs except CLK, CKE and DQMCKE Clock enableMasks system clock to freeze operation from the next clock cycle.CKE should be enabled at least one cycle prior to new command.Disable input buffers for power down in standby.A 0 ~ A 11AddressRow/column addresses are multiplexed on the same pins.Row address : RA 0 ~ RA 11,Column address : (x4 : CA 0 ~ CA 9, x8 : CA 0 ~ CA 8 , x16 : CA 0 ~ CA 7)BA 0 ~ BA 1Bank select address Selects bank to be activated during row address latch time.Selects bank for read/write during column address latch time.RAS Row address strobe Latches row addresses on the positive going edge of the CLK with RAS low.Enables row access & precharge.CAS Column address strobe Latches column addresses on the positive going edge of the CLK with CAS low.Enables column access.WE Write enableEnables write operation and row tches data in starting from CAS, WE active.DQM Data input/output mask Makes data output Hi-Z, t SHZ after the clock and masks the output.Blocks data input when DQM active.DQ 0 ~ X15Data input/output Data inputs/outputs are multiplexed on the same pins.V DD /V SS Power supply/ground Power and ground for the input buffers and the core logic.V DDQ /V SSQ Data output power/ground Isolated power supply and ground for the output buffers to provide improved noise immunity.N.C/RFUNo connection/reserved for future useThis pin is recommended to be left No Connection on the device.x16x8x4x16x8x4V DD DQ0V DDQ DQ1DQ2V SSQ DQ3DQ4V DDQ DQ5DQ6V SSQ DQ7V DD LDQM WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ15V SSQ DQ14DQ13V DDQ DQ12DQ11V SSQ DQ10DQ9V DDQ DQ8V SSN.C/RFU UDQM CLK CKE N.C A11A9A8A7A6A5A4V SSV DD N.C V DDQ N.C DQ0V SSQ N.C N.C V DDQ N.C DQ1V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/APA0A1A2A3V DDV SS N.C V SSQ N.C DQ3V DDQ N.C N.C V SSQ N.C DQ2V DDQ N.C V SSN.C/RFU DQM CLK CKE N.C A11A9A8A7A6A5A4V SSV DD DQ0V DDQ N.C DQ1V SSQ N.C DQ2V DDQ N.C DQ3V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ7V SSQ N.C DQ6V DDQ N.C DQ5V SSQ N.C DQ4V DDQ N.C V SSN.C/RFU DQM CLK CKE N.C A11A9A8A7A6A5A4V SSSDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003ABSOLUTE MAXIMUM RATINGSParameter Symbol Value Unit Voltage on any pin relative to V SS V IN , V OUT -1.0 ~ 4.6V Voltage on V DD supply relative to V SS V DD , V DDQ-1.0 ~ 4.6V Storage temperature T STG -55 ~ +150°C Power dissipation P D 1W Short circuit currentI OS50mAPermanent device damage may occur if "ASOLUTE MAXIMUM RATINGS" are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Note :DC OPERATING CONDITIONSRecommended operating conditions (Voltage referenced to V SS = 0V, T A = 0 to 70°C)Parameter Symbol Min Typ Max Unit NoteSupply voltage V DD , V DDQ3.0 3.3 3.6V Input logic high voltage V IH 2.0 3.0V DD +0.3V 1Input logic low voltage V IL -0.300.8V 2Output logic high voltage V OH 2.4--V I OH = -2mA Output logic low voltage V OL --0.4V I OL = 2mAInput leakage currentI LI-10-10uA31. V IH (max) = 5.6V AC.The overshoot voltage duration is ≤ 3ns.2. V IL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.3. Any input 0V ≤ V IN ≤ V DDQ .Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.Notes :CAPACITANCE (V DD = 3.3V, T A = 23°C, f = 1MHz, V REF =1.4V ± 200 mV)PinSymbol Min Max Unit Note ClockC CLK 2.5 4.0pF 1RAS, CAS, WE, CS, CKE, DQM C IN 2.5 5.0pF 2Address C ADD 2.5 5.0pF 2DQ 0 ~ DQ 3C OUT4.06.5pF31. -75 only specify a maximum value of 3.5pF2. -75 only specify a maximum value of3.8pF 3. -75 only specify a maximum value of 6.0pFNotes :SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 20031. Measured with outputs open.2. Refresh period is 64ms.3. K4S6404(08)32H-TC**4. K4S6404(08)32H-TL**5. Unless otherwise noted, input swing IeveI is CMOS(V IH /V IL =V DDQ /V SSQ)Notes :(Recommended operating condition unless otherwise noted, T A = 0 to 70°C for x4, x8)ParameterSymbolTest ConditionVersion Unit Note75Operating current (One bank active)I CC1 Burst length = 1 t RC ≥ t RC (min) I O = 0 mA75mA 1Precharge standby current in power-down modeI CC2P CKE ≤ V IL (max), t CC = 10ns 1mAI CC2PS CKE & CLK ≤ V IL (max), t CC = ∞1Precharge standby current in non power-down mode I CC2NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns15mAI CC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 6Active standby current in power-down mode I CC3P CKE ≤ V IL (max), t CC = 10ns 3mAI CC3PS CKE & CLK ≤ V IL (max), t CC = ∞3Active standby current in non power-down mode (One bank active)I CC3NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns30mAI CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25Operating current (Burst mode)I CC4 I O = 0 mA Page burst4Banks Activated t CCD = 2CLKs 115mA 1Refresh current I CC5t RC ≥ t RC (min)135mA 2Self refresh currentI CC6CKE ≤ 0.2VC 1mA 3L400uA4DC CHARACTERISTICSSDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 20031. Measured with outputs open.2. Refresh period is 64ms.3. K4S641632H-TC**4. K4S641632H-TL**5. Unless otherwise noted, input swing IeveI is CMOS(V IH /V IL =V DDQ /V SSQ)Notes :DC CHARACTERISTICS(Recommended operating condition unless otherwise noted, T A = 0 to 70°C for x16 only)ParameterSymbolTest ConditionVersionUnit Note607075Operating current (One bank active)I CC1 Burst length = 1 t RC ≥ t RC (min) I O = 0 mA140115110mA 1Precharge standby current in power-down modeI CC2P CKE ≤ V IL (max), t CC = 10ns 1mAI CC2PS CKE & CLK ≤ V IL (max), t CC = ∞1Precharge standby current in non power-down mode I CC2NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns15mAI CC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 6Active standby current in power-down mode I CC3P CKE ≤ V IL (max), t CC = 10ns 3mAI CC3PS CKE & CLK ≤ V IL (max), t CC = ∞3Active standby current in non power-down mode (One bank active)I CC3NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns30mAI CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25Operating current (Burst mode)I CC4 I O = 0 mA Page burst4Banks Activated t CCD = 2CLKs 160140135mA 1Refresh current I CC5t RC ≥ t RC (min)160140135mA 2Self refresh currentI CC6CKE ≤ 0.2VC 1mA 3L400uA4SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003AC OPERATING TEST CONDITIONS (V DD = 3.3V ± 0.3V, T A = 0 to 70°C)Parameter Value Unit AC input levels (Vih/Vil)2.4/0.4V Input timing measurement reference level 1.4V Input rise and fall timetr/tf = 1/1ns Output timing measurement reference level 1.4VOutput load conditionSee Fig. 23.3V1200Ω870ΩOutput30pFV OH (DC) = 2.4V, I OH = -2mA V OL (DC) = 0.4V, I OL = 2mAVtt = 1.4V50ΩOutput30pFZ0 = 50Ω(Fig. 2) AC output load circuit(Fig. 1) DC output load circuit Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle timeand then rounding off to the next higher integer.2. Minimum delay is required to complete write.3. All parts allow every cycle column address change.4. In case of row precharge interrupt, auto precharge and read burst stop.OPERATING AC PARAMETER(AC operating conditions unless otherwise noted)ParameterSymbol VersionUnit Note 607075Row active to row active delay t RRD (min)121415ns 1RAS to CAS delay t RCD (min)182020ns 1Row precharge time t RP (min)182020ns 1Row active time t RAS (min)424945ns 1t RAS (max)100us Row cycle timet RC (min)606865ns 1Last data in to row precharge t RDL (min)2CLK 2Last data in to Active delayt DAL (min) 2 CLK + tRP-Last data in to new col. address delay t CDL (min)1CLK 2Last data in to burst stopt BDL (min)1CLK 2Col. address to col. address delay t CCD (min)1CLK 3Number of valid output dataCAS latency = 32ea4CAS latency = 21SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 20031. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Notes :DQ BUFFER OUTPUT DRIVE CHARACTERISTICSParameterSymbol Condition Min TypMax Unit Notes Output rise time trh Measure in linear region : 1.2V ~ 1.8V 1.37 4.37Volts/ns 3 Output fall time tfh Measure in linear region : 1.2V ~ 1.8V 1.30 3.8Volts/ns 3 Output rise time trh Measure in linear region : 1.2V ~ 1.8V 2.8 3.9 5.6Volts/ns 1,2 Output fall timetfhMeasure in linear region : 1.2V ~ 1.8V2.02.9 5.0Volts/ns1,21. Rise time specification based on 0pF + 50 Ω to V SS , use these values to design to.2. Fall time specification based on 0pF + 50 Ω to V DD , use these values to design to.3. Measured into 50pF only, use these values to characterize to.4. All measurements done with respect to V SS .Notes :AC CHARACTERISTICS (AC operating conditions unless otherwise noted)ParameterSymbol607075Unit NoteMin Max Min Max Min Max CLK cycle time CAS latency=3t CC 61000710007.51000ns 1CAS latency=2--10CLK to valid output delay CAS latency=3t SAC 56 5.4ns 1,2CAS latency=2--6Output data hold timeCAS latency=3t OH 2.533ns 2CAS latency=2--3CLK high pulse width t CH 2.53 2.5ns 3CLK low pulse width t CL 2.53 2.5ns 3Input setup time t SS 1.52 1.5ns 3Input hold time t SH 110.8ns 3CLK to output in Low-Z t SLZ111ns2CLK to output in Hi-ZCAS latency=3t SHZ56 5.4nsCAS latency=2--6SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003I OH Characteristics (Pull-up)Voltage 133MHz Min 133MHz Max (V)I (mA)I (mA)3.45- -1.683.30- -19.113.00-0.35 -51.872.70-3.75-90.442.50-6.65-107.311.95-13.75-137.91.80-17.75-158.341.65-20.55-173.61.50-23.55-188.791.40-26.2-199.011.00-36.25-241.150.20-46.5-351.68IBIS SPECIFICATIONI OL Characteristics (Pull-down)Voltage 133MHz Min 133MHz Max (V)I (mA)I (mA)3.4543.92155.823.30--3.0043.36153.721.9541.20148.401.8040.56146.021.6539.60141.751.5038.40136.081.4037.28131.391.0030.08105.840.8526.6493.660.6521.5275.250.4014.1649.140-100-200-300-400-500-600030.511.522.53.5Voltagem A250200150100500030.511.522.53.5Voltagem A133MHz Pull-up133MHz Pull-downI OH Min (133MHz)I OH Max (133MHz)I OL Min (133MHz)I OL Max (133MHz)SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003V DD Clamp @ CLK, CKE, CS, DQM & DQV DD (V)I (mA)0.00.00.20.00.40.00.60.00.70.00.80.00.90.01.0 0.231.2 1.341.4 3.021.6 5.061.8 7.352.0 9.832.212.482.415.302.618.31V SS Clamp @ CLK, CKE, CS, DQM & DQV SS (V)I (mA)-2.6-57.23-2.4-45.77-2.2-38.26-2.0-31.22-1.8-24.58-1.6-18.37-1.4-12.56-1.2 -7.57-1.0 -3.37-0.9 -1.75-0.8 -0.58-0.7 -0.05-0.6 0.0-0.4 0.0-0.2 0.0 0.00.0201510500312Voltagem AI (mA)Voltagem AI (mA)Minimum V DD clamp current(Referenced to V DD )Minimum V SS clamp current0-10-20-30-40-30-2-1-50-60SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.4 November 2003SIMPLIFIED TRUTH TABLE (V=Valid, X=Don ′t care, H=Logic high, L=Logic low)CommandCKEn-1CKEnCSRASCASWEDQMBA 0,1A 10/APA 11,A 9 ~ A 0NoteRegisterMode register set H X L L L L X OP code1,2RefreshAuto refreshH H L L L H X X 3Self refreshEntry L 3ExitL H L H H H X X3H X X X 3Bank active & row addr.H X L L H H X V Row address Read &column address Auto precharge disable H X L H L H X V L Column address (A 0 ~ A 9)4Auto precharge enable H 4,5Write &column address Auto precharge disable H X L H L L X VL Column address (A 0 ~ A 9)4Auto precharge enableH 4,5Burst stop HX L H H L X X 6Precharge Bank selection H X L L H L X V L XAll banksX H Clock suspend or active power downEntry H L H X X X X XL V V V Exit L H X X X X X Precharge power down modeEntryH L H X X X XXL H H H ExitL HH X X X X L V V V DQMH X V X 7No operation commandHXH X X X XXLHHH1. OP Code : Operand codeA 0 ~ A 11 & BA 0 ~ BA 1 : Program keys. (@ MRS)2. MRS can be issued only at all banks precharge state.A new command can be issued after 2 CLK cycles of MRS.3. Auto refresh functions are as same as CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at all banks precharge state.4. BA 0 ~ BA 1 : Bank select addresses.If both BA 0 and BA 1 are "Low" at read, write, row active and precharge, bank A is selected.If both BA 0 is "Low" and BA 1 is "High" at read, write, row active and precharge, bank B is selected. If both BA 0 is "High" and BA 1 is "Low" at read, write, row active and precharge, bank C is selected. If both BA 0 and BA 1 are "High" at read, write, row active and precharge, bank D is selected. If A 10/AP is "High" at row precharge, BA 0 and BA 1 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at t RP after the end of burst.6. Burst stop command is valid at every burst length.7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)Notes :。

CN5616中文资料_开关模式LED驱动芯片

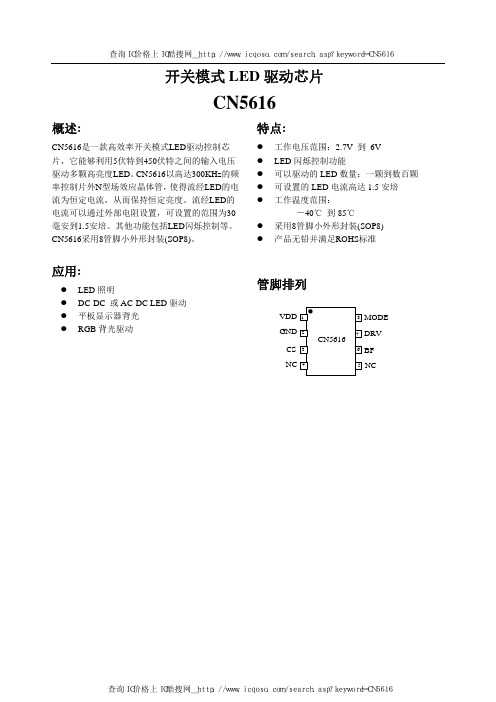

开关模式LED驱动芯片CN5616概述:CN5616是一款高效率开关模式LED驱动控制芯片,它能够利用5伏特到450伏特之间的输入电压驱动多颗高亮度LED。

CN5616以高达300KHz的频率控制片外N型场效应晶体管,使得流经LED的电流为恒定电流,从而保持恒定亮度。

流经LED的电流可以通过外部电阻设置,可设置的范围为30毫安到1.5安培。

其他功能包括LED闪烁控制等。

CN5616采用8管脚小外形封装(SOP8)。

应用:●LED照明●DC-DC 或AC-DC LED驱动●平板显示器背光●RGB背光驱动特点:●工作电压范围:2.7V 到 6V●LED闪烁控制功能●可以驱动的LED数量:一颗到数百颗●可设置的LED电流高达1.5安培●工作温度范围:-40℃到85℃●采用8管脚小外形封装(SOP8)●产品无铅并满足ROHS标准管脚排列BFGNDNCCSVDDNCDRVMODE查询IC价格上IC酷搜网_http://www.icqoso.com/search.asp?keyword=CN5616查询IC价格上IC酷搜网_http://www.icqoso.com/search.asp?keyword=CN5616典型应用电路输入电压5V 到 450V图1 典型应用电路其中:●L1为电感●流经电阻R6的电流既要满足稳压二极管击穿的需要,也要为CN5616提供约0.5毫安的工作电流。

●C1是滤波电容,电容值为10uF●电容C2用来控制闪烁周期,闪烁周期=2.53×10+6×C (秒)●D1是稳压二极管,其稳压电压的选择要确保能够驱动片外场效应晶体管M1。

对高压场效应晶体管,击穿电压应该在5.8V左右。

●D2为整流二极管,采用肖特基二极管可以提高转换效率。

对于输入电压大于200V的应用,可以查询IC价格上IC酷搜网_http://www.icqoso.com/search.asp?keyword=CN5616选择FR106/FR107等型号。

VK3266

Viken 01/2007

VK3266数据手册 Ver0.12

维肯电子 2006年 发布 版权所有

1 of 29

维肯电子

VK3266

SPI/UART/8位并行总线接口 宽工作电压 4通道 16级FIFO的UART

维肯电子

VK3266

SPI/UART/8位并行总线接口 宽工作电压 4通道 16级FIFO的UART

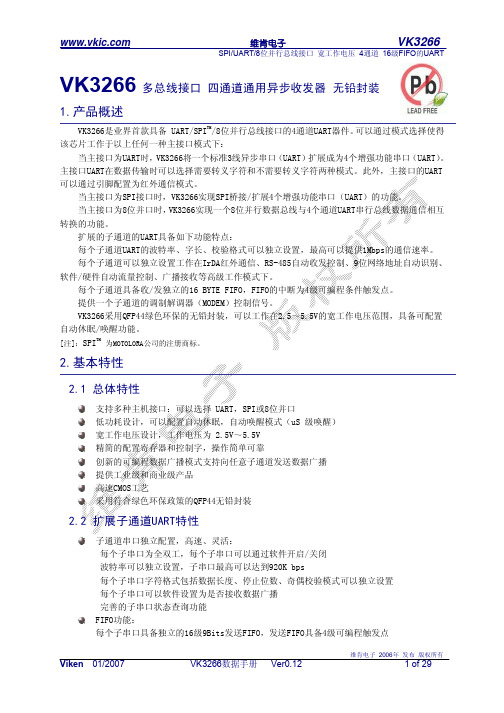

VK3266 多总线接口 四通道通用异步收发器 无铅封装

1.产品概述

VK3266是业界首款具备 UART/SPITM/8位并行总线接口的4通道UART器件。可以通过模式选择使得 该芯片工作于以上任何一种主接口模式下:

6.1封装图

Viken 01/2007

VK3266数据手册 Ver0.12

维肯电子 2006年 发布 版权所有

3 of 29

维肯电子

VK3266

SPI/UART/8位并行总线接口 宽工作电压 4通道 16级FIFO的UART

44 GND 43 OSCI 42 OSCO 41 CLKSEL 40 CLKIN 39 VCC 38 RTS3 37 RX3 36 TX3 35 CTS3 34 RTS1

2.4 SPI主接口特性

最高速度5M bit/s 仅支持SPI从模式 16位,SPI模式0

2.5 8位并口主接口特性

标准8位MCU总线接口 命令和数据共用8位地址总线,通过A0(数据/控制)信号进行切换 子通道选择通过命令字控制和指示,无需额外的通道指示信号线 仅占用2个地址空间

3.应用领域

多串口服务器/多串口卡 工业/自动化现场RS-485控制 通过CDMA/GPRS MODEM的无线数据传输 车载信息平台/车载GPS定位系统 远传自动抄表(AMR)系统 POS/税控POS/金融机具 DSP/嵌入式系统

K4S561632H-UP75中文资料

RAS

Row address strobe

CAS

Column address strobe

WE

Write enable

DQM

Data input/output mask

GENERAL DESCRIPTION

The K4S560432H / K4S560832H / K4S561632H is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 16,777,216 words by 4 bits / 4 x 8,388,608 words by 8bits / 4 x 4,194,304 words by 16bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

CLK ADD

Row Buffer Refresh Counter

电子元器件参数大全

IX0773CE 红外遥控信号发射集成电路 IX0776CE 伴音混频集成电路 IX0812CE 开关电源厚膜集成电路 IX0823GE 微处理集成电路 IX0875CE 开关电源厚膜集成电路 IX0933CE 微处理集成电路 IX0948CE 场扫描输出集成电路 IX0969 色度、亮度信号处理集成电路 IX0981CEN1 微处理集成电路 IX0981GE 伺服控制接口集成电路 IX1194CEN2 微处理集成电路 IX1463GE 误差信号发生集成电路 IX1473GE 伺服控制集成电路 IX1474GE 解码、纠错集成电路 IX1504AF 状态控制集成电路 IX1763CEN1 视频、色度及行场扫描信号 处理集成电路 IX1807CE 微处理集成电路 IX2164CE 微处理集成电路 IX2249AF 系统控制处理集成电路 IX2287CE 存储集成电路 IX2341AF 伺服控制集成电路 IX2372CE 微处理集成电路 IX2915CE 色度、亮度及行场扫描信号处 理集成电路 IX3081CE2 微处理集成电路 IZ0052CE 字符信号处理集成电路 IZ0055CE 音频控制集成电路 IZ0068CE 视频缓冲放大集成电路 JCE4501 数/模转换集成电路 JLC1562BF 输入/输出扩展接口集成电路 JQ5544H 电子石英闹钟集成电路 JRC4555D 双运算放大集成电路 JRC6308B 话筒信号放大集成电路 JU0005 视频输出厚膜集成电路 JU0006 音质改善集成电路 JU0026 电源稳压厚膜集成电路 JU0027 视频输出厚膜集成电路 JU0114 开关电源稳压厚膜集成电路 K2959M 图像中频滤波集成电路 K5T8257B 存储集成电路 K6259K 滤波集成电路 K6265K 滤波集成电路

设备安装工程交互式电子技术手册设计与实现

设备安装工程交互式电子技术手册的设计与实现摘要:本文对设备安装工程现状进行分析,并提出设备安装工程交互式电子技术手册,并对其硬件、软件进行了阐述,并给出了具体设计思路。

关键词:电子技术手册;arm中图分类号:tf082 文献标识码:a 文章编号:1001-828x(2013)06-0-01一、引言目前,随着设备安装工程技术的迅速发展,设备安装过程中的新设备、新工艺和新方法也不断涌现,同一施工单位的不同施工点或者是同一施工类型的不同项目其安装过程都是大相径庭的,这在一定程度上会造成施工组织的混乱,或者是施工质量的参差不齐,因此对安装规范进行统一汇编,建立无纸化的交互式电子技术手册,不失为一科学的选择。

本文基于嵌入式技术,选择arm9s3c2410为内核来组建系统平台,分别对其硬件电路和系统软件进行分析设计,并在此基础上对电力设备安装和风水设备安装的相关知识进行整理归类,以最终形成具有安装规范统一,交互性强和便携性高的指导安装作业的微型电脑。

二、arm9s3c2410简介s3c2410是韩国三星公司的一款基于arm920t内核的16/32位risc嵌入式微处理器,主要面向手持设备以及高性价比、低功耗的应用,运行的频率可达203mhz。

arm920t核由armtdmi、存储单元和高速缓存三部分组成,其中mmu管理虚拟内存,高速缓存由独立的16kb地址和16kb数据高速cache组成。

三、硬件设计一个嵌入式处理器是不能独立工作的,必须给它供电,加上时钟信号、复位信号,如果没有片内存储器,还要加上存储器系统,最后提供调试测试接口,即构成了嵌入式系统的最小架构。

因为考虑到本模拟训练系统的开发成本和对i/o接口的特殊要求,选择嵌入式系统最小系统是科学和合理的。

(1)电源模块设计s3c2410的arm芯片均有4组电源输入,数字3.3和1.8v,模拟3.3和1.8v,考虑不使用a/d功能,又需要单点接地或大面积铺地,末级电源只需要提供两组电源。

嵌入式系统应用开发实例(52)

另外,系统建立了输入的抽象层,屏蔽了不同输入设备。

12:40

32

1.2.3 GSM/GPRS Server多工通信服务器软件

GSM/GPRS Server多工通信服务器软件是电话、短信及 数据业务的守护进程,负责响应应用程序转发的用户操作事 件及从串口的获得的无线通信模块事件,是整个智能手机系 统的核心。在这部分的工作中要实现多链路的数据通信、事件 优先级判别,并在执行数据通信时,保证电话、短信的接入。 具体程序设备结构如下图所示。

12:40

35

电话控制程序状态切换关系图

12:40

36

电话控制程序状态切换

电话控制程序设计分为三个运行态:PowerOn State(上电 态)、Idle State(空闲态)、Execution State(执行态)。上图表

示了三个状态之间的关系和进入各个状态的条件。

电话控制程序在智能手机系统上电复位、GSM/GPRS

设计对动态库中封装的函数进行了分层。其中直接针对 Framebuffer进行输出的函数位于系统最低层,其上是设备上 下文。因每次对一个窗口输出的时都要首先建立设备上下文, 所以设备上下文总可以引用窗体结构,自然也可以引用到窗口 剪切域,在剪切域范围内才可以进行输出。

图形设备接口建立在设备上下文之上,主要包括点、线、面、 文本等。如上文所述,输出之前,首先建立设备上下文,即其 输出的目标是设备上下文,而不是窗口。

12:40

6

智能手机的主要参数

串口:RS-232口; LED: 红(在充电指示)、绿(软件运行或电池故障指示) 电源管理:Full featured-Sipports Run,Idle and Sleep modes 复位:设置复位开关; 电池:3.7V锂离子电池 物理尺寸:主板尺寸为65x53x5.5mm 电源适配器:5V直流; 外部连接器:Possible integration、CF卡、Sensor、 Bluetooth、SIM Card、其他

实验2 C语言程序设计及 LED跑马灯实验

BWSCON寄存器

0000 0000 0000 0000 0001 0000 0000 0000 0000 0001 0000 0000 0000 0000 0001 0000 0000 0000 0000 0010 0000 0000 0000 0000 0001 0000 0000 0000 0000 0010 0000 0000 0000 0000 0010

;将以上单独表达的各参数整合为32位字数据,以备写入REFRESH寄存器之用。

DCD ((REFEN<<23)+(TREFMD<<22)+(Trp<<20)+(Tsrc<<18)+(Tchr<<16)+REFCNT)

本实验所需的存储器参数预定义(符号化表示)

DW16 DW32 B1_BWSCON B2_BWSCON B3_BWSCON B4_BWSCON B5_BWSCON B6_BWSCON B7_BWSCON B0_Tacs B0_Tcos B0_Tacc B0_Tcoh B0_Tah B0_Tacp B0_PMC B6_MT B6_Trcd B6_SCAN REFEN TREFMD Trp Tsrc Tchr REFCNT EQU (0x1) EQU (0x2) EQU (DW16) EQU (DW16) EQU (DW16) EQU (DW32) EQU (DW16) EQU (DW32) EQU (DW32) EQU 0x3 EQU 0x3 EQU 0x7 EQU 0x3 EQU 0x3 EQU 0x1 EQU 0x0 EQU 0x3 EQU 0x1 EQU 0x1 EQU 0x1 EQU 0x0 EQU EQU 0x1 EQU 0x2 EQU 1268 ; AMD flash(AM29LV160DB), 16-bit, for nCS1 ; PCMCIA(PD6710), 16-bit ; Ethernet(CS8900), 16-bit ; Intel Strata(28F128), 32-bit, for nCS4 ; A400/A410 Ext, 16-bit ; SDRAM(K4S561632C) 32MBx2, 32-bit ; N.C. ;0clk ;0clk ;14clk ;0clk ;0clk ;normal ;SDRAM ;3clk ;9bit ;Refresh enable ;CBR(CAS before RAS)/Auto refresh 0x1 ;3clk ;5clk Trc= Trp(3)+Tsrc(5) = 8clock ;3clk ;HCLK=105Mhz, (2048+1-7.81*100);75M->1463

K4S561632E-UC60中文资料

CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)256Mb E-die SDRAM SpecificationRevision 1.3August 2004* Samsung Electronics reserves the right to change products or specification without notice.54 TSOP-II with Pb-Free(RoHS compliant)CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)Revision HistoryRevision 1.0 (May. 2003)- First generation for Pb_free products Revision 1.1 (August. 2003)- Corrected typo in Page #8, 9Revision 1.2 (May. 2004)- Added Note 5. sentense of tRDL parameter Revision 1.3 (August. 2004) - Corrected typo.CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)Part No.Orgainization Max Freq.Interface Package K4S560432E-UC(L)7564M x 4 133MHz LVTTL 54pin TSOP(II)K4S560832E-UC(L)7532M x 8 133MHz LVTTL 54pin TSOP(II)K4S561632E-UC(L)60/7516M x 16133MHzLVTTL54pin TSOP(II)The K4S560432E / K4S560832E / K4S561632E is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 16,785,216 / 4 x 8,392,608 / 4 x 4,196,304 words by 4bits, fabricated with SAMSUNG's high performance CMOS technology. Synchro-nous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of oper-ating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.• JEDEC standard 3.3V power supply • LVTTL compatible with multiplexed address • Four banks operation• MRS cycle with address key programs -. CAS latency (2 & 3)-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)• All inputs are sampled at the positive going edge of the system clock. • Burst read single-bit write operation• DQM (x4,x8) & L(U)DQM (x16) for masking • Auto & self refresh• 64ms refresh period (8K Cycle)• 54 TSOP(II) Pb-free Package• RoHS compliantGENERAL DESCRIPTIONFEATURES16M x 4Bit x 4 Banks / 8M x 8Bit x 4 Banks / 4M x 16Bit x 4 Banks SDRAMOrdering InformationRow & Column address configurationOrganizationRow Address Column Address 64Mx4A0~A12A0-A9, A1132Mx8A0~A12A0-A916Mx16A0~A12A0-A8CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)54Pin TSOP(II) Package DimensionPackage Physical DimensionCMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)FUNCTIONAL BLOCK DIAGRAMLWE LDQMDQi* Samsung Electronics reserves the right to change products or specification without notice.CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)PIN CONFIGURATION (Top view)V DD N.C V DDQ N.C DQ0V SSQ N.C N.C V DDQ N.C DQ1V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/APA0A1A2A3V DD123456789101112131415161718192021222324252627545352515049484746454443424140393837363534333231302928V SS N.C V SSQ N.C DQ3V DDQ N.C N.C V SSQ N.C DQ2V DDQ N.C V SSN.C/RFU DQM CLK CKE A12A11A9A8A7A6A5A4V SS54Pin TSOP(400mil x 875mil)(0.8 mm Pin pitch)PIN FUNCTION DESCRIPTIONPin NameInput FunctionCLK System clock Active on the positive going edge to sample all inputs.CS Chip select Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQMCKEClock enableMasks system clock to freeze operation from the next clock cycle.CKE should be enabled at least one cycle prior to new command.Disable input buffers for power down in standby.A 0 ~ A 12AddressRow/column addresses are multiplexed on the same pins.Row address : RA 0 ~ RA 12,Column address : (x4 : CA 0 ~ CA 9,CA 11), (x8 : CA 0 ~ CA 9), (x16 : CA 0 ~ CA 8)BA 0 ~ BA 1Bank select address Selects bank to be activated during row address latch time.Selects bank for read/write during column address latch time.RAS Row address strobe Latches row addresses on the positive going edge of the CLK with RAS low.Enables row access & precharge.CAS Column address strobe Latches column addresses on the positive going edge of the CLK with CAS low.Enables column access.WE Write enableEnables write operation and row tches data in starting from CAS, WE active.DQM Data input/output mask Makes data output Hi-Z, t SHZ after the clock and masks the output.Blocks data input when DQM active.DQ 0 ~ N Data input/output Data inputs/outputs are multiplexed on the same pins.(x4 : DQ 0 ~ 3), (x8 : DQ 0 ~ 7), (x16 : DQ 0 ~ 15)V DD /V SS Power supply/ground Power and ground for the input buffers and the core logic.V DDQ /V SSQ Data output power/ground Isolated power supply and ground for the output buffers to provide improved noise immunity.N.C/RFUNo connection/reserved for future useThis pin is recommended to be left No Connection on the device.V DD DQ0V DDQ N.C DQ1V SSQ N.C DQ2V DDQ N.C DQ3V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ7V SSQ N.C DQ6V DDQ N.C DQ5V SSQ N.C DQ4V DDQ N.C V SSN.C/RFU DQM CLK CKE A12A11A9A8A7A6A5A4V SSV DD DQ0V DDQ DQ1DQ2V SSQ DQ3DQ4V DDQ DQ5DQ6V SSQ DQ7V DD LDQM WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ15V SSQ DQ14DQ13V DDQ DQ12DQ11V SSQ DQ10DQ9V DDQ DQ8V SSN.C/RFU UDQM CLK CKE A12A11A9A8A7A6A5A4V SSx16x8x4x16x8x4CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)ABSOLUTE MAXIMUM RATINGSParameter Symbol Value Unit Voltage on any pin relative to Vss V IN , V OUT -1.0 ~ 4.6V Voltage on V DD supply relative to Vss V DD , V DDQ-1.0 ~ 4.6V Storage temperature T STG -55 ~ +150°C Power dissipation P D 1W Short circuit currentI OS50mAPermanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Note :DC OPERATING CONDITIONSRecommended operating conditions (Voltage referenced to V SS = 0V, T A = 0 to 70°C) Parameter Symbol Min Typ Max Unit NoteSupply voltage V DD , V DDQ3.0 3.3 3.6V Input logic high voltage V IH 2.0 3.0V DD +0.3V 1Input logic low voltage V IL -0.300.8V 2Output logic high voltage V OH 2.4--V I OH = -2mA Output logic low voltage V OL --0.4V I OL = 2mAInput leakage currentI LI-10-10uA31. V IH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.2. V IL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.3. Any input 0V ≤ V IN ≤ V DDQ .Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.Notes :CAPACITANCE (V DD = 3.3V, T A = 23°C, f = 1MHz, V REF =1.4V ± 200 mV)PinSymbol Min Max Unit NoteClockC CLK 2.5 3.5pF RAS, CAS, WE, CS, CKE, DQM C IN 2.5 3.8pF AddressC ADD2.53.8pF (x4 : DQ 0 ~ DQ 3), (x8 : DQ 0 ~ DQ 7), (x16 : DQ 0 ~ DQ 15) C OUT4.06.0pFCMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)(Recommended operating condition unless otherwise noted, T A = 0 to 70°C)ParameterSymbolTest ConditionVersion Unit Note75Operating current (One bank active)I CC1 Burst length = 1 t RC ≥ t RC (min) I O = 0 mA80mA 1Precharge standby current in power-down mode I CC2P CKE ≤ V IL (max), t CC = 10ns 2mAI CC2PS CKE & CLK ≤ V IL (max), t CC = ∞2Precharge standby current in non power-down mode I CC2NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns20mAI CC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 10Active standby current in power-down mode I CC3PCKE ≤ V IL (max), t CC = 10ns6mA I CC3PS CKE & CLK ≤ V IL (max), t CC = ∞6Active standby current in non power-down mode (One bank active)I CC3N CKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns 25mA I CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25mAOperating current (Burst mode)I CC4 I O = 0 mA Page burst4banks Activated.t CCD = 2CLKs 100mA 1Refresh current I CC5t RC ≥ t RC (min)180mA 2Self refresh currentI CC6CKE ≤ 0.2VC 3mA 3L1.5mA41. Measured with outputs open.2. Refresh period is 64ms.3. K4S5604(08)32E-UC4. K4S5604(08)32E-UL5. Unless otherwise noticed, input swing level is CMOS(V IH /V IL =V DDQ /V SSQ ).Notes :DC CHARACTERISTICS (x4, x8)CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)(Recommended operating condition unless otherwise noted, T A = 0 to 70°C)ParameterSymbolTest ConditionVersion Unit Note6075Operating current (One bank active)I CC1Burst length = 1t RC ≥ t RC (min)I O = 0 mA14090mA 1Precharge standby current in power-down modeI CC2P CKE ≤ V IL (max), t CC = 10ns 2mA I CC2PS CKE & CLK ≤ V IL (max), t CC = ∞2Precharge standby current in non power-down mode I CC2N CKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns 20mAI CC2NS CKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 10Active standby current in power-down mode I CC3P CKE ≤ V IL (max), t CC = 10ns 6mA I CC3PS CKE & CLK ≤ V IL (max), t CC = ∞6Active standby current in non power-down mode (One bank active)I CC3N CKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns 25mA I CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25mAOperating current (Burst mode)I CC4I O = 0 mA Page burst4banks Activated.t CCD = 2CLKs 170130mA 1Refresh current I CC5t RC ≥ t RC (min)200180mA 2Self refresh currentI CC6CKE ≤ 0.2VC 3mA 3 L1.5mA41. Measured with outputs open.2. Refresh period is 64ms.3. K4S561632E-UC4. K4S561632E-UL5. Unless otherwise noticed, input swing level is CMOS(V IH /V IL =V DDQ /V SSQ ).Notes :DC CHARACTERISTICS (x16)CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)AC OPERATING TEST CONDITIONS (V DD = 3.3V ± 0.3V, T A = 0 to 70°C)Parameter Value Unit AC input levels (Vih/Vil)2.4/0.4V Input timing measurement reference level 1.4V Input rise and fall timetr/tf = 1/1ns Output timing measurement reference level 1.4VOutput load conditionSee Fig. 23.3V1200Ω870ΩOutput50pFV OH (DC) = 2.4V, I OH = -2mA V OL (DC) = 0.4V, I OL = 2mAVtt = 1.4V50ΩOutput50pFZ0 = 50Ω(Fig. 2) AC output load circuit(Fig. 1) DC output load circuit OPERATING AC PARAMETER(AC operating conditions unless otherwise noted)ParameterSymbol VersionUnit Note 6075Row active to row active delay t RRD (min)1215ns 1RAS to CAS delay t RCD (min)1820ns 1Row precharge time t RP (min)1820ns 1Row active time t RAS (min)4245ns 1t RAS (max)100us Row cycle timet RC (min)6065ns 1Last data in to row precharge t RDL (min)2CLK 2, 5Last data in to Active delayt DAL (min) 2 CLK + tRP-5Last data in to new col. address delay t CDL (min)1CLK 2Last data in to burst stopt BDL (min)1CLK 2Col. address to col. address delay t CCD (min)1CLK 3Number of valid output dataCAS latency=32ea4CAS latency=2-11. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle timeand then rounding off to the next higher integer.2. Minimum delay is required to complete write.3. All parts allow every cycle column address change.4. In case of row precharge interrupt, auto precharge and read burst stop.5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported. SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP .Notes :CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)DQ BUFFER OUTPUT DRIVE CHARACTERISTICSParameterSymbol ConditionMin TypMax Unit Notes Output rise time trh Measure in linear region : 1.2V ~ 1.8V 1.37 4.37Volts/ns 3 Output fall time tfh Measure in linear region : 1.2V ~ 1.8V 1.30 3.8Volts/ns 3 Output rise time trh Measure in linear region : 1.2V ~ 1.8V 2.8 3.9 5.6Volts/ns 1,2 Output fall timetfhMeasure in linear region : 1.2V ~ 1.8V2.02.9 5.0Volts/ns1,21. Rise time specification based on 0pF + 50 Ω to V SS , use these values to design to.2. Fall time specification based on 0pF + 50 Ω to V DD , use these values to design to.3. Measured into 50pF only, use these values to characterize to.4. All measurements done with respect to V SS .Notes :AC CHARACTERISTICS (AC operating conditions unless otherwise noted)ParameterSymbol 6075Unit Note Min Max Min Max CLK cycle time CAS latency=3t CC 610007.51000ns 1CAS latency=2-10CLK to valid output delay CAS latency=3t SAC 5 5.4ns 1,2CAS latency=2-6Output data hold timeCAS latency=3t OH 2.53ns 2CAS latency=2-3CLK high pulse width t CH 2.5 2.5ns 3CLK low pulse width t CL 2.5 2.5ns 3Input setup time t SS 1.5 1.5ns 3Input hold time t SH 10.8ns 3CLK to output in Low-Z t SLZ 11ns2CLK to output in Hi-ZCAS latency=3t SHZ5 5.4nsCAS latency=2-61. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Notes :CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)I OH Characteristics (Pull-up)Voltage 100MHz 133MHz Min 100MHz 133MHz Max 66MHz Min (V)I (mA)I (mA)I (mA)3.45 -2.43.3 -27.33.0 0.0 -74.1 -0.72.6-21.1-129.2 -7.52.4-34.1-153.3-13.32.0-58.7-197.0-27.51.8-67.3-226.2-35.5 1.65-73.0-248.0-41.11.5-77.9-269.7-47.91.4-80.8-284.3-52.41.0-88.6-344.5-72.50.0-93.0-502.4-93.0IBIS SPECIFICATIONI OL Characteristics (Pull-down)Voltage 100MHz 133MHz Min 100MHz 133MHz Max 66MHz Min (V)I (mA)I (mA)I (mA)0.0 0.0 0.0 0.00.427.5 70.217.7 0.6541.8107.526.9 0.8551.6133.833.31.058.0151.237.61.470.7187.746.61.572.9194.448.0 1.6575.4202.549.51.877.0208.650.7 1.9577.6212.051.53.080.3219.654.2 3.4581.4222.654.90-100-200-300-400-500-600030.511.522.53.5Voltagem A250200150100500030.511.522.53.5Voltagem A66MHz and 100MHz/133MHz Pull-up66MHz and 100MHz/133MHz Pull-downI OH Min (100MHz)I OH Max (66 and 100MHz)I OH Min (66MHz)I OL Min (100MHz)I OL Max (100MHz)I OL Min (66MHz)CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)V DD Clamp @ CLK, CKE, CS, DQM & DQV DD (V)I (mA)0.00.00.20.00.40.00.60.00.70.00.80.00.90.01.0 0.231.2 1.341.4 3.021.6 5.061.8 7.352.0 9.832.212.482.415.302.618.31V SS Clamp @ CLK, CKE, CS, DQM & DQV SS (V)I (mA)-2.6-57.23-2.4-45.77-2.2-38.26-2.0-31.22-1.8-24.58-1.6-18.37-1.4-12.56-1.2 -7.57-1.0 -3.37-0.9 -1.75-0.8 -0.58-0.7 -0.05-0.6 0.0-0.4 0.0-0.2 0.0 0.00.0201510500312Voltagem AI (mA)Voltagem AI (mA)Minimum V DD clamp current(Referenced to V DD )Minimum V SS clamp current0-10-20-30-40-30-2-1-50-60CMOS SDRAMRev. 1.3 August 2004SDRAM 256Mb E-die (x4, x8, x16)SIMPLIFIED TRUTH TABLE (V=Valid, X=Don't care, H=Logic high, L=Logic low)CommandCKEn-1CKEnCSRASCASWEDQMBA 0,1A 10/APA 0 ~ A 9 A 11, A 12NoteRegisterMode register set H X L L L L X OP code1,2RefreshAuto refreshH H L L L H X X 3Self refreshEntry L 3ExitL H L H H H X X3H X X X 3Bank active & row addr.H X L L H H X V Row address Read &column address Auto precharge disable H X L H L H X V L Column address 4Auto precharge enable H 4,5Write &column address Auto precharge disable H X L H L L X VL Column address4Auto precharge enableH 4,5Burst stop HX L H H L X X 6Precharge Bank selection H X L L H L X V L XAll banksX H Clock suspend or active power downEntry H L H X X X X XL V V V Exit L H X X X X X Precharge power down modeEntryH L H X X X XXL H H H ExitL HH X X X X L V V V DQMH X V X 7No operation commandHXH X X X XXLHHHNotes :1. OP Code : Operand codeA 0 ~ A 12 & BA 0 ~ BA 1 : Program keys. (@ MRS)2. MRS can be issued only at all banks precharge state.A new command can be issued after 2 CLK cycles of MRS.3. Auto refresh functions are as same as CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at all banks precharge state.4. BA 0 ~ BA 1 : Bank select addresses.If both BA 0 and BA 1 are "Low" at read, write, row active and precharge, bank A is selected. If BA 0 is "High" and BA 1 is "Low" at read, write, row active and precharge, bank B is selected. If BA 0 is "Low" and BA 1 is "High" at read, write, row active and precharge, bank C is selected. If both BA 0 and BA 1 are "High" at read, write, row active and precharge, bank D is selected. If A 10/AP is "High" at row precharge, BA 0 and BA 1 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at t RP after the end of burst.6. Burst stop command is valid at every burst length.7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)。

第8章 处理器核心电路设计和底层软件移植

L=27

CCCR[4:0] =00001

最终的CCCR寄存器的值应当配置为0x00000161

注二十页,共七十八页。

2. CKEN寄存器

CKEN(Clock Enable Register)寄存器是一个控制 外部设备时钟使能的寄存器。它对嵌入式系统的电量消 耗有着决定性的作用;对于那些没有用到的外设,应当 关闭其时钟供应。

现在你正浏览到当前第二十二页,共七十八页。

3. ICMR寄存器

ICMR(Interrupt Controller Mask Register) 寄存器是中断使能寄存器。1代表使能,0代表屏蔽 。

一般来说,PXA255处理器在Bootloader启动阶 段必须屏蔽所有中断,所以ICMR寄器应当设置为 0x00000000。

下面就以异步静态存储器(Flash)和同步动态存 储器(SDRAM)为例,说明PXA2XX系统的存储器扩展原 理。

7 现在你正浏览到当前第七页,共七十八页。

1.异步静态存储器接口设计原理 如图8-3所示,采用两片Intel的E28F128J3A-150

Flash芯片,构成了32 MB的F1ash存储器。这里的Flash 芯片是16位的,故采用两块并联的方法为处理器提供32 位的数据总线支持。

1. CCCR寄存器

CCCR(Core Clock Configuration Register)寄存器 控制着内存、LCD、DMA控制器所使用的时钟。这些时钟都 是由处理器的3.6864MHz钟振倍频上去的,控制倍频比例的 参数有三个,见表4-2。

表8-2 CCCR控制倍频比例的参数

名称

使用方法

MSCx十分重要,因为它记录了有关于存储器的几个重要参数 ,见P197表8-4所列。

u-boot设计文档

u-boot 设计文档1. 引言u-boot是bootloader成员中一种应用普遍,功能强大,极具代表意义的引导程序。

在嵌入式开发中起着举足轻重的作用。

U-boot是一段运行于内核之前的代码,为内核的启动初始化硬件环境并提供必需的参数,引导内核运行。

总之,u-boot的基本工作就是能够成功得引导内核运行。

一般情况下u-boot映像,内核和根文件系统映像都存储在Flash上。

也就是说开发板是从Nor Flash启动的。

但考虑到Nor flash容量小,价格高的因素,而Nand Flash 有更高的性价比,增加了从Nand Flash启动的功能。

2. 目标实现初始化开发板硬件环境,为启动内核提供硬件平台参数,引导内核启动的基本功能。

实现Nor/Nand Flash两种启动模式。

3. u-boot启动流程分析为了能够更好的移植u-boot到新的开发板上,有必要掌握u-boot的启动流程。

借助u-boot 启动流程图,简单介绍u-boot的启动过程。

考虑到执行效率和代码的扩展性和灵活性,一般情况把u-boot启动过程分为两个阶段。

第一阶段代码由汇编实现,这是u-boot一开始就执行的操作,其目的是为第二阶段的执行以及随后的kernel 的执行准备好一些基本的硬件环境。

通常包括以下步骤:硬件设备初始化;为加载u-boot第二阶段准备RAM 空间;拷贝u-boot第二阶段代码到RAM空间中;设置好堆栈;跳转到第二阶段的C 入口点。

第二阶段用c语言编写,用以实现复杂的功能。

通常包括以下步骤:初始化本阶段要使用到的硬件设备;检测系统内存映射(memory map);将kernel 映像和根文件系统映像从flash上读到RAM 空间中;为内核设置启动参数;调用内核。

4. u-boot移植U-Boot能够支持多种体系结构的处理器,支持的开发板也越来越多。

因为系统引导程序是完全依赖硬件平台的,所以在新电路板上需要移植U-Boot程序。

SDRAM K4S561632C-TC75 (32MB)介绍

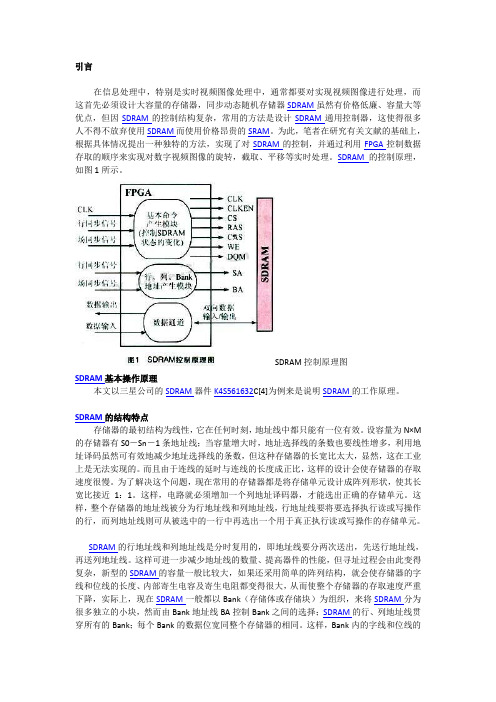

引言在信息处理中,特别是实时视频图像处理中,通常都要对实现视频图像进行处理,而这首先必须设计大容量的存储器,同步动态随机存储器SDRAM虽然有价格低廉、容量大等优点,但因SDRAM的控制结构复杂,常用的方法是设计SDRAM通用控制器,这使得很多人不得不放弃使用SDRAM而使用价格昂贵的SRAM。

为此,笔者在研究有关文献的基础上,根据具体情况提出一种独特的方法,实现了对SDRAM的控制,并通过利用FPGA控制数据存取的顺序来实现对数字视频图像的旋转,截取、平移等实时处理。

SDRAM的控制原理,如图1所示。

SDRAM控制原理图SDRAM基本操作原理本文以三星公司的SDRAM器件K4S561632C[4]为例来是说明SDRAM的工作原理。

SDRAM的结构特点存储器的最初结构为线性,它在任何时刻,地址线中都只能有一位有效。

设容量为N×M 的存储器有S0-Sn-1条地址线;当容量增大时,地址选择线的条数也要线性增多,利用地址译码虽然可有效地减少地址选择线的条数,但这种存储器的长宽比太大,显然,这在工业上是无法实现的。

而且由于连线的延时与连线的长度成正比,这样的设计会使存储器的存取速度很慢。

为了解决这个问题,现在常用的存储器都是将存储单元设计成阵列形状,使其长宽比接近1:1。

这样,电路就必须增加一个列地址译码器,才能选出正确的存储单元。

这样,整个存储器的地址线被分为行地址线和列地址线,行地址线要将要选择执行读或写操作的行,而列地址线则可从被选中的一行中再选出一个用于真正执行读或写操作的存储单元。

SDRAM的行地址线和列地址线是分时复用的,即地址线要分两次送出,先送行地址线,再送列地址线。

这样可进一步减少地址线的数量、提高器件的性能,但寻址过程会由此变得复杂,新型的SDRAM的容量一般比较大,如果还采用简单的阵列结构,就会使存储器的字线和位线的长度、内部寄生电容及寄生电阻都变得很大,从而使整个存储器的存取速度严重下降,实际上,现在SDRAM一般都以Bank(存储体或存储块)为组织,来将SDRAM分为很多独立的小块,然而由Bank地址线BA控制Bank之间的选择;SDRAM的行、列地址线贯穿所有的Bank;每个Bank的数据位宽同整个存储器的相同。

5616中文资料

5616中文资料56162-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCKU E D P R O D UCT E F E R E N C E O N LY 2-FUNCTION, 4-DIGITLCD AUTOMOTIVE CLOCK—PROGRAMMABLEThe SCL5616HW is a 2-function digital automotive clock circuit.Fabricated on a single monolithic chip using silicon-gate CMOS PROM technology, it offers low cost, low power, and high reliability. It also includes digital frequency correction, stored in the internal nonvolatile memory, for easy adjustment of the oscillator nominal frequency.The SCL5616HW is supplied in wafer form and is rated for continuous operation over the automotive temperature range of -40°C to +85°C.FEATURESs Digital Tuning of Crystal Frequencys PROM for Storing Frequency Correction Information s 12 or 24 Hour Timekeeping Option s Flashing Colons Two Switches Control All Setting Functions s High Noise Immunitys Internal Power-Up Reset Circuitry s Internal Voltage RegulationAlways order by complete part number:SCL5616HW .5616Data Sheet 2611056162-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCK115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000WCopyright ? 1990, 1995, Allegro MicroSystems, Inc.56162-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCKLimitsCharacteristicSymbol Test Conditions Min.Typ.Max. Units Operating Voltage Range V DD T A = +25°C 4.5——V Zener Voltage V DD I DD = 1.0 mA5.5—6.8V Segment Output CurrentI OUT V DD = 5.0 V, V OUT = 4.8 V -20——μA V DD = 5.0 V, V OUT = 0.2 V120——μA Backplane Output CurrentI OUT V DD = 5.0 V, V OUT = 4.8 V -80——μA V DD = 5.0 V, V OUT = 0.2 V240——μA LCD Drive Signal V DISP V DD ≥5.0 V4.0——V Input Current I IN S1, S2, DATA, or SELECT-55—-700μA Oscillator Frequency f OSC — 4.194 304—MHz Oscillator Starting Time t OSC V DD = Zener voltage ——200ms Oscillator Stability ?f OSC ?V DD = ±100 mV ——±1.0ppM Backplane Frequency f BP —64—Hz Switch Debounce Time t DB 0—62.5ms Osc. Feedback Resistance R OSC —16—M ?Osc. Input Capacitance C OSCI —15—pF Osc. Output Capacitance C OSCO —30—pF Supply CurrentI DDV DD = 5.0 V ——1.0mANOTE: Negative current is defined as coming out of (sourcing) the specified device terminal.ELECTRICAL CHARACTERISTICS at T A = -40°C to +85°C, in Typical Application (unless otherwise noted).DISPLAY FORMATa1a2a3a4d1d2d3d4g1g2g3g4b2b4b1b3c1c3c4e1e2e4f2f4f3Dwg. No. OC-00156162-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCK115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000FUNCTIONAL DESCRIPTIONDATA Logic Levels are V DD and GroundPower-Up Reset. When power up occurs, the hours and minutes counters are reset, and the clock starts running:Operation12-Hour mode and counting starts from 1:00 AMProgramming Modes. Data is loaded by pulling DATA low (1 μs pulse duration) n times to set the desired bits for frequency correction into the data input register. This information is latched in the RAM, thus allowing the testing of the oscillator frequency adjustment withoutstoring the selected pattern in the PROM cells. The data latched in the RAM is stored in the PROM cells when DATA is held low for a mini-mum of 10 ms.The data stored in the data input register is cleared on any SELECT transition (low to high or high to low). It is also cleared when theprogram power voltage (V PP ) is reduced from 18 V to V DD . Clearing the data input register does not affect the data latched in the RAM.Program DATA SELECT V PP V D V S Operation18 V Pulse Ground DATA load for frequency correction 18 V Ground V DD DATA storeV DDV DDGroundVerify stored dataFREQUENCY CORRECTIONDwg. No. WC-001-1VERIFY CYCLE (V = V )t DHPLt PLSXt SVDLt DLHt wD V PPV DV St PHDLt SHDXt SLDVV SPP DD SEGMENT OUTPUTSt DHL 123FREQUENCY CORRECTION 127 M A X56162-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCKS1S2IGNITION OperationOpen Open X Clock running X X Ground Setting disabled Ground Open 12 V Set hours Open Ground 12 V Set Minutes Ground Ground12 VChange counting sequence (12 to 24 hour or 24 to 12 hour) Frequency Correction. The on-chip oscillator circuit increasesthe crystal frequency approximately 40 ppm. This ensures that the typical crystal will operate within the tuning range. With V S at ground, data pulses are then used to trim the internal clock frequency by 2 to 254ppm to the required value. The quantity of data pulses needed (1 to 127) isn = f BP - 64 128 x 10-6where f BP is the measured frequency at BACKPLANE. Prior to trim-ming, it must be between 64.000 128 Hz and 64.016 256 Hz.X = Irrelevant, ground or 12 VClock Running Mode. During the clock running mode, settingfunctions are achieved by either momentary or continuous operation of switches S1 and S2, which are enabled by IGNITION. Hours or minutes are incremented on S1 or S2 (respectively) depression and continue at a 1 Hz rate while the switch is depressed.X = Irrelevant, ground or 12 V for IGNITION, ground or open for S1 and S2Diagnostic Mode. To enter the diagnostic mode, S1 and S2 are oper-ated with IGNITION connected to 12 V. All segments are displayed for as long as S1 and S2 are depressed. On opening S1 and S2, the clock will leave the diagnostic mode and go through a power-up sequence.In the SCL5616HW, the counting sequence will change (from 12 hour to 24 hour or from 24 hour to 12 hour). To inhibit the power-up reset,hold the DATA input low (ground). The counting mode will change without resetting the hours or minutes counters.Program SELECT V PP V S S1S2IGNITION Mode V DD V DD Open Open X Clock running V DD V DD Ground Ground 12 V Diagnostic 18 VGroundOpenOpenXProgrammingOperating Modes. The operating modes of the clock are controlled by the voltages applied to V PP , SELECT, IGNITION, and switches S1and S2.56162-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCK115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Frequency Selection Pulses 6432168421Segmentb4c4d4e4c3e3c2CharacteristicSymbol Min.Max.Units PROGRAM High (18 V) to DATA Low t PHDL 1.0—μs SELECT Valid to DATA Low t SVDL 25—μs DATA Low to DATA High t DLH1.0 1.5μs DATA High to DATA Low t DHL1.0—μs DATA Store Pulse Duration t wD 10—ms DATA High to PROGRAM Low t DHPL 1.0—μs PROGRAM Low to SELECT Change t PLSX 1.0—μs SELECT Low (Verify) to DATA Valid t SLDV —1.0μs DATA Hold from End of Verifyt SHDX—10nsRECOMMENDED FLASHPROGRAMMING CHARACTERISTICSat T A = +25°C, Logic Levels are V DD and Ground(except PROGRAM High)Stored Data Verification. In the verify mode, the complement value of the information stored in the PROM cells is brought out directly to the segment output terminals for easy verification of the stored data.If a bit is programmed (high), the appropriate segment output is turned ON (low). The segments represent the binary equivalent of the number of frequency correction data pulses entered.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improve-ments in the design of its products.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems,Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.。

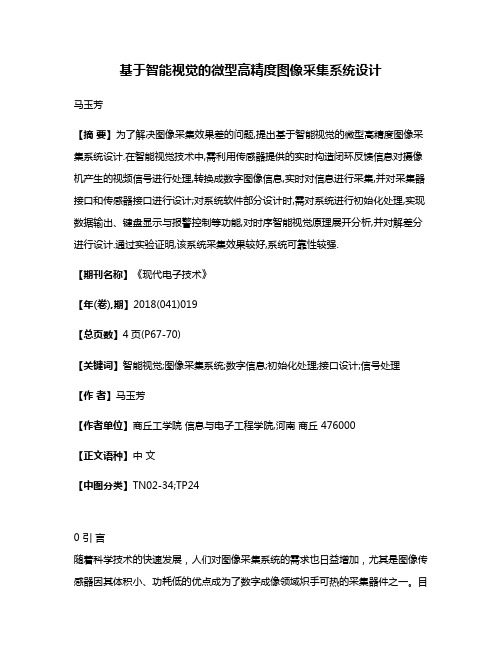

基于智能视觉的微型高精度图像采集系统设计

基于智能视觉的微型高精度图像采集系统设计马玉芳【摘要】为了解决图像采集效果差的问题,提出基于智能视觉的微型高精度图像采集系统设计.在智能视觉技术中,需利用传感器提供的实时构造闭环反馈信息对摄像机产生的视频信号进行处理,转换成数字图像信息,实时对信息进行采集,并对采集器接口和传感器接口进行设计;对系统软件部分设计时,需对系统进行初始化处理,实现数据输出、键盘显示与报警控制等功能,对时序智能视觉原理展开分析,并对解差分进行设计.通过实验证明,该系统采集效果较好,系统可靠性较强.【期刊名称】《现代电子技术》【年(卷),期】2018(041)019【总页数】4页(P67-70)【关键词】智能视觉;图像采集系统;数字信息;初始化处理;接口设计;信号处理【作者】马玉芳【作者单位】商丘工学院信息与电子工程学院,河南商丘 476000【正文语种】中文【中图分类】TN02-34;TP240 引言随着科学技术的快速发展,人们对图像采集系统的需求也日益增加,尤其是图像传感器因其体积小、功耗低的优点成为了数字成像领域炽手可热的采集器件之一。

目前图像采集器集成的转换电路一般为8 bit,这样的精准度可满足一般图像成像原理,但如果应用系统对图像采集精准度要求较高时,由于传统采集系统存在采集效果差的问题就显得力不从心[1]。

为此,根据实际指标,需采集更高精度的图像,为此本文提出基于智能视觉的微型高精度图像采集系统设计。

设计以智能视觉采集芯片为主控系统,结合微型高精度LM98640实现对图像传感器信号的采集。

在智能视觉技术中,需利用传感器提供的实时构造闭环反馈信息对摄像机产生的视频信号进行处理,实时对信息进行采集,并对采集器接口和传感器接口进行设计;对系统软件部分设计时,需对系统进行初始化处理,实现数据输出、键盘显示与报警控制等功能,并重点研究时序设计和后续图像信号采集处理,同时给出相关时序设计仿真波形,由此呈现出实际成像效果。

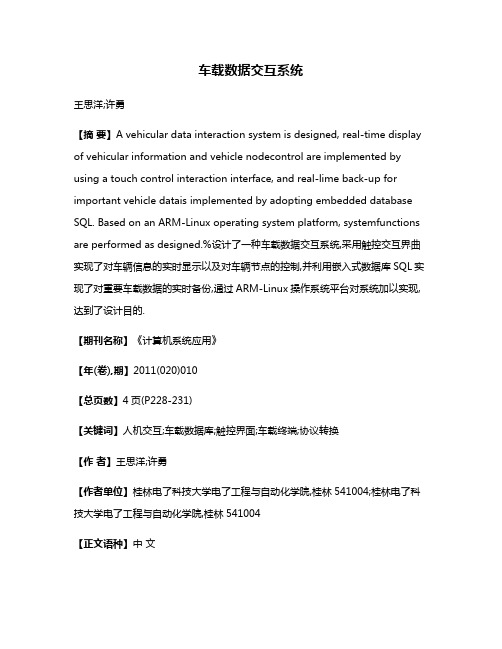

车载数据交互系统

车载数据交互系统王思洋;许勇【摘要】A vehicular data interaction system is designed, real-time display of vehicular information and vehicle nodecontrol are implemented by using a touch control interaction interface, and real-lime back-up for important vehicle datais implemented by adopting embedded database SQL. Based on an ARM-Linux operating system platform, systemfunctions are performed as designed.%设计了一种车载数据交互系统,采用触控交互界曲实现了对车辆信息的实时显示以及对车辆节点的控制,并利用嵌入式数据库SQL实现了对重要车载数据的实时备份,通过ARM-Linux操作系统平台对系统加以实现,达到了设计目的.【期刊名称】《计算机系统应用》【年(卷),期】2011(020)010【总页数】4页(P228-231)【关键词】人机交互;车载数据库;触控界面;车载终端;协议转换【作者】王思洋;许勇【作者单位】桂林电了科技大学电了工程与自动化学院,桂林541004;桂林电了科技大学电了工程与自动化学院,桂林541004【正文语种】中文随着汽车技术的日新月异,汽车正朝着电子化、智能化和网络化发展,汽车功能将越来越强大,车内装备的运行监控和调度管理也越来越复杂,这要求驾驶员需要更多地掌握车内动态数据信息以进行相应的控制[1]。

传统方式安排的各种开关、功能键和显示仪表已经难以适应这种变化。

为此,设计了一种车载数据交互系统,该系统通过触控平台快捷地为驾驶员提供车辆信息和相应的触控界面,极大地方便了驾驶员对汽车的操作[2]。

一种新型移动保密存储设备

一种新型移动保密存储设备熊玉朋;陈兴欣;庞俊锐【摘要】现有移动存储设备为人们工作带来极大方便的同时也带来了极大的失泄密隐患和管理上的难题,这是由于存储介质本身一经涉密终生涉密、数据易被恢复;而且设备工作于通用的文件管理系统下,摆渡攻击现象大量存在,因此使用现有移动存储设备无法保证非保密网与保密网之间的信息交换的安全性.刻录光盘在一定程度上解决了问题,但累计成本高,工作效率低下.针对以上情况,为了解决因移动存储设备的使用而造成的物理隔离网络间信息交换的安全性问题,提出了以FPGA为控制核心和SDRAM为存储介质,USB为传输端口制作新型移动保密存储器的设想,进行了硬件的选择与软件的设计,并完成了原理样机的制作.原理样机实现了预期设想,可以安全、高效、稳定地进行物理隔离网络之间的信息传输.创新之处在于应用SDRAM为存储介质,同时考虑软件和硬件,确保安全保密.【期刊名称】《现代电子技术》【年(卷),期】2010(033)005【总页数】3页(P89-91)【关键词】移动存储设备;FPGA;USB 2.0;SDRAM;通信协议【作者】熊玉朋;陈兴欣;庞俊锐【作者单位】国防科学技术大学,光电科学与工程学院,湖南,长沙,410073;国防科学技术大学,光电科学与工程学院,湖南,长沙,410073;国防科学技术大学,光电科学与工程学院,湖南,长沙,410073【正文语种】中文【中图分类】TP3090 引言现有移动存储设备的广泛使用极大方便了工作和生活,但不可否认的是移动存储设备的广泛使用也带来了失密、泄密问题。

经过调研发现,这是由于现有移动存储设备自身的工作机理引起的,例如U盘以FLASH为存储介质,存在数据不能彻底清除、易被恢复等数据安全问题,设备丢失也是泄密的隐患;同时由于现有移动存储设备大多使用Windows的通用驱动和通用文件管理系统,为摆渡病毒的攻击提供了便利条件,使摆渡攻击大量存在;另外,现有移动存储设备数据的拷贝过程难于监管,无意泄密和有意泄密事件大量存在,且管理上的难度较大。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CLK ADD

Column Decoder Col. Buffer Latency & Burst Length

LRAS

LCBR

LCKE LRAS LCBR LWE LCAS

Programming Register LWCBR LDQM

Timing Register

CLK

CKE

CS

RAS

CAS

WE

L(U)DQM

VDD DQ0 VDDQ DQ1 DQ2 VSSQ DQ3 DQ4 VDDQ DQ5 DQ6 VSSQ DQ7 VDD LDQM WE CAS RAS CS BA0 BA1 A10/AP A0 A1 A2 A3 VDD 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 VSS DQ15 VSSQ DQ14 DQ13 VDDQ DQ12 DQ11 VSSQ DQ10 DQ9 VDDQ DQ8 VSS N.C/RFU UDQM CLK CKE A12 A11 A9 A8 A7 A6 A5 A4 VSS

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.4 Sept. 2001

元器件交易网

K4S561632C

PIN CONFIGURATION (Top view)

VDD/VSS VDDQ/VSSQ N.C/RFU

Rev. 0.4 Sept. 2001

元器件交易网

K4S561632C

ABSOLUTE MAXIMUM RATINGS

Parameter Voltage on any pin relative to Vss Voltage on VDD supply relative to Vss Storage temperature Power dissipation Short circuit current Symbol VIN, VOUT VDD, VDDQ TSTG PD IOS Value -1.0 ~ 4.6 -1.0 ~ 4.6 -55 ~ +150 1 50

Rev. 0.4 Sept. 2001

元器件交易网

K4S561632C

Revision History Revision 0.1 (Feb. 15, 2001)

• Added DC charcteristics.

CMOS SDRAM

Revision 0.2 (Mar. 06, 2001)

ORDERING INFORMATION

Max Freq. 166MHz(CL=3) 133MHz(CL=2) 133MHz(CL=3) 100MHz(CL=2) 100MHz(CL=3) LVTTL 54pin TSOP(II) Interface Package

FUNCTIONAL BLOCK DIAGRAM

I/O Control

LWE

Data Input Register

LDQM

Bank Select 4M x 16 4M x 16 4M x 16 4M x 16 Refresh Counter

Output Buffer

Row Decoder

Sense AMP

Row Buffer

DQi

Address RegistERAL DESCRIPTION

The K4S561632C is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 4,196,304 words by 16 bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

• Deleted "Preliminary" • Changed DC charcteristics

Revision 0.3 (Jun 04, 2001)

• Corrected typo in DC characteristics

Revision 0.4 (Sep. 06, 2001)

• • Redefined IDD1 & IDD4 in DC Characteristics Changed the Notes in Operating AC Parameter. < Before > 5. For 1H/1L, tRDL=1CLK and tDAL=1CLK+tRP is also supported . SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP. < After > 5.In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported. SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP.

元器件交易网

K4S561632C

CMOS SDRAM

256Mbit SDRAM

4M x 16bit x 4 Banks Synchronous DRAM LVTTL

Revision 0.4 Sept. 2001

* Samsung Electronics reserves the right to change products or specification without notice.

CKE

Clock enable

A0 ~ A12 BA0 ~ BA1 RAS CAS WE L(U)DQM DQ0 ~

15

Address Bank select address Row address strobe Column address strobe Write enable Data input/output mask Data input/output Power supply/ground Data output power/ground No connection /reserved for future use

CMOS SDRAM

54Pin TSOP (II) (400mil x 875mil) (0.8 mm Pin pitch)

PIN FUNCTION DESCRIPTION

Pin CLK CS Name System cock Chip select Input Function Active on the positive going edge to sample all inputs. Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQM Masks system clock to freeze operation from the next clock cycle. CKE should be enabled at least one cycle prior to new command. Disable input buffers for power down in standby. Row/column addresses are multiplexed on the same pins. Row address : RA0 ~ RA12, Column address : CA0 ~ CA8 Selects bank to be activated during row address latch time. Selects bank for read/write during column address latch time. Latches row addresses on the positive going edge of the CLK with RAS low. Enables row access & precharge. Latches column addresses on the positive going edge of the CLK with CAS low. Enables column access. Enables write operation and row precharge. Latches data in starting from CAS, WE active. Makes data output Hi-Z, tSHZ after the clock and masks the output. Blocks data input when L(U)DQM active. Data inputs/outputs are multiplexed on the same pins. Power and ground for the input buffers and the core logic. Isolated power supply and ground for the output buffers to provide improved noise immunity. This pin is recommended to be left No Connection on the device.