TDA7473A;中文规格书,Datasheet资料

SN7473中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9675101QCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC 5962-9675101QDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NC 5962-9675101QDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NC 5962-9675101VCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC 5962-9675101VCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC 5962-9675101VDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NC 5962-9675101VDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NC SN54LS73AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN54LS73AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN7473N OBSOLETE PDIP N14TBD Call TI Call TISN7473N OBSOLETE PDIP N14TBD Call TI Call TISN7473N3OBSOLETE PDIP N14TBD Call TI Call TISN7473N3OBSOLETE PDIP N14TBD Call TI Call TISN74LS73AD ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73AD ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73ADE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73ADE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73ADR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73ADR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73ADRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73ADRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS73AN ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS73AN ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS73ANE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS73ANE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SNJ54LS73AFD OBSOLETE LCCC FK20TBD Call TI Level-NC-NC-NC SNJ54LS73AFD OBSOLETE LCCC FK20TBD Call TI Level-NC-NC-NC SNJ54LS73AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54LS73AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54LS73AW ACTIVE CFP W141TBD Call TI Level-NC-NC-NC SNJ54LS73AW ACTIVE CFP W141TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

AO4803A;中文规格书,Datasheet资料

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

Gate-Source Voltage

VGS

Continuous Drain

TA=25°C

Current

TA=70°C

Pulsed Drain Current C

Avalanche Current C

Avalanche energy L=0.1mH C

ID

IDM IAS, IAR EAS, EAR

TA=25°C Power Dissipation B TA=70°C

PD

Junction and Storage Temperature Range

TJ, TSTG

Maximum -30 ±20 -5 -4 -30 17 14 2 1.3

7473中文资料

© 2000 Fairchild Semiconductor Corporation DS006525September 1986Revised February 2000DM7473 Dual Master-Slave J-K Flip-Flops with Clear and Complementary OutputsDM7473Dual Master-Slave J-K Flip-Flopswith Clear and Complementary OutputsGeneral DescriptionThis device contains two independent positive pulse trig-gered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flops after a complete clock pulse. While the clock is LOW the slave is isolated from the master. On the positive transition of the clock, the data from the J and K inputs is transferred to the master. While the clock is HIGH the J and K inputs are disabled. On the negative transition of the clock, the data from the master is transferred to the slave. The logic states of the J and K inputs must not be allowed to change while the clock is HIGH. Data transfers to the outputs on the falling edge of the clock pulse. A LOW logic level on the clear input will reset the outputs regardless of the logic states of the other inputs.Ordering Code:Connection Diagram Function TableH = HIGH Logic Level L = LOW Logic LevelX = Either LOW or HIGH Logic Level= Positive pulse data. the J and K inputs must be held constant whilethe clock is HIGH. Data is transferred to the outputs on the falling edge of the clock pulse.Q 0 = The output logic level before the indicated input conditions wereestablished.Toggle = Each output changes to the complement of its previous level oneach HIGH level clock pulse.Order Number Package NumberPackage DescriptionDM7473NN14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WideInputsOutputsCLR CLK J K Q Q L XX X L H H L L Q 0Q 0H H L H L H L H L HHHHToggle 2D M 7473Absolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsNote 2: The symbol (↑, ↓) indicates the edge of the clock pulse is used for reference: (↑) for rising edge, (↓) for falling edge.Note 3: T A = 25°C and V CC = 5V.Electrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 4: All typicals are at V CC = 5V, T A = 25°C.Note 5: Not more than one output should be shorted at a time.Note 6: With all outputs OPEN, I CC is measured with the Q and Q outputs HIGH in turn. At the time of measurement the clock input grounded.Switching Characteristics at V CC = 5V and T A = 25°CSupply Voltage 7V Input Voltage5.5VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range−65°C to +150°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −0.4mA I OL LOW Level Output Current 16mA f CLK Clock Frequency (Note 3)015MHzt WPulse Width Clock HIGH 20(Note 3)Clock LOW 47nsClear LOW25t SU Input Setup Time (Note 2)(Note 3)0↑ns t H Input Hold Time (Note 2)(Note 3)0↓ns T AFree Air Operating Temperature70°C Symbol Parameter Conditions MinTyp (Note 4)Max Units V I Input Clamp Voltage V CC = Min, I I = −12 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max 2.43.4V Output Voltage V IL = Max, V IH = Min V OL LOW Level V CC = Min, I OL = Max 0.20.4V Output Voltage V IH = Min, V IL = Max I I Input Current @ Max Input Voltage V CC = Max, V I = 5.5V1mAI IHHIGH Level V CC = Max J, K 40Input CurrentV I = 2.4V Clock 80µAClear 80I ILLOW Level Input V CC = Max J, K −1.6CurrentV I = 0.4VClock −3.2mA Clear−3.2I OS Short Circuit Output Current V CC = Max (Note 5)−18−55mA I CCSupply CurrentV CC = Max, (Note 6)1834mA Symbol ParameterFrom (Input)R L = 400Ω, C L = 15 pF Units To (Output)Min Maxf MAX Maximum Clock Frequency15MHz t PHL Propagation Delay Time HIGH-to-LOW Level Output Clear to Q 40ns t PLH Propagation Delay Time LOW-to-HIGH Level Output Clear to Q 25ns t PHL Propagation Delay Time HIGH-to-LOW Level Output Clock to Q or Q 40ns t PLHPropagation Delay Time LOW-to-HIGH Level OutputClock to Q or Q 25ns3DM7473 Dual Master-Slave J-K Flip-Flops with Clear and Complementary OutputsPhysical Dimensions inches (millimeters) unless otherwise noted14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N14AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

HT7133A中文资料

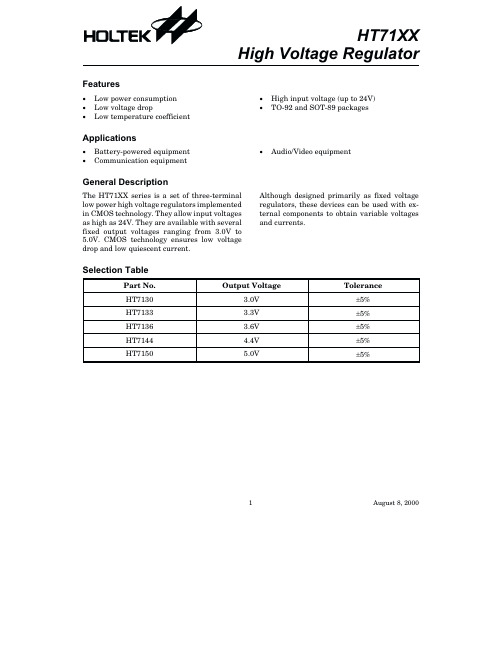

HT71XXHigh Voltage RegulatorSelection TablePart No.Output VoltageToleranceHT7130 3.0V ±5%HT7133 3.3V ±5%HT7136 3.6V ±5%HT7144 4.4V ±5%HT71505.0V±5%1August 8,2000Features·Low power consumption ·Low voltage drop·Low temperature coefficient·High input voltage (up to 24V)·TO-92and SOT-89packagesApplications·Battery-powered equipment ·Communication equipment·Audio/Video equipmentGeneral DescriptionThe HT71XX series is a set of three-terminal low power high voltage regulators implemented in CMOS technology.They allow input voltages as high as 24V.They are available with several fixed output voltages ranging from 3.0V to 5.0V.CMOS technology ensures low voltage drop and low quiescent current.Although designed primarily as fixed voltage regulators,these devices can be used with ex-ternal components to obtainvariable voltages and currents.Block DiagramPin AssignmentPad Assignment Pad CoordinatesUnit:m m Pad No.X Y 1-480.00-451.50287.50-444.503482.00-444.50Chip size:1374´1294(m m)2*The IC substrate should be connected to VDD in the PCB layout artwork.2August 8,2000Absolute Maximum RatingsSupply Voltage..............................-0.3V to28V Storage Temperature................-50°C to125°C Power Consumption.............................200mW Operating Temperature.................0°C to70°CNote:These are stress ratings only.Stresses exceeding the range specified under Absolute Maxi-mum Ratings may cause substantial damage to the device.Functional operation of this de-vice at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.Electrical CharacteristicsHT7130,+3.0V output typeHT7133,+3.3V output type Ta=25°C3August8,2000HT7144,+4.4V output type Ta=25°C4August8,2000Application CircuitsBasic circuits5August8,2000High output current positive voltage regulatorShort-Circuit protection by Tr1Circuit for increasing output voltageV V (1+R2R1)I R2OUT XX SS =+HT71XX6August 8,2000Circuit for increasing output voltageV OUT=V XX+V D1 Constant current regulatorI VR IOUTXXA SS=+Dual supply7August8,20008August 8,2000Copyright Ó2000by HOLTEK SEMICONDUCTOR INC.The information appearing in this Data Sheet is believed to be accurate at the time of publication.However,Holtek assumes no responsibility arising from the use of the specifications described.The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification,nor recommends the use of its products for application that may pres-ent a risk to human life due to malfunction or otherwise.Holtek reserves the right to alter its products without prior notification.For the most up-to-date information,please visit our web site at .Holtek Semiconductor Inc.(Headquarters)No.3Creation Rd.II,Science-based Industrial Park,Hsinchu,Taiwan,R.O.C.Tel:886-3-563-1999Fax:886-3-563-1189Holtek Semiconductor Inc.(Taipei Office)5F,No.576,Sec.7Chung Hsiao E.Rd.,Taipei,Taiwan,R.O.C.Tel:886-2-2782-9635Fax:886-2-2782-9636Fax:886-2-2782-7128(International sales hotline)Holtek Semiconductor (Hong Kong)Ltd.RM.711,Tower 2,Cheung Sha Wan Plaza,833Cheung Sha Wan Rd.,Kowloon,Hong Kong Tel:852-2-745-8288Fax:852-2-742-8657。

大功率AB类音频放大器资料(pdf 10页)

TDA、LM系列大功率AB类音频放大器资料型号输出功率1输出功率2声道数封装工作电压输出电流TDA735022W1MW1118V5ATDA736022W1MW1118V5ATDA73656W2MW1518V4ATDA7370 6.5W20W4MW1518V 4.5A TDA73726W不支持BTL4MW1518V4ATDA737421W2MW1518V 4.5A TDA737535W2MW1518V 4.5A TDA7376B35W2MW1518V 4.5A TDA73776W30W4MW1518V 4.5A TDA737913W38W4MW1522V5ATDA738125W4FW2518V4ATDA738222W4FW2518V 5.5A TDA738330W4FW2518V 5.5A TDA738435W4FW2518V 5.5A TDA738530W4FW2518V 5.5A TDA738640W4FW2518V 5.5A TDA738841W4FW2518V 5.5A TDA7388A42W4FW2718V 5.5A TDA738945W4FW2518V 5.5A TDA739135W1MW1118V6ATDA739332W2MW1518V 5.5A TDA739430W2MW1518V 5.5A TDA739645W1MW1118V7ATDA74517W22W4FW2518V4ATDA745435W4FW2518V8ATDA748010W(D类)1DIP-20±20V5ATDA748118W(D类)1MW15±25V5ATDA748225W(D类)1MW15±28V5ATDA749025W(D类)50W2FW25±30V5ATDA749410W1MW1535V 1.9A TDA749511W2MW1535V 2.4A TDA74965W2MW1535V 1.3A TDA7497S8W+8W+15W3MW1535V2A+2.5A TDA74996W2MW11±20V 2.5A TDA756045W(DMOS)4FW2518V10ATDA756135W(DMOS)4FW2518V8ATDA756235W(DMOS)4FW2718V8ATDA756340W(DMOS)4FW2718V8ATDA756445W(DMOS)4FW2518V8ATDA756640W(DMOS)4FW2518V8ATDA757540W(DMOS)2PowerSO3618V8ATDA785050W(DMOS)4FW2518V10A TDA7850LV50W(DMOS)4FW25MIN6V10A TDA7851A45W(DMOS)4FW2718V10A TDA7851F45W(DMOS)4FW2518V10A TDA785447W(DMOS)4FW2518V10A TDA2009A10W18W2MW1128V 4.5A TDA2030A18W34W1TO220-5±22V 3.5A TDA204020W30W1TO220-5±20V4ATDA205032W1TO220-5±25V5ATDA205140W1TO220-5±25V6ATDA205260W1TO220-7±25V6ATDA726425W2MW8/11±20V 4.5A TDA726525W2MW11±25V 4.5A TDA726910W2MW11±22V3ATDA729240W2MW11±35V5ATDA7293100W200W(HE)1MW15±50V10A TDA7294100W170W(HE)1MW15±40V10A TDA729580W100W BTL1MW15±40V6ATDA729660W60W BTL1MW15±35V5ATDA729720W BTL2MW1520V2ATDA74965W2MW1535V 1.3A LM387660W45W1MW11±42V6ALM187623W20W2MW15±32V 3.5A LM287645W8欧75W Peak1MW11±35V4ALM387545W56W1MW11±42V6ALM187520W25W1TO220-5±30V4ALM388668W63W1MW11±42V11.5A LM476522W30W2MW15±32V 3.5A LM476642W26W2MW15±37V4ALM478060W55W2FW27±42V11.5A LM478135W25W3FW27±35V4ALM478232W25W3FW27±32V 3.5A注:1.这里的“输出功率1”对于TDA系列是指EIAJ标准的输出,对于LM系列是指4欧姆负载,THD=1%时的输出功率,“输出功率2”对于TDA系列是指BTL输出的功率,对于LM系列是指8欧姆负载,THD=1%时的输出功率。

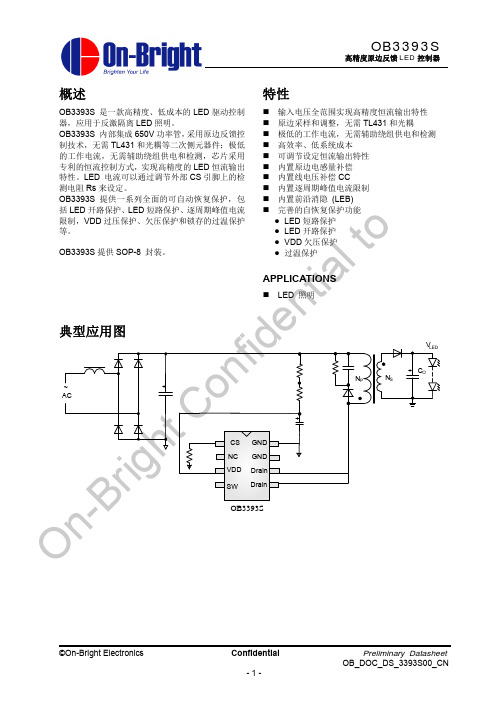

OB3393SCPA规格书 Datasheet

保证声明 昂宝电子有限公司依从其标准保单书承诺,出售时所有硬件产品性能参数均符合产品的相应使用规格书。产

恒

OB3393S 提供一系列全面的可自动恢复保护,包 括 LED 开路保护、LED 短路保护、逐周期峰值电流

深 限制,VDD 过压保护、欠压保护和锁存的过温保护

等。

to OB3393S 提供 SOP-8 封装。

内置前沿消隐 (LEB) 完善的自恢复保护功能

LED 短路保护 LED 开路保护 VDD 欠压保护

8-Pin Plastic SOP

OB3393S

高精度原边反馈 LED 控制器

恒

ht Confidential to 深 Symbol ig A

A1

r A2

b

Bc -D

E

nE1 e

OL

Dimensions In Millimeters

Min

Max

1.350

1.750

0.050

0.250

1.250

1.650

I/O 描述 I 电流采样端

无连接,必须悬空

P 电源供电端 I 内部高压功率管源极 I 内部高压功率管漏极 P 无连接,必须悬空并且不要放置焊盘 P地

©On-Bright Electronics

Confidential 3

Preliminary Datasheet OB_DOC_DS_3393S00_CN

启动电流 工作电流 VDD 欠压保护(OFF)阈值 VDD 欠压保护(ON)阈值 VDD 钳位阈值

HT7033a规格书

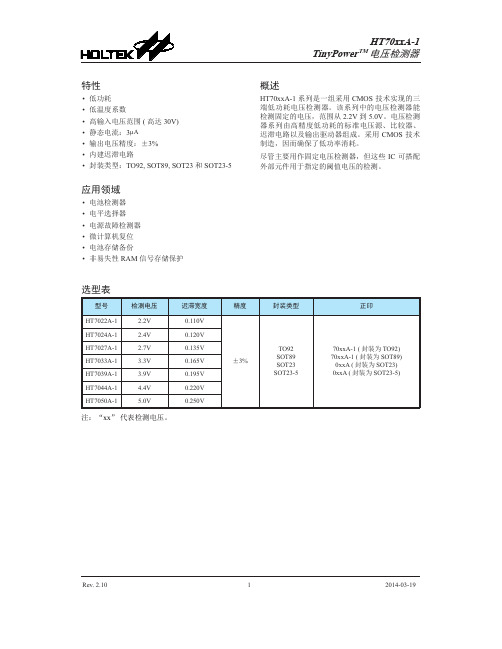

Rev. 2.1012014-03-19• 低功耗• 低温度系数• 高输入电压范围 (高达 30V)• 静态电流:3µA • 输出电压精度:±3%• 内建迟滞电路• 封装类型:TO92, SOT89, SOT23和 SOT23-5应用领域• 电池检测器• 电平选择器• 电源故障检测器• 微计算机复位• 电池存储备份• 非易失性RAM 信号存储保护HT70xxA-1系列是一组采用CMOS 技术实现的三端低功耗电压检测器。

该系列中的电压检测器能检测固定的电压,范围从 2.2V 到 5.0V 。

电压检测器系列由高精度低功耗的标准电压源、比较器、迟滞电路以及输出驱动器组成。

采用 CMOS 技术制造,因而确保了低功率消耗。

尽管主要用作固定电压检测器,但这些 IC 可搭配外部元件用于指定的阈值电压的检测。

选型表注:“xx ” 代表检测电压。

Rev. 2.1022014-03-19N 沟道开漏输出(常开,低有效)输出表格和曲线图..引脚图电源供应电压 ..............................V SS-0.3V ~ V SS+33V 输出电压 ....................................V SS-0.3V ~ V DD+0.3V 输出电流 ..............................................................50mA 功耗 ..................................................................200mW 储存温度范围 .................................................−50°C ~ 125°C 工作环境温度 .........................................−40°C ~ 85°C注:这里只强调额定功率,超过极限参数所规定的范围将对芯片造成损害,无法预期芯片在上述标示范围外的工作状态,而且若长期在标示范围外的条件下工作,可能影响芯片的可靠性。

通信原理书籍

***********通信原理书籍目录 ************* 《The ARRL Antenna Book(19th)》30页《电磁场基本教程》319页《电磁场与波》391页《电信工程设计手册_短波通信.12》702页《电子书籍》•121兆大小《短波通信电路设计》328页《高速通讯线路与系》14.8兆大小《国外军用飞机通信设备手册》462页《晶体管接收机电路的原理与设计》637页《宽带匹配网络的理论与设计(增订本)》13.8兆《无线电波传播》1059页《无线通信常用数据手册(修订本)[1].part1》680页《现代电信交换》396页《dds9851频率合成器》《大功率宽带射频脉冲功率放大器设计》《电子设备中的隔离技术》《分体中波超远程接受装置》《全固态中波发射机的维护》《衰减器原理》《有源窄带晶体滤波器》《1915的QST杂志》28页《OFDM移动通信技术原理与应用》283页《trk90电台外接单片机调节频率》《WS430型无线收信机的维修》195页《半导体无线电广播接收机理论与计算基础》395页《变容二极管的应用》333页《参量放大器》65页《超短波的传播》56页《超短波调频广播》115页《超短波无线通信》481页《超高频电视调谐器设计与原理》318页《超高频技术》355页《超高频接收机》589页《初级无线电技术》251页《地球站微波收发信机》361页《电报史话》84页《电波的世界》225页•《电话电报移动通信实用手册》291页《电视和调频发射机》466页《电信工程设计手册--短波通信》717页《电子爱好者的金桥-业余无线电通信》187页《电子调谐器原理与设计》723页《电子工程师便携手册》451页《电子学与无线电原理上册》559页《电子学与无线电原理下册》567页《调频广播用发射机与接收机》182页《调频及其应用》311页《调频立体声广播发射机》319页《调频袖珍电台的设计与制造》431页《短波单边带小型台维护手册(XDD-D2B及IC-M700TY电台)》269页《短波电台电力设备维护手册》157页《短波数字通信自适应选频技术》327页《短波通信电路设计》335页《短波中小型收发信机维护手册》302页《发射测量-英文》《范氏基本图解无线电学》301页《峰窝式移动电话原理-使用-检修》178页《高频电路基础》364页《高频电路设计技术》195页《高频电路设计与制作》259页《高频电路原理》270页《高频调谐器原理与维修》500页《各种发射类别的无线电接收机的测量方法》85页《广播发射新技术》239页《广播发送技术》338页《简单无线电装置》91页《简明无线电爱好者实用资料手册》530页《简明无线电原理》218页《简易无线电测试》82页•《晶体管接收机电路的原理与设计》645页《精品系列无线电爱好者读本(上)(第二次修订本)》609页《精品系列无线电爱好者读本(下)(第二次修订本)》418页《列车调度无线电话》202页《模范无线电读本》160页《平流层气球载通信系统》《千万个为什么(9)无线电篇》322页《浅谈无线电通信》129页《青年无线电工程师》221页《青少年电子巧技》288页《趣味无线电工学》220页《少年无线电》95页《少年无线电爱好者(上册)》159页《少年无线电爱好者(下册)》150页《少年无线电入门》158页《甚高频通信设备原理与维修》197页《实验无线电对讲机》244页《实用高频电路集》39页《实用无线电讲话》599页《实用移动无线电通信》358页《数字声频与广播播控技术》270页《数字微波收发信机维护手册》420页《苏联业余无线电丛书无线电电子设备的可靠性》69页《特高频无线电技术问题》122页《铁淦氧在无线电机中的应用》83页《通信、广播电路与系统》378页《通信广播电路原理与应用》431页《通信技术常识第二集超短波调频电台》56页《通信接收机:DSP、软件无线电和设计》595页《通信原理》436页《通信原理与电路》357页《外军电台手册》280页•《万有文库第一集一千种_无线电报及无线电话》155页《万有文库第一集一千种_无线电原理》137页《无线电“猎狐”》235页《无线电爱好者创作资料集 1》46页《无线电爱好者电路》622页《无线电波传播》1081页《无线电波传播理论及其应用》534页《无线电波是怎样传播的》90页《无线电测量术》146页《无线电常识(上册)》138页《无线电常识(下册)》173页《无线电初步》263页《无线电电路研究》218页《无线电电子学第二册》330页《无线电电子学第三册》234页《无线电电子学第一册》273页《无线电电子知识入门》372页《无线电读本上册》190页《无线电读本下册》252页《无线电短波收信机测试》108页《无线电多路通讯》422页《无线电发射接收原理》202页《无线电工程(上、下册)》486页《无线电工学(苏-布拉麦尔)》578页《无线电工学(苏-亚力山大罗夫)》349页《无线电工学基础》393页《无线电工业常用胶粘剂》121页《无线电广播工程》232页《无线电广播技术手册》1175页《无线电广播与接收》359页《无线电广播中的调频技术》344页《无线电话收音机管理法全一册》55页•《无线电机件装配指南》162页《无线电机修理法》139页《无线电基本知识》234页《无线电基础》407页《无线电基础与收音机》287页《无线电计量》386页《无线电技术》158页《无线电技术-2》427页《无线电技术参考资料印制电路及其制造》77页《无线电技术基础》241页《无线电技术基础(上册)》550页《无线电技术基础(苏)》744页《无线电技术讲座》212页《无线电讲话》230页《无线电接收》511页《无线电接收的工业干扰及其抑制》316页《无线电接收机大意》151页《无线电接收设备》404页《无线电接收设备(上册)》228页《无线电接收设备(下册)》352页《无线电结构设计手册》800页《无线电器材设计》290页《无线电器材试验》352页《无线电器材制造(上下册)》683页《无线电钳工基础工艺》315页《无线电设备的回路零件》330页《无线电设备结构设计》296页《无线电设备结构设计与工艺》306页《无线电设备元件零件的结构设计与制造工艺(上册)》574页《无线电设备元件零件的结构设计与制造工艺(下册)》393页《无线电设计结构设计》298页《无线电识图与电路故障分析轻松入门》•469页《无线电实用技术手册》469页《无线电世界》415页《无线电世界(中)》408页《无线电收信和无线电收信机的工作》252页《无线电收信中心》496页《无线电数学(上册)》253页《无线电数学(下册)》369页《无线电台是怎样工作的》258页《无线电通信设备维修》287页《无线电小组及其工作》95页《无线电信号频谱》308页《无线电修理技术(上册)》471页《无线电修理技术(下册)》477页《无线电修理技术(中册)》829页《无线电学》171页《无线电摇控制作》153页《无线电遥测》207页《无线电遥控电路专集》196页《无线电遥控模型飞机》129页《无线电遥控组件及其应用电路》254页《无线电应用手册》283页《无线电应用数学(上、下册)》337页《无线电与电视(2003年2,3,4,6,7期)》325页《无线电原理上、下册》698页《无线电原理及应用》345页《无线电知识》106页《无线短波发信机维护手册——6_8千瓦单边带发信机》161页《无线短波发信机维护手册——35千瓦单边带发信机》184页《无线短波发信机维护手册——50_80千瓦短波发信机》230页《无线短波收信机维护手册——5601型单边带接收机》203页《无线短波收信机维护手册——WR811型移频电报接收机》242页《无线通信电路基础教程》257页•《现代通信技术应用大全》744页《现代通信新技术(第2版)》458页《现代无线电通信知识讲座》307页《小型电台及其组网应用》323页《小型无线电机》375页《小型无线电机的电源》172页《小型无线电台》120页《小型无线电台的使用与维护》118页《小型无线电台技术手册》162页《新旧电气图形符号对照读本》69页《新型无线电通信接收机》182页《业余超短波无线电通信》103页《业余无线电1》42页《业余无线电及其机械维修技巧1200例》436页《业余无线电计算图表》116页《业余无线电手册》378页《业余无线电通信》237页《业余无线电问答(苏)》135页《业余无线电问答(中)》102页《业余无线电元器件手册》489页《移动式无线电台》97页《应用无线电及电子技术公式集》499页《怎样实现电视和调频广播远距离接收》289页《怎样抑制电气设备对无线电的干扰》90页《中短波辐射》《中短波广播发射机》182页《高速PCB设计指南》《锁相环设计软件》《印刷电路板排版设计》288页《2002ARRL HANDBOOK》114页《ARRL HANDBOOK 2006 CD.ISO---》• 《ARRL Radio Amateur Handbook 2000》《GSM基础讲座》105页《jarl业余无线电手册_11198348超星阅读》《wireless communications》545页《超再生式无线收信机》《带阻及低通微带滤波器的分析与设计》《电磁干扰排查及故障解决的电磁兼容技术》235页《电力线载波通信设计资料》4.83兆大小《电子科技大学通信原理19讲-视频》788兆大小《电子元器件焊接技术-视频》199兆《多相滤波器的原理及其实现》《高频无源部件设计》33页《国内外功率晶体管实用手册(下)_10004037》1429页《集群通信系统概述》《晶体管手册》《扩展频谱通信简介》《雷达手册》1051页《射频电平单位dBW、dBm、dBmV、dBμV的关系》《射频微波工程百科全书.Encyclopedia.of.RF.and.Microwave.Engineering》119兆大小《实用电子线路集》612页《通信电路》3.49兆大小《通信知识》1.63兆大小《微波电子线路》236页《现代微波滤波器的结构与设计》899页《业余超短波无线电通信》103页《振荡电路实用设计手册_10844117》311页《无线电应用基础知识必读》《PCB板蛇形走线有什么作用》《丙类倍频器》《短波频带中的各种信号》《短波收音机混频电路浅析》•《混频器,滤波器,功率合成..》《火腿肠谈盗听器发现和秘话解读功能》《滤波器的过去、现在与未来》《漫谈DDS,PLL和纯LC振荡器》《漫谈短波的音质》《密码电台》《偏转管混频器介绍》《软件无线电》《深入浅出话拍频》《说说现代业余无线电接收技术中的常用功能《跳频术:巧设信息战安全走廊》》《通俗点来谈SSB工作模式和原理》《通信系统传输单位—分贝》《直接频率合成(DDS)技术介绍》《转贴一篇有关频率合成的文章》************晶体、电子管、功放目录 ************* 《15瓦射频放大器》《LM386功放电路图》《TL-922 完整的短波电子管功放电路图及内部实物图》《电真空器件手册》818页《电子管手册(1-4辑)》•1827页《负反馈》164页《射频功放的收发切换电路》《苏联《输出变压器的设计》中文》《自制高频电子管功率放大器》《2-30MHz 8W宽带线性放大器》《15w射频功率放大器》《40瓦28兆电子管(FU-7)功放电路图》《100w功放内部图(晶体管)》《600瓦FL-2100B电子管功放(内部图片)》《1932年的电子管原理教材(部分)》《Alpha87A射频电子管功放内部图片(超清析-漂亮)》《C1970与C1971的区别》《DIY 708B电台 10W功放》《FU-50高频电子管功率放大器电路图》《HF PA SU IRF640 廉价功放》《LM386低电压应用设计音频功率放大器》《MOTO AN779晶体管功放图片》《NE602使用资料》《PTT控制电路》《常用稳压电子管参数》《常用元器件的识别》《成品HF功放比拼,看看怎样DIY》《大功率电子管电路及PTT控制电路(老外)》《胆机故障分析》《胆机噪声完全手册》《电子管116短波功率放大器改造图纸》《电子管差分放大功放的制作与调试》《电子管发明简史》《电子管发射机图纸(15-20瓦)》《电子管功放的调整》《电子管及其电路》《电子管特性曲线》•《高功率放大器设计(内有实物及电路图)》《高频电子管功率放大器(内有实物及电路图)》《高频全波段25瓦线性放大器》《功放板改造》《功放图片(内有实物及电路图)真养眼功放汇集(内有实物及电路图)》《功放图片(实物)》《功放图片汇集(内有实物及电路图)》《短波功放欣赏:ACOM-1000(真养眼)》《功率合成》《功率合成器电路图》《军机74上的400W功放及天调部分》《看朋友解剖大功放及大小81电台演变等(详细图片)》《宽频带高频功率放大器》《请看我DIY的80瓦电子管射频功放》《束射四极管常用电路及其电路数据》《肖特基二极管简介》《学习一下短波胆龟的制作(图片及电路图)》《一个电子管的CW发射(图文并茂)》《栅放大器的几个线路》《中国真空电子工业的发展历程》《1-50兆100瓦经典射频功放-图文并茂》《2sc1945发射晶体管参数》《2sc1946发射晶体管参数》《2sc1970发射晶体管参数》《2sc1972发射晶体管参数》《2sc2053发射晶体管参数》《2sc2237发射晶体管参数》《2sc2383发射晶体管参数》《2sc2538发射晶体管参数》《2sc2539发射晶体管参数》《2sc2539发射晶体管参数》•《2sc2690发射晶体管参数》《2sc2904发射晶体管参数》《2sc3019发射晶体管参数》《2sc3021发射晶体管参数》《2sc3101发射晶体管参数》《2sc3356发射晶体管参数》《74-3CE型军用发射机功放电路图》《300瓦短波线型放大器原理与调试(图文并茂)》《57704m三菱射频功放模块》《57704uh三菱射频功放模块》《67741h三菱射频功放模块》《67741l三菱射频功放模块》《96834_MITSUBISHI_QM30HC-2H(三菱模块)》《ct60AM三极管》《IRFBC40管参数》《M68702L东芝射频功放模块》《MRF392射频功放管参数》《MRF464射频功放管参数》《S-AU27东芝射频功放模块》《S-AU57东芝射频功放模块》《TA7805-24S稳压管详细参数》《常见三菱发射管参数》《常用电子管、离子管、晶体管手册》74页《常用电子管电路手册》178页《常用电子元件及典型应用》518页《常用电子元器件使用技巧300问》498页《常用集成电路实用手册》762页《常用三极管替换手册》1414页《常用收信电子管应用手册》268页《场效应管手册》386页《超高频电子管-01》•436页《超高频电子管-02》364页《超高频电子管原理》277页《超高频电子学引论电子管计算基础》297页《从电子管到超大规模集成电路》154页《大型发射管实用维修手册》307页《低电压晶体管电路》202页《电子爱好者实用资料大全元器件篇》1190页《电子功放电路图》177页《电子管科学图书大库图解电子学(三)》台湾,141页《电子管(上册)》362页《电子管(下册)》316页《电子管测试》207页《电子管的计算与设计》207页《电子管的理论和计算基础下册》446页《电子管的维护》259页《电子管等效参数手册》181页《电子管电路基础》214页《电子管放大电路实践》177页《电子管放大器基础》《电子管放大器基础-2 (1)-2》106页《电子管放大器基础-2 (2)》474页《电子管及其设计基础》,250页《电子管实验室手册》118页《电子管手册》894页《电子管手册(第二集)》112页《电子管数据手册》504页《电子管与离子管》466页《电子管与真空技术手册》927页《电子管在实验物理中的应用(上册)》353页《电子管在实验物理中的应用(下册)》645页《电子管直流放大器》84页《电子管制造工艺学》•422页《电子器件及放大器(上册电子器件部分)》283页《电子器件及放大器(下册放大器部分)》279页《电子设计员手册晶体管线路设计入门》290页《电子束管》160页《电子束管无线电电子学知识丛书》152页《电子元件五十年》436页《电子元器件选用入门》355页《电子元器件与实用电路基础(修订版)》367页《电子注与电子枪电子管技术丛书之一》496页《短波段低通滤波器电原理图》《二极管手册》1496页《发射电子管电报状态的理论与计算》152页《发射管设计手册》633页《放大电路原理》462页《放大电路指南》313页《高保真胆机制作》《高频加热用的电子管》193页《功率供应器与放大器科学图书大库图解电子学(五)-台湾》172页《国内外晶体管性能对照手册》1190页《国内外最新三极管特性参数与互换速查手册》603页《国外晶体管参数与代换大全》1085页《国外晶体三极管速查代换大全》756页《集成电路简明应用手册音响设备专辑》744页《集成电路应用识图方法》283页《结型场效应晶体管原理与应用》242页《晶体管电路基础》242页《晶体管放大器》126页《晶体管放大器的信号流图分析法》181页《晶体管放大与振荡电路》220页《晶体管高频电路(上册)》496页《晶体管高频电路(下册)》497页《晶体管宽频带放大器分析》192页《晶体管手册》153页《晶体管谐振放大器》37页《晶体管原理与实践》360页《晶体检波器和放大器》73页《宽频带放大器用电子管》108页《瞭解真空管及电晶体电路基本电学与电子学第三卷》234页《三极管上的印字,与真实型号对照表》53页《三极管手册》1562页《三菱57704el功放模块》《三菱57704l射频功放模块》《射频收发转换用MI402-开关二极管》《射频收发转换用开关管比较1》《射频收发转换用开关管比较2》《实用晶体管电路设计》327页《世界电子管电路手册》776页《世界电子管手册(上册)》498页《世界电子管手册(下册)》722页《世界晶体管实用手册》1668页《世界真空管大全(小)》432页《世界最新晶体管代换手册——国外与国外、国外与国内晶体管》1412页《收信放大电子管》38页《苏联电子管手册》501页《苏联无线电元件装置元件手册》449页《速查速用世界最新场效应管替换手册》1043页《速查速用世界最新三极管替换手册》2953页《特殊新型电子元器件手册》593页《通信集成电路大全》1070页《图表细说电子元器件》334页《图解晶体管实用电路》245页《微波电子管》102页《微波电子管磁路设计手册》77页《微波电子管原理上册》234页《微波电子管原理下册》197页《无线电材料与元件》286页《无线电元件目录》•354页《无线电元器件检测与修理技术轻松入门》404页《无线电元器件检测与修理技术入门》325页《无线电元器件精汇》483页《无线电元器件应用手册》313页《无线电元器件原理及选用》254页《无线电原理(电子管及其电路)》850页《无线电真空管》45页《无线电子学知识丛书电子管》116页《无线接收发射应用集成电路手册》1167页《线性集成电路参数与代换大全--《家用电器集成电路应用大全》姐妹篇》973页《新编常用晶体三极管手册》920页《新编晶体管实用手册》1526页《新编实用半导体器件手册》320页《新编无线电元器件应用手册》514页《新编中外晶体管互换全集》1259页《新编中外晶体管互换全集-2》996页《新型实用功率放大电路集锦(音响)》370页《用FU-7及6P15制的电子管发射机》《元器件自学通》637页《怎样设计放大器》392页《真空电子器件测试》435页《真空管的精义》107页《真空管的应用》109页《直流电子放大器》301页《中国电子元件相关GB标准100条索引[1].pdf》《中国真空电子器件数据手册》504页《自动控制装置中的晶体三极管》149页《最新集成电路互换手册》568页《最新集成电路应用手册》245页《最新美国欧洲韩国晶体管参数及互换全集》590页《最新世界场效应管特性代换手册》386页《最新世界场效应管详尽参数及互换手册》537页《最新世界二极管特性代换手册》907页《最新世界集成电路互换手册(最新增订本)》644页《最新世界三极管特性代换手册》1567页《最新中外电子元器件特性参数及代换手册》1064页《4x811电子管功放电路图》《811a-50瓦-6米段电子管功放电路图》《811a-50瓦-6米段电子管功放电路图及实物图》《811ax1-6m电子管功放》《811x1-200w电子管功放原理图》《811x6-1300w电子管功放》《a811x4 pcb电子管功放原理图及详细参数电路板设计及实物图(养眼呀)》《delta1000电子管功放原理图(用811A)》《高频管使用方法(摘自无线电世界)》《世界可控硅参数大全》666页《世界最新集成运算放大器互换手册——日、美、西德、荷兰、法和中国型号及其互换》691页《电子管放大电路实践》183页《电子管放大电路实践》《2sc1970-1971-1972发射管参数》《2sc2053发射管参数及使用电路图》《9011~9018三极管参数手册》《circuit_hl1kgx电子管功放原理图》《circuit_hl37v电子管功放原理图》《circuit_hl82v晶体管功放原理图》《circuit_hl110v晶体管功放原理图》《circuit_hl160v25a晶体管功放原理图》《circuit_hl180v晶体管功放原理图》《CMOS 4000系列集成电路标准中文数据手册》523页《CS-5A型电子管测试仪-BD7EI》41页《FU-13 及FU-50射频电子管功放电路图》•《HL-37V射频功放电路图(晶体管)》《HL-82V射频功放电路图(晶体管)》《IC集成电路应用手册_10185782》327页《mc145163频率合成器应用资料》《NE602使用资料》《TS440S电台功放带通电路图》《常用IC、数码管、三极管管脚排列》24页《常用电子管应用电路》2035页《常用收信电子管应用手册_0》268页《电子功放电射频路大图(超详细)》《电子管_0》52页《电子管测试_0》207页《电子管电路基础(增订本)_0》303页《电子管电路基础_0》214页《电子管放大器图集(音频)》20页《电子管手册》894页《电子管手册_0》894页《电子管与真空技术手册(内部)_10171618》927页《短波1600w军机功放手册》68页《国内外功率晶体管实用手册(上)_10004036》664页《国内外小功率晶体管实用手册(上)(国外部分)_10004038》827页《国内外小功率晶体管实用手册(下)(国内部分)_10004039》888页《家用电器元器件手册_10004041》728页《晶体管手册》《世界电子管手册_0》722页《苏联无线电元件装置元件手册_10184067》449页《最新世界二极管特性代换手册_10421419》907页《最新世界三极管特性代换手册_10421200》1567页《测判三极管的口诀》《常用发射机用三级管》《场效应管参数符号及意义》《大功率电视发射管的使用及维护》《电子管厂(七七四厂)和无线电器材联合厂(七一八厂)的筹建》《电子管高频功率放大器输出回路的馈电形式》《电子管功放的输入匹配问题》《调整双工器放大器的类别》《高频磁环的识别》《高频管和低频管的判别》《关于电子工艺管制造》《火腿电台的补品:电子束偏转管》《晶体管参数(部分)》《空气电容片距与耐压对照值》《判断三极管口诀》《使用电子管时应该特别注意的事项》《无线电台常用发射模块参数》************天线目录 ************* 《DBJ -1型VHFUHF两波段J型天线》《FORCE12的部分天线资料内有详细天线尺寸)》《GP天线》《八木天线-》《多段J型天线设计计算软件》•《接地与搭接》《近代天线设计》《实用天线设计与制作-书籍》144页《天线工程手册》1252页《天线设计与制作(R.A彭福德(英)著)》80页《435兆八木天线图》《FMA9901A调频广播专用天线》《懒汉天线原理图》《144MHz九单元八木天线制作》《st310a军用天线使用说明书》《0.7米6单元HB9CV天线(图片)》《2 米波段杜普勒矩环定向天线》《2.4G天线(图片)》《6M,2M,0。

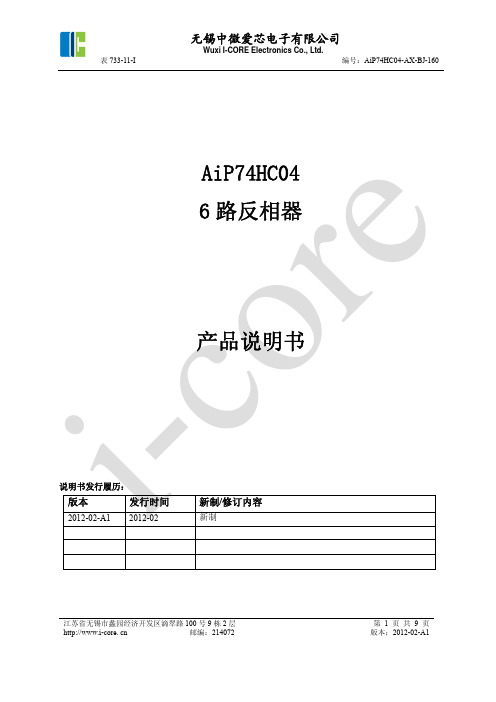

AiP74HC04中文资料

VCC=2.0V IO=-20uA

VCC=4.5V IO =-20uA

Vi=VIH 或 VIL

VCC=4.5V IO=-4.0mA

VCC=6.0V IO=-20uA

VCC=6.0V IO=-5.2mA

VCC=2.0V IO=20uA

VCC=4.5V IO=20uA

Vi=VIH 或 VIL

VCC=4.5V IO=4.0mA

江苏省无锡市蠡园经济开发区滴翠路 100 号 9 栋 2 层

http://www.i-core. cn

邮编:214072

第6页共9页 版本:2012-02-A1

表 733-11-I

5、封装尺寸与外形图 5. 1、DIP14 图与封装尺寸

无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

编号:AiP74HC04-AX-BJ-160

6、声明及注意事项:

6.1、产品中有毒有害物质或元素的名称及含量

有毒有害物质或元素

部件名称

铅(Pb)

汞(Hg) 镉(Cd)

六阶铬 多溴联苯 多溴联苯 (C(r Ⅵ)) (PBBs) 醚(PBDEs)

引线框

○

○

○

○

○

○

i-core 塑封树脂 芯片 内引线 装片胶

VCC=6.0V IO=20uA

VCC=6.0V IO=5.2mA

VCC=6.0V Vi= VCC 或 GND

VCC=6.0V Vi=VIH 或 VIL Vo= VCC 或 GND

VCC=6.0V Vi =VCC 或 GND IO=0

最小

1.5 3.15 4.2 - - - 1.9

AP4313中文规格书,AP4313KTR-G1中文datasheet翻译

2.650(0.104) 2.950(0.116) 1.500(0.059) 1.700(0.067)

引脚1含有圆点标注

1

2

3

0.950(0.037)典型

1.800(0.071) 2.000(0.079)

0.700(0.028)参考值

0.000(0.000) 0.150(0.006)

GND

R5

ICTRL

VSENSE

R1

R6 500

Rss

VOUT

= VREF

× R1+ R2 R1

(V)

限流电流 = VSENSE (A) RSS

图 10. AP4313的典型应用1

VOUT+ IL Load

VOUT-

2010年5月 版本2. 0

BCD 新进半导体制造有限公司 8

恒压恒流控制器 典型应用 (续页)

产品规格书 AP4313

I (mA)

OS

I (mA)

CC

60

50

40

30

20

V =12V

CC

V =5V

CC

V =2.5V

10

CC

0

-40

-20

0

20

40

60

80

100

120

环境温度(oC)

图 8. 输出引脚的短路电流 – 环境温度 关系图

1.4

1.0

0.8

0.6

0.4

0.2

0.0

-40

-20

0

CC

V =5V CC

BCD 新进半导体制造有限公司 1

恒压恒流控制器 引脚信息

TDA7388A, 规格书,Datasheet 资料

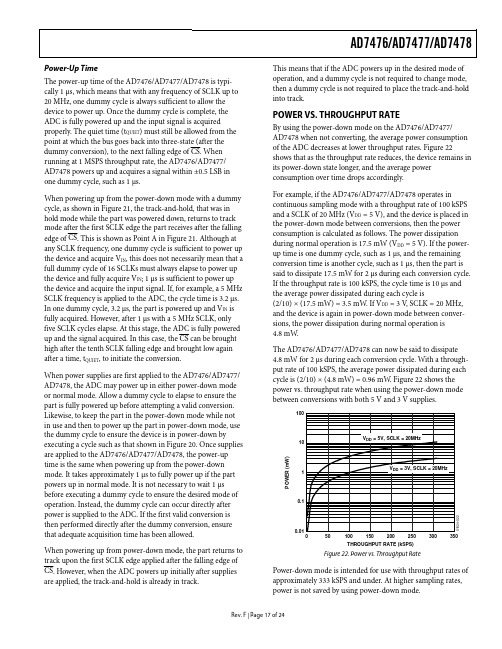

This is information on a product in full production.July 2012Doc ID 14257 Rev 31/13TDA7388A4 x 42 W quad bridge car radio amplifierDatasheet − production dataFeatures■High output power capability:– 4 x 42 W / 4 Ω max.– 4 x 27 W / 4 Ω @ 14.4 V , 1 kHz, 10 %■Low distortion ■Low output noise ■Standby function ■Mute function■Automute at min. supply voltage detection ■Low external component count:–Internally fixed gain (26 dB)–No external compensation –No bootstrap capacitors ■Clipping detector ■Offset detector ■Diagnostic facility for:–Out to GND short –Out to V S short –Thermal shutdown■Protections:–Output short circuit to GND, to V S , across the load–Very inductive loads–Overrating chip temperature with soft thermal limiter–Load dump voltage –Fortuitous open GND–Reversed battery –ESDDescriptionThe TDA7388A is a new technology class AB audio power amplifier in Flexiwatt27 package designed for high end car radio applications.Thanks to the fully complementary PNP/NPN output configuration the TDA7388A allows a rail to rail output voltage swing with no need of bootstrap capacitors. The extremely reduced components count allows very compact sets.The TDA7388A is also equipped with Clipping detector and Offset detector features.Table 1.Device summaryOrder code Package Packing TDA7388AFlexiwatt27TubeContents TDA7388AContents1Pin connection and test/application diagrams . . . . . . . . . . . . . . . . . . . . 52Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.1Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.2Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.3Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.4Electrical characteristic curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83Application hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103.1SVR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103.2Input stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103.3Standby and muting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 4Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 5Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122/13Doc ID 14257 Rev 3TDA7388A List of tables List of tablesTable 1.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 3.Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 4.Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 5.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Doc ID 14257 Rev 33/13List of figures TDA7388A List of figuresFigure 1.Pin connections (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 2.Standard test and application circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3.Quiescent current vs. supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 4.Output power vs. supply voltage (4 Ohm) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5.Distortion vs. output power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6.Distortion vs. frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 7.Supply voltage rejection vs. frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8.Crosstalk vs. frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 9.Output noise vs. source resistance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10.Power dissipation & efficiency vs. output power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 11.ITU R-ARM frequency response, weighting filter for transient pop. . . . . . . . . . . . . . . . . . . . 9 Figure 12.Flexiwatt27 mechanical data and package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 4/13Doc ID 14257 Rev 3TDA7388A Pin connection and test/application diagrams 1 Pin connection and test/application diagramsDoc ID 14257 Rev 35/13Electrical specifications TDA7388A6/13Doc ID 14257 Rev 32 Electrical specifications2.1Absolute maximum ratings2.2 Thermal data2.3 Electrical characteristicsV S = 14.4 V; f = 1 kHz; R g = 600 Ω; R L = 4 Ω; T amb = 25 °C; Refer to the test and applicationdiagram (Figure 2), unless otherwise specified.Table 2.Absolute maximum ratingsSymbol ParameterValue Unit V S Operating supply voltage 18V V S (DC)DC supply voltage28V V S (pk)Peak supply voltage (t = 50 ms)50V I O Output peak current:Repetitive (duty cycle 10 % at f = 10 Hz)Non repetitive (t = 100 μs) 4.55.5A A P tot Power dissipation, (T case = 70°C)80W T j Junction temperature 150°C T stg Storage temperature – 55 to 150°C T ambOperative temperature range– 40 to 105°CTable 3.Thermal dataSymbol ParameterValue Unit R th j-caseThermal resistance junction-to-casemax.1°C/WTable 4.Electrical characteristicsSymbol ParameterTest conditionMin.Typ.Max.Unit I q1Quiescent current R L = ∞100190350mA V OSOutput offset voltagePlay mode--±100mV dV OSDuring mute ON/OFF output offset voltage ITU R-ARM weightedsee Figure 11-10-+10mV During St-By ON/OFFoutput offset voltage -50-+50mV G v Voltage gain-252627dB ΔG v Channel gain unbalance ---±1dB P oOutput powerTHD = 10 %; V S = 14.4 V2527-WTDA7388A Electrical specificationsDoc ID 14257 Rev 37/13P o max Max.output power (1)V S = 14.4 V 3942-W THD Distortion P o = 4 W -0.040.10%e No Output noise"A" Weighted -5070µV Bw = 20 Hz to 20 kHz -70100µV SVR Supply voltage rejection f = 100 Hz; V r = 1 V rms 5065-dB f ch High cut-off frequency P o = 0.5 W 100200-kHz R i Input Impedance -70100-k ΩC T Cross talk f = 1 kHz; P o = 4 W 6070-dB f = 10 kHz; P o = 4 W -60-dB I SB Standby current consumption V St-By = 0 V --20µA I pin4Standby pin current V St-By = 1.2 to 2.6 V --±10µA V SB out Standby out threshold voltage(Amp: on)2.6--V V SB IN Standby in threshold voltage (Amp: off)-- 1.2V A M Mute attenuationP Oref = 4 W 8090dB V M out Mute out threshold voltage (Amp: Play) 2.6--V V M inMute in threshold voltage(Amp: Mute)-- 1.2V V AM in V S automute threshold(Amp: Mute); Att ≥ 80 dB;P Oref = 4 W(Amp: Play); Att < 0.1 dB;P O = 0.5 W -7.66.58.5V VI pin22Muting pin current V MUTE = 1.2 V (Source current)51120µAOffset detectorV off Detected diff. output offset V St-by =5V ±1.4±2±2.6V V OFF LK V OFF high leakage current OD off--10µA V OFF SATV OFF det saturation voltageOD on; I OD = 1 mA-300-mVClipping detectorCD LK Clip det high leakage current CD Off --10µA CD SAT Clip det sat voltage DC On; I CD = 1 mA -300-mV CD THDClip det THD level--0.2-%1.Saturated square wave output.Table 4.Electrical characteristics (continued)Symbol ParameterTest conditionMin.Typ.Max.UnitElectrical specifications TDA7388A8/13Doc ID 14257 Rev 32.4Electrical characteristic curvesFigure 3.Quiescent current vs. supply voltageFigure 4.Output power vs. supply voltage (4 Ohm)Figure 5.Distortion vs. output powerFigure 6.Distortion vs. frequencyFigure 7.Supply voltage rejection vs. frequencyFigure 8.Crosstalk vs. frequencyTDA7388A Electrical specificationsDoc ID 14257 Rev 39/13Figure 9.Output noise vs. source resistanceFigure 10.Power dissipation & efficiency vs.output powerFigure 11.ITU R-ARM frequency response,weighting filter for transient popApplication hints TDA7388A10/13Doc ID 14257 Rev 33 Application hintsRef. to the circuit of Figure 2.3.1 SVRBesides its contribution to the ripple rejection, the SVR capacitor governs the turn ON/OFFtime sequence and, consequently, plays an essential role in the pop optimization during ON/OFF transients.To conveniently serve both needs, its minimum recommended value is 10 µF .3.2 Input stageThe TDA7388A’s inputs are ground-compatible and can stand very high input signals(± 8Vpk) without any performances degradation.If the standard value for the input capacitors (0.1 µF) is adopted, the low frequency cut-off will amount to 16 Hz.3.3 Standby and mutingStandby and muting facilities are both 3.3V CMOS-compatible. If unused, a straightconnection to V S of their respective pins would be admissible.Conventional/low-power transistors can be employed to drive muting and stand-by pins in absence of true CMOS ports or microprocessors. R-C cells have always to be used in order to smooth down the transitions for preventing any audible transient noises.Since a DC current of about 10 µA normally flows out of pin 23, the maximum allowable muting-series resistance (R 2) is 70 k Ω, which is sufficiently high to permit a muting capacitor reasonably small (about 1 µF).If R 2 is higher than recommended, the involved risk will be that the voltage at pin 23 may rise to above the 1.5 V threshold voltage and the device will consequently fail to turn OFF when the mute line is brought down.About the stand-by, the time constant to be assigned in order to obtain a virtually pop-free transition has to be slower than 2.5 V/ms.TDA7388A Package informationDoc ID 14257 Rev 311/134 Package informationIn order to meet environmental requirements, ST offers these devices in different grades ofECOPACK ® packages, depending on their level of environmental compliance. ECOPACK ® specifications, grade definitions and product status are available at: .ECOPACK ® is an ST trademark.Revision history TDA7388A12/13Doc ID 14257 Rev 35 Revision historyTable 5.Document revision historyDate RevisionChanges06-Dec-20071Initial release.15-Oct-20082Document status promoted from preliminary data to datasheet.Updated Table 3: Thermal data on page 6.06-Jul-20123Updated Table 2: Absolute maximum ratings on page 6.TDA7388APlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2012 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of AmericaDoc ID 14257 Rev 313/13。

TDA7056A中文资料

THERMAL RESISTANCE 55 K/W 10 K/W

Note to the thermal resistance

VP = 12 V; RL = 16 Ω; The maximum sine-wave dissipation is = 1.8 W. The Rth vj-a of the package is 55 K/W; Tamb (max) = 150 − 55 x 1.8 = 51 °C

EXTENDED TYPE NUMBER

TDA7056A

PINS 9

Note 1. SOT110-1; 1996 August 21.

PIN POSITION SIL

PACKAGE MATERIAL plastic

CODE SOT110

July 1994

2

元器件交易网

Philips Semiconductors

3 W BTL mono audio output amplifier with DC volume control

Product specificiation

TDA7056A

handbook, full pagewidth

n.c.

1

n.c.

9

positive input

3

5 DC volume control

7 power ground

8 negative output

9 not connected

handbook, halfpage

n.c. 1

VP 2 VI 3 GND1 4

VC 5 TDA7056A

OUT+ 6

GND2 7

OUT− 8

n.c. 9

TDA7053A资料

元器件交易网

Philips Semiconductors

Product specification

Stereo BTL audio output amplifier with DC volume control

FEATURES • DC volume control • Few external components • Mute mode • Thermal protection • Short-circuit proof • No switch-on and switch-off clicks • Good overall stability • Low power consumption • Low HF radiation • ESD protected on all pins. QUICK REFERENCE DATA SYMBOL VP Pout PARAMETER supply voltage output power TDA7053A TDA7053AT Gv GC Iq(tot) THD voltage gain gain control total quiescent current total harmonic distortion TDA7053A TDA7053AT ORDERING INFORMATION TYPE NUMBER TDA7053A TDA7053AT PACKAGE NAME DIP16 SO16 DESCRIPTION plastic dual in-line package; 16 leads (300 mil); long body plastic small outline package; 16 leads; body width 7.5 mm Pout = 0.5 W Pout = 0.25 W − − 0.3 0.3 VP = 6 V; RL = ∞ VP = 6 V RL = 8 Ω RL = 16 Ω 0.85 0.5 39.5 68.0 − 1.0 0.55 40.5 73.5 22 CONDITIONS MIN. 4.5 − TYP. Missing Current Limiter (MCL) GENERAL DESCRIPTION

EVAL-AD7472资料

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.Tel: 617/329-4700 Fax: 617/326-8703REV. AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aEvaluation Board for 12-bit high speed,low p ower, s uccessive-approximation A DCEVAL-AD7472CBFUNCTIONAL BLOCK DIAGRAMFEATURESFull-Featured Evaluation Board for the AD7472EVAL-CONTROL BOARD Compatible HSC-INTERFACE BOARD Compatible Stand Alone CapabilityOn-Board Analog Buffering and Reference Optional On-Board Analog Bias-Up CircuitOptional On-Board Burst Clock Generator Circuit Various Linking OptionsPC Software for Control and Data Analysis when used with EVAL-CONTROL BOARD INTRODUCTIONThis Technical Note describes the evaluation board for the AD7472 12-bit, high speed, low power, successive approxi-mation A/D converter that operates from a single 2.7 V to 5.25 V supply. Full data on the AD7472 is available in the AD7472 data sheet available from Analog Devices and should be consulted in conjunction with this Technical Note when using the Evaluation Board.On-board components include an AD780 which is a pin programmable +2.5 V or +3 V ultra high precision bandgap reference, two AD797 op-amps used to buffer the analog input, and an OP07 op-amp used to buffer the DC bias voltage applied to the optional analog input bias-up circuit.There are various link options which are explained in detail on page 2.Interfacing to this board is through a 96-way connector. This 96-way connector is compatible with the EVAL-CONTROL BOARD which is also available from Analog Devices.External sockets are provided for the CONVST input,CLKIN input and the VIN inputs.OPERATING THE AD7472 EVALUATION BOARD Power SuppliesWhen using this evaluation board with the EVAL-CON-TROL BOARD all supplies are provided from the EVAL-CONTROL BOARD through the 96 way connector.When using the board as a stand alone unit or with the HSC-INTERFACE BOARD, external supplies must be provided.This evaluation board has five power supply inputs: V DD ,A GND , V SS , V DRIVE and D GND . +5 V must be connected to the V DD input to supply the AV DD and DV DD pins on the AD7472,the AD780 voltage reference, the positive supply pin of all three op-amps and the digital control logic. 0 V is connected to the A GND input. -5 V must be connected to the V SS input to supply the negative supply pins on all three op-amps. The V DRIVE input can be used to provide an external voltage for the output drivers on the AD7472. If an external V DRIVE is supplied, it is referenced to the D GND input which should be tied to 0 V. The supplies are decoupled to the relevant ground plane with 47µF tantalum and 0.1µF multilayer ceramic capacitors at the point where they enter the board. The supply pins of the op-amps and reference are also decoupled to A GND with a 10µF tantalum and a 0.1µF ceramic capacitor. The AD7472 AV DD supply pin is decoupled to A GND with 10uF tantalum and 0.1µF multilayer ceramic capacitors. The AD7472 DV DD and VDRIVE pins are decoupled to A GND with 10uF tantalum capacitors and to D GND with 0.1µF multilayer ceramic capacitors.Extensive ground planes are used on this board to minimize the effect of high frequency noise interference. There are two ground planes, A GND and D GND . These are connected at one location close to the AD7472.EVAL-AD7472CBAnalog Input SectionThe analog input section of this evaluation board accommodates unipolar and bipolar signals. Unipolar signals within the AD7472 analog input signal range of 0 V - 2.5 V are connected via SK5. They are then buffered by the on-board buffer before being applied to the VIN pin of the AD7472. Bipolar signals are connected via SK3 and are biased up by the on-board bias-up buffer circuit before being applied to the VIN pin of the AD7472. The input impedence of the bias-up circuit is 50W which is determined by the value of R7. The input impedence may be modified by removing/changing the value of R7. To obtain optimum performance from this evaluation board the use of an impedence matched, passive filter is recommended before the analog signal is applied to the evaluation board. For example, when using a 100KHz input tone, a 100KHz 50W filter from TTE (part number KC5-100K-15K-50/50-720B) is suitable.R8 Potentiometer (50Kohm)This variable resistor is used to trim the DC bias voltage applied to the optional analog input bias-up circuit. This bias voltage is factory preset to 1.25 V which biases a bipolar signal to swing around the midpoint of the analog input range (0 - 2.5 V). If any adjustment is required, the user can use the histogram window in the eval-board software to analyze the DC voltage variation while adjusting the trim pot. To view this properly, an analog input signal should not be applied to the board. Under normal operation this pot should not be adjusted as it is preset for optimum performance.LINK AND SWITCH OPTIONSThere are 11 link options which must be set for the required operating setup before using the evaluation board. The functions of these options are outlined below.Link No.Function.LK1This link is used to select the DC bias voltage to be applied to the optional Vin bias-up circuit.If the user is using the bias-up circuit, this link must be inserted which will apply the 2.7 V reference voltageto the bias-up circuit. This causes a bipolar signal (applied to the bipolar vin input socket) to be biased uparound +1.25 V before it is applied to the AD7472 VIN pin. - see also LK10 (below)If the bias up circuit is not being used this link should be removed.LK2This link must be in position "A" if external power supplies are being used. In this position the control logic is being powered by the voltage applied to the VDD input.When power is being supplied from the EVAL-CONTROL BOARD, this link can be moved to position "B"if the user wants to drive the control logic from a separate +5 V which is generated on the EVAL-CONTROLBOARD.LK3This link option selects the source of the CLKIN input.When this link is in position "A" the CLKIN input is provided by the EVAL-CONTROL BOARD.When this link is in position "B" the CLKIN input is provided via the on-board 25MHz oscillator.When this link is in position "C", an external CLKIN signal must be provided via SK1.When using the on-board generated burst clock, this link must be in position "D".LK4This link option selects the source of the CONVST input.When this link is in position "A" the CONVST input is provided by the EVAL-CONTROL BOARD.When this link is in position "B" the CONVST input is provided via the external socket, SK2.LK5This link option selects the source of the RD input.When this link is in position "A" the RD input is provided by the EVAL-CONTROL BOARD.When this link is in position "B" the RD input is tied to GND. This option must be selected while using theHigh Speed Converter Interface Board.LK6This link option selects the source of the CS input.When this link is in position "A" the CS input is provided by the EVAL-CONTROL BOARD.When this link is in position "B" the CS input is tied to GND. This option must be selected while using theHigh Speed Converter Interface Board.LK7This link option sets the voltage applied to the VDRIVE pin on the AD7472.When this link is in position "A", VDRIVE is connected directly to the DVDD pin.When this link is in position "B", an external voltage must be applied to the VDRIVE pin Via J3.LK8This link selects the source of the V DD supply.When this link is in position "A" V DD must be supplied from an external source via J2.When this link is in position "B" V DD is supplied from the EVAL-CONTROL BOARD.LK9This link selects the source of the V SS supply.When this link is in position "A" V SS must be supplied from an external source via J2.When this link is in position "B" V SS is supplied from the EVAL-CONTROL BOARD.LK10This link must be in position "A" if a bipolar AIN signal is being applied to the bipolar Vin socket, SK3.This link must be in position "B" if a unipolar AIN signal is being applied to the unipolar Vin socket, SK5Continued on next page–2–REV. AEVAL-AD7472CB LK11This link is used to provide a clock signal path to the burst mode circuit generator from either the on-board clock oscillator or from an extermnal clock source via SK1.In position "A" the master clock signal is provided from the on-board crystal oscillator.In position "B" the master clock signal must be provided from an external source via SK1.SET-UP CONDITIONSCare should be taken before applying power and signals to the evaluation board to ensure that all link positions are as per the required operating mode. Table I shows the position in which all the links are set when the evaluation board is sent out. All links are set for use with the EVAL-CONTROL BOARD.Table I. Initial Link and Switch PositionsLink No.Position Function.LK1Inserted Provides DC bias voltage to the analog bias-up circuit.LK2A The digital logic circuitry is powered from the same voltage as the AD7472.LK3A CLKIN signal is provided by the EVAL-CONTROL BOARD via J1.LK4A CONVST signal is provided by the EVAL-CONTROL BOARD via J1.LK5A RD signal is provided by the EVAL-CONTROL BOARD via J1.LK6A CS signal is provided by the EVAL-CONTROL BOARD via J1.LK7A AD7472 VDRIVE pin is connected to the AD7472 DVDD pin.LK8B V DD is supplied by the EVAL-CONTROL BOARD via J1.LK9B V SS is supplied by the EVAL-CONTROL BOARD via J1.LK10A The AD7472 Vin pin is connected to the output of the bias-up circuit.LK11A Master clock for burst clock generator is provided from the on-board clock oscillator. REV. A–3–EVAL-AD7472CB–4–REV. AEVAL-CONTROL BOARD INTERFACINGInterfacing to the EVAL-CONTROL BOARD is via a 96-way connector, J1. The pinout for the J1 connector is shownin Figure 2 and its pin designations are given in Table II.Connector, J196-Way Connector Pin DescriptionD0-D11Data Bit 0 to Data Bit 11. Three-state TTL outputs. D11 is the MSB.SCLK0Serial Clock Zero. This continuous clock can be connected to the CLKIN pin of the AD7472 via LK3.+5VDDigital +5 V supply. This can be used to provide a separate +5 V supply for the digital logic if required via LK2.R D Read. This is an active low logic input connected to the RD pin of the AD7472 via LK5.C S Chip Select. This is an active low logic input connected to the CS pin of the AD7472 via LK6.FL0Flag zero. This logic input is connected to the CONVST input of the AD7472 via LK4.IRQ2Interrupt Request 2. This is a logic output and is connected to the BUSY logic output on the AD7472.DGNDDigital Ground. These lines are connected to the digital ground plane on the evaluation board. It allows the user to provide the digital supply via the connector along with the other digital signals.AGNDAnalog Ground. These lines are connected to the analog ground plane on the evaluation board.AV SS Negative Supply Voltage. This provides a nega-tive supply to the on-board op-amps via LK9.AV DDPositive Supply Voltage. This provides a positive supply to the op-amps, the reference, the AD7472and the digital logic.When interfacing directly to the EVAL-CONTROL BOARD,all power supplies and control signals are generated by the EVAL-CONTROL BOARD. However, due to the nature of the DSP interface on the EVAL-CONTROL BOARD,AD7472 sampling rates greater than 400 KHz are not supported when interfacing the EVAL-AD7472CB directly to the EVAL-CONTROL BOARD. To achieve sample rates greater than 400 KHz, the HSC-INTERFACE BOARD must be used. The HSC-INTERFACE BOARD is a board designed to interface between evaluation boards for high speed analog-to-digital converters and the EVAL-CON-TROL BOARD. It can be ordered from Analog Devices through the normal channels using the part number "HSC-INTERFACE BOARD".Table II. 96-Way Connector Pin Functions.ROW AROWBROWC12D03D14DGNDDGND DGND5D26D37SCLK0D4SCLK08+5VD +5VD +5VD 9R D D510D6C S 11D712DGND DGND DGND 13D814D915D1016DGND DGND DGND 17FL0D11IRQ2181920DGND DGND DGND 21AGND AGND AGND 22AGND AGND AGND 23AGND AGND AGND 24AGND AGND AGND 25AGND AGND AGND 26AGND AGND AGND27AGND 28AGND 29AGND AGND AGND 30AGND 31 AVSS AVSS AVSS 32AVDD AVDDAVDDNote : The unused pins of the 96-way connector are not shown.EVAL-AD7472CBREV. A –5–HIGH SPEED CONVERTER (HSC) BOARD INTERFACINGInterfacing to the HSC BOARD is via a 40-way connector,J4. The pinout for the J4 connector is shown in Figure 3 and its pin designations are given in Table III.123940 Figure 3. Pin Configuration for the 40-pin HSCInterface Connector, J1Table III. HSC Interface Connector Pin Functions.Pin No.Function Pin No.Function 1D112G N D 3D104G N D 5D96G N D 7D88G N D 9D710G N D 11D612G N D 13D514G N D 15D416G N D 17D318G N D 19D220G N D 21D122G N D 23D024G N D 25N/C 26G N D 27N/C 28G N D 29N/C 30G N D 31N/C 32G N D 33BUSY 34G N D 35N/C 36G N D 37N/C 38G N D 39N/C40G N DN/C = Not Connected.40-Way Connector Pin DescriptionD0-D11Data Bit 0 to Data Bit 11. Three-state TTL outputs. D11 is the MSB.BUSYBUSY. This is a logic output and is connected to the BUSY logic output on the AD7472 via an inverting buffer.G N DGround. These lines are connected to the digital ground plane on the evaluation board.When interfacing to the High Speed Converter Interface board, all required power supplies must be supplied from external sources via the power terminal, J2.The CLKIN signal can be generated on-board (using the crystal oscillator or the burst clock generator circuit) or provided externally via SK1.The RD and CS inputs to the AD7472 must all be tied low using LK5 and LK6 respectively.The CONVST signal must be provided externally via SK1.Due to the 25 MHz on-board crystal (not the maximum of 26 MHz as specified in the datasheet) the throughput rate will not meet the maximum datasheet specification of 1.5 MSPS.Refer to the documentation included with the HSC-INTER-FACE BOARD for more information. Note, the HSC-INTERFACE BOARD was designed for other high speed ADC devices but it is compatible with the AD7472 evalua-tion system.EVAL-AD7472CB–6–REV. ASOCKETSThere are four input sockets relevant to the operation of the AD7472 on this evaluation board. The function of these sockets is outlined in Table IV.Table IV. Socket FunctionsSocket FunctionSK1Sub-Miniature BNC Socket for external clock input.SK2Sub-Miniature BNC Socket for external CONVST input.SK3Sub-Miniature BNC Socket for Bipolar ana-log input The AD7472 can only accept analog inputs in the range 0 V to REFIN. Bipolar analog inputs in the range -1.25 V to +1.25 V applied to this socket are biased up to the acceptable AD7472 input range by the on-board bias-up circuit before being applied to the AD7472 VIN pin.SK5Sub-Miniature BNC Socket for unipolar ana-log input. Analog inputs in the acceptable AD7472 analog input range (0 V to REFIN)are applied to this socket. The signal is then buffered before it is applied to the AD7472VIN pin.CONNECTORSThere are four connectors on the AD7472 evaluation board as outlined in Table V.Table V. Connector FunctionsConnector FunctionJ196-Way Connector for EVAL-CONTROL BOARD interface connections.J2External VDD, VSS & AGND power connec-tor.J3External VDRIVE & DGND power connec-tor.J440-Way Connector for HIGH SPEED CON-VERTER INTERFACE BOARD connec-tions.OPERATING WITH THE EVAL-CONTROL BOARDThe evaluation board can be operated in a stand-alone mode or operated in conjunction with the EVAL-CONTROL BOARD (with or without the HSC-INTERFACE BOARD).This EVAL-CONTROL BOARD is available from Analog Devices under the order entry "EVAL-CONTROL BOARD".When interfacing directly to this control board, all supplies and control signals to operate the AD7472 are provided by the EVAL-CONTROL BOARD when it is run under control of the AD7472 software which is provided with the AD7472evaluation board package. This EVAL-CONTROL BOARD will also operate with all Analog Devices evaluation boards which end with the letters CB in their title.The 96-way connector on the EVAL-AD7472CB plugs directly into the 96-way connector on the EVAL-CON-TROL BOARD. No power supplies are required in the system. The EVAL-CONTROL BOARD generates all the required supplies for itself and the EVAL-AD7472CB. The EVAL-CONTROL BOARD is powered from a 12 V AC transformer. This is a standard 12 V AC transformer capable of supplying 1 A current and is available as an accessory from Analog Devices under the following part numbers:EVAL-110VAC-US:For use in the U.S. or Japan EVAL-220VAC-UK:For use in the U.K.EVAL-220VAC-EU:For use in EuropeThese transformers are also available for other suppliers including Digikey (U.S.) and Campbell Collins (U.K.).Connection between the EVAL-CONTROL BOARD and the serial port of a PC is via a standard RS-232 cable which is provided as part the EVAL-CONTROL BOARD pack-age. Please refer to the manual which accompanies the EVAL-CONTROL BOARD for more details on the EVAL-CONTROL BOARD package.EVAL-AD7472CBREV. A–7–Figure 4. Main ScreenSOFTWARE DESCRIPTIONIncluded in the EVAL-AD7472CB evaluation board pack-age is a PC-compatible disk. This disk has two sub-directo-ries called EVAL_CTRL and HSC_INT, each containing software for controlling and evaluating the performance of the AD7472 when it is operated with the EVAL-CONTROL BOARD or the HSC-INTERFACE BOARD. The EVAL-AD7472CB Demonstration/Evaluation Software runs under DOS 4.0 or later and requires a minimum of a 386-based machine with 400kB of base RAM and 500kB of free hard disk space. The user interface on the PC is a dedicated program written especially for the AD7472.The disk which accompanies the EVAL-AD7472CB con-tains two sub-directories. The user should create a new directory on the main PC drive and label this "AD7472".Then, the sub-directories (and all files contained within them) on the EVAL-AD7472CB disk should be copied into this directory. The Mouse Driver on the PC should be enabled before running the software. If this has not been loaded, the program will not run.To run the software, simply make the AD7472\EVAL_CTL directory or the AD7472\HSC_INT directory (depending on which setup is being used) the current directory and type "go". When the evaluation program starts, the user sees the screen shown on Figure 3 (without any FFT or scope waveforms). This is the main screen and it is divided into three parts. The top part provides the main control interface for the AD7472 evaluation software. The middle part of the main screen functions as a Digital Storage Oscilloscope and the bottom part of the main screen operates as either a Digital Spectrum Analyzer or a Histogram analyzer.Each part of the screen has several buttons that can be pressed by using the mouse or the keyboard. To press a button using the mouse, simply use it to move the on-screen pointer to the button to be activated and click. To use the keyboard, simply press the appropriate key as highlighted on the button. Lower case letters must be used. When a button is pressed, it is highlighted on the screen. The next button can be high-lighted by using the Tab key or the previous button by holding down the shift key and the Tab key together. The highlighted button can also be pressed by pressing the space bar. Pressing the ESC key halts any operation currently in progress. In this document, if a button can be activated from the keyboard then the key used is shown in bold in the button name. For example, "no p rog" has the "p" highlighted in bold, indicating that the button can be activated by pressing the p key.Some buttons have a red indicator. A red indicator on the button means that the function associated with that button is on. Absence of the red indicator light means that the function associated with the button is off. The on/off status of these buttons is changed simply by selecting the button.Setting up the EVAL-CONTROL BOARDWhen the software is run, the "F2 Setup" button in the top left of the screen should be selected to pop up the setup menu (see fig. 4). This menu sets up the EVAL-CONTROL BOARD for use with the EVAL-AD7472CB.Firstly, a configuration file must be chosen. The configura-tion file contains the default configuration information for the EVAL-CONTROL BOARD, the Digital Spectrum Analyzer and the Digital Storage Oscilloscope. It also tells the AD7472.EXE software which .HIP file to download to the ADSP-2111. The .HIP file contains the DSP code which is executed by the ADSP-2111. Normally, the "no p rog"button is off, so when the configuration file is loaded, the .HIP file is automatically downloaded to the ADSP-2111.However, if the "no p rog" button is on, then the .HIP file isnot downloaded to the ADSP-2111.EVAL-AD7472CB–8–REV. AUse the mouse or the keyboard to highlight the configuration file and load it by clicking the "l oad" button.The "Analog in" section shows the analog input range and DC offset voltage.The user can then select the required number of samples and sampling frequency. Note: While the AD7472 data sheet specifies a maximum clock frequency of 26 MHz, the on-board crystal oscillator outputs a 25MHz clock. Therefore the max. sampling frequency will be less than that specified on the data sheet. An external clock frequency (up to the max specified on the data sheet) can be applied via the external socket, SK1.Click the OK button to return to the main screen.MAIN SCREENThe top left part of the main screen contains eight buttons which are selected using the mouse or by using the function keys from the keyboard. These buttons and the actions they perform are:F1:Info. This button shows information on the software.F2:Setup. This button activates the setup menu.F3:Samp. When this key is pressed, the software causes the AD7472 to perform a number of conversions as determined by the setup menu (see above). The data from these conversions is then analyzed by the AD7472evaluation software. Another set of samples may be taken by pressing the F3 key again.F4:Cont. Pressing this button causes the software to repeatedly perform conversions and analyze them.Once the conversions and analysis has been done for one set of samples, the software automatically repeats the process. It continues to do this until the ESC key is pressed.saved in the "binary" format are for viewing purposes only.F6:Load. This allows the user to load data from a file with a .DAT extension. Only data that was saved as ints can be loaded and analyzed. A configuration file must be loaded via the "F2 Setup" menu before the data file can be analyzed. If there is no EVAL-CONTROL BOARD connected to the PC, then the "no p rog" button in the "F2 Setup" menu must be on.Once a configuration file has been loaded, the data loaded from the .DAT file is analyzed according to the settings in the "F2 Setup" menu.F7:Reset. Choosing this option resets the EVAL-CON-TROL BOARD.F10:Quit. This quits the AD7472 evaluation software and returns control to the operating system.INFORMATION WINDOWSThere are three information windows at the top of the main screen. The left-hand window is the configuration window and gives details about part being evaluated. It shows the name of the program that has been downloaded to the EVAL-CONTROL BOARD, the sampling frequency, the number of bits, the analog input range of the part and the output code format of the part. The right-hand large window is the Status window. This window provides feedback to the user as to what operations are currently being performed by the soft-ware and also displays error messages.Test ModeAt the top right of the main screen are the Test Mode buttons.These buttons determine what sort of testing is done on the samples captured by the software. Both an ac analysis and dc analysis can be performed. The function of these buttons are:f ft plotChoosing this button causes the Digital Spec-trum Analyzer to appear at the bottom of the screen.Histo g ram:Choosing this button causes the Histogram Analyzer to be displayed at the bottom of the screen.There is one other button near the top of the screen, beside the "F10 Quit" button. This is:blackman-harris: When performing a Fourier transformof the sampled data, this button determines whether or not the data is windowed by a blackman-harris window before the transform. When this button is on, the data is windowed. When this button is off,the data isn't windowed. See the Digital Spectrum Analyzer section for more details.F5:Save. This saves a set of samples to a file for use either at a later date or with other software. The samples can be saved either as "volts", "ints" or "binary". The format of all these files is ASCII text. Note that the AD7472 software can only load files saved in the "ints"format. Files saved in the "volts" and "ints" formats can be used with packages such as Mathcad. FilesFigure 5. Setup Menu ScreenEVAL-AD7472CBREV. A –9–Figure 6 Histogram ScreenDIGITAL STORAGE OSCILLOSCOPE.When samples of data are captured, they are displayed on the Digital Storage Oscilloscope. If the b lackman-harris button is turned on then the windowed data is also displayed on the oscilloscope. The 'scope has been designed to act in a similar way as a conventional oscilloscope. To the right of the oscilloscope are several buttons that control the manner in which data is displayed on the 'scope. The timebase for the oscilloscope is automatically chosen by the software if the Time/Div "Auto" button is on. The user can also select the timebase by clicking in the Time/Div window and scrolling up and down through the possible timebases. Similarly, the vertical scale of the oscilloscope is chosen automatically if the Volt/Div "Auto" button is on. The user also has the option of selecting the desired vertical scale in a similar manner to selecting the timebase.The other buttons associated with the oscilloscope are:g r id This button toggles the grid display of the oscillo-scope on and off.a xis This button toggles the axis display of the oscillo-scope on and off t ext This button toggles the text displayed on the oscil-loscope screen on and off.l ine When the line button is on, the displayed samplesare joined together by lines. When this button is off,the samples are displayed as points.a c When this button is on, the dc component of thesampled signal is removed and the signal is dis-played. This has the effect of centering the signal vertically on the oscilloscope screen. When this button is off, the dc component is not removed andthe signal is displayed with its horizontal axis corresponding to a code of 0. The a c display option is useful for zooming in on a low-level signal that has a large dc offset.d ualWhen the "d ual" button is on, the oscilloscope screen is divided into two parts with the sampled data display centered on one horizontal axis and the windowed data display centered on another. When the "d ual" button is off, both traces are centered on the same horizontal axis.1This button toggles the sampled data trace on and off.2This button toggles the windowed data trace on and off.HISTOGRAM ANALYZERThe histogram analyzer counts the number of occurrences of each code in the captured samples and displays a histogram of these counts. The most frequently occurring code is displayed in the center of the histogram. The analyzer is normally used with a dc input signal and calculates the mean and the standard deviation of the sampled data. The mean and standard deviation are displayed in both volts and in units of the lsb size of the converter. The histogram gives a good indication of the dc noise performance of the ADC. The standard deviation shows directly the noise introduced in theconversion process.。

半导体传感器AD7470ARUZ中文规格书